# SN65HVD64 AISG® 开关键控同轴调制解调器收发器

# 1 特性

- 3V 至 5.5V 电源范围

- 1.6V 至 5.5V 独立逻辑电源

- - 15dBm 至 +5dBm 宽输入动态范围 接收器

- 可在 0dBm 至 6dBm 范围内调节 驱动器为同轴电缆提供的功率

- 支持 AISG<sup>®</sup> V2.0 和 V3.0

- 低功耗待机模式

- 针对 RS-485 总线仲裁的 方向控制输出

- 支持高达 115kbps 的信号传输速率

- 集成有源带诵滤波器的中心频率 为 2.176MHz

- 支持 -40℃ 至 120℃ 环境温度

- 3mm × 3mm 16 引脚 VQFN 封装

### 2 应用

- AISG 针对天线线路器件的接口

- 塔顶放大器 (TMA)

- 普通调制解调器 (Modem) 接口

# 3 说明

SN65HVD64 收发器对逻辑(基带)接口和适用于长同 轴介质的频率之间的信号进行调制和解调,以便无线设 备之间进行有线数据传输。

SN65HVD64 器件是一款集成 AISG 收发器,旨在满足 "天线接口标准组织 v2.0 和 v3.0 规范"的要求。

SN65HVD64 接收器集成了一个有源带通滤波器,这样 即使存在寄生频率组件仍然能够解调信号。该滤波器的 中心频率为 2.176MHz。

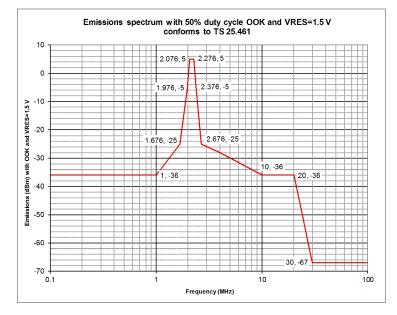

发送器支持在 +0dBm 至 6dBm 的范围内调节为 50  $\Omega$ 同轴电缆提供的输出功率。SN65HVD64 发送器符合 AISG 标准针对发射频谱的要求。

该器件提供的方向控制输出使得对 RS-485 接口的总线 仲裁更加便捷。该器件为晶振集成了一个振荡器输入, 并且接受到振荡器的标准时钟输入。

|           | 器件信息              |                 |

|-----------|-------------------|-----------------|

| 器件型号      | 封装 <sup>(1)</sup> | 封装尺寸(标称值)       |

| SN65HVD64 | VQFN (16)         | 3.00mm × 3.00mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

# **Table of Contents**

| 1 特性                                 | 1  |

|--------------------------------------|----|

| 2 应用                                 | 1  |

| 3 说明                                 | 1  |

| 4 Revision History                   |    |

| 5 Pin Configuration and Functions    | 3  |

| 6 Specifications                     |    |

| 6.1 Absolute Maximum Ratings         | 4  |

| 6.2 ESD Ratings                      | 4  |

| 6.3 Recommended Operating Conditions |    |

| 6.4 Thermal Information              | 5  |

| 6.5 Electrical Characteristics       | 6  |

| 6.6 Switching Characteristics        | 7  |

| 6.7 Typical Characteristics          | 8  |

| 7 Parameter Measurement Information  | 11 |

| 8 Detailed Description               |    |

| 8.1 Overview                         | 14 |

| 8.2 Functional Block Diagram         | 14 |

| 8.3 Feature Description                               | .14  |

|-------------------------------------------------------|------|

| 8.4 Device Functional Modes                           |      |

| 9 Application and Implementation                      | . 17 |

| 9.1 Application Information                           | . 17 |

| 9.2 Typical Application                               | . 18 |

| 10 Power Supply Recommendations                       |      |

| 11 Layout                                             | .21  |

| 11.1 Layout Guidelines                                |      |

| 11.2 Layout Example                                   |      |

| 12 Device and Documentation Support                   |      |

| 12.1 Documentation Support                            |      |

| 12.2 Receiving Notification of Documentation Updates. | .22  |

| 12.3 Support Resources                                | . 22 |

| 12.4 Trademarks                                       |      |

| 12.5 Electrostatic Discharge Caution                  |      |

| 12.6 Glossary                                         |      |

| ,                                                     |      |

# **4** Revision History

| DATE         | REVISION | NOTES            |  |  |

|--------------|----------|------------------|--|--|

| October 2020 | *        | Initial release. |  |  |

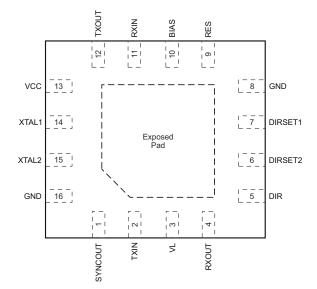

# **5** Pin Configuration and Functions

#### 表 5-1. Pin Functions

|                 | PIN |      | DESCRIPTION                                                                                                        |  |  |

|-----------------|-----|------|--------------------------------------------------------------------------------------------------------------------|--|--|

| NAME            | NO. | TYPE | DESCRIPTION                                                                                                        |  |  |

| BIAS            | 10  | 0    | Bias voltage output for setting driver output power by external resistors                                          |  |  |

| DIR             | 5   | 0    | Direction control output signal for bus arbitration                                                                |  |  |

| DIRSET1         | 7   | —    | DIRSET1 and DIRSET2: Bits to set the duration of DIR                                                               |  |  |

| DIRSET2         | 6   | _    | DIRSET[2:1]: [L:L] = 9.6 kbps; [L:H] = 38.4 kbps; [H:L] = 115 kbps; [H:H] = standby mode                           |  |  |

| CND             | 8   |      | Ground                                                                                                             |  |  |

| GND             | 16  |      | Glound                                                                                                             |  |  |

| RES             | 9   | Р    | Input voltage to adjust driver output power that is set by external resistors from BIAS pin to GND                 |  |  |

| RXIN            | 11  | I    | Modulated input signal to the receiver                                                                             |  |  |

| RXOUT           | 4   | 0    | Digital data bit stream from receiver                                                                              |  |  |

| SYNCOUT         | 1   | 0    | Open-drain output to synchronize other devices to the 4x-carrier oscillator at XTAL1 and XTAL2                     |  |  |

| TXIN            | 2   | I    | Digital data bit stream to driver                                                                                  |  |  |

| TXOUT           | 12  | 0    | Modulated output signal from the driver                                                                            |  |  |

| V <sub>CC</sub> | 13  | Р    | Analog supply voltage for the device                                                                               |  |  |

| VL              | 3   | Р    | Logic supply voltage for the device                                                                                |  |  |

| XTAL1           | 14  | I/O  | I/O pins of the crystal oscillator. Connect a 4 × f <sub>C</sub> crystal between these pins or connect XTAL1 to an |  |  |

| XTAL2           | 15  |      | 8.704-MHz clock and connect XTAL2 to GND.                                                                          |  |  |

| EP              | _   | _    | Exposed pad. Connection to ground plane is recommended for best thermal conduction.                                |  |  |

### 6 Specifications

#### 6.1 Absolute Maximum Ratings

#### See (1)

|                                                      | MIN                         | MAX                   | UNIT |

|------------------------------------------------------|-----------------------------|-----------------------|------|

| Supply voltage, V <sub>CC</sub> and VL               | - 0.5                       | 6                     | V    |

| Voltage at coax pins                                 | - 0.5                       | 6                     | V    |

| Voltage at logic pins                                | - 0.3                       | V <sub>VL</sub> + 0.3 | V    |

| Logic output current                                 | - 20                        | 20                    | mA   |

| TXOUT output current                                 | Internally limited          |                       |      |

| SYNCOUT output current                               | Internall                   | y limited             |      |

| Junction temperature, T <sub>J</sub>                 |                             | 170                   | °C   |

| Continuous total power dissipation                   | See the Thermal Information |                       | °C   |

| Storage temperature, T <sub>stg</sub> <sup>(2)</sup> | - 65                        | 150                   | °C   |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Applicable before the device is installed in the final product.

#### 6.2 ESD Ratings

|   |                    |                         |                                                                   | VALUE | UNIT |   |

|---|--------------------|-------------------------|-------------------------------------------------------------------|-------|------|---|

| • | V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000 | V    | ĺ |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### **6.3 Recommended Operating Conditions**

|                    |                                                          |                         | MIN                | NOM   | MAX               | UNIT |

|--------------------|----------------------------------------------------------|-------------------------|--------------------|-------|-------------------|------|

| V <sub>CC</sub>    | Analog supply voltage                                    |                         | 3                  |       | 5.5               | V    |

| VL                 | Logic supply voltage                                     |                         | 1.6                |       | 5.5               | V    |

| V <sub>I(pp)</sub> | Input signal amplitude at RXIN                           |                         |                    |       | 1.12              | Vpp  |

| V                  | High-level input voltage                                 | TXIN, DIRSET1, DIRSET2  | 70%V <sub>L</sub>  |       | VL                | V    |

| V <sub>IH</sub>    |                                                          | XTAL1, XTAL2            | 70%V <sub>CC</sub> |       | V <sub>CC</sub>   | v    |

| V                  |                                                          | TXIN, DIRSET1, DIRSET2  | 0                  |       | 30%V <sub>L</sub> | V    |

| VIL                | Low-level input voltage                                  | XTAL1, XTAL2            | 0                  |       | $30\%V_{CC}$      | v    |

| 1/t <sub>UI</sub>  | Data signaling rate                                      |                         | 9.6                |       | 115               | kbps |

| F <sub>OSC</sub>   | Oscillator frequency                                     |                         | – 30 ppm           | 8.704 | 30 ppm            | MHz  |

| 7                  | Load impedance between TXOUT to RXIN                     |                         |                    | 50    |                   | Ω    |

| Z <sub>LOAD</sub>  | Load impedance between RXIN and GND at $f_{C}$ (channel) |                         |                    | 50    |                   | Ω    |

| R1                 | Bias resistor between BIAS an                            | d RES                   |                    | 4.1   |                   | kΩ   |

| R2                 | Bias resistor between RES and                            | d GND                   |                    | 10    |                   | kΩ   |

| R <sub>SYNC</sub>  | Pullup resistor between SYNC                             | OUT and V <sub>CC</sub> |                    | 1     |                   | kΩ   |

| V <sub>RES</sub>   | Voltage at RES pin                                       |                         | 0.7                |       | 1.5               | V    |

| C <sub>C</sub>     | Coupling capacitance betweer                             | RXIN and coax (channel) |                    | 220   |                   | nF   |

| C <sub>BIAS</sub>  | Capacitance between BIAS an                              | d GND                   |                    | 1     |                   | μF   |

| T <sub>A</sub>     | Operating free-air temperature                           |                         | - 40               |       | 120               | °C   |

| TJ                 | Junction temperature                                     |                         | - 40               |       | 125               | °C   |

#### 6.4 Thermal Information

|                      | THERMAL METRIC <sup>(1)</sup>                | VQFN        | UNIT |

|----------------------|----------------------------------------------|-------------|------|

|                      |                                              | RGT 16 Pins | UNIT |

| R <sub>0 JA</sub>    | Junction-to-ambient thermal resistance       | 49.4        | °C/W |

| R <sub>0</sub> JCtop | Junction-to-case (top) thermal resistance    | 64.2        | °C/W |

| R <sub>0 JB</sub>    | Junction-to-board thermal resistance         | 22.9        | °C/W |

| ΨJT                  | Junction-to-top characterization parameter   | 1.7         | °C/W |

| ψ <sub>JB</sub>      | Junction-to-board characterization parameter | 22.9        | °C/W |

| R <sub>0</sub> JCbot | Junction-to-case (bottom) thermal resistance | 25          | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### **6.5 Electrical Characteristics**

over recommended operating conditions (unless otherwise noted)

|                           | PARAMETER                                      | ,                                                                                                                          | ONDITIONS                            | MIN                | TYP   | MAX                | UNIT            |  |

|---------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------|-------|--------------------|-----------------|--|

| POWER SI                  |                                                |                                                                                                                            |                                      |                    |       |                    |                 |  |

|                           |                                                |                                                                                                                            | TXIN = L (active)                    |                    | 28    | 33                 |                 |  |

|                           |                                                | DIRSET1 = L                                                                                                                | TXIN = H (quiescent)                 |                    | 25    | 31                 |                 |  |

| I <sub>CC</sub>           | Supply current                                 | DIRSET2 = H                                                                                                                | TXIN = 115 kbps,<br>50% duty cycle   |                    | 27    | 33                 | mA              |  |

|                           |                                                | DIRSET1 = H, DIRSET2 =                                                                                                     |                                      |                    | 12    | 17                 |                 |  |

| I <sub>VL</sub>           | Logic supply current                           | TXIN = H, RXIN = DC inpu                                                                                                   |                                      |                    |       | 50                 | μA              |  |

| PSRR                      | Receiver power supply rejection ratio          | V <sub>TXIN</sub> = V <sub>L</sub>                                                                                         |                                      | 45                 | 60    |                    | dB              |  |

| T <sub>SD RISE</sub>      | Thermal shutdown rising                        |                                                                                                                            |                                      | 143                | 156   | 170                | °C              |  |

| T <sub>SD FALL</sub>      | Thermal shutdown falling                       |                                                                                                                            |                                      | 123                | 136   | 147                | °C              |  |

| T <sub>SD HYS</sub>       | Thermal shutdown hysteresis                    |                                                                                                                            |                                      | 18                 | 20    | 23                 | °C              |  |

| LOGIC PIN                 | IS                                             |                                                                                                                            |                                      |                    |       |                    |                 |  |

| V <sub>OH</sub>           | High-level logic output voltage (RXOUT, DIR)   | $I_{OH} = -4 \text{ mA for } V_L > 2.4$<br>$I_{OH} = -2 \text{ mA for } V_L < 2.4$                                         |                                      | 90%V <sub>VL</sub> |       |                    | V               |  |

| V <sub>OL</sub>           | Low-level logic output voltage<br>(RXOUT, DIR) | $I_{OL} = 4 \text{ mA for } V_L > 2.4 \text{ V},$<br>$I_{OL} = 2 \text{ mA for } V_L < 2.4 \text{ V}$                      |                                      |                    |       | 10%V <sub>VL</sub> | V               |  |

| COAX DRI                  | VER                                            |                                                                                                                            |                                      |                    |       |                    |                 |  |

|                           | Peak-to-peak output voltage at device pin      | V <sub>RES</sub> = 1.5 V (Maximum s                                                                                        | etting)                              | 2.24               | 2.5   |                    |                 |  |

| V <sub>O(PP)</sub>        | TXOUT<br>(see 图 7-1)                           | V <sub>RES</sub> = 0.7 V (Minimum se                                                                                       | tting)                               |                    | 1.17  | 1.3                | V <sub>PP</sub> |  |

| Manag                     | Peak-to-peak voltage at coax out               | V <sub>RES</sub> = 1.5 V                                                                                                   |                                      | 5                  | 6     |                    | dBm             |  |

| V <sub>O(PP)</sub>        | (see 图 7-1)                                    | V <sub>RES</sub> = 0.7 V                                                                                                   |                                      |                    | - 0.6 | 0.3                |                 |  |

| V <sub>O(OFF)</sub>       | Off-state output voltage                       | At TXOUT                                                                                                                   |                                      |                    |       | 1                  | mVpp            |  |

| VO(OFF)                   | On-state output voltage                        | At coax out                                                                                                                |                                      |                    |       | - 60               | dBm             |  |

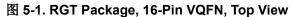

|                           | Output emissions                               | Coupled to coaxial cable with characteristic impedance of 50 $^{\Omega}$ , as shown in 🔀 6-1 $^{(1)}$ $^{(2)}$             |                                      |                    |       |                    | N/A             |  |

| f <sub>O</sub>            | Output frequency                               |                                                                                                                            |                                      |                    | 2.176 |                    | MHz             |  |

| Δf                        | Output frequency variation                     |                                                                                                                            |                                      | - 100              |       | 100                | ppm             |  |

| 7                         | Output impedance                               | At 100 kHz                                                                                                                 |                                      |                    | 0.03  |                    |                 |  |

| Z <sub>O</sub>            | Output impedance                               | At 10 MHz                                                                                                                  |                                      |                    | 3.5   |                    | Ω               |  |

| I <sub>OS</sub>           | Short-circuit output current                   | TXOUT is also protected to circuit during short-circuit                                                                    |                                      |                    | 300   | 450                | mA              |  |

| COAX REC                  | EIVER                                          |                                                                                                                            |                                      |                    |       | ·                  |                 |  |

| VIT                       | Input threshold                                | f <sub>IN</sub> = 2.176 MHz                                                                                                |                                      | 79                 | 112   | 158                | mVPP            |  |

| v∏                        |                                                |                                                                                                                            |                                      | - 18               | - 15  | - 12               | dBm             |  |

| Z <sub>IN</sub>           | Input impedance                                | f = f <sub>O</sub>                                                                                                         |                                      | 11                 | 21    |                    | kΩ              |  |

| RECEIVER                  | FILTER                                         |                                                                                                                            |                                      |                    |       |                    |                 |  |

| f <sub>PB</sub>           | Passband                                       | VRXIN = 1.12VP_P                                                                                                           |                                      | 1.1                |       | 4.17               | MHz             |  |

| f <sub>REJ</sub>          | Receiver rejection range                       | 2.176-MHz carrier amplitude of 112.4 mV <sub>PP</sub> ,<br>frequency band of spurious components with 800<br>mVPP allowed. |                                      | 1.1                |       | 4.17               | MHz             |  |

|                           | Receiver noise filter time (slow bit rate)     | DIRSET for 9.6 kbps                                                                                                        |                                      |                    | 4     |                    | μs              |  |

| t <sub>noise</sub> filter | Receiver noise filter time (fast bit rate)     | DIRSET for > 9.6 kbps                                                                                                      |                                      |                    | 2     |                    | μs              |  |

| XTAL AND                  | SYNC                                           |                                                                                                                            |                                      |                    |       |                    |                 |  |

| lı                        | Input leakage current                          | XTAL1, XTAL2, 0V < V <sub>IN</sub> <                                                                                       | V <sub>CC</sub>                      | - 15               |       | 15                 | μA              |  |

| V <sub>OL</sub>           | Output low voltage                             | SYNCOUT, with 1-kΩ resi                                                                                                    | stor from SYNCOUT to V <sub>CC</sub> |                    |       | 0.4                | V               |  |

(1) Specified by design with a recommended 470-pF capacitor between RXIN and GND. Measurements above 150 MHz are determined by setup.

(2) Conforms to AISG spectrum emissions mask, 3GPP TS 25.461, see 7-3.

# 6.6 Switching Characteristics

over recommended operating conditions (unless otherwise noted)

| PARAMETER                           |                                          | TEST CONDITIONS                                                                      |     | TYP  | MAX | UNIT |  |

|-------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------|-----|------|-----|------|--|

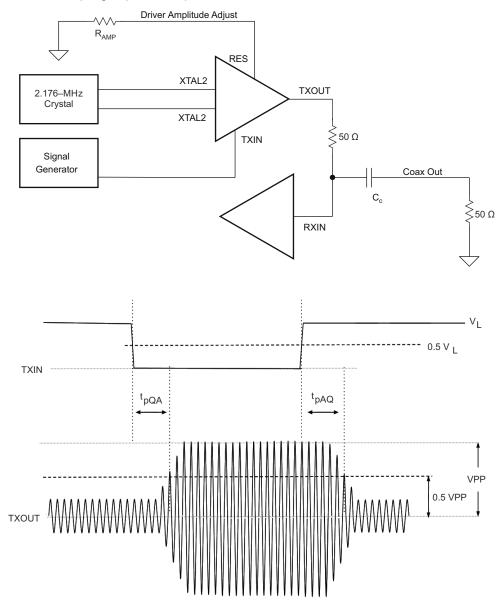

| t <sub>pAQ</sub> , t <sub>pQA</sub> | Coax driver propagation delay            | See 图 7-1                                                                            |     |      | 5   | μs   |  |

| t <sub>r</sub> , t <sub>f</sub>     | Coax receiver output rise/fall time      | C <sub>L</sub> = 15 pF, R <sub>L</sub> = 1 kΩ; see 图 7-1                             |     |      | 20  | ns   |  |

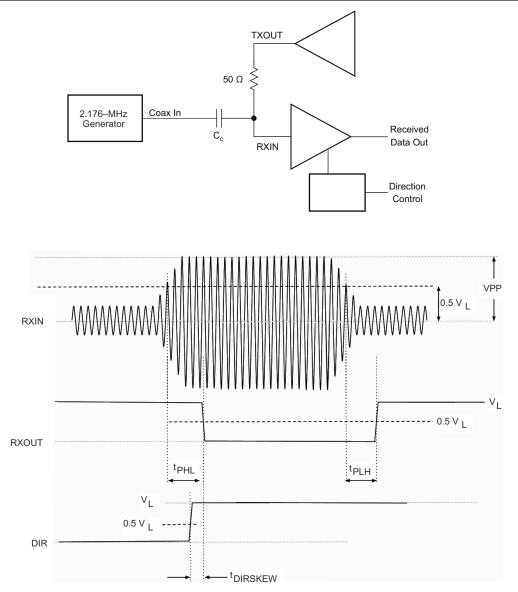

| t <sub>PHL</sub> , t <sub>PLH</sub> | Receiver propagation delay               | See 图 7-2                                                                            |     | 5.5  | 11  | μs   |  |

|                                     |                                          | V <sub>RXIN(ON)</sub> = 630 mVpp, V <sub>RXIN(OFF)</sub> < 5 mVpp,<br>50% duty cycle | 40% |      | 60% |      |  |

|                                     | Coax receiver output duty cycle          | V <sub>RXIN(ON)</sub> = 200 mVpp, V <sub>RXIN(OFF)</sub> < 5 mVpp,<br>50% duty cycle | 40% |      | 60% |      |  |

|                                     | Direction control active duration        | DIRSET2 = GND or OPEN, DIRSET1 = GND<br>or OPEN                                      |     | 1667 |     |      |  |

| t <sub>DIR</sub>                    |                                          | DIRSET2 = GND, DIRSET1 = VL                                                          | i   | 417  |     | μs   |  |

|                                     |                                          | DIRSET2 = VL, DIRSET1 = VL                                                           |     | 137  |     |      |  |

| t <sub>DIRSKEW</sub>                | Direction control skew<br>(DIR to RXOUT) |                                                                                      | 270 |      |     | ns   |  |

| t <sub>dis</sub>                    | Standby disable delay                    | 300 mV <sub>PP</sub> at 2.176 MHz on RXIN                                            | 2   |      | ms  |      |  |

| t <sub>en</sub>                     | Standby enable delay                     | 300 mV <sub>PP</sub> at 2.176 MHz on RXIN                                            |     | 2    |     | ms   |  |

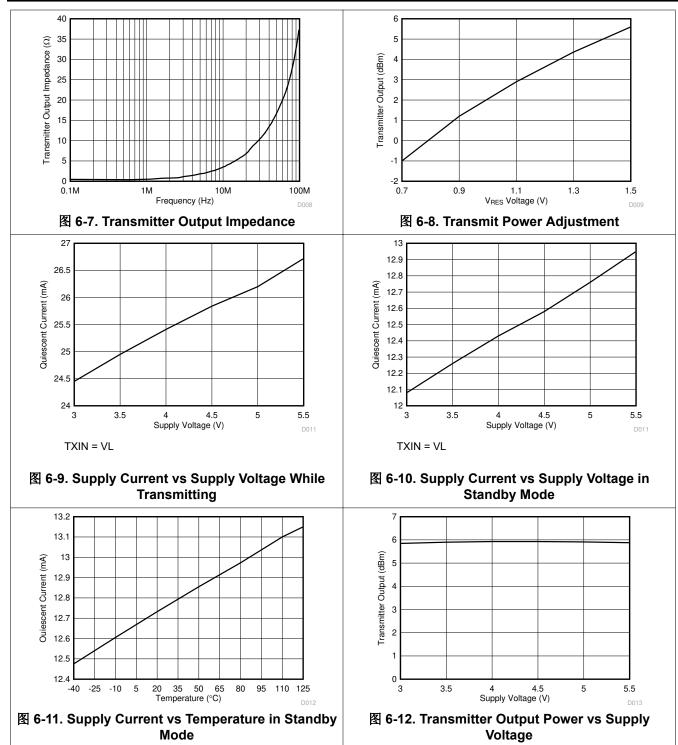

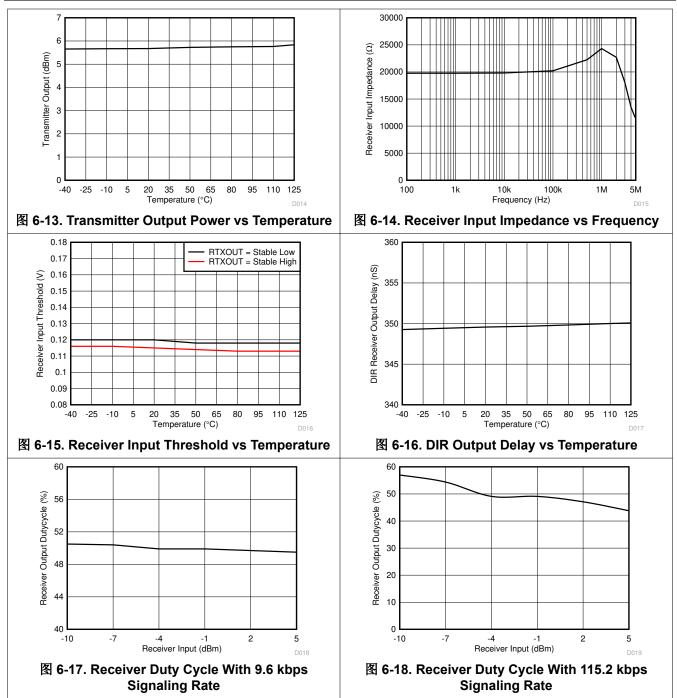

# 6.7 Typical Characteristics

SN65HVD64 ZHCSL88 - OCTOBER 2020

#### **7 Parameter Measurement Information**

Signal generator rate is 115 kbps, 50% duty cycle. Rise and fall times are less than 6 ns, and nominal output levels are 0 V and 3 V. Coupling capacitor,  $C_C$ , is 220 nF.

图 7-1. Measurement of Modem Driver Output Voltage With 50- $\Omega$  Loads

图 7-2. Measurement of Modem Receiver Propagation Delays

图 7-3. AISG Emissions Template

# 8 Detailed Description

#### 8.1 Overview

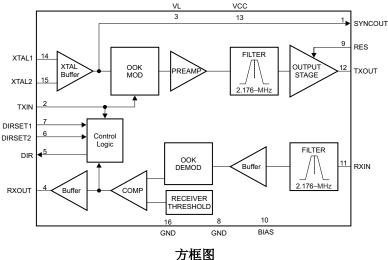

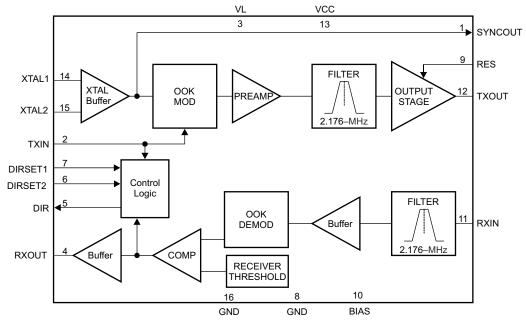

The SN65HVD64 transceiver modulates and demodulates signals between the logic (baseband) and a frequency suitable for long coaxial media. The SN65HVD64 device is an integrated AISG transceiver designed to meet the requirements of the Antenna Interface Standards Group v2.0 and v3.0 specification. The SN65HVD64 receiver integrates an active bandpass filter to enable demodulation of signals even in the presence of spurious frequency components. The filter has a 2.176-MHz center frequency. The transmitter supports adjustable output power levels from 0 dBm to 6 dBm delivered to the 50- $\Omega$  coax cable. The SN65HVD64 transmitter is compliant with the spectrum emission requirement provided by the AISG standard. A direction control output facilitates bus arbitration for an RS-485 interface. This device integrates an oscillator input for a crystal, and also accepts standard clock inputs to the oscillator.

#### 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Coaxial Interface

The SN65HVD64 transceiver enables the transfer of data between radio equipment by modulating baseband data to a carrier frequency of 2.176 MHz (per the AISG standard). The transmitter output amplitude can be configured from 0 dBm to 6 dBm in order to communicate over a variety of different links, and the output emissions spectrum is designed to be compliant to AISG limits. The receiver features an active bandpass filter circuit that helps to separate the carrier frequency data from other spurious frequency components.

#### 8.3.2 Reference Input

The 2.176-MHz modulation frequency is derived from an input reference that is nominally 8.704 MHz. The input reference can come either from a crystal or from an oscillator circuit with a tolerance of up to 30 ppm.

#### 8.3.3 RS-485 Direction Control

To facilitate bus arbitration of an RS-485 interface, the SN65HVD64 provides a direction control output that can be used to control the enable/disable controls of an RS-485 transceiver. The direction control output automatically toggles based on activity present on the coaxial input interface, and has an adjustable time constant (controlled by the DIRSET1 and DIRSET2 pins) in order to accommodate various signaling rates.

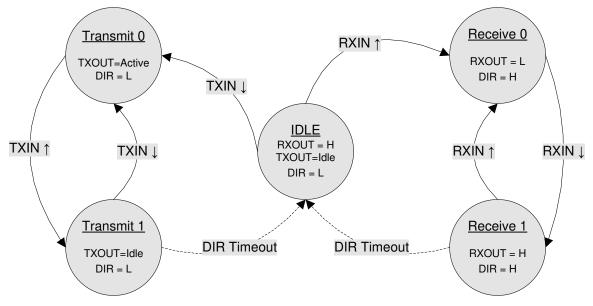

#### 8.4 Device Functional Modes

If DIRSET1 and DIRSET2 are in a logic high state, the device will be in standby mode. While in standby mode, the receiver functions normally, detecting carrier frequency activity on the RXIN pin and setting the RXOUT state. The transmitter circuits are not active in standby mode, thus the TXOUT pin is idle regardless of the logic state of TXIN. The supply current in standby mode is significantly reduced, allowing power savings when the node is not transmitting.

When not in standby mode, the default power-on state is idle. When in idle mode, RXOUT is high, and TXOUT is quiet. The device transitions to receive mode when a valid modulated signal is detected on the RXIN line or the device transitions to transmit mode when TXIN goes low. The device stays in either receive or transmit mode until DIR time-out (nominal 16 bit times) after the last activity on RXOUT or TXIN.

When in receive mode:

- RXOUT responds to all valid modulated signals on RXIN, whether from the local transmitter, a remote transmitter, or long noise burst.

- TXOUT responds to TXIN, generating 2.176-MHz signals on TXOUT when TXIN is low, and TXOUT is quiet when TXIN is high. (In normal operation, TXIN is expected to remain high when the device is in receive mode.)

- The device stays in receive mode until 16 bit times after the last rising edge on RXOUT, caused by valid modulated signal on the RXIN line.

When in transmit mode:

- RXOUT stays high, regardless of the input signal on RXIN.

- TXOUT responds to TXIN, generating 2.176-MHz signals on TXOUT when TXIN is low, and TXOUT is quiet when TXIN is high.

- The device stays in transmit mode until 16 bit times after TXIN goes high.

表 8-1 shows the driver functions. 表 8-2 shows the receiver functions. 图 8-1 shows the transitions between each state.

| TXIN <sup>(1)</sup> | [DIRSET1, DIRSET2]     | тхоит                             | COMMENT           |  |  |  |  |  |  |

|---------------------|------------------------|-----------------------------------|-------------------|--|--|--|--|--|--|

| Н                   | [L,L], [L,H] or [H,L]  | < 1 mV <sub>PP</sub> at 2.176 MHz | Driver not active |  |  |  |  |  |  |

| L                   | נב,בן, נב,דון טרנדו,בן | V <sub>OPP</sub> at 2.176 MHz     | Driver active     |  |  |  |  |  |  |

| Х                   | [H,H]                  | < 1 mV <sub>PP</sub> at 2.176 MHz | Standby mode      |  |  |  |  |  |  |

#### 表 8-1. Driver Function Table

(1) H = High, L = Low, X = Indeterminate

#### 表 8-2. Receiver and DIR Function Table

| RXIN <sup>(1)</sup>                                                      | RXOUT | DIR | COMMENT (see 🔀 8-1)                              |  |  |  |  |  |  |

|--------------------------------------------------------------------------|-------|-----|--------------------------------------------------|--|--|--|--|--|--|

| IDLE mode (not transmitting or receiving)                                |       |     |                                                  |  |  |  |  |  |  |

| < V <sub>IT</sub> at 2.176 MHz for longer than DIR time-out              | Н     | L   | No outgoing or incoming signal                   |  |  |  |  |  |  |

| RECEIVE mode (not already transmitting)                                  |       |     |                                                  |  |  |  |  |  |  |

| < V <sub>IT</sub> at 2.176 MHz for less than t <sub>DIR time-out</sub>   | Н     | Н   | Incoming 1 bit, DIR stays HIGH for DIR time-out  |  |  |  |  |  |  |

| > V <sub>IT</sub> at 2.176 MHz for longer than t <sub>noise filter</sub> | L     | Н   | Incoming 0 bit, DIR output is HIGH               |  |  |  |  |  |  |

| TRANSMIT mode (not already receiving)                                    |       |     |                                                  |  |  |  |  |  |  |

| X                                                                        | Н     | L   | Outgoing message, DIR stays LOW for DIR time-out |  |  |  |  |  |  |

(1) H = High, L = Low, X = Indeterminate

图 8-1. State Transition Diagram

### 9 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 9.1 Application Information

#### 9.1.1 Driver Amplitude Adjust

VTXOUT (V<sub>PP</sub>) =  $(2.5 V_{PP} \times V_{RES} (V)) / 1.5 V V_{RES} (V) = 1.5 V \times R2 / (R1 + R2) V_{TXOUT} (V_{PP}) = 2.5 V_{PP}$  (1) × R2 / (R1 + R2)

The voltage at the RES pin should be from 0.7 V to 1.5 V. Connect RES directly to the BIAS (R1 = 0  $\Omega$ ) for maximum output level of 2.5 VPP. This gives a minimum voltage level at TXOUT of 1.2 VPP, corresponding to about 0 dBm at the coaxial cable. A 1-  $\mu$  F capacitor should be connected between the BIAS pin and GND. To obtain a nominal power level of 3 dBm at the feeder cable as the AISG standard requires, use R1 = 4.1 k $\Omega$  and R2 = 10 k $\Omega$  that provide 1.78 V<sub>PP</sub> at TXOUT.

#### 9.1.2 Direction Control

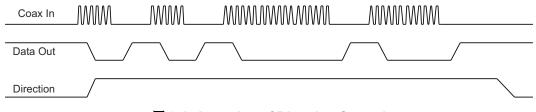

In many applications the mast-top modem that receives data from the base distributes the received data through an RS-485 network to several mast-top devices. When the mast-top modem receives the first logic 0 bit (active modulated signal) it takes control of the mast-top RS-485 network by asserting the direction control signal. The duration of the direction control assertion should be optimized to pass a complete message of length B bits at the known signaling rate  $(1/t_{B|T})$  before relinquishing control of the mast-top RS-485 network. For example, if the messages are 10 bits in length (B=10) and the signaling rate is 9600 bits per second ( $t_{B|T} = 0.104$  ms) then a positive pulse of duration 1.7 ms is sufficient (with margin to allow for network propagation delays) to enable the mast-top RS-485 drivers to distribute each received message.  $\boxed{8}$  9-1 shows the assertion of direction control.

图 9-1. Assertion of Direction Control

#### 9.1.3 Direction Control Time Constant

The time constant for the direction control function can be set by the control mode pins, DIRSET1 and DIRSET2. These pins should be set to correspond to the desired data rate. With no external connections to the control mode pins, the internal time constant is set to the maximum value, corresponding to the minimum data rate.

#### 9.1.4 Conversion Between dBm and Peak-to-Peak Voltage

$$dBm = 20 \times LOG10 [Volts-pp / SQRT(0.008 \times Z_o)] = 20 \times LOG10 [VPP / 0.63] \text{ for } Z_o = 50 \ \Omega$$

(2)

$$VPP = SQRT(0.008 \times Z_o) \times 10^{(dBm/20)} = 0.63 \times 10^{(dBm/20)} \text{ for } Z_o = 50 \ \Omega$$

(3)

$\ddagger$  9-1 shows conversions between dBm and peak-to-peak voltage with a 50- $\Omega$  load, for various levels of interest including reference levels from the 3GPP TS 25.461 Technical Specification.

| SIGNAL ON COAX                  | dBm  | V <sub>PP</sub> |  |  |  |  |  |  |

|---------------------------------|------|-----------------|--|--|--|--|--|--|

| Maximum Driver ON Signal        | 5    | 1.12            |  |  |  |  |  |  |

| Nominal Driver ON Signal        | 3    | 0.89            |  |  |  |  |  |  |

| Minimum Driver ON Signal        | 1    | 0.71            |  |  |  |  |  |  |

| AISG Maximum Receiver Threshold | - 12 | 0.16            |  |  |  |  |  |  |

| Nominal Receiver Threshold      | - 15 | 0.11            |  |  |  |  |  |  |

| Minimum Receiver Threshold      | - 18 | 0.08            |  |  |  |  |  |  |

| Maximum Driver OFF Signal       | - 40 | 0.006           |  |  |  |  |  |  |

| Maximum Driver OFF Signal       | - 40 | 0.006           |  |  |  |  |  |  |

#### 表 9-1. Conversions Between dBM and Peak-to-Peak Voltage

#### 9.2 Typical Application

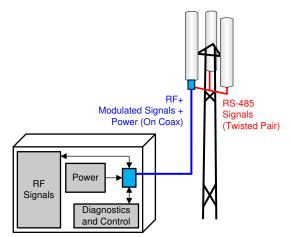

The AISG On-Off Keying (OOK) interface allows for command, control, and diagnostic information to be communicated between a base station and the corresponding tower-mounted antennae. 🛛 9-2 shows a typical application.

图 9-2. Typical AISG Application

#### 9.2.1 Design Requirements

An AISG transceiver is used to convert between digital logic-level signals and RF signals. The AISG standard requires an RF carrier frequency of 2.176 MHz with 100-ppm accuracy. The output signal of the driver, when active, should be from 1 dBm to 5 dBm. The receiver must be designed such that the input threshold is from - 18 dBm to - 12 dBm.

#### 9.2.2 Detailed Design Procedure

To ensure accuracy of the carrier frequency, an input reference frequency equal to four times the carrier (that is, 8.704 MHz) should be connected to the XTAL1 or XTAL2 inputs. This signal can come from a crystal (connected between XTAL1 and XTAL2) or from a PLL/clock generator circuit (connected to XTAL1 with XTAL2 grounded). The frequency accuracy must be within 100 ppm.

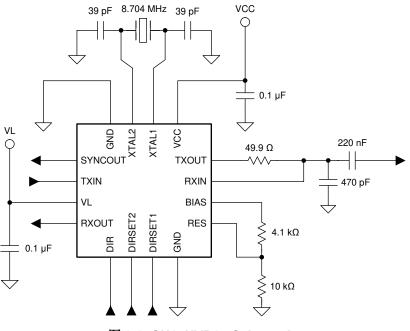

The driver output power level of the SN65HVD64 device can be adjusted through use of the RES pin. To align with AISG requirements, a nominal power level of 3 dBm should be configured by connecting a 4.1-k $\Omega$  resistor between RES and BIAS and a 10-k $\Omega$  resistor between RES and GND.  $\[Begin{bmatrix} 9-3 \\ 9-3 \\ 9-3 \\ 8 \\ 9-3 \\ 8 \\ 9-3 \\ 8 \\ 9-3 \\ 8 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\ 10-1 \\$

图 9-3. SN65HVD64 Schematic

#### 9.2.3 Application Curve

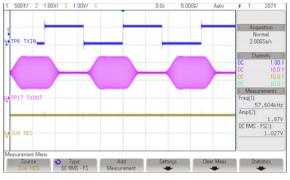

图 9-4 shows the application curve for the SN65HVD64 device.

图 9-4. SN65HVD64 Application Curve

### **10 Power Supply Recommendations**

The SN65HVD64 device has two power supply pins: V<sub>CC</sub>, which provides power to the analog circuitry, and VL, which is a logic supply. V<sub>CC</sub> should be operated from 3 V to 5.5 V, while VL can range from 1.6 V to 5.5 V to interface to different logic levels. Power supply decoupling capacitances of at least 0.1  $\mu$ F should be placed as close as possible to each power supply pin.

### 11 Layout

#### **11.1 Layout Guidelines**

Best practices for high-speed PCB design should be observed because the coax interface to the SN65HVD64 device operates at RF. The RF signaling traces should have a controlled characteristic impedance that is wellmatched to the coaxial line. A continuous reference plane should be used to avoid impedance discontinuities. Power and ground distribution should be done through planes rather than traces to decrease series resistance and increase the effective decoupling capacitance on the power rails.

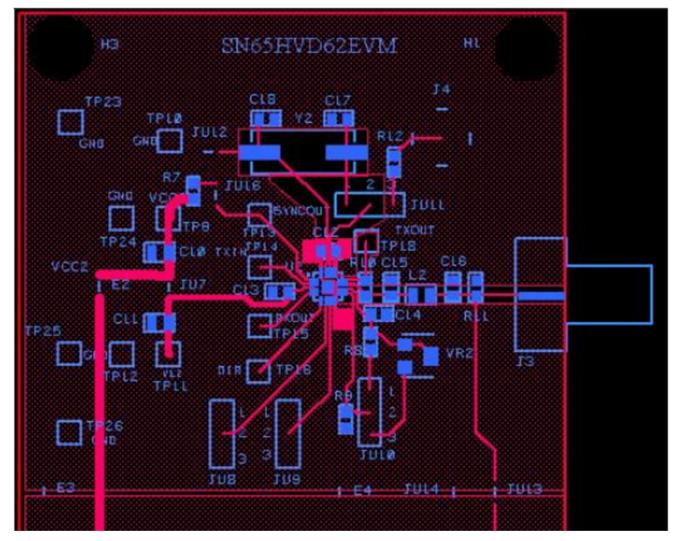

### 11.2 Layout Example

图 11-1. SN65HVD64 Layout

### **12 Device and Documentation Support**

TI offers an extensive line of development tools. Tools and software to evaluate the performance of the device, generate code, and develop solutions are listed below.

#### **12.1 Documentation Support**

#### 12.1.1 Related Documentation

#### **12.2 Receiving Notification of Documentation Updates**

To receive notification of documentation updates, navigate to the device product folder on ti.com. Click on *Subscribe to updates* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### **12.3 Support Resources**

TI E2E<sup>m</sup> support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### 12.4 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

AISG® is a registered trademark of Antenna Interface Standards Group, Ltd.

所有商标均为其各自所有者的财产。

#### 12.5 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 12.6 Glossary

**TI Glossary** This glossary lists and explains terms, acronyms, and definitions.

#### Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

### PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | e Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|----------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| SN65HVD64RGTR    | ACTIVE        | VQFN         | RGT                  | 16   | 3000           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 120   | HVD64                   | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <= 1000ppm threshold. Antimony trioxide based flame retardants must also meet the <= 1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(<sup>6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **GENERIC PACKAGE VIEW**

# VQFN - 1 mm max height PLASTIC QUAD FLATPACK - NO LEAD

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

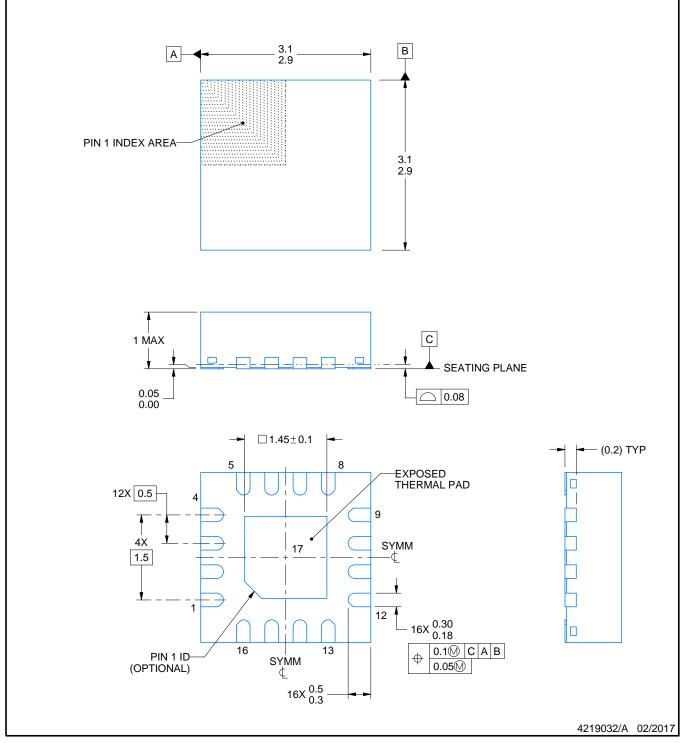

# **RGT0016A**

# **PACKAGE OUTLINE**

# VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice.

- The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

Reference JEDEC registration MO-220

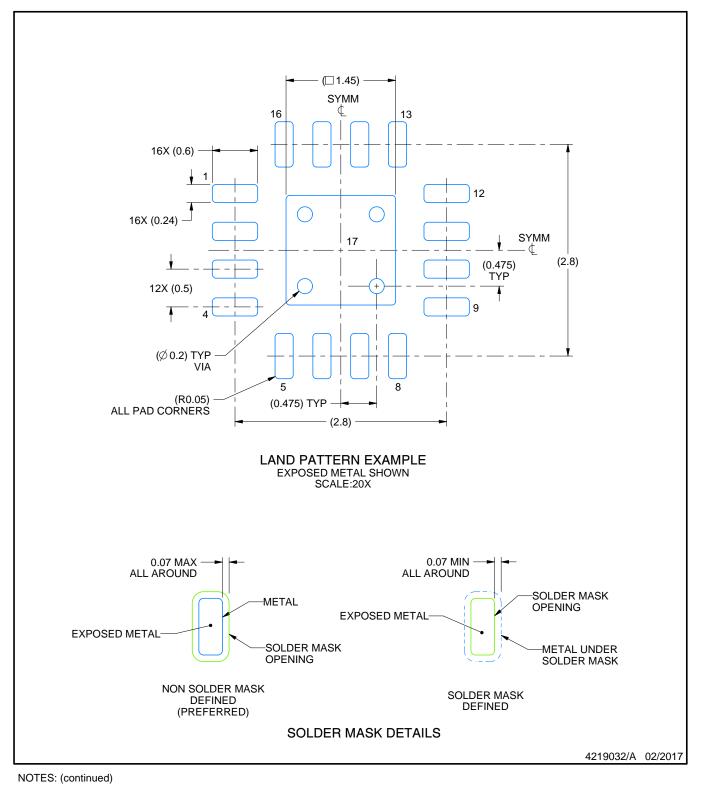

# **RGT0016A**

# **EXAMPLE BOARD LAYOUT**

# VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

5. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

6. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

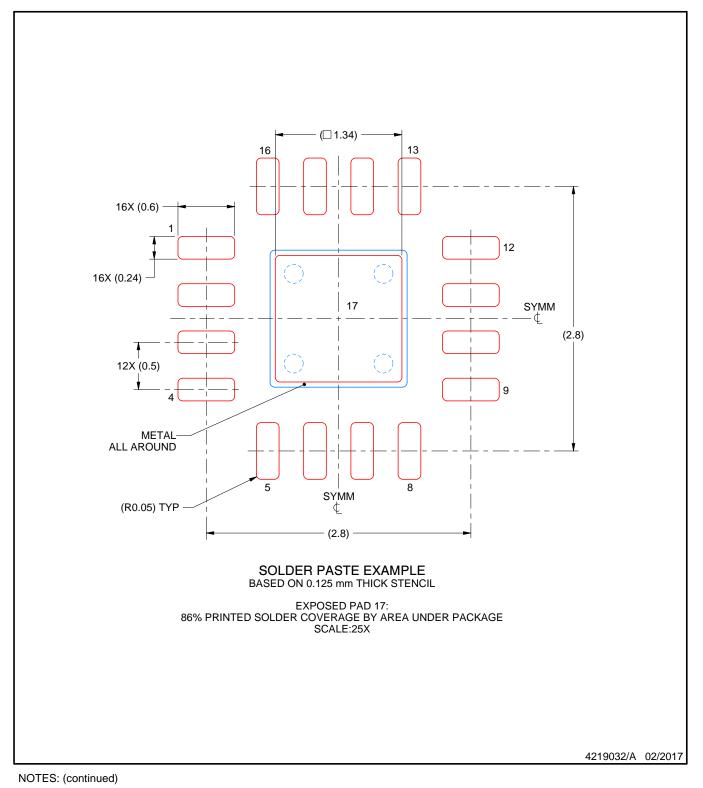

# **RGT0016A**

# **EXAMPLE STENCIL DESIGN**

# VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

7. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### 重要声明和免责声明

TI 提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没 有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保或其他要求。这些资源如有变更,恕不另行通知。TI 授权您仅可 将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知 识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款 (https:www.ti.com.cn/zh-cn/legal/termsofsale.html) 或 ti.com.cn 上其他适用条款/TI 产品随附的其他适用条款 的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

> 邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码:200122 Copyright © 2021 德州仪器半导体技术(上海)有限公司