www.ti.com.cn

# 具有扩展共模范围的故障保护 RS-485 收发器

查询样品: SN65HVD1792-EP

## 特性

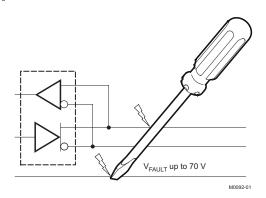

- 总线引脚故障保护达到 > ±70V

- 共模电压范围(-20V至25V),此范围超过 TIA/EIA 485 要求的两倍

- 总线 I/O 保护

- ±16kV JEDEC 人体模型 (HBM) 保护

- 减少了高达 256 个节点的单位负载

- 针对开路、短路和空闲总线情况下的故障安全接收器

- 低功耗

- 低待机电源电流,典型值 1µA

- 运行期间 Icc静态电流为 5mA

- 加电、断电无毛刺脉冲运行

### 应用范围

• 设计用于 RS-485 和 RS-422 网络

支持国防、航空航天、和医疗应用

- 受控基线

- 一个组装和测试场所

- 一个制造场所

- 延长的产品生命周期

- 延长的产品变更通知

- 产品可追溯性

## 说明

SN65HVD1792 被设计成在诸如电源直接短接、错误接线故障、接头故障、电缆破损和工具误用等所造成的过压故障情况下不受损坏。 它还借助于对人体模型技术规范的高级保护在静电放电 (ESD) 事件发生时稳定耐用。

SN65HVD1792 将一个差动驱动器和一个差动接收器组合在一起,这两个器件由一个单电源供电。 SN65HVD1792 额定工作温度范围 -40℃ 至 105℃。

## ORDERING INFORMATION(1)

| T <sub>A</sub> | PACKAGE <sup>(2)</sup> | ORDERABLE PART NUMBER | TOP-SIDE MARKING | VID NUMBER       |

|----------------|------------------------|-----------------------|------------------|------------------|

| 40°C to 405°C  | COIC D                 | SN65HVD1792TDREP      | 4700ED           | V62/13620-01XE   |

| –40°C to 105°C | SOIC - D               | SN65HVD1792TDEP       | 1792EP           | V62/13620-01XE-T |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

<sup>(2)</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## **DEVICE INFORMATION**

## **DRIVER FUNCTION TABLE**

| Input | Enable | Outputs |   |                                    |

|-------|--------|---------|---|------------------------------------|

| D     | DE     | Α       | В |                                    |

| Н     | Н      | Н       | L | Actively drive bus high            |

| L     | Н      | L       | Н | Actively drive bus low             |

| X     | L      | Z       | Z | Driver disabled                    |

| Х     | OPEN   | Z       | Z | Driver disabled by default         |

| OPEN  | Н      | Н       | L | Actively drive bus high by default |

### **RECEIVER FUNCTION TABLE**

| Differential Input           | Enable | Output |                              |

|------------------------------|--------|--------|------------------------------|

| $V_{ID} = V_A - V_B$         | RE     | R      |                              |

| $V_{IT+} < V_{ID}$           | L      | Н      | Receive valid bus high       |

| $V_{IT-} < V_{ID} < V_{IT+}$ | L      | ?      | Indeterminate bus state      |

| $V_{ID} < V_{IT-}$           | L      | L      | Receive valid bus low        |

| X                            | Н      | Z      | Receiver disabled            |

| X                            | OPEN   | Z      | Receiver disabled by default |

| Open-circuit bus             | L      | Н      | Fail-safe high output        |

| Short-circuit bus            | L      | Н      | Fail-safe high output        |

| Idle (terminated) bus        | L      | Н      | Fail-safe high output        |

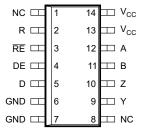

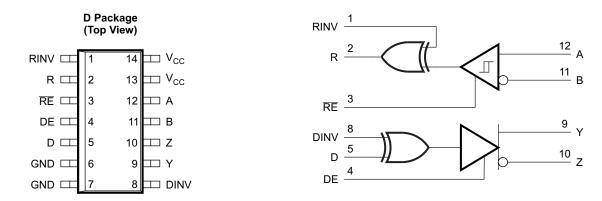

### D Package (Top View)

NC - No internal connection

Pins 6 and 7 are connected together internally.

Pins 13 and 14 are connected together internally.

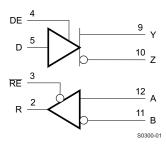

Logic Diagram (Positive Logic)

www.ti.com.cn

### ABSOLUTE MAXIMUM RATINGS(1)

|          |                                                                    |                | VALUE                    | UNIT |

|----------|--------------------------------------------------------------------|----------------|--------------------------|------|

| $V_{CC}$ | Supply voltage                                                     |                | -0.5 to 7                | V    |

|          | Voltage range at bus pins                                          | A, B pins      | -70 to 70                | V    |

|          | Input voltage range at any logic pin                               |                | $-0.3$ to $V_{CC} + 0.3$ | V    |

|          | Transient overvoltage pulse through 100 Ω per TIA-485              |                | -100 to 100              | V    |

|          | Receiver output current                                            |                | -24 to 24                | mA   |

| $T_{J}$  | Junction temperature                                               |                | 170                      | °C   |

|          | IEC 60749-26 ESD (human-body model), bus terminals and GND         |                | ±16                      | kV   |

|          | JEDEC Standard 22, Test Method A114 (human-body model), bus term   | ninals and GND | ±16                      | kV   |

|          | JEDEC Standard 22, Test Method A114 (human-body model), all pins   |                | ±4                       | kV   |

|          | JEDEC Standard 22, Test Method C101 (charged-device model), all pi | ns             | ±2                       | kV   |

|          | JEDEC Standard 22, Test Method A115 (machine model), all pins      |                | ±400                     | V    |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### THERMAL INFORMATION

|                  |                                                             | SN65HVD1792-EP |       |

|------------------|-------------------------------------------------------------|----------------|-------|

|                  | THERMAL METRIC <sup>(1)</sup>                               | D              | UNITS |

|                  |                                                             | 14 PINS        |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 70.8           |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance (3)               | 29.4           |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance <sup>(4)</sup>         | 25.3           | 90044 |

| ΨЈТ              | Junction-to-top characterization parameter <sup>(5)</sup>   | 8.2            | °C/W  |

| ΨЈВ              | Junction-to-board characterization parameter (6)            | 25             |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | N/A            |       |

- (1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

- (2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- (5) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- (6) The junction-to-board characterization parameter, ψ<sub>JB</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- (7) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

### RECOMMENDED OPERATING CONDITIONS

|                   |                                                                                  | MIN | NOM | MAX             | UNIT |

|-------------------|----------------------------------------------------------------------------------|-----|-----|-----------------|------|

| $V_{CC}$          | Supply voltage                                                                   | 4.5 | 5   | 5.5             | V    |

| VI                | Input voltage at any bus terminal (separately or common mode) <sup>(1)</sup>     | -20 |     | 25              | V    |

| V <sub>IH</sub>   | High-level input voltage (driver, driver enable, and receiver enable inputs)     | 2   |     | V <sub>CC</sub> | V    |

| V <sub>IL</sub>   | Low-level input voltage (driver, driver enable, and receiver enable inputs)      | 0   |     | 0.8             | V    |

| $V_{ID}$          | Differential input voltage                                                       | -25 |     | 25              | V    |

|                   | Output current, driver                                                           | -60 |     | 60              | mA   |

| IO                | Output current, receiver                                                         | -8  |     | 8               | mA   |

| R <sub>L</sub>    | Differential load resistance                                                     | 54  | 60  |                 | Ω    |

| C <sub>L</sub>    | Differential load capacitance                                                    |     | 50  |                 | pF   |

| 1/t <sub>UI</sub> | Signaling rate                                                                   |     |     | 1               | Mbps |

| T <sub>A</sub>    | Operating free-air temperature (see application section for thermal information) | -40 |     | 105             | °C   |

| TJ                | Junction temperature                                                             | -40 |     | 150             | °C   |

<sup>(1)</sup> By convention, the least positive (most negative) limit is designated as minimum in this data sheet.

## **ELECTRICAL CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                     | PARAMETER                                                                        | TEST                                                                   | TEST CONDITIONS                 |      | TYP                      | MAX | UNIT |

|---------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------|------|--------------------------|-----|------|

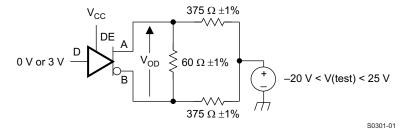

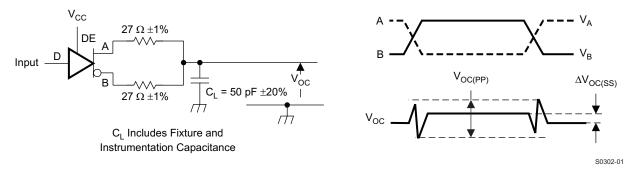

|                     | Driver differential output voltage                                               | RS-485 with common-mode load, $V_{CC} > 4.75 \text{ V}$ , See Figure 1 |                                 |      |                          |     |      |

| V <sub>OD</sub>     | magnitude                                                                        | $R_L = 54 \Omega$ , $4.75 V \le V_{CC}$                                | 1.5                             | 2    |                          | V   |      |

|                     |                                                                                  | $R_L = 100 \ \Omega, 4.75 \ V \le V_{CO}$                              | <sub>2</sub> ≤ 5.25 V           | 2    | 2.5                      |     |      |

| Δ V <sub>OD</sub>   | Change in magnitude of driver differential output voltage                        | R <sub>L</sub> = 54 Ω                                                  |                                 | -0.2 | 0                        | 0.2 | V    |

| $V_{OC(SS)}$        | Steady-state common-mode output voltage                                          |                                                                        |                                 | 1    | V <sub>CC</sub> /2       | 3   | ٧    |

| ΔV <sub>OC</sub>    | Change in differential driver output common-mode voltage                         |                                                                        |                                 | -100 | 0                        | 100 | mV   |

| V <sub>OC(PP)</sub> | Peak-to-peak driver common-mode output voltage                                   | Center of two 27-Ω load                                                |                                 | 500  |                          | mV  |      |

| C <sub>OD</sub>     | Differential output capacitance                                                  |                                                                        |                                 | 23   |                          | pF  |      |

| V <sub>IT+</sub>    | Positive-going receiver differential input voltage threshold                     |                                                                        | V <sub>CM</sub> = -20 V to 25 V |      |                          | -10 | mV   |

| V <sub>IT</sub>     | Negative-going receiver differential input voltage threshold                     | $V_{CM} = -20 \text{ V to } 25 \text{ V}$                              |                                 |      |                          |     | mV   |

| $V_{HYS}$           | Receiver differential input voltage threshold hysteresis ( $V_{IT+} - V_{IT-}$ ) |                                                                        |                                 | 30   | 50                       |     | mV   |

| $V_{OH}$            | Receiver high-level output voltage                                               | I <sub>OH</sub> = -8 mA                                                |                                 | 2.4  | V <sub>CC</sub><br>- 0.3 |     | ٧    |

| 0                   |                                                                                  | I <sub>OH</sub> = -400 μA                                              |                                 | 4    |                          |     |      |

| V <sub>OL</sub>     | Receiver low-level output voltage                                                | I <sub>OL</sub> = 8 mA                                                 | I <sub>OL</sub> = 8 mA          |      | 0.2                      | 0.5 | V    |

| I                   | Driver input, driver enable, and receiver enable input current                   |                                                                        |                                 | -100 |                          | 100 | μΑ   |

| l <sub>oz</sub>     | Receiver output high-impedance current                                           | $V_O = 0 \text{ V or } V_{CC}, \overline{RE} \text{ at } V_{CC}$       |                                 | -1   |                          | 1   | μA   |

| Ios                 | Driver short-circuit output current                                              |                                                                        |                                 | -250 |                          | 250 | mA   |

|                     | Bus input current (disabled driver)                                              | V <sub>CC</sub> = 4.5 to 5.5 V or                                      | V <sub>I</sub> = 12 V           |      | 75                       | 125 |      |

| I <sub>I</sub>      | bus input current (disabled driver)                                              | $V_{CC} = 0 \text{ V}, DE \text{ at } 0 \text{ V}$                     | V <sub>I</sub> = -7 V           | -100 | -100 -40                 |     | μA   |

www.ti.com.cn

# **ELECTRICAL CHARACTERISTICS (continued)**

over recommended operating conditions (unless otherwise noted)

|                 | PARAMETER                  | TEST                                                                                                                                                                                      | CONDITIONS                                                                                        |                                    | MIN | TYP | MAX | UNIT |

|-----------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------|-----|-----|-----|------|

|                 |                            | Driver and receiver enabled                                                                                                                                                               | DE = V <sub>CC</sub> ,<br>RE = GND,<br>no load                                                    |                                    |     | 4   | 6.3 |      |

|                 |                            | Driver enabled, receiver disabled   DE = V <sub>CC</sub> , RE = V <sub>CC</sub> , no load    Supply current (quiescent)   Driver disabled, receiver enabled   DE = GND, RE = GND, no load |                                                                                                   | 3                                  | 5.2 | mA  |     |      |

| I <sub>cc</sub> | Supply current (quiescent) |                                                                                                                                                                                           |                                                                                                   | 2                                  | 4.3 |     |     |      |

|                 |                            | Driver and receiver                                                                                                                                                                       | DE = GND,<br>D = open                                                                             | T <sub>J</sub> = -40°C to<br>105°C |     | 0.5 | 5.2 | μА   |

|                 |                            | disabled                                                                                                                                                                                  | $ \begin{array}{c c} \text{disabled} & \text{RE} = V_{\text{CC}}, \\ \text{no load} \end{array} $ |                                    |     | 15  | 29  | μ, τ |

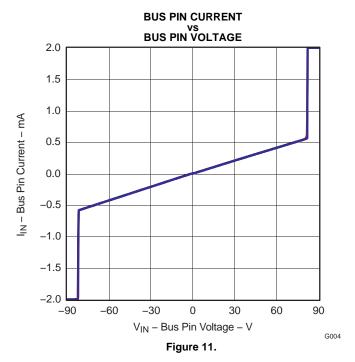

|                 | Supply current (dynamic)   | See TYPICAL CHA                                                                                                                                                                           | See TYPICAL CHARACTERISTICS section                                                               |                                    |     |     |     |      |

## **SWITCHING CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                                           | PARAMETER                                                                   | TEST CO                              | NDITIONS                          | MIN | TYP | MAX | UNIT |

|-------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------|-----------------------------------|-----|-----|-----|------|

| DRIVER                                    |                                                                             |                                      |                                   |     |     | *   |      |

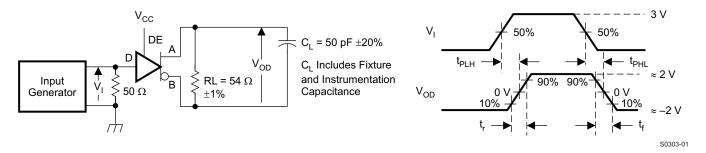

| t <sub>r</sub> , t <sub>f</sub>           | Driver differential output rise/fall time                                   |                                      |                                   | 50  |     | 300 | ns   |

| t <sub>PHL</sub> , t <sub>PLH</sub>       | Driver propagation delay                                                    | $R_1 = 54 \Omega, C_1 = 50$          | oF See Figure 3                   |     |     | 200 | ns   |

| t <sub>SK(P)</sub>                        | Driver differential output pulse skew,  t <sub>PHL</sub> - t <sub>PLH</sub> | 11 - 04 12, 00 - 00                  | or, occirigate o                  |     |     | 29  | ns   |

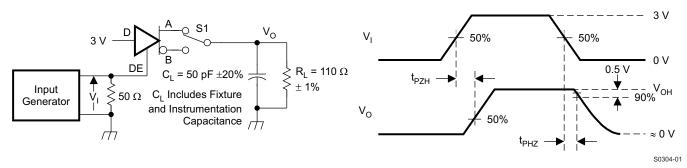

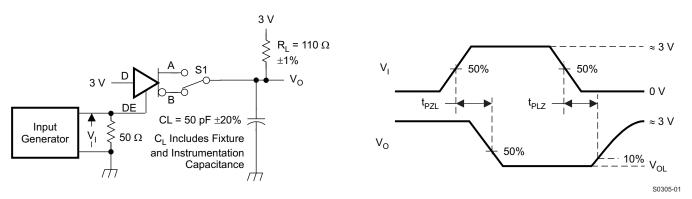

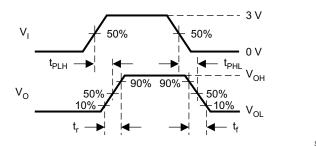

| t <sub>PHZ</sub> , t <sub>PLZ</sub>       | Driver disable time                                                         |                                      |                                   |     |     | 3   | μs   |

| t <sub>PZH</sub> , t <sub>PZL</sub>       |                                                                             | Receiver enabled                     | See Figure 4 and Figure 5         |     |     | 300 | ns   |

|                                           | Driver enable time                                                          | Receiver disabled                    |                                   |     |     | 10  | μs   |

|                                           |                                                                             | Receiver enabled                     | V <sub>CM</sub> > V <sub>CC</sub> |     | 500 |     | ns   |

| RECEIVER                                  |                                                                             |                                      |                                   |     |     |     |      |

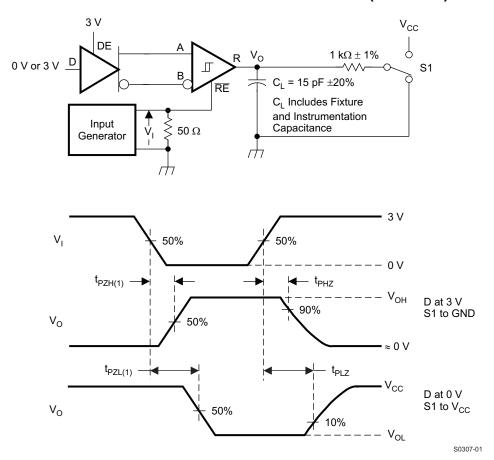

| t <sub>r</sub> , t <sub>f</sub>           | Receiver output rise/fall time                                              |                                      |                                   |     | 4   | 15  | ns   |

| t <sub>PHL</sub> , t <sub>PLH</sub>       | Receiver propagation delay time                                             | C <sub>1</sub> = 15 pF, See Fig      | ure 6                             |     | 100 | 200 | ns   |

| t <sub>SK(P)</sub>                        | Receiver output pulse skew,  t <sub>PHL</sub> - t <sub>PLH</sub>            | C <sub>L</sub> = 15 μr, see rigule 6 |                                   |     | 6   | 20  | ns   |

| t <sub>PLZ</sub> , t <sub>PHZ</sub>       | Receiver disable time                                                       | Driver enabled, See Figure 7         |                                   |     | 15  | 100 | ns   |

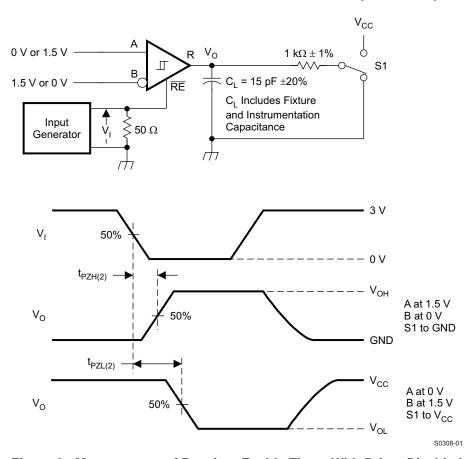

| t <sub>PZL(1)</sub> , t <sub>PZH(1)</sub> | Daneiras anabla tima                                                        | Driver enabled, See                  | Figure 7                          |     | 80  | 300 | ns   |

| $t_{PZL(2)}, t_{PZH(2)}$                  | Receiver enable time                                                        | Driver disabled, See                 |                                   | 3   | 9   | μs  |      |

### PARAMETER MEASUREMENT INFORMATION

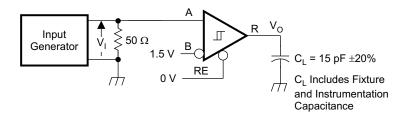

Input generator rate is 100 kbps, 50% duty cycle, rise and fall times less than 6 nsec, output impedance 50 Ω.

Figure 1. Measurement of Driver Differential Output Voltage With Common-Mode Load

Figure 2. Measurement of Driver Differential and Common-Mode Output With RS-485 Load

Figure 3. Measurement of Driver Differential Output Rise and Fall Times and Propagation Delays

NOTE: D at 3 V to test non-inverting output, D at 0 V to test inverting output.

Figure 4. Measurement of Driver Enable and Disable Times With Active High Output and Pulldown Load

## **PARAMETER MEASUREMENT INFORMATION (continued)**

NOTE: D at 0 V to test non-inverting output, D at 3 V to test inverting output.

Figure 5. Measurement of Driver Enable and Disable Times With Active-Low Output and Pullup Load

Figure 6. Measurement of Receiver Output Rise and Fall Times and Propagation Delays

## **PARAMETER MEASUREMENT INFORMATION (continued)**

Figure 7. Measurement of Receiver Enable/Disable Times With Driver Enabled

## PARAMETER MEASUREMENT INFORMATION (continued)

Figure 8. Measurement of Receiver Enable Times With Driver Disabled

### **TYPICAL CHARACTERISTICS**

# TYPICAL CHARACTERISTICS (continued) DIFFERENTIAL OUTPUT VOLTAGE

#### ADDITIONAL OPTIONS

The SN65HVD1792 also has options for J1708 applications, for always-enabled full-duplex versions (industry-standard SN65LBC179 footprint) and for inverting-polarity versions, which allow users to correct a reversal of the bus wires without re-wiring. Contact your local Texas Instruments representative for information on these options.

| PART NUMBER                               | SN65HVD1792 |        |      |  |  |  |

|-------------------------------------------|-------------|--------|------|--|--|--|

| FOOTPRINT/FUNCTION                        | SLOW        | MEDIUM | FAST |  |  |  |

| Half-duplex (176 pinout)                  | 85          | 86     | 87   |  |  |  |

| Full-duplex no enables (179 pinout)       | 88          | 89     | 90   |  |  |  |

| Full-duplex with enables (180 pinout)     | 91          | 92     | 93   |  |  |  |

| Half-duplex with cable invert             | 94          | 95     | 96   |  |  |  |

| Full-duplex with cable invert and enables | 97          | 98     | 99   |  |  |  |

| J1708                                     | 08          | 09     | 10   |  |  |  |

Figure 13. SN65HVD1792 With Inverting Feature to Correct for Miswired Cables

### APPLICATION INFORMATION

## **Hot-Plugging**

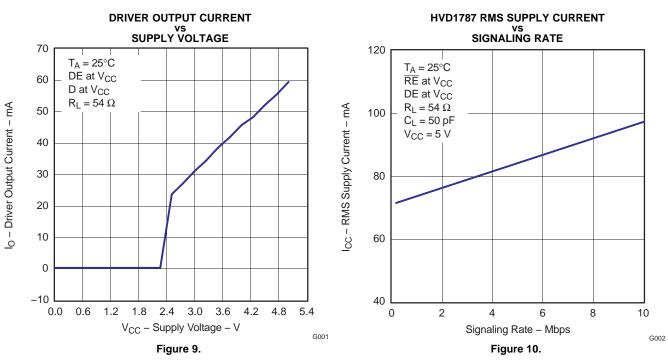

The SN65HVD1792 is designed to operate in "hot swap" or "hot pluggable" applications. Key features for hot-pluggable applications are power-up, power-down glitch free operation, default disabled input/output pins, and receiver failsafe. As shown in Figure 9, an internal Power-On Reset circuit keeps the driver outputs in a high-impedance state until the supply voltage has reached a level at which the device will reliably operate. This ensures that no spurious transitions (glitches) will occur on the bus pin outputs as the power supply turns on or turns off.

As shown in the device **FUNCTION TABLE**, the *ENABLE* inputs have the feature of default disable on both the driver enable and receiver enable. This ensures that the device will neither drive the bus nor report data on the R pin until the associated controller actively drives the enable pins.

www.ti.com.cn

### Receiver Failsafe

The differential receiver is "failsafe" to invalid bus states caused by:

- · open bus conditions such as a disconnected connector,

- shorted bus conditions such as cable damage shorting the twisted-pair together,

- or idle bus conditions that occur when no driver on the bus is actively driving.

In any of these cases, the differential receiver outputs a failsafe logic High state, so that the output of the receiver is not indeterminate.

In the SN65HVD1792, receiver failsafe is accomplished by offsetting the receiver thresholds so that the "input indeterminate" range does not include zero volts differential. In order to comply with the RS-422 and RS-485 standards, the receiver output must output a High when the differential input  $V_{ID}$  is more positive than 200 mV, and must output a Low when the  $V_{ID}$  is more negative than -200 mV. The SN65HVD1792 receiver parameters which determine the failsafe performance are  $V_{IT+}$  and  $V_{IT-}$  and  $V_{HYS}$ . In the *Electrical Characteristics* table,  $V_{IT-}$  has a typical value of -150 mV and a minimum (most negative) value of -200 mV, so differential signals more negative than -200 mV will always cause a Low receiver output. Similarly, differential signals more positive than 200 mV will always cause a High receiver output, because the typical value of  $V_{IT+}$  is -100mV, and  $V_{IT+}$  is never more positive than -10 mV under any conditions of temperature, supply voltage, or common-mode offset.

When the differential input signal is close to zero, it will still be above the  $V_{IT+}$  threshold, and the receiver output will be High. Only when the differential input is more negative than  $V_{IT-}$  will the receiver output transition to a Low state. So, the noise immunity of the receiver inputs during a bus fault condition includes the receiver hysteresis value  $V_{HYS}$  (the separation between  $V_{IT+}$  and  $V_{IT-}$ ) as well as the value of  $V_{IT+}$ .

For the SN65HVD1792, the typical noise immunity is typically about 150 mV, which is the negative noise level needed to exceed the  $V_{IT}$  threshold ( $V_{IT}$  TYP = -150 mV). In the worst case, the failsafe noise immunity is never less than 40 mV, which is set by the maximum positive threshold ( $V_{IT}$  MAX = -10mV) plus the minimum hysteresis voltage ( $V_{HYS}$  MIN = 30 mV).

### 70-V Fault-Protection

The SN65HVD1792 is designed to survive bus pin faults up to ±70V. The devices designed for fast signaling rate (10 Mbps) will not survive a bus pin fault with a direct short to voltages above 30V when:

- 1. the device is powered on AND

- 2a. the driver is enabled (DE=HIGH) AND D=HIGH AND the bus fault is applied to the A pin OR

- 2b. the driver is enabled (DE=HIGH) AND D=LOW AND the bus fault is applied to the B pin

Under other conditions, the device will survive shorts to bus pin faults up to 70V. Table 1 summarizes the conditions under which the device may be damaged, and the conditions under which the device will not be damaged.

**Table 1. Device Conditions**

| POWER | DE | D | Α                           | В                           | RESULTS          |

|-------|----|---|-----------------------------|-----------------------------|------------------|

| OFF   | Х  | Х | -70V < V <sub>A</sub> < 70V | -70V < V <sub>B</sub> < 70V | Device survives  |

| ON    | LO | Х | -70V < V <sub>A</sub> < 70V | -70V < V <sub>B</sub> < 70V | Device survives  |

| ON    | HI | L | -70V < V <sub>A</sub> < 70V | $-70V < V_B < 30V$          | Device survives  |

| ON    | HI | L | -70V < V <sub>A</sub> < 70V | 30V < V <sub>B</sub>        | Damage may occur |

| ON    | HI | Н | -70V < V <sub>A</sub> < 30V | -70V < V <sub>B</sub> < 30V | Device survives  |

| ON    | HI | Н | 30V < V <sub>A</sub>        | -70V < V <sub>B</sub> < 30V | Damage may occur |

www.ti.com 11-Nov-2025

### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/        | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|----------------|-----------------------|------|---------------|--------------------|--------------|--------------|

|                       | (1)    | (2)           |                |                       | (3)  | Ball material | Peak reflow        |              | (6)          |

|                       |        |               |                |                       |      | (4)           | (5)                |              |              |

| SN65HVD1792TDEP       | Active | Production    | SOIC (D)   14  | 50   TUBE             | Yes  | NIPDAU        | Level-1-260C-UNLIM | -40 to 105   | 1792EP       |

| SN65HVD1792TDEP.A     | Active | Production    | SOIC (D)   14  | 50   TUBE             | Yes  | NIPDAU        | Level-1-260C-UNLIM | -40 to 105   | 1792EP       |

| SN65HVD1792TDREP      | Active | Production    | SOIC (D)   14  | 2500   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -40 to 105   | 1792EP       |

| SN65HVD1792TDREP.A    | Active | Production    | SOIC (D)   14  | 2500   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -40 to 105   | 1792EP       |

| V62/13620-01XE        | Active | Production    | SOIC (D)   14  | 2500   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -40 to 105   | 1792EP       |

| V62/13620-01XE-T      | Active | Production    | SOIC (D)   14  | 50   TUBE             | Yes  | NIPDAU        | Level-1-260C-UNLIM | -40 to 105   | 1792EP       |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

## PACKAGE OPTION ADDENDUM

www.ti.com 11-Nov-2025

## OTHER QUALIFIED VERSIONS OF SN65HVD1792-EP:

● Catalog : SN65HVD1792

NOTE: Qualified Version Definitions:

Catalog - TI's standard catalog product

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 24-Jul-2025

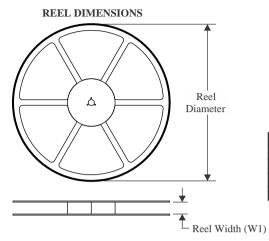

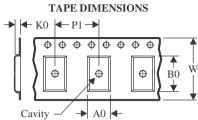

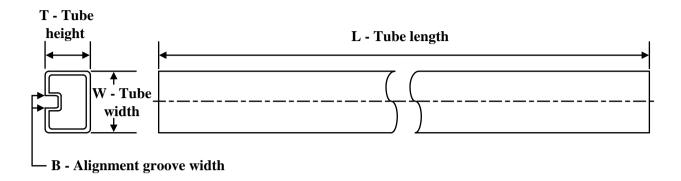

## TAPE AND REEL INFORMATION

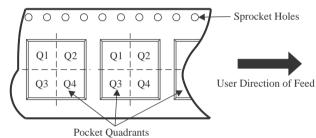

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

### \*All dimensions are nominal

| Device           | _    | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| SN65HVD1792TDREP | SOIC | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.0        | 2.1        | 8.0        | 16.0      | Q1               |

www.ti.com 24-Jul-2025

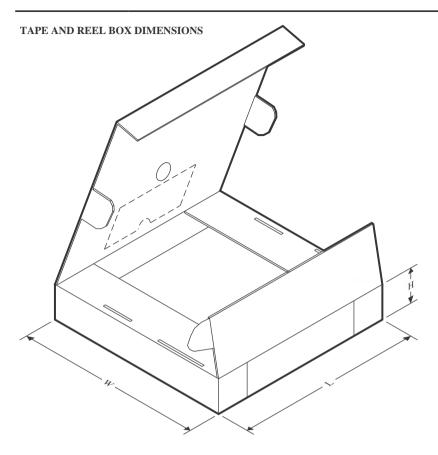

## \*All dimensions are nominal

| Γ | Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Г | SN65HVD1792TDREP | SOIC         | D               | 14   | 2500 | 353.0       | 353.0      | 32.0        |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 24-Jul-2025

## **TUBE**

\*All dimensions are nominal

| Device            | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|-------------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| SN65HVD1792TDEP   | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940   | 4.32   |

| SN65HVD1792TDEP.A | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940   | 4.32   |

| V62/13620-01XE-T  | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940   | 4.32   |

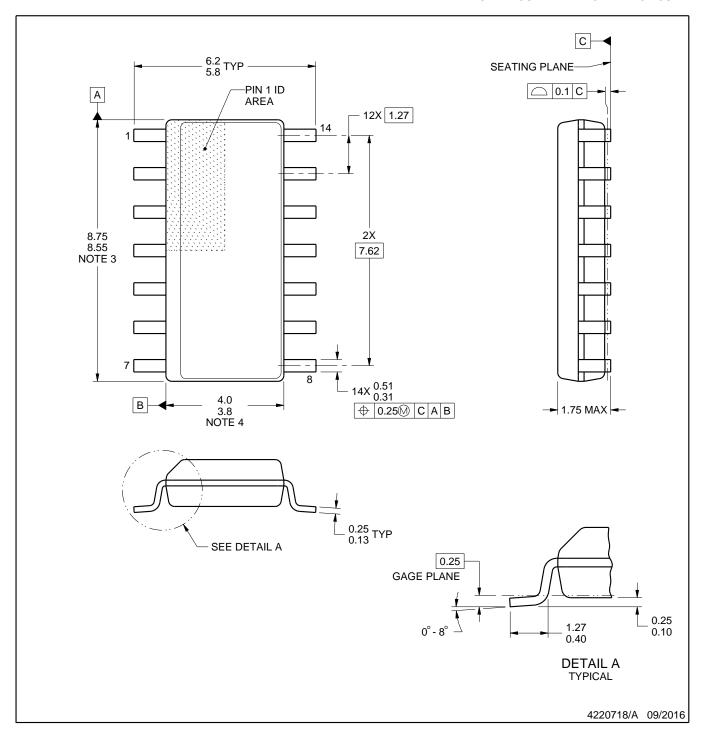

SMALL OUTLINE INTEGRATED CIRCUIT

### NOTES:

- 1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm, per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.43 mm, per side.

- 5. Reference JEDEC registration MS-012, variation AB.

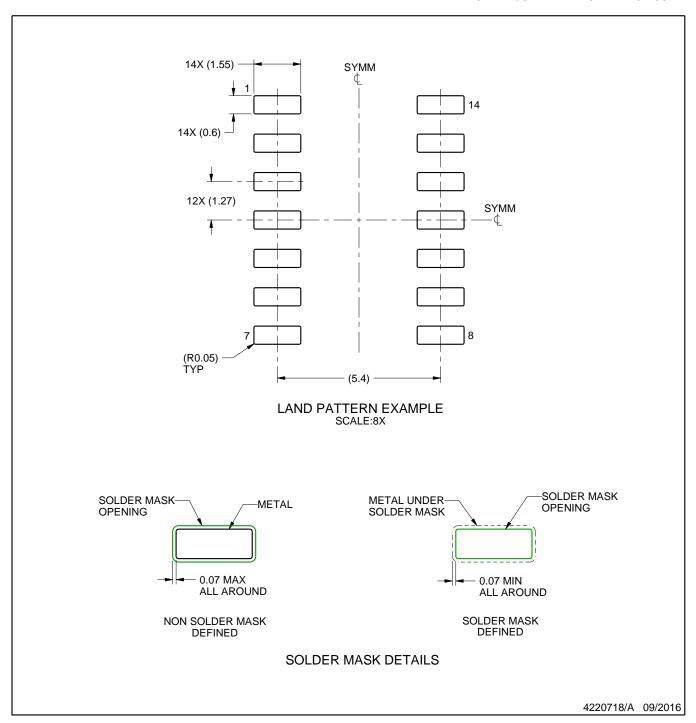

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

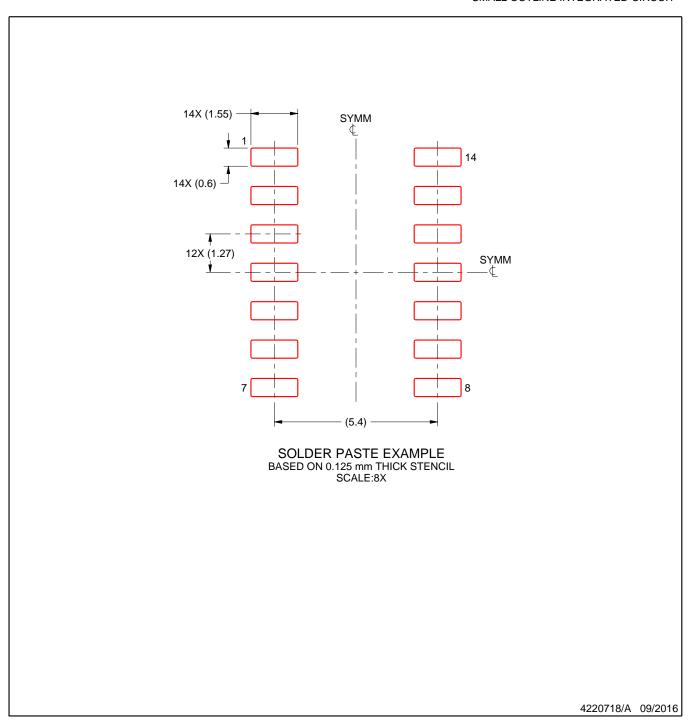

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

## 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月