# 高速差分线路接收器

查询样品: SN55LVDS32-SP

### 特性

- 符合 QML-V, SMD 5962-97621

- 由一个单 3.3V 电源供电运行

- 设计用于信号传输速率高达 100Mbps 的应用

- 最大差分输入阀值为 ±100mV

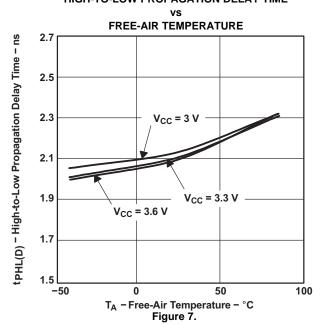

- 典型传播延迟时间为 2.1ns

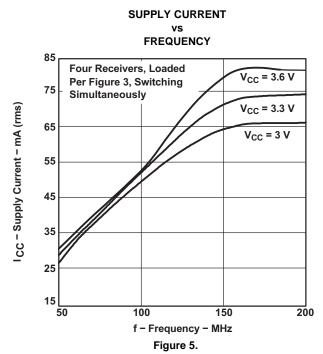

- 在最大数据速率下每个接收器的功率耗散典型值为 60mW

- 总线-端子静电放电 (ESD) 保护超过 8kV

- 低压 TTL(LVTTL) 逻辑输入电平

- 开电路故障安全

- 针对有冗余需求的太空和高可靠性应用的冷备用

### J OR W PACKAGE (TOP VIEW) 16 V<sub>CC</sub> 1B **∏** 15 4B 1A [] 2 14 🛮 4A 1Y 📙 3 13 4Y G 📙 4 2Y 🛚 12 G 5 2A 4 11 3Y 6 2B 4 10 3A 7 3B **GND** 9

### 说明

SN55LVDS32 是一款差分线路驱动器,此驱动器执行低压差分信号传输 (LVDS) 的电气特性。 这个信号传输技术降低了 5V 差分标准电平(例如 EIA/TIA-422B)的输出电压电平,从而减少了功耗、增加了开关速度、并可实现在 3.3V 电源轨供电下的运行。 四个差分接收器中的任何一个在输入共模电压范围内提供具有 ±100mV 差分输入电压的有效逻辑输出状态。 此输入共模电压范围允许两个 LVDS 节点间 1V 的接地电势差。

这些器件和信号传输技术用于接近 100Ω 的受控阻抗介质上的点到点和多支路(一个驱动器和多个接收器)的数据 传输应用。此传输介质可以是印刷电路板走线、底板、或者电缆。 数据传输的最终速率和距离取决于介质的衰减特性和环境的噪声耦合。

SN55LVDS32 额定运行温度介于 -55°C 至 125°C 之间。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### ORDERING INFORMATION(1)

| T <sub>A</sub> | PACKAGE <sup>(2)</sup> | ORDERABLE PART NUMBER | TOP-SIDE MARKING |  |  |

|----------------|------------------------|-----------------------|------------------|--|--|

| 5500 (- 40500  | CDIP - J               | 5962-9762201VEA       | 5962-9762201VEA  |  |  |

| –55°C to 125°C | CFP - W                | 5962-9762201VFA       | 5962-9762201VFA  |  |  |

- (1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

- (2) Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

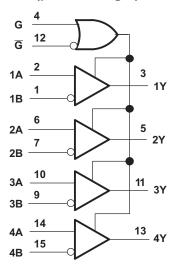

# SN55LVDS32 logic diagram (positive logic)

Table 1. FUNCTION TABLE<sup>(1)</sup>

| SN55LVDS32                         |     |      |        |  |  |  |  |

|------------------------------------|-----|------|--------|--|--|--|--|

| DIFFERENTIAL INPUT                 | ENA | BLES | OUTPUT |  |  |  |  |

| A, B                               | G   | G    | Y      |  |  |  |  |

| \/ > 100 m\/                       | Н   | X    | Н      |  |  |  |  |

| V <sub>ID</sub> ≥ 100 mV           | Х   | L    | Н      |  |  |  |  |

| 100 mV . V < 100 mV                | Н   | X    | ?      |  |  |  |  |

| -100 mV < V <sub>ID</sub> ≤ 100 mV | X   | L    | ?      |  |  |  |  |

| \\ < 100 m\\                       | Н   | X    | L      |  |  |  |  |

| V <sub>ID</sub> ≤ −100 mV          | X   | L    | L      |  |  |  |  |

| X                                  | L   | Н    | Z      |  |  |  |  |

| Open                               | Н   | X    | Н      |  |  |  |  |

| Open                               | X   | L    | Н      |  |  |  |  |

(1) H = high level, L = low level, X = irrelevant, Z = high impedance (off), ? = indeterminate

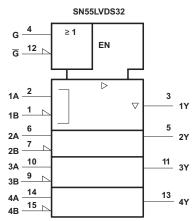

### logic symbol<sup>†</sup>

<sup>&</sup>lt;sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

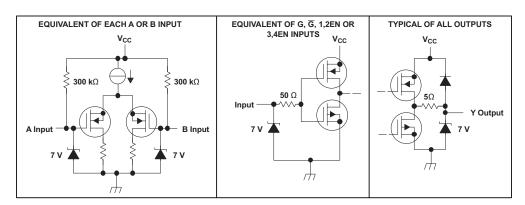

### **EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS**

### ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range (unless otherwise noted)

|                                                     |                                            | UNIT          |

|-----------------------------------------------------|--------------------------------------------|---------------|

| V <sub>CC</sub> Supply voltage range <sup>(2)</sup> | −0.5 V to 4 V                              |               |

| V <sub>I</sub> Input voltage range                  | $-0.5 \text{ V to V}_{CC} + 0.5 \text{ V}$ |               |

|                                                     | A or B                                     | −0.5 V to 4 V |

| Continuous total power dissipation                  | See Dissipation Rating Table               |               |

| Lead temperature 1,6 mm (1/16 inch) from case for 1 | 260°C                                      |               |

| T <sub>stg</sub> Storage temperature range          | −65°C to 150°C                             |               |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### **DISSIPATION RATING TABLE**

| PACKAGE | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR <sup>(1)</sup><br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING | T <sub>A</sub> = 125°C<br>POWER RATING |

|---------|---------------------------------------|---------------------------------------------------------------|---------------------------------------|---------------------------------------|----------------------------------------|

| J       | 1375 mW                               | 11 mW/°C                                                      | 880 mW                                | 715 mW                                | 275 mW                                 |

| W       | 1000 mW                               | 8 mW/°C                                                       | 640 mW                                | 520 mW                                | 200 mW                                 |

<sup>(1)</sup> This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

### RECOMMENDED OPERATING CONDITIONS

|                                                |                                         |                       | MIN                 | NOM | MAX                        | UNIT |

|------------------------------------------------|-----------------------------------------|-----------------------|---------------------|-----|----------------------------|------|

| V <sub>CC</sub>                                | Supply voltage                          |                       | 3                   | 3.3 | 3.6                        | V    |

| $V_{IH}$                                       | High-level input voltage                | G, G, 1,2EN, or 3,4EN | 2                   |     |                            | V    |

| $V_{IL}$                                       | Low-level input voltage                 | G, G, 1,2EN, or 3,4EN |                     |     | 0.8                        | V    |

| $ V_{ID} $                                     | Magnitude of differential input voltage |                       | 0.1                 |     | 0.6                        | V    |

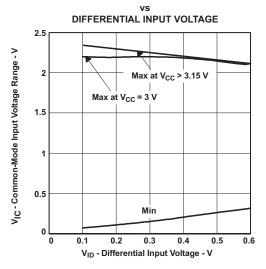

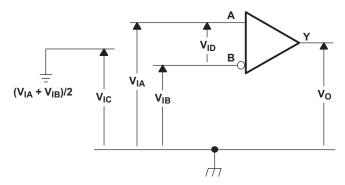

| V <sub>IC</sub> Common-mode input voltage (see |                                         | (see Figure 1)        | V <sub>ID</sub>  /2 |     | 2.4 -  V <sub>ID</sub>  /2 | V    |

|                                                |                                         |                       |                     |     | V <sub>CC</sub> - 0.8      | V    |

| T <sub>A</sub>                                 | Operating free-air temperatur           | e                     | -55                 |     | 125                        | °C   |

### COMMON-MODE INPUT VOLTAGE RANGE

Figure 1.  $V_{IC}$  Versus  $V_{ID}$  and  $V_{CC}$

<sup>(2)</sup> All voltages, except differential I/O bus voltages, are with respect to the network ground terminal.

### **ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                               | TEST CONDITIONS                           | MIN  | TYP <sup>(1)</sup> | MAX | UNIT |

|---------------------|---------------------------------------------------------|-------------------------------------------|------|--------------------|-----|------|

| V <sub>ITH+</sub>   | Positive-going differential input voltage threshold     | See Figure 2, Table 2, and <sup>(2)</sup> |      |                    | 100 | mV   |

| V <sub>ITH</sub> _  | Negative-going differential input voltage threshold (3) | See Figure 2, Table 2, and <sup>(2)</sup> | -100 |                    |     | mV   |

| V <sub>OH</sub>     | High-level output voltage                               | I <sub>OH</sub> = -8 mA                   | 2.4  |                    |     | V    |

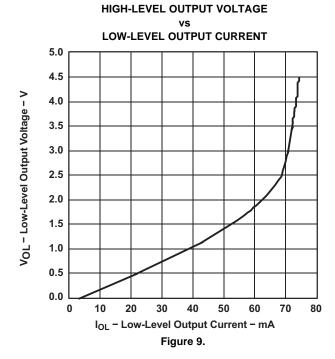

| V <sub>OL</sub>     | Low-level output voltage                                | I <sub>OL</sub> = 8 mA                    |      |                    | 0.4 | V    |

|                     | Complex compact                                         | Enabled, No load                          |      | 10                 | 18  | A    |

| I <sub>CC</sub>     | Supply current                                          | Disabled                                  |      | 0.25               | 0.5 | mA   |

|                     | land summer (A or Dispute)                              | V <sub>I</sub> = 0                        | -2   | -10                | -20 |      |

| Ч                   | Input current (A or B inputs)                           | V <sub>I</sub> = 2.4 V                    | -1.2 | -3                 |     | μΑ   |

| I <sub>I(OFF)</sub> | Power-off input current (A or B inputs)                 | $V_{CC} = 0,$ $V_{I} = 2.4 \text{ V}$     |      | 6                  | 20  | μΑ   |

| I <sub>IH</sub>     | High-level input current (EN, G, or G inputs)           | V <sub>IH</sub> = 2 V                     |      |                    | 10  | μΑ   |

| I <sub>IL</sub>     | Low-level input current (EN, G, or G inputs)            | V <sub>IL</sub> = 0.8 V                   |      |                    | 10  | μΑ   |

| l <sub>OZ</sub>     | High-impedance output current                           | $V_O = 0$ or $V_{CC}$                     |      |                    | ±12 | μΑ   |

<sup>(1)</sup> All typical values are at  $T_A = 25^{\circ}C$  and with  $V_{CC} = 3.3$  V. (2)  $|V_{ITH}| = 200$  mV for operation at  $-55^{\circ}C$ .

### **SWITCHING CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                    | PARAMETER                                                   | TEST CONDITIONS                      | MIN | TYP | MAX | UNIT |

|--------------------|-------------------------------------------------------------|--------------------------------------|-----|-----|-----|------|

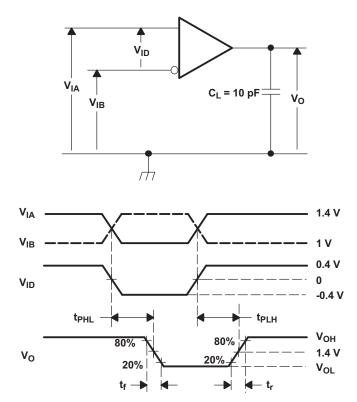

| t <sub>PLH</sub>   | Propagation delay time, low-to-high-level output            |                                      | 1.3 | 2.3 | 6   | ns   |

| t <sub>PHL</sub>   | Propagation delay time, high-to-low-level output            |                                      | 1.4 | 2.2 | 6.1 | ns   |

| t <sub>sk(o)</sub> | Channel-to-channel output skew <sup>(1)</sup>               | C <sub>L</sub> = 10 pF, See Figure 3 |     | 0.1 |     | ns   |

| t <sub>r</sub>     | Differential output signal rise time (20% to 80%)           |                                      |     | 0.6 |     | ns   |

| t <sub>f</sub>     | Differential output signal fall time (80% to 20%)           |                                      |     | 0.7 |     | ns   |

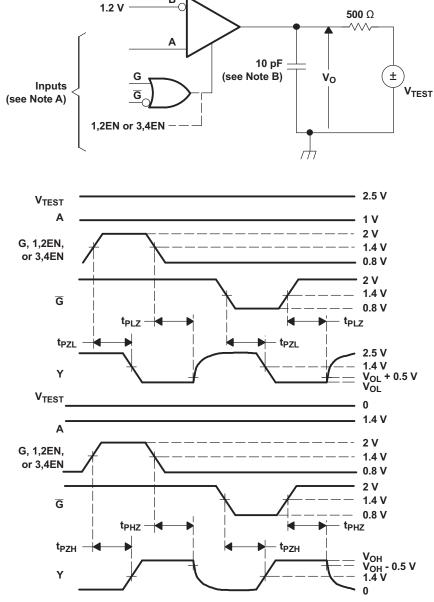

| t <sub>PHZ</sub>   | Propagation delay time, high-level-to-high-impedance output |                                      |     | 6.5 | 12  | ns   |

| $t_{PLZ}$          | Propagation delay time, low-level-to-high-impedance output  | Can Figure 4                         |     | 5.5 | 12  | ns   |

| t <sub>PZH</sub>   | Propagation delay time, high-impedance-to-high-level output | See Figure 4                         |     | 8   | 12  | ns   |

| t <sub>PZL</sub>   | Propagation delay time, high-impedance-to-low-level output  |                                      |     | 3   | 12  | ns   |

<sup>(1)</sup>  $t_{sk(o)}$  is the maximum delay time difference between drivers on the same device.

The algebraic convention, in which the less-positive (more-negative) limit is designated minimum, is used in this data sheet for the negative-going differential input voltage threshold only.

### PARAMETER MEASUREMENT INFORMATION

Figure 2. Voltage Definitions

Table 2. Receiver Minimum and Maximum Input Threshold Test Voltages

|                      |                                 | •                    |                                            |  |  |

|----------------------|---------------------------------|----------------------|--------------------------------------------|--|--|

| APPLIED V            | APPLIED VOLTAGES <sup>(1)</sup> |                      | RESULTING COMMON-<br>MODE<br>INPUT VOLTAGE |  |  |

| V <sub>IA</sub> (mV) | V <sub>IB</sub> (mV)            | V <sub>ID</sub> (mV) | V <sub>IC</sub> (mV)                       |  |  |

| 1.25                 | 1.15                            | 100                  | 1.2                                        |  |  |

| 1.15                 | 1.25                            | -100                 | 1.2                                        |  |  |

| 2.4                  | 2.3                             | 100                  | 2.35                                       |  |  |

| 2.3                  | 2.4                             | -100                 | 2.35                                       |  |  |

| 0.1                  | 0                               | 100                  | 0.05                                       |  |  |

| 0                    | 0.1                             | -100                 | 0.05                                       |  |  |

| 1.5                  | 0.9                             | 600                  | 1.2                                        |  |  |

| 0.9                  | 1.5                             | -600                 | 1.2                                        |  |  |

| 2.4                  | 1.8                             | 600                  | 2.1                                        |  |  |

| 1.8                  | 2.4                             | -600                 | 2.1                                        |  |  |

| 0.6                  | 0                               | 600                  | 0.3                                        |  |  |

| 0                    | 0.6                             | -600                 | 0.3                                        |  |  |

<sup>(1)</sup> These voltages are applied for a minimum of  $1.5 \mu s$ .

- A. All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$  ns, pulse repetition rate(PRR) = 50 Mpps, pulse width = 10 ±0.2 ns.

- B. C<sub>L</sub> includes instrumentation and fixture capacitance within 6 mm of the D.U.T.

Figure 3. Timing Test Circuit and Waveforms

- A. All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$  ns, pulse repetition rate(PRR) = 0.5 Mpps, pulse width = 500 ± 10 ns.

- B. C<sub>L</sub> includes instrumentation and fixture capacitance within 6 mm of the D.U.T.

Figure 4. Enable- and Disable-Time Test Circuit and Waveforms

### **TYPICAL CHARACTERISTICS**

### **TYPICAL CHARACTERISTICS (continued)**

# VS FREE-AIR TEMPERATURE 2.7 V<sub>CC</sub> = 3 V V<sub>CC</sub> = 3.6 V V<sub>CC</sub> = 3.6 V T<sub>A</sub> - Free-Air Temperature - °C

Figure 6.

LOW-TO-HIGH PROPAGATION DELAY TIME

### HIGH-TO-LOW PROPAGATION DELAY TIME

www.ti.com.cn

**ISTRUMENTS**

ZHCS771 - MARCH 2012

### **TYPICAL CHARACTERISTICS (continued)**

# HIGH-LEVEL OUTPUT VOLTAGE HIGH-LEVEL OUTPUT CURRENT 3.5 3.0 VOH - High-Level Output Voltage - V 2.5 2.0 1.5 1.0 0.5 0.0 -60

I<sub>OH</sub> - High-Level Output Current - mA

Figure 8.

### **APPLICATION INFORMATION**

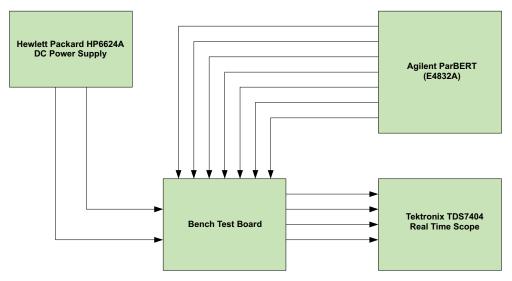

### **EQUIPMENT**

- Hewlett Packard HP6624A DC power supply

- Tektronix TDS7404 Real Time Scope

- Agilent ParBERT E4832A

Figure 10. Equipment Setup

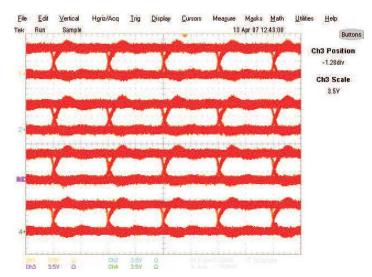

All Rx running at 100 Mbps; Channel 1: 1Y, Channel 2: 2Y; Channel 3: 3Y; Channel 4: 4Y

Figure 11. Typical Eye Patterns SN55LVDS32: (T =  $25^{\circ}$ C;  $V_{CC}$  = 3.6 V; PRBS =  $2^{23-1}$ )

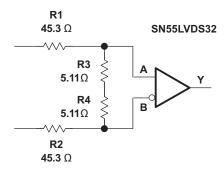

### **USING AN LVDS RECEIVER WITH RS-422 DATA**

Receipt of data from a TIA/EIA-422 line driver can be accomplished using a TIA/EIA-644 line receiver with the addition of an attenuator circuit. This technique gives the user a high-speed and low-power 422 receiver.

If the ground noise between the transmitter and receiver is not a concern (less than ±1 V), the answer can be as simple as shown in Figure 12. A resistor divider circuit in front of the LVDS receiver attenuates the 422 differential signal to LVDS levels.

TEXAS INSTRUMENTS

The resistors present a total differential load of  $100~\Omega$  to match the characteristic impedance of the transmission line and to reduce the signal 10:1. The maximum 422 differential output signal, or 6 V, is reduced to 600 mV. The high input impedance of the LVDS receiver prevents input bias offsets and maintains a greater than 200-mV differential input voltage threshold at the inputs to the divider. This circuit is used in front of each LVDS channel that also receives 422 signals.

NOTE: The components used were standard values. (1) R1, R2 = NRC12F45R3TR, NIC components, 45.3  $\Omega$ , 1/8 W, 1%, 1206 package (2) R3, R4 = NRC12F5R11TR, NIC components, 5.11  $\Omega$ , 1/8 W, 1%, 1206 package (3) The resistor values do not need to be 1% tolerance. However, it can be difficult locating a supplier of resistors having values less than 100  $\Omega$  in stock and readily available. The user may find other suppliers with comparable parts having tolerances of 5% or even 10%. These parts are adequate for use in this circuit.

Figure 12. RS-422 Data Input to an LVDS Receiver Under Low Ground-Noise Conditions

If ground noise between the RS-422 driver and LVDS receiver is a concern, the common-mode voltage must be attenuated. The circuit must then be modified to connect the node between R3 and R4 to the LVDS receiver ground. This modification to the circuit increases the common-mode voltage from ±1 V to greater than ±4.5 V.

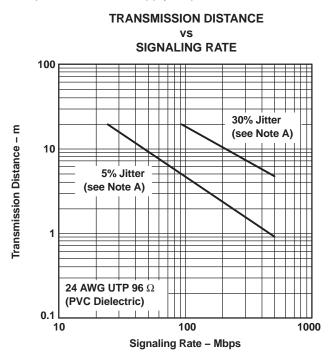

The devices are generally used as building blocks for high-speed point-to-point data transmission where ground differences are less than 1 V. Devices can interoperate with RS-422, PECL, and IEEE-P1596. Drivers/receivers approach ECL speeds without the power and dual-supply requirements.

A. This parameter is the percentage of distortion of the unit interval (UI) with a pseudorandom data pattern.

Figure 13. Typical Transmission Distance Versus Signaling Rate

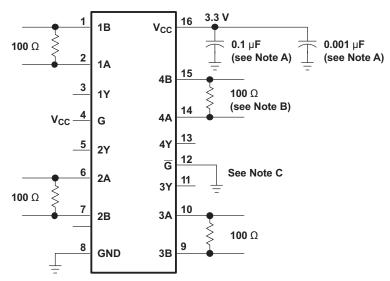

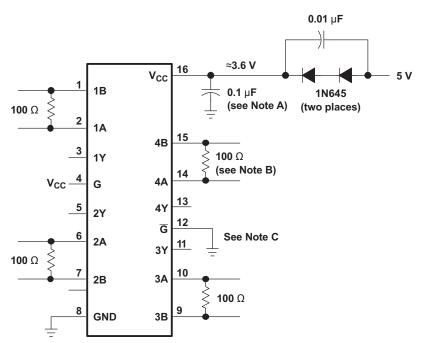

- A. Place a 0.1-μF and a 0.001-μF Z5U ceramic, mica, or polystyrene dielectric, 0805 size, chip capacitor between VCC and the ground plane. The capacitors should be located as close as possible to the device terminals.

- B. The termination resistance value should match the nominal characteristic impedance of the transmission media with ±10%.

- C. Unused enable inputs should be tied to  $V_{\mbox{\footnotesize CC}}$  or GND as appropriate.

Figure 14. Typical Application Circuit Schematic

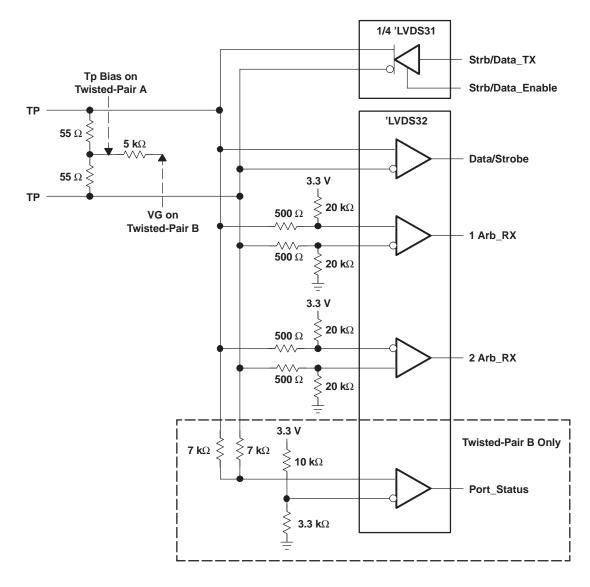

NOTES: A. Resistors are leadless, thick film (0603), 5% tolerance.

- B. Decoupling capacitance is not shown, but recommended.

- C.  $V_{CC}$  is 3 V to 3.6 V.

- D. The differential output voltage of the 'LVDS31 can exceed that specified by IEEE1394.

Figure 15. 100-Mbps IEEE 1394 Transceiver

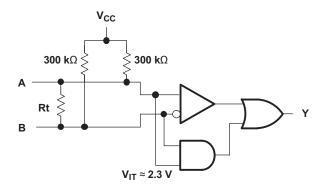

### **FAIL-SAFE**

One of the most common problems with differential signaling applications is how the system responds when no differential voltage is present on the signal pair. The LVDS receiver is like most differential line receivers in that its output logic state can be indeterminate when the differential input voltage is between -100 mV and100 mV if it is within its recommended input common-mode voltage range. However, TI LVDS receivers handle the openinput circuit situation differently.

Open-input circuit means that there is little or no input current to the receiver from the data line itself. This could be when the driver is in a high-impedance state or the cable is disconnected. When this occurs, the LVDS receiver pulls each line of the signal pair to near  $V_{CC}$  through 300-k $\Omega$  resistors (see Figure 16). The fail-safe feature uses an AND gate with input voltage thresholds at about 2.3 V to detect this condition and force the output to a high level, regardless of the differential input voltage.

Figure 16. Open-Circuit Fail-Safe of LVDS Receiver

It is only under these conditions that the output of the receiver is valid with less than a 100-mV differential input voltage magnitude. The presence of the termination resistor, Rt, does not affect the fail-safe function as long as it is connected as shown in Figure 16. Other termination circuits may allow a dc current to ground that could defeat the pullup currents from the receiver and the fail-safe feature.

- A. Place a 0.1-μF Z5U ceramic, mica, or polystyrene dielectric, 0805 size, chip capacitor between V<sub>CC</sub> and the ground plane. The capacitor should be located as close as possible to the device terminals.

- B. The termination resistance value should match the nominal characteristic impedance of the transmission media with ±10%.

- C. Unused enable inputs should be tied to V<sub>CC</sub> or GND, as appropriate.

Figure 17. Operation With 5-V Supply

### **COLD SPARING**

Systems using cold sparing have a redundant device electrically connected without power supplied. To support this configuration, the spare must present a high-input impedance to the system so that it does not draw appreciable power. In cold sparing, voltage may be applied to an I/O before and during power up of a device. When the device is powered off,  $V_{CC}$  must be clamped to ground and the I/O voltages applied must be within the specified recommended operating conditions.

### **RELATED INFORMATION**

IBIS modeling is available for this device. Contact the local TI sales office or the TI Web site at www.ti.com for more information.

For more application guidelines, see the following documents:

- Low-Voltage Differential Signaling Design Notes (SLLA014)

- Interface Circuits for TIA/EIA-644 (LVDS) (SLLA038)

- Reducing EMI With LVDS (SLLA030)

- Slew Rate Control of LVDS Circuits (SLLA034)

- Using an LVDS Receiver With RS-422 Data (SLLA031)

www.ti.com 11-Nov-2025

### PACKAGING INFORMATION

| Orderable part number | Status (1) | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6)                    |

|-----------------------|------------|---------------|----------------|-----------------------|------|-------------------------------|----------------------------|--------------|-------------------------------------|

| 5962-9762201VFA       | Active     | Production    | CFP (W)   16   | 25   TUBE             | No   | SNPB                          | N/A for Pkg Type           | -55 to 125   | 5962-9762201VF<br>A<br>SNV55LVDS32W |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

- (3) RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

- (4) Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

- (5) MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

- (6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

### OTHER QUALIFIED VERSIONS OF SN55LVDS32-SP:

Catalog: SN55LVDS32

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

## **PACKAGE OPTION ADDENDUM**

www.ti.com 11-Nov-2025

NOTE: Qualified Version Definitions:

$_{\bullet}$  Catalog - TI's standard catalog product

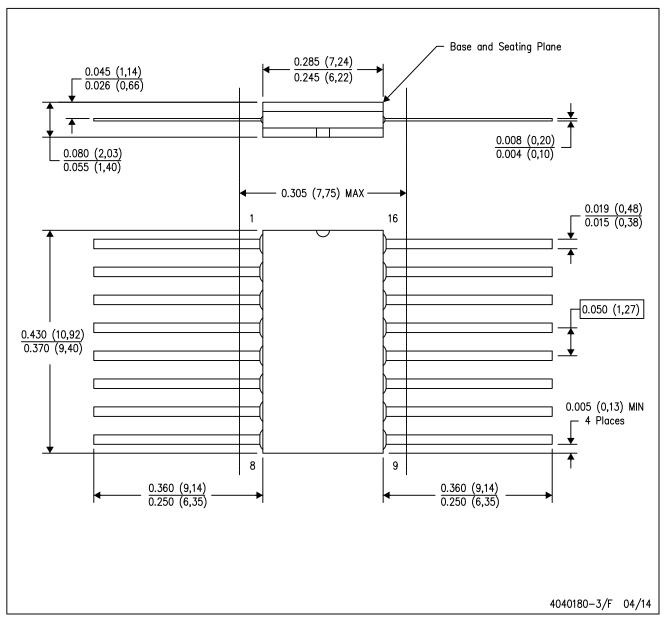

# W (R-GDFP-F16)

### CERAMIC DUAL FLATPACK

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a ceramic lid using glass frit.

- D. Index point is provided on cap for terminal identification only.

- E. Falls within MIL STD 1835 GDFP2-F16

### 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月