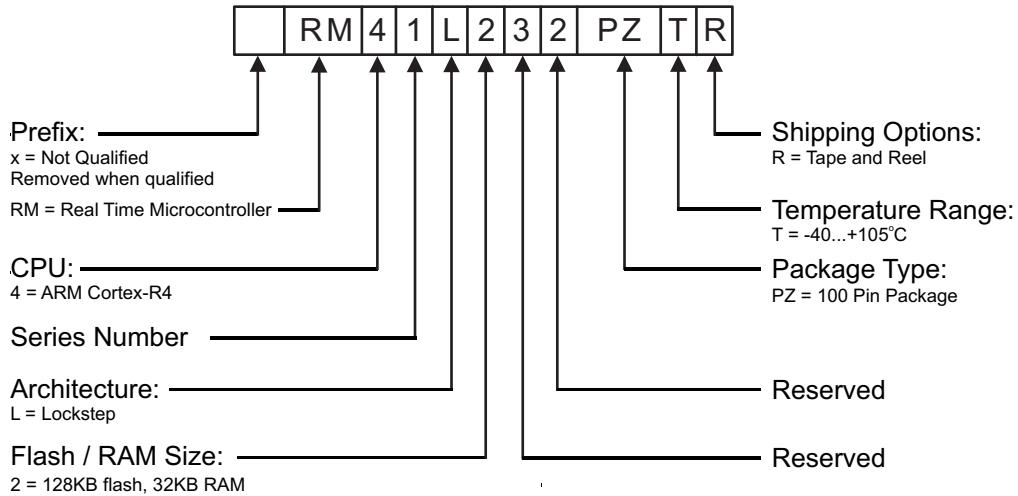

# RM41L232 16 位和 32 位 RISC 闪存微控制器

## 1 器件概述

### 1.1 特性

- 针对安全关键应用的高性能微控制器

- 运行在锁步中的双中央处理单元 (CPU)

- 闪存和 RAM 接口上的 ECC

- 针对 CPU 和片上 RAM 的内置自检

- 带有错误引脚的错误信令模块

- 电压和时钟监视

- ARM® Cortex®-R4 32 位 RISC CPU

- 带有 8 级管线的高效 1.66 DMIPS/MHz

- 8 区域内存保护单元

- 带有第三方支持的开放式架构

- 运行条件

- 80MHz 系统时钟

- 内核电源电压 ( $V_{CC}$ ): 标称 1.2V

- I/O 电源电压 ( $V_{CCIO}$ ): 标称 3.3V

- ADC 电源电压 ( $V_{CCAD}$ ): 标称 3.3V

- 集成存储器

- 128KB 且支持 ECC 的程序闪存

- 支持 ECC 的 32KB RAM

- 支持 ECC、用于仿真 EEPROM 的 16KB 闪存

- Hercules™ 通用平台架构

- 系列间一致的存储器映射

- 实时中断 (RTI) 定时器 (操作系统 (OS) 定时器)

- 96 通道矢量中断模块 (VIM)

- 2 通道循环冗余校验器 (CRC)

- 带有内置跳周检测器的调频锁相环 (FMPLL)

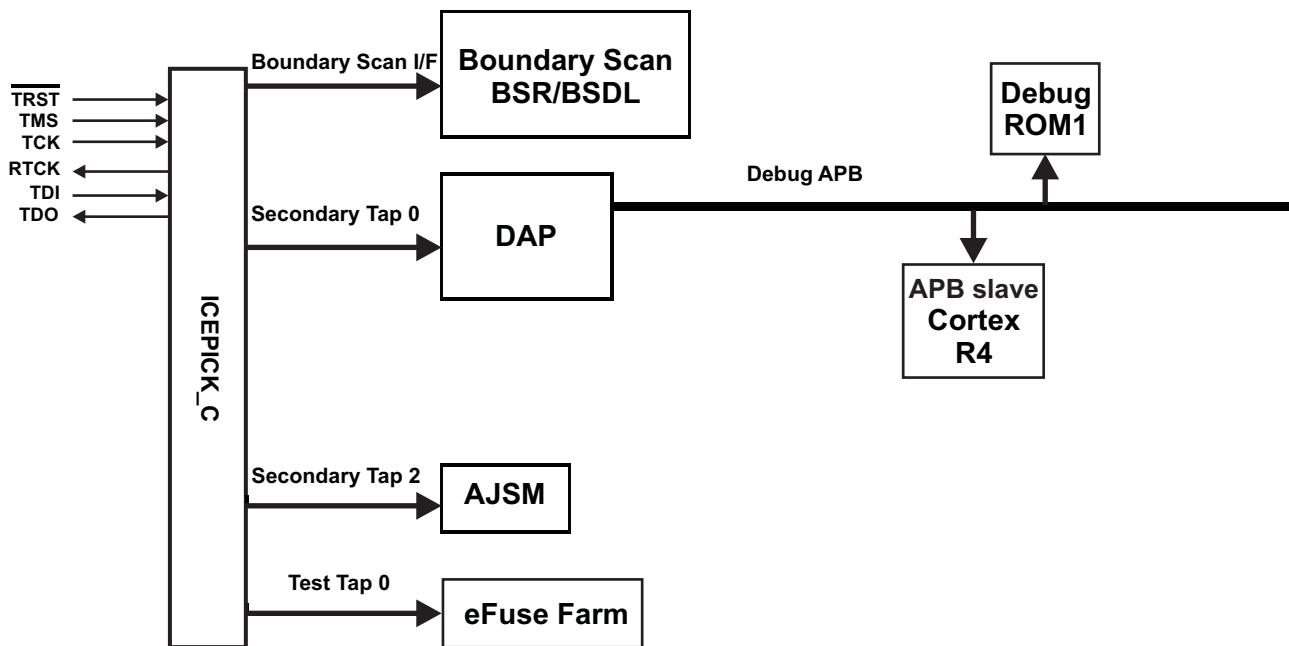

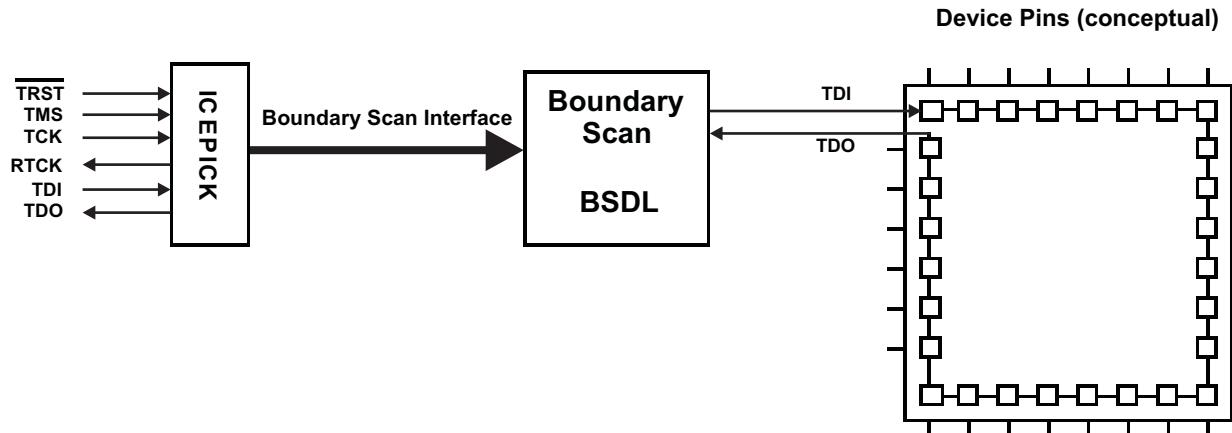

- IEEE 1149.1 JTAG, 边界扫描和 ARM CoreSight™ 组件

- 高级 JTAG 安全模块 (AJSM)

- 多通信接口

- 两个控制器局域网 (CAN) 控制器 (DCAN)

- DCAN1 - 32 个具有奇偶校验保护的邮箱

- DCAN2 - 16 个具有奇偶校验保护的邮箱

- 与 CAN 协议 2.0B 版兼容

- 多通道缓冲串行外设接口 (MibSPI) 模块

- 128 个具有奇偶校验保护的字

- 两个标准串行外设接口 (SPI) 模块

- 支持本地互连网络 (LIN 2.1) 接口的 UART (SCI) 接口

- 高端定时器 (N2HET) 模块

- 多达 19 个可编程引脚

- 带有奇偶校验保护的 128 字指令 RAM

- 专用高端定时器传输单元 (HTU)

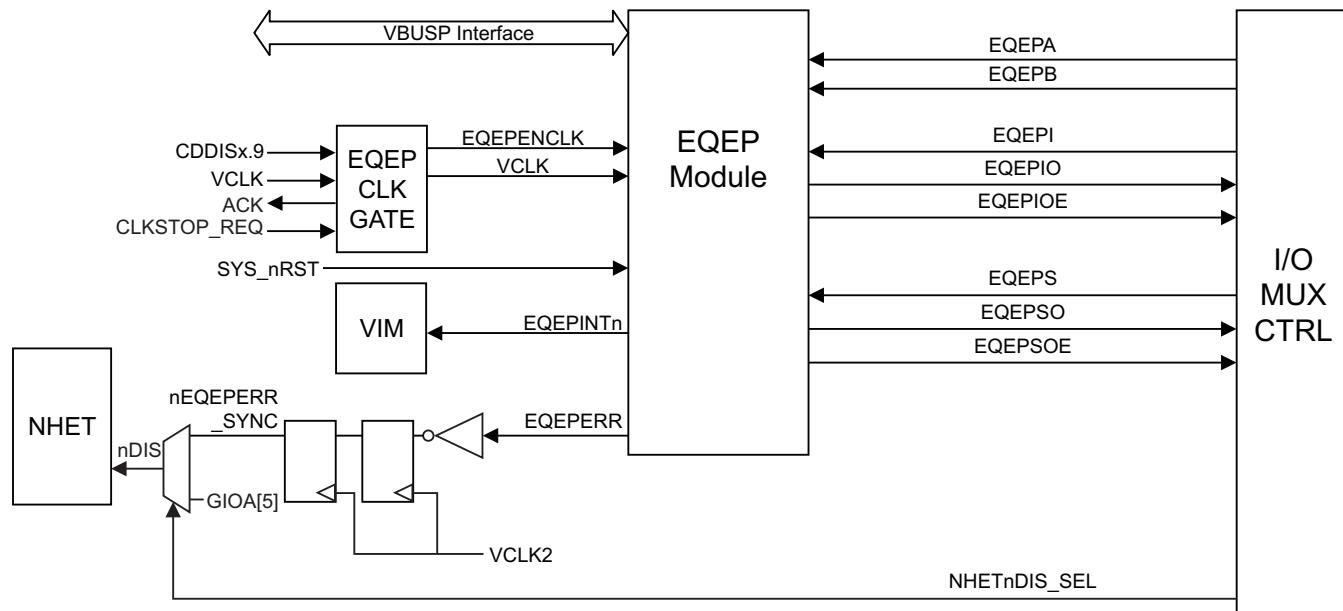

- 增强型正交编码器脉冲 (eQEP) 模块

- 电机位置编码器接口

- 12 位多通道缓冲模数转换器 (ADC) 模块

- 16 个通道

- 64 个具有奇偶校验保护的结果缓冲器

- 多达 45 个通用 I/O (GPIO) 功能引脚

- 8 个专用 GPIO 引脚, 最多带有 8 个外部中断

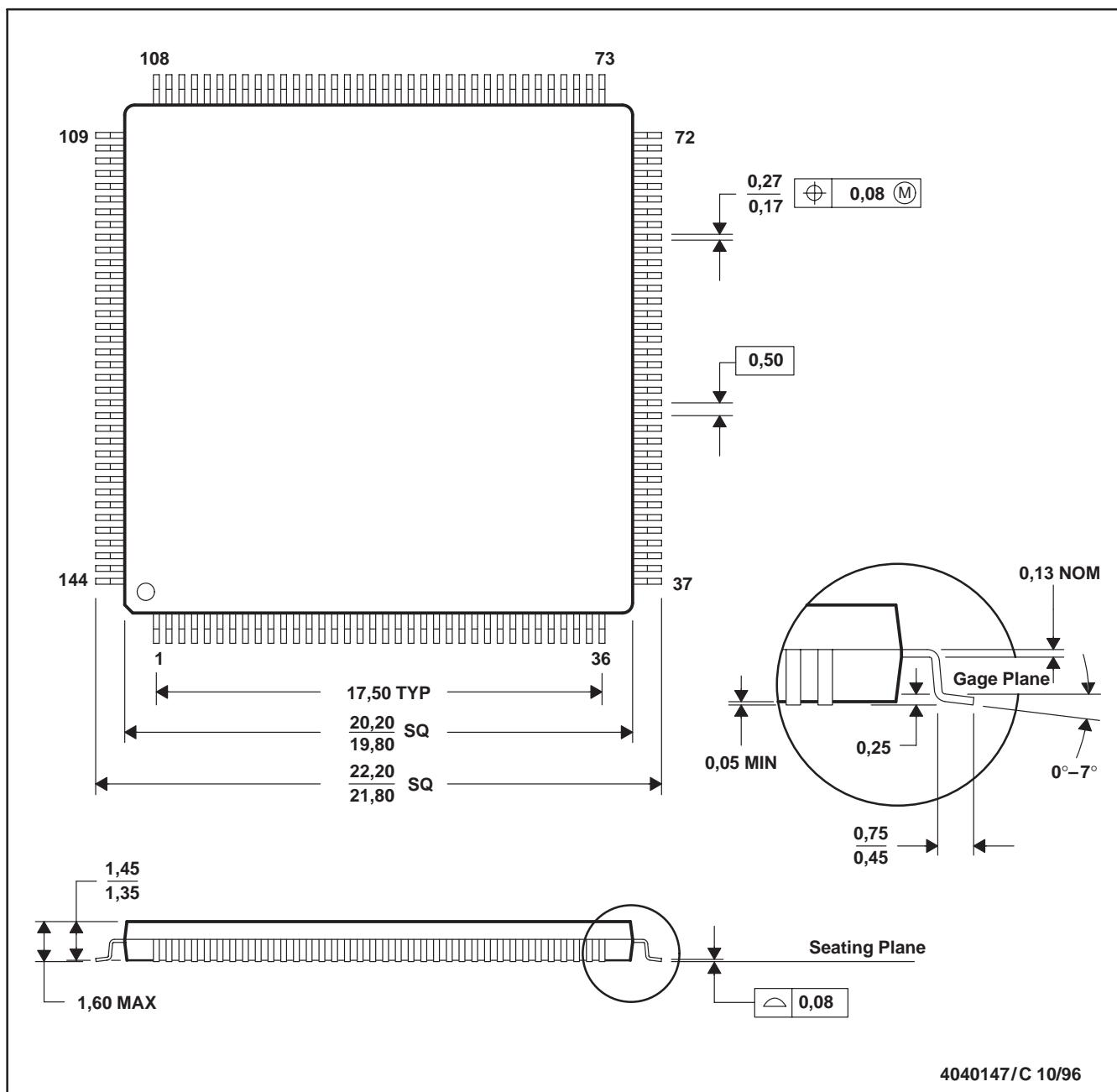

- 封装

- 100 引脚四方扁平封装 (PZ) [绿色环保]

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

## 1.2 应用

- 工业安全应用

- 工业自动化

- 安全可编程逻辑控制器 (PLC)

- 发电和配电

- 涡轮机和风力发动机

- 电梯和自动扶梯

- 医疗应用

- 呼吸机

- 除颤器

- 输液泵和胰岛素泵

- 放射治疗

- 机器人外科手术

### 1.3 说明

RM41L232 器件是用于安全系统的高性能微控制器系列。该安全架构包括锁步中的双 CPU, CPU 和内存内置自检 (BIST) 逻辑, 闪存和数据 SRAM 上的 ECC, 外设存储器上的奇偶校验以及外设 IO 上的回路功能。

RM41L232 器件集成了 ARM Cortex-R4 CPU, 该 CPU 提供高效 1.66 DMIPS/MHz, 运行频率高达 80MHz, 可提供高达 132 DMIPS。此器件支持小端序 (LE) 格式。

RM41L232 器件具有 128KB 集成闪存以及 32KB 数据 RAM, 具有单位纠错和双位错误检测功能。该器件上的闪存存储器是实现了 64 位宽数据总线接口的可电擦除且可编程的非易失性存储器。对于所有读取、编程和擦除操作, 该闪存都工作在 3.3V 电源输入 (与 I/O 电源相同的电平)。当处于管线模式时, 闪存可在 80MHz 的系统时钟频率下工作。SRAM 在整个支持的频率范围内支持字节、半字和字模式的单周期读取/写入访问。

RM41L232 器件具有针对实时控制类应用的外设, 包括带有总共 最多 19 个 I/O 引脚的新一代高端定时器 (N2HET) 时序协处理器和支持 16 个输入的 12 位模数转换器 (ADC), 采用 100 引脚封装。

N2HET1 是一款高级智能定时器, 此定时器能够为实时应用提供精密的计时功能。该定时器为软件控制型, 采用一个精简指令集, 并具有一个专用的定时器微级机和一个连接的 I/O 端口。N2HET 可用于脉宽调制输出、捕捉或比较输入, 或 GPIO。N2HET 特别适合于要求多个传感器信息并且用复杂和准确时间脉冲来驱动致动器的应用。一个高端定时器传输单元 (HTU) 能够执行 DMA 类型处理来与主存储器之间传输 N2HET 数据。一个内存保护单元 (MPU) 被内置于 HTU 内。

增强型正交编码器脉冲 (eQEP) 模块用于直接连接一个线性或旋转递增编码器, 进而从一个高性能运动和位置控制系统中正在旋转的机械中获得位置、方向、和速度信息。

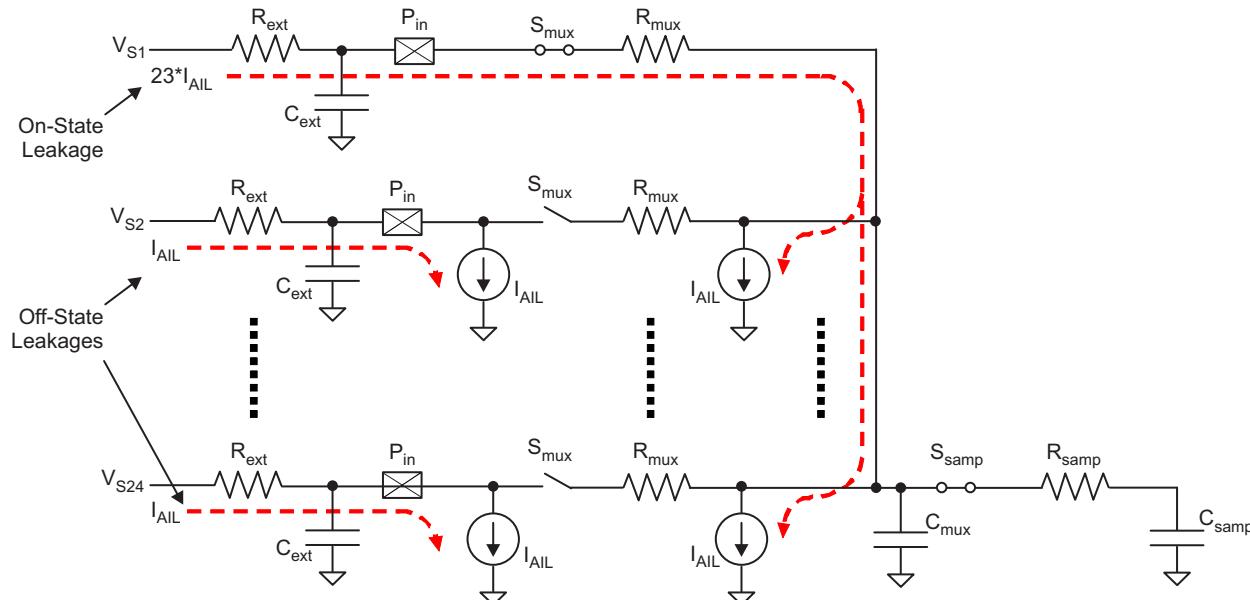

该器件具有一个 12 位分辨率 MibADC, 共有 16 个通道以及带奇偶校验保护的 64 字缓冲 RAM。MibADC 通道可被独立转换或者可针对顺序转换序列由软件分组。有三个独立的组。每个组可在被触发时转换一次, 或者通过配置以执行连续转换模式。

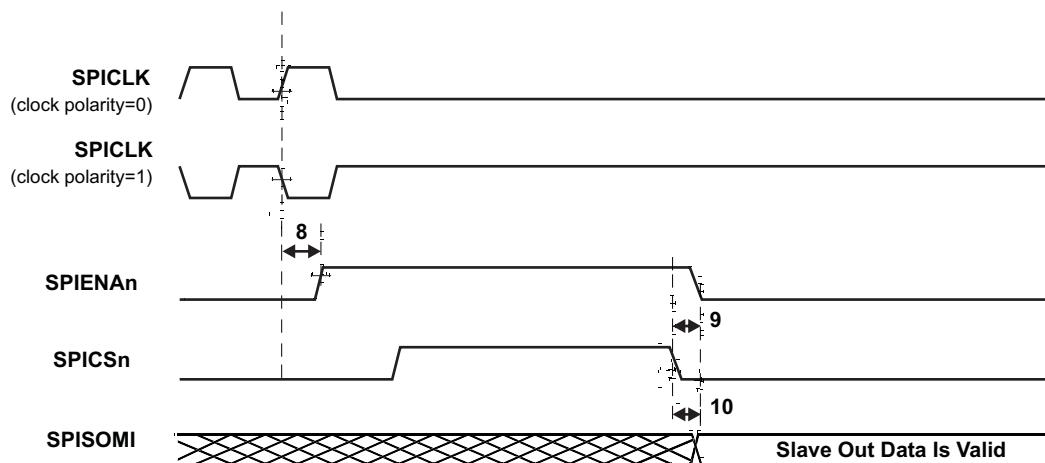

该器件有多个通信接口: 一个 MibSPI, 两个 SPI, 一个 UART/LIN 和两个 DCAN。SPI 为相似的移位寄存器类型器件之间的高速通信提供了一种便捷的串行交互方法。UART/LIN 支持本地互联标准 2.1 并可被用作一个使用标准不归零码 (NRZ) 格式的全双工模式 UART。DCAN 支持 CAN 2.0B 协议标准并使用串行多主机通信协议, 此协议有效支持对最高速率为 1Mbps 的稳健通信实现分布式实时控制。DCAN 非常适合嘈杂和恶劣环境中的应用 (例如: 汽车和工业领域), 此类应用需要可靠的串行通信或多路复用布线。

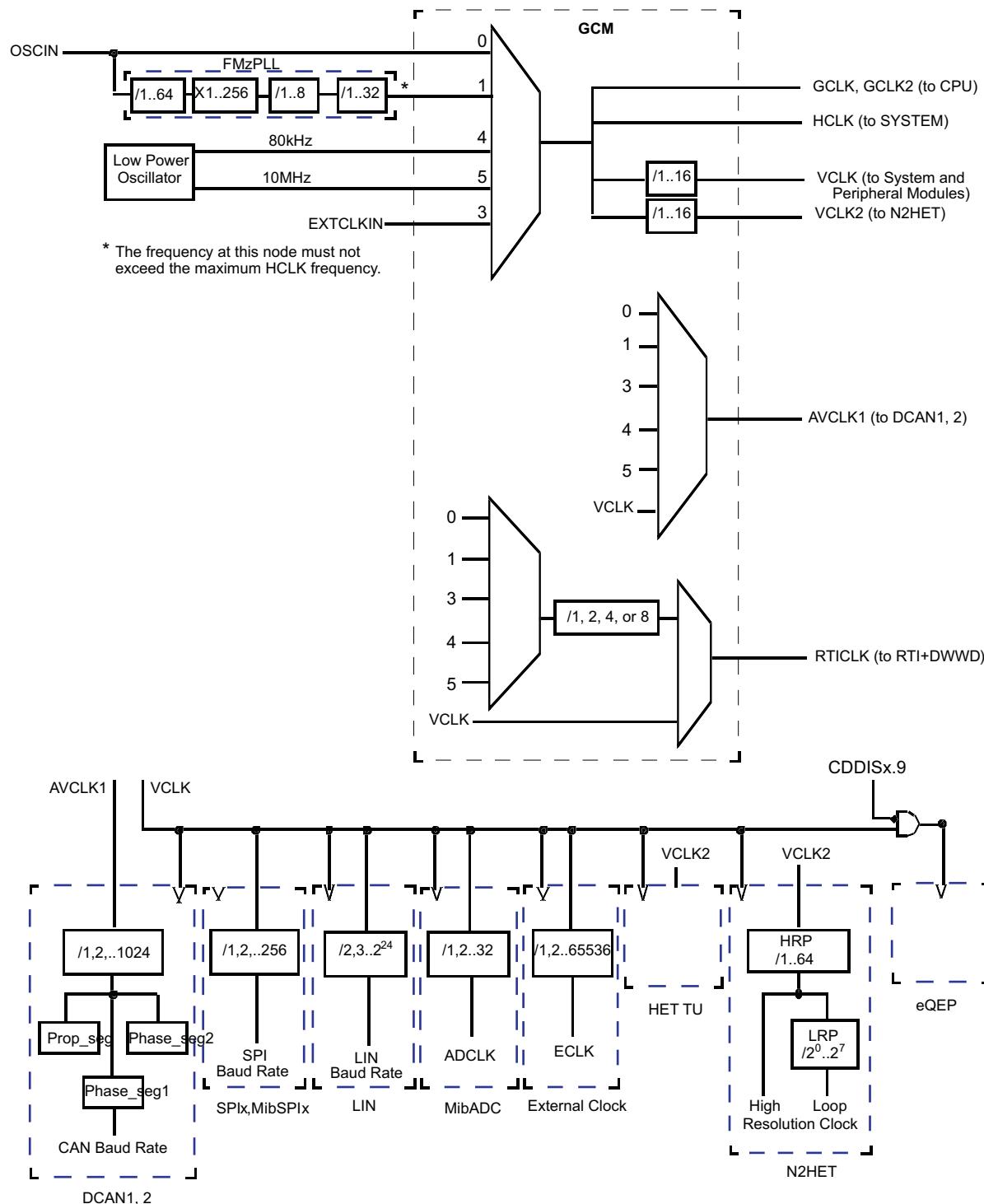

该调频锁相环 (FMPPLL) 时钟模块被用来将外部频率基准与一个内部使用的更高频率相乘。FMPPLL 为全局时钟模块 (GCM) 提供 5 个可能时钟源输入中的一个。GCM 管理可用时钟源与器件时钟域间的映射。

该器件还具有一个外部时钟预分频器 (ECP) 模块。当 ECP 启用时, 它在 ECLK 引脚上输出连续的外部时钟。ECLK 频率与外设接口时钟 (VCLK) 频率的比例是用户可编程的。该低频输出可进行外部监视, 作为器件运行频率的指示器。

信令模块 (ESM) 监控所有器件错误并在检测到故障时确定是触发一个中断还是触发一个外部错误引脚。可从外部监视 nERROR 引脚, 作为微控制器内故障条件的指示器。

I/O 多路复用和控制模块 (IOMM) 允许配置输入/输出引脚以支持替代功能。有关本器件上支持多个功能的引脚列表, 请参见表 3-17。

凭借集成的安全特性以及各类通信和控制外设, RM41L232 器件已成为对安全要求严格的实时控制应用的理想解决方案。

#### 器件信息<sup>(1)</sup>

| 器件编号       | 封装         | 封装尺寸              |

|------------|------------|-------------------|

| RM41L232PZ | LQFP (100) | 14.00mm x 14.00mm |

(1) 更多信息请参见 节 8, 机械封装和可订购产品信息。

## 1.4 功能方框图

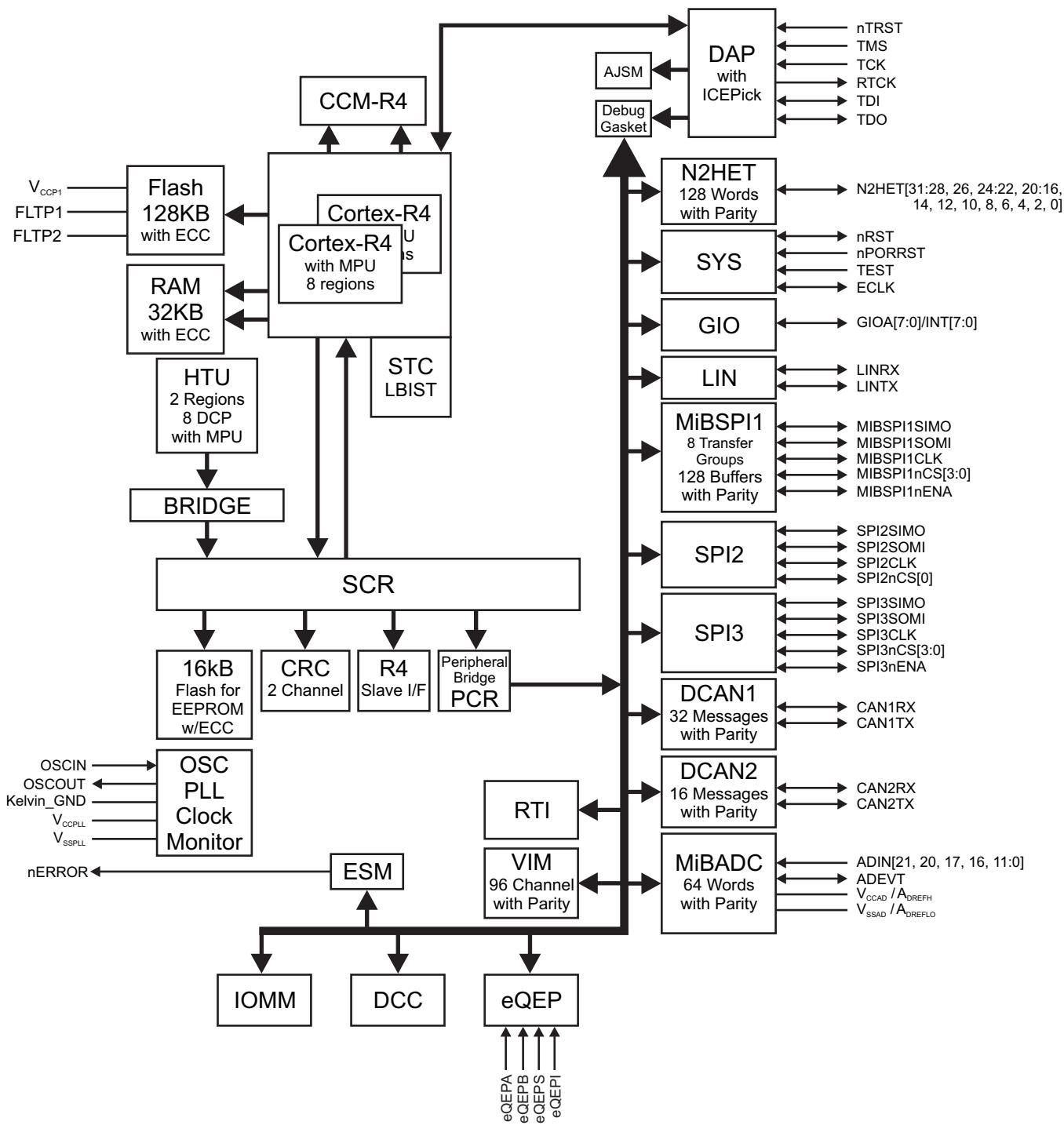

图 1-1 显示器件的功能方框图。

图 1-1. 功能方框图

## 内容

|          |                        |           |          |                      |            |

|----------|------------------------|-----------|----------|----------------------|------------|

| <b>1</b> | <b>器件概述</b>            | <b>1</b>  | 5.9      | 闪存存储器                | <b>46</b>  |

| 1.1      | 特性                     | 1         | 5.10     | 程序闪存的闪存编程和擦除时序       | 48         |

| 1.2      | 应用                     | 2         | 5.11     | 闪存编程和擦除时序数据闪存        | 48         |

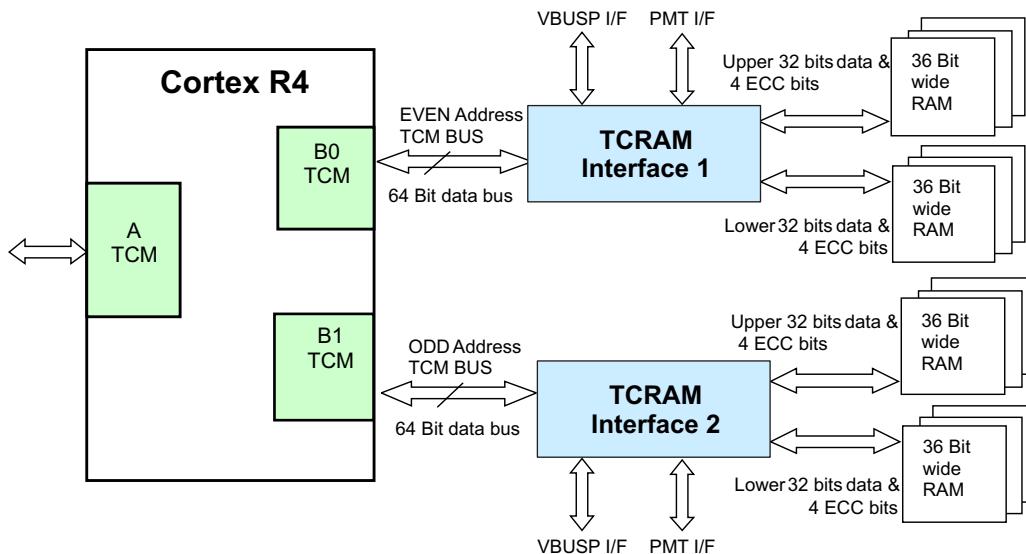

| 1.3      | 说明                     | 3         | 5.12     | 紧耦合 RAM 接口模块         | 49         |

| 1.4      | 功能方框图                  | 4         | 5.13     | 用于外设 RAM 访问的奇偶校验保护   | 49         |

| <b>2</b> | <b>修订历史记录</b>          | <b>6</b>  | 5.14     | 片载 SRAM 初始化和测试       | 51         |

| <b>3</b> | <b>器件封装和引脚功能</b>       | <b>7</b>  | 5.15     | 矢量中断管理器              | 53         |

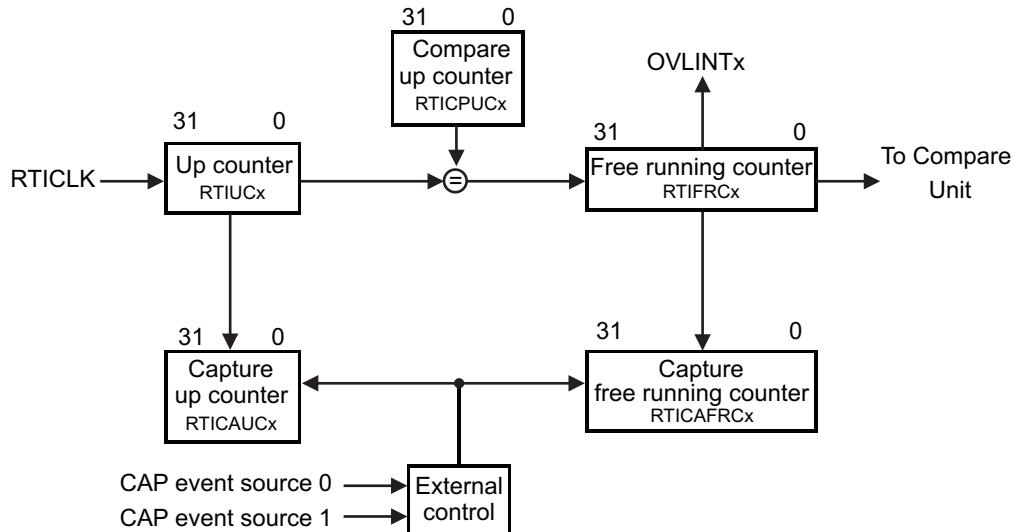

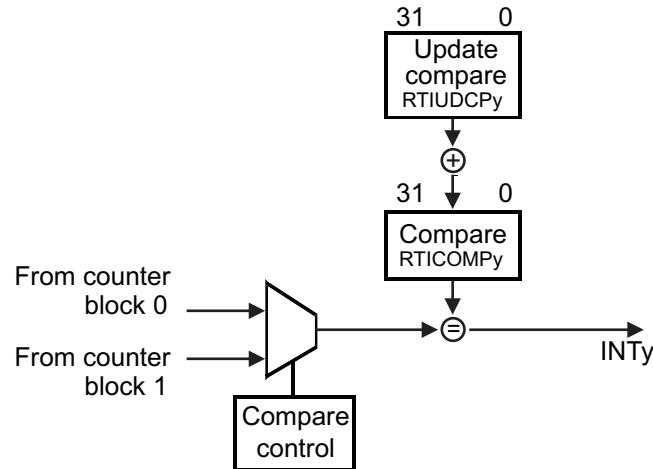

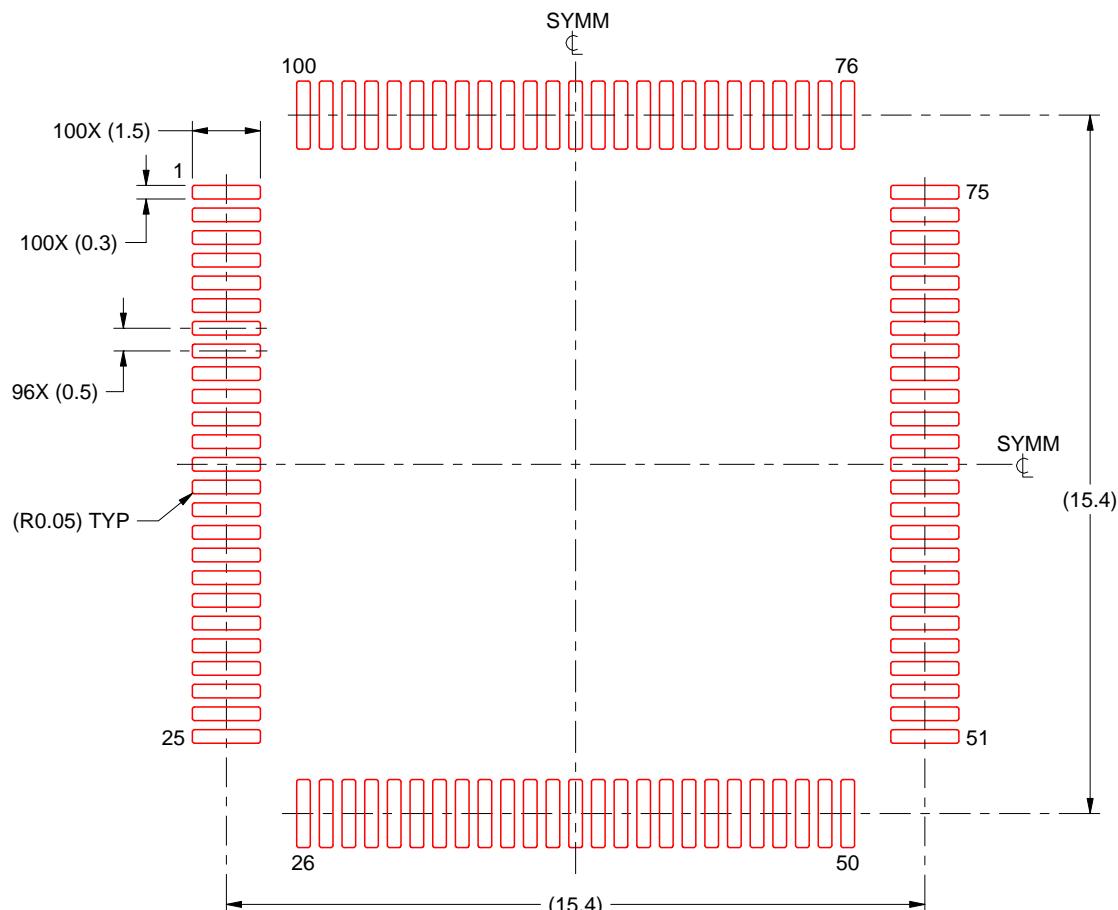

| 3.1      | PZ QFP 封装引脚分配 (100 引脚) | 7         | 5.16     | 实时中断模块               | 55         |

| 3.2      | 引脚配置和功能                | 8         | 5.17     | 错误信令模块               | 57         |

| 3.3      | 输出复用和控制                | 14        | 5.18     | 复位/异常中断/错误状态         | 61         |

| 3.4      | 特定复用选项                 | 15        | 5.19     | 数字窗口式看门狗             | 62         |

| <b>4</b> | <b>规范</b>              | <b>16</b> | 5.20     | 调试子系统                | 63         |

| 4.1      | 自然通风运行温度范围内的最大绝对值      | 16        | <b>6</b> | <b>外设信息和电气技术规范</b>   | <b>67</b>  |

| 4.2      | 处理额定值                  | 16        | 6.1      | 外设图例                 | 67         |

| 4.3      | 上电小时数 (POH)            | 16        | 6.2      | 多缓冲12位模数转换器          | 67         |

| 4.4      | 建议的运行条件                | 17        | 6.3      | 通用输入/输出              | 75         |

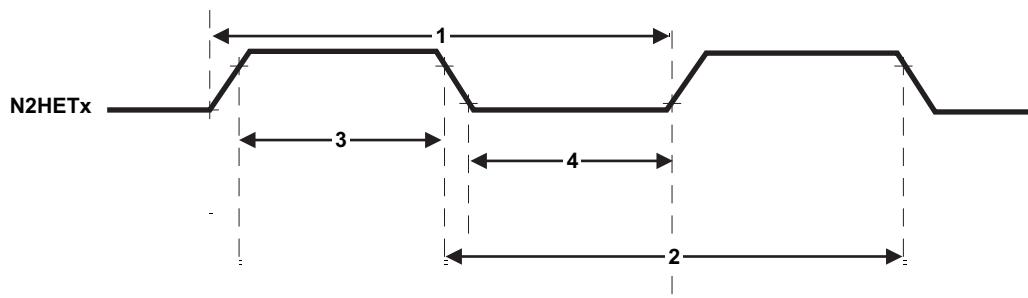

| 4.5      | 建议时钟域运行条件下的开关特性        | 17        | 6.4      | 增强型高端定时器 (N2HET)     | 76         |

| 4.6      | 要求等待状态                 | 18        | 6.5      | 控制器局域网络 (DCAN)       | 79         |

| 4.7      | 推荐运行条件内的功耗             | 19        | 6.6      | 本地互连网络接口 (LIN)       | 80         |

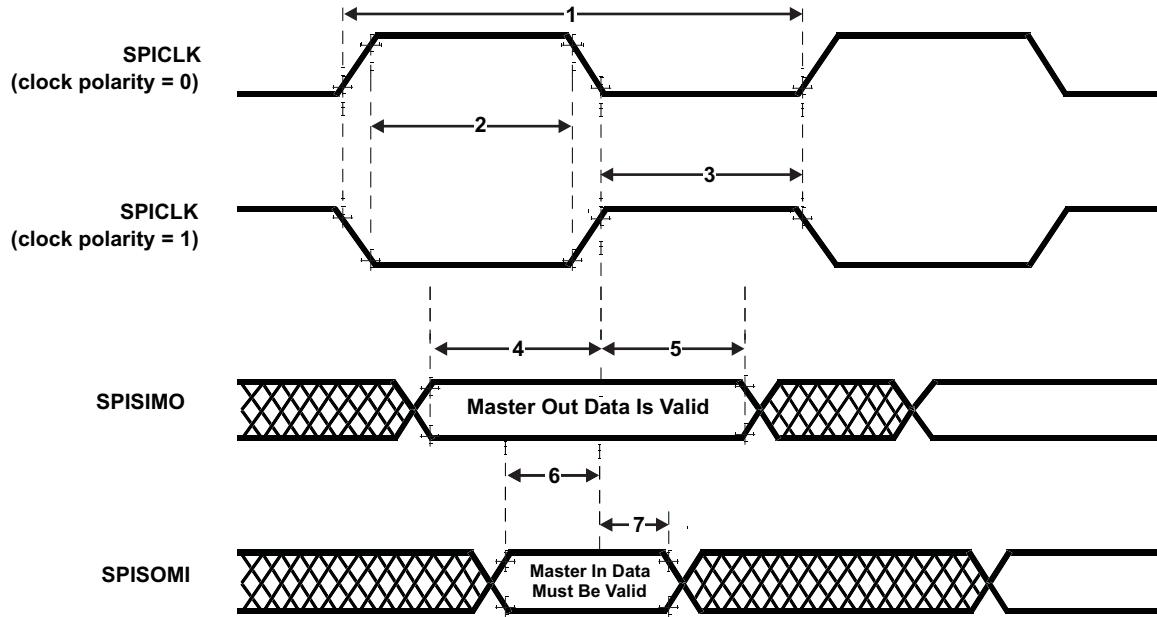

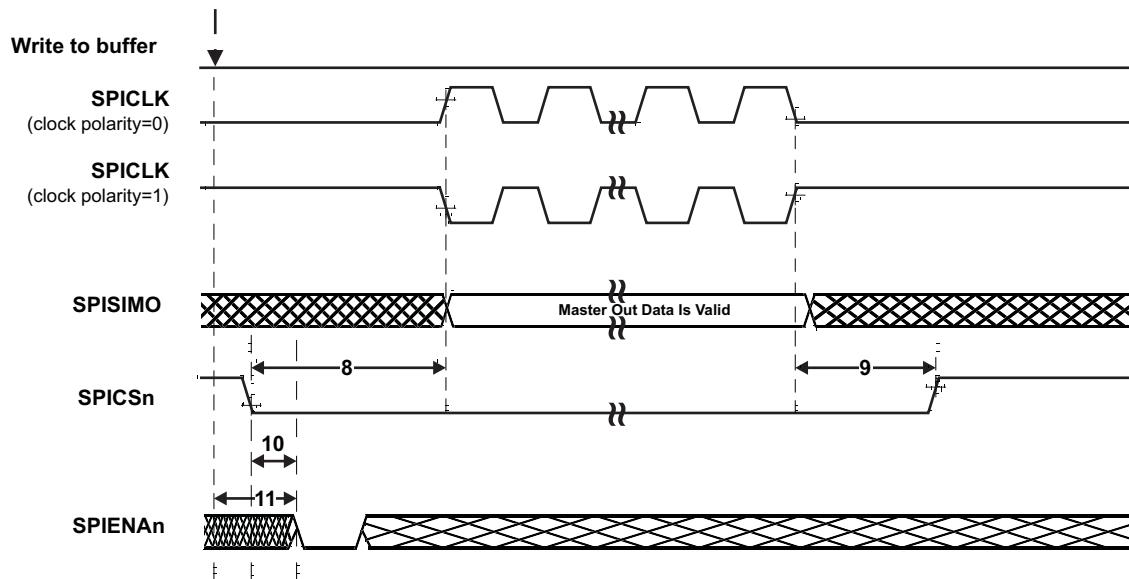

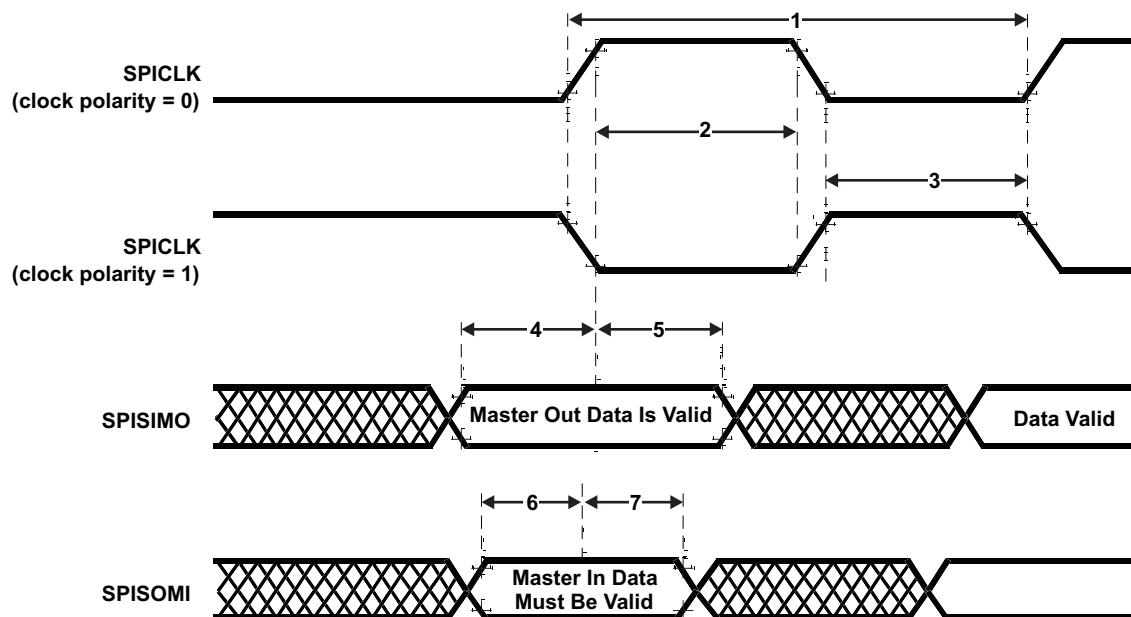

| 4.8      | PZ 的热阻特性               | 20        | 6.7      | 多缓冲/标准串行外设接口         | 81         |

| 4.9      | 推荐运行条件下的输入/输出电气特性      | 20        | 6.8      | 增强型正交编码器 (eQEP)      | 91         |

| 4.10     | 输出缓冲器驱动强度              | 21        | <b>7</b> | <b>器件和文档支持</b>       | <b>93</b>  |

| 4.11     | 输入时序                   | 22        | 7.1      | 器件支持                 | 93         |

| 4.12     | 输出时序                   | 23        | 7.2      | 文档支持                 | 95         |

| <b>5</b> | <b>系统信息和电气技术规范</b>     | <b>25</b> | 7.3      | 社区资源                 | 95         |

| 5.1      | 电压监视器特性                | 25        | 7.4      | 商标                   | 95         |

| 5.2      | 电源排序和加电复位              | 26        | 7.5      | 静电放电警告               | 95         |

| 5.3      | 热复位 (nRST)             | 28        | 7.6      | 术语表                  | 95         |

| 5.4      | ARM Cortex-R4 CPU 信息   | 29        | 7.7      | 器件识别码寄存器             | 95         |

| 5.5      | 时钟                     | 32        | 7.8      | 芯片识别寄存器              | 96         |

| 5.6      | 时钟监视                   | 39        | 7.9      | 模块认证                 | 97         |

| 5.7      | 去毛刺脉冲滤波器               | 41        | <b>8</b> | <b>机械、封装和可订购产品附录</b> | <b>102</b> |

| 5.8      | 器件存储器映射                | 42        | 8.1      | 封装信息                 | 102        |

## 2 修订历史记录

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| 日期         | 修订版本 | 注释     |

|------------|------|--------|

| 2014 年 8 月 | *    | 最初发布版本 |

### 3 器件封装和引脚功能

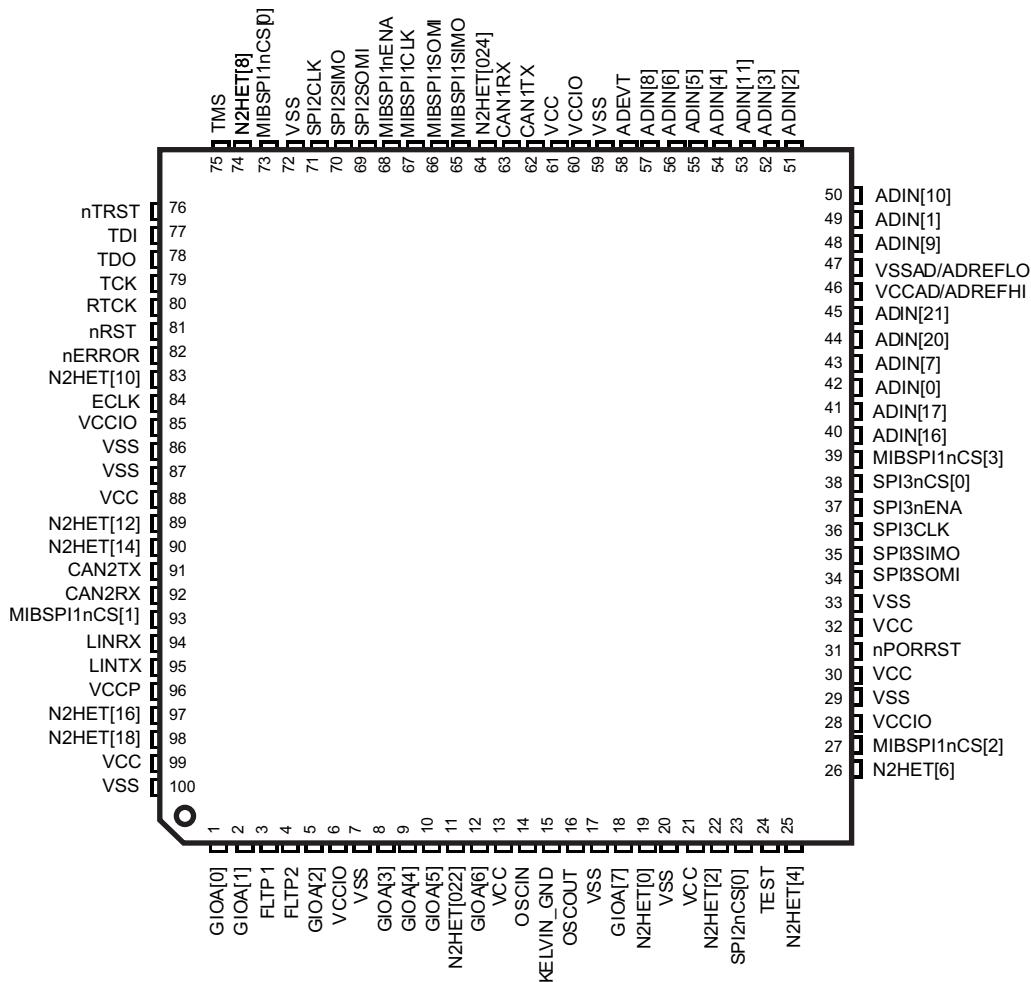

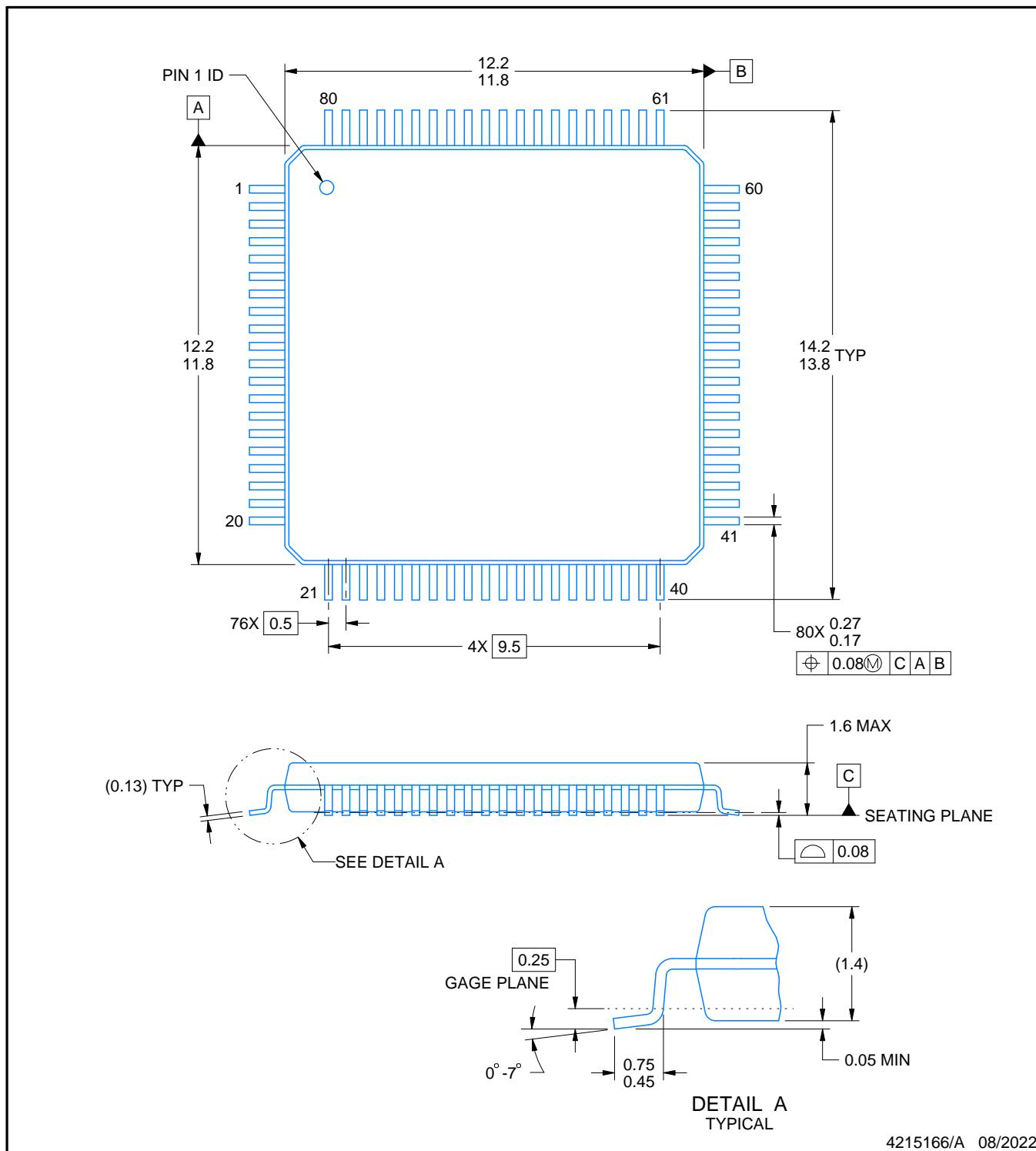

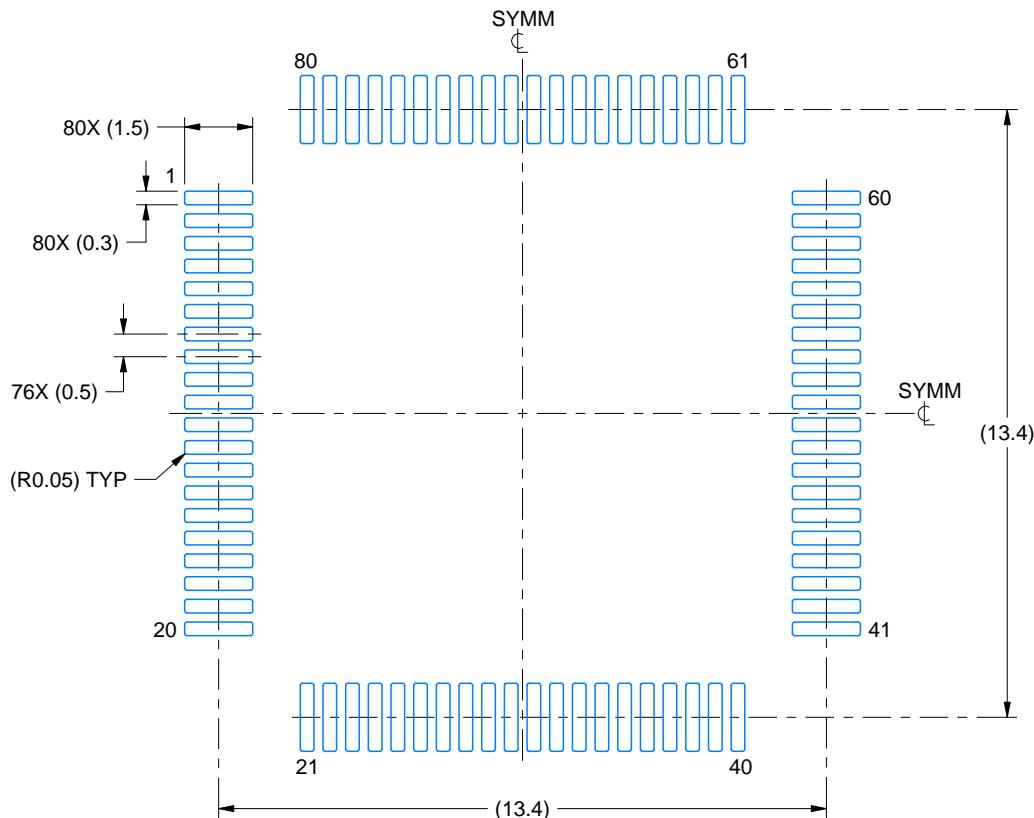

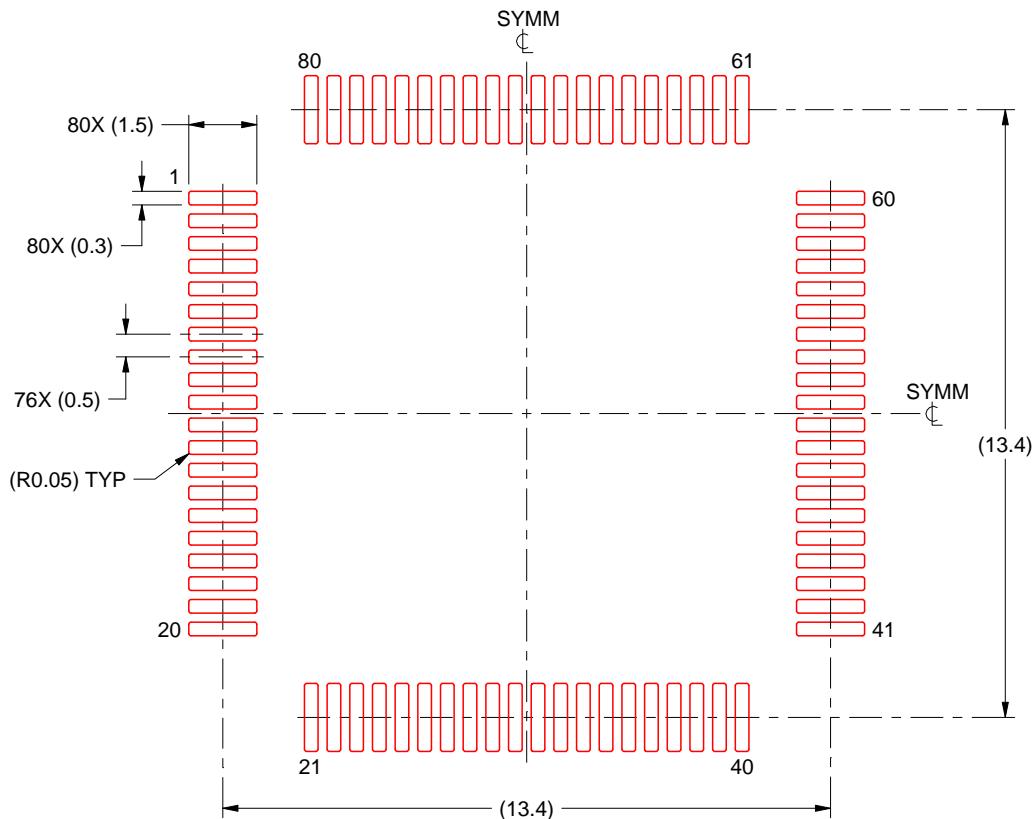

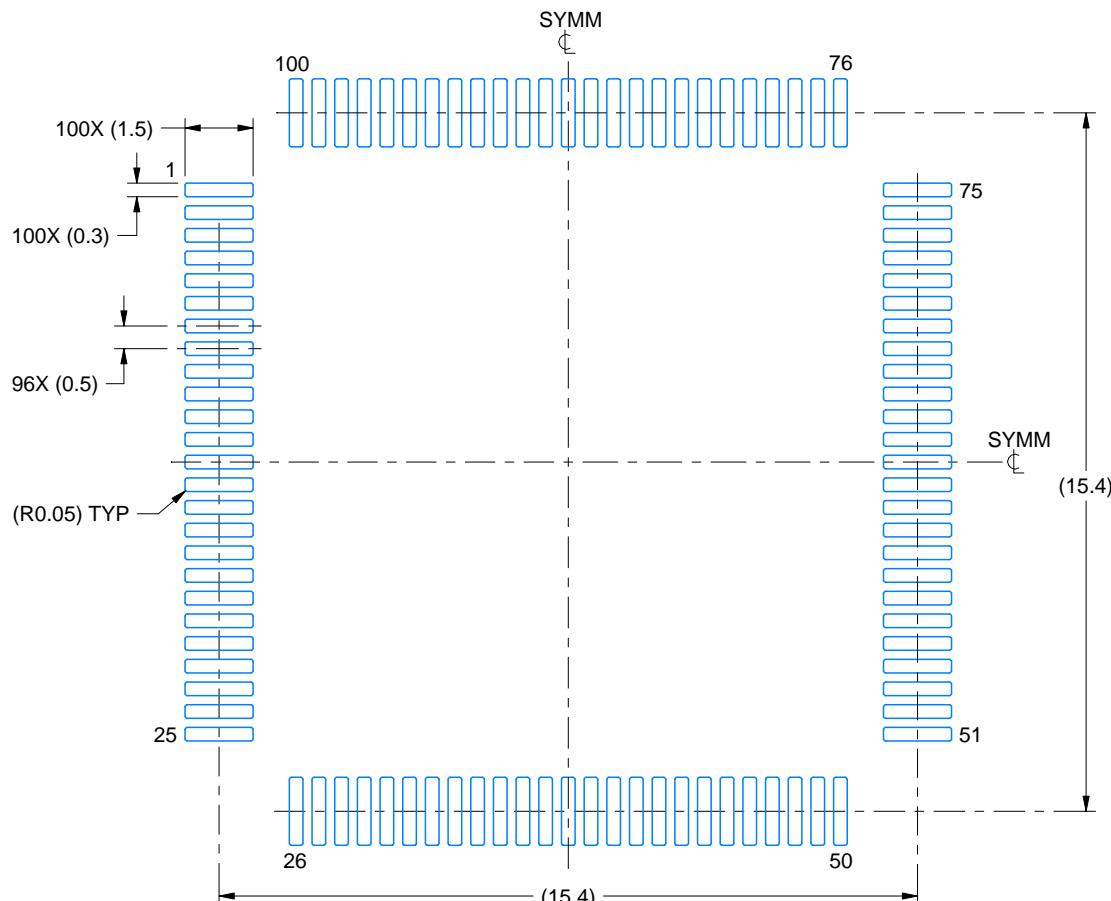

#### 3.1 PZ QFP 封装引脚分配 (100 引脚)

图 3-1. PZ QFP 封装引脚分配 (100 引脚)

请注意：引脚可具有复用功能。上面的图中只显示了缺省功能。

### 3.2 引脚配置和功能

下表确认了外部信号名称、相关的引脚数量以及机械封装标识符、引脚类型（输入，输出，IO，电源或接地）、引脚是否带有任何内部上拉/下拉电阻器、引脚是否可被配置为一个通用输入输出（GIO），和一个功能引脚说明。

注

当 nPORRST 为低电平以及变为高电平后，所有 I/O 引脚，除了 nRST 之外，立即都被配置为输入。

在 nPORRST 为低电平时，所有只输出引脚可被配置为输入，而在 nPORRST 变为高电平后，被立即配置为输出。

当 nPORRST 为低电平时，输入缓冲器被禁用，并且输出缓冲器为三态。

注

在下面的引脚功能表中，“缺省拉动状态”是 nPORRST 为低电平时以及 nPORRST 变为高电平后的上拉或下拉状态。当软件为一个替代功能配置引脚时，缺省拉动方向也许会发生变化。

“拉动类型”是指针对指定引脚使能粗体名称的信号时生效的拉动类型。

#### 3.2.1 高端定时器 (N2HET)

表 3-1. 高端定时器 (N2HET)

| 引脚                                             | 信号名称          | 信号类型 | 缺省拉动状态 | 拉动类型     | 说明                                                                |

|------------------------------------------------|---------------|------|--------|----------|-------------------------------------------------------------------|

|                                                | <b>100 PZ</b> |      |        |          |                                                                   |

| <b>N2HET[0]</b>                                | 19            | I/O  | 下拉     | 可编程，20uA | 定时器输入捕捉或输出比较。N2HET 适用引脚可被设定为通用输入/输出（GIO）。                         |

| <b>N2HET[2]</b>                                | 22            |      |        |          | 每个 N2HET 引脚都配备有一个抑制滤波器。如果该引脚被配置为一个输入引脚，它将启用过滤器来过滤掉小于一个可编程持续时间的脉冲。 |

| <b>N2HET[4]</b>                                | 25            |      |        |          |                                                                   |

| <b>N2HET[6]</b>                                | 26            |      |        |          |                                                                   |

| <b>N2HET[8]</b>                                | 74            |      |        |          |                                                                   |

| <b>N2HET[10]</b>                               | 83            |      |        |          |                                                                   |

| <b>N2HET[12]</b>                               | 89            |      |        |          |                                                                   |

| <b>N2HET[14]</b>                               | 90            |      |        |          |                                                                   |

| <b>N2HET[16]</b>                               | 97            |      |        |          |                                                                   |

| MIBSPI1nCS[1]/EQEPS/<br><b>N2HET[17]</b>       | 93            |      |        |          |                                                                   |

| <b>N2HET[18]</b>                               | 98            |      |        |          |                                                                   |

| MIBSPI1nCS[2]/N2HET[20]/<br><b>N2HET[19]</b>   | 27            |      |        |          |                                                                   |

| MIBSPI1nCS[2]/ <b>N2HET[20]</b> /<br>N2HET[19] | 27            |      |        |          |                                                                   |

| <b>N2HET[22]</b>                               | 11            |      |        |          |                                                                   |

| <b>N2HET[24]</b>                               | 64            |      |        |          |                                                                   |

| MIBSPI1nCS[3]/ <b>N2HET[26]</b>                | 39            |      |        |          |                                                                   |

| ADEV/T/N2HET[28]                               | 58            |      |        |          |                                                                   |

| <b>GIOA[7]/N2HET[29]</b>                       | 18            |      |        |          |                                                                   |

| MIBSPI1nENA/N2HET[23]/<br><b>N2HET[30]</b>     | 68            |      |        |          |                                                                   |

| <b>GIOA[6]/SPI2nCS[1]/N2HET[31]</b>            | 12            |      |        |          |                                                                   |

### 3.2.2 增强型正交编码器脉冲模块 (eQEP)

表 3-2. 增强型正交编码器脉冲模块 (eQEP)

| 引脚                            | 信号类型              | 缺省拉动状态 | 拉动类型 | 说明           |

|-------------------------------|-------------------|--------|------|--------------|

| 信号名称                          | <b>100<br/>PZ</b> |        |      |              |

| SPI3CLK/EQEPA                 | 36                | 输入     | 上拉   | 增强型 QEP 输入 A |

| SPI3nENA/EQEPB                | 37                | 输入     |      | 增强型 QEP 输入 B |

| SPI3nCS[0]/EQEPI              | 38                | I/O    |      | 增强型 QEP 索引   |

| MIBSPI1nCS[1]/EQEPS/N2HET[17] | 93                | I/O    |      | 增强型 QEP 阀门   |

### 3.2.3 通用输入/输出 (GPIO)

表 3-3. 通用输入/输出 (GPIO)

| 引脚                           | 信号类型              | 缺省拉动状态 | 拉动类型 | 说明                                                        |

|------------------------------|-------------------|--------|------|-----------------------------------------------------------|

| 信号名称                         | <b>100<br/>PZ</b> |        |      |                                                           |

| GIOA[0]/SPI3nCS[3]           | 1                 | I/O    | 下拉   | 可编程, 20uA<br>通用输入/输出<br>所有 GPIO 引脚能够在上升/下降/双边沿上生成 CPU 中断。 |

| GIOA[1]/SPI3nCS[2]           | 2                 |        |      |                                                           |

| GIOA[2]/SPI3nCS[1]           | 5                 |        |      |                                                           |

| GIOA[3]/SPI2nCS[3]           | 8                 |        |      |                                                           |

| GIOA[4]/SPI2nCS[2]           | 9                 |        |      |                                                           |

| GIOA[5]/EXTCLKIN             | 10                |        |      |                                                           |

| GIOA[6]/SPI2nCS[1]/N2HET[31] | 12                |        |      |                                                           |

| GIOA[7]/N2HET[29]            | 18                |        |      |                                                           |

### 3.2.4 控制器局域网络接口模块 (DCAN1, DCAN2)

表 3-4. 控制器局域网络接口模块 (DCAN1, DCAN2)

| 引脚     | 信号类型              | 缺省拉动状态 | 拉动类型 | 说明                      |

|--------|-------------------|--------|------|-------------------------|

| 信号名称   | <b>100<br/>PZ</b> |        |      |                         |

| CAN1RX | 63                | I/O    | 上拉   | CAN1 接收, 或通用 I/O (GPIO) |

| CAN1TX | 62                |        |      | CAN1 发送, 或 GPIO         |

| CAN2RX | 92                |        |      | CAN2 接收, 或 GPIO         |

| CAN2TX | 91                |        |      | CAN2 发送, 或 GPIO         |

### 3.2.5 多缓冲串行外设接口 (MibSPI1)

表 3-5. 多缓冲串行外设接口 (MibSPI1)

| 引脚                                       | 信号名称 | 100<br>PZ | 信号类型 | 缺省拉动<br>状态 | 拉动类型                                                                                                                                 | 说明                                                                                                                                   |

|------------------------------------------|------|-----------|------|------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| <b>MIBSPI1CLK</b>                        | 67   | I/O       | 上拉   | 可编程, 20uA  | MibSPI1 串行时钟, 或 GPIO<br>MibSPI1 芯片选择, 或 GPIO<br>MibSPI1 使能, 或 GPIO<br>MibSPI1 从器件-输入-主器件-输出, 或 GPIO<br>MibSPI1 从器件-输出-主器件-输入, 或 GPIO | MibSPI1 串行时钟, 或 GPIO<br>MibSPI1 芯片选择, 或 GPIO<br>MibSPI1 使能, 或 GPIO<br>MibSPI1 从器件-输入-主器件-输出, 或 GPIO<br>MibSPI1 从器件-输出-主器件-输入, 或 GPIO |

| <b>MIBSPI1nCS[0]</b>                     | 73   |           |      |            |                                                                                                                                      |                                                                                                                                      |

| <b>MIBSPI1nCS[1]/EQEPS/N2HET[17]</b>     | 93   |           |      |            |                                                                                                                                      |                                                                                                                                      |

| <b>MIBSPI1nCS[2]/N2HET[20]/N2HET[19]</b> | 27   |           |      |            |                                                                                                                                      |                                                                                                                                      |

| <b>MIBSPI1nCS[3]/N2HET[26]</b>           | 39   |           |      |            |                                                                                                                                      |                                                                                                                                      |

| <b>MIBSPI1nENA/N2HET[23]/N2HET[30]</b>   | 68   |           |      |            |                                                                                                                                      |                                                                                                                                      |

| <b>MIBSPI1SIMO</b>                       | 65   |           |      |            |                                                                                                                                      |                                                                                                                                      |

| <b>MIBSPI1SOMI</b>                       | 66   |           |      |            |                                                                                                                                      |                                                                                                                                      |

### 3.2.6 标准串行外设接口 (SPI2)

表 3-6. 标准串行外设接口 (SPI2)

| 引脚                                                                                                                                                                | 信号名称 | 100<br>PZ | 信号类型 | 缺省拉动<br>状态 | 拉动类型                                                                                                                  | 说明                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------|------|------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| <b>SPI2CLK</b>                                                                                                                                                    | 71   | I/O       | 上拉   | 可编程, 20uA  | SPI2 串行时钟, 或 GPIO<br>SPI2 芯片选择, 或 GPIO<br>SPI2 使能, 或 GPIO<br>SPI2 从器件-输入-主器件-输出, 或 GPIO<br>SPI2 从器件-输出-主器件-输入, 或 GPIO | SPI2 串行时钟, 或 GPIO<br>SPI2 芯片选择, 或 GPIO<br>SPI2 使能, 或 GPIO<br>SPI2 从器件-输入-主器件-输出, 或 GPIO<br>SPI2 从器件-输出-主器件-输入, 或 GPIO |

| <b>SPI2nCS[0]</b>                                                                                                                                                 | 23   |           |      |            |                                                                                                                       |                                                                                                                       |

| <b>GIOA[6]/SPI2nCS[1]/N2HET[31]</b>                                                                                                                               | 12   |           |      |            |                                                                                                                       |                                                                                                                       |

| <b>GIOA[4]/SPI2nCS[2]</b>                                                                                                                                         | 9    |           |      |            |                                                                                                                       |                                                                                                                       |

| <b>GIOA[3]/SPI2nCS[3]</b>                                                                                                                                         | 8    |           |      |            |                                                                                                                       |                                                                                                                       |

| <b>SPI2SIMO</b>                                                                                                                                                   | 70   |           |      |            |                                                                                                                       |                                                                                                                       |

| <b>SPI2SOMI</b>                                                                                                                                                   | 69   |           |      |            |                                                                                                                       |                                                                                                                       |

| 通过分别配置 SPI2 的 SPIPC9 寄存器的 SRS 位来独立地选择 SPI2CLK, SPI2SIMO 和 SPI2SOMI 的驱动强度。<br>8mA 驱动 (快速) 时, SRS=0。因为 SPIPC9 寄存器中 SRS 位缺省为 0, 所以该模式为缺省模式。<br>2mA 驱动 (慢速) 时, SRS=1。 |      |           |      |            |                                                                                                                       |                                                                                                                       |

| <b>SPI3CLK/EQEPA</b>                                                                                                                                              | 36   | I/O       | 上拉   | 可编程, 20uA  | SPI3 串行时钟, 或 GPIO<br>SPI3 芯片选择, 或 GPIO<br>SPI3 使能, 或 GPIO<br>SPI3 从器件-输入-主器件-输出, 或 GPIO<br>SPI3 从器件-输出-主器件-输入, 或 GPIO | SPI3 串行时钟, 或 GPIO<br>SPI3 芯片选择, 或 GPIO<br>SPI3 使能, 或 GPIO<br>SPI3 从器件-输入-主器件-输出, 或 GPIO<br>SPI3 从器件-输出-主器件-输入, 或 GPIO |

| <b>SPI3nCS[0]/EQEPI</b>                                                                                                                                           | 38   |           |      |            |                                                                                                                       |                                                                                                                       |

| <b>GIOA[2]/SPI3nCS[1]</b>                                                                                                                                         | 5    |           |      |            |                                                                                                                       |                                                                                                                       |

| <b>GIOA[1]/SPI3nCS[2]</b>                                                                                                                                         | 2    |           |      |            |                                                                                                                       |                                                                                                                       |

| <b>GIOA[0]/SPI3nCS[3]</b>                                                                                                                                         | 1    |           |      |            |                                                                                                                       |                                                                                                                       |

| <b>SPI3nENA/EQEPA</b>                                                                                                                                             | 37   |           |      |            |                                                                                                                       |                                                                                                                       |

| <b>SPI3SIMO</b>                                                                                                                                                   | 35   |           |      |            |                                                                                                                       |                                                                                                                       |

| <b>SPI3SOMI</b>                                                                                                                                                   | 34   |           |      |            |                                                                                                                       |                                                                                                                       |

### 3.2.7 本地互连网络控制器 (LIN)

表 3-7. 本地互连网络控制器 (LIN)

| 引脚           | 信号名称 | 100<br>PZ | 信号类型 | 缺省拉动<br>状态 | 拉动类型                             | 说明             |

|--------------|------|-----------|------|------------|----------------------------------|----------------|

| <b>LINRX</b> | 94   | I/O       | 上拉   | 可编程, 20uA  | LIN 接收, 或 GPIO<br>LIN 发送, 或 GPIO | LIN 接收, 或 GPIO |

| <b>LINTX</b> | 95   |           |      |            |                                  | LIN 发送, 或 GPIO |

### 3.2.8 多缓冲模数转换器 (MibADC)

表 3-8. 多缓冲模数转换器 (MibADC)

| 引脚                     | 信号名称              | 信号类型  | 缺省拉动状态 | 拉动类型      | 说明                   |

|------------------------|-------------------|-------|--------|-----------|----------------------|

|                        | <b>100<br/>PZ</b> |       |        |           |                      |

| <b>ADEVT/N2HET[28]</b> | 58                | I/O   | 上拉     | 可编程, 20uA | ADC 事件触发器或 GPIO      |

| <b>ADIN[0]</b>         | 42                | 输入    | -      | -         | 模拟输入                 |

| <b>ADIN[1]</b>         | 49                |       |        |           |                      |

| <b>ADIN[2]</b>         | 51                |       |        |           |                      |

| <b>ADIN[3]</b>         | 52                |       |        |           |                      |

| <b>ADIN[4]</b>         | 54                |       |        |           |                      |

| <b>ADIN[5]</b>         | 55                |       |        |           |                      |

| <b>ADIN[6]</b>         | 56                |       |        |           |                      |

| <b>ADIN[7]</b>         | 43                |       |        |           |                      |

| <b>ADIN[8]</b>         | 57                |       |        |           |                      |

| <b>ADIN[9]</b>         | 48                |       |        |           |                      |

| <b>ADIN[10]</b>        | 50                |       |        |           |                      |

| <b>ADIN[11]</b>        | 53                |       |        |           |                      |

| <b>ADIN[16]</b>        | 40                |       |        |           |                      |

| <b>ADIN[17]</b>        | 41                |       |        |           |                      |

| <b>ADIN[20]</b>        | 44                |       |        |           |                      |

| <b>ADIN[21]</b>        | 45                |       |        |           |                      |

| ADREFHI/VCCAD          | 46                | 输入/电源 | -      | -         | ADC 高基准电平 / ADC 运行电源 |

| ADREFLO/VSSAD          | 47                | 输入/接地 | -      | -         | ADC 低基准电平 / ADC 电源接地 |

### 3.2.9 系统模块

表 3-9. 系统模块

| 引脚                      | 信号名称              | 信号类型 | 缺省拉动状态 | 拉动类型      | 说明                                                                                      |

|-------------------------|-------------------|------|--------|-----------|-----------------------------------------------------------------------------------------|

|                         | <b>100<br/>PZ</b> |      |        |           |                                                                                         |

| <b>ECLK</b>             | 84                | I/O  | 下拉     | 可编程, 20uA | 外部预分频时钟输出, 或 GIO。                                                                       |

| <b>GIOA[5]/EXTCLKIN</b> | 10                | 输入   | 下拉     | 20uA      | 外部时钟输入                                                                                  |

| <b>nPORRST</b>          | 31                | 输入   | 下拉     | 100uA     | 加电复位, 冷复位外部电源监视器电路必须在任何微控制器电源下降到指定范围之外时将 nPORRST 驱动为低电平。该引脚有一个毛刺脉冲滤波器。                  |

| <b>nRST</b>             | 81                | I/O  | 上拉     | 100uA     | 外部电路必须通过将 nRST 驱动为低电平来将一个系统复位置为有效。为了确保外部复位不会随意产生, TI 建议将一个外部上拉电阻器连接到该引脚。这个引脚有一个毛刺脉冲滤波器。 |

### 3.2.10 错误信令模块 (ESM)

表 3-10. 错误信令模块 (ESM)

| 引脚            | 信号名称              | 信号类型 | 缺省拉动状态 | 拉动类型 | 说明                   |

|---------------|-------------------|------|--------|------|----------------------|

|               | <b>100<br/>PZ</b> |      |        |      |                      |

| <b>nERROR</b> | 82                | I/O  | 下拉     | 20uA | ESM 错误信号。指示严重程度高的错误。 |

### 3.2.11 主振荡器

表 3-11. 主振荡器

| 引脚                | 信号类型              | 缺省拉动状态 | 拉动类型 | 说明 |

|-------------------|-------------------|--------|------|----|

| 信号名称              | <b>100<br/>PZ</b> |        |      |    |

| <b>OSCIN</b>      | 14                | 输入     | -    | -  |

| <b>OSCOUT</b>     | 16                | 输出     | -    | -  |

| <b>KELVIN_GND</b> | 15                | 输入     | -    | -  |

### 3.2.12 测试/调试接口

表 3-12. 测试/调试接口

| 引脚           | 信号类型              | 缺省拉动状态 | 拉动类型 | 说明                                                                   |

|--------------|-------------------|--------|------|----------------------------------------------------------------------|

| 信号名称         | <b>100<br/>PZ</b> |        |      |                                                                      |

| <b>nTRST</b> | 76                | 输入     | 下拉   | 固定, 100uA                                                            |

| <b>RTCK</b>  | 80                | 输出     | -    | -                                                                    |

| <b>TCK</b>   | 79                | 输入     | 下拉   | 固定, 100uA                                                            |

| <b>TDI</b>   | 77                | I/O    | 上拉   | 固定, 100uA                                                            |

| <b>TDO</b>   | 78                | I/O    | 下拉   | 固定, 100uA                                                            |

| <b>TMS</b>   | 75                | I/O    | 上拉   | 固定, 100uA                                                            |

| <b>TEST</b>  | 24                | I/O    | 下拉   | 固定, 100uA<br>测试使能。仅供内部使用。这个引脚有一个毛刺脉冲滤波器。<br>为了正确运行, 此引脚必须通过一个外部电阻接地。 |

### 3.2.13 闪存

表 3-13. 闪存

| 引脚           | 信号类型              | 缺省拉动状态  | 拉动类型 | 说明 |

|--------------|-------------------|---------|------|----|

| 信号名称         | <b>100<br/>PZ</b> |         |      |    |

| <b>FLTP1</b> | 3                 | 输入      | -    | -  |

| <b>FLTP2</b> | 4                 | 输入      | -    | -  |

| <b>VCCP</b>  | 96                | 3.3V 电源 | -    | -  |

闪存测试引脚。为了正确运行, 该引脚必须只连接至一个测试焊盘或者根本就不相连 [无连接 (NC)]。

在有可能受到 ESD 事件影响的最终产品中, 测试焊盘一定不能暴露在外。

闪存外部泵电压 (3.3V) 闪存读取和闪存编程和擦除操作中都需要用到该引脚。

### 3.2.14 内核电源

表 3-14. 内核电源

| 引脚  | 信号名称 | 100<br>PZ | 信号类型    | 缺省拉动<br>状态 | 拉动类型 | 说明           |

|-----|------|-----------|---------|------------|------|--------------|

| VCC |      | 13        | 1.2V 电源 | -          | -    | 数字逻辑和 RAM 电源 |

| VCC |      | 21        |         |            |      |              |

| VCC |      | 30        |         |            |      |              |

| VCC |      | 32        |         |            |      |              |

| VCC |      | 61        |         |            |      |              |

| VCC |      | 88        |         |            |      |              |

| VCC |      | 99        |         |            |      |              |

### 3.2.15 I/O 电源

表 3-15. I/O 电源

| 引脚    | 信号名称 | 100<br>PZ | 信号类型    | 缺省拉动<br>状态 | 拉动类型 | 说明     |

|-------|------|-----------|---------|------------|------|--------|

| VCCIO |      | 6         | 3.3V 电源 | -          | -    | I/O 电源 |

| VCCIO |      | 28        |         |            |      |        |

| VCCIO |      | 60        |         |            |      |        |

| VCCIO |      | 85        |         |            |      |        |

### 3.2.16 内核和 I/O 电源接地基准

表 3-16. 内核和 I/O 电源接地基准

| 引脚  | 信号名称 | 100<br>PZ | 信号类型 | 缺省拉动<br>状态 | 拉动类型 | 说明                              |

|-----|------|-----------|------|------------|------|---------------------------------|

| VSS |      | 7         | 接地   | -          | -    | 器件接地基准 这是除 ADC 电源外所有电源的一个单接地基准。 |

| VSS |      | 17        |      |            |      |                                 |

| VSS |      | 20        |      |            |      |                                 |

| VSS |      | 29        |      |            |      |                                 |

| VSS |      | 33        |      |            |      |                                 |

| VSS |      | 59        |      |            |      |                                 |

| VSS |      | 72        |      |            |      |                                 |

| VSS |      | 86        |      |            |      |                                 |

| VSS |      | 87        |      |            |      |                                 |

| VSS |      | 100       |      |            |      |                                 |

### 3.3 输出复用和控制

输出复用将被用于器件中。使用复用是为了允许附加程序包/功能组合的开发，同时也是为了保持引脚分配与市场上器件系列的兼容性。

在所有被指定为多路复用的情况下，输出缓冲器均是复用的。

**表 3-17. 输出多路复用器选项**

| 100 PZ 引脚 | 缺省功能          | 控制 1        | 选项 2       | 控制 2        | 选项 3      | 控制 3        |

|-----------|---------------|-------------|------------|-------------|-----------|-------------|

| 1         | GIOA[0]       | PINMMR0[8]  | SPI3nCS[3] | PINMMR0[9]  | -         | -           |

| 2         | GIOA[1]       | PINMMR1[0]  | SPI3nCS[2] | PINMMR1[1]  | -         | -           |

| 5         | GIOA[2]       | PINMMR1[8]  | SPI3nCS[1] | PINMMR1[9]  | -         | -           |

| 8         | GIOA[3]       | PINMMR1[16] | SPI2nCS[3] | PINMMR1[17] | -         | -           |

| 9         | GIOA[4]       | PINMMR1[24] | SPI2nCS[2] | PINMMR1[25] | -         | -           |

| 10        | GIOA[5]       | PINMMR2[0]  | EXTCLKIN   | PINMMR2[1]  | -         | -           |

| 12        | GIOA[6]       | PINMMR2[8]  | SPI2nCS[1] | PINMMR2[9]  | N2HET[31] | PINMMR2[10] |

| 18        | GIOA[7]       | PINMMR2[16] | N2HET[29]  | PINMMR2[17] | -         | -           |

| 93        | MIBSPI1nCS[1] | PINMMR6[8]  | EQEPS      | PINMMR6[9]  | N2HET[17] | PINMMR6[10] |

| 27        | MIBSPI1nCS[2] | PINMMR3[0]  | N2HET[20]  | PINMMR3[1]  | N2HET[19] | PINMMR3[2]  |

| 39        | MIBSPI1nCS[3] | PINMMR4[8]  | N2HET[26]  | PINMMR4[9]  | -         | -           |

| 68        | MIBSPI1nENA   | PINMMR5[8]  | N2HET[23]  | PINMMR5[9]  | N2HET[30] | PINMMR5[10] |

| 36        | SPI3CLK       | PINMMR3[16] | EQEPA      | PINMMR3[17] | -         | -           |

| 38        | SPI3nCS[0]    | PINMMR4[0]  | EQEPI      | PINMMR4[1]  | -         | -           |

| 37        | SPI3nENA      | PINMMR3[24] | EQEPB      | PINMMR3[25] | -         | -           |

| 58        | ADEVT         | PINMMR4[16] | N2HET[28]  | PINMMR4[17] | -         | -           |

#### 3.3.1 输出多路复用的注意事项

表 3-17 显示了为每个引脚选择所需功能性的输出信号的复用和控制信号。

- 该信号的默认引脚由表 3-17 中的“默认功能”栏来定义。

- “CTRL x”栏表示多路复用的控制寄存器并且该位必须被置位，以此来选择任何特定引脚上输出的相应功能。

例如，说到引脚 18 的复用，如下所示。

**表 3-18. 多路复用实例**

| 100 PZ 引脚 | 缺省功能    | 控制 1        | 选项 2      | 控制 2        | 选项 3 | 控制 3 |

|-----------|---------|-------------|-----------|-------------|------|------|

| 18        | GIOA[7] | PINMMR2[16] | N2HET[29] | PINMMR2[17] | -    | -    |

- 在 GIO 模块控制寄存器中，如果 GIOA[7] 被配置为一个输出引脚，那么可编程的引脚电平将缺省显示在引脚 18 上。PINMMR2[16] 位被默认置位，以此来表示 GIOA[7] 信号被选择为输出。

- 如果应用需要在引脚 18 上输出 N2HET[29] 信号，则必须清除 PINMMR2[16] 并且置位 PINMMR2[17]。

- 注意：该引脚作为输出引脚被连接至 GIO 和 N2HET 两种模块。也就是说，在这类引脚上没有输入复用。

#### 3.3.2 多路复用控制寄存器的通用规则

- PINMMR 控制寄存器只能在特权模式下才可以被写入。在非特权模式下的写入将会产生一个错误响应。

- 如果该应用向任一个 PINMMR 控制寄存器中写入全 0，那么将为受影响的引脚选择缺省功能。

- 一个 PINMMR 控制寄存器中的每个字节都被用于为一个给定的引脚选择功能性。对于任意引脚来说，如果应用在一个字节内置位了多个位，那么将为该引脚选择缺省功能。

- PINMMR 控制寄存器内的一些位可以与那些 100 引脚封装所不具有的内部焊盘相关联。因此，被标记为保存的位不应该作为一个 1 被写入。

### 3.4 特定复用选项

执行特别控制来影响这个微控制器上的特定功能。在这节中将对这些控制进行描述。

### 3.4.1 eQEP 输入过滤

#### 3.4.1.1 eQEPA 输入

- 当 PINMMR8[0]=1 时, 使用 VCLK 来使 eQEPA 输入双同步。

- 当 PINMMR8[0]=0 并且 PINMMR8[1]=1 时, 通过使用 VCLK, eQEPA 输入被双同步, 然后由一个固定的 6 位奇数器进行限定。

- PINMMR8[0]=0 并且 PINMMR8[1]=0 是一个非法组合而且运行方式缺省为 PINMMR8[0]=1。

#### 3.4.1.2 eQEPB 输入

- 当 PINMMR8[8]=1 时, 使用 VCLK 来使 eQEPB 输入双同步。

- 当 PINMMR8[8]=0 并且 PINMMR8[9]=1 时, 通过使用 VCLK, eQEPB 输入被双同步, 然后由一个固定的 6 位奇数器进行限定。

- PINMMR8[8]=0 并且 PINMMR8[9]=0 是一个非法组合而且运行方式缺省为 PINMMR8[8]=1。

#### 3.4.1.3 eQEPI 输入

- 当 PINMMR8[16]=1 时, 使用 VCLK 来使 eQEPI 输入双同步。

- 当 PINMMR8[16]=0 并且 PINMMR8[17]=1 时, 通过使用 VCLK, eQEPI 输入被双同步, 然后由一个固定的 6 位奇数器进行限定。

- PINMMR8[16]=0 并且 PINMMR8[17]=0 是一个非法组合而且运行方式缺省为 PINMMR8[16]=1。

#### 3.4.1.4 eQEPS 输入

- 当 PINMMR8[24]=1 时, 使用 VCLK 来使 eQEPS 输入双同步。

- 当 PINMMR8[24]=0 并且 PINMMR8[25]=1 时, 通过使用 VCLK, eQEPS 输入被双同步, 然后由一个固定的 6 位奇数器进行限定。

- PINMMR8[24]=0 并且 PINMMR8[25]=0 是一个非法组合而且运行方式缺省为 PINMMR8[24]=1。

### 3.4.2 N2HET PIN\_nDISABLE 输入端口

- 当 PINMMR9[0]=1 时, GIOA[5] 被直接接至 N2HET 模块的 N2HET PIN\_nDISABLE 输入。

- 当 PINMMR9[0]=0 并且 PINMMR9[1]=1 时, EQEPERR 在直接接至 N2HET 模块的 N2HET PIN\_nDISABLE 输入前使用 VCLK 将其反相并双同步。

- PINMMR9[0]=0 并且 PINMMR9[1]=0 是一个非法的组合而且运行方式缺省为 PINMMR9[0]=1。

## 4 规范

### 4.1 自然通风运行温度范围内的最大绝对值, <sup>(1)</sup>

|                     |                                                                                | 最小值  | 最大值  | 单位 |

|---------------------|--------------------------------------------------------------------------------|------|------|----|

| 电源电压范围:             | $V_{CC}^{(2)}$                                                                 | -0.3 | 1.43 | V  |

|                     | $V_{CCIO}, V_{CCP}^{(2)}$                                                      | -0.3 | 4.6  | V  |

|                     | $V_{CCAD}$                                                                     | -0.3 | 3.6  | V  |

| 输入电压范围:             | 所有的输入引脚                                                                        | -0.3 | 4.6  | V  |

|                     | ADC 输入引脚                                                                       | -0.3 | 4.6  | V  |

| 输入钳位电流:             | $I_{IK}(V_I < 0 \text{ 或 } V_I > V_{CCIO})$<br>所有引脚, 除了 ADIN[21:20,17:16,11:0] | -20  | +20  | mA |

|                     | $I_{IK}(V_I < 0 \text{ 或 } V_I > V_{CCAD})$<br>ADIN[21:20,17:16,11:0]          | -10  | +10  | mA |

|                     | 总计                                                                             | -40  | +40  | mA |

| 自然通风运行温度范围, $T_A$ : |                                                                                | -40  | 105  | °C |

| 运行结温范围, $T_J$ :     |                                                                                | -40  | 130  | °C |

| 锁断性能:               | 测试, 所有 I/O 引脚                                                                  | -100 | +100 | mA |

- (1) 超出“最大绝对额定值”下列出的值的应力可能会对器件造成永久损坏。这些仅为在应力额定值下的工作情况, 对于额定值下的器件的功能性操作或者在超出“推荐的操作条件”下的任何其它情况, 在此并未说明。长时间运行在最大绝对额定条件下会影响设备的可靠性。

(2) 长时间在最大额定值条件下运行有可能会影响器件可靠性。所有电压值均是相对于和它们相连的地线。

### 4.2 处理额定值

|           |                |                                                                                                    | 最小值 | 最大值 | 单位 |

|-----------|----------------|----------------------------------------------------------------------------------------------------|-----|-----|----|

| $T_{stg}$ | 储存温度范围         |                                                                                                    | -65 | 150 | °C |

| $V_{ESD}$ | 静电放电 (ESD) 性能: | 人体模型 (HBM), 符合 ANSI/ESDA/JEDEC JS001 <sup>(1)</sup><br>充电器件模型 (CDM), 符合 JESD22-C101 <sup>(2)</sup> | -2  | 2   | kV |

- (1) JEDEC 文档 JEP155 规定: 500V HBM 允许在标准 ESD 控制流程下安全生产。

(2) JEDEC 文档 JEP157 规定: 250V CDM 允许在标准 ESD 控制流程下安全生产。

### 4.3 上电小时数 (POH)

为方便起见, 本节单独提供, 并且未扩展或修改适用于 TI 半导体产品的 TI 标准条款和条件下提供的保修范围。中所示的值。

POH 是电压、温度和时间的函数。如果在较高电压和温度下使用, 实现相同可靠性性能的 POH 会减少。

可靠性数据基于与 100000 上电小时 (结温温度 105°C) 等效的温度系统配置。

#### 4.4 建议的运行条件<sup>(1)</sup>

|                        |                                                  | 最小值  | 标称值 | 最大值          | 单位         |

|------------------------|--------------------------------------------------|------|-----|--------------|------------|

| $V_{CC}$               | 数字逻辑电源电压 (内核)                                    | 1.14 | 1.2 | 1.32         | V          |

| $V_{CCIO}$             | 数字逻辑电源电压 (I/O)                                   | 3    | 3.3 | 3.6          | V          |

| $V_{CCAD}/V_{ADREFHI}$ | MibADC 电源电压/模数转换高电压基准源                           | 3    | 3.3 | 3.6          | V          |

| $V_{CCP}$              | 闪存泵电源电压                                          | 3    | 3.3 | 3.6          | V          |

| $V_{SS}$               | 数字逻辑电源接地                                         |      | 0   |              | V          |

| $V_{SSAD}/V_{ADREFLO}$ | MibADC 电源接地/模数转换低电压基准源                           | -0.1 | 0.1 |              | V          |

| $V_{SLEW}$             | 针对 $V_{CCIO}$ , $V_{CCAD}$ 和 $V_{CCP}$ 电源的最大正转换率 |      | 1   |              | V/ $\mu$ s |

| $T_A$                  | 自然通风工作温度范围                                       | -40  | 105 | $^{\circ}$ C |            |

| $T_J$                  | 工作结温 <sup>(2)</sup>                              | -40  | 130 | $^{\circ}$ C |            |

(1) 所有的电压都以  $V_{SS}$  为基准, 除了  $V_{CCAD}$  以  $V_{SSAD}$  为基准

(2) 可靠性数据基于与 100000 小时加电小时 (结温温度 105 $^{\circ}$ C) 等效的温度系统配置

#### 4.5 建议时钟域运行条件下的开关特性

表 4-1. 时钟域时序规范

| 参数           |                                                    | 条件 | 最小值 | 最大值        | 单位  |

|--------------|----------------------------------------------------|----|-----|------------|-----|

| $f_{HCLK}$   | HCLK - 系统时钟频率                                      |    |     | 80         | MHz |

| $f_{GCLK}$   | GCLK - CPU 时钟频率 (比率 $f_{GCLK}$<br>$f_{HCLK}=1:1$ ) |    |     | $f_{HCLK}$ | MHz |

| $f_{VCLK}$   | VCLK - 初级外设时钟频率                                    |    |     | 80         | MHz |

| $f_{VCLK2}$  | VCLK2 - 次级外设时钟频率                                   |    |     | 80         | MHz |

| $f_{VCLKA1}$ | VCLKA1 - 初级异步外设时钟频率                                |    |     | 80         | MHz |

| $f_{RTICLK}$ | RTICLK - 时钟频率                                      |    |     | $f_{VCLK}$ | MHz |

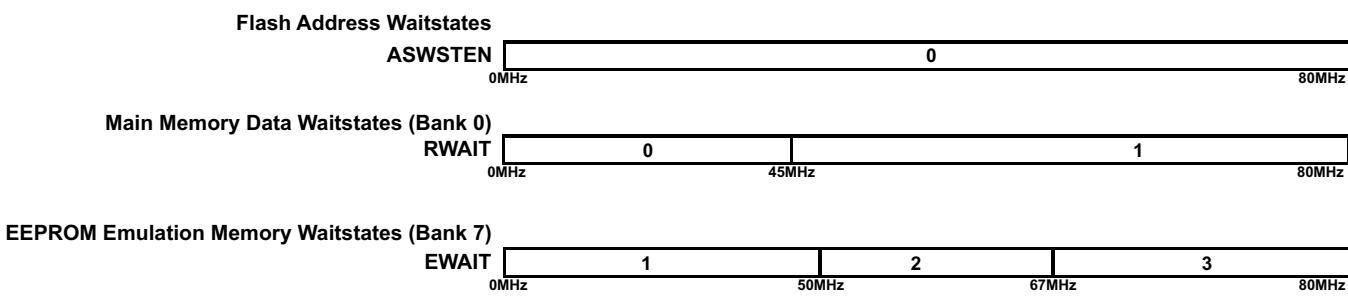

## 4.6 要求等待状态

TCM RAM 可支持 CPU 全速编程和取数据，而无需任何地址或数据等待状态。没有需要为 RAM 等待状态编程的寄存器。

TCM 闪存可支持零地址和非管道模式中高达 45MHz CPU 速度的数据等待状态。在无地址等待状态和数据等待状态下，在管道模式中，该闪存支持 80MHz 的最大 CPU 时钟速率。

正确的等待状态应在寄存器字段地址设置等待状态使能 (ASWSTEN 0xFFFF87000[4])、随机等待状态 (RWAIT 0xFFFF87000[11:8]) 和仿真等待状态 (EWAIT 0xFFFF872B8[19:16]) 中设置，如下面的图 4-1 所示。

图 4-1. 等待状态机制

闪存包装程序默认为非管道模式，其中禁用地址等待状态，ASWSTEN=0；主内存随机读取数据等待状态，RWAIT=1；仿真内存随机读取等待状态，EWAIT=1。

#### 4.7 推荐运行条件内的功耗

| 参数                            |                            | 测试条件                           | 最小值 | 典型值 | 最大值                   | 单位 |

|-------------------------------|----------------------------|--------------------------------|-----|-----|-----------------------|----|

| $I_{CC}$                      | $V_{CC}$ 数字电源电流 (工作模式)     | $f_{HCLK} = 80MHz$             |     |     | 135 <sup>(1)</sup>    | mA |

|                               | $V_{CC}$ 数字电源电流 (LBIST 模式) | LBIST 时钟速率 = 45MHz             |     |     | 145 <sup>(2)(3)</sup> | mA |

|                               | $V_{CC}$ 数字电源电流 (PBIST 模式) | PBIST ROM 时钟频率 = 80MHz         |     |     | 135 <sup>(2)(3)</sup> | mA |

| $I_{CCREFH}$                  | $AD_{REFH}$ 电源电流 (运行模式)    | $AD_{REFH}max$                 |     |     | 3                     | mA |

| $I_{CCAD}$                    | $V_{CCAD}$ 电源电流 (工作模式)     | $V_{CCAD}max$                  |     |     | 45 <sup>(4)</sup>     | mA |

| $I_{CCIO}$                    | $V_{CCIO}$ 数字电源电流 (工作模式)。  | 无直流负载, $V_{CCmax}$             |     |     |                       |    |

| $I_{CCP}$                     | $V_{CCP}$ 泵电源电流            | 读取模式                           |     |     |                       |    |

| $I_{CCP}, I_{CCIO}, I_{CCAD}$ | 3.3V 电源电流                  | 从一组中读取并编程或擦除另外一组, $V_{CCP}max$ |     |     | 65 <sup>(4)</sup>     | mA |

(1) 可降低最大  $I_{CC}$  值

- 随电压线性变化

- 对于较低工作频率, 在  $f_{HCLK} = f_{VCLK}$  时, 减小比率为 0.76 mA/MHz

- 对于较低结温温度, 减小比率由以下等式给出, 其中,  $T_{JK}$  是单位为开 (Kelvin) 的结温温度, 结果的单位为毫安培。

$$60 - 0.001 e^{0.026 T_{JK}}$$

(2) 可降低最大  $I_{CC}$  值

- 随电压线性变化

- 对于较低结温温度, 减小比率由以下等式给出, 其中,  $T_{JK}$  是单位为开 (Kelvin) 的结温温度, 结果的单位为毫安培。

$$60 - 0.001 e^{0.026 T_{JK}}$$

(3) LBIST 和 PBIST 电流持续时间短, 通常少于 10ms。通常在器件和稳压器的热计算中将它们忽略

(4) 三个组合电源的最大电流要求

## 4.8 PZ 的热阻特性

表 4-2 给出了 PQFP-PZ 机械封装的热敏电阻特性。

**表 4-2. 热敏电阻特性

(S-PQFP 封装) [PZ]**

| 参数              | °C/W |

|-----------------|------|

| $R_{\theta JA}$ | 48   |

| $R_{\theta JC}$ | 5    |

## 4.9 推荐运行条件下的<sup>(1)</sup>输入/输出电气特性

| 参数        |                 | 测试条件                                               | 最小值              | 典型值  | 最大值              | 单位      |

|-----------|-----------------|----------------------------------------------------|------------------|------|------------------|---------|

| $V_{hys}$ | 输入滞后            | 所有输入                                               |                  | 180  |                  | mV      |

| $V_{IL}$  | 低电平输入电压         | 所有输入 <sup>(2)</sup>                                |                  | -0.3 | 0.8              | V       |

| $V_{IH}$  | 高电平输入电压         | 所有输入 <sup>(2)</sup>                                |                  | 2    | $V_{CCIO} + 0.3$ | V       |

| $V_{OL}$  | 低电平输出电压         | $I_{OL} = I_{OLmax}$                               |                  |      | 0.2 $V_{CCIO}$   | V       |

|           |                 | $I_{OL} = 50\mu A$ , 标准输出模式                        |                  |      | 0.2              |         |

| $V_{OH}$  | 高电平输出电压         | $I_{OH} = I_{OHmax}$                               | 0.8 $V_{CCIO}$   |      |                  | V       |

|           |                 | $I_{OH} = 50\mu A$ , 标准输出模式                        | $V_{CCIO} - 0.3$ |      |                  |         |

| $I_{IC}$  | 输入钳位电流 (I/O 引脚) | $V_I < V_{SSIO} - 0.3$ 或<br>$V_I > V_{CCIO} + 0.3$ | -3.5             |      | 3.5              | mA      |

| $I_I$     | 输入电流 (I/O 引脚)   | $I_{IH}$ 下拉 $20\mu A$                              | $V_I = V_{CCIO}$ | 5    | 40               | $\mu A$ |

|           |                 | $I_{IH}$ 下拉 $100\mu A$                             | $V_I = V_{CCIO}$ | 40   | 195              |         |

|           |                 | $I_{IL}$ 上拉 $20\mu A$                              | $V_I = V_{SS}$   | -40  | -5               |         |

|           |                 | $I_{IL}$ 上拉 $100\mu A$                             | $V_I = V_{SS}$   | -195 | -40              |         |

|           |                 | 所有其他引脚                                             | 无上拉或下拉           | -1   | 1                |         |

| $C_I$     | 输入电容            |                                                    |                  |      | 2                | pF      |

| $C_O$     | 输出电容            |                                                    |                  |      | 3                | pF      |

(1) 源电流 (器件输出) 为负, 而灌电流 (器件输入) 为正。

(2) 这并不适用于 nPORRST 引脚。

## 4.10 输出缓冲器驱动强度

表 4-3. 输出缓冲器驱动强度

| 低电平输出电流,<br>$I_{OL}$ , 此时 $V_I = V_{OLmax}$<br>或<br>高电平输出电流,<br>$I_{OH}$ , 此时 $V_I = V_{OHmin}$ | 信号                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8mA                                                                                             | EQEPI, EQEPS,<br>TMS, TDI, TDO, RTCK,<br>nERROR                                                                                                                                                                                                                                      |

| 4mA                                                                                             | TEST,<br>MIBSPI1SIMO, MIBSPI1SOMI, MIBSPI1CLK, SPI3CLK, SPI3SIMO, SPI3SOMI,<br>nRST                                                                                                                                                                                                  |

| 2mA 零主导                                                                                         | AD1EVT,<br>CAN1RX, CAN1TX, CAN2RX, CAN2TX,<br>GIOA[0-7],<br>LINRX, LINTX,<br>MIBSPI1NCS[0-3], MIBSPI1NENA<br>N2HET[0], N2HET[2], N2HET[4], N2HET[6], N2HET[8], N2HET[10], N2HET[12], N2HET[14], N2HET[16], N2HET[18], N2HET[22], N2HET[24],<br>SPI2NCS[0-3], SPI3NENA,<br>SPI3NCS[0] |

| 可选 8mA/2mA                                                                                      | ECLK,<br>SPI2CLK, SPI2SIMO, SPI2SOMI<br>输出缓冲器对于这些信号的缺省驱动强度为 8mA。                                                                                                                                                                                                                     |

表 4-4. 可选 8mA/2mA 控制

| 信号       | 控制位                        | 地址          | 8mA | 2mA |

|----------|----------------------------|-------------|-----|-----|

| ECLK     | SYSPC10[0]                 | 0xFFFF FF78 | 0   | 1   |

| SPI2CLK  | SPI2PC9[9] <sup>(1)</sup>  | 0xFFFF F668 | 0   | 1   |

| SPI2SIMO | SPI2PC9[10] <sup>(1)</sup> | 0xFFFF F668 | 0   | 1   |

| SPI2SOMI | SPI2PC9[11] <sup>(1)</sup> | 0xFFFF F668 | 0   | 1   |

(1) 不要对 SPI2PC9[31..16] 进行字节或半字写入操作, 这是因为这样会不小心改变 SPI2 引脚的驱动强度

## 4.11 输入时序

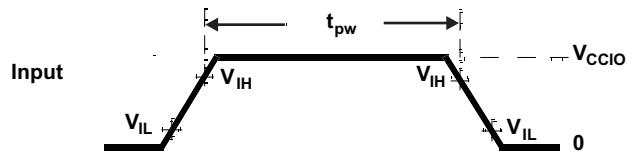

图 4-2. TTL - 电平输入

表 4-5. 对于输入的时序要求<sup>(1)</sup>

|          |          | 最小值                       | 最大值 | 单位 |

|----------|----------|---------------------------|-----|----|

| $t_{pw}$ | 输入最小脉冲宽度 | $t_c(V_{CLK}) + 10^{(2)}$ |     | ns |

(1)  $t_c(V_{CLK})$  = 外设 VBUS 时钟周期时间 =  $1/f_{(VCLK)}$

(2) 上面显示的时序仅对在 GIO 模式中使用的引脚有效。

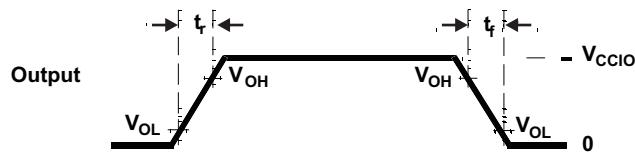

## 4.12 输出时序

表 4-6. 输出时序与负载电容 (CL) 间关系的开关特性

| 参数          |                  | 最小值        | 最大值  | 单位 |  |

|-------------|------------------|------------|------|----|--|

| 上升时间, $t_r$ | 8mA 引脚           | CL=15pF    | 2.5  | ns |  |

|             |                  | CL = 50pF  | 4    |    |  |

|             |                  | CL = 100pF | 7.2  |    |  |

|             |                  | CL = 150pF | 12.5 |    |  |

| 下降时间, $t_f$ |                  | CL = 15pF  | 2.5  | ns |  |

|             |                  | CL = 50pF  | 4    |    |  |

|             |                  | CL = 100pF | 7.2  |    |  |

|             |                  | CL = 150pF | 12.5 |    |  |

| 上升时间, $t_r$ | 4mA 引脚           | CL=15pF    | 5.6  | ns |  |

|             |                  | CL = 50pF  | 10.4 |    |  |

|             |                  | CL = 100pF | 16.8 |    |  |

|             |                  | CL = 150pF | 23.2 |    |  |

| 下降时间, $t_f$ |                  | CL = 15pF  | 5.6  | ns |  |

|             |                  | CL = 50pF  | 10.4 |    |  |

|             |                  | CL = 100pF | 16.8 |    |  |

|             |                  | CL = 150pF | 23.2 |    |  |

| 上升时间, $t_r$ | 2mA-z 引脚         | CL=15pF    | 8    | ns |  |

|             |                  | CL = 50pF  | 15   |    |  |

|             |                  | CL = 100pF | 23   |    |  |

|             |                  | CL = 150pF | 33   |    |  |

| 下降时间, $t_f$ |                  | CL = 15pF  | 8    | ns |  |

|             |                  | CL = 50pF  | 15   |    |  |

|             |                  | CL = 100pF | 23   |    |  |

|             |                  | CL = 150pF | 33   |    |  |

| 上升时间, $t_r$ | 可选的 8mA/2mA-z 引脚 | CL = 15pF  | 2.5  | ns |  |

|             |                  | CL = 50pF  | 4    |    |  |

|             |                  | CL = 100pF | 7.2  |    |  |

|             |                  | CL = 150pF | 12.5 |    |  |

| 下降时间, $t_f$ |                  | CL = 15pF  | 2.5  | ns |  |

|             |                  | CL = 50pF  | 4    |    |  |

|             |                  | CL = 100pF | 7.2  |    |  |

|             |                  | CL = 150pF | 12.5 |    |  |

| 上升时间, $t_r$ |                  | CL=15pF    | 8    | ns |  |

|             |                  | CL = 50pF  | 15   |    |  |

|             |                  | CL = 100pF | 23   |    |  |

|             |                  | CL = 150pF | 33   |    |  |

| 下降时间, $t_f$ |                  | CL = 15pF  | 8    | ns |  |

|             |                  | CL = 50pF  | 15   |    |  |

|             |                  | CL = 100pF | 23   |    |  |

|             |                  | CL = 150pF | 33   |    |  |

图 4-3. CMOS 电平输出

表 4-7. 对于输入的时序要求<sup>(1)</sup>

| 参数           | 最小值                                                              | 最大值 | 单位   |

|--------------|------------------------------------------------------------------|-----|------|

| $t_d$ (并行输出) | 通用输出信号从低到高或从高到低转换间的延迟可由一个应用并行配置, 例如 GIOA 端口中的所有信号, 或所有 N2HET 信号。 |     | 5 ns |

(1) 这个技术规格并未将任何输出缓冲器驱动强度差异或者任何外部电容负载差异计算在内。检查表 4-3 每个信号上的输出缓冲器驱动强度信息。

## 5 系统信息和电气技术规范

### 5.1 电压监视器特性

在这个器件上执行一个电压监视器。这个电压监视器的目的是，当给内核电源和 I/O 电源电压上电时，消除对一个特定序列的要求。

#### 5.1.1 重要考虑

- 当电源电压在范围之外时，电压监视器仍然需要一个电压监控器来保证器件被保留在复位状态。

- 电压监视器只监视内核电源 (VCC) 和 I/O 电源 (VCCIO)。其它电源不受 VMON 监视。例如，如果 VCCAD 或 VCCP 由一个 VCCIO 以外的电源供电，那么就没有针对 VCCAD 和 VCCP 电源的内部电压监视器。

#### 5.1.2 电压监视器运行

电压监视器在器件上生成电源正常微控制器 (MCU) 信号 (PGMCU) 以及 I/O 电源正常 IO 信号 (PGIO)。在加电或断电期间，当内核或者 I/O 电源低于额定最小监视阈值的时候，PGMCU 和 PGIO 被驱动为低电平。PGIO 和 PGMCU 成为低电平，在电源加电或者断电期间，隔离内核逻辑以及 I/O 控制。这样可以使得内核和 I/O 电源能够以任一顺序加电或断电。

当电压监视器在 I/O 电源上检测到一个低电压时，它将一个加电复位位置为有效。当电压监视器在内核电源上检测到一个范围以外的电压时，它以异步方式使所有输出引脚高阻抗，并将一个加电复位位置为有效。当器件进入一个低功耗模式时，电压监视器被禁用。

VMON 还包含一个针对 nPORRST 输入的毛刺脉冲滤波器。有关这个毛刺脉冲滤波器的时序信息请参考节 [5.2.3.1](#)。

表 5-1. 电压监视技术规格

| 参数   |        | 最小值                                  | 典型值  | 最大值 | 单位   |

|------|--------|--------------------------------------|------|-----|------|

| VMON | 电压监视阀值 | VCC 低电平-低于这个阀值的 VCC 电平会由于过低而被删除。     | 0.75 | 0.9 | 1.13 |

|      |        | VCC 高电平-高于这个阀值的 VCC 电平会由于过高而被删除。     | 1.40 | 1.7 | 2.1  |

|      |        | VCCIO 低电平-低于这个阀值的 VCCIO 电平会由于过低而被删除。 | 1.85 | 2.4 | 2.9  |

#### 5.1.3 电源过滤

VMON 具有过滤 VCC 和 VCCIO 电源上毛刺脉冲的功能。

下面的表格显示了电源滤波的特性。电源中大于最大技术参数的毛刺脉冲不能被滤除。

表 5-2. VMON 电源毛刺脉冲滤波功能

| 参数                   | 最小值   | 最大值 |

|----------------------|-------|-----|

| VCC 上可以被滤除的毛刺脉冲的宽度   | 250ns | 1us |

| VCCIO 上可以被滤除的毛刺脉冲的宽度 | 250ns | 1us |

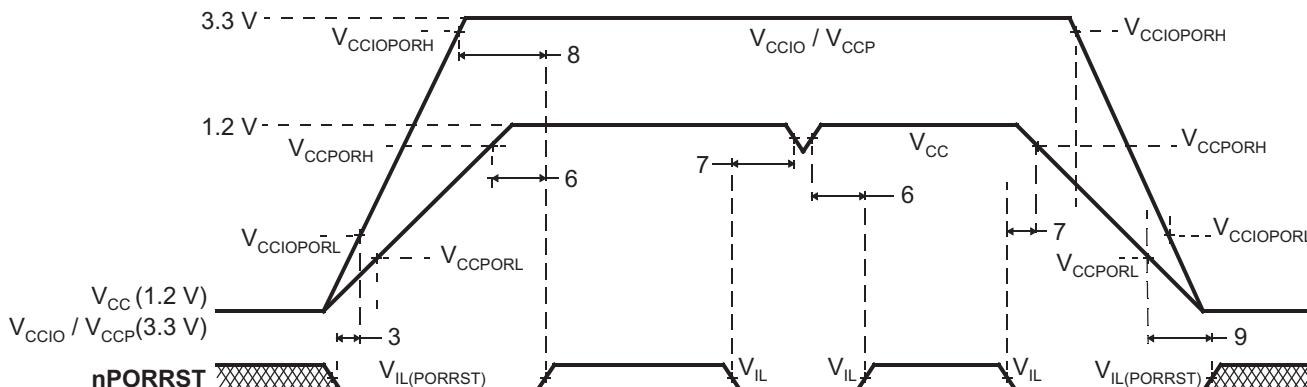

## 5.2 电源排序和加电复位

### 5.2.1 加电顺序

VCCIO 的斜升和 VCC 电源间没有时序关系。加电序列随着 I/O 电压上升到高于最小 I/O 电源阈值, (详细信息请见表 5-4), 内核电压上升到高于最小内核电源阈值和加电复位的释放开始。高频振荡器将首先启动并且其振幅将上升到一个可接受的水平。振荡器启动时间取决于振荡器的类型并且由振荡器销售商提供。到器件的不同电源可以以任何顺序加电。

加电期间, 此器件经过下列顺序阶段。

表 5-3. 加电阶段

|             |                    |

|-------------|--------------------|

| 振荡器启动和有效性检查 | 1032 个振荡器周期        |

| 熔丝自动载入      | 1160 个振荡器周期        |

| 闪存泵加电       | 688 个振荡器周期         |

| 闪存组加电       | 617 个振荡器周期         |

| 总计          | <b>3497 个振荡器周期</b> |

在上述序列的末尾 CPU 复位被释放并且从地址 0x00000000 中取出第一条指令。

## 5.2.2 断电序列

到器件的不同电源可以以任一顺序断电。

## 5.2.3 加电复位: *nPORRST*

只要 I/O 或内核电源在推荐范围之外, 这个复位就必须由一个外部电路置为有效。这个信号的上面有一个毛刺脉冲滤波器。它还有一个内部下拉电阻器。

### 5.2.3.1 *nPORRST* 电气和时序要求

表 5-4. *nPORRST* 的电气要求

| 编号 | 参数                                                                                          | 最小值  | 最大值              | 单位 |

|----|---------------------------------------------------------------------------------------------|------|------------------|----|

|    | $V_{CCPORL}$ 当 <i>nPORRST</i> 在加电期间必须有效时, $V_{CC}$ 的低电源电平                                   |      | 0.5              | V  |

|    | $V_{CCPORH}$ 当 <i>nPORRST</i> 在加电期间必须保持有效并在断电期间变为有效时, $V_{CC}$ 的高电源电平                       | 1.14 |                  | V  |

|    | $V_{CCIOPORL}$ 当 <i>nPORRST</i> 在加电期间必须有效时, $V_{CCIO}/V_{CCP}$ 的低电源电平                       |      | 1.1              | V  |

|    | $V_{CCIOPORH}$ 当 <i>nPORRST</i> 在加电期间保持有效并且在断电期间变为有效时, $V_{CCIO}/V_{CCP}$ 高电源电平             | 3.0  |                  | V  |

|    | $V_{IL(PORRST)}$ <i>nPORRST</i> $V_{CCIO}$ 的低电平输入电压 $> 2.5V$                                |      | 0.2 * $V_{CCIO}$ | V  |

|    | <i>nPORRST</i> $V_{CCIO}$ 的低电平输入电压 $> 2.5V$                                                 |      | 0.5              | V  |

| 3  | $t_{su(PORRST)}$ 建立时间, 加电期间, 在 $V_{CCIO}$ 和 $V_{CCP} > V_{CCIOPORL}$ 前的 <i>nPORRST</i> 有效时间 | 0    |                  | ms |

| 6  | $t_h(PORRST)$ 保持时间, $V_{CC} > V_{CCPORH}$ 后, <i>nPORRST</i> 的有效时间                           | 1    |                  | ms |

| 7  | $t_{su(PORRST)}$ 建立时间, 断电期间, 在 $V_{CC} < V_{CCPORH}$ 前, <i>nPORRST</i> 的有效时间                | 2    |                  | μs |

| 8  | $t_h(PORRST)$ 保持时间, 在 $V_{CCIO}$ 和 $V_{CCP} > V_{CCIOPORH}$ 后 <i>nPORRST</i> 的有效时间          | 1    |                  | ms |

| 9  | $t_h(PORRST)$ 保持时间, 在 $V_{CC} < V_{CCPORL}$ 后 <i>nPORRST</i> 的有效时间                          | 0    |                  | ms |

|    | $t_f(nPORRST)$ 滤波时间 <i>nPORRST</i> 引脚:<br>小于最小值 (MIN) 的脉冲将被滤除掉, 大于最大值 (MAX) 的脉冲将生成一个复位。     | 475  | 2000             | ns |

NOTE: There is no timing dependency between the ramp of the  $V_{CCIO}$  and the  $V_{CC}$  supply voltage; this is just an exemplary drawing.

图 5-1. *nPORRST* 时序图

## 5.3 热复位 (nRST)

这是一个双向复位信号。内部电路在检测到任何器件复位条件时将此信号驱动为低电平。一个外部电路能够通过将此信号强制为低电平来将一个器件复位置为有效。在这个引脚上，输出缓冲器被执行为一个开漏器件（只驱动低电平）。为了确保外部复位不会随意产生，TI 建议将一个外部上拉电阻连接到该引脚。

这个引脚有一个毛刺脉冲滤波器。它还有一个内部上拉电阻。

### 5.3.1 热复位的原因

表 5-5. 热复位的原因

| 器件事件                | 系统状态标志          |

|---------------------|-----------------|

| 加电复位                | 异常状态寄存器，位 15    |

| 振荡器故障               | 全局状态寄存器，位 0     |

| PLL 跳周              | 全局状态寄存器，位 8 和 9 |

| 安全装置异常/调试器复位        | 例外状态寄存器，位 13    |

| CPU 复位（由 CPUSTC 驱动） | 异常状态寄存器，位 5     |

| 软件复位                | 异常状态寄存器，位 4     |

| 外部复位                | 异常状态寄存器，位 3     |

### 5.3.2 nRST 时序要求

表 5-6. nRST 时序要求

|               |                                                     | 最小值                  | 最大值  | 单位 |

|---------------|-----------------------------------------------------|----------------------|------|----|

| $t_{V(RST)}$  | 有效时间，nPORRST 无效之后 nRST 的有效时间                        | $2256t_c(OSC)^{(1)}$ |      | ns |

|               | 有效时间，nRST 有效的时间（所有其它系统复位条件）                         | $32t_c(VCLK)$        |      |    |

| $t_{f(nRST)}$ | 滤波器时间 nRST 引脚。<br>小于 MIN 的脉冲将被滤除掉，大于 MAX 的脉冲将生成一个复位 | 475                  | 2000 | ns |

(1) 假定振荡器已经在 nPORRST 被释放前启动且稳定。

## 5.4 ARM Cortex-R4 CPU 信息

### 5.4.1 ARM Cortex-R4 CPU 的特性概要

ARM Cortex-R4 CPU 的特性包括：

- 具有整体嵌入式 ICE-RT 逻辑的整数单元。

- 高速高级微处理器总线架构 (AMBA) 高级 eXtensible 接口 (AXI)，用于二级 (L2) 主器件和从器件接口。

- 具有一个全局历史记录缓冲器的动态分支预测，和一个 4 入口返回堆栈

- 低中断延迟。

- 不可屏蔽中断

- 一个具有如下组件的哈弗一级存储器系统：

- 支持纠错或奇偶校验检查存储器的紧耦合存储器 (TCM) 接口

- 带有 8 个区域的 ARMv7-R 架构存储器保护单元 (MPU)

- 安全应用中针对故障检测的双内核逻辑

- 一个 L2 存储器接口：

- 单个 64 位 AXI 接口

- 64 位到 TCM RAM 块的受控 AXI 接口

- 一个到 CoreSight 调试访问端口 (DAP) 的调试接口

- 一个性能监视单元 (PMU)

- 一个矢量化中断控制器 (VIC) 端口，

更多有关 ARM Cortex-R4 CPU 的信息，请参阅[www.arm.com](http://www.arm.com)。

### 5.4.2 由软件启用的 ARM Cortex-R4 CPU 的功能

以下的 CPU 特性在复位时被禁用并且必须在需要时由应用启用。

- 紧耦合存储器 (TCM) 访问上的纠错码 (ECC)

- 硬件矢量化中断 (VIC) 端口

- 内存保护单元 (MPU)

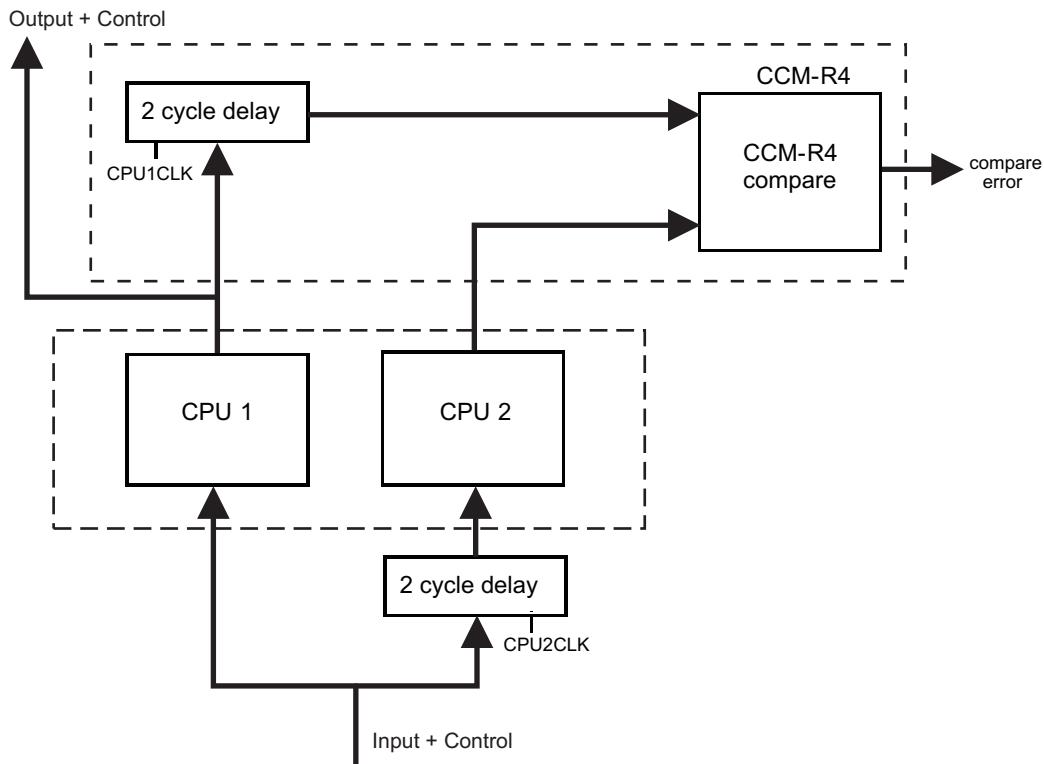

### 5.4.3 双内核执行

此器件有两个 Cortex-R4 内核，在 CCM-R4 单元中比较两个 CPU 的输出信号。为了避免共模影响，将被进行比较的 CPU 的信号延迟 2 个时钟周期，如图 5-3 所示。

CPU 有一个由下列要求指定的不同的 CPU 布局：

- 不同的方向；例如 CPU1 = 朝“北”，CPU2 = 朝向“偏西”

- 针对每个 CPU 的专用保护环

图 5-2. 双 - CPU 方向

### 5.4.4 GCLK 之后的双重 CPU 时钟树

CPU 时钟域被分成两个时钟树，每个 CPU 一个，其中第二个 CPU 的时钟的运行频率一样并且与 CPU1 的时钟协同工作。请参考图 5-3。

### 5.4.5 ARM Cortex-R4 CPU 用于安全目的的比较模块 (CCM)

这个器件有两个 ARM Cortex-R4 CPU 内核，在这两个内核之中，两个 CPU 的输出信号都在 CCM-R4 中进行比较。为了避免共模影响，将要进行比较的 CPU 的信号，以下面图表中所示的不同方式将这些信号延迟。

图 5-3. 双内核执行

为了避免不正确的 CCM-R4 比较错误，应用软件必须在寄存器被读取前初始化两个 CPU 的寄存器，其中包括将寄存器值压入堆栈的函数调用。

### 5.4.6 CPU 自检

通过将确定性逻辑内置自检 (BIST) 控制器用作测试引擎，CPU STC (自检控制器) 被用于测试两个 Cortex-R4 CPU。

自检控制器的主要特性包括：

- 能够将完整测试运行分频成独立的测试间隔

- 能够运行完整的测试或每次运行几个间隔

- 能够继续从上次执行的时间间隔中（测试设置）或从开始重新启动（第一个测试设置）

- 在自检运行期间将被自检测试的 CPU 内核从系统的其余部分完全隔离

- 能够捕获故障间隔数

- 针对 CPU 自检的超时计数器具有一个故障安全特性

#### 5.4.6.1 针对 CPU 自检的应用序列

1. 配置时钟域频率。

2. 选择要运行的测试时间间隔数。

3. 配置针对自检运行的超时周期。

4. 如果需要的话，保存 CPU 的状态

5. 启用自检。

6. 等待 CPU 复位。

7. 在复位处理器中, 读取 CPU 自检状态来识别任何故障。

8. 按需要检索 CPU 状态。

更多信息请参阅《器件技术参考手册》。

#### 5.4.6.2 CPU 自检时钟配置

自检的最大时钟速率为 45MHz。必要时, STCCLK 是从 CPU 时钟上分频的。这个分频器由位于地址 0xFFFFE108 上的 STCCLKDIV 寄存器配置。

更多信息请参阅《器件技术参考手册》。

#### 5.4.6.3 CPU 自检范围

表 5-7 显示了每个自检间隔实现的 CPU 测试范围。它还列出了累积测试周期。通过将测试周期数量与 STC 时钟周期相乘可以计算出测试时间。

**表 5-7. CPU 自检范围**

| 间隔 | 测试覆盖率, % | 测试周期  |

|----|----------|-------|

| 0  | 0        | 0     |

| 1  | 60.06    | 1365  |

| 2  | 68.71    | 2730  |

| 3  | 73.35    | 4095  |

| 4  | 76.57    | 5460  |

| 5  | 78.7     | 6825  |

| 6  | 80.4     | 8190  |

| 7  | 81.76    | 9555  |

| 8  | 82.94    | 10920 |

| 9  | 83.84    | 12285 |

| 10 | 84.58    | 13650 |

| 11 | 85.31    | 15015 |

| 12 | 85.9     | 16380 |

| 13 | 86.59    | 17745 |

| 14 | 87.17    | 19110 |

| 15 | 87.67    | 20475 |

| 16 | 88.11    | 21840 |

| 17 | 88.53    | 23205 |

| 18 | 88.93    | 24570 |

| 19 | 89.26    | 25935 |

| 20 | 89.56    | 27300 |

| 21 | 89.86    | 28665 |

| 22 | 90.1     | 30030 |

| 23 | 90.36    | 31395 |

| 24 | 90.62    | 32760 |

| 25 | 90.86    | 34125 |

| 26 | 91.06    | 35490 |

## 5.5 时钟

### 5.5.1 时钟源

下面的表列出了器件上可用的时钟源。可使用系统模块中的 **CSDISx** 寄存器来启用或禁用每个时钟源。表中的时钟源数量与针对那个时钟源的 **CSDISx** 寄存器中的控制位相对应。

此表还显示了每个时钟源的缺省状态。

表 5-8. 可用时钟源

| 时钟源编号 | 名称        | 说明           | 默认状态 |

|-------|-----------|--------------|------|

| 0     | OSCIN     | 主振荡器         | 被启用  |

| 1     | PLL1      | PLL1的输出      | 被禁用  |

| 2     | 被保留       | 被保留          | 被禁用  |

| 3     | EXTCLKIN1 | 外部时钟输入 #1    | 被禁用  |

| 4     | CLK80K    | 内部基准振荡器的低频输出 | 被启用  |

| 5     | CLK10M    | 内部基准振荡器的高频输出 | 被启用  |

| 6     | 被保留       | 被保留          | 被禁用  |

| 7     | 被保留       | 被保留          | 被禁用  |

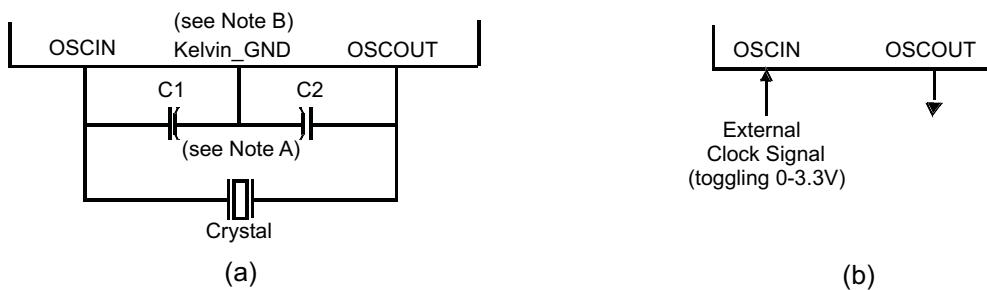

#### 5.5.1.1 主振荡器

如所示，通过在外部 OSCIN 和 OSCOUT 引脚之间连接适合的基本谐振器/晶振图 5-4 和负载电容来启用此振荡器。振荡器是一种单级变换器，由一个集成的偏置电阻器保持在偏置状态。该电阻在泄漏测试测量期间和低功耗模式中被禁用。

**TI** 强烈建议顾客提交该器件的样品让谐振器/晶振供应商测试其性能。供应商有专门设备来确定多大的负载电容能够最好的调节他们的谐振器/晶振来满足微控制器在温度/电压极值范围内对于最优启动和运行的要求。

通过在 OSCIN 引脚上连接一个 3.3V 的时钟信号并使 OSCOUT 引脚悬空（断开）（如下面的图标所示），可使用一个外部振荡器源。

Note A: The values of C1 and C2 should be provided by the resonator/crystal vendor.

Note B: Kelvin\_GND should not be connected to any other GND.

图 5-4. 推荐的晶振/时钟连接

### 5.5.1.1.1 针对主振荡器的时序要求

**表 5-9. 针对主振荡器的时序要求**

| 参数          |                                           | 最小值 | 典型值 | 最大值 | 单位 |

|-------------|-------------------------------------------|-----|-----|-----|----|

| tc(OSC)     | 周期时间, OSCIN (当使用一个正弦波输入时)                 | 50  |     | 200 | ns |

| tc(OSC_SQR) | 周期时间, OSCIN, (当到 OSCIN 的输入是一个方波时)         | 50  |     | 200 | ns |

| tw(OSCIL)   | 脉冲持续时间, OSCIN 低电平的时间 (当到 OSCIN 的输入是一个方波时) | 15  |     |     | ns |

| tw(OSCIH)   | 脉冲持续时间, OSCIN 高电平的时间 (当到 OSCIN 的输入是一个方波时) | 15  |     |     | ns |

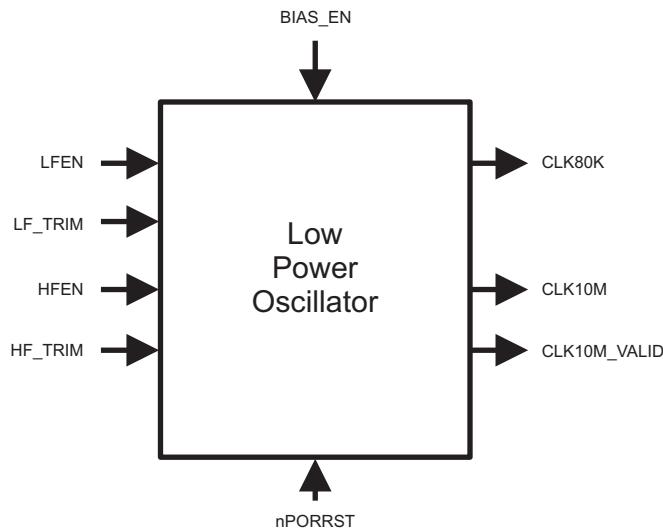

### 5.5.1.2 低功耗振荡器

低功耗振荡器 (LPO) 由一个单宏中的两个振荡器 - 高频 (HF) LPO 和低频 (LF) LPO 组成。

#### 5.5.1.2.1 特性

LPO 的主要特性有：

- 针对省电模式，以极低功耗为一个时钟供源。这个被连接为全局时钟模块的时钟源 #4。

- 针对非时序关键系统，为一个高频时钟供源。这个被连接为全局时钟模块的时钟源 #5。

- 为晶体振荡器故障检测电路提供一个比较时钟。

图 5-5. LPO 方框图

图 5-5 显示了一个内部基准振荡器的方框图。这是一个低功耗振荡器 (LPO) 并且提供两个时钟源：一个的标称值为 80KHz，而另一个的标称值为 10MHz。

#### 5.5.1.2.2 LPO 电气和时序技术规格

表 5-10. LPO 技术规格

| 参数                          |                                                        | 最小值   | 典型值  | 最大值   | 单位      |

|-----------------------------|--------------------------------------------------------|-------|------|-------|---------|

| 时钟检测                        | 振荡器故障频率 - 更低的阀值，使用未经修整的 LPO 输出                         | 1.375 | 2.4  | 4.875 | MHz     |

|                             | 振荡器故障频率 - 更高的阀值，使用未经修整的 LPO 输出                         | 22    | 38.4 | 78    | MHz     |

| LPO-HF 振荡器 ( $f_{HF,LPO}$ ) | 未经修整的频率                                                | 5.5   | 9    | 19.5  | MHz     |

|                             | 已修整的频率                                                 | 8     | 9.6  | 11    | MHz     |

|                             | 从待机 (STANDBY) 的启动时间 (LPO BIAS_EN 高电平时间至少为 900 $\mu$ s) |       |      | 10    | $\mu$ s |

|                             | 冷启动时间                                                  |       |      | 900   | $\mu$ s |

| LPO-LF 振荡器                  | 未经修整的频率                                                | 36    | 85   | 180   | kHz     |

|                             | 从待机 (STANDBY) 的启动时间 (LPO BIAS_EN 高电平时间至少为 900 $\mu$ s) |       |      | 100   | $\mu$ s |

|                             | 冷启动时间                                                  |       |      | 2000  | $\mu$ s |

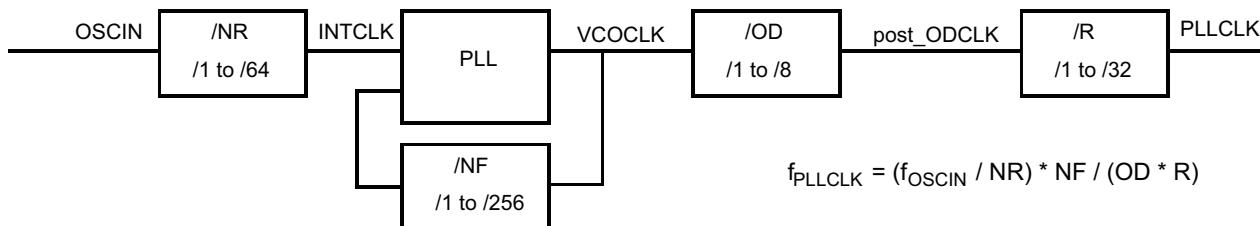

### 5.5.1.3 锁相环 (PLL) 时钟模块

PLL 用于将输入频率倍乘以获得更高的频率。

PLL 的主要特性为：

- 频率调制可被有选择性地添加到 PLL 的合成频率上。

- 可配置频率倍频器和分频器。

- 内置 PLL 跳周监视电路。

- 检测到一个 PLL 跳周时将器件复位的选项。

#### 5.5.1.3.1 方框图

下图显示了一个在该微控制器上的 PLL 宏的高级方框图。

图 5-6. PLL 方框图

#### 5.5.1.3.2 PLL 时序技术规格

表 5-11. PLL 时序技术规格

| 参数                |                               | 最小值 | 最大值 | 单位  |

|-------------------|-------------------------------|-----|-----|-----|

| $f_{INTCLK}$      | PLL1 基准时钟频率                   | 1   | 20  | MHz |

| $f_{post\_ODCLK}$ | Post-ODCLK-PLL1 后置分频器输入时钟基准   |     | 400 | MHz |

| $f_{VCOCLK}$      | VCOCLK-PLL1 输出分频器 (OD) 输入时钟基准 | 150 | 550 | MHz |

## 5.5.2 时钟域

### 5.5.2.1 时钟域说明

下面的表格列出了器件时钟域和它们的缺省时钟源。这个表还显示了被用于为每个时钟域选择一个可用时钟源的系统模块控制寄存器。

表 5-12. 时钟域说明

| 时钟域, 名称 | 缺省时钟源 | 时钟源选择寄存器 | 说明                                                                                                                                                                                                                        |

|---------|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HCLK    | OSCIN | GHVSRC   | <ul style="list-style-type: none"> <li>由 CDDISx 寄存器位 1 禁用</li> </ul>                                                                                                                                                      |

| GCLK    | OSCIN | GHVSRC   | <ul style="list-style-type: none"> <li>一直与 HCLK 的频率保持一致</li> <li>与 HCLK 同相</li> <li>可由 CDDISx 寄存器位 0 与 HCLK 分别被禁用</li> <li>通过使用地址 0xFFFFE108 上的 STCCLKDIV 寄存器的 CLKDIV 字段, 当运行 CPU 自检 (LBIST) 时, 可被 1 到最高 8 分频。</li> </ul> |

| GCLK2   | OSCIN | GHVSRC   | <ul style="list-style-type: none"> <li>一直与 GCLK 的频率保持一致</li> <li>比 GCLK 晚 2 个周期</li> <li>与 GCLK 一起被禁用</li> <li>当运行 CPU 自检 (LBIST) 时, 使用与 GCLK 一样的分频器设置进行分频。</li> </ul>                                                    |

表 5-12. 时钟域说明 (continued)

| 时钟域, 名称 | 缺省时钟源 | 时钟源选择寄存器 | 说明                                                                                                                                                                                                                                                                |

|---------|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCLK    | OSCIN | GHVSRC   | <ul style="list-style-type: none"> <li>由 HCLK 分频获得</li> <li>可以为 HCLK/1, HCLK/2, ... 或 HCLK/16</li> <li>可由 CDDISx 寄存器位 2 与 HCLK 分别被禁用</li> <li>通过使用 CDDISx 寄存器的位 9 可单独禁用 eQEP</li> </ul>                                                                           |

| VCLK2   | OSCIN | GHVSRC   | <ul style="list-style-type: none"> <li>由 HCLK 分频获得</li> <li>可以为 HCLK/1, HCLK/2, ... 或 HCLK/16</li> <li>频率必须为 VCLK 频率的整数倍数。</li> <li>可由 CDDISx 寄存器位 3 与 HCLK 分别被禁用</li> </ul>                                                                                      |

| VCLKA1  | VCLK  | VCLKASRC | <ul style="list-style-type: none"> <li>缺省将 VCLK 作为一个源</li> <li>频率速度可与 HCLK 频率一样</li> <li>由 CDDISx 寄存器位 4 禁用</li> </ul>                                                                                                                                            |

| RTICLK  | VCLK  | RCLKSRC  | <ul style="list-style-type: none"> <li>缺省将 VCLK 作为一个源</li> <li>如果一个 VCLK 以外的时钟源被选为 RTICLK, 那么 RTICLK 频率必须小于或等于 VCLK/3。 <ul style="list-style-type: none"> <li>如果需要的话, 应用可以通过编辑 RCLKSRC 寄存器的 RTI1DIV 字段来确保这一要求。</li> </ul> </li> <li>由 CDDISx 寄存器位 6 禁用</li> </ul> |

### 5.5.2.2 将时钟域映射到器件模块

每个时钟模块都有一个专用功能，如在下图中所示。

图 5-7. 器件时钟域

### 5.5.3 时钟测试模式

RM4x平台架构定义了一个特别模块，此模块允许在 ECLK 引脚和 N2HET[2] 器件输出上生成不同的时钟信号。这个模块被称为时钟测试模块。它对于调试十分有用并且可由系统模块中的 CLKTEST 寄存器配置。

表 5-13. 时钟测试模式选项

| CLKTEST[3-0] | ECLK 上的信号               | CLKTEST[11-8] | N2HET[2] 上的信号 |

|--------------|-------------------------|---------------|---------------|

| 0000         | 振荡器                     | 0000          | 振荡器有效状态       |

| 0001         | 主 PLL 自由运行时钟输出 (PLLCLK) | 0001          | 主 PLL 有效状态    |

| 0010         | 被保留                     | 0010          | 被保留           |

| 0011         | 被保留                     | 0011          | 被保留           |

| 0100         | CLK80K                  | 0100          | 被保留           |

| 0101         | CLK10M                  | 0101          | CLK10M 有效状态   |

| 0110         | 被保留                     | 0110          | 被保留           |

| 0111         | 被保留                     | 0111          | 被保留           |

| 1000         | GCLK                    | 1000          | CLK80K        |

| 1001         | RTI时基                   | 1001          | 振荡器有效状态       |

| 1010         | 被保留                     | 1010          | 振荡器有效状态       |

| 1011         | VCLKA1                  | 1011          | 振荡器有效状态       |

| 1100         | 被保留                     | 1100          | 振荡器有效状态       |

| 1101         | 被保留                     | 1101          | 振荡器有效状态       |

| 1110         | 被保留                     | 1110          | 振荡器有效状态       |

| 1111         | 闪存 HD 泵振荡器              | 1111          | 振荡器有效状态       |

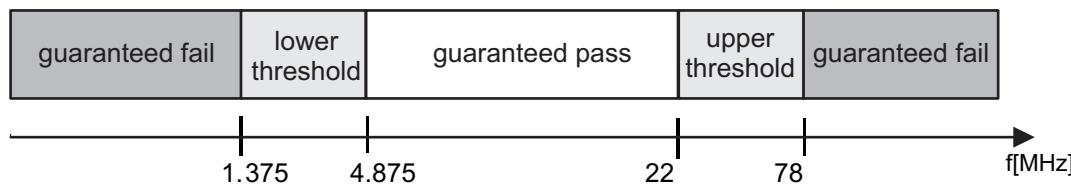

## 5.6 时钟监视

LPO 时钟检测 (LPOCLKDET) 模块由一个时钟监视器 (CLKDET) 和一个内部低功耗振荡器 (LPO) 组成。

LPO 提供两个时钟源-一个低频 (LFLPO) 和一个高频 (HFLPO)。

CLKDET 是为一个针对外部提供的时钟信号 (OSCIN) 的监控电路。在OSCIN 频率下降到低于一个频率窗口的情况下, CLKDET 在全局状态寄存器中标记这个情况 (GLBSTAT 位 0: 振荡器故障 (OSC FAIL)) 并且将所有由 OSCIN 供源的时钟域切换至HFLPO 时钟 (跛行模式时钟)。

有效 OSCIN 频率范围被定义为:  $f_{HFLPO}/4 < f_{OSCIN} < f_{HFLPO} * 4$ 。

### 5.6.1 时钟监视时序

有关 LPO 和时钟检测的更多信息, 请参考表 5-10。

图 5-8. LPO 和时钟检测, 未修整的 HFLPO

### 5.6.2 外部时钟 (ECLK) 输出功能

ECLK 引脚可被配置为输出一个预分频时钟信号, 此信号表示一个内部器件时钟。这个输出可被外部监视为一个安全诊断。

### 5.6.3 双时钟比较器

双时钟比较器 (DCC) 模块通过计数两个独立时钟源 (计数器 0 和计数器 1) 的脉冲数来确定所选时钟源的准确性。如果一个时钟在技术参数之外, 那么就生成一个错误信号。例如, DCC 可被配置为使用 CLK10M 作为基准时钟 (用于计数器 0), 而 VCLK 作为“测试中的时钟” (用于计数器 1)。这个配置使得 DCC 能够在 VCLK 正在使用 PLL 输出作为其时钟源的时候监视 PLL 输出时钟。

这个模块的一个另外的用途是测量一个可选时钟源的频率, 方法是使用输入时钟作为一个基准, 通过计算两个独立时钟源的脉冲来测量。计数器 0 在一个预先设定的脉冲数量之后生成一个定宽计数窗口。计数器 1 在一个预先设定的脉冲数量之后生成一个定宽脉冲 (1 个周期)。如果计数器 1 在由计数器 0 生成的计数窗口内没有达到 0, 那么这个脉冲被设定为一个错误信号。

#### 5.6.3.1 特性

- 将两个不同的时钟源作为到两个独立计数器块的输入。

- 时钟源中的一个为已知正常, 或基准时钟; 第二个时钟源是“测试中的时钟。”

- 每个计数器可使用初始的, 或者种子值进行编程。

- 计数器块同时从它们的种子值开始倒计数; 与针对测试中时钟的预计频率的不匹配将生成一个错误信号, 此信号被用于中断 CPU。

#### 5.6.3.2 DCC 时钟源中断的映射

表 5-14. DCC 计数器 0 时钟源

| 测试模式 | 时钟源 [3:0] | 时钟名称        |

|------|-----------|-------------|

| 0    | 其它        | 振荡器 (OSCIN) |

|      | 0x5       | 高频 LPO      |

|      | 0xA       | 测试时钟 (TCK)  |

| 1    | X         | VCLK        |

表 5-15. DCC 计数器 1 时钟源

| 测试模式 | 键 [3:0] | 时钟源 [3:0] | 时钟名称          |

|------|---------|-----------|---------------|

| 0    | 其它      | -         | N2HET[31]     |

|      |         | 0x0       | 主 PLL自由运行时钟输出 |

|      |         | 0x1       | 不可用           |

|      |         | 0x2       | 低频 LPO        |

|      |         | 0x3       | 高频 LPO        |

|      |         | 0x4       | 闪存 HD 泵振荡器    |

|      |         | 0x5       | EXTCLKIN      |

|      |         | 0x6       | 不可用           |

|      |         | 0x7       | 环形振荡器         |

|      |         | 0x8-0xF   | VCLK          |

| 1    | X       | X         | HCLK          |

## 5.7 去毛刺脉冲滤波器

一个毛刺脉冲滤波器出现在以下信号上。

表 5-16. 毛刺脉冲滤波器时序技术规格

| 引脚      | 参数               |                                                                       | 最小值 | 最大值  | 单位 |

|---------|------------------|-----------------------------------------------------------------------|-----|------|----|

| nPORRST | $t_{f(nPORRST)}$ | 滤波时间 nPORRST 引脚;<br>小于 MIN 的脉冲将被滤除掉, 大于 MAX 的脉冲将生成一个复位 <sup>(1)</sup> | 475 | 2000 | ns |

| nRST    | $t_{f(nRST)}$    | 滤波器时间 nRST 引脚。<br>小于 MIN 的脉冲将被滤除掉, 大于 MAX 的脉冲将生成一个复位                  | 475 | 2000 | ns |

| TEST    | $t_f$ (测试)       | 滤波器时间 TEST 引脚。<br>小于 MIN 的脉冲将被滤除掉, 大于 MAX 的脉冲将通过                      | 475 | 2000 | ns |

(1) nPORRST 信号上的毛刺脉冲滤波器被设计成振幅脉冲将不会复位微控制器的任何部件 (闪存泵, I/O 引脚等)。无也生成一个到 CPU 的有效复位。

## 5.8 器件存储器映射

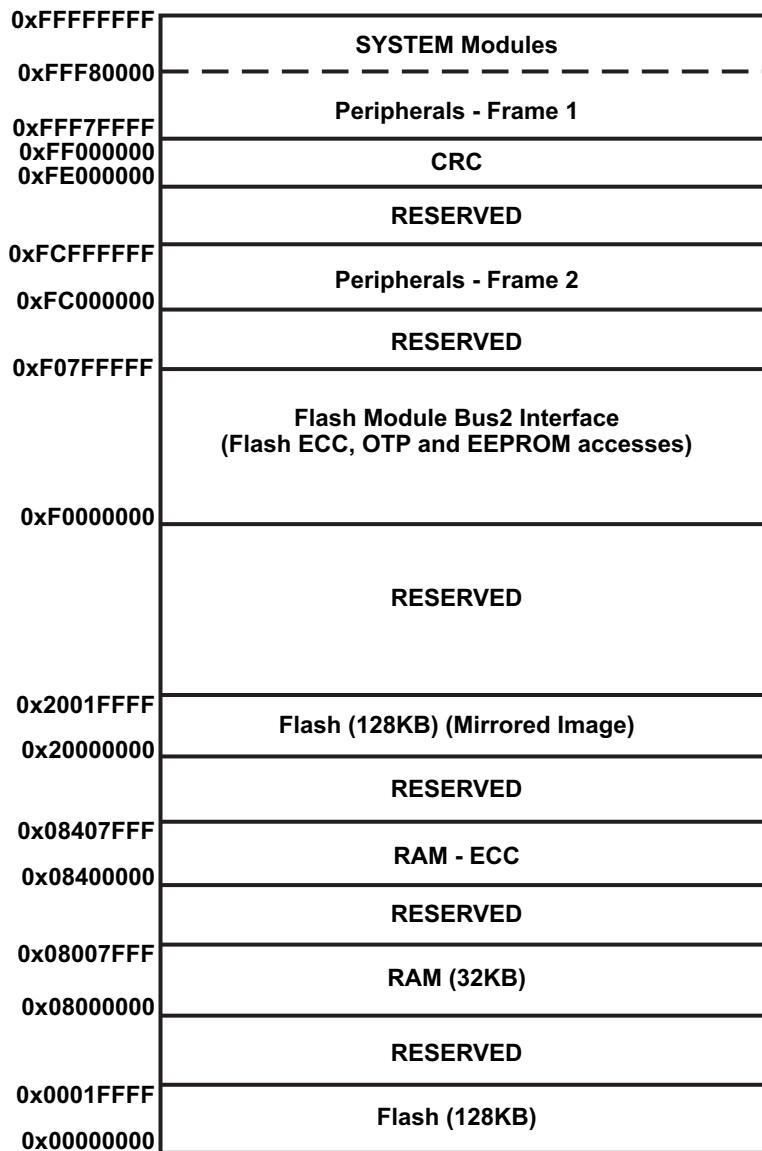

### 5.8.1 存储器映射图

图 5-9 显示了器件存储器映射。

图 5-9. RM41232 存储器映射

在所有配置中的闪存存储器被镜像来支持 ECC 逻辑测试。被镜像的闪存映像的基地址为 0x2000 0000。

## 5.8.2 存储器映射表

请参阅图 1-1 给出的器件互连方框图。

表 5-17. 器件存储器映射

| 模块名称                        | 帧芯片选择   | 地址范围        |             | 帧大小   | 实际大小   | 对帧内未实现位置的访问的响应                                                                               |

|-----------------------------|---------|-------------|-------------|-------|--------|----------------------------------------------------------------------------------------------|

|                             |         | 启动 (START)  | 结束 (END)    |       |        |                                                                                              |