**OPA607, OPA2607** ZHCSKG0J - OCTOBER 2019 - REVISED APRIL 2021

# 适用于成本敏感型系统的 OPAx607 50MHz、低功耗、轨至轨输出 CMOS 运算 放大器

### 1 特性

增益带宽积 (GBW): 50MHz 静态电流:900μA(典型值)

• 宽带噪声: 3.8nV/√Hz

输入温漂: 1.5 μ V/°C(最大值) 失调电压:120µV(典型值)

输入偏置电流:10pA(最大值)

• 轨至轨输出 (RRO)

• 解补偿增益 ≥ 6V/V (稳定)

关断电流:1µA(最大值)

电源电压范围: 2.2V 至 5.5V

### 2 应用

电流感应

探鱼器和声纳

超声波流量计

园艺和电动工具

打印机

光幕和安全防护装置

光学模块

手持测试设备

PM2.5 和 PM10 颗粒传感器

### 3 说明

OPA607 和 OPA2607 器件是一款解补偿通用 CMOS 运算放大器,最小稳定增益为 6V/V,具有 3.8nV/√Hz 的低噪声和 50MHz 的 GBW。OPAx607 器件具有低噪 声和高带宽特性,因此非常适合要求在成本和性能之间 达到良好平衡的通用应用。高阻抗 CMOS 输入使得 OPAx607 放大器适合连接具有高输出阻抗的传感器 (例如,压电式传感器)。

OPAx607 器件具有断电模式,最大静态电流小于 1µA,因此,该器件适用于便携式电池供电型应用。 OPAx607 器件的轨至轨输出 (RRO) 相对于电源轨具有 高达 8mV 的摆幅,从而更大限度提高动态范围。

OPAx607 经过优化,适合在低至 2.2V (±1.1V) 和高达 5.5V (±2.75V) 的低电源电压下工作,且额定工作温度 范围为 - 40°C 至 +125°C。

器件信息(1)

|  | HH 11 1H 20 |            |                 |  |  |  |  |

|--|-------------|------------|-----------------|--|--|--|--|

|  | 器件型号        | 封装         | 封装尺寸 ( 标称值 )    |  |  |  |  |

|  | OPA607      | SC70 (6)   | 2.00mm × 1.25mm |  |  |  |  |

|  | OFA001      | SOT23 (5)  | 2.90mm × 1.60mm |  |  |  |  |

|  |             | SOIC (8)   | 4.90mm × 3.91mm |  |  |  |  |

|  | OPA2607     | VSSOP (8)  | 3.00mm × 3.00mm |  |  |  |  |

|  |             | X2QFN (10) | 1.50mm x 2.00mm |  |  |  |  |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

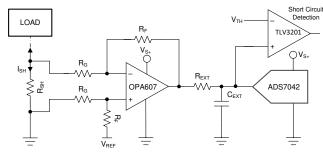

适用于电流感应应用的 OPAx607

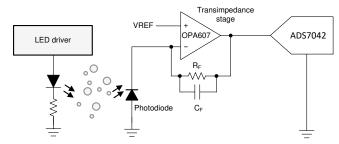

适用于跨阻应用的 OPAx607

### **Table of Contents**

| 1 特性                                 | 1 | 9 Application and Implementation                   | 22                  |

|--------------------------------------|---|----------------------------------------------------|---------------------|

| 2 应用                                 |   | 9.1 Application Information                        |                     |

| - 二八                                 |   | 9.2 Typical Applications                           | 22                  |

| 4 Revision History                   |   | 10 Power Supply Recommendations                    |                     |

| 5 Device Comparison                  |   | 11 Layout                                          |                     |

| 6 Pin Configuration and Functions    |   | 11.1 Layout Guidelines                             |                     |

| 7 Specifications                     |   | 11.2 Layout Examples                               |                     |

| 7.1 Absolute Maximum Ratings         |   | 12 Device and Documentation Support                | 31                  |

| 7.2 ESD Ratings                      |   | 12.1 Device Support                                | 31                  |

| 7.3 Recommended Operating Conditions |   | 12.2 Documentation Support                         | 31                  |

| 7.4 Thermal Information              |   | 12.3 Related Links                                 | <b>3</b> 1          |

| 7.5 Electrical Characteristics       |   | 12.4 Receiving Notification of Documentation Updat | es <mark>3</mark> 1 |

| 7.6 Typical Characteristics          |   | 12.5 支持资源                                          | 31                  |

| 8 Detailed Description               |   | 12.6 Trademarks                                    |                     |

| 8.1 Overview                         |   | 12.7 Electrostatic Discharge Caution               | 31                  |

| 8.2 Functional Block Diagram         |   | 12.8 Glossary                                      |                     |

| 8.3 Feature Description              |   | 13 Mechanical, Packaging, and Orderable            |                     |

| 8.4 Device Functional Modes          |   | Information                                        | 31                  |

|                                      |   |                                                    |                     |

4 Revision History 注:以前版本的页码可能与当前版本的页码不同

| С | hanges from Revision I (February 2021) to Revision J (April 2021)                                      | Page  |

|---|--------------------------------------------------------------------------------------------------------|-------|

| • | 删除了 <i>器件信息</i> 表中 VSSOP (8) 和 X2QFN (10) 封装的预发布声明                                                     | 1     |

| • | Removed the preview statement from the OPA2607 X2QFN (RUG) package and VSSOP (DGK) in the              | 4     |

| • | Device Comparison section                                                                              |       |

| C | hanges from Revision H (December 2020) to Revision I (February 2021)                                   | Page  |

| • | 更新了数据表标题。                                                                                              | 1     |

| С | hanges from Revision G (October 2020) to Revision H (December 2020)                                    | Page  |

| • | Updated the I/O and Descriptions in the Pin Functions—Single Channel table                             | 5     |

| С | hanges from Revision F (September 2020) to Revision G (October 2020)                                   | Page  |

| • | Removed the RUG Package 8-Pin X2QFN pinout to the Pin Configuration and Functions section              | 5     |

| • | Removed the N/C pin decription from the Pin Functions - Single Channel table                           | 5     |

| • | Changed Overdrive Recovery Time from 0.25µs to 0.3µs                                                   | 9     |

| • | Updated the Turn-On and Turn-Off Time figure in the Typical Characteristics section                    | 11    |

| • | Updated the Power Down Pin Bias Current vs Power Down Pin Voltage figure in the Typical Characteris    | stics |

|   | section                                                                                                |       |

| • | Updated the Input Offset Voltage vs Temperature figure in the <i>Typical Characteristics</i> section   |       |

| • | Updated the Common Mode Rejection Ratio vs Temperature figure in the Typical Characteristics section   | n11   |

| • | Updated the Short-Circuit Current vs Temperature figure in the <i>Typical Characteristics</i> section  | 11    |

| • | Updated the Input Bias and Offset Current vs Temperature figure in the Typical Characteristics section |       |

| • | Updated the Output Voltage vs Output Current Sourcing and Sinking figure in the Typical Characteristic |       |

|   | section                                                                                                | 11    |

| • | Added the Electromagnetic Interference Rejection Ratio Referred to Noninverting Input (EMIRR+) vs      |       |

|   | Frequency figure to the <i>Typical Characteristics</i> section                                         |       |

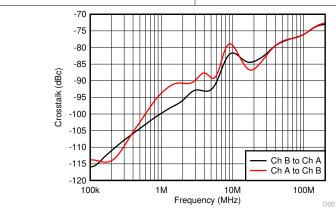

| • | Added the Crosstalk vs Frequency figure to the Typical Characteristics section                         | 11    |

### www.ti.com.cn

| •  | Added the Quiescent Current vs Temperature figure to the <i>Typical Characteristics</i> section                                                                      | 11   |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

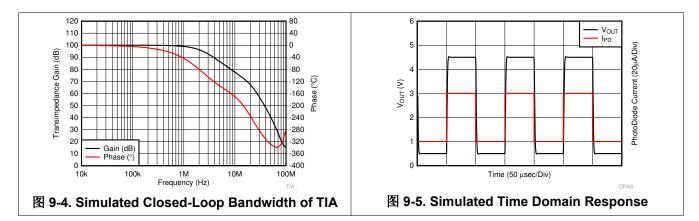

| •  | Updated the Simulated Closed-Loop Bandwidth of TIA figure in the Application Curves section                                                                          | 23   |

| •  | Updated the Simulated Time Domain Response figures in the Application Curves section                                                                                 | 23   |

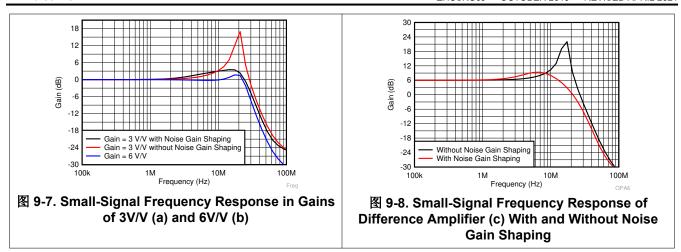

| •  | Updated the Small-Signal Frequency Response in Gains of 3V/V (a) and 6V/V (b) figure in the <i>Noninvert Gain of 3 V/V</i> section                                   | _    |

| •  | Updated the Small-Signal Frequency Response of Difference Amplifier (c) With and Without Noise Gain Shaping figures in the <i>Noninverting Gain of 3 V/V</i> section |      |

| CI | nanges from Revision E (August 2020) to Revision F (September 2020)                                                                                                  | Page |

| •  | Deleted blank CMRR specifications from Electrical Characteristics table                                                                                              | 9    |

| CI | nanges from Revision D (May 2020) to Revision E (August 2020)                                                                                                        | Page |

| •  | 更新了整个文档的表、图和交叉参考的编号格式                                                                                                                                                | 1    |

| •  | 将 OPA2607 SOIC (8) 封装的状态从 预发布 更改为 正在供货                                                                                                                               | 1    |

| CI | nanges from Revision C (April 2020) to Revision D (May 2020)                                                                                                         | Page |

| •  | 将状态从 <i>预告信息</i> 更改为 <i>量产数据</i>                                                                                                                                     | 1    |

# **5 Device Comparison**

|         | NO. OF   | PACKAGE LEADS |                               |             |                               |              |  |  |

|---------|----------|---------------|-------------------------------|-------------|-------------------------------|--------------|--|--|

| DEVICE  | CHANNELS | SOIC<br>(D)   | X2QFN<br>(RUG) <sup>(1)</sup> | VSSOP (DGK) | SC-70<br>(DCK) <sup>(1)</sup> | SOT-23 (DBV) |  |  |

| OPA607  | 1        | _             | _                             | _           | 6 <sup>(1)</sup>              | 5            |  |  |

| OPA2607 | 2        | 8             | 10 <sup>(1)</sup>             | 8           | _                             | _            |  |  |

### (1) Package with Power Down mode.

| DEVICE  | INPUT   | NPUT DRIFT STAE |   | INPUT DRIFT STABLE GA |    | I <sub>Q</sub> / CHANNEL GBW (MHz) |     | SLEW RATE<br>(V/μs) | VOLTAGE<br>NOISE<br>(nV/√Hz) |  |

|---------|---------|-----------------|---|-----------------------|----|------------------------------------|-----|---------------------|------------------------------|--|

| OPAx365 | CMOS    | 1               | 1 | 4.6                   | 50 | 25                                 | 4.5 |                     |                              |  |

| OPAx607 | CMOS    | 0.3             | 6 | 0.9                   | 50 | 24                                 | 3.8 |                     |                              |  |

| OPAx837 | Bipolar | 0.4             | 1 | 0.6                   | 50 | 105                                | 4.7 |                     |                              |  |

Product Folder Links: OPA607 OPA2607

# **6 Pin Configuration and Functions**

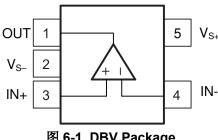

图 6-1. DBV Package 5-Pin SOT-23 Top View

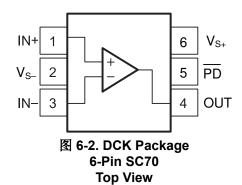

### Pin Functions - Single Channel

|                  | PIN |     | 1/0 | DESCRIPTION                                             |  |  |

|------------------|-----|-----|-----|---------------------------------------------------------|--|--|

| NAME             | DBV | DCK | 1/0 | DESCRIPTION                                             |  |  |

| IN -             | 4   | 3   | I   | Inverting input                                         |  |  |

| IN+              | 3   | 1   | I   | Non inverting input                                     |  |  |

| OUT              | 1   | 4   | 0   | Output                                                  |  |  |

| PD               | _   | 5   | I   | Power down (can be left floating)                       |  |  |

| V <sub>S</sub> - | 2   | 2   | _   | Negative supply or ground (for single-supply operation) |  |  |

| V <sub>S+</sub>  | 5   | 6   | _   | Positive supply                                         |  |  |

**Top View**

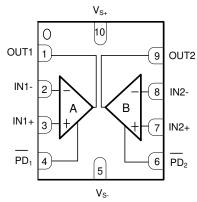

图 6-4. OPA2607 RUG Package 10-Pin X2QFN Top View

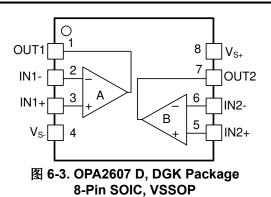

### Pin Functions - Dual Channel

|                  | PIN    |     | 1/0 | DESCRIPTION                                                                                                          |  |  |

|------------------|--------|-----|-----|----------------------------------------------------------------------------------------------------------------------|--|--|

| NAME             | D, DGK | RUG | I/O | DESCRIPTION                                                                                                          |  |  |

| IN1 -            | 2      | 2   | I   | Inverting input, channel 1                                                                                           |  |  |

| IN1+             | 3      | 3   | I   | Noninverting input, channel 1                                                                                        |  |  |

| IN2 -            | 6      | 8   | I   | Inverting input, channel 2                                                                                           |  |  |

| IN2+             | 5      | 7   | I   | Noninverting input, channel 2                                                                                        |  |  |

| OUT1             | 1      | 1   | 0   | Output, channel 1                                                                                                    |  |  |

| OUT2             | 7      | 9   | 0   | Output, channel 2                                                                                                    |  |  |

| V <sub>S</sub> - | 4      | 5   |     | Negative (lowest) supply or ground (for single-supply operation)                                                     |  |  |

| V <sub>S+</sub>  | 8      | 10  | _   | Positive (highest) supply                                                                                            |  |  |

| PD1              | _      | 4   | I   | Low = amplifier 1 disabled, high = amplifier 1 enabled; see the <i>Power Down Mode</i> section for more information. |  |  |

| PD2              | _      | 6   | I   | Low = amplifier 2 disabled, high = amplifier 2 enabled; see the <i>Power Down Mode</i> section for more information. |  |  |

## 7 Specifications

### 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)(1)

|                                         |                                           | MIN                      | MAX              | UNIT |

|-----------------------------------------|-------------------------------------------|--------------------------|------------------|------|

| (V <sub>S+</sub> ) - (V <sub>S-</sub> ) | Supply voltage, V <sub>s</sub>            |                          | 6                | V    |

| V <sub>IN+</sub> , V <sub>IN</sub> -    | Input voltage                             | (V <sub>S-</sub> ) - 0.5 | $(V_{S+}) + 0.5$ | V    |

| V <sub>PD</sub>                         | PD voltage                                | (V <sub>S-</sub> ) - 0.5 | 6                | V    |

| V <sub>ID</sub>                         | Differential input voltage <sup>(4)</sup> |                          | ±5               | V    |

| I <sub>I</sub>                          | Continuous input current <sup>(2)</sup>   |                          | ±10              | mA   |

| Io                                      | Continuous output current <sup>(3)</sup>  |                          | ±20              | mA   |

|                                         | Continuous power dissipation              | See Thermal Information  |                  |      |

| T <sub>J</sub>                          | Maximum junction temperature              |                          | 150              | °C   |

| T <sub>A</sub>                          | Operating free-air temperature            | - 40                     | 125              | °C   |

| T <sub>stg</sub>                        | Storage temperature                       | - 65                     | 150              | °C   |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not supported.

### 7.2 ESD Ratings

|        |               |                                                                                            | VALUE | UNIT |

|--------|---------------|--------------------------------------------------------------------------------------------|-------|------|

| V/ECD) |               | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                          | ±2000 |      |

|        | Electrostatic | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup>             | ±1000 | V    |

|        | discharge     | D Package , Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±750  |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                | <u> </u>                                               |      |     |       |      |

|----------------|--------------------------------------------------------|------|-----|-------|------|

|                |                                                        | MIN  | NOM | MAX   | UNIT |

| Vs             | Supply voltage (V <sub>S+</sub> ) - (V <sub>S</sub> -) | 2.2  |     | 5.5   | V    |

|                |                                                        | ±1.1 |     | ±2.75 | V    |

| T <sub>A</sub> | Ambient operating temperature                          | - 40 | 25  | 125   | °C   |

<sup>(2)</sup> Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.5 V beyond the supply rails should be current limited to 10 mA or less.

<sup>(3)</sup> Short-circuit to ground, one amplifier per package.

<sup>(4)</sup> Long term drift of offset voltage (> 1mV) if a differential input in excess of ≈ 2V is applied continuously between the IN+ and IN- pins at elevated temperatures.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 7.4 Thermal Information

|                        |                                              | OPAx607  |                |                |            |                |      |

|------------------------|----------------------------------------------|----------|----------------|----------------|------------|----------------|------|

| THERMAL METRIC(1)      |                                              | D (SOIC) | DGK<br>(VSSOP) | DBV<br>(SOT23) | DCK (SC70) | RUG<br>(X2QFN) | UNIT |

|                        |                                              | 8 PINS   | 8 PINS         | 5 PINS         | 6 PINS     | 10 PINS        |      |

| R <sub>0 JA</sub>      | Junction-to-ambient thermal resistance       | 131.1    | 179            | 196.5          | 219.7      | 152            | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 73.2     | 71             | 118.7          | 182.6      | 58             | °C/W |

| R <sub>0</sub> JB      | Junction-to-board thermal resistance         | 74.5     | 101            | 64.5           | 105.7      | 77             | °C/W |

| ΨJT                    | Junction-to-top characterization parameter   | 24.5     | 13             | 41.1           | 87         | 1.2            | °C/W |

| ψ ЈВ                   | Junction-to-board characterization parameter | 73.3     | 100            | 64.2           | 105.4      | 77             | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 7.5 Electrical Characteristics

At  $T_A$  = 25°C,  $V_S$  = 2.2 V to 5.5 V, G = 6 V/V<sup>(5)</sup>,  $R_F$  = 5 k  $\Omega$  ,  $C_F$  = 2.5 pF,  $V_{CM}$  = (V<sub>S</sub> / 2)  $^-$  0.5 V,  $C_L$  = 10 pF,  $R_L$  = 10 k $\Omega$  connected to (V<sub>S</sub> / 2)  $^-$  0.5 V, and,  $\overline{PD}$  connected to (V<sub>S+</sub>) (unless otherwise noted)<sup>(1)</sup>

|                      | PARAMETER                                        | TEST CONDITIONS                                                               | MIN                 | TYP         | MAX                      | UNIT         |  |

|----------------------|--------------------------------------------------|-------------------------------------------------------------------------------|---------------------|-------------|--------------------------|--------------|--|

| OFFSET V             | OLTAGE                                           |                                                                               |                     |             |                          |              |  |

| .,                   | Input offset voltage                             |                                                                               | - 0.6               | 0.12        | 0.6                      | .,           |  |

| V <sub>OS</sub>      | Input offset voltage                             | T <sub>A</sub> = -40°C to +125°C                                              | - 0.7               | 0.12        | 0.7                      | mV           |  |

| dV <sub>OS</sub> /dT | Input offset voltage drift                       | T <sub>A</sub> = -40°C to +125°C                                              |                     | ±0.3        | ±1.5                     | μV/°C        |  |

| PSRR                 | Power-supply rejection ratio                     | V <sub>S</sub> = 2.2 V to 5.5 V                                               | 95                  | 120         |                          | dB           |  |

| INPUT VOI            | TAGE RANGE                                       |                                                                               |                     |             |                          |              |  |

| V <sub>CM</sub>      | Common-mode voltage range                        |                                                                               | (V <sub>S</sub> - ) |             | (V <sub>S+</sub> ) - 1.1 | V            |  |

| CMRR                 | Common-mode rejection ratio <sup>(3)</sup>       | $(V_{S^-}) < V_{CM} < (V_{S^+}) - 1.1 V$                                      | 90                  | 100         |                          | dB           |  |

| INPUT BIA            | S CURRENT                                        |                                                                               |                     |             |                          | I            |  |

|                      | (2)                                              |                                                                               |                     | ±3          | ±10                      |              |  |

| I <sub>B</sub>       | Input bias current <sup>(2)</sup>                | T <sub>A</sub> = −40°C to 125°C                                               |                     | See Fig. 29 |                          | pА           |  |

| Ios                  | Input offset current <sup>(2)</sup>              |                                                                               |                     | ±3          | ±10                      |              |  |

| NOISE                |                                                  |                                                                               |                     |             |                          |              |  |

|                      | Input voltage noise (peak-to-peak)               | f = 0.1 Hz to 10 Hz                                                           |                     | 1.6         |                          | $\mu V_{PP}$ |  |

| e <sub>N</sub>       | Input voltage noise density                      | f = 10 kHz, 1/f corner at 1 kHz                                               |                     | 3.8         |                          | nV/ √ Hz     |  |

| i <sub>N</sub>       | Input current noise density                      | f = 1 kHz                                                                     |                     | 46          |                          | fA/ √ Hz     |  |

| INPUT IMP            | EDANCE                                           |                                                                               |                     |             |                          |              |  |

| C                    | Differential                                     |                                                                               |                     | 11.5        |                          | nE           |  |

| C <sub>IN</sub>      | Common-mode                                      |                                                                               |                     | 5.5         |                          | pF           |  |

| OPEN-LOC             | DP GAIN                                          |                                                                               |                     | -           |                          |              |  |

| A <sub>OL</sub>      | Open-loop voltage gain <sup>(3)</sup>            | (V <sub>S</sub> - ) + 400 mV < V <sub>OUT</sub> < (V <sub>S+</sub> ) - 400 mV | 110                 | 130         |                          | dB           |  |

|                      | Phase margin                                     |                                                                               |                     | 65          |                          | ٥            |  |

| AC Charac            | teristics (V <sub>S</sub> = 5 V)                 |                                                                               |                     |             |                          |              |  |

| SSBW                 | Small-signal bandwidth                           | V <sub>OUT</sub> = 20 mVpp                                                    |                     | 9           |                          | MHz          |  |

| GBW                  | Gain-bandwidth product                           | G = 20 V/V                                                                    |                     | 50          |                          | IVII IZ      |  |

| SR                   | Slew rate                                        | 3-V output step (10-90%), V <sub>OCM</sub> = mid-supply                       |                     | 24          |                          | V/µs         |  |

| t <sub>S</sub>       | Settling time                                    | To 0.1%, 3-V step, G = 40, V <sub>OCM</sub> = mid-supply                      | 1                   |             |                          | μs           |  |

| *5                   | Column g umo                                     | To 0.01%, 3-V step, G = 40, V <sub>OCM</sub> = mid-supply                     | 1.8                 |             |                          | μο           |  |

|                      | Overdrive recovery time                          | V <sub>IN+</sub> × Gain > V <sub>S</sub>                                      |                     | 0.3         |                          | μs           |  |

|                      |                                                  | $V_{OUT}$ = 2 $V_{PP}$ , f = 1 kHz , $R_L$ = 10 k $\Omega$                    |                     | -103        |                          |              |  |

| THD + N              | Total Harmonic Distortion + Noise <sup>(6)</sup> | $V_{OUT}$ = 2 $V_{PP}$ , f = 20 kHz , $R_L$ = 10 k $\Omega$                   | -91.5               |             |                          | dB           |  |

|                      | Total Farmonio Distortion - Noise                | $V_{OUT}$ = 2 $V_{PP}$ , f = 1 kHz , $R_L$ = 1 k $\Omega$                     | -96                 |             |                          | ] ub         |  |

|                      |                                                  | $V_{OUT}$ = 2 $V_{PP}$ , f = 20 kHz , $R_L$ = 1 k $\Omega$                    |                     | -72.8       |                          |              |  |

| HD2                  | Second-order harmonic distortion                 | V <sub>OUT</sub> = 2 V <sub>PP</sub> f = 20 kHz                               |                     | -105        |                          | dBc          |  |

| HD3                  | Third-order harmonic distortion                  | V <sub>OUT</sub> = 2 V <sub>PP</sub> f = 20 kHz                               |                     | -95         |                          | ubc          |  |

|                      | Channel-to-channel crosstalk                     | V <sub>OUT</sub> = 2 V <sub>PP</sub> , f = 100 kHz                            |                     | -114        |                          | dBc          |  |

### 7.5 Electrical Characteristics (continued)

At  $T_A$  = 25°C,  $V_S$  = 2.2 V to 5.5 V, G = 6 V/V<sup>(5)</sup>,  $R_F$  = 5 k  $\Omega$  ,  $C_F$  = 2.5 pF,  $V_{CM}$  = ( $V_S$  / 2) - 0.5 V,  $C_L$  = 10 pF,  $K\Omega$  connected to ( $V_S$  / 2) - 0.5 V, and,  $\overline{PD}$  connected to ( $V_{S+}$ ) (unless otherwise noted)<sup>(1)</sup>

$R_{I} = 10$

|                                 | PARAMETER                                                 | TEST CONDITIONS                            | MIN TYP              | MAX                  | UNIT |  |

|---------------------------------|-----------------------------------------------------------|--------------------------------------------|----------------------|----------------------|------|--|

| OUTPU                           | Т                                                         |                                            |                      |                      |      |  |

|                                 | O. 44 14 1                                                |                                            | 8                    | 12                   | mV   |  |

|                                 | Output voltage swing from supply rails                    | T <sub>A</sub> = - 40°C to +125°C          |                      | 12                   | IIIV |  |

| I <sub>SC</sub>                 | Output Short-circuit current                              |                                            | 60                   |                      | mA   |  |

| Z <sub>O</sub>                  | Open-loop output impedance                                | f = 1 MHz                                  | 500                  |                      | Ω    |  |

| POWER                           | SUPPLY                                                    |                                            | •                    |                      |      |  |

|                                 | Quiescent current per amplifier                           | I <sub>O</sub> = 0 mA                      | 900                  | 1100                 |      |  |

| Quiescent current per amplifier | Quiescent current per ampliner                            | $I_{O} = 0$ mA, $T_{A} = -40$ °C to +125°C |                      | 1200                 | μA   |  |

| POWER                           | DOWN (Device Enabled When Floating)                       |                                            | <b>1</b>             |                      |      |  |

|                                 | Power Down quiescent current per amplifier <sup>(4)</sup> | PD = V <sub>S</sub> -                      | 750                  | 1000                 | ~ A  |  |

|                                 | Power Down pin bias current per amplifier <sup>(7)</sup>  | PD = V <sub>S</sub> -                      | - 750                | - 1000               | nA   |  |

|                                 | Enable voltage threshold                                  | Logic-High threshold                       |                      | 0.7 x V <sub>S</sub> | V    |  |

|                                 | Disable voltage threshold                                 | Logic-Low threshold                        | 0.2 x V <sub>S</sub> |                      | V    |  |

| t <sub>ON</sub>                 | Turn-on time delay <sup>(2)</sup>                         |                                            | 10                   | 15                   |      |  |

| t <sub>OFF</sub>                | Turn-off time delay                                       |                                            | 0.5                  |                      | μs   |  |

<sup>(1)</sup> Parameters with minimum or maximum specification limits are 100% production tested at 25°C, unless otherwise noted. Over temperature limits are based on characterization and statistical analysis.

- (2) Specified by design and characterization or both; not production tested.

- (3) Production Tested at  $V_S = 5.5V$

- (4) In Power Down mode current drawn by the opamp is equal to the bias current sourced on the PD pin

- (5) All Gains (G) mentioned are in V/V unless otherwise noted.

- 6) Lowpass-filter bandwidth is 92kHz for f = 20 kHz and 20 kHz for f = 1 kHz.

- (7) Negative value of the Power Down bias current indicates current being sourced from the opamp's PD pin towards external circuit.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

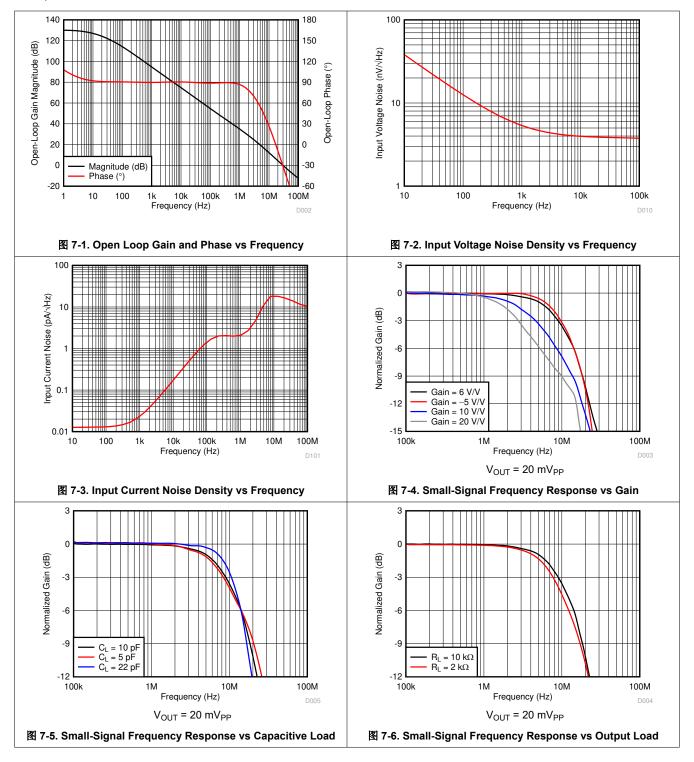

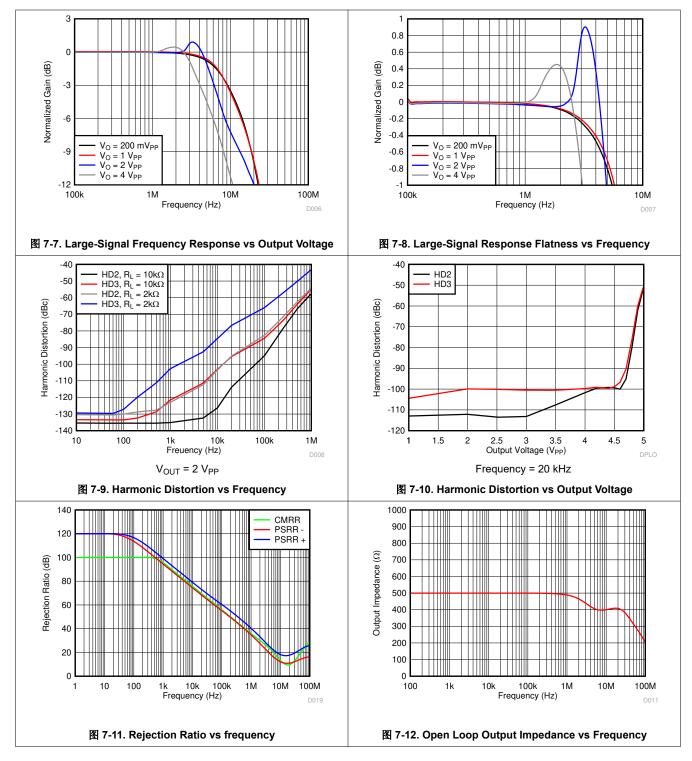

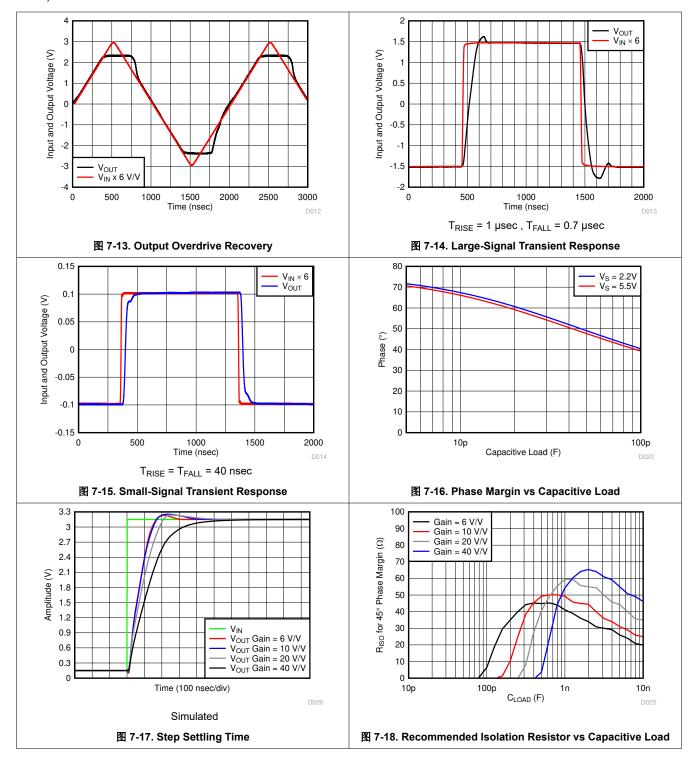

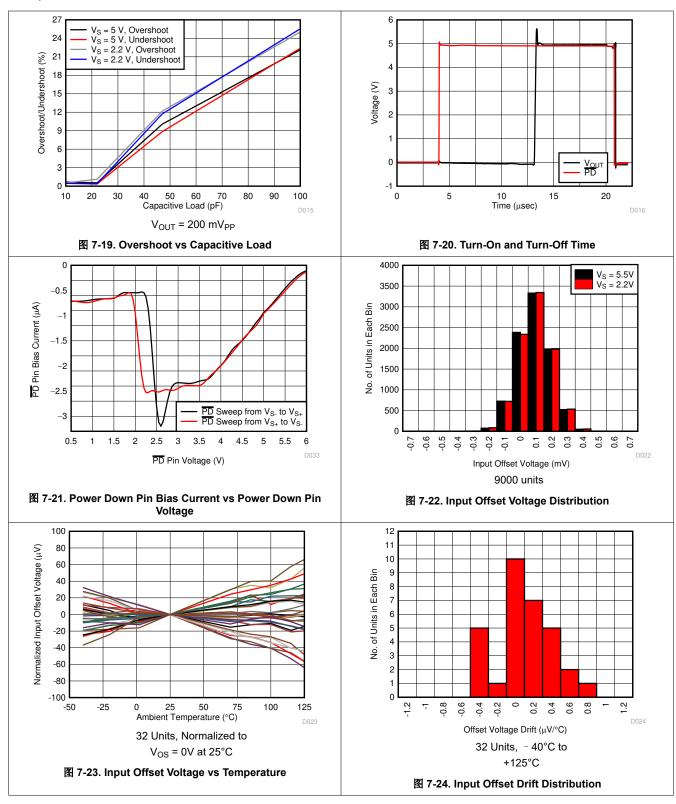

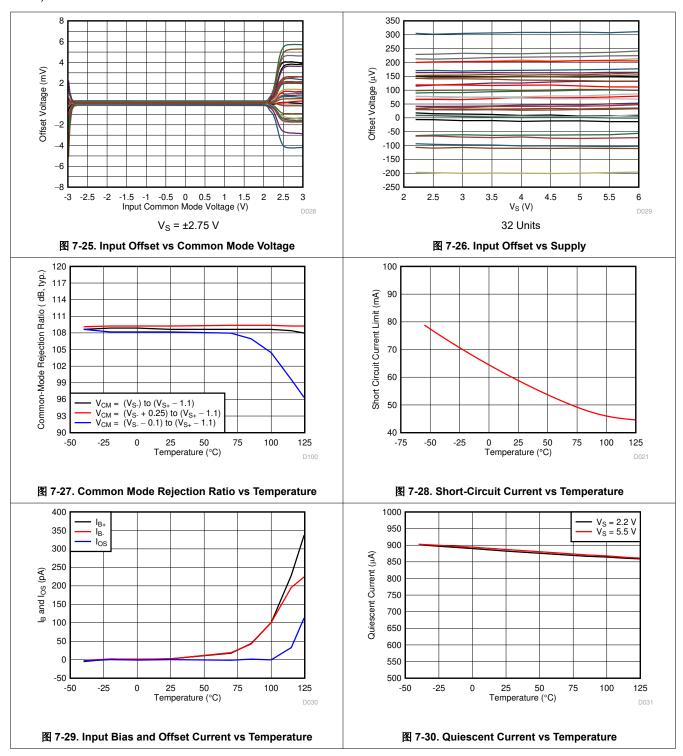

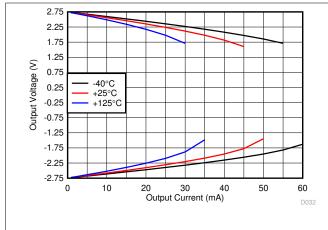

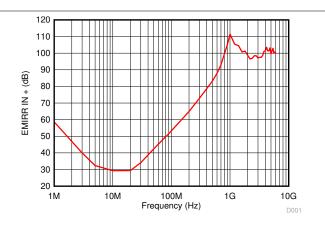

### 7.6 Typical Characteristics

At  $T_A$  = +25°C,  $V_S$  = 5.5 V,  $R_L$  = 10 k  $\Omega$  ,  $R_F$ = 5 k  $\Omega$  ,  $C_F$ = 2.5 pF,  $V_{CM}$  = midsupply - 0.5 V, G = 6 V/V (unless otherwise noted).

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

At  $T_A$  = +25°C,  $V_S$  = 5.5 V,  $R_L$  = 10 k  $\Omega$  ,  $R_F$ = 5 k  $\Omega$  ,  $C_F$ = 2.5 pF,  $V_{CM}$  = midsupply - 0.5 V, G = 6 V/V (unless otherwise noted).

图 7-31. Output Voltage vs Output Current Sourcing and Sinking

图 7-32. Electromagnetic Interference Rejection Ratio Referred to Noninverting Input (EMIRR+) vs Frequency

图 7-33. Crosstalk vs Frequency

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

### **8 Detailed Description**

### 8.1 Overview

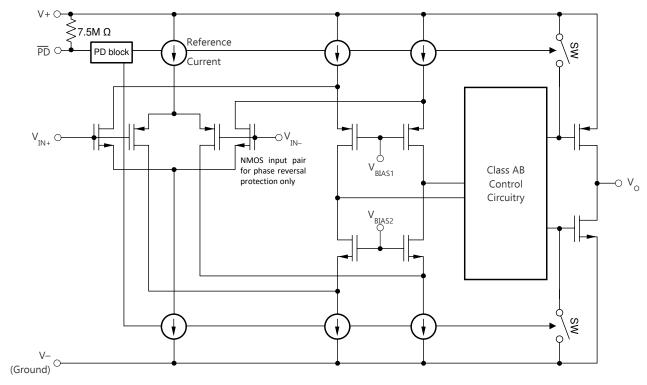

The OPAx607 devices are low-noise, rail-to-rail output (RRO) operational amplifiers (op amp). The devices operate from a supply voltage of 2.2 V to 5.5 V. The input common-mode voltage range also extends down to the negative rail allowing the OPAx607 to be used in most single-supply applications. Rail-to-rail output swing significantly increases dynamic range, especially in low-supply, voltage-range applications, which results in complete usage of the full-scale range of the consecutive analog-to-digital converters (ADCs). The decompensated architecture allows for a favorable tradeoff of low-quiescent current for a very-high gain-bandwidth product (GBW) and low-distortion performance in high-gain applications.

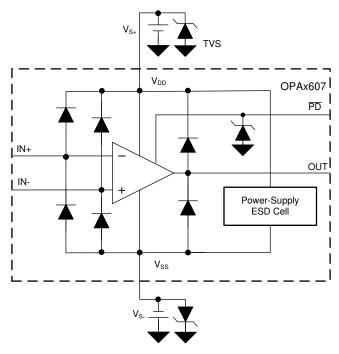

### 8.2 Functional Block Diagram

### 8.3 Feature Description

### 8.3.1 Operating Voltage

The OPAx607 operational amplifiers are fully specified and assured for operation from 2.2 V to 5.5 V, applicable from  $-40^{\circ}$ C to  $+125^{\circ}$ C. The OPAx607 devices are completely operational with asymmetric, symmetric and single supply voltages applied across the supply pins. The total voltage (that is,  $(V_{S+}) - (V_{S-})$ ) must be less than the supply voltage mentioned in  $^{\ddagger}$  7.1.

#### 8.3.2 Rail-to-Rail Output and Driving Capacitive Loads

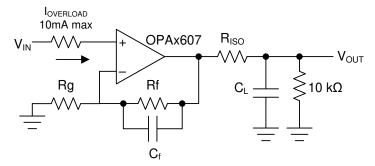

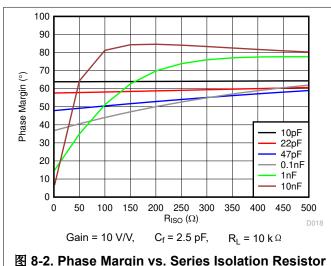

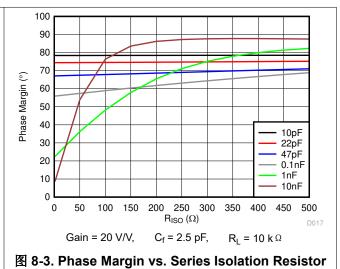

Designed as a low-power, low-voltage operational amplifier, the OPAx607 devices are capable of delivering a robust output drive. For resistive loads of 10 k  $\Omega$ , the output swings to within a few millivolts of either supply rail, regardless of the applied power-supply voltage. Different load conditions change the ability of the amplifier to swing close to the rails. The OPAx607 devices drive up to a nominal capacitive load of 47 pF on the output with no special consideration and without the need of a series isolation resistor  $R_{ISO}$  while still being able to achieve 45° of phase margin. When driving capacitive loads greater than 47 pF, TI recommends using  $R_{ISO}$  as shown in 8-1 in series with the output as close to the device as possible. Refer to 7-18 for looking up different values of 7-18 required for 7-18 to achieve 45° phase margin. Without 7-18 required for 7-18 for looking up different values of 7-18 required for 7-18 for looking up different values of 7-18 required for 7-18 for looking up different values of 7-18 required for 7-18 for looking up different values of 7-18 required for 7-18 for looking up different values of 7-18 required for 7-18 for looking up different values of 7-18 required for 7-18 for looking up different values of 7-18 required for 7-18 for looking up different values of 7-1

图 8-1. Input Current Protection and Driving Capacitive Loads

图 8-2 and 图 8-3 show the phase margin achieved with varying R<sub>ISO</sub> with different values of C<sub>L</sub>.

a o-z. Phase margin vs. Series isolation Resistor

#### 8.3.3 Input and ESD Protection

When the primary design goal is a linear amplifier with high CMRR, do not exceed the op amp input common-mode voltage range ( $V_{CM}$ ). This CMRR is used to set the common-mode input range specifications in  $\ddagger$  7.5. The typical  $V_{CM}$  specifications for the OPAx607 devices are from the negative rail to 1.1 V below the positive rail. Assuming the op amp is in linear operation, the voltage difference between the input pins is small (ideally 0 V) and the input common-mode voltage can be analyzed at either input pin; the other input pin is assumed to be at the same potential. The voltage at  $V_{IN+}$  is easy to evaluate. In a noninverting configuration ( $\blacksquare$  8-1) the input signal,  $V_{IN+}$ , must not exceed the  $V_{CM}$  rating. However, in an inverting amplifier configuration,  $V_{IN+}$  must be connected to the voltage within  $V_{CM}$ . The input signal applied at  $V_{IN-}$  can be any voltage, such that the output voltage swings with a headroom of 10 mV from either of the supply rails.

The input voltage limits have fixed headroom to the power rails and track the power-supply voltages. For single 5-V supply, the linear input voltage range is 0 V to 3.9 V and with a 2.2-V supply this range is 0 V to 1.1 V. The headroom to each power-supply rail is the same in either case: 0 V and 1.1 V. A weak NMOS input pair from  $V_{IN+}$  to  $V_{IN+}$  – 1.1 V ensures that an output phase reversal issue does not occur when the  $V_{CM}$  is violated.

图 8-4. Internal ESD Structure

The OPAx607 devices also incorporate internal electrostatic discharge (ESD) protection circuits on all pins. For the input and output pins, this protection primarily consists of current-steering diodes connected between the input and power-supply pins. These ESD protection diodes provides input overdrive protection, as long as the current is limited with a series resistor to 10 mA, as stated in 节 7.1. 图 8-1 shows a series input resistor can be added to the driven input to limit the input current.

### 8.3.4 Decompensated Architecture with Wide Gain-Bandwidth Product

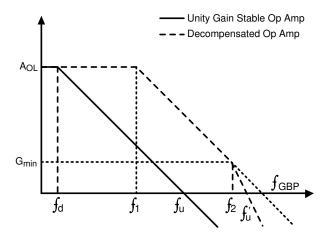

Amplifiers such as the OPAx607 devices are not unity-gain stable are referred to as decompensated amplifiers. The decompensated architecture typically allows for higher GBW, higher slew rate, and lower noise compared to a unity-gain stable amplifier with similar quiescent currents. The increased available bandwidth reduces the rise time and the settling time of the op amp, allowing for sampling at faster rates in an ADC-based signal chain.

As shown in 8-5, the dominant pole  $f_d$  is moved to the frequency  $f_1$  in the case of a decompensated op amp. The solid A<sub>OL</sub> plot is the open-loop gain plot of a traditional unity-gain stable op amp. The change in internal compensation in a decompensated amp such as the OPAx607, increase the bandwidth for the same amount of power. That is, the decompensated op amp has an increased bandwidth to power ratio when compared to a unity-gain stable op amp of equivalent architecture. Besides the advantages in the above mentioned parameters, an increased slew rate and a better distortion (HD2 and HD3) value is achieved because of the higher available loop-gain, compared to its unity-gain counterpart. The most important factor to consider is ensuring that the op amp is in a noise gain (NG) greater than G<sub>min</sub>. A value of NG lower than G<sub>min</sub> results in instability, as shown in 🗵 8-5, because the 1/ß curve intersects the A<sub>OL</sub> curve at 40 dB/decade. This method of analyzing stability is called the rate of closure method. See the precision lab training videos from TI for a better understanding on device stability and for different techniques of ensuring stability.

图 8-5. Gain vs Frequency Characteristics for a Unity-Gain Stable Op Amp and a Decompensated Op Amp

The OPAx607 devices are stable in a noise gain of 6 V/V (15.56 dB) or higher in conventional gain circuits; see 🛮 8-6. The device has 9 MHz of small-signal bandwidth (SSBW) in this gain configuration with approximately 65° of phase margin. The high GBW and low voltage noise of the OPAx607 devices make them suitable for general-purpose, high-gain applications.

Product Folder Links: OPA607 OPA2607

#### 8.4 Device Functional Modes

The OPAx607 devices have two functional modes: normal operating mode and Power Down (PD) mode.

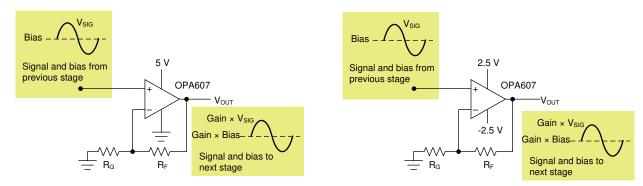

### 8.4.1 Normal Operating Mode

The OPAx607 devices are operational when the power-supply voltage is between 2.2 V ( $\pm 1.1$  V) and 5.5 V ( $\pm 2.75$  V). Most newer systems use a single power supply to improve efficiency and simplify the power tree design. The OPAx607 devices can be used with a single-supply power ( $V_{S-}$  connected to GND) with no change in performance from split supply, as long as the input and output pins are biased within the linear operating region of the device. The valid input and output voltage ranges are given in  $\dagger 7.5$ . The outputs nominally swing rail-to-rail with approximately 10-mV headroom required for linear operation. The inputs can typically swing up to the negative rail (typically ground) and to within 1.1 V from the positive supply.

图 8-6. Single-Supply and Dual-Supply Operation

#### 8.4.2 Power Down Mode

The OPAx607 devices feature a Power Down mode for power critical applications. Under logic control, the amplifier can be switched from normal operation (consuming  $\leq$  1 mA) to a Power Down current of less than 1  $\mu$ A. When the  $\overline{PD}$  pin is connected high, the amplifier is active. Connecting the  $\overline{PD}$  pin to logic low disables the amplifier and places the output in a high-impedance state. The output of an op amp is high impedance similar to a tri-state high-impedance gate under a Power Down condition; however, the feedback network behaves as a parallel load.

If the Power Down mode is not used, connect  $\overline{PD}$  to the positive supply pin or leave floating. See the *Power Down (Device Enabled When Floating)* section in  $\overline{T}$  7.5 table for the enable and disable threshold voltages. The  $\overline{PD}$  pin can be left floating to keep the op amp always enabled, which is primarily possible because of the presence of an internal pullup resistor within the op amp that, by default, always keeps the  $\overline{PD}$  pin weakly tied to  $V_{S+}$ . However it is also acceptable to strengthen the pull up from the  $\overline{PD}$  pin by connecting a low value resistance from the  $\overline{PD}$  pin to  $V_{S+}$ . This helps make the part less susceptible to noise and transient pick up on the  $\overline{PD}$  pin. Looking at the  $\overline{PD}$  pin bias current in  $\overline{R}$  7-21 can help us get an accurate understanding of the voltage required to be applied on the  $\overline{PD}$  pin for enabling and powering down. Note: the hysteresis present in  $\overline{R}$  7-21 help with single shot power up and power down of OPAx607 devices.

The  $\overline{PD}$  pin exhibits a special type of ESD protection which allows users to apply any voltage between  $V_{S-}$  to 6 V irrespective of the voltage at the  $V_{S+}$ . Special ESD structure at the  $\overline{PD}$  pin helps in relaxing the requirements on power sequencing during power up and power down condition. Refer to 8.4 for details of the internal ESD structure. The absolute voltage limits applicable on  $\overline{PD}$  pin can be found in 7.1 table. Another key care about in PD condition is to ensure the IN+ and IN - are not exposed to a high differential voltage continuously. In a power up condition the op-amp's loop gain ensure the IN+ pin and the IN - track each other closely. However in PD condition the op-amp is inactive and IN - will be usually weakly tied to GND through the  $R_G$  resistor. Exposing the IN+ pin continuously to a high voltage in such a condition will result in irreversible offset voltage  $V_{OS}$  shift.

Copyright © 2021 Texas Instruments Incorporated

### 9 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

### 9.1 Application Information

The OPAx607 devices feature a 50-MHz GBW with 900  $\mu$ A of supply current, providing good AC performance at low-power consumption. The low input noise voltage of 3.8 nV/  $\sqrt{\text{Hz}}$ , the approximate pA of bias current, and a typical input offset voltage of 0.1 mV make the device very suitable for both AC and DC applications.

### 9.2 Typical Applications

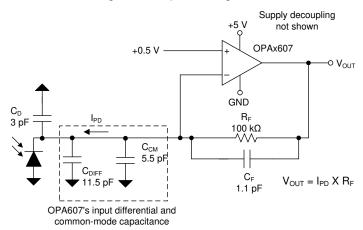

### 9.2.1 100-k $\Omega$ Gain Transimpedance Design

The high GBW and low input voltage and current noise for the OPAx607 devices make it an excellent wideband transimpedance amplifier for moderate to high transimpedance gains.

图 9-1. Wideband, High-Sensitivity, Transimpedance Amplifier

#### 9.2.1.1 Design Requirements

Design a high-bandwidth, high-transimpedance-gain amplifier with the design requirements shown in 表 9-1.

表 9-1. Design Requirements

| TARGET BANDWIDTH (MHz) | TRANSIMPEDANCE-GAIN (kΩ) | PHOTODIODE CAPACITANCE (pF) |

|------------------------|--------------------------|-----------------------------|

| 2                      | 100                      | 3                           |

Submit Document Feedback

#### 9.2.1.2 Detailed Design Procedure

Designs that require high bandwidth from a large area detector with relatively high transimpedance-gain benefit from the low input voltage noise of the OPAx607 devices. Use the Excel<sup>™</sup> calculator available at *What You Need To Know About Transimpedance Amplifiers* – *Part 1* to help with the component selection based on total input capacitance and  $C_{TOT}$ .  $C_{TOT}$  is referred as  $C_{IN}$  in the calculator.  $C_{TOT}$  is the sum of  $C_D$ ,  $C_{DIFF}$ , and  $C_{CM}$  which is 20 pF. Using this value of  $C_{TOT}$ , and the targeted closed-loop bandwidth (f - 3dB) of 2 MHz and transimpedance gain of 100 k  $\Omega$  results in amplifier GBW of approximately 50 MHz and a feedback capacitance ( $C_F$ ) of 1.1 pF as shown in  $\Omega$  9-2. These results are for a Butterworth response with a  $\Omega$  = 0.707 and a phase margin of approximately 65° which corresponds to 4.3% overshoot.

| <u>Calculator II</u>                           |        |             |

|------------------------------------------------|--------|-------------|

| Closed-loop TIA Bandwidth (f <sub>-3dB</sub> ) | 2.00   | MHz         |

| Feedback Resistance (R <sub>F</sub> )          | 100.00 | <u>kOhm</u> |

| Input Capacitance (C <sub>IN</sub> )           | 20.00  | <u>pF</u>   |

| Opamp Gain Bandwidth Product (GBP)             | 50.27  | MHz         |

| Feedback Capacitance (C <sub>F</sub> )         | 1.110  | <u>pF</u>   |

图 9-2. Results of Inputting Design Parameters in the TIA Calculator

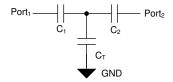

The OPA607's 50 MHz GBW, is suitable for the above design requirements. If the required feedback capacitance  $C_F$  comes out to be a very low value capacitor to be practically achievable, a T-Network capacitor circuit as shown below can be used. A very low capacitor value ( $C_{EQ}$ ) can be achieved between Port<sub>1</sub> and Port<sub>2</sub> using standard value capacitors in a T-Network circuit as shown in  $\boxed{\$}$  9-3.

$$C_{EQ} = \frac{C_1 \times C_2}{C_1 + C_2 + C_T}$$

(1)

图 9-3. T-Network

### 9.2.1.3 Application Curves

#### 9.2.2 Noninverting Gain of 3 V/V

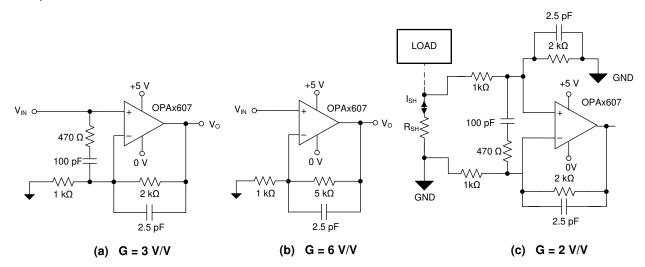

The OPAx607 devices are normally stable in noise gain configurations (see SBOA066) of greater than 6 V/V when conventional feedback networks are used, which is discussed in 节 8.3.4. The OPAx607 devices can be configured in noise gains of less than 6 V/V by using capacitors in the feedback path and between the inputs to maintain the desired gain at lower frequencies and increase the gain greater that 6 V/V at higher frequencies such that the amplifier is stable. Configuration (a) in 图 9-6 shows OPAx607 devices configured in a gain of 3 V/V by using capacitors and resistors to shape the noise gain and achieve a phase margin of approximately 56° that is very close to the phase margin achieved for the conventional 6 V/V configuration (b) in 图 9-6.

The key benefit of using a decompensated amplifier (such as the OPAx607) below the minimum stable gain, is that it takes advantage of the low noise and low distortion performance at quiescent powers smaller than comparable unity-gain stable architectures. By reducing the 100-pF input capacitor, higher closed-loop bandwidth can be achieved at the expense of increased peaking and reduced phase margin. Ensure that low parasitic capacitance layout techniques on the IN – pin are as small as 1 pF to 2 pF of parasitic capacitance on the inverting input, which will require tweaking the noise-shaping component values to get a flat frequency response and the desired phase margin. Configurations in 9-6 does not take into account this parasitic capacitance but it must be considered for practical purposes. Details on the benefits of decompensated architectures are discussed in *Using a decompensated op amp for improved performance*. The *one-capacitor*, *externally compensated type* method is used for noise gain shaping in the below circuit.

In a difference amplifier circuit, typically used for low side current sensing applications, the (noise gain) = (signal gain + 1).

图 9-6. Noninverting Gain of 3 V/V, 6 V/V Configurations and Difference Amplifier in Signal Gain of 2 V/V

### 9.2.3 High-Input Impedance (Hi-Z), High-Gain Signal Front-End

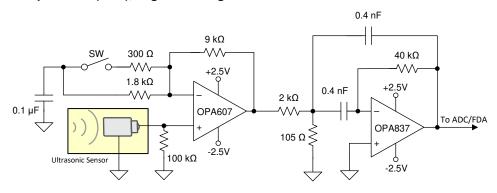

图 9-9. Hi-Z, High-Gain Front-End Circuit

### 9.2.3.1 Design Requirements

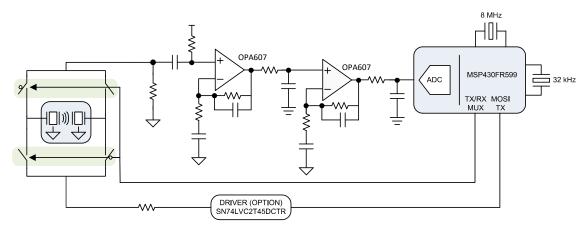

The objective is to design a high-input impedance, high-dynamic range, signal-conditioning front-end. An example application for such a front-end circuit is the receive signal chain in an ultrasonic-based end equipment (EE) such as fish finders, printers and flow meters. 表 9-2 lists the design requirements for this application.

表 9-2. Design Parameters

| PARAMETER                | DESIGN REQUIREMENT |  |  |  |  |

|--------------------------|--------------------|--|--|--|--|

| Amplifier supply         | ±2.5 V             |  |  |  |  |

| Input signal frequency   | 200 kHz            |  |  |  |  |

| Minimum voltage          | 300 μVrms          |  |  |  |  |

| Minimum SNR at 300 μVrms | 40 dB              |  |  |  |  |

#### 9.2.3.2 Detailed Design Procedure

To achieve a SNR of greater than 40 dB for signals from 300 uVrms to 30 mV the front-end stage has two gain settings: 6 V/V and 31 V/V. The SW (switch, relay, or analog mux) can be dynamically toggled to ensure maximum sensitively to the receiving signal. The OPAx607 devices prove to be an attractive solution for this front-end signal chain because of the right balance of low noise and high input impedance. The ultrasonic sensors (Ex. piezo crystal) have high output impedance. The OPAx607 devices have an input bias current of 20 pA (maximum). This small bias current results in reduced distortion and signal loss across the source impedance when compared with a bipolar amplifier with input bias currents in the range of a few hundreds of nano-amperes. The OPAx607's high-gain front-end is followed by a narrowband band-pass filter that is tuned to a 200-kHz center frequency. The narrowband filter is designed using the OPA837. OPA837 can be used as a variable gain mux / PGA as shown in TIDA-01565. In this application section the OPA837-based band-pass filter was designed using the techniques mentioned in the *Filter Design in Thirty Seconds* application report.

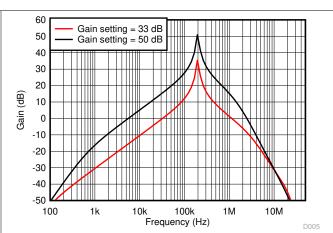

§ 9-11 shows the frequency response of circuit in

§ 9-9. As shown in

§ 9-11, the frequency response is a high-Q factor band-pass filter centered around 200 kHz. Designing such a high-Q band-pass filter helps eliminate white band noise along with other interferences present in the circuitry, resulting in a high SNR signal chain. The OPAx607's front-end combined with the OPA837-based band-pass filter help to achieve a total gain of 33 dB (44 V/V) or 50 dB (316 V/V) based on the SW (switch) position.

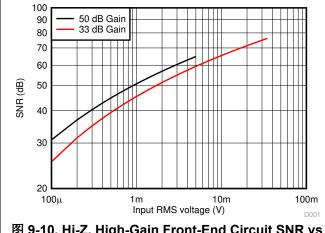

### 9.2.3.3 Application Curves

图 9-10. Hi-Z, High-Gain Front-End Circuit SNR vs Input

图 9-11. Hi-Z, High-Gain Front-End Circuit Gain vs Frequency

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

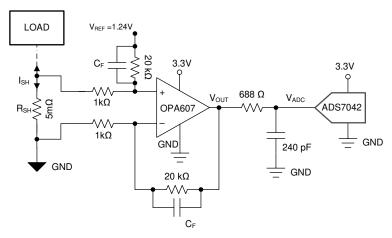

### 9.2.4 Low-Cost, Low Side, High-Speed Current Sensing

图 9-12. Low Side Current Sensing

#### 9.2.4.1 Design Requirements

The objective is to design a high-speed, high-gain bidirectional current-sensing circuit for power systems and motor drive systems. † 9.2.4.2 lists the design requirements of this application.

表 9-3. Design Parameters

| PARAMETER                                       | DESIGN REQUIREMENT |  |  |  |

|-------------------------------------------------|--------------------|--|--|--|

| Amplifier and ADC supply                        | 3.3 V              |  |  |  |

| Peak current to be measured from load to ground | 20 A               |  |  |  |

| Peak current to be measured from ground to load | 12 A               |  |  |  |

| Required Accuracy of current measurement        | 0.1%               |  |  |  |

| Signal-Setting time at ADC input                | < 1 µs             |  |  |  |

| Current sensing direction                       | Bidirectional      |  |  |  |

### 9.2.4.2 Detailed Design Procedure

The aim of this application section is to measure bidirectional current with relatively high accuracy in a low-side-sensing-based, high-frequency switching system.

As shown in 🖺 9-12, a single op amp of high bandwidth is capable of sensing current in a high gain configuration as well as have the required effective bandwidth to drive the consecutive SAR ADC input. The SAR ADC can be a standalone ADC or integrated inside a Micro-controller.

$$V_{OUT} = (20 \text{ k}\Omega / 1 \text{ k}\Omega \times V_{DIFF}) + V_{REF}, \text{ where } V_{DIFF} = I_{SH} \times R_{SH}$$

(2)

The reference voltage is 1.24 V. When the  $I_{SH}$  flowing across  $R_{SH}$  equals zero, the  $V_{OUT}$  of the difference amplifier sits ideal at 1.24 V.

When the current ( $I_{SH}$ ) flows from LOAD to GND, the output of the OPAx607 increase above 1.24 V with a value equal to 20 ×  $V_{SH}$  and when the current flows from GND to LOAD (in the opposite direction) the output of the OPAx607 decrease below 1.24 V with a value proportional to 20 ×  $V_{SH}$ .

One of the main challenges in a high speed current sensing design is to choose an op amp of with sufficient GBW that can drive a SAR ADC, while still being able to gain the signal by the required amount. The 0.1% and 0.01% settling of OPAx607 can found in 7.5. Another key care about is to ensure the op amp output rises in less than 1  $\mu$ s so as to feed the output to a comparator for short-circuit protection. This comparator based short circuit protection loop is extremely fast and enables to turn off the switching devices very quickly. This requirement makes a low cost high speed part like the OPAx607 very desirable in a current-sensing circuit. Equation of the rise time as a function of bandwidth is shown below.

$t_R$  (10% to 90%) = 0.35 Hz / BW

(3)

For an ADC like ADS7042 running at a sampling rate of 500 kSPS of a clock of 12.5 MHz, the effective bandwidth of the op amp required to drive such an ADC is approximately 2.7 MHz. See the TI precision lab videos on driving SAR ADCs to understand the underlying calculation. The OPAx607 has a GBW of 50 MHz. With a gain of 20 V/V, the closed loop bandwidth turns out to approximately 2.5 MHz, making this device the most suitable, cost-optimized amplifier for this application. The RC charge bucket (240  $\Omega$  and 688 pF in  $\Omega$  9-12) designed at the input of the SAR ADC is derived from the calculations provided in the SAR ADC precision lab videos. The fundamental concept behind the design of this charge bucket filter is to ensure that the sample and hold capacitor is charged to the required final voltage within the acquisition window of the ADC.

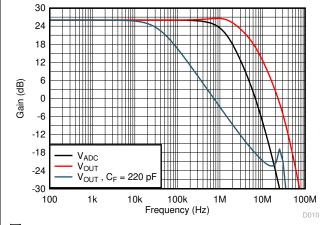

As shown in  $\[ \]$  9-14, a DC accuracy of higher than 0.05% is achieved with the OPAx607. The simulations are captured with and without voltage offset calibration. Frequency response shown in  $\[ \]$  9-13 indicate different signal bandwidth at  $V_{OUT}$ ,  $V_{ADC}$  and with and without  $C_F$  of 220 pF.

### 9.2.4.3 Application Curves

5.2 0.16 4.4 0.12 3 6 0.08 0.04 2.8 2 0 1.2 -0.04 -0.08 0.4 Measured Output -0.4 -0.12 Ideal Output % Error w/o callibration -1.2 -0.16 % Error with callibration -0.2 -15 5 10 15 30 Current across R<sub>SH</sub> (A)

图 9-13. Frequency Response of Low Side Current Sensing

图 9-14. DC Current-Sense Transfer Function

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

#### 9.2.5 Ultrasonic Flow Meters

图 9-15. High-Gain Ultrasonic Front-End

#### 9.2.5.1 Design Requirements

The OPAx607 devices have a wide operating voltage range of 2.2 V to 5.5 V with a maximum quiescent current of 1 mA. The availability of the inbuilt shutdown function enables designers to power cycle the front-end signal chain, reducing the net quiescent current even further. The minimum operating voltage range of 2.2 V proves to be very suitable for battery-powered and power sensitive applications such as the ultrasonic-based flow meters. The high GBW of the OPAx607 devices enable the gain stages and the ADC drive stages to be designed and combined, thereby reducing component count. A schematic similar to that of 89-12 can be used in ultrasonic flow meters for the front-end signal chain.

The *Ultrasonic sensing subsystem reference design for gas flow measurement* design guide has a detailed design procedure for ultrasonic-based sensing for gas flow measurement. The OPAx607 devices are very suitable op amps for the discrete front-end design described in this design guide.

### 10 Power Supply Recommendations

The OPAx607 devices are specified for operation from 2.2 V to 5.5 V ( $\pm 1.1$  V to  $\pm 2.75$  V), applicable from  $-40^{\circ}$ C to  $\pm 125^{\circ}$ C. Place 0.1- $\mu$ F bypass capacitors close to the power-supply pins to reduce errors coupling in from noisy or high-impedance power supplies.

#### **CAUTION**

Supply voltages larger than 6 V can permanently damage the device (see † 7.1).

For more detailed information on bypass capacitor placement, see #11.1.

### 11 Layout

### 11.1 Layout Guidelines

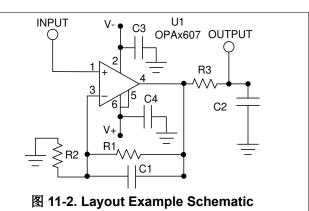

For best operational performance of the device, use good printed circuit board (PCB) layout practices, including:

- Noise can propagate into analog circuitry through the power-supply pins of the circuit as a whole and of the

operational amplifier. Bypass capacitors are used to reduce the coupled noise by providing low-impedance

power sources local to the analog circuitry.

- Connect low-equivalent series resistance (ESR), 0.1-µF ceramic bypass capacitors between each supply pin and ground, placed as close to the device as possible. A single bypass capacitor from V+ to ground is applicable for single-supply applications.

- Separate grounding for analog and digital portions of the circuitry is one of the simplest and most effective methods of noise suppression. One or more layers on multilayer PCBs are usually devoted to ground planes. A ground plane helps distribute heat and reduces electromagnetic interference (EMI) noise pickup. Make sure to physically separate digital and analog grounds, paying attention to the flow of the ground current.

- To reduce parasitic coupling, run the input traces as far away from the supply or output traces as possible. If these traces cannot be kept separate, crossing the sensitive trace perpendicularly is much better than crossing in parallel with the noisy trace.

- Place the external components as close to the device as possible. Keeping R<sub>F</sub> and R<sub>G</sub> close to the inverting input minimizes parasitic capacitance; see

11-1 and

11-2.

- Keep the length of input traces as short as possible. Always remember that the input traces are the most sensitive part of the circuit.

- Consider a driven, low-impedance guard ring around the critical traces. A guard ring can significantly reduce leakage currents from nearby traces that are at different potentials.

### 11.2 Layout Examples

图 11-1. Operational Amplifier Board Layout for a Noninverting Configuration

Submit Document Feedback

## 12 Device and Documentation Support

### 12.1 Device Support

### 12.1.1 Development Support

Texas Instruments, precision lab videos

#### **12.2 Documentation Support**

#### 12.2.1 Related Documentation

For related documentation see the following:

- Texas Instruments, OPA2834 50-MHz, 170- μA, Negative-Rail In, Rail-to-Rail Out, Voltage-Feedback Amplifier data sheet

- Texas Instruments, ADS7042 Ultra-Low Power, Ultra-Small Size, 12-Bit, 1-MSPS, SAR ADC data sheet

- Texas Instruments, Ultrasonic Sensing Subsystem Reference Design For Gas Flow Measurement design guide

- Texas Instruments, OPAx836 Very-Low-Power, Rail-to-Rail Out, Negative Rail In, Voltage-Feedback Operational Amplifiers data sheet

- Texas Instruments, Filter Design in Thirty Seconds application report

#### 12.3 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to order now.

### 12.4 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 12.5 支持资源

TI E2E™ 支持论坛是工程师的重要参考资料,可直接从专家获得快速、经过验证的解答和设计帮助。搜索现有解答或提出自己的问题可获得所需的快速设计帮助。

链接的内容由各个贡献者"按原样"提供。这些内容并不构成 TI 技术规范,并且不一定反映 TI 的观点;请参阅 TI 的《使用条款》。

#### 12.6 Trademarks

Excel<sup>™</sup> is a trademark of Microsoft Coproration.

TI E2E™ is a trademark of Texas Instruments.

所有商标均为其各自所有者的财产。

### 12.7 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### 12.8 Glossary

TI Glossary This glossary lists and explains terms, acronyms, and definitions.

### 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

### 重要声明和免责声明

TI 提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保或其他要求。这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款 (https://www.ti.com/legal/termsofsale.html) 或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021,德州仪器 (TI) 公司 www.ti.com 9-Jul-2024

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| OPA2607IDGKR     | ACTIVE | VSSOP        | DGK                | 8    | 2500           | RoHS & Green | (6)<br>NIPDAU                 | Level-1-260C-UNLIM  | -40 to 125   | 2FRT                    | Samples |

| OPA2607IDR       | ACTIVE | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | OP2607                  | Samples |

| OPA2607SIRUGR    | ACTIVE | X2QFN        | RUG                | 10   | 3000           | RoHS & Green | NIPDAUAG                      | Level-2-260C-1 YEAR | -40 to 125   | KJF                     | Samples |

| OPA607IDBVR      | ACTIVE | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU   SN                   | Level-1-260C-UNLIM  | -40 to 125   | O6BV                    | Samples |

| OPA607IDBVT      | ACTIVE | SOT-23       | DBV                | 5    | 250            | RoHS & Green | NIPDAU   SN                   | Level-1-260C-UNLIM  | -40 to 125   | O6BV                    | Samples |

| OPA607IDCKR      | ACTIVE | SC70         | DCK                | 6    | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | 1G4                     | Samples |

| OPA607IDCKT      | ACTIVE | SC70         | DCK                | 6    | 250            | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | 1G4                     | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 9-Jul-2024

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF OPA2607, OPA607:

Automotive: OPA2607-Q1, OPA607-Q1

NOTE: Qualified Version Definitions:

Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 10-Jan-2024

### TAPE AND REEL INFORMATION

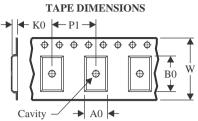

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

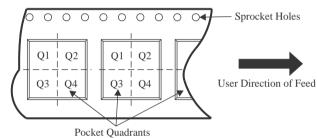

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| OPA2607IDGKR  | VSSOP           | DGK                | 8  | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| OPA2607IDR    | SOIC            | D                  | 8  | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| OPA2607SIRUGR | X2QFN           | RUG                | 10 | 3000 | 178.0                    | 8.4                      | 1.75       | 2.25       | 0.56       | 4.0        | 8.0       | Q1               |

| OPA607IDBVR   | SOT-23          | DBV                | 5  | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| OPA607IDBVT   | SOT-23          | DBV                | 5  | 250  | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| OPA607IDCKR   | SC70            | DCK                | 6  | 3000 | 180.0                    | 8.4                      | 2.47       | 2.3        | 1.25       | 4.0        | 8.0       | Q3               |

| OPA607IDCKT   | SC70            | DCK                | 6  | 250  | 180.0                    | 8.4                      | 2.47       | 2.3        | 1.25       | 4.0        | 8.0       | Q3               |

www.ti.com 10-Jan-2024

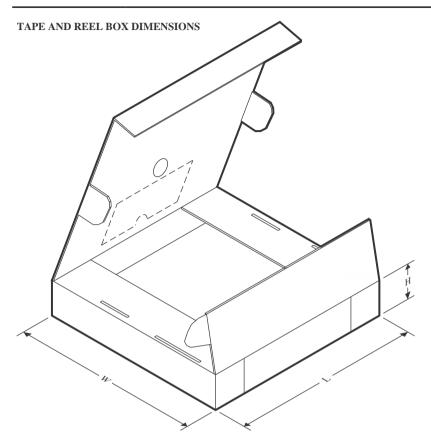

### \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| OPA2607IDGKR  | VSSOP        | DGK             | 8    | 2500 | 366.0       | 364.0      | 50.0        |

| OPA2607IDR    | SOIC         | D               | 8    | 2500 | 356.0       | 356.0      | 35.0        |

| OPA2607SIRUGR | X2QFN        | RUG             | 10   | 3000 | 205.0       | 200.0      | 33.0        |

| OPA607IDBVR   | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| OPA607IDBVT   | SOT-23       | DBV             | 5    | 250  | 210.0       | 185.0      | 35.0        |

| OPA607IDCKR   | SC70         | DCK             | 6    | 3000 | 213.0       | 191.0      | 35.0        |

| OPA607IDCKT   | SC70         | DCK             | 6    | 250  | 213.0       | 191.0      | 35.0        |

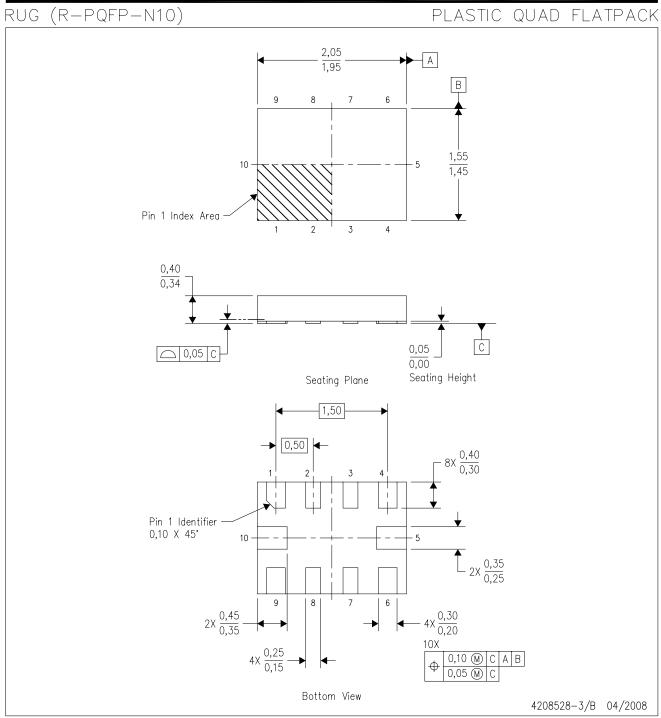

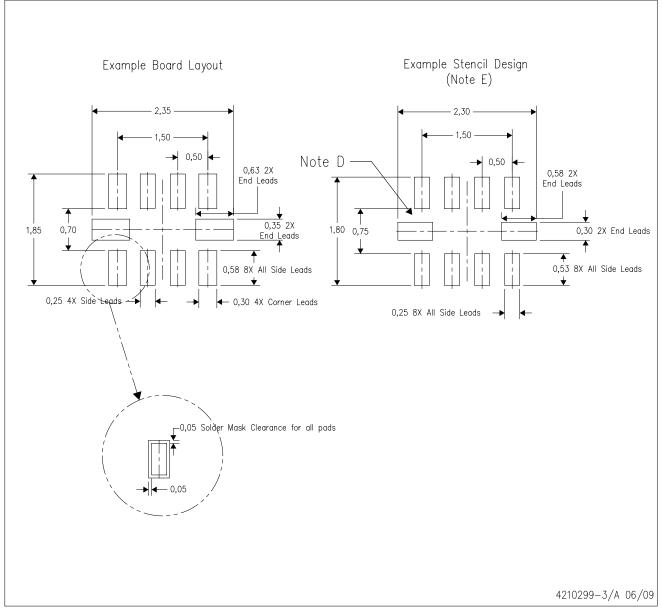

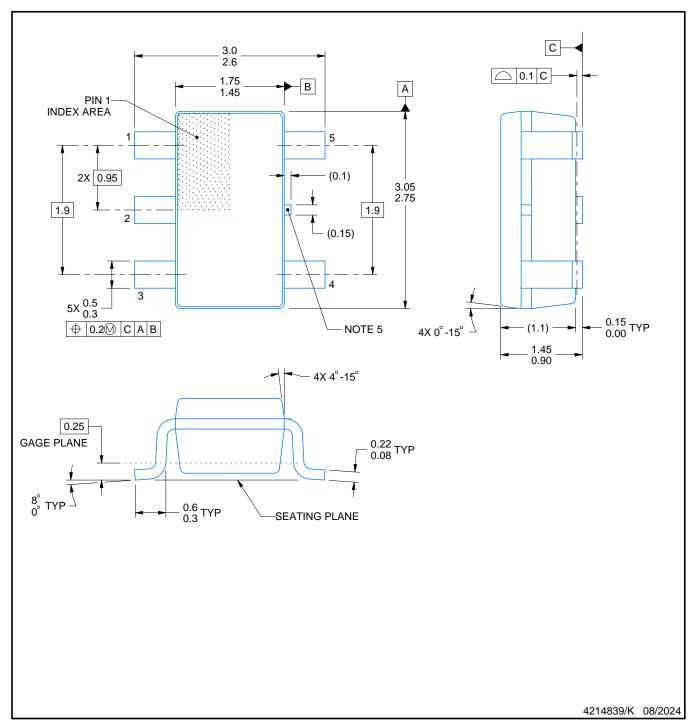

NOTES: All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

C. QFN (Quad Flatpack No-Lead) package configuration.

D. This package complies to JEDEC MO-288 variation X2EFD.

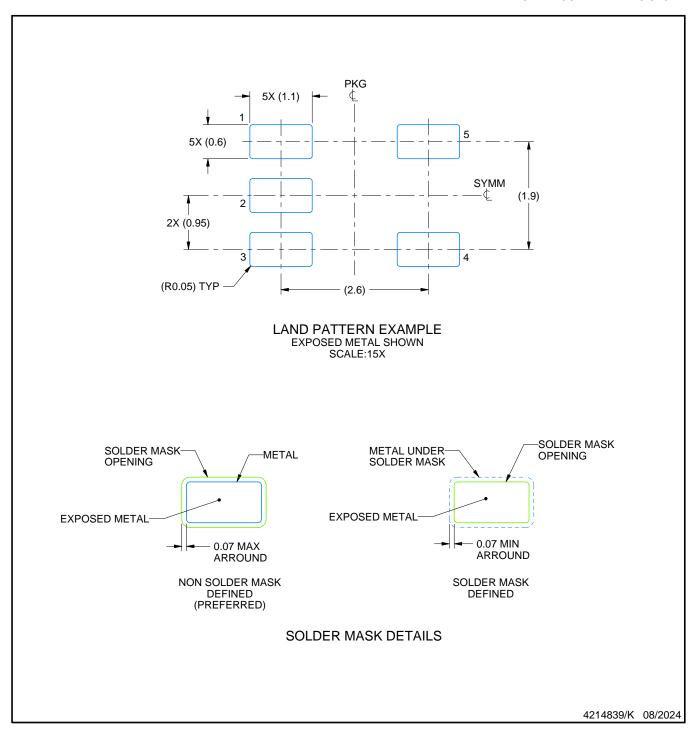

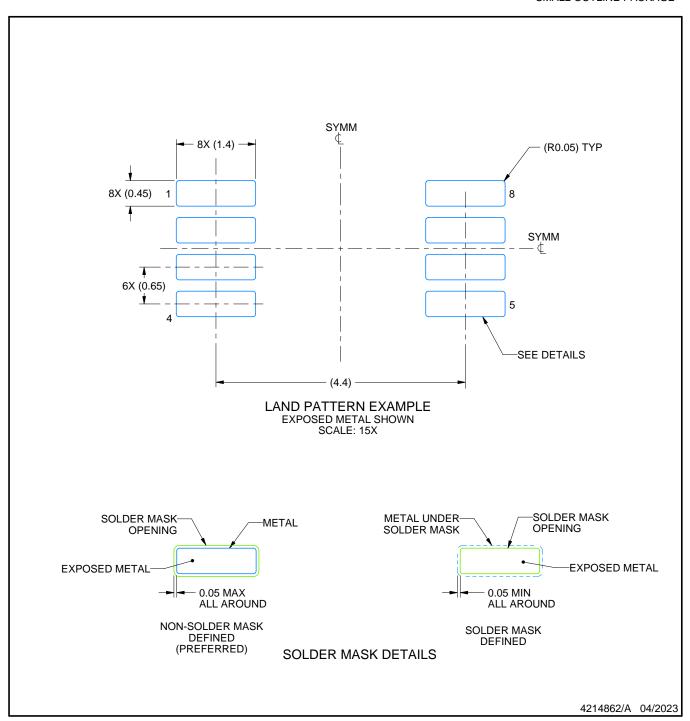

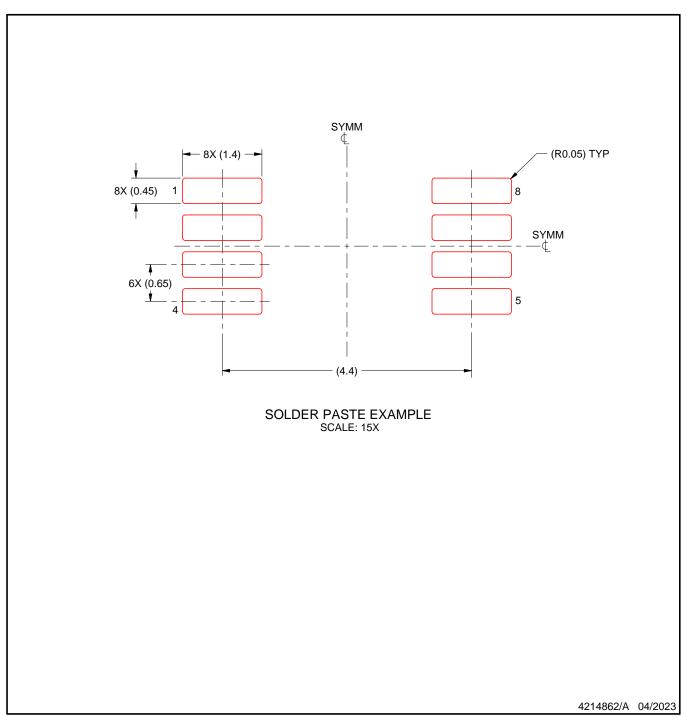

# RUG (R-PQFP-N10)

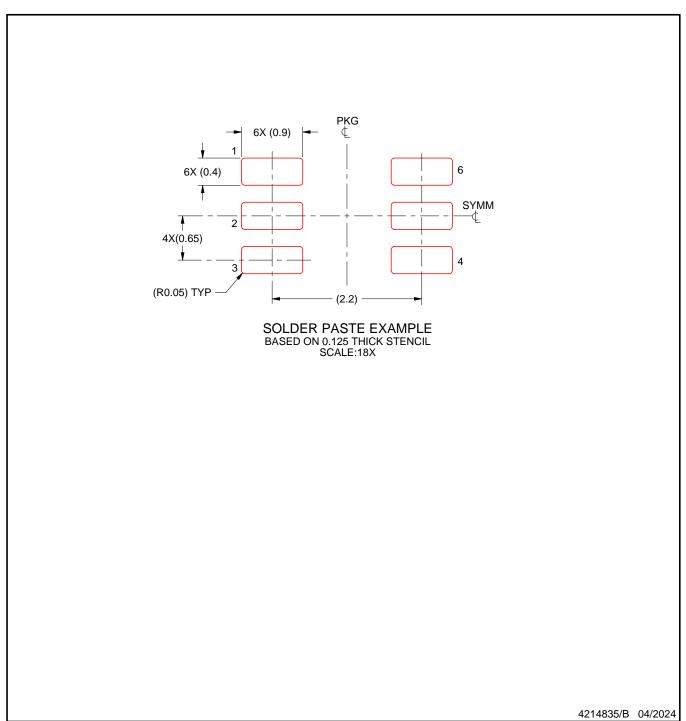

- NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Customers should contact their board fabrication site for minimum solder mask web tolerances between signal pads.

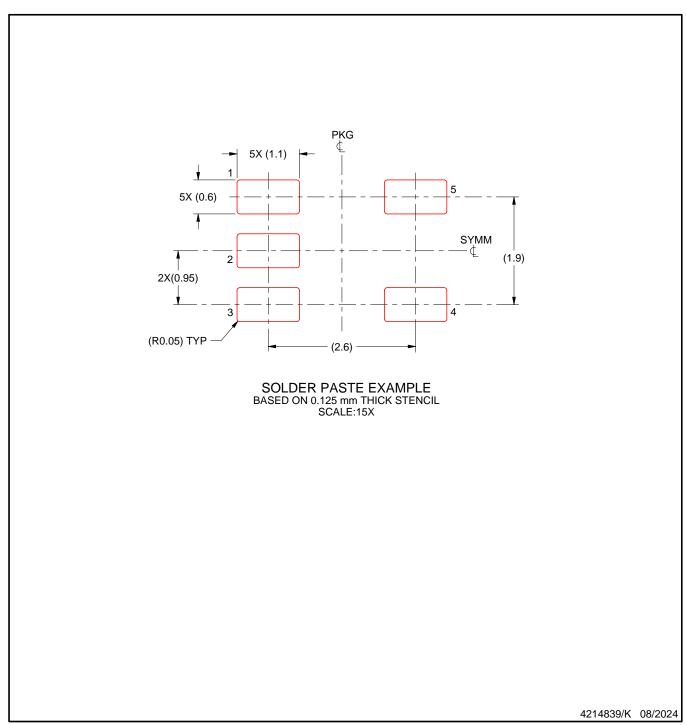

- E. Maximum stencil thickness 0,127 mm (5 mils). All linear dimensions are in millimeters.

- F. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- G. Side aperture dimensions over-print land for acceptable area ratio > 0.66. Customer may reduce side aperture dimensions if stencil manufacturing process allows for sufficient release at smaller opening.

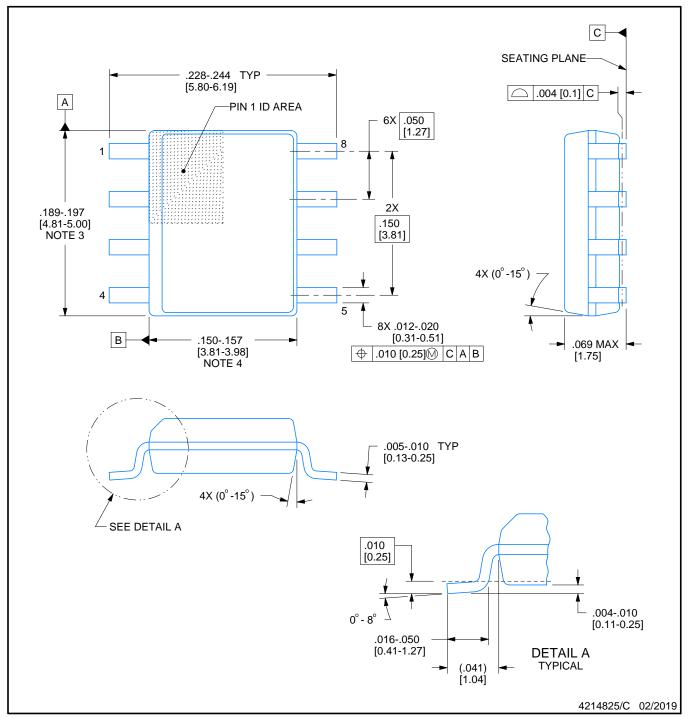

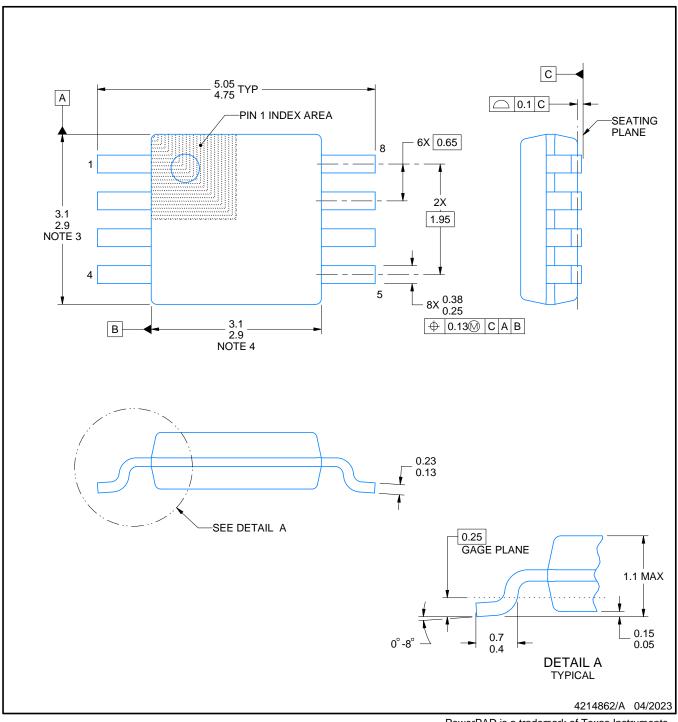

SMALL OUTLINE INTEGRATED CIRCUIT

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

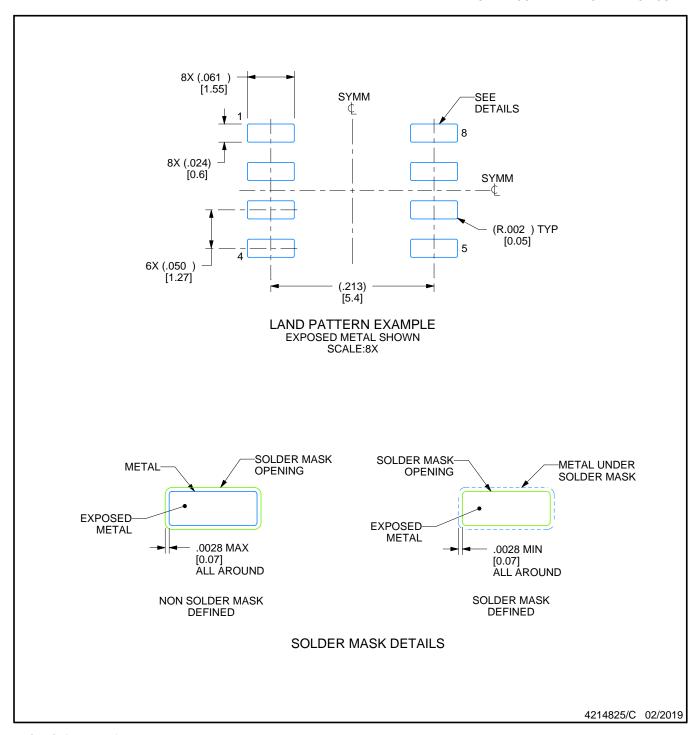

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

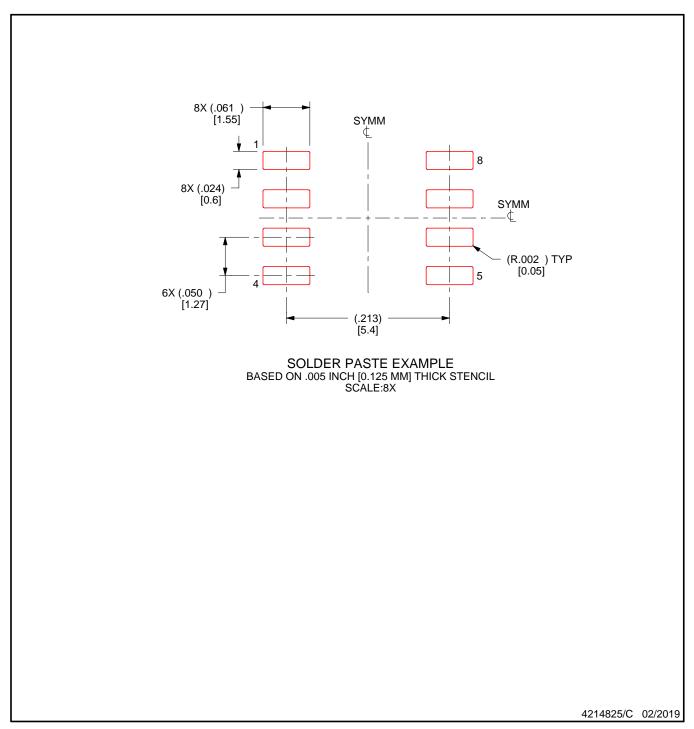

SMALL OUTLINE INTEGRATED CIRCUIT

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

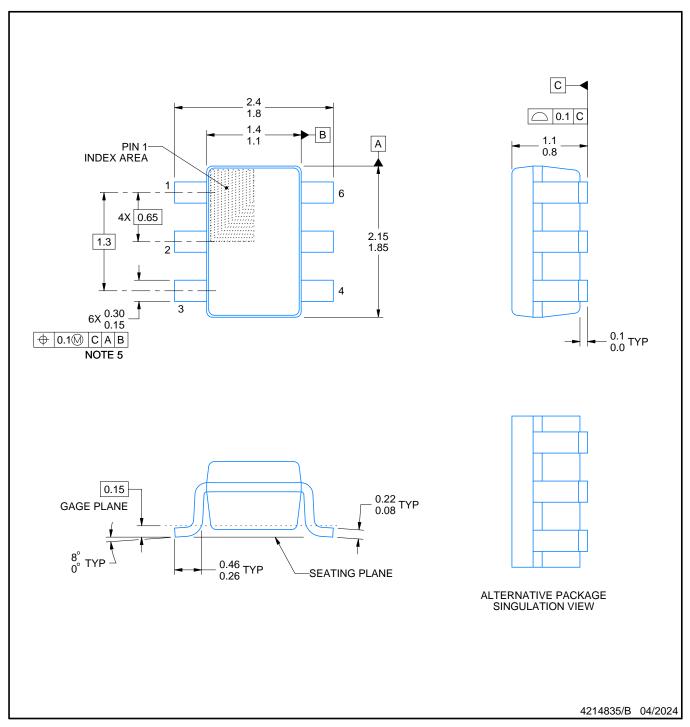

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Reference JEDEC MO-178.

- 4. Body dimensions do not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.25 mm per side.

- 5. Support pin may differ or may not be present.

NOTES: (continued)

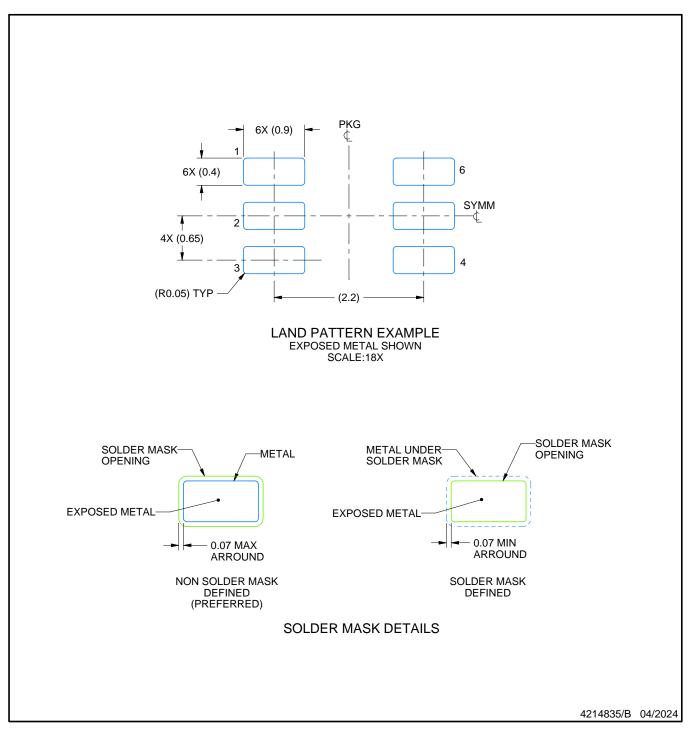

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.