ZHCSAW8B - APRIL 2012 - REVISED MARCH 2013

## LMV601/LMV602/LMV604 1MHz, 低功耗通用, 2.7V 运算放大器

查询样品: LMV601, LMV602, LMV604

### 特性

- (典型 2.7V 电源值;除非另外注明)

- 2.7V 和 5V 技术规格

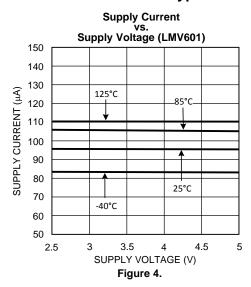

- 电源电流(每个放大器)100μA

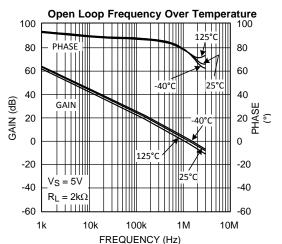

- 增益带宽产品 1.0MHz

- 关断电流 (LMV601) 45pA

- 从关断中的接通时间 (LMV601) 5µs

- 内部偏置电流 20fA

### 应用范围

- 无绳/蜂窝电话

- 笔记本电脑

- 掌上电脑 (PDA)

- PCMCIA 卡/音频

- 便携式/电池供电类设备

- 电源电流监控

- 电池监控

- 缓冲器

- 滤波器

- 驱动器

## 说明

LMV601/LMV602/LMV604 是单路、双路和四路低 压、低功率运算放大器。 它们专门针对低压通用应用 而设计。 其它重要产品特性是低输入偏置电流、轨到 轨输出和宽温度范围。 LMV601/LMV602/LMV604 在 10KHz, 1MHz GBW, 1.0V/us 转换率和 0.25mV Vos 时的电压噪声为 29nV。 LMV601/2/4 可由一个低至 2.7V 的单个电源电压供电运行,同时汲取的静态电流 为 100uA (典型值)。 在关断模式中,此电流可被减 至 45pA。

-40°C 至 125°C 的工业增强型温度范围使得 LMV601/LMV602/LMV604 能够适应广泛的广泛环境 应用。

LMV601 提供一个可用来禁用器件的关断引脚。 一旦 处于关断模式,电源电流被减少至 45pA (典型值)。

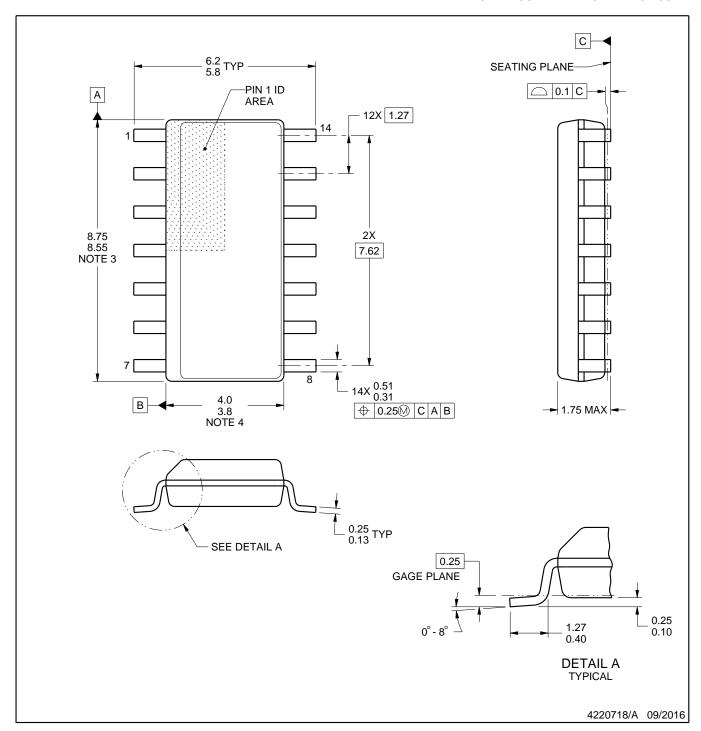

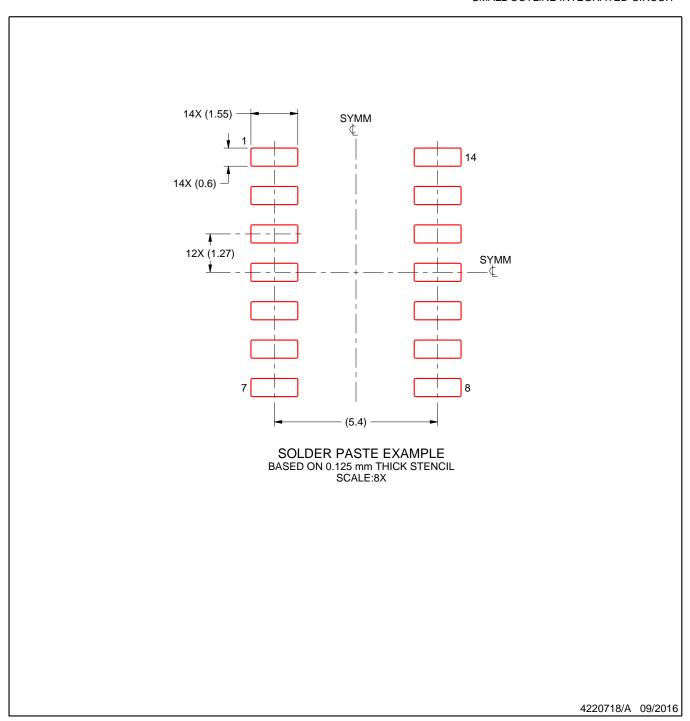

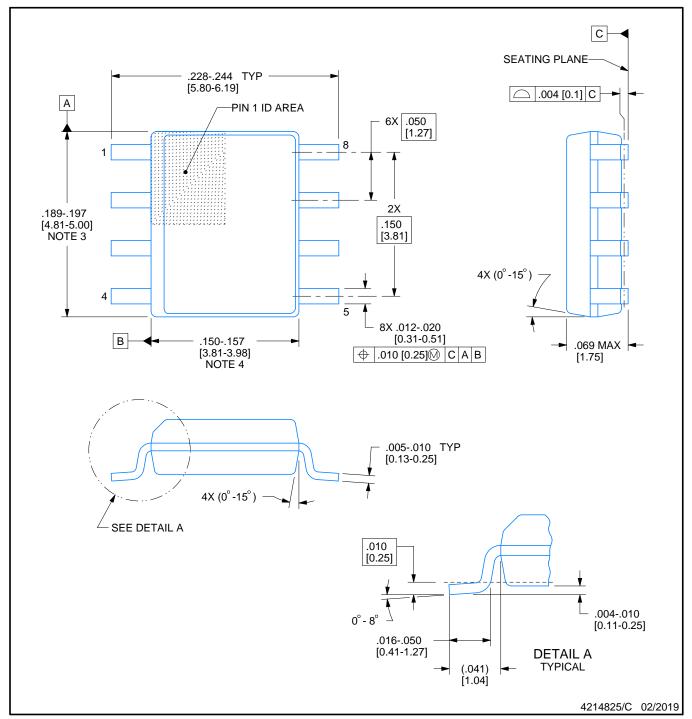

LMV601 采用微型 6 引脚 SC70 封装, LMV602 采用 节省空间的 8 引脚超薄型小外形尺寸封装 (VSSOP) 和 小外形尺寸集成电路封装 (SOIC), 而 LMV604 采用 14 引脚薄型小外形尺寸封装 (TSSOP) 和 SOIC 封 装。 这些小型封装放大器为需要最小印刷电路板 (PCB) 封装尺寸的应用提供了理想的解决方案。 有空 间受限 PC 电路板要求的应用包含便携式和电池供电类 电子元器件。

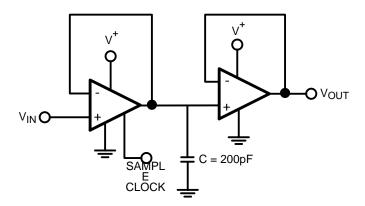

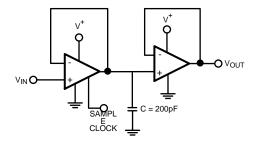

### 采样和保持电路

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

## Absolute Maximum Ratings (1)(2)

| ECD Telegraps (3)                   | Machine Model                           | 200V             |  |  |

|-------------------------------------|-----------------------------------------|------------------|--|--|

| ESD Tolerance (3)                   | Human Body Model                        | 2000V            |  |  |

| Differential Input Voltage          |                                         | ± Supply Voltage |  |  |

| Supply Voltage (V + -V -)           | 6.0V                                    |                  |  |  |

| Output Short Circuit to V +         | See <sup>(4)</sup>                      |                  |  |  |

| Output Short Circuit to V -         | See <sup>(5)</sup>                      |                  |  |  |

| Storage Temperature Range           | -65°C to 150°C                          |                  |  |  |

| Junction Temperature <sup>(6)</sup> |                                         | 150°C            |  |  |

| Mounting Temperature                | Infrared or Convection Reflow (20 sec.) | 235°C            |  |  |

| Mounting Temperature                | Wave Soldering Lead Temp. (10 sec.)     | 260°C            |  |  |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications and the test conditions, see the Electrical Characteristics.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

- (3) Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC)Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

- (4) Shorting output to V<sup>+</sup> will adversely affect reliability.

- (5) Shorting output to V will adversely affect reliability.

- (6) The maximum power dissipation is a function of T

<sub>J(MAX)</sub>, θ

<sub>JA</sub>. The maximum allowable power dissipation at any ambient temperature is P

<sub>D</sub> = (T

<sub>J(MAX)</sub> T

<sub>A</sub>)/ θ

<sub>JA</sub>. All numbers apply for packages soldered directly onto a PC Board.

## Operating Ratings<sup>(1)</sup>

| Supply Voltage            |              | 2.7V to 5.5V   |

|---------------------------|--------------|----------------|

| Temperature Range         |              | -40°C to 125°C |

| Thermal Resistance (θ JA) | 6-Pin SC70   | 414°C/W        |

|                           | 8-Pin SOIC   | 190°C/W        |

|                           | 8-Pin VSSOP  | 235°C/W        |

|                           | 14-Pin TSSOP | 155°C/W        |

|                           | 14-Pin SOIC  | 145°C/W        |

|                           |              |                |

<sup>(1)</sup> Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications and the test conditions, see the Electrical Characteristics.

## 2.7V DC Electrical Characteristics(1)

Unless otherwise specified, all limits ensured for  $T_J = 25^{\circ}C$ ,  $V^+ = 2.7V$ ,  $V^- = 0V$ ,  $V_{CM} = V^+/2$ ,  $V_O = V^+/2$  and  $R_L > 1M\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter                          | Conditions                                        | Min <sup>(2)</sup> | Тур <sup>(3)</sup>     | Max <sup>(2)</sup> | Units |  |

|-------------------|------------------------------------|---------------------------------------------------|--------------------|------------------------|--------------------|-------|--|

| Vos               | Input Offset Voltage               | LMV601                                            |                    | 0.25                   | 4                  | >/    |  |

|                   |                                    | LMV602/LMV604                                     |                    | 0.55                   | 5                  | mV    |  |

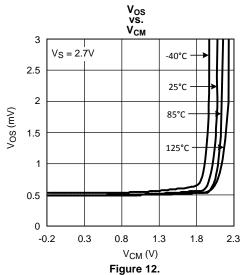

| TCV <sub>OS</sub> | Input Offset Voltage Average Drift |                                                   |                    | 1.7                    |                    | μV/°C |  |

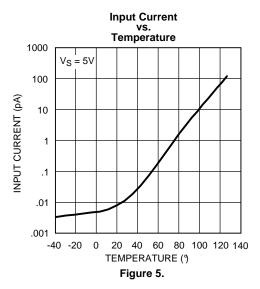

| I <sub>B</sub>    | Input Bias Current                 |                                                   |                    | 0.02                   |                    | рА    |  |

| los               | Input Offset Current               |                                                   |                    | 6.6                    |                    | fA    |  |

| I <sub>S</sub>    | Supply Current                     | Per Amplifier                                     |                    | 100                    | 170                | μΑ    |  |

|                   |                                    | Shutdown Mode, V <sub>SD</sub> = 0V (LMV601)      |                    | 45pA                   | 1µA                |       |  |

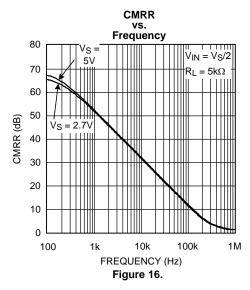

| CMRR              | Common Mode Rejection Ratio        | $0V \le V_{CM} \le 1.7V$ $0V \le V_{CM} \le 1.6V$ |                    | 80                     |                    | dB    |  |

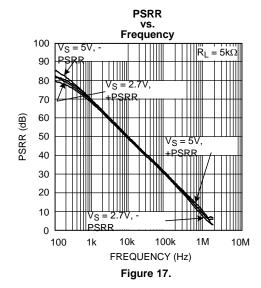

| PSRR              | Power Supply Rejection Ratio       | 2.7V ≤ V <sup>+</sup> ≤ 5V                        |                    | 82                     |                    | dB    |  |

| V <sub>CM</sub>   | Input Common Mode Voltage          | For CMRR ≥ 50dB                                   | 0                  | -0.2 to 1.9<br>(Range) | 1.7                | V     |  |

| A <sub>V</sub>    | Large Signal Voltage Gain          | $R_L = 10k\Omega$ to 1.35V                        |                    | 113                    |                    | dB    |  |

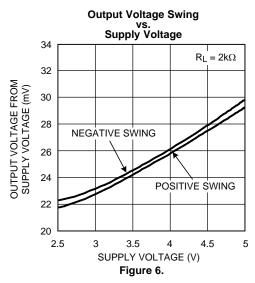

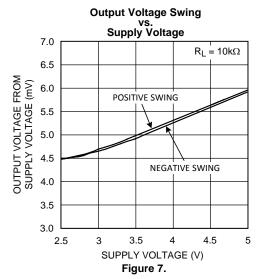

| Vo                | Output Swing                       | $R_L = 10k\Omega$ to 1.35V                        |                    | 5.0                    | 30                 | >/    |  |

|                   |                                    |                                                   | 30                 | 5.3                    |                    | mV    |  |

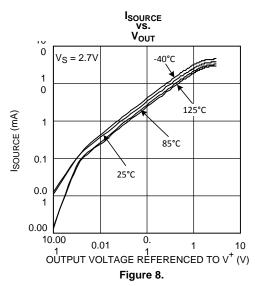

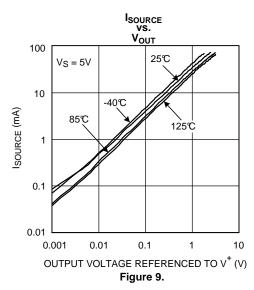

| I <sub>O</sub>    | Output Short Circuit Current       | Sourcing<br>LMV601/LMV602                         |                    | 32                     |                    |       |  |

|                   |                                    | Sourcing<br>LMV604                                |                    | 24                     |                    | mA    |  |

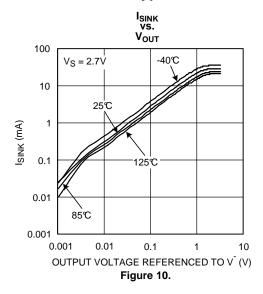

|                   |                                    | Sinking                                           |                    | 24                     |                    |       |  |

| t <sub>on</sub>   | Turn-on Time from Shutdown         | (LMV601)                                          |                    | 5                      |                    | μs    |  |

| V <sub>SD</sub>   | Shutdown Pin Voltage Range         | ON Mode (LMV601)                                  |                    | 1.7 to 2.7             | 2.4 to 2.7         | V     |  |

|                   |                                    | Shutdown Mode (LMV601)                            |                    | 0 to 1                 | 0 to 0.8           | V     |  |

<sup>(1)</sup> Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that T<sub>J</sub> = T<sub>A</sub>. No assurance of parametric performance is indicated in the electrical tables under conditions of internal self heating where T<sub>J</sub> > T<sub>A</sub>.

<sup>(2)</sup> All limits are ensured by testing or statistical analysis.

<sup>(3)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

## 2.7V AC Electrical Characteristics(1)

Unless otherwise specified, all limits ensured for  $T_J = 25^{\circ}C$ ,  $V^+ = 2.7V$ ,  $V^- = 0V$ ,  $V_{CM} = V^+/2$ ,  $V_O = V^+/2$  and  $R_L > 1M\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol         | Parameter                    | Conditions                                                  | Min <sup>(2)</sup> | Typ <sup>(3)</sup> | Max <sup>(2)</sup> | Units              |

|----------------|------------------------------|-------------------------------------------------------------|--------------------|--------------------|--------------------|--------------------|

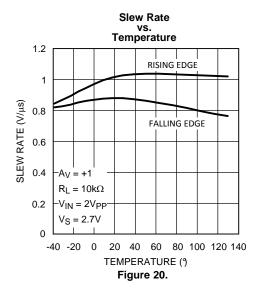

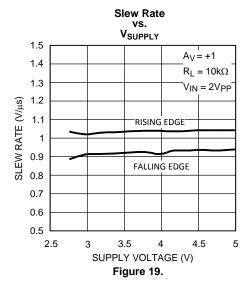

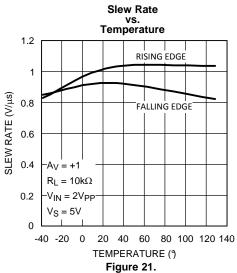

| SR             | Slew Rate                    | $R_L = 10k\Omega$ , (4)                                     |                    | 1.0                |                    | V/µs               |

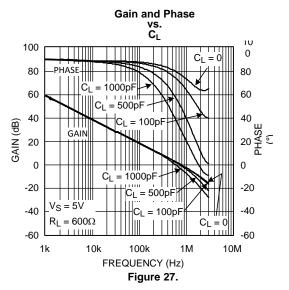

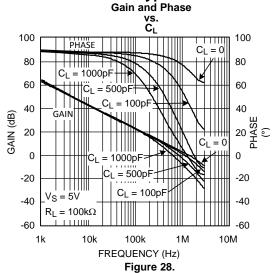

| GBW            | Gain Bandwidth Product       | $R_L = 100k\Omega, C_L = 200pF$                             |                    | 1.0                |                    | MHz                |

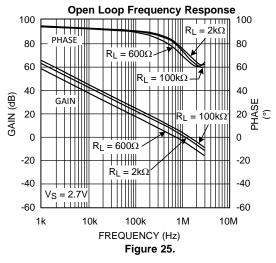

| Φ <sub>m</sub> | Phase Margin                 | $R_L = 100k\Omega$                                          |                    | 72                 |                    | deg                |

| G <sub>m</sub> | Gain Margin                  | $R_L = 100k\Omega$                                          |                    | 20                 |                    | dB                 |

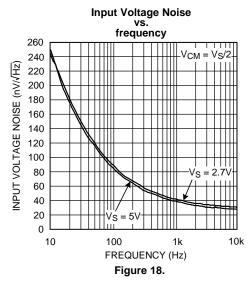

| e <sub>n</sub> | Input-Referred Voltage Noise | f = 1kHz                                                    |                    | 40                 |                    | nV/√ <del>Hz</del> |

| i <sub>n</sub> | Input-Referred Current Noise | f = 1kHz                                                    |                    | 0.001              |                    | pA/√Hz             |

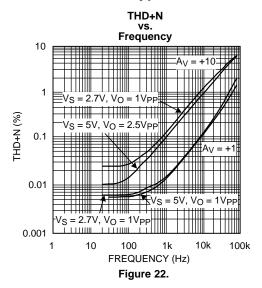

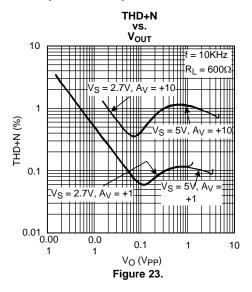

| THD            | Total Harmonic Distortion    | $f = 1kHz, A_V = +1$<br>$R_L = 600\Omega, V_{IN} = 1V_{PP}$ |                    | 0.017              |                    | %                  |

- (1) Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that T<sub>J</sub> = T<sub>A</sub>. No assurance of parametric performance is indicated in the electrical tables under conditions of internal self heating where T<sub>J</sub> > T<sub>A</sub>.

- (2) All limits are ensured by testing or statistical analysis.

- (3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

- (4) Connected as voltage follower with 2V<sub>PP</sub> step input. Number specified is the slower of the positive and negative slew rates.

## 5V DC Electrical Characteristics (1)

Unless otherwise specified, all limits ensured for  $T_J = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V^+/2$ ,  $V_O = V^+/2$  and  $R_L > 1M\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol                                                     | Parameter                                      | Conditions                                         | Min <sup>(2)</sup> | Typ <sup>(3)</sup>     | Max <sup>(2)</sup> | Units |  |

|------------------------------------------------------------|------------------------------------------------|----------------------------------------------------|--------------------|------------------------|--------------------|-------|--|

| V <sub>OS</sub>                                            | Input Offset                                   | LMV601                                             |                    | 0.25                   | 4                  | >/    |  |

|                                                            | Voltage                                        | LMV602/LMV604                                      |                    | 0.70                   | 5                  | mV    |  |

| TCV <sub>OS</sub> Input Offset<br>Voltage Average<br>Drift |                                                |                                                    |                    | 1.9                    |                    | μV/°C |  |

| I <sub>B</sub>                                             | Input Bias Current                             |                                                    |                    | 0.02                   |                    | pA    |  |

| I <sub>OS</sub>                                            | Input Offset<br>Current                        |                                                    |                    | 6.6                    |                    | fA    |  |

| I <sub>S</sub>                                             | Supply Current                                 | Per Amplifier                                      |                    | 107                    | 200                | μΑ    |  |

|                                                            |                                                | Shutdown Mode,<br>V <sub>SD</sub> = 0V<br>(LMV601) |                    | 0.033                  | 1                  | μА    |  |

| CMRR                                                       | CMRR Common Mode 0V ≤ \ Rejection Ratio 0V ≤ \ |                                                    |                    | 86                     |                    | dB    |  |

| PSRR Power Supply Rejection Ratio                          |                                                | 2.7V ≤ V <sup>+</sup> ≤ 5V                         |                    | 82                     |                    | dB    |  |

| V <sub>CM</sub>                                            | Input Common<br>Mode Voltage                   | For CMRR ≥ 50dB                                    | 0                  | -0.2 to 4.2<br>(Range) | 4                  | V     |  |

| A <sub>V</sub> Large Signal Voltage Gain <sup>(4)</sup>    |                                                | $R_L = 10k\Omega$ to 2.5V                          |                    | 116                    |                    | dB    |  |

| Vo                                                         | Output Swing                                   | $R_L = 10k\Omega$ to 2.5V                          |                    | 7                      | 30                 | m)/   |  |

|                                                            |                                                |                                                    | 30                 | 7                      |                    | mV    |  |

| lo                                                         | Output Short                                   | Sourcing                                           |                    | 113                    |                    | ^     |  |

|                                                            | Circuit Current                                | Sinking                                            |                    | 75                     |                    | mA mA |  |

<sup>(1)</sup> Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that T<sub>J</sub> = T<sub>A</sub>. No assurance of parametric performance is indicated in the electrical tables under conditions of internal self heating where T<sub>J</sub> > T<sub>A</sub>.

<sup>(2)</sup> All limits are ensured by testing or statistical analysis.

<sup>(3)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

<sup>(4)</sup>  $R_L$  is connected to mid-supply. The output voltage is GND + 0.2V  $\leq$  V<sub>O</sub>  $\leq$  V<sup>+</sup> =0.2V

www.ti.com.cn

## 5V DC Electrical Characteristics<sup>(1)</sup> (continued)

Unless otherwise specified, all limits ensured for  $T_J=25^{\circ}C,\ V^+=5V,\ V^-=0V,\ V_{CM}=V^+/2,\ V_O=V^+/2$  and R  $_L>1M\Omega.$  Boldface limits apply at the temperature extremes.

| Symbol          | Parameter                     | Conditions             | Min <sup>(2)</sup> | Typ <sup>(3)</sup> | Max <sup>(2)</sup> | Units |

|-----------------|-------------------------------|------------------------|--------------------|--------------------|--------------------|-------|

| t <sub>on</sub> | Turn-on Time from Shutdown    | (LMV601)               |                    | 5                  |                    | μs    |

| V <sub>SD</sub> | Shutdown Pin<br>Voltage Range | ON Mode<br>(LMV601)    |                    | 3.1 to 5           | 4.5 to 5.0         | V     |

|                 |                               | Shutdown Mode (LMV601) |                    | 0 to 1             | 0 to 0.8           | V     |

## 5V AC Electrical Characteristics(1)

Unless otherwise specified, all limits ensured for  $T_J = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V^+/2$ ,  $V_O = V^+/2$  and  $R_L > 1M\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol         | Parameter                    | Conditions                                                        | Min <sup>(2)</sup> | Тур <sup>(3)</sup> | Max <sup>(2)</sup> | Units              |

|----------------|------------------------------|-------------------------------------------------------------------|--------------------|--------------------|--------------------|--------------------|

| SR             | Slew Rate                    | $R_L = 10k\Omega,^{(4)}$                                          |                    | 1.0                |                    | V/µs               |

| GBW            | Gain-Bandwidth Product       | $R_L = 10k\Omega$ , $C_L = 200pF$                                 |                    | 1.0                |                    | MHz                |

| Φ <sub>m</sub> | Phase Margin                 | $R_L = 100k\Omega$                                                |                    | 70                 |                    | deg                |

| G <sub>m</sub> | Gain Margin                  | $R_L = 100k\Omega$                                                |                    | 20                 |                    | dB                 |

| e <sub>n</sub> | Input-Referred Voltage Noise | f = 1kHz                                                          |                    | 39                 |                    | nV/√ <del>Hz</del> |

| in             | Input-Referred Current Noise | f = 1kHz                                                          |                    | 0.001              |                    | pA/√Hz             |

| THD            | Total Harmonic Distortion    | $f = 1kHz$ , $A_V = +1$<br>$R_L = 600\Omega$ , $V_{IN} = 1V_{PP}$ |                    | 0.012              |                    | %                  |

- (1) Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that T<sub>J</sub> = T<sub>A</sub>. No assurance of parametric performance is indicated in the electrical tables under conditions of internal self heating where T<sub>J</sub> > T<sub>A</sub>.

- (2) All limits are ensured by testing or statistical analysis.

- (3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

- (4) Connected as voltage follower with 2V<sub>PP</sub> step input. Number specified is the slower of the positive and negative slew rates.

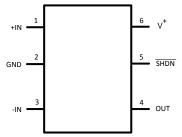

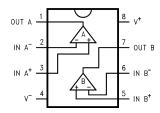

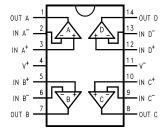

### **Connection Diagrams**

Figure 1. 6-Pin SC70 – Top View See Package Number DCK

Figure 2. 8-Pin VSSOP/SOIC – Top View See Package Number DGK or D

Figure 3. 14-Pin TSSOP/SOIC Top View See Package Number PW or D

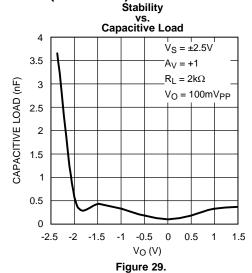

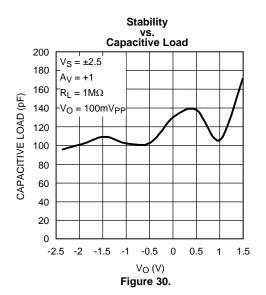

### **Typical Performance Characteristics**

Figure 24.

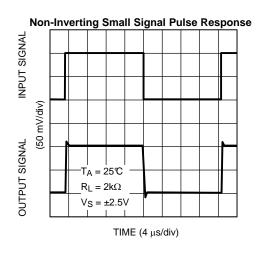

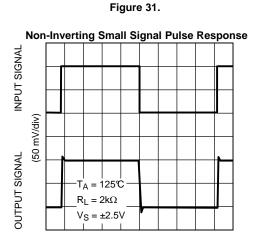

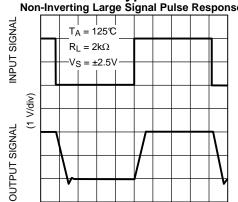

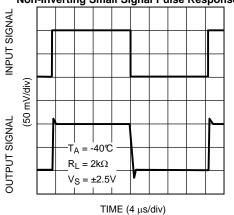

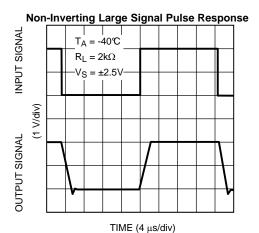

# Typical Performance Characteristics (continued) Non-Inverting Large Signal Pulse Response Non-Inverting Small Signal Pulse Response

TIME (4 µs/div) Figure 34.

Figure 35.

Figure 36.

Figure 37.

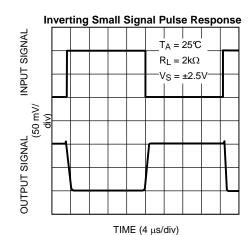

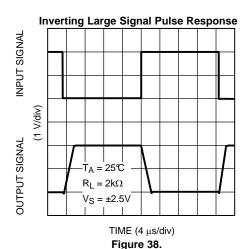

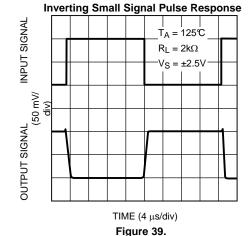

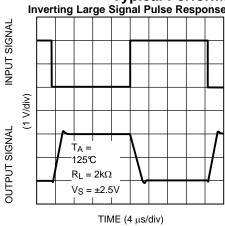

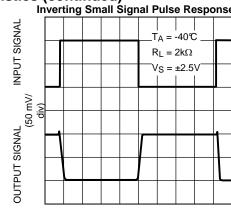

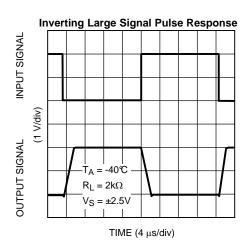

# Typical Performance Characteristics (continued) Inverting Large Signal Pulse Response Inverting Small Signal Pulse Response

Figure 40.

TIME (4 μs/div)

Figure 42.

Copyright © 2012–2013, Texas Instruments Incorporated

#### **APPLICATION SECTION**

### LMV601/LMV602/LMV604

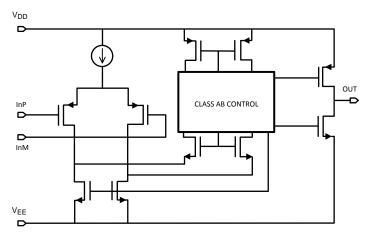

The LMV601/LMV602/LMV604 family of amplifiers features low voltage, low power, and rail-to-rail output operational amplifiers designed for low voltage portable applications. The family is designed using all CMOS technology. This results in an ultra low input bias current. The LMV601 has a shutdown option, which can be used in portable devices to increase battery life.

A simplified schematic of the LMV601/LMV602/LMV604 family of amplifiers is shown in Figure 44. The PMOS input differential pair allows the input to include ground. The output of this differential pair is connected to the Class AB turnaround stage. This Class AB turnaround has a lower quiescent current, compared to regular turnaround stages. This results in lower offset, noise, and power dissipation, while slew rate equals that of a conventional turnaround stage. The output of the Class AB turnaround stage provides gate voltage to the complementary common-source transistors at the output stage. These transistors enable the device to have rail-to-rail output.

Figure 44. Simplified Schematic

#### **CLASS AB TURNAROUND STAGE AMPLIFIER**

This patented folded cascode stage has a combined class AB amplifier stage, which replaces the conventional folded cascode stage. Therefore, the class AB folded cascode stage runs at a much lower quiescent current compared to conventional folded cascode stages. This results in significantly smaller offset and noise contributions. The reduced offset and noise contributions in turn reduce the offset voltage level and the voltage noise level at the input of the LMV601/LMV602/LMV604. Also the lower quiescent current results in a high open-loop gain for the amplifier. The lower quiescent current does not affect the slew rate of the amplifier nor its ability to handle the total current swing coming from the input stage.

The input voltage noise of the device at low frequencies, below 1kHz, is slightly higher than devices with a BJT input stage; However the PMOS input stage results in a much lower input bias current and the input voltage noise drops at frequencies above 1kHz.

### SAMPLE AND HOLD CIRCUIT

The lower input bias current of the LMV601 results in a very high input impedance. The output impedance when the device is in shutdown mode is quite high. These high impedances, along with the ability of the shutdown pin to be derived from a separate power source, make LMV601 a good choice for sample and hold circuits. The sample clock should be connected to the shutdown pin of the amplifier to rapidly turn the device on or off.

Figure 45 shows the schematic of a simple sample and hold circuit. When the sample clock is high the first amplifier is in normal operation mode and the second amplifier acts as a buffer. The capacitor, which appears as a load on the first amplifier, will be charging at this time. The voltage across the capacitor is that of the non-inverting input of the first amplifier since it is connected as a voltage-follower. When the sample clock is low the first amplifier is shut off, bringing the output impedance to a high value. The high impedance of this output, along with the very high impedance on the input of the second amplifier, prevents the capacitor from discharging. There is very little voltage droop while the first amplifier is in shutdown mode. The second amplifier, which is still in normal operation mode and is connected as a voltage follower, also provides the voltage sampled on the capacitor at its output.

Figure 45. Sample and Hold Circuit

### **SHUTDOWN FEATURE**

The LMV601 is capable of being turned off in order to conserve power and increase battery life in portable devices. Once in shutdown mode the supply current is drastically reduced, 1µA maximum, and the output will be "tri-stated."

The device will be disabled when the shutdown pin voltage is pulled low. The shutdown pin should never be left unconnected. Leaving the pin floating will result in an undefined operation mode and the device may oscillate between shutdown and active modes.

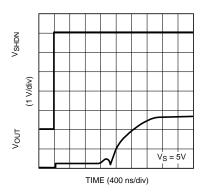

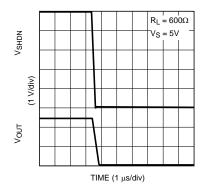

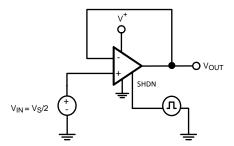

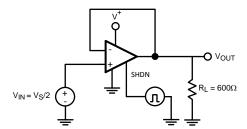

The LMV601 typically turns on 2.8 $\mu$ s after the shutdown voltage is pulled high. The device turns off in less than 400ns after shutdown voltage is pulled low. Figure 46 and Figure 47 show the turn-on and turn-off time of the LMV601, respectively. In order to reduce the effect of the capacitance added to the circuit by the scope probe, in the turn-off time circuit a resistive load of  $600\Omega$  is added. Figure 48 and Figure 49 show the test circuits used to obtain the two plots.

Figure 46. Turn-on Time

Figure 47. Turn-off Time

Figure 48. Turn-on Time

Figure 49. Turn-off Time

### **LOW INPUT BIAS CURRENT**

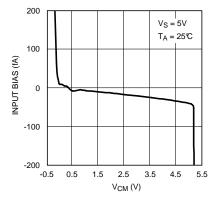

The LMV601/LMV602/LMV604 Amplifiers have a PMOS input stage. As a result, they will have a much lower input bias current than devices with BJT input stages. This feature makes these devices ideal for sensor circuits. A typical curve of the input bias current of the LMV601 is shown in Figure 50.

Figure 50. Input Bias Current vs. V<sub>CM</sub>

## **REVISION HISTORY**

| CI | hanges from Revision A (March 2013) to Revision B  | Pag | ge |

|----|----------------------------------------------------|-----|----|

| •  | Changed layout of National Data Sheet to TI format |     | 16 |

www.ti.com 11-Nov-2025

## **PACKAGING INFORMATION**

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|-----------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

| LMV601MG/NOPB         | Active | Production    | SC70 (DCK)   6  | 1000   SMALL T&R      | Yes             | SN                            | Level-1-260C-UNLIM         | -40 to 125   | AUA              |

| LMV601MG/NOPB.A       | Active | Production    | SC70 (DCK)   6  | 1000   SMALL T&R      | Yes             | SN                            | Level-1-260C-UNLIM         | -40 to 125   | AUA              |

| LMV601MGX/NOPB        | Active | Production    | SC70 (DCK)   6  | 3000   LARGE T&R      | Yes             | SN                            | Level-1-260C-UNLIM         | -40 to 125   | AUA              |

| LMV601MGX/NOPB.A      | Active | Production    | SC70 (DCK)   6  | 3000   LARGE T&R      | Yes             | SN                            | Level-1-260C-UNLIM         | -40 to 125   | AUA              |

| LMV602MA/NOPB         | Active | Production    | SOIC (D)   8    | 95   TUBE             | Yes             | SN                            | Level-1-260C-UNLIM         | -40 to 125   | LMV60<br>2MA     |

| LMV602MA/NOPB.A       | Active | Production    | SOIC (D)   8    | 95   TUBE             | Yes             | SN                            | Level-1-260C-UNLIM         | -40 to 125   | LMV60<br>2MA     |

| LMV602MAX/NOPB        | Active | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes             | SN                            | Level-1-260C-UNLIM         | -40 to 125   | LMV60<br>2MA     |

| LMV602MAX/NOPB.A      | Active | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes             | SN                            | Level-1-260C-UNLIM         | -40 to 125   | LMV60<br>2MA     |

| LMV602MAX/NOPB.B      | Active | Production    | SOIC (D)   8    | 2500   LARGE T&R      | -               | Call TI                       | Call TI                    | -40 to 125   |                  |

| LMV602MM/NOPB         | Active | Production    | VSSOP (DGK)   8 | 1000   SMALL T&R      | Yes             | SN                            | Level-1-260C-UNLIM         | -40 to 125   | AC9A             |

| LMV602MM/NOPB.A       | Active | Production    | VSSOP (DGK)   8 | 1000   SMALL T&R      | Yes             | SN                            | Level-1-260C-UNLIM         | -40 to 125   | AC9A             |

| LMV602MMX/NOPB        | Active | Production    | VSSOP (DGK)   8 | 3500   LARGE T&R      | Yes             | SN                            | Level-1-260C-UNLIM         | -40 to 125   | AC9A             |

| LMV602MMX/NOPB.A      | Active | Production    | VSSOP (DGK)   8 | 3500   LARGE T&R      | Yes             | SN                            | Level-1-260C-UNLIM         | -40 to 125   | AC9A             |

| LMV604MA/NOPB         | Active | Production    | SOIC (D)   14   | 55   TUBE             | Yes             | SN                            | Level-1-260C-UNLIM         | -40 to 125   | LMV604MA         |

| LMV604MA/NOPB.A       | Active | Production    | SOIC (D)   14   | 55   TUBE             | Yes             | SN                            | Level-1-260C-UNLIM         | -40 to 125   | LMV604MA         |

| LMV604MA/NOPB.B       | Active | Production    | SOIC (D)   14   | 55   TUBE             | -               | Call TI                       | Call TI                    | -40 to 125   |                  |

| LMV604MAX/NOPB        | Active | Production    | SOIC (D)   14   | 2500   LARGE T&R      | Yes             | SN                            | Level-1-260C-UNLIM         | -40 to 125   | LMV604MA         |

| LMV604MAX/NOPB.A      | Active | Production    | SOIC (D)   14   | 2500   LARGE T&R      | Yes             | SN                            | Level-1-260C-UNLIM         | -40 to 125   | LMV604MA         |

| LMV604MAX/NOPB.B      | Active | Production    | SOIC (D)   14   | 2500   LARGE T&R      | -               | Call TI                       | Call TI                    | -40 to 125   |                  |

| LMV604MT/NOPB         | Active | Production    | TSSOP (PW)   14 | 94   TUBE             | Yes             | NIPDAU   SN                   | Level-1-260C-UNLIM         | -40 to 125   | LMV604<br>MT     |

| LMV604MT/NOPB.A       | Active | Production    | TSSOP (PW)   14 | 94   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | LMV604<br>MT     |

| LMV604MTX/NOPB        | Active | Production    | TSSOP (PW)   14 | 2500   LARGE T&R      | Yes             | NIPDAU   SN                   | Level-1-260C-UNLIM         | -40 to 125   | LMV604<br>MT     |

| LMV604MTX/NOPB.A      | Active | Production    | TSSOP (PW)   14 | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | LMV604<br>MT     |

## PACKAGE OPTION ADDENDUM

www.ti.com 11-Nov-2025

- (1) Status: For more details on status, see our product life cycle.

- (2) Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

- (3) RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

- (4) Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

- (5) MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

- (6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

### NOTES:

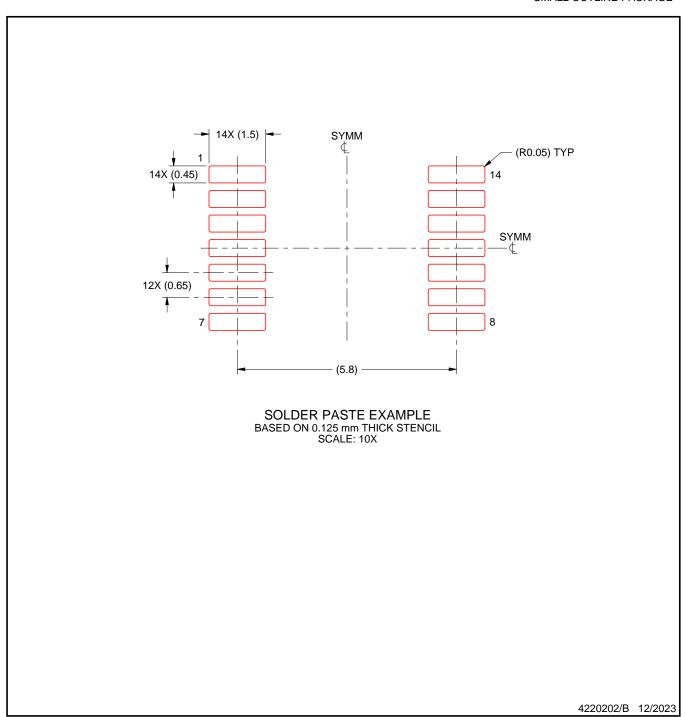

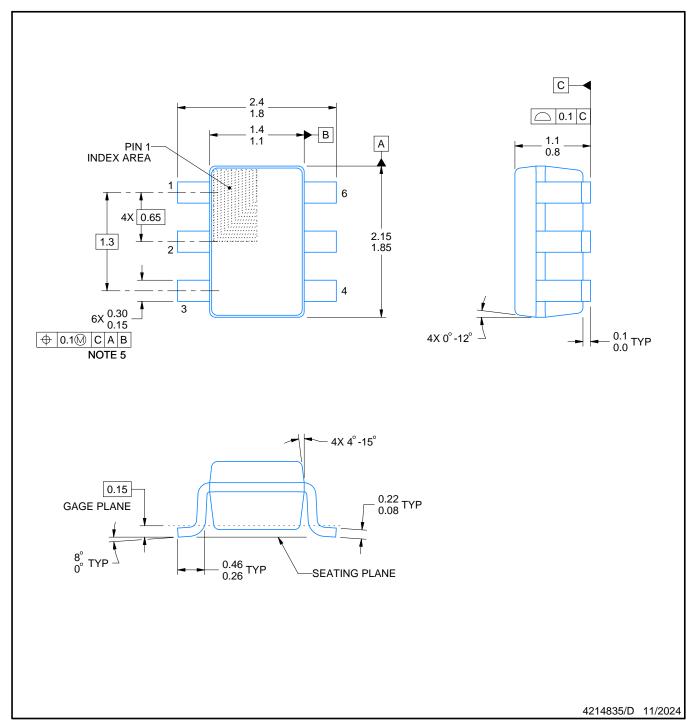

- 1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm, per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.43 mm, per side.

- 5. Reference JEDEC registration MS-012, variation AB.

NOTES: (continued)

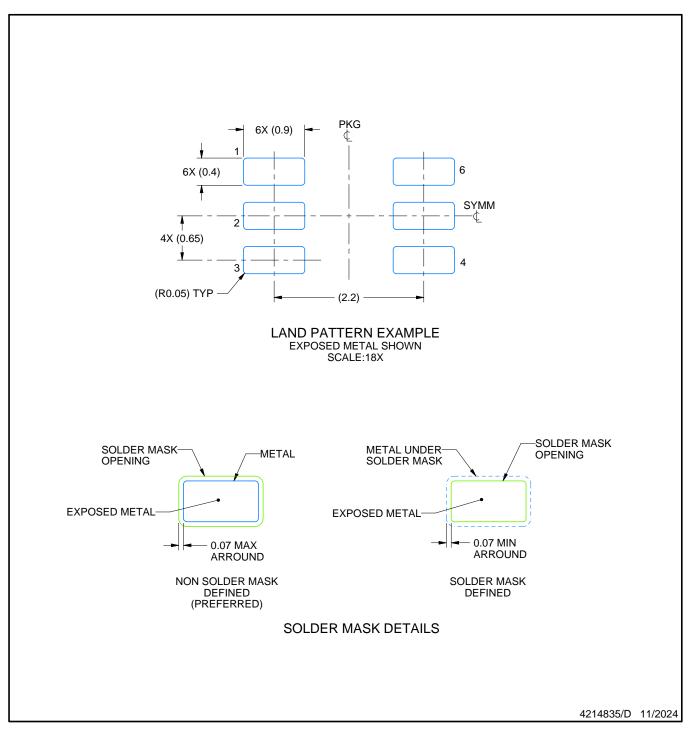

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

NOTES: (continued)

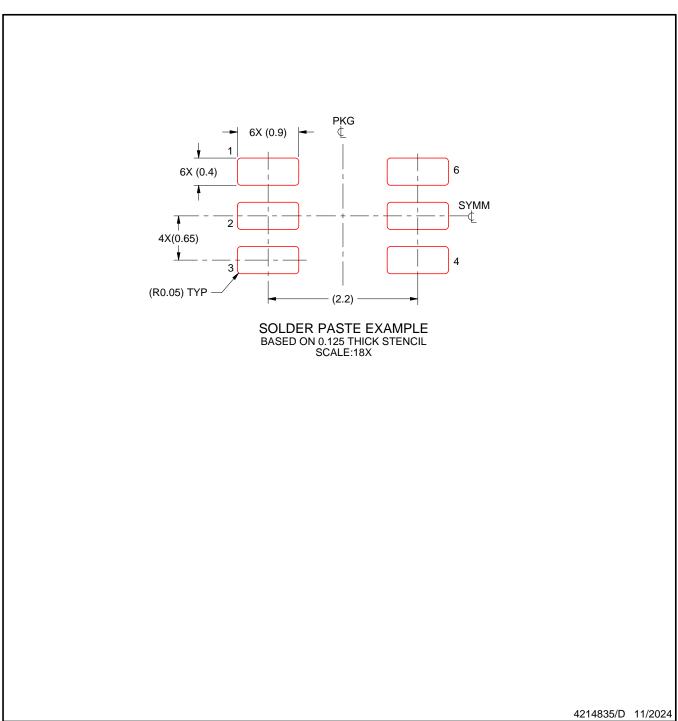

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

### NOTES:

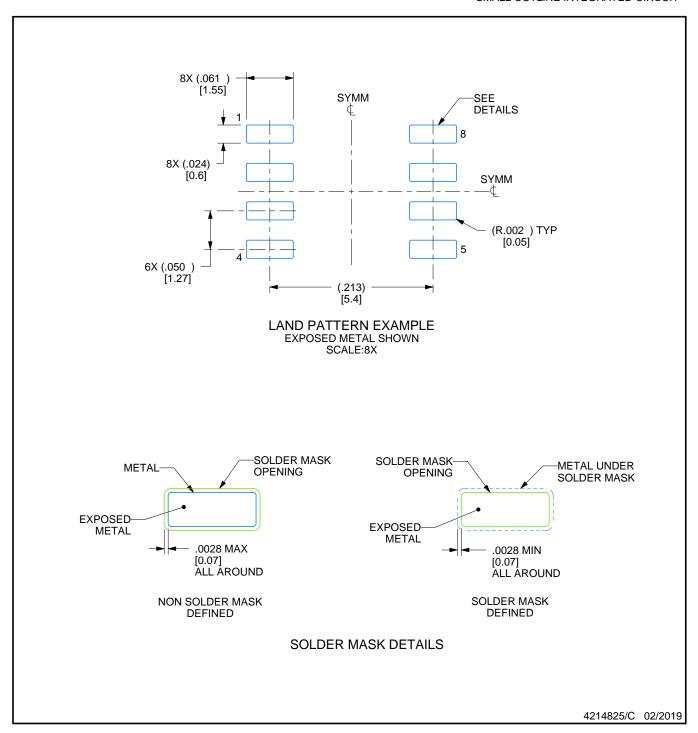

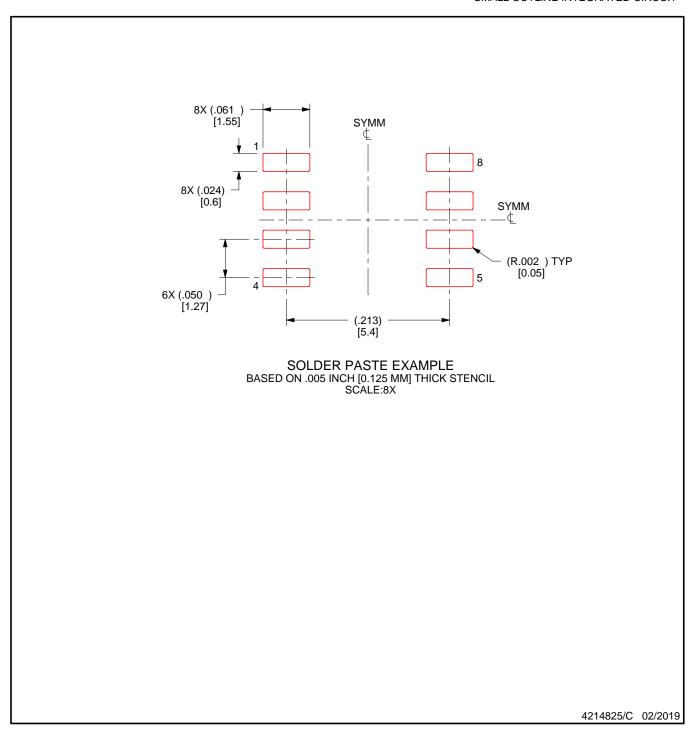

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

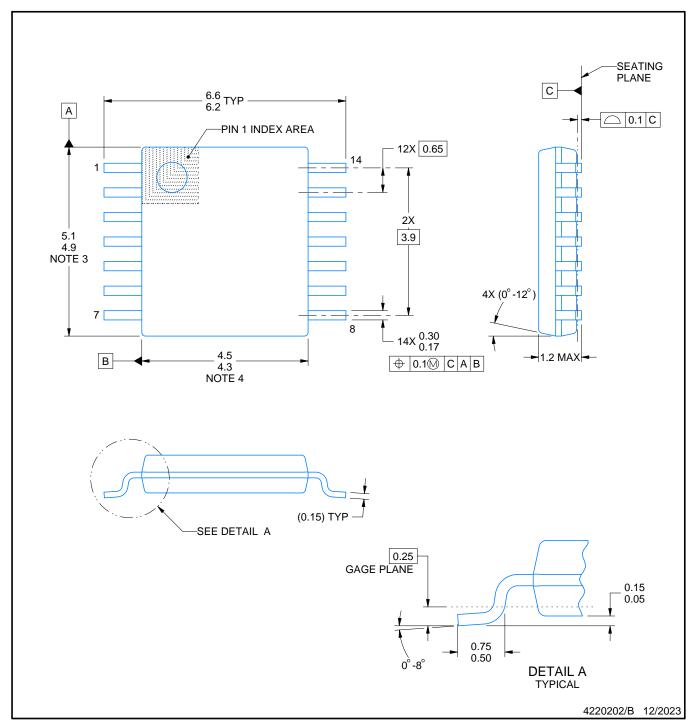

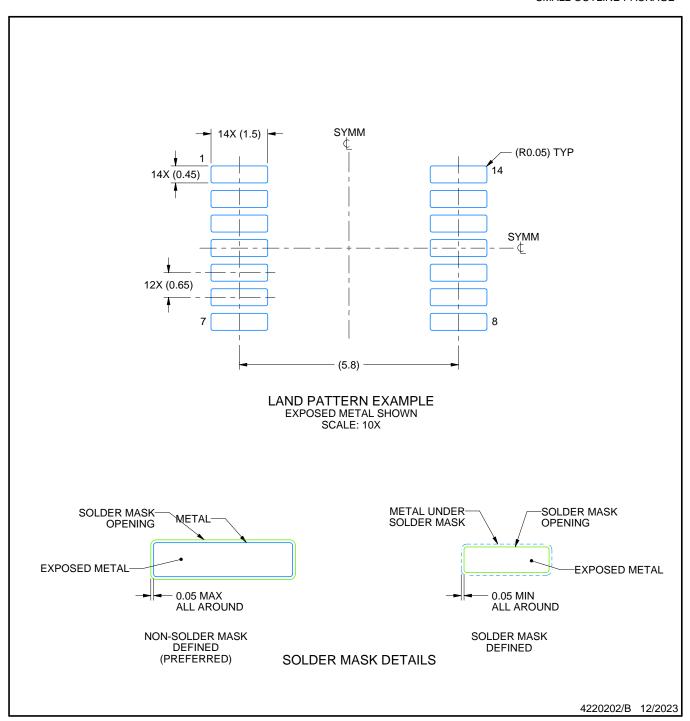

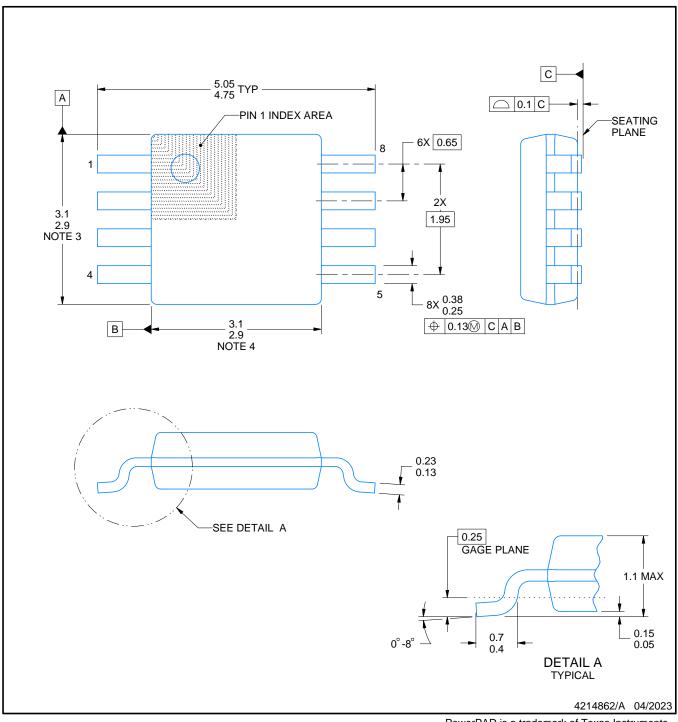

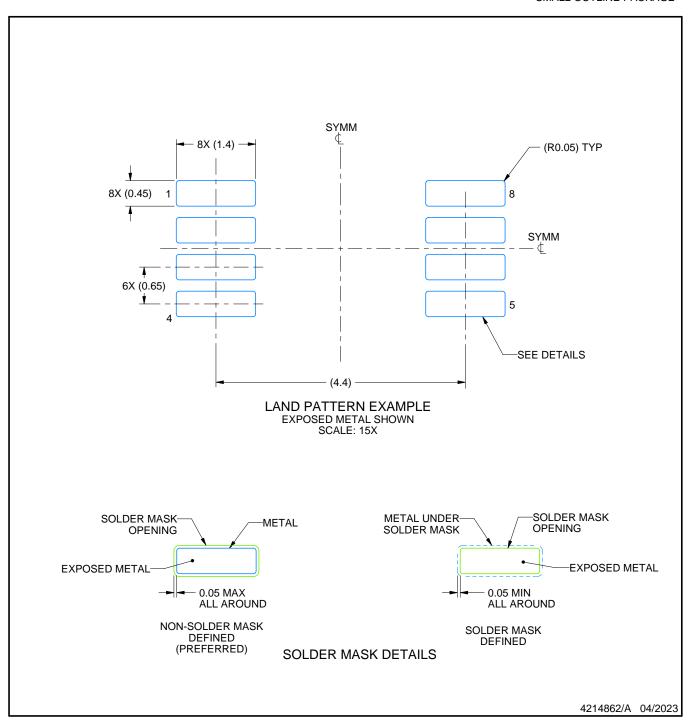

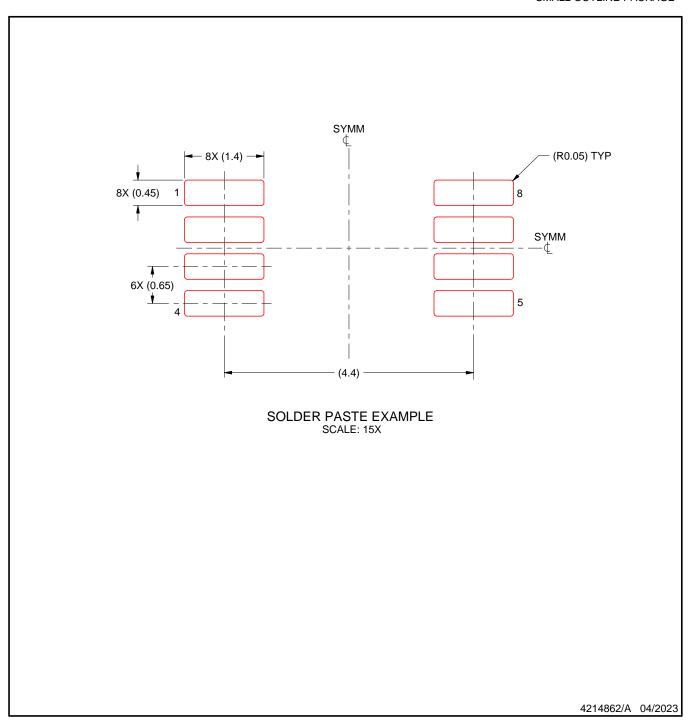

### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187.

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

- 9. Size of metal pad may vary due to creepage requirement.

NOTES: (continued)

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 12. Board assembly site may have different recommendations for stencil design.

SMALL OUTLINE TRANSISTOR

### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side.

4. Falls within JEDEC MO-203 variation AB.

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

5. Publication IPC-7351 may have alternate designs.

6. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

- 7. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 8. Board assembly site may have different recommendations for stencil design.

### 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月