LMP92066

ZHCSCA9A - MARCH 2014 - REVISED APRIL 2015

# LMP92066 具有集成 EEPROM 和输出开/关控制的双路温度控制数模转换器 (DAC)

## 1 特性

- 内部 12 位温度传感器

- 精度(-40°C 至 120°C): ±3.2°C(最大值)

- 存储在 EEPROM 中的两个独立传输函数

- 双模拟输出

- 两个 12 位 DAC

- 输出范围为 -5V 至 0V 或 0V 至 5V

- 可耐受高达 10µF 的高容性负载

- 后置校准精度: ±2.4mV(典型值)

- 输出开/关控制切换时间为 50ns (典型值)

- 切换时间为 50ns (典型值)

- 导通电阻 (RDSON): 5Ω (最大值)

- I<sup>2</sup>C 接口:标准且快速

- 9个可选从地址

- 超时功能

- VDD 电源电压 4.75V 至 5.25V

- VIO 范围 1.65V 至 3.6V

- 额定工作温度范围: -25°C 至 120°C

- 工作温度范围: -40°C 至 125°C

#### 2 应用范围

- GaN 或 LDMOS PA 偏置控制器

- 传感器温度补偿

- 定时电路温度补偿

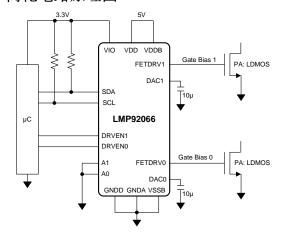

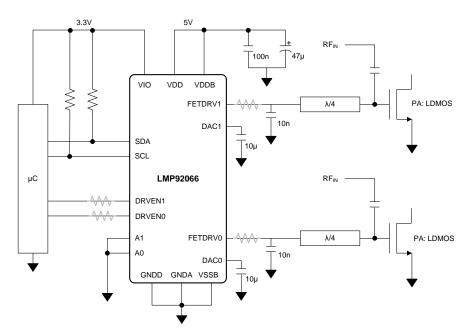

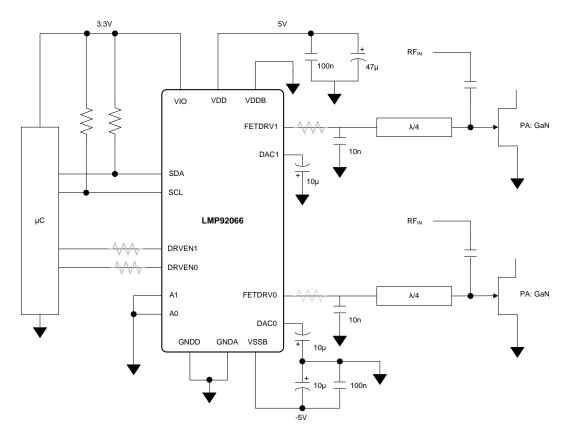

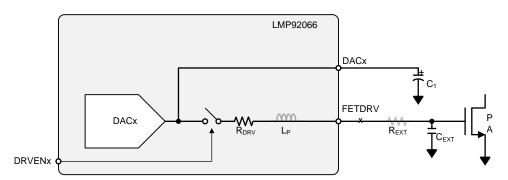

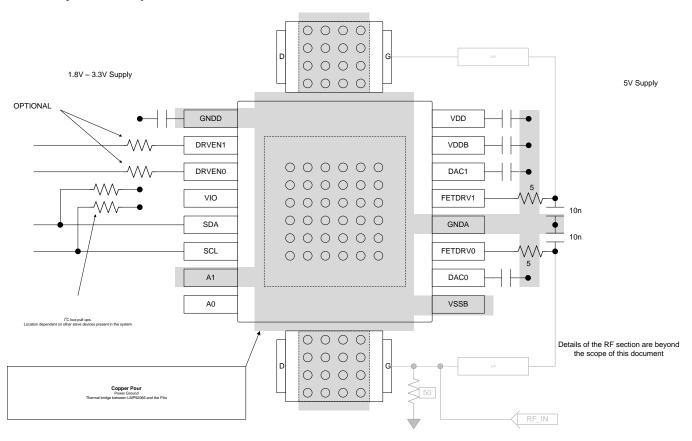

#### 4 简化电路原理图

#### 3 说明

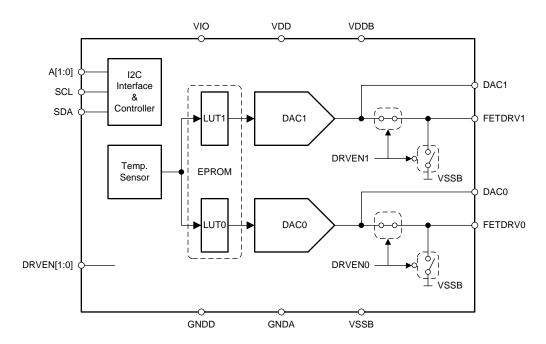

LMP92066 是一款高度集成的温度控制双路 DAC。 这两个 DAC 可由两个独立的、用户定义的温度至电压转换函数(存储在内部 EEPROM 中)编程,从而可以在无需其他外部电路的情况下校正任何温度影响。 一旦被加电,此器件自主运行,而无需系统控制器干预,以便为控制应用中偏置电压和电流的设置和补偿提供完整解决方案。

LMP92066 具有两个支持双输出范围的模拟输出: 0 至 +5V,以及 0 至 -5V。每个输出可通过专用控制引脚单独切换为负载。输出切换被设计用于快速响应,从而使此器件适合于射频 (RF) 功率放大器偏置应用。

EEPROM 经 100 次写入操作验证,从而实现重复字段 更新。 EEPROM 编程由用户发出的  $I^2$ C 命令完成。

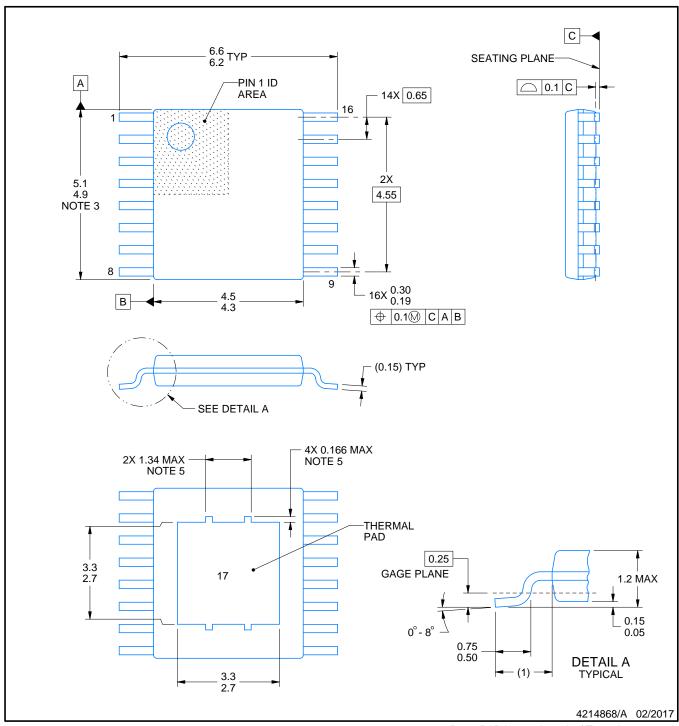

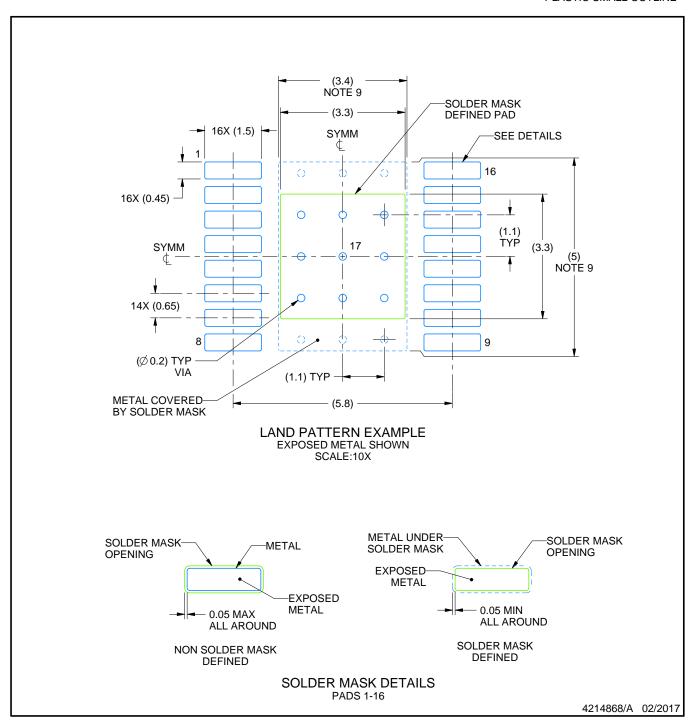

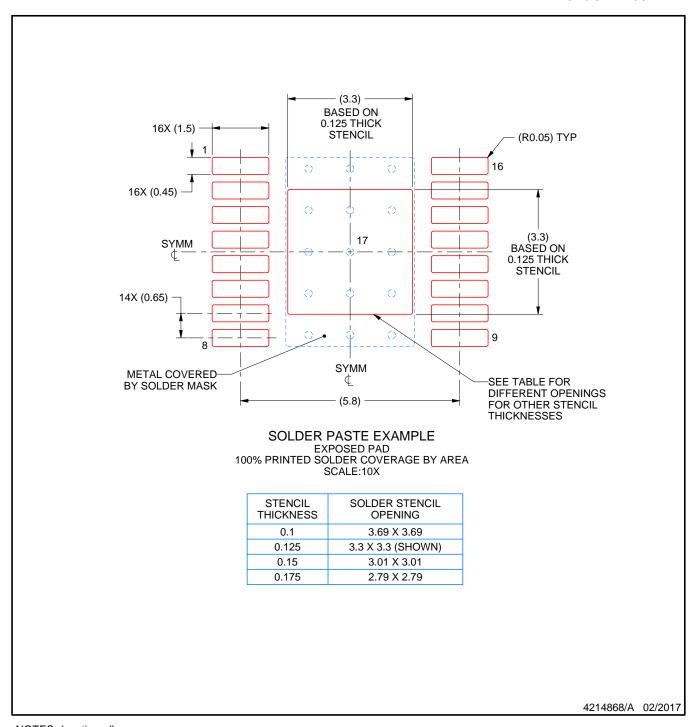

LMP92066 的数字端口可作为设置数字 I/O 电平的专用 VIO 引脚与各种系统控制器相连。 此器件采用耐热增强型 PowerPAD™ 封装,从而实现高精度印刷电路板 (PCB) 温度测量。

## 器件信息

| 器件型号     | 封装          | 封装尺寸            |

|----------|-------------|-----------------|

| LMP92066 | HTSSOP (16) | 5.00mm x 4.40mm |

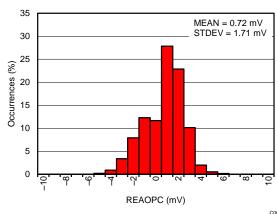

#### 一点校准后的残余误差

Coos

| $\neg$ | $\Rightarrow$ |

|--------|---------------|

| -      | ملب           |

| -      | w             |

| 特性                                                                                                                                                                | 8.6 Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3 4 4 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Detailed Description         14           8.1 Overview         14           8.2 Functional Block Diagram         14           8.3 Features Description         15 | 12.3 静电放电警告<br>12.4 术语表                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                   | 应用范围       1         说明       1         简化电路原理图       1         修订历史记录       2         Pin Configuration and Functions       3         Specifications       5         7.1 Absolute Maximum Ratings       5         7.2 ESD Ratings       5         7.3 Recommended Operating Conditions       5         7.4 Thermal Information       5         7.5 Electrical Characteristics       6         7.6 Timing Requirements       8         7.7 Output Switching Characteristics       8         7.8 Typical Characteristics       10         Detailed Description       14         8.1 Overview       14         8.2 Functional Block Diagram       14         8.3 Features Description       15 | 应用范围       1       8.6 Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## 5 修订历史记录

## Changes from Original (March 2014) to Revision A

| Р | а | a | 6 |

|---|---|---|---|

|   |   |   |   |

| 已更改 器件信息表的标题行;将整篇文档中的"端子"修订为"引脚";将处理额定值表更改为 ESD 额定值表;删除了正值前的"+";将交叉引用部分改为斜体;为表 3、4、5 和 6 添加了标题                                                               | 1                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Added "Ω" after "k" in EC table                                                                                                                              | 6                                     |

| Added "Ω" after "k" in <i>Output Switching</i> table                                                                                                         | 8                                     |

| Added "NOTE" to beginning of Applications and Implementations                                                                                                | 43                                    |

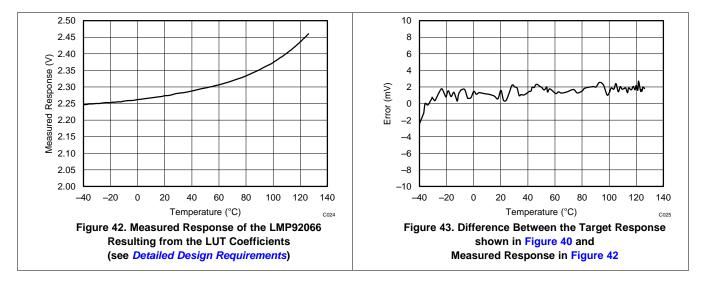

| Changed title from Application Performance Plots to Application Curves; deleted reference to Figure 43 in first sentence of first Application Curves section | 47                                    |

| Added change "5 mA" to "50 mA"                                                                                                                               | 54                                    |

|                                                                                                                                                              | 值前的"+";将交叉引用部分改为斜体;为表 3、4、5 和 6 添加了标题 |

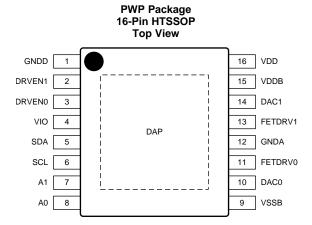

## 6 Pin Configuration and Functions

#### **Pin Functions**

|        | PIN                | TYPE (1) | DESCRIPTION                                     | ESD STRUCTURES |

|--------|--------------------|----------|-------------------------------------------------|----------------|

| NUMBER | NAME               | ITPE (") | DESCRIPTION                                     | ESD STRUCTURES |

| 1      | GNDD               | G        | Lower power rail of the digital I/O             | VIO            |

| 2:3    | DRVEN[1:0]         | I        | Asynchronous control of the Changeover Switches |                |

| 4      | VIO                | I        | Digital I/O power supply rail                   |                |

| 5      | SDA                | I/O      | I <sup>2</sup> C bi-directional data line       |                |

| 6      | SCL                | I        | I <sup>2</sup> C clock input                    | GNDA           |

| 7:8    | A[1:0]             | I        | I <sup>2</sup> C slave address selector         | VIO            |

| 9      | VSSB               | Р        | Output drive lower supply rail                  | GNDA           |

| 10, 14 | DAC0<br>DAC1       | 0        | DAC0 output                                     | VDDB           |

| 11, 13 | FETDRV0<br>FETDRV1 | 0        | Gate drive of the external FET device           | VSSB           |

## Pin Functions (continued)

|        | PIN  | TVDE (1) | TYPE (1) DESCRIPTION ESD STR                                                                                  |                  |

|--------|------|----------|---------------------------------------------------------------------------------------------------------------|------------------|

| NUMBER | NAME | ITPE (") | DESCRIPTION                                                                                                   | ESD STRUCTURES   |

| 12     | GNDA | G        | Analog block lower rail                                                                                       | Merril Clamp     |

| 15     | VDDB | Р        | Output drive upper supply rail                                                                                | VDD              |

| 16     | VDD  | Р        | Analog block upper rail                                                                                       | VDD Merril Clamp |

|        | DAP  | G        | Die Attach Pad. For best thermal, and noise performance it should be soldered to the local system ground pad. | GNDA             |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                           |                                     | MIN  | MAX | UNIT |

|---------------------------|-------------------------------------|------|-----|------|

| VDD                       |                                     | -0.3 | 5.5 |      |

| VDDB                      |                                     | -0.3 | 5.5 |      |

| VIO                       | Supply voltage with respect to GNDA | -0.3 | 5.5 | V    |

| VSSB                      |                                     | -5.5 | 0.3 |      |

| GNDD                      |                                     | -0.3 | 0.3 |      |

| VDDB to VSSB              |                                     | -0.3 | 5.5 | V    |

| Any other pins to GNDA    |                                     | -0.3 | 5.5 | V    |

| DAC output current        |                                     |      | 10  | m ^  |

| Current at all other pins |                                     |      | 5   | mA   |

| Storage temperature, T    | stg                                 | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 7.2 ESD Ratings

|                    |                                                        |                                                                     | VALUE | UNIT |

|--------------------|--------------------------------------------------------|---------------------------------------------------------------------|-------|------|

|                    | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1) | ±2500                                                               |       |      |

| V <sub>(ESD)</sub> | Electrostatic discharge                                | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|           |                             | MIN  | MAX  | UNIT |  |

|-----------|-----------------------------|------|------|------|--|

|           | Operational temperature     | -40  | 125  | °C   |  |

|           | Specification temperature   | -25  | 120  |      |  |

|           | DAC output load capacitance | 8    | 12   | μF   |  |

| VDD       | Supply voltage range (VDD)  | 4.75 | 5.25 | V    |  |

| VIO       | Digital I/O supply voltage  | 1.65 | 3.3  |      |  |

| VDDB-VSSB | LDMOS mode VSSB = GNDA      |      | 5    | V    |  |

|           | GaN mode VSSB = −5 V        |      | 5    |      |  |

#### 7.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)</sup>                | PWP (HTSSOP)<br>16 PINS | UNIT |

|-----------------------|----------------------------------------------|-------------------------|------|

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 38.2                    |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 21.3                    |      |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 15.1                    | 9000 |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.5                     | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 14.9                    |      |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.4                     |      |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 7.5 Electrical Characteristics

Unless otherwise noted: VDD = 5 V  $\pm$ 5%, VIO = 1.8 V to 3.3 V,  $T_A$  = 25°C. VDDB = 5 V  $\pm$ 5%, VSSB = GNDA,  $V_{DACx}$  output range 0 V to 5 V; or VDDB = GNDA, VSSB = -5 V  $\pm$ 5%,  $V_{DACx}$  output range 0 V to -5V. DAC input code range 48 to 4047.  $V_{DACx}$  load  $C_L$  = 10  $\mu$ F.

|                  | PARAMETER                                                          | TEST CONDITIONS                                                                               | MIN   | TYP    | MAX  | UNIT   |

|------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------|--------|------|--------|

| ANALOG           | SIGNAL PATH CHARACTERISTICS (DAG                                   | , Buffer Amplifier, Internal Reference)                                                       |       |        |      |        |

|                  | Resolution                                                         | 05°C . T 400°C                                                                                | 12    |        | 12   | Dita   |

|                  | Monotonic                                                          | -25°C < T <sub>A</sub> < 120°C                                                                | 12    |        |      | Bits   |

| DNL              | Differential non-linearity                                         | $R_L = 100 \text{ k}\Omega, -25^{\circ}\text{C} < T_A < 120^{\circ}\text{C}$                  | -0.99 |        | 1    | LCD    |

| INL              | Integral non-linearity                                             | $R_L = 100 \text{ k}\Omega, -25^{\circ}\text{C} < T_A < 120^{\circ}\text{C}$                  | -1.93 |        | 2.78 | LSB    |

|                  |                                                                    | LDMOS mode, $R_L$ = 100 kΩ,<br>-25°C < $T_A$ < 120°C                                          | -14   |        | 14   |        |

| OE               | Offset error <sup>(1)</sup>                                        | LDMOS mode, $R_L = 100 \text{ k}\Omega$                                                       |       | ±1     |      | mV     |

|                  |                                                                    | GaN mode, $R_L = 100 \text{ k}\Omega$ , $-25^{\circ}\text{C} < T_A < 120^{\circ}\text{C}$     | -16.5 |        | 16.5 |        |

| OETC             | Offset error temperature coefficient (1)(2)                        | $R_L = 100 \text{ k}\Omega, -25^{\circ}\text{C} < T_A < 120^{\circ}\text{C}$                  |       |        | 43   | μV/°C  |

| GE               | Gain error <sup>(1)</sup>                                          | $R_L = 100 \text{ k}\Omega, -25^{\circ}\text{C} < T_A < 120^{\circ}\text{C}$                  | -0.72 |        | 0.74 | %FS    |

| GETC             | Gain error temperature coefficient (1)(2)                          | $R_L = 100 \text{ k}\Omega, -25^{\circ}\text{C} < T_A < 120^{\circ}\text{C}$                  |       |        | 20   | ppm/°C |

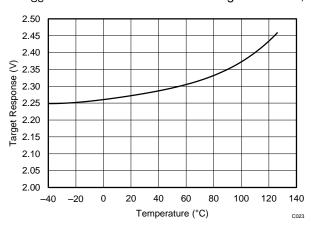

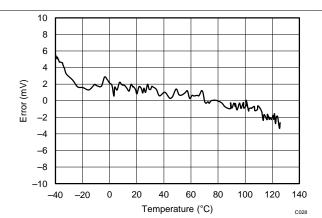

|                  | Residual error after one point calibration <sup>(1)(2)(3)(4)</sup> | BASEx = 1638 (V <sub>DACX</sub> = 2 V at 24°C)<br>-25°C < T <sub>A</sub> < 120°C              | -13.3 |        | 13.3 | - mV   |

| REAOPC           |                                                                    | BASEx = 1638 (V <sub>DACX</sub> = 2 V at 24°C)                                                |       | ±2.4   |      |        |

|                  |                                                                    | BASEx = 819 (V <sub>DACX</sub> = 1 V at 24°C)<br>-25°C < T <sub>A</sub> < 120°C               | -11.3 |        | 11.3 |        |

|                  |                                                                    | BASEx = 819 (V <sub>DACX</sub> = 1 V at 24°C)                                                 |       | ±2.1   |      |        |

| ZCO              | Zana and autout ()/                                                | LDMOS mode, $R_L = 100 \text{ k}\Omega$                                                       |       | 0      |      | mV     |

| 200              | Zero code output (V <sub>DACx</sub> – VSSB)                        | LDMOS mode, I <sub>OUT</sub> = 10 mA                                                          |       | 200    |      |        |

| FSO              | Full-scale output at code 4095 (VDDB –                             | LDMOS mode, $R_L = 100 \text{ k}\Omega$                                                       |       | 10     |      | mV     |

| 130              | V <sub>DACx</sub> )                                                | LDMOS mode, $I_{OUT} = -10 \text{ mA}$                                                        |       | 150    |      | IIIV   |

| Io               | Continuous output current per channel allowed (5)                  | T <sub>A</sub> = 125°C                                                                        |       |        | 10   | mA     |

| ^                | Load capacitance <sup>(5)</sup>                                    | $R_L = 2 \text{ k}\Omega \text{ or } \infty, -25^{\circ}\text{C} < T_A < 120^{\circ}\text{C}$ |       |        | 12   | μF     |

| C <sub>L</sub>   | Load Capacitance V                                                 | $R_L = 2 k\Omega \text{ or } \infty$                                                          |       | 10     |      | μΓ     |

|                  | DAC output resistance                                              | DACCODEx = 2048                                                                               |       | 3      |      | Ω      |

|                  | DAC settling time                                                  | $C_L = 10 \mu F$                                                                              |       | 250    |      | μs     |

| OUTPUT           | SWITCH DC CHARACTERISTICS                                          |                                                                                               |       |        |      |        |

| R <sub>DRV</sub> | On Resistance of the switch between DACx and FETDRVx               | -25°C < T <sub>A</sub> < 120°C                                                                |       |        | 6    | 0      |

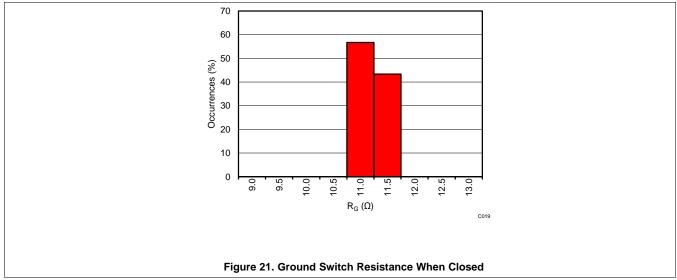

| $R_{G}$          | On Resistance of the switch between FETDRVx and VSSB               |                                                                                               |       | 11     |      | Ω      |

| TEMPERA          | TURE SENSOR CHARACTERISTICS                                        |                                                                                               |       |        |      |        |

|                  | Resolution                                                         |                                                                                               |       | 0.0625 |      | °C/Isb |

| TE               | Temperature sensor error <sup>(2)</sup>                            | $T_A = -40^{\circ}C \text{ to } 120^{\circ}C$                                                 | -3.2  |        | 3.2  | °C     |

|                  | Conversion time                                                    |                                                                                               |       | 25     |      | ms     |

<sup>(1)</sup> The package mechanical stress-induced parameter shift may cause the parts to manifest behavior beyond the specified limits. Mechanical stresses may also arise as a result of the PCB manufacturing process.

Device specification is verified by characterization and is not tested in production.

3) The specification is a calculated worst-case value based on the OE, OETC, GE, and GETC limits.

(5) Parameter based on the process data and circuit simulation.

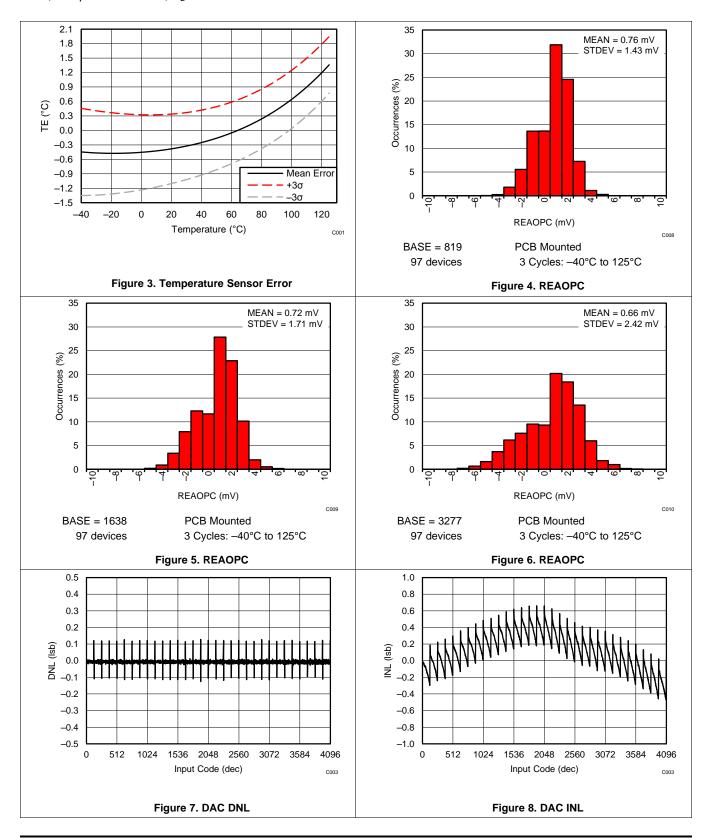

<sup>(4)</sup> The outcome of the REAOPC characterization of the PCB mounted devices is shown in Figure 4, Figure 5, and Figure 6 of the *Typical Characteristics*. The 97, randomly selected, devices from 3 diffusion lots were installed on the 4-layer RO4003 Laminate using Convection Reflow. The Look-Up-Table was set for maximum gain; for example, all DELx = 0xFF. While powered up, the devices were subjected to 3 thermal cycles, from -40°C to 125°C, during which their REAOPC was recorded.

## **Electrical Characteristics (continued)**

Unless otherwise noted: VDD = 5 V  $\pm$ 5%, VIO = 1.8 V to 3.3 V,  $T_A$  = 25°C. VDDB = 5 V  $\pm$ 5%, VSSB = GNDA,  $V_{DACx}$  output range 0 V to 5 V; or VDDB = GNDA, VSSB = -5 V  $\pm$ 5%,  $V_{DACx}$  output range 0 V to -5V. DAC input code range 48 to 4047.  $V_{DACx}$  load  $C_L$  = 10  $\mu$ F.

|                   | PARAMETER                                                   | TEST CONDITIONS                                                                                                                        | MIN          | TYP          | MAX          | UNIT   |  |

|-------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|--------|--|

| EEPRO             | M                                                           |                                                                                                                                        | •            |              |              |        |  |

|                   | Maximum EEPROM write cycles                                 |                                                                                                                                        |              |              | 100          |        |  |

| DIGITA            | L INPUT CHARACTERISTICS (DRVEN0, DF                         | RVEN1, SDA, and SCL)                                                                                                                   |              |              | ,            |        |  |

| $V_{IH}$          | Input high voltage                                          | -25°C < T <sub>A</sub> < 120°C                                                                                                         | 0.7 ×<br>VIO |              |              |        |  |

| $V_{IL}$          | Input low voltage                                           | –25°C < T <sub>A</sub> < 120°C                                                                                                         |              |              | 0.3 ×<br>VIO | V      |  |

|                   | Hysteresis                                                  |                                                                                                                                        |              | 0.2 x<br>VIO |              |        |  |

| $C_{iND}$         | Input capacitance                                           |                                                                                                                                        |              | 5            |              | pF     |  |

| DIGITA            | L INPUT CHARACTERISTICS (A0, A1)                            |                                                                                                                                        | ·            |              |              |        |  |

| $V_{IH}$          | Input high voltage                                          | -25°C < T <sub>A</sub> < 120°C                                                                                                         | 0.7 ×<br>VIO |              |              | V      |  |

| $V_{IL}$          | Input low voltage                                           | -25°C < T <sub>A</sub> < 120°C                                                                                                         |              |              | 0.3 ×<br>VIO | V      |  |

| $R_{UP}$          | Internal pullup resistance                                  |                                                                                                                                        | ·            | 17           |              | kΩ     |  |

| R <sub>DN</sub>   | Internal pulldown resistance                                |                                                                                                                                        | ·            | 17           |              | K22    |  |

|                   | Max external capacitance (5)                                |                                                                                                                                        |              |              | 30           | pF     |  |

| DIGITA            | L OUTPUT CHARACTERISTICS (SDA)                              |                                                                                                                                        | ·            |              |              |        |  |

| \/                | Output low voltage                                          | $I_{OUT} = 4 \text{ mA}, -25^{\circ}\text{C} < T_{A} < 120^{\circ}\text{C}$                                                            |              |              | 0.4          | V      |  |

| $V_{OL}$          |                                                             | I <sub>OUT</sub> = 4 mA                                                                                                                | ·            | 0.16         |              | 7 V    |  |

| I <sub>LEAK</sub> | Open-drain output leakage current with output high $^{(5)}$ | Current from the supply rail through the pullup resistor into the drain of the opendrain output device, –25°C < T <sub>A</sub> < 120°C |              |              | ±1           | μΑ     |  |

| C <sub>OUT</sub>  | Output capacitance                                          |                                                                                                                                        | ·            | 4            |              | pF     |  |

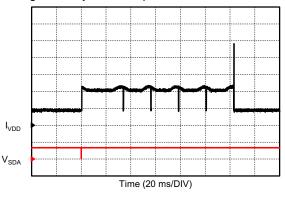

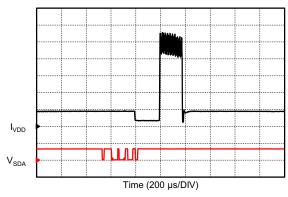

| SUPPL             | Y CURRENT SPECIFICATIONS                                    |                                                                                                                                        |              |              | ,            |        |  |

|                   |                                                             | Normal operation <sup>(6)</sup> , –25°C < T <sub>A</sub> < 120°C                                                                       |              |              | 2.6          |        |  |

| I <sub>DD</sub>   |                                                             | While executing EEPROM BURN <sup>(7)</sup>                                                                                             |              | 4            |              | mA     |  |

| טטי               |                                                             | While transferring EEPROM content to operating memory <sup>(8)</sup>                                                                   |              | 9            |              | 1117 ( |  |

|                   |                                                             | I <sup>2</sup> C inactive, –25°C < T <sub>A</sub> < 120°C                                                                              |              |              | 3            |        |  |

| I <sub>VIO</sub>  |                                                             | I <sup>2</sup> C in fast mode, –25°C < T <sub>A</sub> < 120°C                                                                          |              |              | 3.1          | μA     |  |

| I <sub>VDDB</sub> |                                                             | LDMOS mode, R <sub>L</sub> = ∞, −25°C < T <sub>A</sub> < 120°C                                                                         | ·            |              | 1.5          | m ^    |  |

| I <sub>VSSB</sub> |                                                             | GaN mode, R <sub>L</sub> = ∞, −25°C < T <sub>A</sub> < 120°C                                                                           | -1.4         |              |              | mA     |  |

| PWR<br>(Conv)     | Power consumption, conversion mode                          | All output pins R <sub>L</sub> = ∞                                                                                                     |              | 20           |              | mW     |  |

<sup>(6)</sup> The normal operation current through the VDD excludes the current supplied to the external load, and excludes the current required by the EPPROM BURNS and TRANSFERS.

<sup>(7)</sup> During the EEPROM BURN command execution the device activates internal systems that are not active during the Normal operation. This causes a momentary increase in supply current through the VDDpin. The duration of this temporary surge in supply current is typically 125 ms.

<sup>(8)</sup> During the data transfer from the EEPROM to the Operating memory there will be a momentary surge in supply current through the VDD pin. The duration of this surge is typically 200 µs.

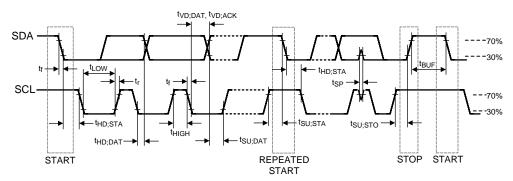

## 7.6 Timing Requirements

Unless otherwise noted: VDD = 5 V  $\pm$ 5%, VIO = 1.8 V to 3.3 V. VDDB = 5 V  $\pm$ 5%, VSSB = GNDA; or VDDB = GNDA, VSSB = -5V  $\pm$ 5%.

|                     | PARAMETER                                                         | TEST CONDITIONS                                       | MIN | MAX | UNIT |

|---------------------|-------------------------------------------------------------------|-------------------------------------------------------|-----|-----|------|

|                     | I <sup>2</sup> C clock frequency                                  |                                                       | 10  | 400 | kHz  |

| t <sub>LOW</sub>    | Clock low time                                                    |                                                       | 1.3 |     |      |

| t <sub>HIGH</sub>   | Clock high time                                                   |                                                       | 0.6 |     |      |

| t <sub>HD-STA</sub> | Hold time repeated START condition                                | After this period, the first clock pulse is generated | 0.6 |     | μs   |

| t <sub>SU;STA</sub> | Setup time for a repeated START condition                         |                                                       | 0.6 |     |      |

| t <sub>HD;DAT</sub> | Data hold time (Note x and y)                                     |                                                       | 0   | 900 |      |

| t <sub>SU;DAT</sub> | Data setup time                                                   |                                                       | 100 |     | ns   |

| t <sub>f</sub>      | SDA fall time                                                     | $I_L \le 3 \text{ mA and } C_L \le 400 \text{ pF}$    |     | 250 |      |

| t <sub>SU;STO</sub> | Setup time for STOP condition                                     |                                                       | 0.6 |     |      |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                  |                                                       | 1.3 |     | μs   |

| C <sub>b</sub>      | SDA capacitive load                                               |                                                       |     | 400 | pF   |

| t <sub>SP</sub>     | Pulse width of spikes that must be suppressed by the input filter |                                                       |     | 50  | ns   |

|                     | SCL and SDA timeout                                               |                                                       | 25  | 35  | ms   |

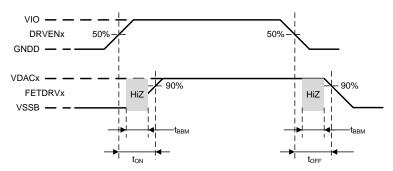

## 7.7 Output Switching Characteristics

Unless otherwise noted: VDD = 5 V  $\pm$ 5%, VIO = 1.8 V to 3.3 V. VDDB = 5 V  $\pm$ 5%, VSSB = GNDA; or VDDB = GNDA, VSSB = -5V  $\pm$ 5%.

|                     | PARAMETER                 | TEST CONDITIONS                              | MIN | TYP | MAX | UNIT |

|---------------------|---------------------------|----------------------------------------------|-----|-----|-----|------|

| t <sub>ON</sub>     | On time                   | DACCODE: 4005 B 400 kO                       |     | 50  |     |      |

| t <sub>OFF</sub>    | Off time                  | DACCODEx = 4095, $R_L = 100 \text{ k}\Omega$ |     | 50  |     | ns   |

| t <sub>BBM</sub>    | Break-before-make time    |                                              |     | 15  |     |      |

| C <sub>FETDRV</sub> | FETDRV output capacitance |                                              |     | 10  |     | pF   |

Figure 1. I<sup>2</sup>C Timing

Figure 2. Switching

## TEXAS INSTRUMENTS

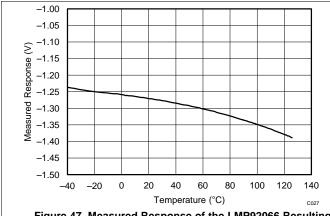

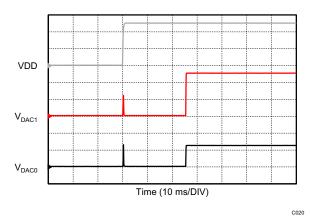

## 7.8 Typical Characteristics

Unless otherwise stated the plot data was collected under these conditions: VDD = 5 V, VDDB = 5 V, VSSB = GNDA, VIO = 3.3 V, Temperature =  $24^{\circ}\text{C}$ ,  $R_L = 100 \text{ k}\Omega$ .

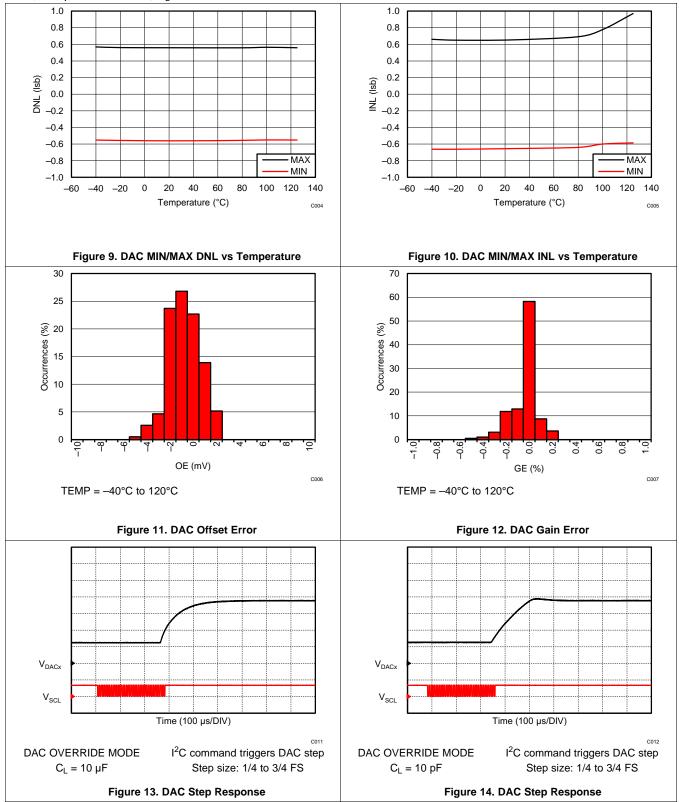

## **Typical Characteristics (continued)**

Unless otherwise stated the plot data was collected under these conditions: VDD = 5 V, VDDB = 5 V, VSSB = GNDA, VIO = 3.3 V, Temperature =  $24^{\circ}\text{C}$ ,  $R_L = 100 \text{ k}\Omega$ .

## TEXAS INSTRUMENTS

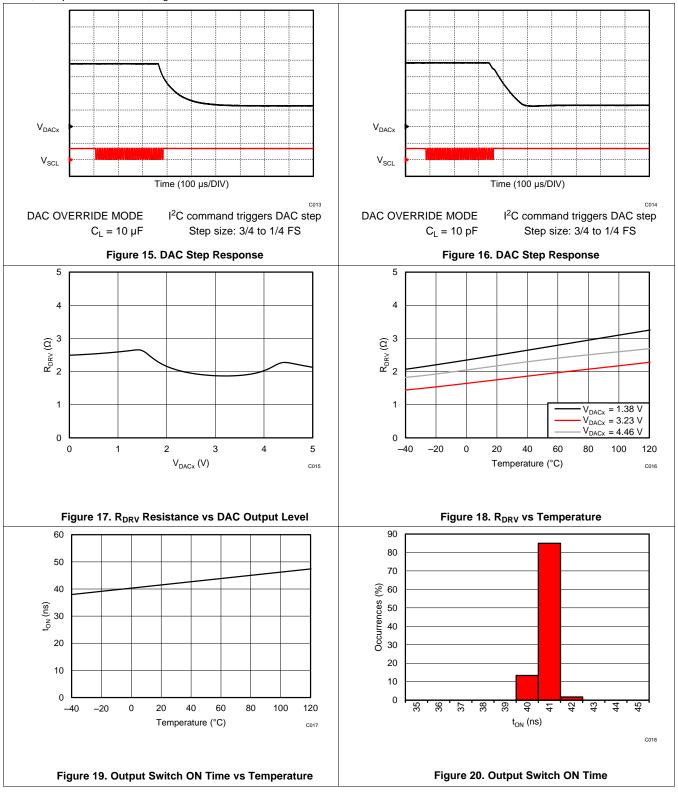

## **Typical Characteristics (continued)**

Unless otherwise stated the plot data was collected under these conditions: VDD = 5 V, VDDB = 5 V, VSSB = GNDA, VIO = 3.3 V, Temperature =  $24^{\circ}$ C,  $R_L$  =  $100 \text{ k}\Omega$ .

## **Typical Characteristics (continued)**

Unless otherwise stated the plot data was collected under these conditions: VDD = 5 V, VDDB = 5 V, VSSB = GNDA, VIO = 3.3 V, Temperature = 24°C,  $R_L$  = 100 k $\Omega$ .

#### 8 Detailed Description

#### 8.1 Overview

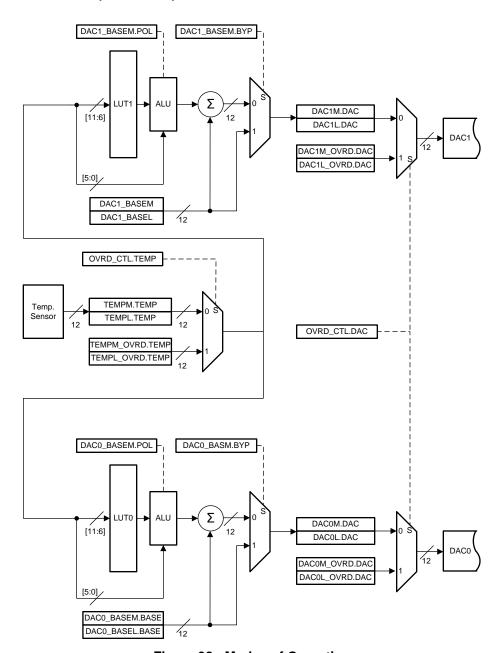

The LMP92066 is a dual temperature-dependent bias generator whose temperature-to-voltage transfer functions are user defined. The device contains a digital temperature sensor that addresses two independently programmable Look-Up-Tables (LUTs). The outputs of LUTs are sent on to their respective 12-bit DACs to produce two independent output voltages. For added flexibility the device can be configured to provide bias potential above or below GNDA.

In applications requiring rapid ON/OFF switching of the bias voltage, the LMP92066 provides asynchronous control over its outputs. Dedicated digital input pins control analog output switching.

All aspects of the device functionality are controlled through internal registers. These registers, and the LUTs, are accessible through the I<sup>2</sup>C-compatible interface.

The LMP92066 can operate autonomously of the system controller, once LUT coefficients have been committed to its non-volatile memory, EEPROM. Upon power up the EEPROM content is automatically transferred to the operating memory, and the device begins to produce required bias voltage.

#### 8.2 Functional Block Diagram

#### 8.3 Features Description

#### 8.3.1 Temperature Sensor

The onboard digital temperature sensor produces 12-bit, twos complement output, where the LSB represents +0.0625°C, and MSB represents -128°C. The output of the temperature sensor is stored in the TEMPM and TEMPL registers. These registers are updated automatically once the temperature sensor completes a new conversion, approximately every 25 ms. The temperature sensor begins operation immediately after the supply voltage at VDD has reached its minimum operating level. Initially, right after power up, TEMPM and TEMPL registers contain 0s. The first measurement result is loaded into TEMPM and TEMPL registers 25 ms after power up.

**Table 1. Temperature Sensor Output**

| TEMPERATURE SENSOR OUTPUT {TEMPM[3:0], TEMPL[7:0]} | TEMPERATURE (°C) |

|----------------------------------------------------|------------------|

| 10000000000                                        | -128.0000        |

| 111001000000                                       | -28.0000         |

| 11111111111                                        | -0.0625          |

| 0000000001                                         | 0.0625           |

| 000110000000                                       | 24.0000          |

| 01111111111                                        | 127.9375         |

#### **NOTE**

The maximum output of the temperature sensor stored in the TEMPM and TEMPL registers is 127.9375°C.

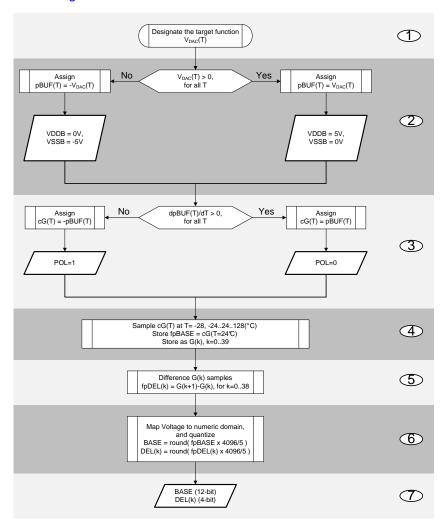

#### 8.3.2 Look-Up-Table (LUT) and Arithmetic-Logic Unit (ALU)

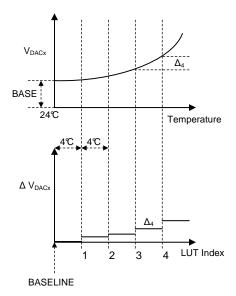

The LUT is used to create an arbitrary transfer function which maps the temperature to the analog output of the device. In concept, the temperature readout is used as a pointer to a table of discrete values that are representative of the samples of the desired temperature-dependent function.

In order to minimize the storage requirements, the LMP92066 LUTs are indexed in 4°C increments. Also, the stored values are only the increments, or first derivatives ( $\Delta$ s) of the modeled transfer function. The internal ALU reconstructs the original transfer function by integrating the coefficients stored in the LUTs. The errors due to the coarseness of the temperature quantization are significantly reduced through the use of linear interpolation, which is also implemented in the ALU.

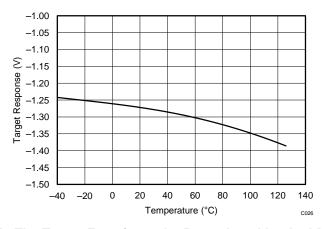

Consider the example shown in Figure 22. The target output vs temperature is shown in the top graph.  $V_{DACx}$  is a smooth, monotonic function with, ideally, infinite precision. The LUT stores only the increments, or the rise, within each 4°C interval.

In order to recreate the original transfer function, the series of increments must be summed together and added to the constant BASE value. BASE represents the constant offset which is lost due to the differentiation - storage of the increments only. This process must also be referenced to the common temperature point. This reference temperature is called BASELINE in this document, and is fixed at 24°C.

Figure 22. Original Transfer Function

The LUT and ALU Organization, LUT Coefficient to Register Mapping, and The LUT Input and Output Ranges sections below detail the operation of the LUTs and the ALUs.

#### 8.3.2.1 LUT and ALU Organization

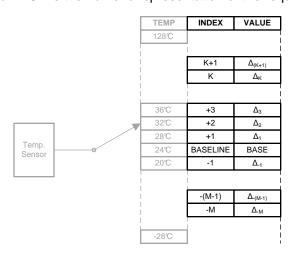

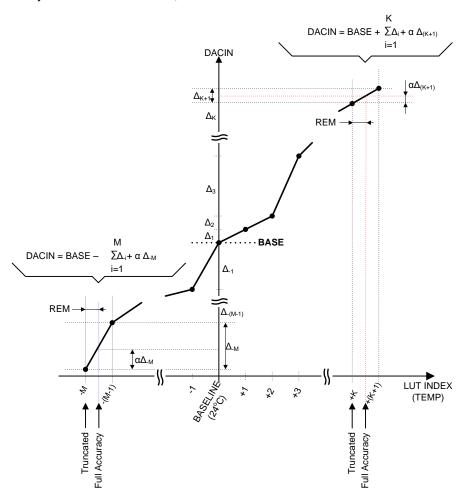

In Figure 23 TEMP represents the 12-bit input value to the LUT. This value is produced by the local temperature sensor, or it can be provided by the user through the use of the OVERRIDE registers. The OVERRIDE modes are described in the later sections.

TEMP is truncated, and TEMP[11:6] is used to index the LUT. The truncation is equivalent to reducing the TEMP resolution from 0.0625°C/LSB to 4°C/LSB.

The overall transfer function is stored in the LUT as a set of unsigned 4-bit increments from the BASE value, that is, LUT location (+1) stores the value of the increment  $\Delta_1$ . This is shown in Figure 23. The BASELINE is 24°C temperature reference point, and BASE is the numeric representation of the required output at 24°C

Figure 23. LUT Organization

When TEMP is above 24°C, the LUT is addressed above the BASELINE address, all increments are added to the BASE value to produce numeric equivalent of the analog output. When TEMP is below 24°C, LUT is addressed below the BASELINE, all increments are subtracted from the BASE value to produce DACIN.

Interpolation function is implemented in the ALU that follows the LUT. The truncated lower bits of the TEMP value, REM = TEMP[5:0], are used to interpolate between data points stored in the LUT. A portion of increment,  $\alpha\Delta i$ , is added to form the final numeric output - the input data to the DAC. The factor  $\alpha$  is a fraction of 4°C temperature span, or equivalently it is a fraction of the 64-code temperature span.

$$\alpha = \frac{\mathsf{REM}}{\mathsf{64}} \tag{1}$$

The process of calculating the DACIN, including the interpolation, is depicted in Figure 24. The DACIN is the final 12-bit value produced by the ALU and the LUT, and forwarded to the DAC for conversion to analog domain.

Figure 24. DACIN Calculation

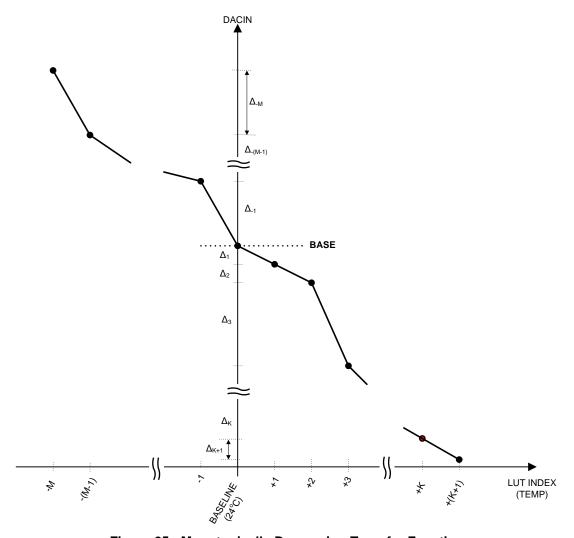

Up to this point the algorithm description concerned only the generation of the monotonically increasing transfer function. The device can also produce monotonically decreasing transfer function by setting the DACx\_BASEM.POL bit.

The effect of polarity reversal (POL = 1) on the overall transfer function is shown in Figure 25. The LUT content is unchanged from the original example above. Note that now the LUT values stored at locations above BASELINE address are subtracted from BASE value, and the LUT values stored at locations below BASELINE address are added to the BASE value.

Figure 25. Monotonically Decreasing Transfer Function

The expressions used in the calculation of the transfer function are summarized below:

## LUT index > BASELINE:

DACIN = BASE +

$$(-1)^{POL} \left( \sum_{i=1}^{K} \Delta_i + \alpha \Delta_{(K+1)} \right)$$

(2)

## LUT index < BASELINE:

DACIN = BASE

$$-(-1)^{POL} \left( \sum_{i=1}^{M} \Delta_{-i} - \alpha \Delta_{-M} \right)$$

(3)

#### 8.3.2.2 LUT Coefficient to Register Mapping

For the sake of convenience the preceding sections referred to LUT coefficients as  $\Delta_K$ . These are stored in the operating memory in the registers DELx. This is reflected in the Register Map section of this document. The example of the  $\Delta_K$  to DELx register mapping is shown in Table 2 section below.

| TEMPERATURE | FUNCTION INCREMENT | REGISTER ASSIGNMENT |  |  |

|-------------|--------------------|---------------------|--|--|

| –28°C       | Δ_13               | DEL0                |  |  |

| ↓           | ↓                  | <b>↓</b>            |  |  |

| 20°C        | Δ_1                | DEL12               |  |  |

| 28°C        | $\Delta_{+1}$      | DEL13               |  |  |

| <b>↓</b>    | <u> </u>           | <b>↓</b>            |  |  |

| 124°C       |                    |                     |  |  |

| 128°C       | Δ <sub>+26</sub>   | DEL38               |  |  |

Table 2. AK to DELx Register Mapping

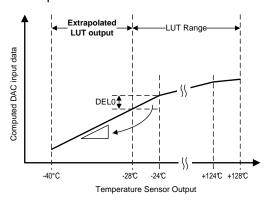

#### 8.3.2.3 The LUT Input and Output Ranges

The programmable LUT input range spans temperatures  $-28^{\circ}$ C to  $128^{\circ}$ C. For the temperatures below  $-28^{\circ}$ C the LUT output is linearly extrapolated; that is, the increment  $\Delta_{-13}$  (register DEL0) stored at the location corresponding to  $-28^{\circ}$ C is used as the slope down to  $-40^{\circ}$ C.

Figure 26. Temperature Sensor Output

Although the maximum output of the temperature sensor is 127.9375°C, the LUT index corresponding to 128°C (DEL38) is required for proper interpolation when the temperature is above 124°C.

The increments stored in the LUT are 4-bit unsigned values. This limits the maximum slope of the transfer function stored in the LUT to:

$$SLOPE_{MAX} = \frac{16LSB}{4^{\circ}C} = \frac{4LSB}{^{\circ}C}$$

(4)

Given this slope limit imposed by the LUT structure, and the fact that the LUT input range is 156°C (from –28°C to 128°C), the maximum output range of the LUT due to the temperature sensor input is 624 LSBs, for the given BASE value.

#### **NOTE**

The maximum span of 624 codes can reside anywhere within the 0 to 4095 code space of the 12-bit DAC input. The total input code to the DAC is the sum of the increments ( $\Delta$ s) and the 12-bit BASE value.

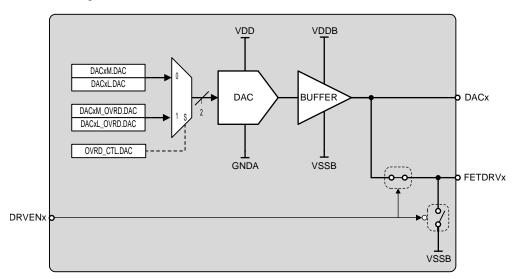

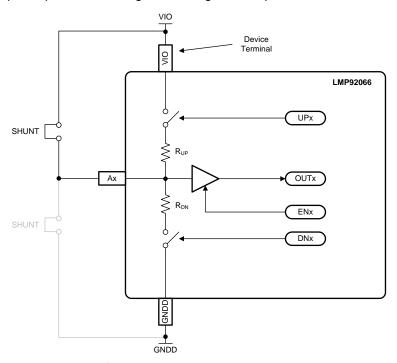

#### 8.3.3 Analog Signal Path

The simplified schematic of one analog channel of the device is shown in Figure 27. The LMP92066 contains 2 such channels. The following sub-sections describe each of the individual blocks within a channel.

Figure 27. One Analog Channel Simplified Schematic

#### 8.3.3.1 DAC

The DAC produces unipolar output voltage proportional to the 12-bit input code. The input code format is offset binary, where 0x000 represents minimum and the 0xFFF full-scale input. The input code is produced by the LUT/ALU and stored in the DACxM and DACxL read-only registers. The user can also insert the DAC input code via the DACxM\_OVRD and DACxL\_OVRD registers, and by setting the OVRD\_CTL.DAC bit. The DAC is referenced to the internally generated 5 V.

The DAC transfer functions:

$$V_{DACx} = 5A \frac{DACIN}{4096} (V)$$

(5)

Where A is the Buffer Amplifier gain (see Buffer Amplifier) and DACIN is the 12-bit input code stored in either:

The LUT Input and Output Ranges describes the maximum output code span of the LUT, for the given base value. This also implies that when DACxM and DACxL registers are selected as the DAC inputs, the maximum  $V_{DACx}$  output excursion over temperature is:

$$dV_{DACx} = SLOPE_{MAX} \times T_{RANGE} \times V_{LSB} = \frac{4LSB}{C} \times 156 C \times \frac{5V}{4096} = 762 \text{mV}$$

(6)

However, this limitation is lifted when using DACxM\_OVRD and DACxL\_OVRD registers as the DAC inputs. In this case the DAC input range is full 4096 codes, and the output spans 0 V to 5 V.

#### 8.3.3.2 Buffer Amplifier

The buffer amplifier provides the low impedance drive for the potential generated by the DAC. The output of the amplifier is always available at the DACx output pin of the device. The buffer is designed to drive large capacitive loads, as high as 10  $\mu$ F.

The structure of the Buffer is such that it can produce output voltages above or below GNDA potential. Both Buffer Amplifiers are biased from dedicated supply rails: VDDB and VSSB. The difference between the VDDB and VSSB is nominally 5 V, but the span can be above or below GNDA. The gain A of the Buffer Amplifier depends on the state of supply rails VDDB and VSSB.

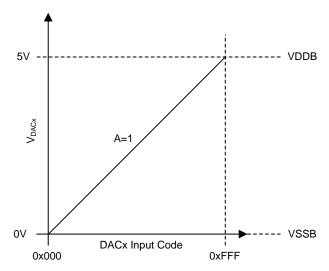

When the span is above GNDA, or VDDB = 5 V and VSSB = 0 V, then the output buffer gain is A = 1. The net effect on the output of the analog processing chain is shown in Figure 28. The DAC input codes in the range of  $0 \times 0.000 \times 0.00$

Figure 28. Output of Analog Processing Chain: Net Effect

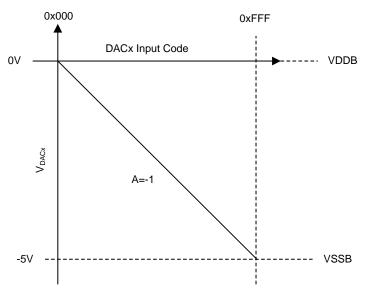

If the span is below GNDA, or VDDB = 0 V and VSSB = -5 V, then the output buffer gain is A = -1. This configuration is depicted Figure 29. This results in effective mapping of the DAC input codes in the range of 0x000 to 0xFFF, to the output voltage range of 0 V to -5 V.

Figure 29. Common Mode Voltage Below GNDA, or VDDB = 0 V and VSSB = -5 V

#### **NOTE**

Both Buffer Amplifiers share the VDDB and VSSB rails. Therefore, both Buffers produce gain of A = 1, or both produce gain of A = -1.

The state of the VDDB and VSSB supplies, whether their span is above or below GNDA is indicated by the state of the DRV\_STATUS.GAN bit, and can be read by the controller via the I<sup>2</sup>C interface.

#### 8.3.3.3 Output On and Off Control

The LMP92066 facilitates rapid turnon and shutdown of the downstream devices. The FETDRVx outputs can be switched ON or OFF by the DRVENx input, independently of the I<sup>2</sup>C bus transactions. The FETDRVx pin is driven by the Buffer amplifier when the corresponding DRVENx input pin is asserted HIGH. Otherwise, the FETDRVx pin is connected to VSSB.

The control and switch design was optimized for minimum delay between the DRVENx input and the FETDRVx switching. The design also ensures that during the state transition there exists an instance when both switches at FETDRVx are open; that is, no possibility for the crow-bar current to flow from the Buffer output to VSSB.

The switches are assured to default to the state where FETDRVx output is connected to VSSB at power up, as long as logic 0 is present at the DRVENx input.

#### 8.3.4 Memory

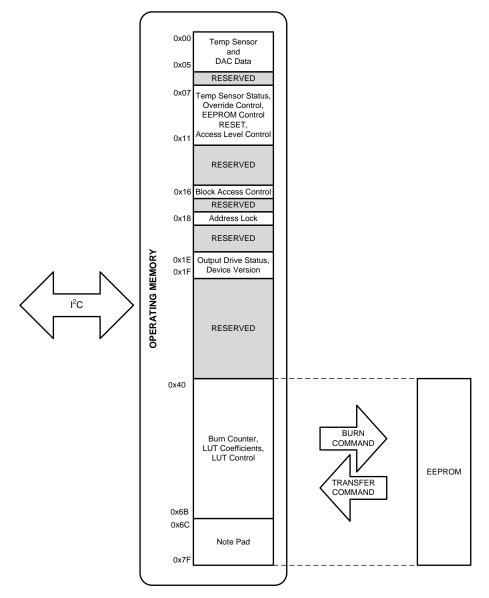

The internal memory of the device consists of 2 distinct areas: the user register set or operating memory and the EEPROM (non-volatile storage).

The operating memory registers provide the control over device functionality, report internal status of the device, and store the signal path data (LUT, temperature sensor output, etc). A section of operating memory, designated as a SCRATCH PAD, is available for arbitrary data storage. All operating memory locations are directly accessible to the user via the  $l^2C$  bus.

The EEPROM is not directly accessible via the  $l^2C$  bus. The EEPROM acquires its data via the transfer from the operating memory, upon user issued command.

Sections READ and WRITE Access, Access Control, LUT, NOTEPAD Storage, and EEPROM, and Figure 30 detail the internal memory functionality.

#### 8.3.4.1 READ and WRITE Access

The operating memory consists of individually addressable bytes whose content can be accessed via a single  $I^2C$  transaction. For 8-bit data, as soon as the  $I^2C$  transfer is complete the transferred value takes effect.

The device also uses values longer that 8 bits — for example, with Temperature Sensor output, Temperature Sensor Override input, and the DAC input and Override registers are 12-bit values which require storage in 2 adjacent registers. For these values any access should start with the register containing the upper 4 bits, immediately followed by the access to the lower byte.

#### **NOTE**

It is the WRITE of the lower byte that results in the update of the 12-bit value. See Table 3.

#### Table 3. Block Writing

| I <sup>2</sup> C OPERATION | REGISTER   | DATA | DESCRIPTION                                                                                                                                                                                                                                                                      |

|----------------------------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WRITE                      | BLK_CNTL   | 0x8F | Enable the BLOCK access and set the block length to 15. This transfer results in the <b>immediate update</b> of the BLK_CNTL register and immediate change of behavior of the I <sup>2</sup> C interface.                                                                        |

| WRITE                      | TEMPM_OVRD | 0x08 | Write the upper nibble of the Temperature Sensor override value. This transaction <b>does not result in the update</b> of the TEMPM_OVRD register. The transferred value is placed on a queue awaiting the transfer of the lower byte. The output of the device is not affected. |

| WRITE                      | TEMPL_OVRD | 0x00 | Write the lower byte of the Temperature Sensor override value. This transaction <b>results in the update of both</b> the TEMPM_OVRD and TEMPL_OVRD registers. The output of the device changes accordingly with the new setting.                                                 |

#### 8.3.4.2 Access Control

By default, all operating memory locations are open to READ access. The WRITE access is controlled by the Access Level setting. Increasing the Access Level, broadens the scope of the WRITE access. There are 3 access levels available to the user; see *Access Control*.

User can change the current Access Level by writing a "password" sequence to the ACC\_CNTL register. The "password" sequences are 2 consecutive I<sup>2</sup>C byte transfers to the ACC\_CNTL register. The data content of each 2 byte transfer is unique for each access level.

For example, to enter access level L2 perform the following 2 transfers:

| I <sup>2</sup> C OPERATION | REGISTER | DATA | DESCRIPTION                                                                                                                                          |

|----------------------------|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| WRITE                      | ACC_CNTL | 0xCD | First byte of the "password".                                                                                                                        |

| WRITE                      | ACC_CNTL | 0xF0 | Second byte of the "password". After this transfer is completed the access level is changed to L2.                                                   |

| READ                       | ACC_CNTL | 0x03 | Optional: Reading the ACC_CNTL serves as status report. The possible returned values are: 0x00 – access level L0 0x01 – access level L1 is activated |

**Table 4. Memory Access Control**

#### **Table 5. EEPROM Access Levels**

0x03 - access level L2 is activated (and due to

nesting, L1 is also indicated)

| ACCESS LEVEL | SCOPE                                                                                     |

|--------------|-------------------------------------------------------------------------------------------|

| LO           | Default. User has READ access only to all locations in the operating memory.              |

| L1           | User has READ access to all locations, and WRITE access to ADR_LK and BLK_CNTL registers. |

| L2           | User has READ and WRITE access to all operating memory locations.                         |

#### **NOTE**

The access levels are nested. This means that L1 access level also gives all L0 level functionality. L2 access level provides L1 and L0 functionality.

#### 8.3.4.3 LUT, NOTEPAD Storage, and EEPROM

The LUT (its coefficients, BASE value, ALU control bits) and the NOTEPAD are stored in the operating memory block spanning addresses 0x40 through 0x7F. This space is directly accessible (READ and WIRITE) via the I<sup>2</sup>C bus.

There is an option to store the LUT and the NOTEPAD in the non-volatile memory, EEPROM. The move of data from the operating memory to the EEPROM (BURN) is initiated by WRITING a command byte to the EEPROM\_CNTL register.

Upon power up the device automatically executes the TRANSFER of the EEPROM data to the operating memory. The user can also issue a command via the I<sup>2</sup>C bus to force the TRANSFER of data from the EEPROM to the operating memory.

**Table 6. EEPROM Control**

| TRANSFER/BURN | I <sup>2</sup> C OPERATION | REGISTER    | DATA | COMMENT                                                   |

|---------------|----------------------------|-------------|------|-----------------------------------------------------------|

| TRANSFER      | WRITE                      | EEPROM_CNTL | 0x4E | Transfer of data from the EEPROM to the operating memory. |

| BURN          | WRITE                      | EEPROM_CNTL | 0xE4 | Transfer of data from the operating memory to the EEPROM. |

The READ of the EEPROM\_CNTL register returns the status of the BURN or TRANSFER.

Table 7. Status of BURN or TRANSFER

| EEPROM_CNTL BIT FIELD | DESCRIPTION                                                                                                                               |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| RDYB                  | 0 - The TRANSFER or BURN has completed 1 – The TRANSFER or BURN is in progress                                                            |

| COR                   | 1 – A bit error was detected during the transfer from EEPROM to the operating memory. The error has been corrected and the data is valid. |

| UCOR                  | 1 – A bit error was detected during the transfer from EEPROM to operating memory. The error was not corrected. LUT data is compromised.   |

Figure 30. Memory-to-EEPROM Mapping

#### 8.3.5 I<sup>2</sup>C Interface

I<sup>2</sup>C bus is used for communication between the Master (the digital supervisor; for example, the microcontroller) and the Slave (LMP92066). This interface provides the user full access to all Data, Status, and Control registers of the device.

LMP92066 supports Standard-mode and Fast-mode, 100 kbit/s and 400 kbit/s, respectively.

All transactions follow the format:

- · Master begins all transactions by generating START condition.

- · All transfers comprise 8-bit bytes.

- First byte following START must contain 7-bit Slave address.

- First byte is followed by a READ/WRITE bit.

- All subsequent bytes contain 8-bit data.

- By default, the device assumes 1-byte data transfers. Block access can be enabled via BLK\_CNTL register, resulting in multi-byte transfers.

- · Bit order within a byte is always MSB first

- ACK/NAK condition follows every byte transfer this can be generated by either Master or the Slave depending on direction of data transfer.

- STOP condition generated by the MASTER terminates all transactions, and resets the I<sup>2</sup>C bus. LMP92066 resets its internal address pointer to 0x00.

#### 8.3.5.1 Supported Data Transfer Formats

Table 8 lists all conditions defined by the I<sup>2</sup>C specification and supported by this device. All following bus descriptions refer to the symbols listed in Table 8.

Table 8. I<sup>2</sup>C Symbol Set

| CONDITION                | SYMBOL | SOURCE       | DESCRIPTION                                                                                                                                           |

|--------------------------|--------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| START                    | S      | Master       | Begins all bus transactions                                                                                                                           |

| STOP                     | Р      | Master       | Terminates all transations and resets bus                                                                                                             |

| ACK (Acknowledge)        | Α      | Master/Slave | Handshaking bit (LOW)                                                                                                                                 |

| NAK (Not<br>Acknowledge) | Ā      | Master/Slave | Handshaking bit (HIGH)                                                                                                                                |

| READ                     | R      | Master       | Active HIGH bit that follows immediately after the slave address sequence. Indicates that the master is initiating the slave-to-master data transfer. |

| WRITE                    | ₩      | Master       | Active LOW bit that follows immediately after the slave address sequence. Indicates that the master is initiating the master-to-slave data transfer.  |

| REPEATED START           | Sr     | Master       | Generated by master, same function as the START condition (highlights the fact that STOP condition is not strictly necessary.)                        |

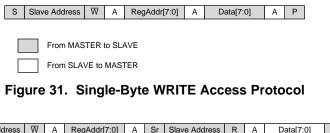

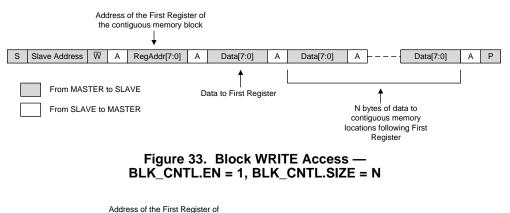

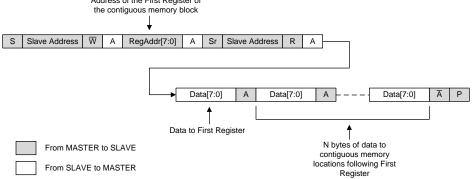

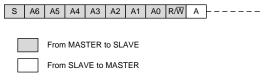

The single data byte transfers are shown in Figure 31 and Figure 32:

S Slave Address W A RegAddr[7:0] A Sr Slave Address R A Data[7:0] A P

From MASTER to SLAVE

From SLAVE to MASTER

Figure 32. Single-Byte READ Access Protocol

Block Access functionality is provided to minimize the transfer overhead of large data sets. By default the LMP92066 is ready to accept multi-byte transfers. Until the transaction is terminated by the STOP condition, the device will READ (WRITE) the subsequent memory locations.

The size of the contiguous block can be limited by the user. This functionality can be enabled by setting BLK\_CNTL.EN bit. The 7-bit value of BLK\_CNTL.SIZE=N sets the size of the contiguous memory block that can be accessed via the block transfer.

If the Master generates a block transfer that is larger than (BLK\_CNTL.SIZE + 1), the internal register pointer wraps around to the First Register address and the access continue to subsequent memory locations. The examples of the block WRITE and READ transactions are shown below in Figure 33 and Figure 34:

Figure 34. Block READ Access — BLK\_CNTL.EN = 1, BLK\_CNTL.SIZE = N

#### 8.3.5.2 Slave Address Selection

The I<sup>2</sup>C bus slave address is selected by installing shunts from A0 and A1 pins of the device to the VIO or GNDD rails. The device discerns between 3 possible options for each pin: shunt to VIO, shunt to GNDD, or left not connected (floating), for the total of 9 possible slave addresses.

The state of the A0 and A1 pins is tested after every occurrence of START condition on the I<sup>2</sup>C bus. However, the user has an option to LOCK the acquired address by setting the ADR\_LK.EN bit. Once the address is locked, the device stores its Slave address internally and does not attempt to decode the address during subsequent I<sup>2</sup>C transactions. The address lock can be disabled by resetting ADR\_LK.EN bit. The device resets the ADR\_LK.EN upon power up.

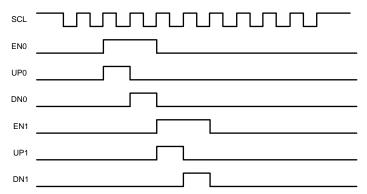

Figure 35 and Figure 36 illustrate the operation of the address decoder circuit. The device internally attempts to pull up, and then pull down, the Ax pin while monitoring the voltage at that pin. If the shunts are installed, the weak pull-ups or pull-downs does not affect the voltage at the Ax pin; that is. the state is fixed by the shunt. If the Ax pin floats, then pull-up and pull-down change the voltage at that pin.

Figure 35. I<sup>2</sup>C Address Decoder - Simplified Diagram

The address decoder operates during 2nd through 4th cycles of the SCL. The decoding of the state of Ax pins is performed serially; that is, A0 is decoded first then A1. The functional diagram of the address decoder is shown in Figure 36.

Figure 36. I<sup>2</sup>C Address Decoder - Functional Diagram

The interpretation of the OUTx values produced from the test phases is summarized in the following table. For example: if a shunt is present between Ax and VIO (first case in the table), both UPx phase and DNx phase result in OUTx being decoded as logical 1, unambiguously indicating the presence of the shunt to VIO, or HI state of Ax.

**Table 9. Address Decoder Output**

|                                   | TEST P  | HASE | DECODED Av.  |  |

|-----------------------------------|---------|------|--------------|--|

|                                   | UPx DNx |      | DECODED Ax ↓ |  |

| SHUNT to VIO: OUTx $\rightarrow$  | 1       | 1    | HI           |  |

| SHUNT to GNDD: OUTx $\rightarrow$ | 0       | 0    | LO           |  |

| NO SHUNT: OUTx →                  | 1       | 0    | N.C.         |  |

The mapping from the decoded Ax states to the I<sup>2</sup>C Slave address is shown in Table 10.

**Table 10. Slave Address Space**

| DEVIC | CE PINS | I <sup>2</sup> C SLAVE ADDRESS |  |

|-------|---------|--------------------------------|--|

| A1    | Α0      | [A6:A0]                        |  |

| LO    | LO      | 0111111                        |  |

| LO    | N.C.    | 1000000                        |  |

| LO    | HI      | 1000001                        |  |

| N.C.  | LO      | 1000010                        |  |

| N.C.  | N.C.    | 1000011                        |  |

| N.C.  | HI      | 1000100                        |  |

| HI    | LO      | 1000101                        |  |

| HI    | N.C.    | 1000110                        |  |

| HI    | HI      | 1000111                        |  |

The Slave Address alignment within the first byte following the START condition is shown in Figure 37:

Figure 37. Slave Address Alignment

#### 8.4 Device Functional Modes

The numeric signal path is shown in Figure 38. The signal flow is generally from left to right: the system input is the temperature sensor, signal processing is done by the LUT/ALU, and the output is driven by the DACs - DAC detail is omitted as DACs provide a conversion from numeric domain to voltage domain only, and they do not affect the signal flow.

There are a number of multiplexers in the signal path which alter the data flow when their respective control bits are set. The multiplexer states, and thus modes of device operation, are described in further detail below.

#### **Device Functional Modes (continued)**

Figure 38. Modes of Operation

#### 8.4.1 Default Operating Mode

This mode of operation is active upon power up. By default the OVRD\_CTL.TEMP and OVRD\_CTL.DAC are cleared. The temperature sensor continuously updates readings every 25 ms (registers: TEMPM, TEMPL). Each temperature sensor update triggers the ALU to re-calculate its output using the user defined coefficients stored in the LUT. The ALU output is passed on to the DACs (registers: DACxM, DACxL) which ultimately drive the V<sub>DACx</sub> outputs. All of the functionality described here occurs automatically, without intervention from the system controller, as long as the power is applied to the device supply pins: VDD, VIO, and VDDB.

#### **Device Functional Modes (continued)**

#### 8.4.2 Temperature Sensor Override

The temperature sensor output can be overridden by the externally supplied data. This capability may be used to verify the validity of the function stored in the LUT. The externally supplied data can act as the temperature sweep input and the output response due to temperature may be readily observed, without actually altering the temperature of the test setup.

This functionality is facilitated by the multiplexer that follows the temperature sensor, and user writable data registers TEMPM\_OVRD and TEMPL\_OVRD. TEMPM\_OVRD[3:0] is the upper nibble of the temperature data. TEMPL\_OVRD[7:0] is the lower byte of the temperature data. The multiplexer control signal is the OVRD\_CTL.TEMP bit.

Table 11 shows an example of the I<sup>2</sup>C bus transfer sequence which results in externally supplied data indexing the LUT.

Table 11. I<sup>2</sup>C Bus Transfer Sequence: Externally Supplied Data Indexing LUT

| I <sup>2</sup> C OPERATION | REGISTER   | DATA | DESCRIPTION                                                                                                                                                                                                                            |

|----------------------------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WRITE                      | ACC_CNTL   | 0xCD | First byte of the "password"                                                                                                                                                                                                           |

| WRITE                      | ACC_CNTL   | 0xF0 | Second byte of the "password". After this transfer is completed the access level is changed to L2                                                                                                                                      |

| READ                       | ACC_CNTL   | 0x03 | Optional: Reading the ACC_CNTL serves as status report. 0x03 – access level L2 is activated (and due to nesting, L1 is also indicated)                                                                                                 |

| WRITE                      | TEMPM_OVRD | 0x01 | Writes 0x1 as the value of the top nibble of the 12-bit, twos complement, temperature value. After this transaction the TEMPM_OVRD register is not updated, yet. The update takes place only after the TEMPL_OVRD register is written. |

| WRITE                      | TEMPL_OVRD | 0x01 | Writes 0x01 into the lower byte of temperature value. After this transaction completes both TEMPM_OVRD and TEMPL_OVRD registers are updated. The 12-bit value in this example is 0x101 which corresponds to 16.0625°C                  |

| WRITE                      | OVRD_CTL   | 0x01 | Sets the OVRD_CTL.TEMP bit. This causes the temperature stored in the TEMPM_OVRD and TEMPL_OVRD to index the LUT.                                                                                                                      |

| READ                       | TEMPM      | 0x** | Optional:                                                                                                                                                                                                                              |

| READ                       | TEMPL      | 0x** | Read the actual temperature reported by the temperature sensor.                                                                                                                                                                        |

The temperature sensor override is cancelled by clearing the OVRD\_CTL.TEMP bit.

#### NOTE

TEMPM\_OVRD, TEMPL\_OVRD and OVRD\_CTL registers are in the volatile section of memory and are not backed by EEPROM. Upon power up these registers are cleared.

#### 8.4.3 ALU Bypass

It may be desirable that the device produces a predetermined constant output level as soon as it is powered up. The ALU bypass mode does that. This mode is enabled by setting DACx\_BASEM.BYP bit. Since DACx\_BASEM.BYP is stored in the EEPROM, its value is automatically loaded into the operating memory at power up. If the stored value for DACx\_BASEM.BYP is 1, upon power up the corresponding DAC output immediately produces an analog output equivalent of the BASE.

In this mode of operation the ALU is bypassed, and the BASE value of the LUT is presented at the input of the DAC. This is the result of DACx\_BASEM.BYP, which controls the mux that follows the ALU in the signal path, being set. Therefore, the output of the device is constant over the operating temperature range of the device.

#### NOTE

Each channel has its own BYP bit, and its own BASE value.

#### 8.4.4 DAC Input Override

The DAC inputs words can be directly written via the I<sup>2</sup>C interface. In this mode the LMP92066 is a dual 12-bit DAC. This functionality is facilitated by the multiplexers that precede the DACs, and user writable data registers DACxM\_OVRD and DACxL\_OVRD. DACxM\_OVRD[3:0] is the upper nibble of the DAC input word. DACxL\_OVRD[7:0] is the lower byte of the DAC input data.

The multiplexer control signal is the OVRD\_CTL.DAC bit. This bit is shared by both channels; that is, both channels are either in the DAC input override mode, or both are in the default mode.

Table 12 shows the example of the I<sup>2</sup>C bus transfer sequence which results in externally supplied data being the source of input to the DACs.

#### Table 12. I<sup>2</sup>C Bus Transfer Sequence: Externally Supplied Data Sourcing Input to DACs

| I <sup>2</sup> C OPERATION | REGISTER   | DATA | DESCRIPTION                                                                                                                                                                                                                                |

|----------------------------|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WRITE                      | ACC_CNTL   | 0xCD | First byte of the "password"                                                                                                                                                                                                               |

| WRITE                      | ACC_CNTL   | 0xF0 | Second byte of the "password". After this transfer is completed the access level is changed to L2                                                                                                                                          |

| READ                       | ACC_CNTL   | 0x03 | Optional: Reading the ACC_CNTL serves as status report. 0x03 – access level L2 is activated (and due to nesting, L1 is also indicated)                                                                                                     |

| WRITE                      | DAC0M_OVRD | 0x08 | Writes 0x8 as the value of the top nibble of the 12-bit, offset binary, DAC0 input value. After this transaction the DAC0M_OVRD register is not updated, yet. The update takes place only after the DAC0L_OVRD register is written.        |

| WRITE                      | DAC0L_OVRD | 0x00 | Writes 0x00 into the lower byte of the DAC0 input value. After this transaction completes both DAC0M_OVRD and DAC0L_OVRD registers are updated. The 12-bit value in this example is 0x800.                                                 |

| WRITE                      | DAC1M_OVRD | 0x04 | Writes 0x4 as the value of the top nibble of the 12-bit, offset binary, DAC1 input value. After this transaction the DAC1M_OVRD register is not updated, yet. The update takes place only after the DAC1L_OVRD register is written.        |

| WRITE                      | DAC1L_OVRD | 0x00 | Writes 0x00 into the lower byte of the DAC1 input value. After this transaction completes both DAC1M_OVRD and DAC1L_OVRD registers are updated. The 12-bit value in this example is 0x400.                                                 |

| WRITE                      | OVRD_CTL   | 0x02 | Sets the OVRD_CTL.TEMP bit. This causes both multiplexers that precede the DACs to start routing the DACx_OVRD values to the inputs of their respective DACs. As a result the outputs of the device are: VDAC0 = 2.5 V, and VDAC1 = 1.25 V |

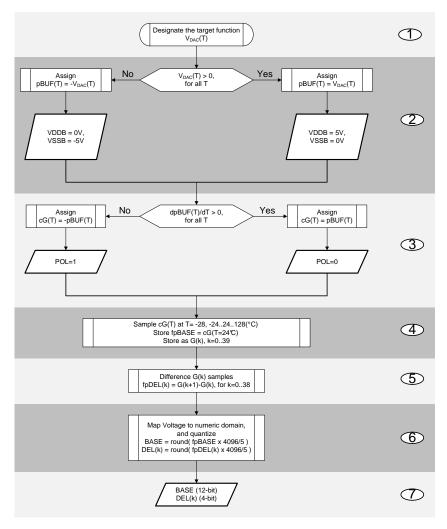

| READ                       | DACOM      | 0x** | Optional:                                                                                                                                                                                                                                  |