LMK1D1208I

ZHCSPZ0A - FEBRUARY 2022 - REVISED JUNE 2023

# LMK1D1208I I<sup>2</sup>C 可配置低附加抖动 LVDS 缓冲器

#### 1 特性

- 具有 2 个输入和 8 个输出的高性能 LVDS 时钟 缓冲器系列

- 输出频率最高可达 2GHz

- 电源电压: 1.8V/2.5V/3.3V ± 5%

- 通过 I<sup>2</sup>C 编程实现器件可配置性

- 单独的输入和输出启用/禁用

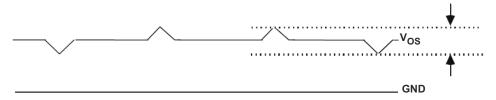

- 单独的输出振幅选择(标准或增强)

- 组输入多路复用器

- 通过 IDX 引脚实现四个可编程 I<sup>2</sup>C 地址

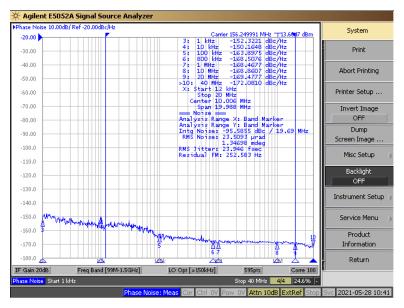

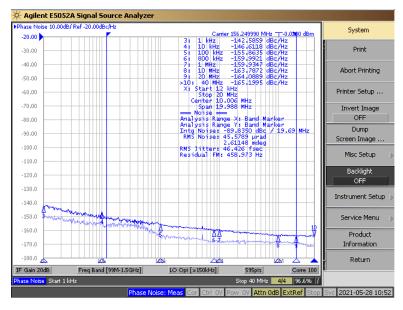

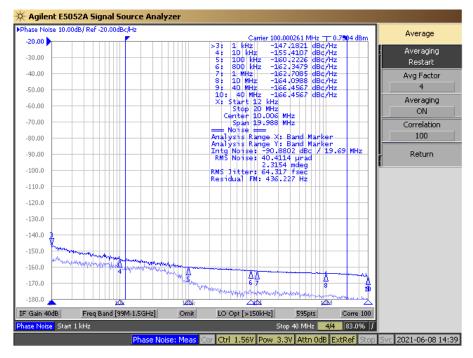

- 低附加抖动:156.25MHz 下 12kHz 至 20MHz 范围 内的

#### RMS 最大值小于 60fs

- 超低相位本底噪声:-164dBc/Hz(典型值)

- 超低传播延迟: < 575ps (最大值)

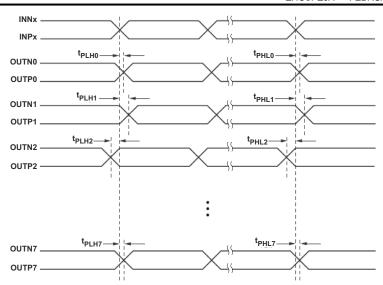

- 输出偏斜:20ps(最大值)

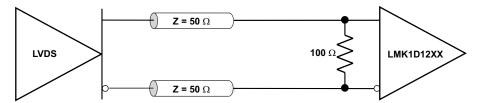

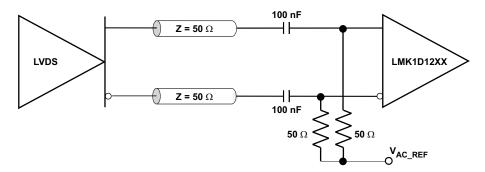

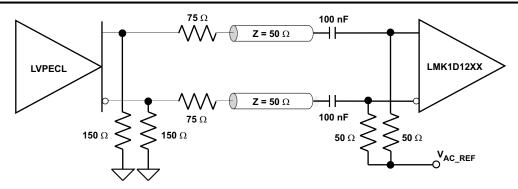

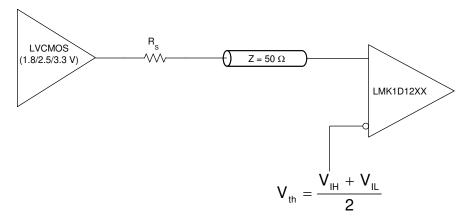

- 通用输入接受 LVDS、LVPECL、LVCMOS、HCSL 和 CML

- 失效防护输入

- LVDS 基准电压, V<sub>AC REF</sub>, 适用于容性耦合输入

- 工业温度范围: 40°C 至 105°C

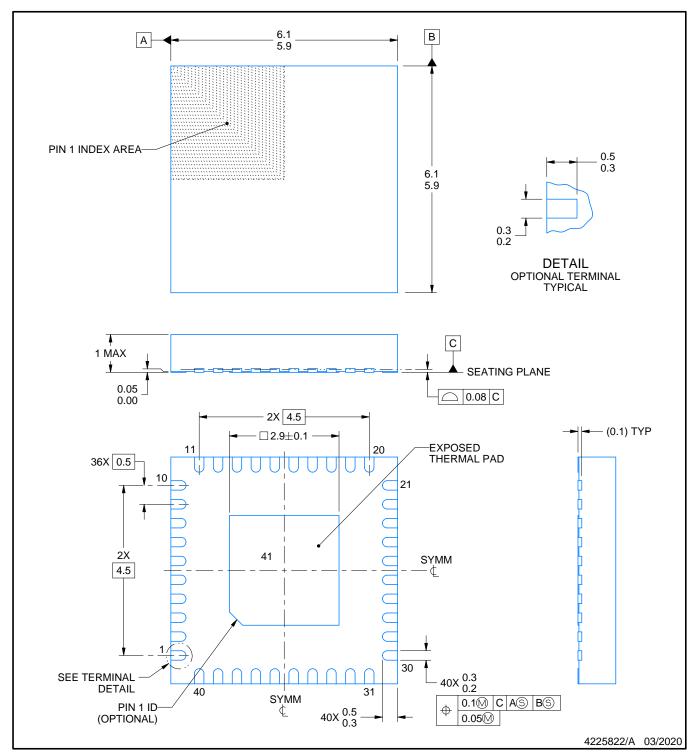

- 可用封装

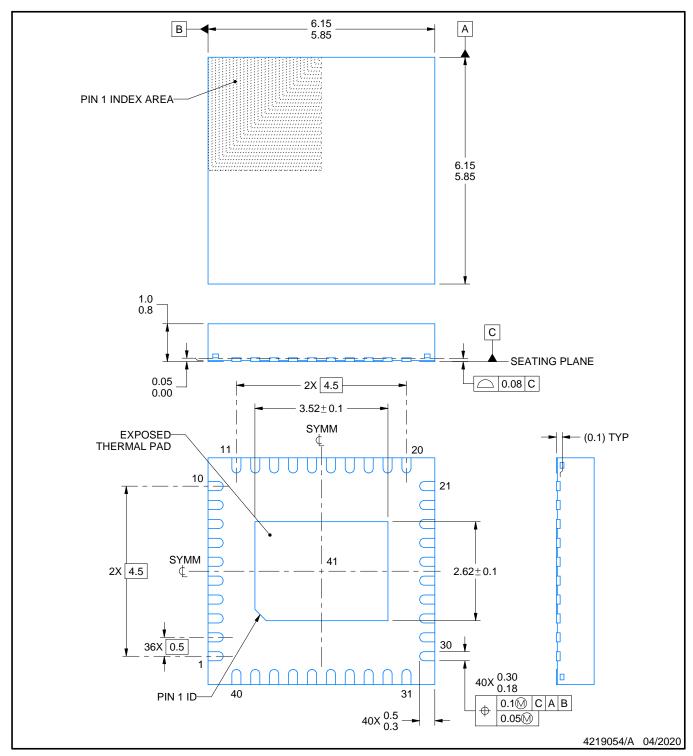

- 6mm × 6mm 40 引脚 VQFN (RHA)

#### 2 应用

- 电信及网络

- 医疗成像

- 测试和测量设备

- 无线通信

- 专业音频/视频

#### 3 说明

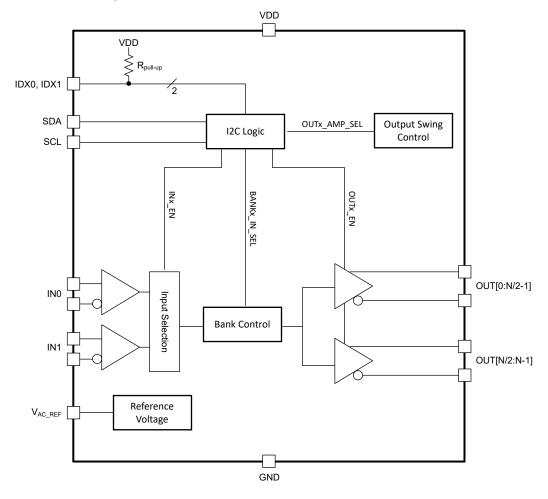

LMK1D1208I 是一款 I<sup>2</sup>C 可编程 LVDS 时钟缓冲器。 该器件具有两个输入和八对差分 LVDS 时钟输出 (OUTO 到 OUT7),具有超小延迟,可实现时钟分 配。输入可以为 LVDS、LVPECL、LVCMOS、HCSL 或 CML。

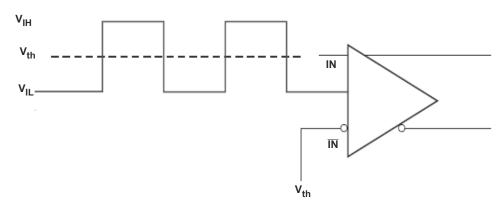

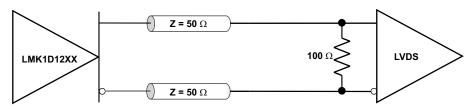

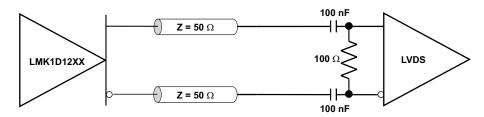

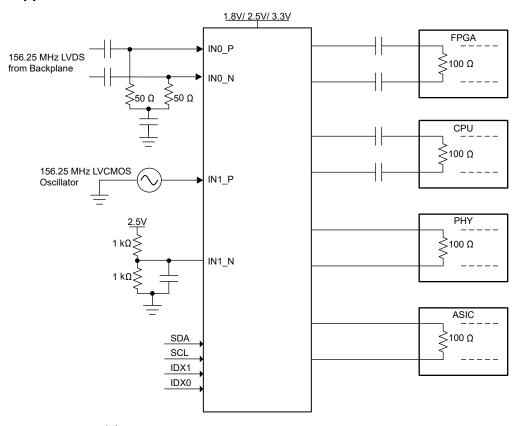

LMK1D1208I 专为驱动  $50\Omega$  传输线路而设计。在单端 模式下驱动输入时,对未使用的负输入引脚施加适当的 偏置电压(请参阅图 9-6)。

I<sup>2</sup>C 编程使该器件能够配置为单组缓冲区(两个输入之 一分配到八个输出对)或双组缓冲区(每个输入分配到 四个输出对)。每个输出都可以配置为具有标准 (350mV) 或增强 (500mV) 摆幅。该器件还通过 I<sup>2</sup>C 编 程集成了单个输出通道的启用/禁用。LMK1D1208I 具 有失效防护输入,可防止在没有输入信号的情况下输出 发生振荡并允许在提供 VDD 之前输入信号。

该器件可在 1.8V、2.5V 或 3.3V 电源环境下工作,其 特点是温度范围为 - 40°C 至 105°C (环境温度)。

#### 封装信息

|            | ~ 4 · 5 4 1 1 · · · ·    |                 |

|------------|--------------------------|-----------------|

| 器件型号       | <b>封装</b> <sup>(1)</sup> | 封装尺寸(标称值)       |

| LMK1D1208I | VQFN (40)                | 6.00mm × 6.00mm |

- (1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

- 封装尺寸(长×宽)为标称值,并包括引脚(如适用)。

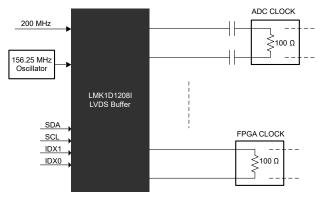

应用示例

### **Table of Contents**

| 1 特性                                  | 1 9.5 Programming                         | 20               |

|---------------------------------------|-------------------------------------------|------------------|

| 2 应用                                  |                                           |                  |

| 3 说明                                  | 46 4 11 41 11 1 4 41                      | 2                |

| 4 Revision History                    |                                           | 25               |

| 5 Device Comparison                   | 40 0 T! 1 A 1! 4!                         | 2                |

| 6 Pin Configuration and Functions     |                                           | <mark>2</mark> 8 |

| 7 Specifications                      | 6 10.4 Layout                             |                  |

| 7.1 Absolute Maximum Ratings          | 6 11 Device and Documentation Support     |                  |

| 7.2 ESD Ratings                       | 44.4.5                                    | 3 <sup>*</sup>   |

| 7.3 Recommended Operating Conditions  | 4.4                                       | 3 <sup>-</sup>   |

| 7.4 Thermal Information               |                                           | 3 <sup>^</sup>   |

| 7.5 Electrical Characteristics        |                                           | 3 <sup>*</sup>   |

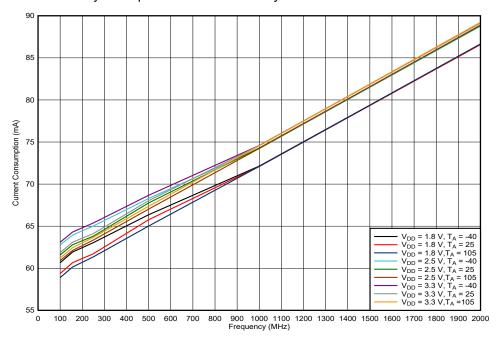

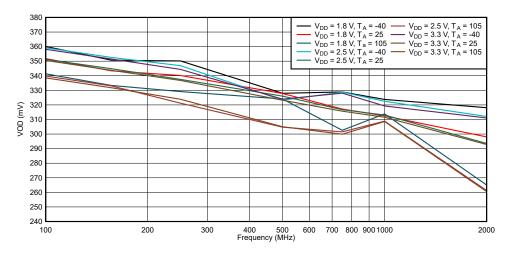

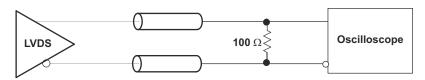

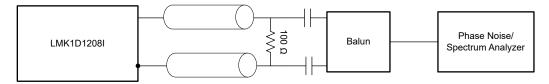

| 7.6 Typical Characteristics1          | 1 11.5 静电放电警告                             | 3 <sup>-</sup>   |

| 8 Parameter Measurement Information 1 |                                           | 3 <sup>-</sup>   |

| 9 Detailed Description1               | 4 12 Mechanical, Packaging, and Orderable |                  |

| 9.1 Overview1                         |                                           | 3 <sup>-</sup>   |

| 9.2 Functional Block Diagram1         | 4 12.1 Package Option Addendum            | 32               |

| 9.3 Feature Description1              |                                           |                  |

| 9.4 Device Functional Modes1          |                                           |                  |

4 Revision History 注:以前版本的页码可能与当前版本的页码不同

| С | hanges from Revision * (February 2022) to Revision A (June 2023)                                 | Page |

|---|--------------------------------------------------------------------------------------------------|------|

| • | 将表标题从"器件信息"更改为"封装信息"                                                                             | 1    |

| • | Added the Device Comparison table for the LMK1Dxxxx buffer device family                         | 3    |

| • | Moved the Power Supply Recommendations and Layout sections to the Application and Implementation | n    |

|   | section                                                                                          | 28   |

# **5 Device Comparison**

| DEVICE             | DEVICE<br>TYPE                                          | FEATURES                                             | OUTPUT<br>SWING            | PACKAGE    | BODY SIZE                |  |

|--------------------|---------------------------------------------------------|------------------------------------------------------|----------------------------|------------|--------------------------|--|

| LMK1D2108          | Dual 1:8                                                | Global output enable and swing                       | 350 mV                     | VQFN (48)  | 7.00 mm × 7.00 mm        |  |

| LIMK 1D2 108       | Dual 1:8                                                | control through pin control                          | through pin control 500 mV |            | 7.00 mm × 7.00 mm        |  |

| LMK1D2106          | Dual 1:6                                                | Global output enable and swing                       | 350 mV                     | VQFN (40)  | 6.00 mm × 6.00 mm        |  |

| LMK1D2106 Dual 1:6 |                                                         | control through pin control                          | 500 mV                     | VQFN (40)  | 0.00 11111 ~ 0.00 11111  |  |

| LMK1D2104          | Dual 1:4                                                | Global output enable and swing                       | 350 mV                     | VQFN (28)  | 5.00 mm × 5.00 mm        |  |

| LIVIN ID2 104      | Duai 1.4                                                | control through pin control                          | 500 mV                     | VQFN (20)  | 3.00 11111 ^ 3.00 11111  |  |

| LMK1D2102          | Dual 1:2                                                | Global output enable and swing                       | 350 mV                     | VQFN (16)  | 3.00 mm × 3.00 mm        |  |

| LIVIN 1D2 102      | Duai 1.2                                                | control through pin control                          | 500 mV                     | VQFN (10)  | 3.00 mm ^ 3.00 mm        |  |

| LMK1D1216          | 2:16 Global output enable control                       |                                                      | 350 mV                     | VQFN (48)  | 7.00 mm × 7.00 mm        |  |

| LIVINTD1210        | 2.10                                                    | through pin control                                  | 500 mV                     | VQ(N(40)   | 7.00 11111 ~ 7.00 111111 |  |

| LMK1D1212          | Global output enable contr                              |                                                      | 350 mV                     | VQFN (40)  | 6.00 mm × 6.00 mm        |  |

| LIVINTD1212        | 2.12                                                    | through pin control                                  | 500 mV                     | VQ(1V(40)  | 0.00 11111 ^ 0.00 11111  |  |

| LMK1D1208P         | 2:8                                                     | Individual output enable control                     | 350 mV                     | VQGN (40)  | 6.00 mm × 6.00 mm        |  |

| LIVIN 1D 12001     | 2.0                                                     | through pin control                                  | 500 mV                     | VQOIV (40) | 0.00 11111 ~ 0.00 11111  |  |

| LMK1D1208I         | 2:8                                                     | Individual output enable control                     | 350 mV                     | VQFN (40)  | 6.00 mm × 6.00 mm        |  |

| LIVIT I ZOOI       | 2.0                                                     | through I <sup>2</sup> C                             | 500 mV                     | VQ(N(40)   | 0.00 11111 ~ 0.00 11111  |  |

| LMK1D1208          | OB 2:8 Global output enable control through pin control |                                                      | 350 mV                     | VQFN (28)  | 5.00 mm × 5.00 mm        |  |

| LMK1D1204P         | 2:4                                                     | Individual output enable control through pin control | 350 mV                     | VQGN (28)  | 5.00 mm × 5.00 mm        |  |

| LMK1D1204          | 2:4                                                     | Global output enable control through pin control     | 350 mV                     | VQFN (16)  | 3.00 mm × 3.00 mm        |  |

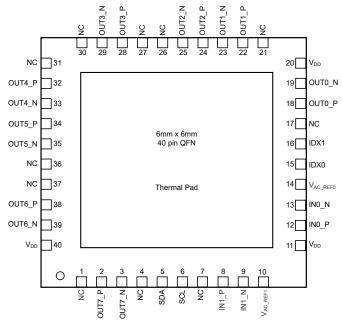

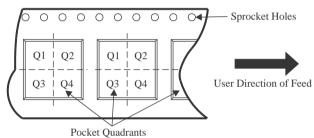

# **6 Pin Configuration and Functions**

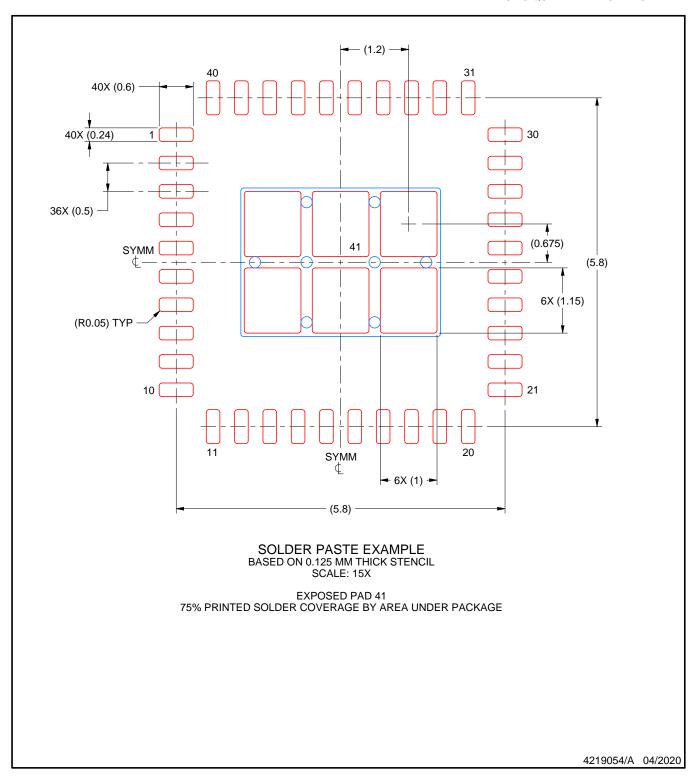

图 6-1. LMK1D1208I: RHA Package 40-Pin VQFN (Top View)

表 6-1. Pin Functions

| PIN                                                            |                 | TYPE <sup>(1)</sup>                    | DESCRIPTION                                                                                                                                                                     |

|----------------------------------------------------------------|-----------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                           | LMK1D1208I      | - ITPE(')                              | DESCRIPTION                                                                                                                                                                     |

| DIFFERENTIAL/SINGLE-E                                          | NDED CLOCK INPU | Т                                      |                                                                                                                                                                                 |

| IN0_P, IN0_N                                                   | 12, 13          | I                                      | Primary: Differential input pair or single-ended input                                                                                                                          |

| IN1_P, IN1_N                                                   | 8, 9            | I                                      | Secondary: Differential input pair or single-ended input.                                                                                                                       |

| I <sup>2</sup> C PROGRAMMING                                   |                 |                                        |                                                                                                                                                                                 |

| SDA                                                            | 5               | I/O                                    | I <sup>2</sup> C data                                                                                                                                                           |

| SCL                                                            | 6               | I                                      | I <sup>2</sup> C clock                                                                                                                                                          |

| IDX0                                                           | 15              | I,S,PU                                 | I <sup>2</sup> C address bit[0]. This is a 2-level input that is decoded in conjunction with pin 15 to set the I <sup>2</sup> C address. It has internal 670-k $\Omega$ pullup. |

| IDX1                                                           | 16              | I,S, PU                                | I <sup>2</sup> C address bit[1]. This is a 2-level input that is decoded in conjunction with pin 16 to set the I <sup>2</sup> C address. It has internal 670-k $\Omega$ pullup. |

| BIAS VOLTAGE OUTPUT                                            | •               |                                        |                                                                                                                                                                                 |

| V <sub>AC_REF0</sub> , V <sub>AC_REF1</sub>                    | 14, 10          | 0                                      | Bias voltage output for capacitive coupled inputs. If used, TI recommends using a 0.1-µF capacitor to GND on this pin.                                                          |

| DIFFERENTIAL CLOCK O                                           | UTPUT           |                                        |                                                                                                                                                                                 |

| OUT0_P, OUT0_N                                                 | 18, 19          | 0                                      | Differential LVDS output pair number 0                                                                                                                                          |

| OUT1_P, OUT1_N                                                 | 22, 23          | 0                                      | Differential LVDS output pair number 1                                                                                                                                          |

| OUT2_P, OUT2_N                                                 | 24, 25          | 0                                      | Differential LVDS output pair number 2                                                                                                                                          |

| OUT3_P, OUT3_N                                                 | 28, 29          | 0                                      | Differential LVDS output pair number 3                                                                                                                                          |

| OUT4_P, OUT4_N 32, 33 O Differential LVDS output pair number 4 |                 | Differential LVDS output pair number 4 |                                                                                                                                                                                 |

| OUT5_P, OUT5_N                                                 | 34, 35          | 0                                      | Differential LVDS output pair number 5                                                                                                                                          |

| OUT6_P, OUT6_N                                                 | 38, 39          | 0                                      | Differential LVDS output pair number 6                                                                                                                                          |

| OUT7_P, OUT7_N                                                 | 2, 3            | 0                                      | Differential LVDS output pair number 7                                                                                                                                          |

# 表 6-1. Pin Functions (continued)

| 2 o m m anotiono (continuou) |                                            |                     |                                                                                               |  |  |  |

|------------------------------|--------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------|--|--|--|

| PIN                          | PIN                                        |                     | DESCRIPTION                                                                                   |  |  |  |

| NAME LMK1D1208I              |                                            | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                   |  |  |  |

| SUPPLY VOLTAGE               |                                            |                     |                                                                                               |  |  |  |

| V <sub>DD</sub>              | 11, 20, 40                                 | Р                   | Device power supply (1.8 V, 2.5 V, or 3.3 V)                                                  |  |  |  |

| GROUND                       | GROUND                                     |                     |                                                                                               |  |  |  |

| DAP                          | DAP                                        | G                   | Die Attach Pad. Connect to the printed circuit board (PCB) ground plane for heat dissipation. |  |  |  |

| NO CONNECT                   | NO CONNECT                                 |                     |                                                                                               |  |  |  |

| NC                           | 1, 4, 7, 17, 21, 26,<br>27, 30, 31, 36, 37 | _                   | No connection. Leave floating.                                                                |  |  |  |

- (1) The definitions below define the I/O type for each pin.

- I = Input

- O = Output

- I / O = Input / Output

- PU = Internal 670-k Ω Pullup

- S = Hardware Configuration Pin

- P = Power Supply

- G = Ground

# 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                    | MIN   | MAX                   | UNIT |

|------------------|------------------------------------|-------|-----------------------|------|

| $V_{DD}$         | Supply voltage                     | - 0.3 | 3.6                   | V    |

| V <sub>IN</sub>  | Input voltage                      | - 0.3 | 3.6                   | V    |

| Vo               | Output voltage                     | - 0.3 | V <sub>DD</sub> + 0.3 | V    |

| I <sub>IN</sub>  | Input current                      | - 20  | 20                    | mA   |

| Io               | Continuous output current          | - 50  | 50                    | mA   |

| TJ               | Junction temperature               |       | 135                   | °C   |

| T <sub>stg</sub> | Storage temperature <sup>(2)</sup> | - 65  | 150                   | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) Device unpowered

#### 7.2 ESD Ratings

|                    |                         |                                                                                     | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>     | ±3000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discrarge | Charged device model (CDM), per ANSI/ESDA/<br>JEDEC JS-002, all pins <sup>(2)</sup> | ±1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                |                                               | MIN   | NOM | MAX   | UNIT |

|----------------|--------------------------------|-----------------------------------------------|-------|-----|-------|------|

|                |                                | 3.3-V supply                                  | 3.135 | 3.3 | 3.465 |      |

| $V_{DD}$       | Core supply voltage            | 2.5-V supply                                  | 2.375 | 2.5 | 2.625 | V    |

|                |                                | 1.8-V supply                                  | 1.71  | 1.8 | 1.89  |      |

| Supply<br>Ramp | Supply voltage ramp            | Requires monotonic ramp (10-90% of $V_{DD}$ ) | 0.1   |     | 20    | ms   |

| T <sub>A</sub> | Operating free-air temperature |                                               | - 40  |     | 105   | °C   |

| TJ             | Operating junction temperature |                                               | - 40  |     | 135   | °C   |

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 7.4 Thermal Information

|                        |                                              | LMK1D1208I |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | VQFN       | UNIT |

|                        |                                              | 40 PINS    |      |

| R <sub>0</sub> JA      | Junction-to-ambient thermal resistance       | 39.1       | °C/W |

| R <sub>θ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 32.4       | °C/W |

| R <sub>θ JB</sub>      | Junction-to-board thermal resistance         | 20.2       | °C/W |

| $\Psi_{JT}$            | Junction-to-top characterization parameter   | 1          | °C/W |

| $\Psi_{JB}$            | Junction-to-board characterization parameter | 20.2       | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 8.3        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 7.5 Electrical Characteristics

$V_{DD}$  = 1.8 V ± 5 %, -40°C  $\leq$  T<sub>A</sub>  $\leq$  105°C. Typical values are at  $V_{DD}$  = 1.8 V, 25°C (unless otherwise noted)

|                           | PARAMETER                                   | TEST CONDITIONS                                                                           | MIN                   | TYP MAX               | UNIT |

|---------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------|-----------------------|------|

| POWER SU                  | PPLY CHARACTERISTICS                        |                                                                                           |                       |                       |      |

| IDD <sub>STAT</sub>       | LMK1D1208I                                  | All-outputs enabled and unterminated, f = 0 Hz (AMP_SEL =1)                               |                       | 55                    | mA   |

| IDD <sub>100M</sub>       | LMK1D1208I                                  | All-outputs enabled, R <sub>L</sub> = 100 $^{\Omega}$ , f =100 MHz (AMP_SEL = 0, default) |                       | 75 95                 | mA   |

| IDD <sub>100M</sub>       | LMK1D1208I                                  | All-outputs enabled, RL = 100 $^{\Omega}$ , f =100 MHz, AMP_SEL = 1                       |                       | 110                   | mA   |

| IDX INPUT                 | CHARACTERISTICS (Applies to V <sub>DE</sub> | $_0 = 1.8 \text{ V} \pm 5\%, 2.5 \text{ V} \pm 5\% \text{ and } 3.3 \text{ V} \pm 5\%$    | )                     |                       |      |

| V <sub>IH</sub>           | Input high voltage                          | Minimum input voltage for a logical "1" state                                             | 0.7 × V <sub>CC</sub> | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IL</sub>           | Input low voltage                           | Maximum input voltage for a logical "0" state                                             | - 0.3                 | 0.3 × V <sub>CC</sub> | V    |

| I <sub>IH</sub>           | Input high current                          | $V_{DD}$ can be 1.8V/2.5V/3.3V with $V_{IH} = V_{DD}$                                     |                       | 30                    | μΑ   |

| I <sub>IL</sub>           | Input low current                           | $V_{DD}$ can be 1.8V/2.5V/3.3V with $V_{IH} = V_{DD}$                                     | - 30                  |                       | μΑ   |

| R <sub>pull-up(IDX)</sub> | Input pullup resistor                       |                                                                                           |                       | 670                   | kΩ   |

| I <sup>2</sup> C INTERF   | ACE CHARACTERISTICS (Applies t              | o $V_{DD} = 1.8 \text{ V} \pm 5\%, 2.5 \text{ V} \pm 5\%$ and 3.3 V                       | ± 5%)                 |                       |      |

| V <sub>IH</sub>           | Input high voltage                          |                                                                                           | 0.7 × V <sub>CC</sub> | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IL</sub>           | Input low voltage                           |                                                                                           | - 0.3                 | 0.3 × V <sub>CC</sub> | V    |

| I <sub>IH</sub>           | Input high current                          |                                                                                           |                       | 30                    | μA   |

| I <sub>IL</sub>           | Input low current                           |                                                                                           | - 30                  |                       | μA   |

| C <sub>IN_SE</sub>        | Input capacitance                           | at 25°C                                                                                   |                       | 2                     | pF   |

| V <sub>OL</sub>           | Output low voltage                          | I <sub>OL</sub> = 3 mA                                                                    |                       | 0.3                   | V    |

|                           |                                             | Standard                                                                                  |                       | 100                   |      |

| f <sub>SCL</sub>          | I <sup>2</sup> C clock rate                 | Fast mode                                                                                 |                       | 400                   | kHz  |

|                           |                                             | Ultra Fast mode                                                                           |                       | 1000                  |      |

| t <sub>SU(START)</sub>    | START condition setup time                  | SCL high before SDA low                                                                   | 0.6                   |                       | us   |

| t <sub>H</sub> (START)    | START condition hold time                   | SCL low after SDA low                                                                     | 0.6                   |                       | us   |

| t <sub>W(SCLH)</sub>      | SCL pulse width high                        |                                                                                           | 0.6                   |                       | us   |

| t <sub>W(SCLL)</sub>      | SCL pulse width low                         |                                                                                           | 1.3                   |                       | us   |

$V_{DD}$  = 1.8 V ± 5 %, -40°C  $\leq$  T<sub>A</sub>  $\leq$  105°C. Typical values are at  $V_{DD}$  = 1.8 V, 25°C (unless otherwise noted)

|                        | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TEST CONDITIONS                                                                                               | MIN             | TYP | MAX   | UNIT     |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------|-----|-------|----------|

| t <sub>SU(SDA)</sub>   | SDA setup time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                               | 100             |     |       | ns       |

| t <sub>H(SDA)</sub>    | SDA hold time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SDA valid after SCL low                                                                                       | 0               |     | 0.9   | us       |

| t <sub>R(IN)</sub>     | SDA/SCL input rise time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                               |                 |     | 300   | ns       |

| t <sub>F(IN)</sub>     | SDA/SCL input fall time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                               | ,               | ,   | 300   | ns       |

| t <sub>F(OUT)</sub>    | SDA output fall time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C <sub>BUS</sub> <= 400 pF                                                                                    |                 |     | 300   | ns       |

| t <sub>SU</sub> (STOP) | STOP condition setup time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                               | 0.6             |     |       | us       |

| t <sub>BUS</sub>       | Bus free time between STOP and START                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                               | 1.3             |     |       | us       |

| SINGLE-END             | DED LVCMOS/LVTTL CLOCK INPUT (App                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | lies to V <sub>DD</sub> = 1.8 V ± 5%, 2.5 V ± 5%                                                              | 6 and 3.3 V ± 5 | %)  |       |          |

| f <sub>IN</sub>        | Input frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Clock input                                                                                                   | DC              |     | 250   | MHz      |

| V <sub>IN_S-E</sub>    | Single-ended Input Voltage Swing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Assumes a square wave input with two levels                                                                   | 0.4             |     | 3.465 | V        |

| dVIN/dt                | Input Slew Rate (20% to 80% of the amplitude)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                               | 0.05            |     |       | V/ns     |

| I <sub>IH</sub>        | Input high current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V <sub>DD</sub> = 3.465 V, V <sub>IH</sub> = 3.465 V                                                          |                 |     | 50    | μA       |

| I <sub>IL</sub>        | Input low current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>DD</sub> = 3.465 V, V <sub>IL</sub> = 0 V                                                              | - 30            |     |       | μA       |

| C <sub>IN_SE</sub>     | Input capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | at 25°C                                                                                                       |                 | 3.5 |       | pF       |

|                        | IAL CLOCK INPUT (Applies to V <sub>DD</sub> = 1.8 \                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | / ± 5%, 2.5 V ± 5% and 3.3 V ± 5%)                                                                            |                 |     |       |          |

| f <sub>IN</sub>        | Input frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Clock input                                                                                                   |                 |     | 2     | GHz      |

|                        | Differential input voltage peak-to-peak                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>ICM</sub> = 1 V (V <sub>DD</sub> = 1.8 V)                                                              | 0.3             |     | 2.4   |          |

| $V_{IN,DIFF(p-p)}$     | {2*(V <sub>INP</sub> -V <sub>INN</sub> )}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V <sub>ICM</sub> = 1.25 V (V <sub>DD</sub> = 2.5 V/3.3 V)                                                     | 0.3             |     | 2.4   | $V_{PP}$ |

| V <sub>ICM</sub>       | Input common mode voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V <sub>IN,DIFF(P-P)</sub> > 0.4 V (V <sub>DD</sub> = 1.8 V/2.5/3.3 V)                                         | 0.25            |     | 2.3   | V        |

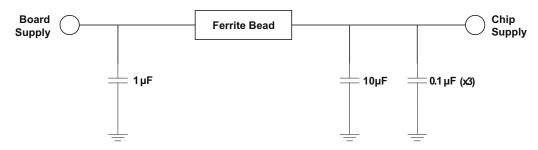

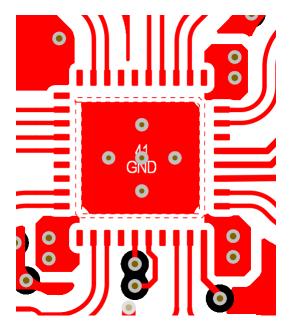

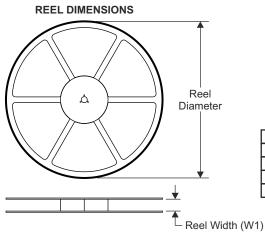

| I <sub>IH</sub>        | Input high current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V <sub>DD</sub> = 3.465 V, V <sub>INP</sub> = 2.4 V, V <sub>INN</sub><br>= 1.2 V                              |                 |     | 30    | μA       |