LMK04208

ZHCSFH1-SEPTEMBER 2016

# LMK04208 具有双环 PLL 的低噪声时钟抖动消除器

# 1 特性

- 超低的均方根值 (RMS) 抖动性能

- 111fs, RMS 抖动(12kHz 至 20MHz)

- 123fs, RMS 抖动(100Hz 至 20MHz)

- 双环路 PLLatinum™锁相环 (PLL) 架构

- PLL1

- 集成低噪声晶体振荡器电路

- 输入时钟丢失时采用保持模式

- 自动或手动触发/恢复

# PLL2

- 标准化锁相环 (PLL) 噪底为 -227dBc/Hz

- 相位检测器速率最高可达 155MHz

- OSCin 倍频器

- 集成低噪声压控振荡器 (VCO)或外部 VCO 模式

- 两个具有 LOS 的冗余输入时钟

- 自动和手动切换模式

- 50% 占空比输出分配, 1 至 1045 (偶数和奇数)

- 6路低电压正射极耦合逻辑 (LVPECL)、低压差分信令 (LVDS) 或低电压互补金属氧化物半导体 (LVCMOS) 可编程输出

- 数字延迟: 固定或可动态调节

- 模拟延迟控制(步长为 25ps)

- 7 路差分输出;最高可达 14 路的单端输出

- 多达 6 个 VCXO/晶振缓冲输出

- 时钟速率高达 1536MHz

- 0 延迟模式

- 加电时 3 个缺省时钟输出

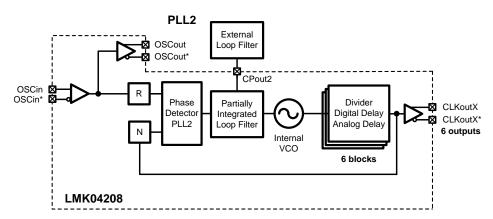

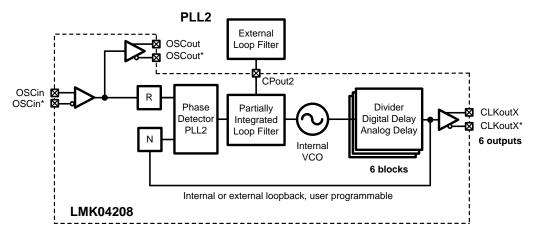

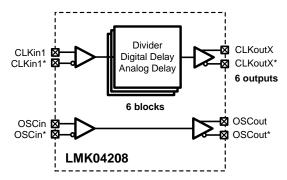

- 多模式:双 PLL、单 PLL 和时钟分配

- 工业温度范围: -40℃ 至 +85℃

- 3.15V 至 3.45V 工作电压

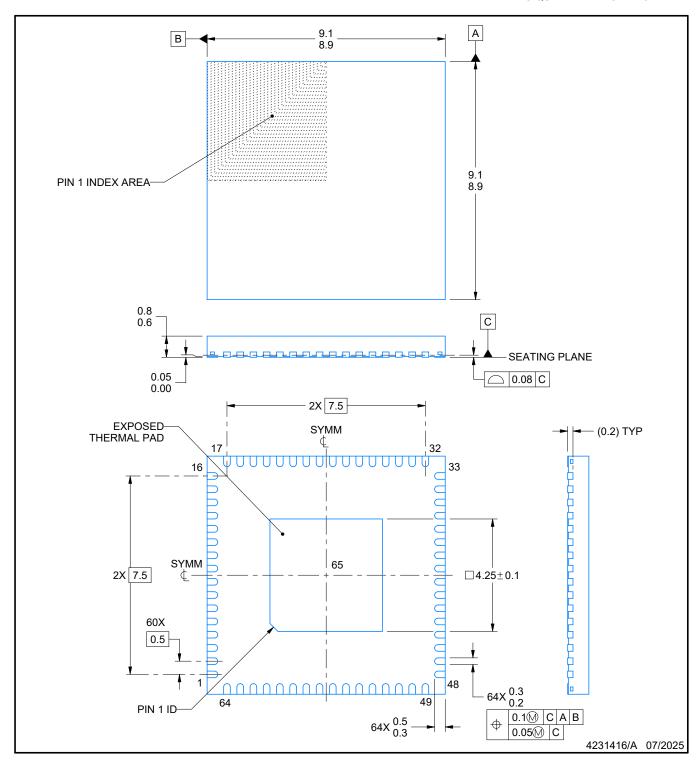

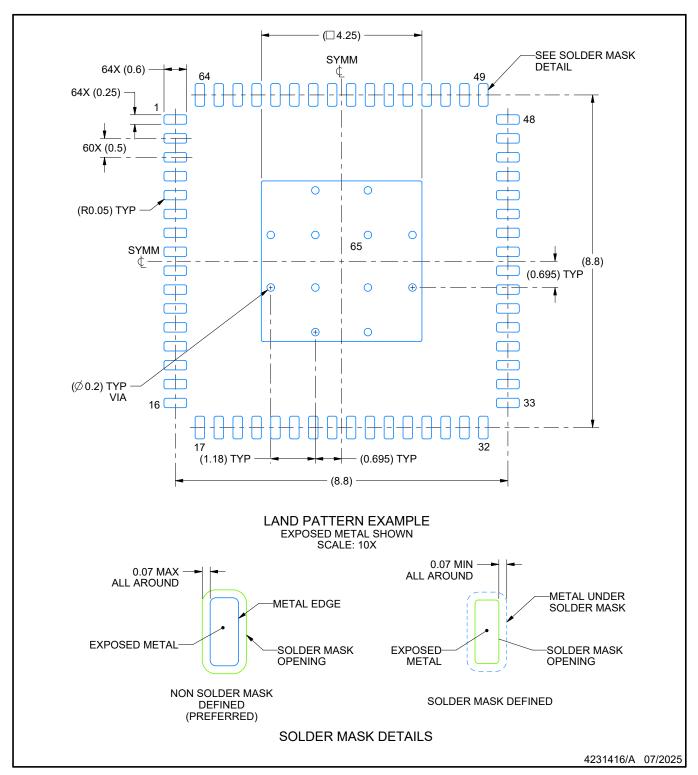

- 64 引脚超薄四方扁平无引线 (WQFN) 封装 (9.0mm × 9.0mm × 0.8mm)

# 2 应用

- 数据转换器计时

- 无线基础设施

- 网络、同步光纤网 (SONET) 或同步数字体系 (SDH)、数字用户线路接入复用器 (DSLAM)

- 医疗、视频、军事和航天领域

- 测试和测量

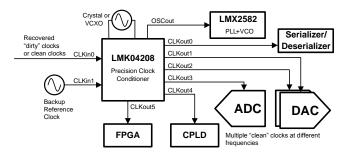

# 3 说明

LMK04208 器件是一款高性能时钟调节器,具备出色的时钟抖动消除、生成和分配等高级功能,能够充分满足新一代系统要求。双环 PLLatinum™架构利用低噪声 VCXO 模块能够实现 111fs RMS 抖动(12kHz至 20MHz)或采用低成本外部晶振及变容二极管实现低于 200fs 的 RMS 抖动(12kHz 至 20MHz)。

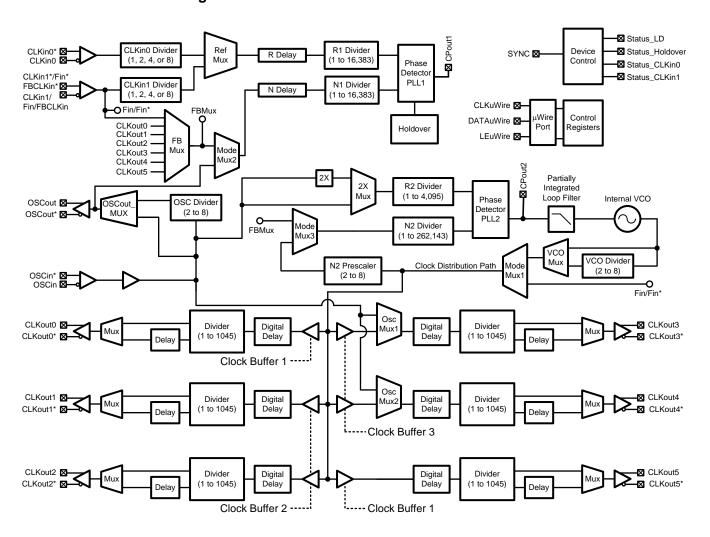

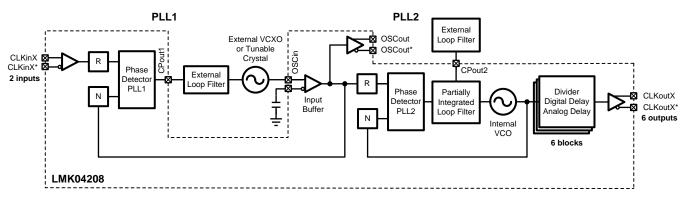

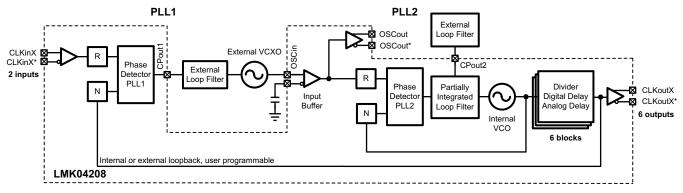

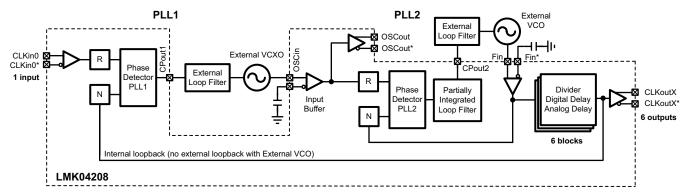

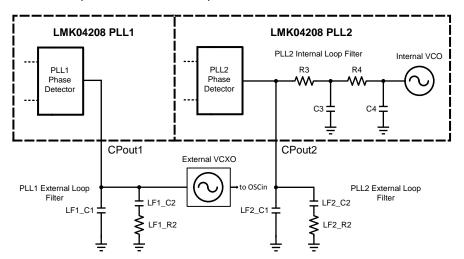

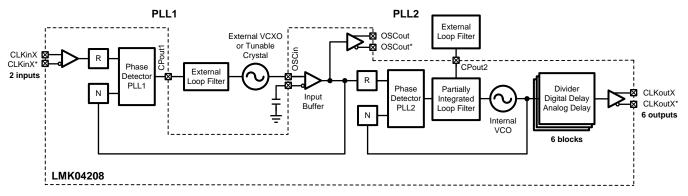

双环架构由两个高性能锁相环 (PLL)、一个低噪声晶体振荡器电路以及一个高性能压控振荡器 (VCO)构成。第一个 PLL (PLL1)具有低噪声抖动消除器功能,而第二个 PLL (PLL2)执行时钟生成。PLL1可配置为与外部 VCXO 模块配合使用,或与具有外部可调晶体和变容二极管的集成式晶体振荡器配合使用。当应用于很窄的环路带宽时,PLL1使用 VCXO模块或可调晶体的优异近端相位噪声(偏移低于 50kHz)清理输入时钟。PLL1的输出将用作 PLL2的清理输入参考,以锁定集成式 VCO。可对 PLL2的环路带宽进行优化以清理远端相位噪声(偏移高于 50kHz),集成式 VCO优于 VCXO模块或 PLL1中使用的可调晶体。

## 器件信息(1)

| 器件型号     | VCO 频率            | 时钟输入 |  |  |  |  |  |

|----------|-------------------|------|--|--|--|--|--|

| LMK04208 | 2750MHz 至 3072MHz | 2    |  |  |  |  |  |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

# 简化电路原理图

www.ti.com.cn

| _ | $\Rightarrow$ |

|---|---------------|

| _ | ملب           |

| _ | w             |

| 1 | 特性 1                                                 |    | 8.6 Register Maps                                           | 52    |

|---|------------------------------------------------------|----|-------------------------------------------------------------|-------|

| 2 | 应用 1                                                 | 9  | Application and Implementation                              | 96    |

| 3 | 说明1                                                  |    | 9.1 Application Information                                 | 96    |

| 4 | 修订历史记录 2                                             |    | 9.2 Typical Applications                                    | 113   |

| 5 | Pin Configuration and Functions                      |    | 9.3 System Examples                                         | 121   |

| 6 | Specifications5                                      |    | 9.4 Do's and Don'ts                                         | 123   |

| Ü | 6.1 Absolute Maximum Ratings 5                       | 10 | Power Supply Recommendations                                | . 124 |

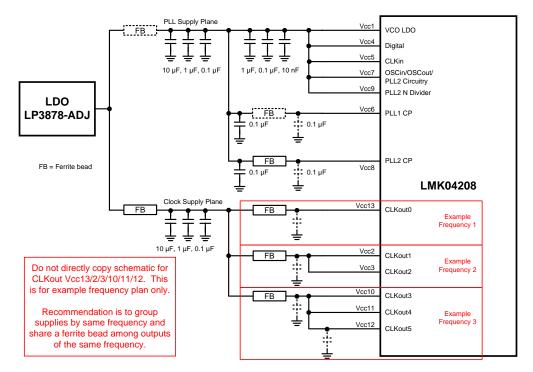

|   | 6.2 ESD Ratings                                      |    | 10.1 Pin Connection Recommendations                         | 124   |

|   | 6.3 Recommended Operating Conditions 5               |    | 10.2 Current Consumption and Power Dissipation Calculations | 126   |

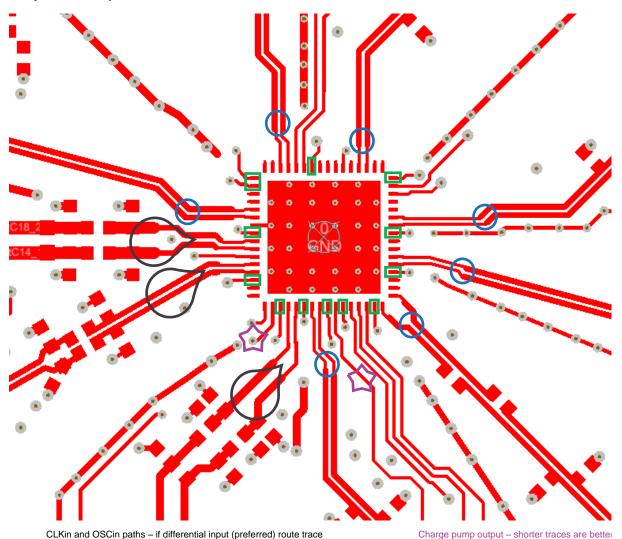

|   | 6.4 Thermal Information                              | 11 | Layout                                                      | . 128 |

|   | 6.5 Electrical Characteristics                       |    | 11.1 Layout Guidelines                                      | 128   |

|   | 6.6 Timing Requirements                              |    | 11.2 Layout Example                                         |       |

|   | 6.7 Typical Characteristics                          | 12 | 器件和文档支持                                                     |       |

| 7 | Parameter Measurement Information 16                 |    | 12.1 器件支持                                                   |       |

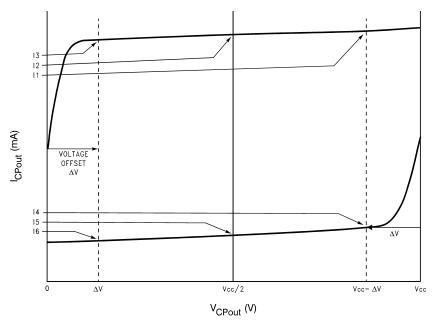

|   | 7.1 Charge Pump Current Specification Definitions 16 |    | 12.2 文档支持                                                   |       |

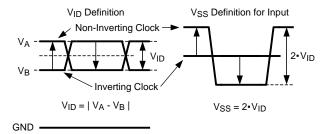

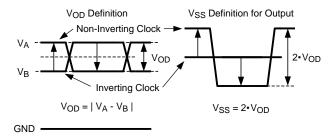

|   | 7.2 Differential Voltage Measurement Terminology 17  |    | 12.3 接收文档更新通知                                               |       |

| 8 | Detailed Description 18                              |    | 12.4 社区资源                                                   |       |

|   | 8.1 Overview                                         |    | 12.5 商标                                                     |       |

|   | 8.2 Functional Block Diagram 22                      |    | 12.6 静电放电警告                                                 |       |

|   | 8.3 Feature Description                              |    |                                                             |       |

|   | 8.4 Device Functional Modes43                        | 40 | · · ·                                                       |       |

|   | 8.5 Programming                                      | 13 | 机械、封装和可订购信息                                                 | . 130 |

# 4 修订历史记录

| 日期         | 修订版本 | 注释    |

|------------|------|-------|

| 2016 年 9 月 | *    | 最初发布。 |

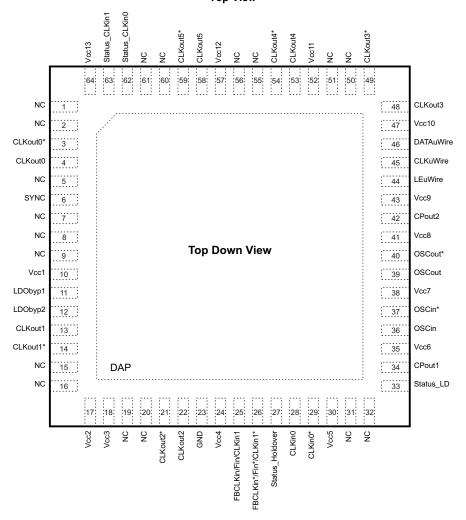

# 5 Pin Configuration and Functions

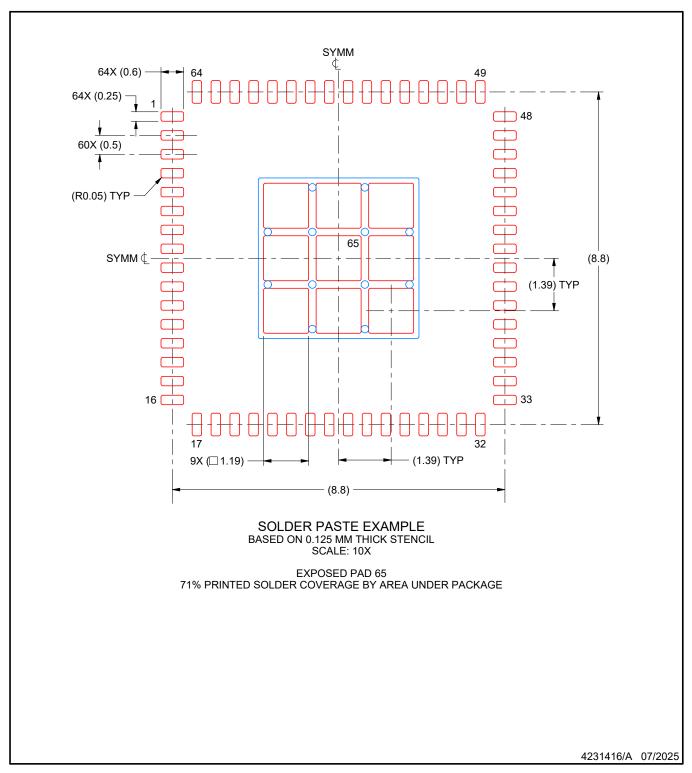

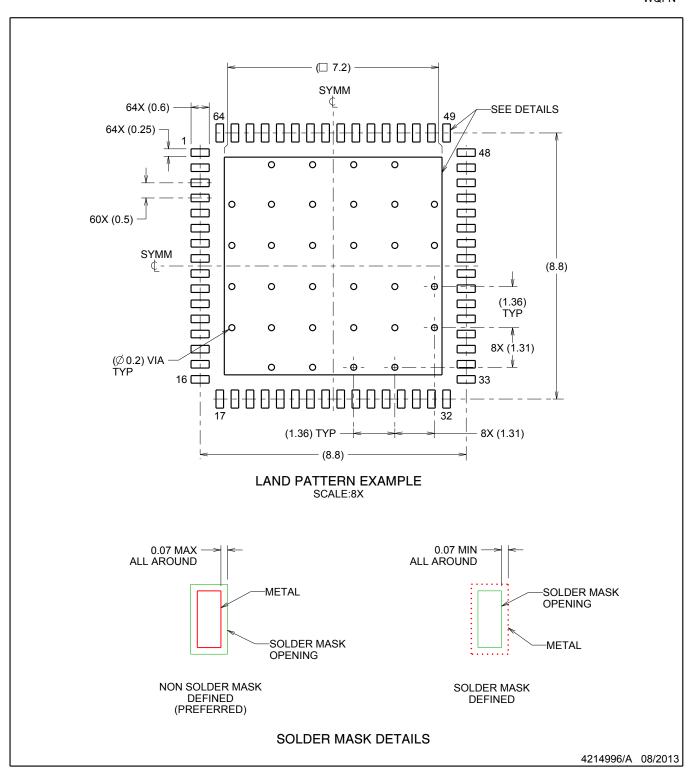

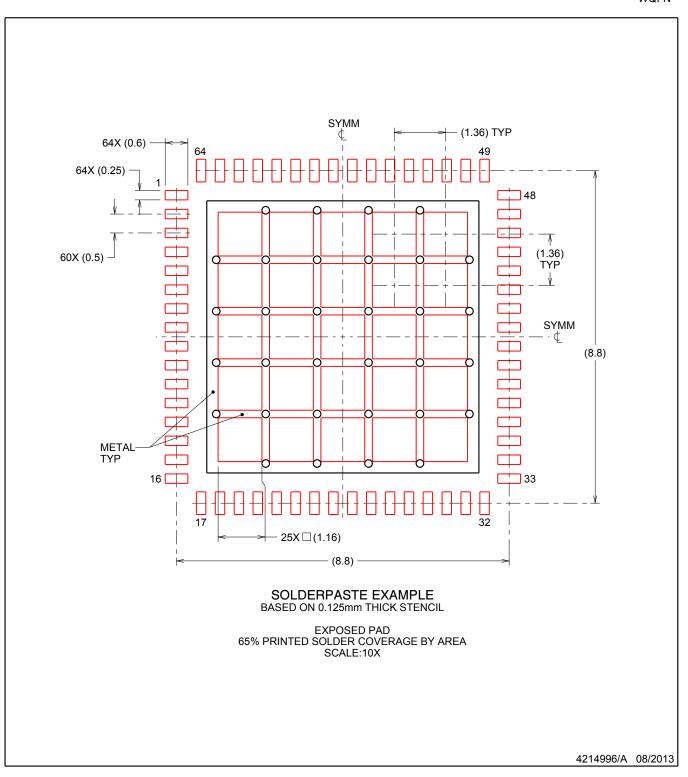

#### NKD Package 64-Pin WQFN with Exposed Pad Top View

# Pin Functions<sup>(1)</sup>

| 1 III I unctions |                   |     |              |                                                          |  |  |

|------------------|-------------------|-----|--------------|----------------------------------------------------------|--|--|

|                  | PIN               | I/O | TYPE         | DESCRIPTION                                              |  |  |

| NO.              | NAME              | 1/0 | ITPE         | DESCRIPTION                                              |  |  |

| 1, 2             | NC                | _   | -            | No Connection. These pins must be left floating.         |  |  |

| 3, 4             | CLKout0*, CLKout0 | 0   | Programmable | Clock output 0.                                          |  |  |

| 5                | NC                | _   | -            | No Connection. These pins must be left floating.         |  |  |

| 6                | SYNC              | I/O | Programmable | CLKout Synchronization input or programmable status pin. |  |  |

| 7, 8, 9          | NC                | _   | -            | No Connection. These pins must be left floating.         |  |  |

| 10               | Vcc1              |     | PWR          | Power supply for VCO LDO.                                |  |  |

| 11               | LDObyp1           |     | ANLG         | LDO Bypass, bypassed to ground with 10-µF capacitor.     |  |  |

| 12               | LDObyp2           |     | ANLG         | LDO Bypass, bypassed to ground with a 0.1-µF capacitor.  |  |  |

| 13, 14           | CLKout1, CLKout1* | 0   | Programmable | Clock output 1.                                          |  |  |

| 15, 16           | NC                | _   | -            | No Connection. These pins must be left floating.         |  |  |

| 17               | Vcc2              |     | PWR          | Power supply for clock output 1.                         |  |  |

# (1) See Pin Connection Recommendations.

# Pin Functions<sup>(1)</sup> (continued)

| PIN    |                   |     |              |                                                                                                                                                                |

|--------|-------------------|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.    | NAME              | 1/0 | TYPE         | DESCRIPTION                                                                                                                                                    |

| 18     | Vcc3              |     | PWR          | Power supply for clock output 2.                                                                                                                               |

| 19, 20 | NC                | -   | _            | No Connection. These pins must be left floating.                                                                                                               |

| 21, 22 | CLKout2*, CLKout2 | 0   | Programmable | Clock output 2.                                                                                                                                                |

| 23     | GND               |     | PWR          | Ground.                                                                                                                                                        |

| 24     | Vcc4              |     | PWR          | Power supply for digital.                                                                                                                                      |

|        | CLKin1, CLKin1*   |     |              | Reference Clock Input Port 1 for PLL1. AC or DC Coupled.                                                                                                       |

| 25, 26 | FBCLKin, FBCLKin* | I   | ANLG         | Feedback input for external clock feedback input (0-delay mode). AC or DC Coupled.                                                                             |

|        | Fin/Fin*          |     |              | External VCO input (External VCO mode). AC or DC Coupled.                                                                                                      |

| 27     | Status_Holdover   | I/O | Programmable | Programmable status pin, default readback output. Programmable to holdover mode indicator. Other options available by programming.                             |

| 28, 29 | CLKin0, CLKin0*   | I   | ANLG         | Reference Clock Input Port 0 for PLL1.<br>AC or DC Coupled.                                                                                                    |

| 30     | Vcc5              |     | PWR          | Power supply for clock inputs.                                                                                                                                 |

| 31, 32 | NC                | _   | _            | No Connection. These pins must be left floating.                                                                                                               |

| 33     | Status_LD         | I/O | Programmable | Programmable status pin, default lock detect for PLL1 and PLL2. Other options available by programming.                                                        |

| 34     | CPout1            | 0   | ANLG         | Charge pump 1 output.                                                                                                                                          |

| 35     | Vcc6              |     | PWR          | Power supply for PLL1, charge pump 1.                                                                                                                          |

| 36, 37 | OSCin, OSCin*     | I   | ANLG         | Feedback to PLL1, Reference input to PLL2. AC Coupled.                                                                                                         |

| 38     | Vcc7              |     | PWR          | Power supply for OSCin, OSCout, and PLL2 circuitry. (2)                                                                                                        |

| 39, 40 | OSCout, OSCout*   | 0   | Programmable | Buffered output of OSCin port. (2)                                                                                                                             |

| 41     | Vcc8              |     | PWR          | Power supply for PLL2, charge pump 2.                                                                                                                          |

| 42     | CPout2            | 0   | ANLG         | Charge pump 2 output.                                                                                                                                          |

| 43     | Vcc9              |     | PWR          | Power supply for PLL2.                                                                                                                                         |

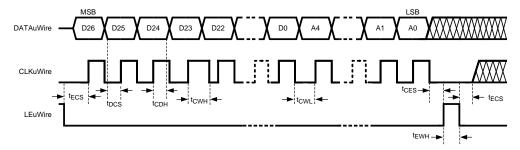

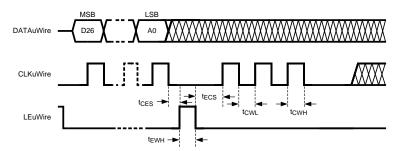

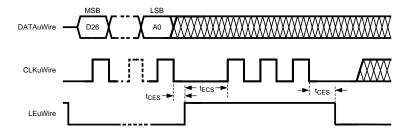

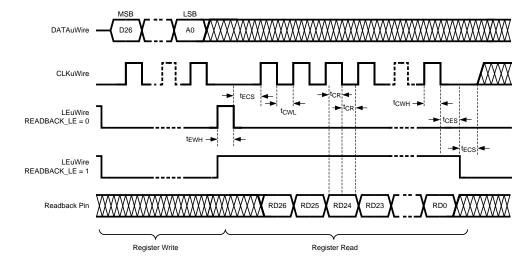

| 44     | LEuWire           | 1   | CMOS         | MICROWIRE Latch Enable Input.                                                                                                                                  |

| 45     | CLKuWire          | 1   | CMOS         | MICROWIRE Clock Input.                                                                                                                                         |

| 46     | DATAuWire         | - 1 | CMOS         | MICROWIRE Data Input.                                                                                                                                          |

| 47     | Vcc10             |     | PWR          | Power supply for clock output 3.                                                                                                                               |

| 48, 49 | CLKout3, CLKout3* | 0   | Programmable | Clock output 3.                                                                                                                                                |

| 50, 51 | NC                | _   | _            | No Connection. These pins must be left floating.                                                                                                               |

| 52     | Vcc11             |     | PWR          | Power supply for clock output 4.                                                                                                                               |

| 53, 54 | CLKout4, CLKout4* | 0   | Programmable | Clock output 4.                                                                                                                                                |

| 55, 56 | NC                | _   | _            | No Connection. These pins must be left floating.                                                                                                               |

| 57     | Vcc12             |     | PWR          | Power supply for clock output 5.                                                                                                                               |

| 58, 59 | CLKout5, CLKout5* | 0   | Programmable | Clock output 5.                                                                                                                                                |

| 60, 61 | NC                | _   | _            | No Connection. These pins must be left floating.                                                                                                               |

| 62     | Status_CLKin0     | I/O | Programmable | NC. Programmable status pin. Default is input for pin control of PLL1 reference clock selection. CLKin0 LOS status and other options available by programming. |

| 63     | Status_CLKin1     | I/O | Programmable | Programmable status pin. Default is input for pin control of PLL1 reference clock selection. CLKin1 LOS status and other options available by programming.     |

| 64     | Vcc13             |     | PWR          | Power supply for clock output 0.                                                                                                                               |

| DAP    | DAP               | -   | GND          | DIE ATTACH PAD, connect to GND.                                                                                                                                |

<sup>(2)</sup> See Vcc5 (CLKin), Vcc7 (OSCin and OSCout) for information on configuring device for optimum performance.

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)(1)

|                  |                                                                                  | MIN  | MAX            | UNIT |

|------------------|----------------------------------------------------------------------------------|------|----------------|------|

| V <sub>CC</sub>  | Supply voltage (3)                                                               | -0.3 | 3.6            | V    |

| $V_{IN}$         | Input voltage                                                                    | -0.3 | $V_{CC} + 0.3$ | V    |

| $T_L$            | Lead temperature (solder 4 seconds)                                              |      | 260            | °C   |

| TJ               | Junction temperature                                                             |      | 150            | °C   |

| I <sub>IN</sub>  | Differential input current (CLKinX/X*, OSCin/OSCin*, FBCLKin/FBCLKin*, Fin/Fin*) |      | ± 5            | mA   |

| MSL              | Moisture Sensitivity Level                                                       |      | 3              |      |

| T <sub>stg</sub> | Storage temperature                                                              | -65  | 150            | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|             |                         |                                                                                | VALUE | UNIT |

|-------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|             |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000 |      |

| $V_{(ESD)}$ | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±750  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions. Pins listed as ±2000 V may actually have higher performance.

# 6.3 Recommended Operating Conditions

|          |                      |                         |   | MIN  | NOM | MAX  | UNIT |

|----------|----------------------|-------------------------|---|------|-----|------|------|

| $T_J$    | Junction temperature |                         |   |      |     | 125  | °C   |

| $T_A$    | Ambient temperature  | V <sub>CC</sub> = 3.3 V |   | -40  | 25  | 85   | °C   |

| $V_{CC}$ | Supply voltage       |                         | ; | 3.15 | 3.3 | 3.45 | V    |

<sup>(2)</sup> If Military/Aerospace specified devices are required, contact the Texas Instruments Sales Office/Distributors for availability and specifications.

<sup>(3)</sup> Never to exceed 3.6 V.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions. Pins listed as ±750 V may actually have higher performance.

#### 6.4 Thermal Information

|                        |                                                                               | LMK04208   |      |

|------------------------|-------------------------------------------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                                                 | NKD (WQFN) | UNIT |

|                        |                                                                               | 64 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance on 4-layer JEDEC PCB <sup>(2)(3)</sup> | 25.2       | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance (4)(5)                              | 6.9        | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance (6)                                      | 4.0        | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter <sup>(7)</sup>                     | 0.1        | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter <sup>(8)</sup>                   | 4.0        | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance (9)                              | 0.8        | °C/W |

- For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

- (2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, High-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) Specification assumes 32 thermal vias connect the die attach pad to the embedded copper plane on the 4-layer JEDEC PCB. These vias play a key role in improving the thermal performance of the WQFN. Note that the JEDEC PCB is a standard thermal measurement PCB and does not represent best performance a PCB can achieve. TI recommends that the maximum number of vias be used in the board layout. R <sub>θJA</sub> is unique for each PCB.

- (4) The junction-to-case(top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (5) Case is defined as the DAP (die attach pad)

- (6) The junction-to-board thermal resistance is obtained by simulating an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- (7) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $R_{\theta JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- (8) The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining R<sub>0JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- (9) The junction-to-case(bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

www.ti.com.cn

# 6.5 Electrical Characteristics

$3.15 \text{ V} \le \text{V}_{\text{CC}} \le 3.45 \text{ V}$ ,  $-40 \text{ °C} \le \text{T}_{\text{A}} \le 85 \text{ °C}$ . Typical values represent most likely parametric norms at  $\text{V}_{\text{CC}} = 3.3 \text{ V}$ ,  $\text{T}_{\text{A}} = 25 \text{ °C}$ , at the Recommended Operating Conditions at the time of product characterization and are not specified. (1)

|                                     | PARAMETER                                                                | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | MIN   | TYP | MAX             | UNIT |

|-------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-----------------|------|

| CURRENT CON                         | SUMPTION                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |     |                 |      |

| CC_PD                               | Power down supply current                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | 1   | 3               | mA   |

| Icc_clks                            | Supply current with all clocks (CLKoutX) and OSCout enabled as LVDS. (2) | All clock delays disabled,<br>CLKoutX_DIV = 1045,<br>EN_SYNC=0<br>PLL1 and PLL2 locked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | 445 | 535             | mA   |

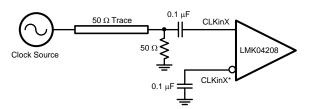

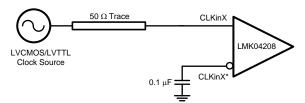

| CLKin0/0* and C                     | CLKin1/1* INPUT CLOCK SPECIFICATION                                      | IS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |     |                 |      |

| CLKin                               | Clock input frequency (3)                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.001 |     | 500             | MHz  |

| SLEW <sub>CLKin</sub> (1)           | Clock input slew rate (4)                                                | 20% to 80%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0.15  | 0.5 |                 | V/ns |

| V <sub>ID</sub> CLKin               |                                                                          | AC coupled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0.25  |     | 1.55            | V    |

| V <sub>SS</sub> CLKin               | Clock input  Differential input voltage (see (5) and                     | CLKinX_BUF_TYPE = 0 (Bipolar)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.5   |     | 3.1             | Vpp  |

| V <sub>ID</sub> CLKin               | Figure 8)                                                                | AC coupled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0.25  |     | 1.55            | V    |

| V <sub>SS</sub> CLKin               |                                                                          | CLKinX_BUF_TYPE = 1 (MOS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.5   |     | 3.1             | Vpp  |

|                                     | Clock input                                                              | AC coupled to CLKinX; CLKinX* AC coupled to Ground 0.25 CLKinX_BUF_TYPE = 0 (Bipolar)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.4   | Vpp |                 |      |

| V <sub>CLKin</sub>                  | Single-ended input voltage (4)                                           | AC coupled to CLKinX; CLKinX* AC coupled to Ground CLKinX_BUF_TYPE = 1 (MOS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.25  |     | 2.4             | Vpp  |

| V <sub>CLKin0-offset</sub>          | DC offset voltage between<br>CLKin0/CLKin0*<br>CLKin0* - CLKin0          | Each pin AC coupled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       | 20  |                 | mV   |

| V <sub>CLKin1-offset</sub>          | DC offset voltage between<br>CLKin1/CLKin1*<br>CLKin1* - CLKin1          | All clock delays disabled, CLKoutX_DIV = 1045, EN_SYNC=0 PLL1 and PLL2 locked.  20% to 80%  AC coupled CLKinX_BUF_TYPE = 0 (Bipolar)  AC coupled to CLKinX; CLKinX* AC coupled to Ground CLKinX_BUF_TYPE = 0 (Bipolar)  AC coupled to CLKinX; CLKinX* AC coupled to Ground CLKinX_BUF_TYPE = 1 (MOS)  AC coupled to CLKinX; CLKinX* AC coupled to Ground CLKinX_BUF_TYPE = 1 (MOS)  Each pin AC coupled CLKinO_BUF_TYPE = 0 (Bipolar)  Each pin AC coupled CLKinX_BUF_TYPE = 1 (MOS)  DC coupled to CLKinX; CLKinX* AC coupled to Ground CLKinX_BUF_TYPE = 1 (MOS)  DC coupled to Ground CLKinX_BUF_TYPE = 1 (MOS)  AC coupled (CLKinX_BUF_TYPE = 0) |       | 0   |                 | mV   |

| V <sub>CLKinX-offset</sub>          | DC offset voltage between<br>CLKinX/CLKinX*<br>CLKinX* - CLKinX          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | 55  |                 | mV   |

| V <sub>CLKin-</sub> V <sub>IH</sub> | High input voltage                                                       | DC coupled to CLKinX; CLKinX* AC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.0   |     | V <sub>CC</sub> | V    |

| V <sub>CLKin-</sub> V <sub>IL</sub> | Low input voltage                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.0   |     | 0.4             | V    |

| FBCLKin/FBCL                        | Kin* and Fin/Fin* INPUT SPECIFICATIONS                                   | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |     |                 |      |

| f <sub>FBCLKin</sub>                | Clock input frequency <sup>(4)</sup>                                     | (CLKinX_BUF_TYPE = 0)<br>MODE = 2 or 8; FEEDBACK_MUX =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0.001 |     | 1000            | MHz  |

| f <sub>Fin</sub>                    | Clock input frequency <sup>(4)</sup>                                     | (CLKinX_BUF_TYPE = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.001 |     | 3100            | MHz  |

| V <sub>FBCLKin/Fin</sub>            | Single Ended<br>Clock input voltage <sup>(4)</sup>                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.25  |     | 2.0             | Vpp  |

| SLEW <sub>FBCLKin/Fin</sub>         | Slew rate on CLKin <sup>(4)(1)</sup>                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.15  | 0.5 |                 | V/ns |

<sup>(1)</sup> In order to meet the jitter performance listed in the subsequent sections of this data sheet, the minimum recommended slew rate for all input clocks is 0.5 V/ns. This is especially true for single-ended clocks. Phase noise performance begins to degrade as the clock input slew rate is reduced. However, the device functions at slew rates down to the minimum listed. When compared to single-ended clocks, differential clocks (LVDS, LVPECL) are less susceptible to degradation in phase noise performance at lower slew rates due to their common mode noise rejection. However, it is also recommended to use the highest possible slew rate for differential clocks to achieve optimal phase noise performance at the device outputs.

<sup>(2)</sup> Load conditions for output clocks: LVDS: 100 Ω differential. See Current Consumption and Power Dissipation Calculations for Icc for specific part configuration and how to calculate Icc for a specific design.

<sup>(3)</sup> CLKin0, CLKin1 maximum is specified by characterization, production tested at 200 MHz.

<sup>(4)</sup> Specified by characterization.

<sup>5)</sup> See Differential Voltage Measurement Terminology for definition of V<sub>ID</sub> and V<sub>OD</sub> voltages.

# STRUMENTS

# **Electrical Characteristics (continued)**

$3.15~\text{V} \leq \text{V}_{\text{CC}} \leq 3.45~\text{V}, -40~\text{°C} \leq \text{T}_{\text{A}} \leq 85~\text{°C}.$  Typical values represent most likely parametric norms at  $\text{V}_{\text{CC}} = 3.3~\text{V}, \text{T}_{\text{A}} = 25~\text{°C},$ at the Recommended Operating Conditions at the time of product characterization and are not specified. (1)

|                                       | PARAMETER                                                          | TEST CONDITIONS                                                                 | MIN  | TYP    | MAX  | UNIT    |

|---------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------|------|--------|------|---------|

| PLL1 SPECIFICA                        | ATIONS                                                             |                                                                                 |      |        |      |         |

| f <sub>PD1</sub>                      | PLL1 phase detector frequency                                      |                                                                                 |      |        | 40   | MHz     |

|                                       |                                                                    | V <sub>CPout1</sub> = V <sub>CC</sub> /2, PLL1_CP_GAIN = 0                      |      | 100    |      |         |

|                                       | PLL1 charge                                                        | V <sub>CPout1</sub> = V <sub>CC</sub> /2, PLL1_CP_GAIN = 1                      |      | 200    |      | 4       |

| I <sub>CPout1</sub> SOURCE            | Pump source current <sup>(6)</sup>                                 | V <sub>CPout1</sub> = V <sub>CC</sub> /2, PLL1_CP_GAIN = 2                      |      | 400    |      | μA      |

|                                       |                                                                    | V <sub>CPout1</sub> = V <sub>CC</sub> /2, PLL1_CP_GAIN = 3                      |      | 1600   | 000  |         |

|                                       |                                                                    | V <sub>CPout1</sub> =V <sub>CC</sub> /2, PLL1_CP_GAIN = 0                       |      | -100   |      |         |

| I OINIK                               | PLL1 charge                                                        | V <sub>CPout1</sub> =V <sub>CC</sub> /2, PLL1_CP_GAIN = 1                       |      | -200   |      | 4       |

| I <sub>CPout1</sub> SINK              | Pump sink current (6)                                              | V <sub>CPout1</sub> =V <sub>CC</sub> /2, PLL1_CP_GAIN = 2                       |      | -400   |      | μA      |

|                                       |                                                                    | V <sub>CPout1</sub> =V <sub>CC</sub> /2, PLL1_CP_GAIN = 3                       |      | -1600  |      |         |

| I <sub>CPout1</sub> %MIS              | Charge pump<br>Sink/source mismatch                                | V <sub>CPout1</sub> = V <sub>CC</sub> /2, T = 25 °C                             |      | 3%     | 10%  |         |

| I <sub>CPout1</sub> V <sub>TUNE</sub> | Magnitude of charge pump current variation vs. charge pump voltage | 0.5 V < V <sub>CPout1</sub> < V <sub>CC</sub> - 0.5 V<br>T <sub>A</sub> = 25 °C |      | 4%     |      |         |

| I <sub>CPout1</sub> %TEMP             | Charge pump current vs. temperature variation                      |                                                                                 |      | 4%     |      |         |

| I <sub>CPout1</sub> TRI               | Charge Pump TRI-STATE leakage current                              | 0.5 V < V <sub>CPout</sub> < V <sub>CC</sub> - 0.5 V                            |      |        | 5    | nA      |

| PN10kHz                               | PLL 1/f noise at 10 kHz offset. (7)                                | PLL1_CP_GAIN = 400 µA                                                           |      | -117   |      | dBc/Hz  |

| PINTUKEZ                              | Normalized to 1 GHz Output Frequency                               | PLL1_CP_GAIN = 1600 μA                                                          |      | -118   |      | UDC/FIZ |

| DN411-                                | Normalized phase poice contribution (8)                            | PLL1_CP_GAIN = 400 µA                                                           |      | -221.5 |      | dDa/Lla |

| PN1Hz                                 | Normalized phase noise contribution (8)                            | PLL1_CP_GAIN = 1600 μA                                                          |      | -223   |      | dBc/Hz  |

| PLL2 REFEREN                          | CE INPUT (OSCin) SPECIFICATIONS                                    |                                                                                 |      |        |      |         |

| f <sub>OSCin</sub>                    | PLL2 reference input <sup>(9)</sup>                                |                                                                                 |      |        | 500  | MHz     |

| SLEW <sub>OSCin</sub>                 | PLL2 reference clock minimum slew rate on OSCin <sup>(4)</sup>     | 20% to 80%                                                                      | 0.15 | 0.5    |      | V/ns    |

| V <sub>OSCin</sub>                    | Input voltage for OSCin or OSCin*(4)                               | AC coupled; Single-ended (Unused pin AC coupled to GND)                         | 0.2  |        | 2.4  | Vpp     |

| V <sub>ID</sub> OSCin                 | Differential colleges and a configuration (and Figure 6)           | A Constant                                                                      | 0.2  |        | 1.55 | V       |

| V <sub>SS</sub> OSCin                 | Differential voltage swing (see Figure 8)                          | AC coupled                                                                      | 0.4  |        | 3.1  | Vpp     |

| V <sub>OSCin-offset</sub>             | DC offset voltage between<br>OSCin/OSCin*<br>OSCinX* - OSCinX      | Each pin AC coupled                                                             |      | 20     |      | mV      |

| f <sub>doubler_max</sub>              | Doubler input frequency (4)                                        | EN_PLL2_REF_2X = 1; <sup>(10)</sup><br>OSCin Duty Cycle 40% to 60%              |      |        | 155  | MHz     |

This parameter is programmable

A specification in modeling PLL in-band phase noise is the 1/f flicker noise, L<sub>PLL\_flicker</sub>(f), which is dominant close to the carrier. Flicker noise has a 10 dB/decade slope. PN10kHz is normalized to a 10 kHz offset and a 1 GHz carrier frequency. PN10kHz = L<sub>PLL\_flicker</sub>(10 kHz) - 20log(Fout / 1 GHz), where L<sub>PLL flicker</sub>(f) is the single side band phase noise of only the flicker noise's contribution to total noise, L(f). To measure L<sub>PLL\_flicker</sub>(f) it is important to be on the 10 dB/decade slope close to the carrier. A high compare frequency and a clean crystal are important to isolating this noise source from the total phase noise, L(f). L<sub>PLL\_flicker</sub>(f) can be masked by the reference oscillator performance if a low power or noisy source is used. The total PLL in-band phase noise performance is the sum of LPLL flicker(f) and L<sub>PLL\_flat</sub>(f).

<sup>(8)</sup> A specification modeling PLL in-band phase noise. The normalized phase noise contribution of the PLL, L<sub>PLL</sub> flat(f), is defined as: PN1HZ=L<sub>PLL\_flat</sub>(f) - 20log(N) - 10log(f<sub>PDX</sub>). L<sub>PLL\_flat</sub>(f) is the single side band phase noise measured at an offset frequency, f, in a 1 Hz bandwidth and f<sub>PDX</sub> is the phase detector frequency of the synthesizer. L<sub>PLL flat</sub>(f) contributes to the total noise, L(f).

<sup>(9)</sup> F<sub>OSCin</sub> maximum frequency specified by characterization. Production tested at 200 MHz.

(10) The EN\_PLL2\_REF\_2X bit (Register 13) enables/disables a frequency doubler mode for the PLL2 OSCin path.

# **Electrical Characteristics (continued)**

|                                       | PARAMETER                                                                                                                                                                                                                                | TEST CONDITIONS                                                                                            | MIN TYP  | MAX  | UNIT        |  |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------|------|-------------|--|

| CRYSTAL OSC                           | ILLATOR MODE SPECIFICATIONS                                                                                                                                                                                                              |                                                                                                            |          |      |             |  |

| f <sub>XTAL</sub>                     | Crystal frequency range <sup>(4)</sup>                                                                                                                                                                                                   | R <sub>ESR</sub> < 40 Ω                                                                                    | 6        | 20.5 | MHz         |  |

| P <sub>XTAL</sub>                     | Crystal power dissipation <sup>(11)</sup>                                                                                                                                                                                                | Vectron VXB1 crystal, 20.48 MHz, $R_{\text{ESR}} < 40~\Omega$ XTAL_LVL = 0                                 | 100      |      | μW          |  |

| C <sub>IN</sub>                       | Input capacitance of<br>LMK04208 OSCin port                                                                                                                                                                                              | -40 to +85 °C                                                                                              | 6        |      | pF          |  |

| PLL2 PHASE D                          | ETECTOR and CHARGE PUMP SPECIFIC                                                                                                                                                                                                         | ATIONS                                                                                                     |          |      |             |  |

| f <sub>PD2</sub>                      | Phase detector frequency                                                                                                                                                                                                                 |                                                                                                            |          | 155  | MHz         |  |

|                                       |                                                                                                                                                                                                                                          | $V_{CPout2}=V_{CC}/2$ , PLL2_CP_GAIN = 0                                                                   | 100      |      |             |  |

| I COLIDOR                             | PLL2 charge pump source current <sup>(6)</sup>                                                                                                                                                                                           | V <sub>CPout2</sub> =V <sub>CC</sub> /2, PLL2_CP_GAIN = 1                                                  | 400      |      | ^           |  |

| I <sub>CPout</sub> SOURCE             |                                                                                                                                                                                                                                          | V <sub>CPout2</sub> =V <sub>CC</sub> /2, PLL2_CP_GAIN = 2                                                  | 1600     |      | μΑ          |  |

|                                       |                                                                                                                                                                                                                                          | V <sub>CPout2</sub> =V <sub>CC</sub> /2, PLL2_CP_GAIN = 3                                                  | 3200     |      |             |  |

|                                       | PLL2 charge pump sink current <sup>(6)</sup>                                                                                                                                                                                             | $V_{CPout2}=V_{CC}/2$ , PLL2_CP_GAIN = 0                                                                   | -100     |      |             |  |

|                                       |                                                                                                                                                                                                                                          | V <sub>CPout2</sub> =V <sub>CC</sub> /2, PLL2_CP_GAIN = 1                                                  | -400     |      |             |  |

| I <sub>CPout</sub> SINK               |                                                                                                                                                                                                                                          | V <sub>CPout2</sub> =V <sub>CC</sub> /2, PLL2_CP_GAIN = 2                                                  | -1600    |      | μA          |  |

|                                       |                                                                                                                                                                                                                                          | V <sub>CPout2</sub> =V <sub>CC</sub> /2, PLL2_CP_GAIN = 3                                                  | -3200    |      |             |  |

| I <sub>CPout2</sub> %MIS              | Charge pump sink/source mismatch                                                                                                                                                                                                         | V <sub>CPout2</sub> =V <sub>CC</sub> /2, T <sub>A</sub> = 25 °C                                            | 3%       | 10%  |             |  |

| I <sub>CPout2</sub> V <sub>TUNE</sub> | Magnitude of charge pump current vs. charge pump voltage variation                                                                                                                                                                       | 0.5 V < V <sub>CPout2</sub> < V <sub>CC</sub> - 0.5 V<br>T <sub>A</sub> = 25 °C                            | 4%       |      |             |  |

| I <sub>CPout2</sub> %TEMP             | Charge pump current vs. Temperature variation                                                                                                                                                                                            |                                                                                                            | 4%       |      |             |  |

| I <sub>CPout2</sub> TRI               | Charge pump leakage                                                                                                                                                                                                                      | 0.5 V < V <sub>CPout2</sub> < V <sub>CC</sub> - 0.5 V                                                      |          | 10   | nA          |  |

| DNAOL I                               | PLL 1/f Noise at 10 kHz offset <sup>(7)</sup> Normalized to 1 GHz output frequency                                                                                                                                                       | PLL2_CP_GAIN = 400 µA                                                                                      | -118     |      | -ID - /I I- |  |

| PN10kHz                               |                                                                                                                                                                                                                                          | PLL2_CP_GAIN = 3200 µA                                                                                     | -121     |      | dBc/Hz      |  |

| DN411-                                | Normalized Phase Noise Contribution (8)                                                                                                                                                                                                  | PLL2_CP_GAIN = 400 µA                                                                                      | -222.5   |      | dDo/Lla     |  |

| PN1Hz                                 | Normalized Phase Noise Contribution (*)                                                                                                                                                                                                  | PLL2_CP_GAIN = 3200 μA                                                                                     | -227     |      | dBc/Hz      |  |

| INTERNAL VCC                          | SPECIFICATIONS                                                                                                                                                                                                                           |                                                                                                            |          |      |             |  |

| f <sub>VCO</sub>                      | VCO tuning range                                                                                                                                                                                                                         | LMK04208                                                                                                   | 2750     | 3072 | MHz         |  |

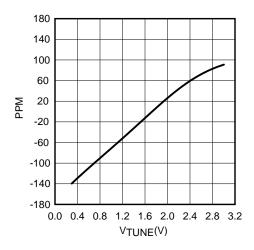

| K <sub>vco</sub>                      | Fine tuning sensitivity (The range displayed in the typical column indicates the lower sensitivity is typical at the lower end of the tuning range, and the higher tuning sensitivity is typical at the higher end of the tuning range). | LMK04208                                                                                                   | 20 to 36 |      | MHz/V       |  |

| $ \Delta T_{CL} $                     | Allowable Temperature Drift for Continuous Lock <sup>(12)</sup> (4)                                                                                                                                                                      | After programming R30 for lock, no changes to output configuration are permitted to ensure continuous lock | -        | 125  | °C          |  |

<sup>(11)</sup> See Application Section discussion of Optional Crystal Oscillator Implementation (OSCin/OSCin\*).

<sup>(12)</sup> Maximum Allowable Temperature Drift for Continuous Lock is how far the temperature can drift in either direction from the value it was at the time that the R30 register was last programmed, and still have the part stay in lock. The action of programming the R30 register, even to the same value, activates a frequency calibration routine. This implies the part works over the entire frequency range, but if the temperature drifts more than the maximum allowable drift for continuous lock, then it is necessary to reload the R30 register to ensure it stays in lock. Regardless of what temperature the part was initially programmed at, the temperature can never drift outside the frequency range of -40 °C to 85 °C without violating specifications.

# **Electrical Characteristics (continued)**

|                                                           | PARAMETER                                                 | TEST CONDITIONS                           | MIN       | TYP    | MAX     | UNIT    |  |

|-----------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------|-----------|--------|---------|---------|--|

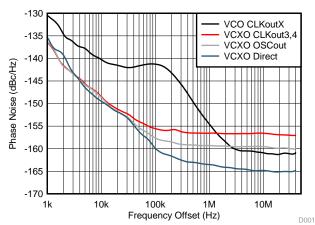

| CLKout CLOSEI                                             | D LOOP JITTER SPECIFICATIONS USING                        | a COMMERCIAL QUALITY VCXO <sup>(13)</sup> |           |        |         |         |  |

|                                                           |                                                           | Offset = 1 kHz                            |           | -122.5 |         |         |  |

|                                                           |                                                           | Offset = 10 kHz                           |           | -132.9 |         |         |  |

|                                                           | LMK04208                                                  | Offset = 100 kHz                          |           | -135.2 |         |         |  |

| L(f) <sub>CLKout</sub>                                    | f <sub>CLKout</sub> = 245.76 MHz<br>SSB Phase noise       | Offset = 800 kHz                          |           | -143.9 |         | dBc/Hz  |  |

| L(i)CLKout                                                | Measured at clock outputs                                 | Offset = 10 MHz; LVDS                     |           | -156.0 |         | abo/112 |  |

|                                                           | Value is average for all output types (14)                | Offset = 10 MHz; LVPECL 1600 mVpp         |           | -157.5 |         |         |  |

|                                                           |                                                           | Offset = 10 MHz; LVCMOS                   |           | -157.1 |         |         |  |

| J <sub>CLKout</sub>                                       | LMK04208 <sup>(14)</sup>                                  | BW = 12 kHz to 20 MHz                     |           | 111    |         |         |  |

| LVDS/LVPECL/<br>LVCMOS                                    | f <sub>CLKout</sub> = 245.76 MHz<br>Integrated RMS jitter | BW = 100 Hz to 20 MHz                     |           | 123    |         | fs, RMS |  |

| <b>CLKout CLOSE</b>                                       | D LOOP JITTER SPECIFICATIONS USING                        | THE INTEGRATED LOW NOISE CRY              | STAL OSCI | LLATOR | CIRCUIT | - (15)  |  |

|                                                           | LMK04208                                                  | BW = 12 kHz to 20 MHz<br>XTAL_LVL = 3     |           | 192    |         | fo rmo  |  |

| f <sub>CLKout</sub> = 245.76 MHz<br>Integrated RMS jitter |                                                           | BW = 100 Hz to 20 MHz<br>XTAL_LVL = 3     |           | 450    |         | fs rms  |  |

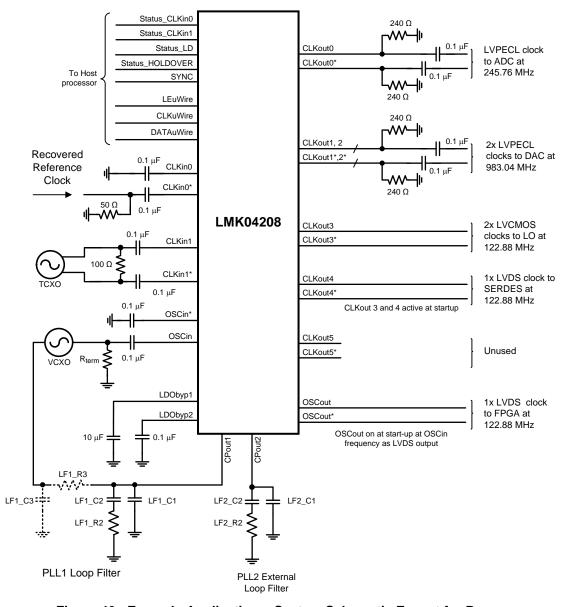

| DEFAULT POWE                                              | ER ON RESET CLOCK OUTPUT FREQUE                           | ENCY                                      | •         |        |         |         |  |

| f <sub>CLKout-startup</sub>                               | Default output clock frequency at device power on (16)    | CLKout4, LVDS, LMK04208                   | 90        | 110    | 130     | MHz     |  |

<sup>(13)</sup> VCXO used is a 122.88-MHz Crystek CVHD-950-122.880.

<sup>(14)</sup>  $f_{VCO} = 2949.12$  MHz, PLL1 parameters:  $F_{PD1} = 1.024$  MHz,  $I_{CP1} = 100$   $\mu$ A, loop bandwidth = 10 Hz. 122.88 MHz Crystek CVHD-950–122.880. PLL2 parameters:  $PLL2_R = 1$ ,  $F_{PD2} = 122.88$  MHz,  $I_{CP2} = 3200$   $\mu$ A, C1 = 47 pF, C2 = 3.9 nF, R2 = 620  $\Omega$ ,  $PLL2_C3_LF = 0$ ,  $PLL2_R3_LF = 0$ ,  $PLL2_C4_LF = 0$ ,  $PLL2_R4_LF = 0$ , PLL2

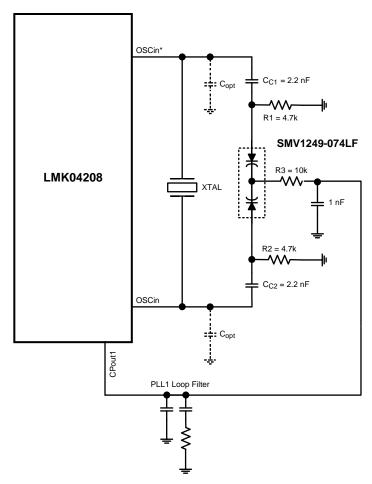

<sup>(15)</sup> Crystal used is a 20.48-MHz Vectron VXB1-1150-20M480 and Skyworks varactor diode, SMV-1249-074LF.

<sup>(16)</sup> CLKout3 and OSCout also oscillate at start-up at the frequency of the VCXO attached to OSCin port.

# **Electrical Characteristics (continued)**

|                                    | PARAMETER                                                                                       | TEST CONDITIONS                                                                                                                                                                                                            | MIN   | TYP  | MAX   | UNIT |

|------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| CLOCK SKEW                         | and DELAY                                                                                       |                                                                                                                                                                                                                            |       |      |       |      |

|                                    |                                                                                                 | LVDS-to-LVDS, T = 25 °C, $F_{CLK}$ = 800 MHz, $R_L$ = 100 $\Omega$ AC coupled                                                                                                                                              |       | 30   |       |      |

| T <sub>SKEW</sub>                  | Maximum CLKoutX to CLKoutY (4) (17)                                                             | LVPECL-to-LVPECL, T = 25 °C, F <sub>CLK</sub> = 800 MHz, R <sub>L</sub> = 100 $\Omega$ emitter resistors = 240 $\Omega$ to GND AC coupled                                                                                  |       | 30   | 30    |      |

|                                    | Maximum skew between any two LVCMOS outputs, same CLKout or different CLKout <sup>(4)(17)</sup> | $R_L = 50 \Omega$ , $C_L = 5 pF$ ,<br>$T = 25 °C$ , $F_{CLK} = 100 MHz$ .                                                                                                                                                  |       | 100  |       |      |

| MixedT <sub>SKEW</sub>             | LVDS or LVPECL to LVCMOS                                                                        | Same device, T = 25 °C,<br>250 MHz                                                                                                                                                                                         |       | 750  |       | ps   |

|                                    |                                                                                                 | MODE = 2<br>PLL1_R_DLY = 0; PLL1_N_DLY = 0                                                                                                                                                                                 |       | 1850 |       |      |

| td <sub>0-DELAY</sub>              | CLKin to CLKoutX delay <sup>(17)</sup>                                                          | MODE = 2 PLL1_R_DLY = 0; PLL1_N_DLY = 0; VCO Frequency = 2949.12 MHz Analog delay select = 0; Feedback clock digital delay = 11; Feedback clock half step = 1; Output clock digital delay = 5; Output clock half step = 0; |       | 0    |       | ps   |

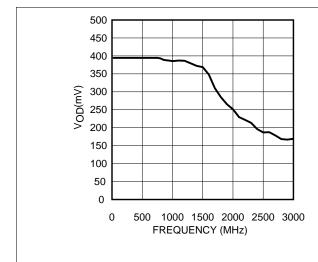

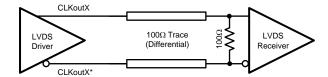

| LVDS CLOCK                         | OUTPUTS (CLKoutX), CLKoutX_TYPE = 1                                                             |                                                                                                                                                                                                                            |       |      |       |      |

| f <sub>CLKout</sub>                | Maximum frequency <sup>(4)(18)</sup>                                                            | $R_L = 100 \Omega$                                                                                                                                                                                                         | 1536  |      |       | MHz  |

| V <sub>OD</sub>                    | Differential autout valtage (and Figure 0)                                                      |                                                                                                                                                                                                                            | 250   | 400  | 450   | mV   |

| V <sub>SS</sub>                    | Differential output voltage (see Figure 9)                                                      |                                                                                                                                                                                                                            | 500   | 800  | 900   | mVpp |

| $\Delta V_{OD}$                    | Change in magnitude of V <sub>OD</sub> for complementary output states                          | T = 25 °C, DC measurement<br>AC coupled to receiver input                                                                                                                                                                  | -50   |      | 50    | mV   |

| V <sub>OS</sub>                    | Output offset voltage                                                                           | $R = 100-\Omega$ differential termination                                                                                                                                                                                  | 1.125 | 1.25 | 1.375 | V    |

| $\Delta V_{OS}$                    | Change in $V_{\text{OS}}$ for complementary output states                                       |                                                                                                                                                                                                                            |       |      | 35    | mV   |

| T /T                               | Output rise time                                                                                | 20% to 80%, RL = 100 $\Omega$                                                                                                                                                                                              | 200   |      |       | no   |

| $T_R / T_F$                        | Output fall time                                                                                | 80% to 20%, RL = 100 $\Omega$                                                                                                                                                                                              |       |      |       | ps   |

| I <sub>SA</sub><br>I <sub>SB</sub> | Output short circuit current single-ended                                                       | Single-ended output shorted to GND T = 25 °C                                                                                                                                                                               | -24   |      | 24    | mA   |

| I <sub>SAB</sub>                   | Output short circuit current - differential                                                     | Complimentary outputs tied together                                                                                                                                                                                        | -12   |      | 12    | mA   |

<sup>(17)</sup> Equal loading and identical clock output configuration on each clock output is required for specification to be valid. Specification is not valid for CLKoutX or CLKoutY in analog delay mode.

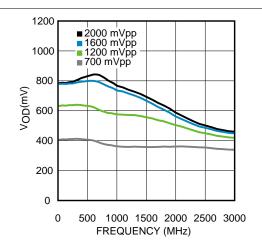

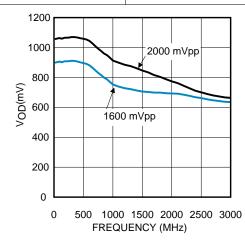

<sup>(18)</sup> Refer to Typical Characteristics for output operation performance at higher frequencies than the minimum maximum output frequency.

# **Electrical Characteristics (continued)**

|                                    | PARAMETER                            | TEST CONDITIONS                                                               | MIN                   | TYP                       | MAX        | UNIT        |  |  |

|------------------------------------|--------------------------------------|-------------------------------------------------------------------------------|-----------------------|---------------------------|------------|-------------|--|--|

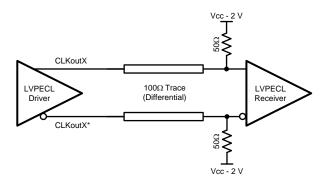

| LVPECL CLOCK OUTPUTS (CLKoutX)     |                                      |                                                                               |                       |                           |            |             |  |  |

| f <sub>CLKout</sub>                | Maximum frequency (4) (18)           |                                                                               | 1536                  |                           |            | MHz         |  |  |

|                                    | 20% to 80% output rise               | RL = 100 $\Omega$ , emitter resistors = 240 $\Omega$                          |                       |                           |            |             |  |  |

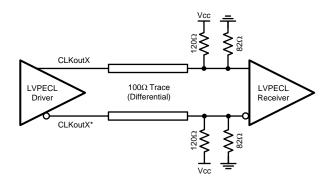

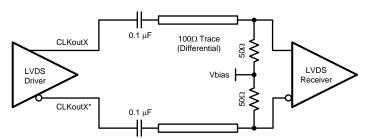

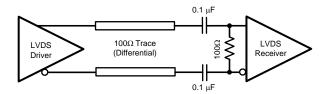

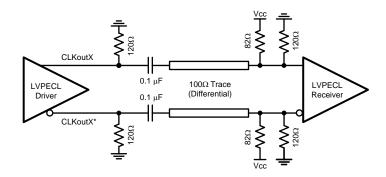

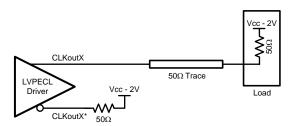

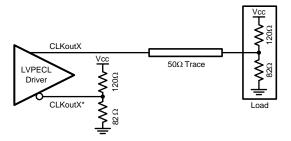

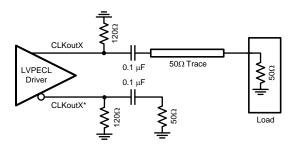

| T <sub>R</sub> / T <sub>F</sub>    | 80% to 20% output fall time          | to GND<br>CLKoutX_TYPE = 4 or 5<br>(1600 or 2000 mVpp)                        |                       | 150                       |            | ps          |  |  |