LMH5485-SP ZHCSLH1A - SEPTEMBER 2021 - REVISED DECEMBER 2021

# LMH5485-SP 耐 Hardened 辐射 (RHA) 型负轨输入、轨至轨输出高精度 850MHz 全差分放大器

### 1 特性

- 已通过 QMLV (QML V 级 ) MIL-PRF-38535 认 证, SMD 5962R1920401VXC

- 辐射加固保障 (RHA) 能力高达 100krad (Si) 总 电离剂量 (TID)

- 单粒子闩锁 (SEL) 对于 LET 的 抗扰度 = 85MeV-cm2/mg

- 支持军用级温度范围: -55°C 至 125°C

- 全差分放大器 (FDA) 架构

- 带宽:490MHz (G = 2V/V)

- 增益带宽积(GBWP):850MHz

- 压摆率:1400V/µs

- HD2、HD3: -79dBc、-97dBc (10MHz、2

- 输入电压噪声: 2.4nV/ √Hz (f > 100kHz)

- 输入失调电压、温漂:±100μV、±0.5μV/°C

- 负轨输入 (NRI)、轨到轨输出 (RRO)

- 输出共模控制

- 电源:

- 电源电压范围: 2.7V 至 5.1V - 静态电流:10.1mA(5V电源) - 断电能力: 2µA(典型值)

### 2 应用

- 低功耗高性能 ADC 驱动器:

- SAR、ΔΣ和流水线

- 差分 DAC 输出驱动器

- 命令和数据处理

- 运载火箭系统

- 空间成像系统:

- 光学成像有效载荷

- 雷达成像有效载荷

- 热成像摄像机

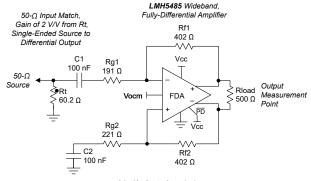

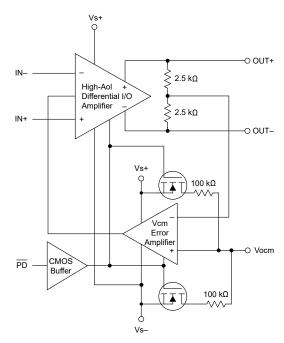

简化版原理图

### 3 说明

LMH5485-SP 是一款辐射、低功耗、电压反馈、全差 分放大器 (FDA),输入共模范围低于负电源轨和轨至轨 输出。专为功耗敏感型数据采集系统而设计,在这些系 统中,高密度对于高性能模数转换器 (ADC) 或数模转 换器 (DAC) 接口设计至关重要。

LMH5485-SP 具有所需的负电源轨输入,可用于连接 直流耦合、以接地为中心的源信号。此负电源轨输入搭 配轨至轨输出,只需使用一个 2.7V 至 5.1V 的电源, 即可轻松将单端接地基准双极信号源与各种逐次逼近寄 存器 (SAR)、Δ-Σ 或流水线 ADC 相连接。 LMH5485-SP 还为此类 ADC 驱动应用提供出色的直流 精度,并可在 - 55°C 至 +125°C 的宽温度范围内运 行。

#### 器件信息

| 器件型号 <sup>(1)</sup> | 等级            | 封装            |

|---------------------|---------------|---------------|

| 5962R1920401VXC     | 耐辐射加固保障 (RHA) | 陶瓷 CFP        |

| 5962-1920401VXC     | QMLV          | HKX (8)       |

| LMH5485HKX/EM       | 工程样片(2)       | 6.5mm × 6.5mm |

- 如需了解所有可用封装,请参阅数据表末尾的封装选项附录。 (1)

- 这些器件仅适用于工程评估。器件按照不合规的流程进行加工 处理。这些器件不适用于质检、生产、辐射测试或飞行。这些 零器件无法在 - 55°C 至 125°C 的完整 MIL 额定温度范围内或 运行寿命中保证其性能。

单端到差分增益为 2 的 100mV<sub>PP</sub> 输出

# **Table of Contents**

| 1 特性                                                      | 9 Detailed Description                                 |

|-----------------------------------------------------------|--------------------------------------------------------|

|                                                           |                                                        |

|                                                           |                                                        |

|                                                           |                                                        |

|                                                           |                                                        |

| • • •                                                     | 12.2 Receiving Notification of Documentation Updates30 |

| 7.5 Electrical Characteristics: $V_{S+} - V_{S-} = 5 V_{$ | 12.3 支持资源30                                            |

| <u> </u>                                                  | 12.4 Trademarks30                                      |

| 7.7 Quality Conformance Inspection                        | 12.5 Electrostatic Discharge Caution30                 |

| 7.8 Typical Characteristics: 5 V Single Supply11          | 12.6 术语表30                                             |

| 7.9 Typical Characteristics: 3 V Single Supply            | 13 Mechanical, Packaging, and Orderable                |

| 7.10 Typical Characteristics: 3 V to 5 V Supply Range13   | Information30                                          |

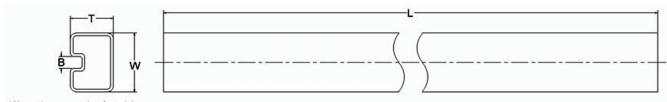

| 8 Parameter Measurement Information                       | 13.1 Tube Information32                                |

| 8.1 Example Characterization Circuits16                   |                                                        |

# **4 Revision History**

注:以前版本的页码可能与当前版本的页码不同

| С | hanges from Revision * (September 2021) to Revision A (December 2021) | Page |

|---|-----------------------------------------------------------------------|------|

| • | Added clarifying text to note 1 in Pin Functions table                | 3    |

| • | Changed 0.9 V to 0.91 V in second paragraph of #9.1 section           | 18   |

| • | Changed 0.9 V to 0.91 V in first paragraph of #9.4.1.1 section        | 22   |

|   | 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3                               |      |

Submit Document Feedback

# **5 Device Comparison Table**

| DEVICE      | RAD TOLERANCE | GBWP<br>(MHz) | I <sub>Q</sub><br>(mA) | HD2 / HD3 (dBc)<br>2 V <sub>PP</sub> AT 10 MHz | INPUT NOISE<br>(nV/ √ Hz) | RAIL-TO-RAIL |

|-------------|---------------|---------------|------------------------|------------------------------------------------|---------------------------|--------------|

| LMH5485-SP  | 100 kRad TID  | 850           | 10.1                   | - <b>79 / - 97</b>                             | 2.4                       | NRI/Out      |

| LMH5485-SEP | 30 kRad TID   | 850           | 10.1                   | - 90 / - 102                                   | 2.4                       | NRI/Out      |

| THS4513-SP  | 150 kRad TID  | 3000          | 37.7                   | - 106 / - 108                                  | 2.2                       | No           |

| LMH5401-SP  | 100 kRad TID  | 6500          | 60                     | - 99 / - 100                                   | 1.25                      | No           |

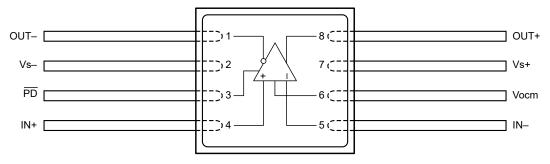

# **6 Pin Configuration and Functions**

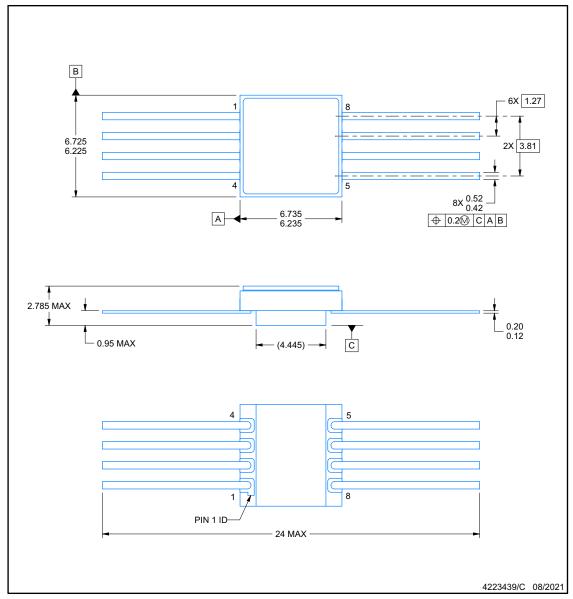

图 6-1. Top View HKX Package 8-Pin CFP

表 6-1. Pin Functions

| PIN   |     |                     |                                                                                  |

|-------|-----|---------------------|----------------------------------------------------------------------------------|

| NAME  | NO. | TYPE <sup>(1)</sup> | DESCRIPTION                                                                      |

| IN+   | 4   | I                   | Noninverting (positive) amplifier input                                          |

| IN -  | 5   | Į.                  | Inverting (negative) amplifier input                                             |

| OUT+  | 8   | 0                   | Noninverted (positive) amplifier output                                          |

| OUT - | 1   | 0                   | Inverted (negative) amplifier output                                             |

| PD    | 3   | I                   | Power down. PD = logic low = power off mode; PD = logic high = normal operation. |

| Vocm  | 6   | I                   | Common-mode voltage input                                                        |

| Vs+   | 7   | Р                   | Positive power-supply input                                                      |

| Vs -  | 2   | Р                   | Negative power-supply input                                                      |

(1) I = input, O = output, P = power

# 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|             |                                       | MIN                     | MAX                             | UNIT          |

|-------------|---------------------------------------|-------------------------|---------------------------------|---------------|

|             | Supply voltage, (Vs+) - Vs -          |                         | 5.25                            | V             |

| Voltage     | Input-output voltage range            | (Vs - ) - 0.5           | (Vs+) + 0.5                     | V             |

|             | Differential input voltage            |                         | ±1                              | V             |

|             | Continuous input current              |                         | ±20                             | mA            |

| Current     | Continuous output current             |                         | ±80                             | mA            |

|             | Continuous power dissipation          | See Thermal Information | on table and <i>The</i> section | rmal Analysis |

|             | Maximum junction temperature          |                         | 150                             | °C            |

| Temperature | Operating free-air temperature range  | - 55                    | 125                             | °C            |

|             | Storage temperature, T <sub>stg</sub> | - 65                    | 150                             | °C            |

<sup>1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute maximum ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If briefly operating outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not sustain damage, but it may not be fully functional. Operating the device in this manner may affect device reliability, functionality, performance, and shorten the device lifetime.

### 7.2 ESD Ratings

|                                              |                                                                   |                                                                       | VALUE | UNIT |

|----------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------|-------|------|

| V <sub>(Fob)</sub>   Flectrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | TBD                                                                   | V     |      |

|                                              | Electrostatic discharge                                           | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | TBD   | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                | 0 1 0 1               |      |     |     |      |

|----------------|-----------------------|------|-----|-----|------|

|                |                       | MIN  | NOM | MAX | UNIT |

| Vs+            | Single-supply voltage | 2.7  | 5   | 5.1 | V    |

| T <sub>A</sub> | Ambient temperature   | - 55 | 25  | 125 | °C   |

### 7.4 Thermal Information

|                        |                                              | LMH5485-SP |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC(1)                            | HKX (CFP)  | UNIT |

|                        |                                              | 8 PINS     |      |

| R <sub>0</sub> JA      | Junction-to-ambient thermal resistance       | 145.7      | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 67.6       | °C/W |

| R <sub>0</sub> JB      | Junction-to-board thermal resistance         | 128.1      | °C/W |

| ψJT                    | Junction-to-top characterization parameter   | 61.1       | °C/W |

| ψ <sub>ЈВ</sub>        | Junction-to-board characterization parameter | 122.1      | °C/W |

| R <sub>θ</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 55.8       | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

Submit Document Feedback

# 7.5 Electrical Characteristics: $V_{S+} - V_{S-} = 5 \text{ V}$

The specifications shown below correspond to the respectively identified subgroup temperature (see  $\dagger$  7.7), unless otherwise noted. VOCM = open (defaults midsupply),  $V_{OUT}$  = 2  $V_{PP}$ , Rf = 402  $\Omega$ , Rload = 499  $\Omega$ , 50- $\Omega$  input match, G = 2 V/V, single-ended input, differential output, and  $\overline{PD}$  = +Vs, unless otherwise noted. See  $\underline{\mathbb{R}}$  8-1 for an AC-coupled gain of a 2-V/V test circuit, and  $\underline{\mathbb{R}}$  8-3 for a DC-coupled gain of a 2-V/V test circuit.

|                 | PARAMETER                                 | TEST CONE                                          | DITIONS                   | SUBGROUP <sup>(1)</sup> | MIN               | TYP              | MAX  | UNIT        |

|-----------------|-------------------------------------------|----------------------------------------------------|---------------------------|-------------------------|-------------------|------------------|------|-------------|

| AC PEF          | RFORMANCE                                 |                                                    |                           |                         |                   |                  |      |             |

|                 | Small-signal bandwidth                    | Vout = 100 mV <sub>PP</sub> , 0                    | G = 1                     |                         |                   | 530              |      | MHz         |

|                 | Small-signal bandwidth                    | Vout = 100 mV <sub>PP</sub> , 0                    | G = 2                     |                         |                   | 490              |      | MHz         |

|                 | Small-signal bandwidth                    | Vout = 100 mV <sub>PP</sub> , 0                    | G = 5                     |                         |                   | 240              |      | MHz         |

|                 | Small-signal bandwidth                    | Vout = 100 mV <sub>PP</sub> , 0                    | G = 10                    |                         |                   | 125              |      | MHz         |

| GBWP            | Gain-bandwidth product                    | Vout = 100 mV <sub>PP</sub> , 0                    | G = 20                    |                         |                   | 850              |      | MHz         |

|                 | Large-signal bandwidth                    | Vout = 2 V <sub>PP</sub>                           |                           |                         |                   | 315              |      | MHz         |

|                 | Bandwidth for 0.1-dB flatness             | Vout = 2 V <sub>PP</sub>                           |                           |                         |                   | 50               |      | MHz         |

|                 | Slew rate <sup>(2)</sup>                  | Vout = 2-V <sub>PP</sub> , FPB                     | N                         |                         |                   | 1400             |      | V/µs        |

|                 | Rise/fall time                            | Vout = 2-V step, in                                | out $\leq$ 0.5 ns $t_{r}$ |                         |                   | 1.4              |      | ns          |

|                 | Settling time                             | Vout = 2-V step,                                   | To 1%                     |                         |                   | 5.4              |      | ns          |

|                 | Setting time                              | t <sub>r</sub> = 2 ns                              | To 0.1%                   |                         |                   | 10               |      | ns          |

|                 | Overshoot and undershoot                  | Vout = 2-V step, in                                | out $\leq$ 0.3 ns $t_r$   |                         |                   | 24%              |      |             |

|                 | 400 1:11-1:                               | Vant. O.V                                          | HD2                       |                         |                   | - 111            |      | dBc         |

|                 | 100-kHz harmonic distortion               | Vout = 2 V <sub>PP</sub>                           | HD3                       |                         |                   | - 149            |      | dBc         |

|                 |                                           |                                                    | HD2                       |                         |                   | - 79             |      | dBc         |

|                 | 10-MHz harmonic distortion                | Vout = 2 V <sub>PP</sub>                           | HD3                       |                         |                   | - 97             |      | dBc         |

|                 | 2nd-order intermodulation distortion      | f = 10 MHz, 100-kH                                 |                           |                         |                   | - 90             |      | dBc         |

|                 | 3rd-order intermodulation distortion      | spacing, Vout enve<br>(1 V <sub>PP</sub> per tone) | lope = 2 V <sub>PP</sub>  |                         |                   | - 85             |      | dBc         |

|                 | Input voltage noise                       | f > 100 kHz                                        |                           |                         |                   | 2.4              |      | nV/ √<br>Hz |

|                 | Input current noise                       | f > 1 MHz                                          |                           |                         |                   | 1.9              |      | pA/ √<br>Hz |

|                 | Overdrive recovery time                   | 2x output overdrive polarity                       | , either                  |                         |                   | 20               |      | ns          |

|                 | Closed-loop output impedance              | f = 10 MHz (differen                               | ntial)                    |                         | -                 | 0.1              |      | Ω           |

| DC PEF          | RFORMANCE                                 |                                                    |                           |                         |                   |                  |      |             |

| A <sub>OL</sub> | Open-loop voltage gain                    |                                                    |                           | [1, 2, 3]               | 97                | 119              |      | dB          |

|                 | Input-referred offset voltage             |                                                    |                           | [1, 2, 3]               | - 900             | ±100             | 900  | μV          |

|                 | Input offset voltage drift <sup>(3)</sup> |                                                    |                           |                         | - 2.5             | ±0.5             | 2.5  | μV/°C       |

|                 | Input bias current                        | Positive out of node                               | 9                         | [1, 2, 3]               | 1.7               | 10               | 15   | μA          |

|                 | Input bias current drift <sup>(3)</sup>   |                                                    |                           |                         |                   | 6                | 15   | nA/°C       |

|                 | Input offset current                      |                                                    |                           | [1, 2, 3]               | - 650             | ±150             | 650  | nA          |

|                 | Input offset current drift <sup>(3)</sup> |                                                    |                           |                         | - 1.5             | ±0.3             | 1.5  | nA/°C       |

| INPUT           | 1                                         | ı                                                  |                           | 1                       |                   |                  |      |             |

|                 | Common-mode input low                     | < 3-dB degradation from midsupply                  | in CMRR                   | [1, 2, 3]               |                   | (Vs - ) -<br>0.2 | Vs - | V           |

|                 | Common-mode input high                    | < 3-dB degradation from midsupply                  | in CMRR                   | [1, 2, 3]               | (Vs+) -<br>1.3 (V | /s+) - 1.2       |      | V           |

|                 | Common-mode rejection ratio               | Input pins at midsu                                |                           | [1, 2, 3]               | 82                | 100              |      | dB          |

# 7.5 Electrical Characteristics: $V_{S+} - V_{S-} = 5 V$ (continued)

The specifications shown below correspond to the respectively identified subgroup temperature (see # 7.7), unless otherwise noted. VOCM = open (defaults midsupply),  $V_{OUT}$  = 2  $V_{PP}$ , Rf = 402  $\Omega$ , Rload = 499  $\Omega$ , 50- $\Omega$  input match, G = 2 V/V, single-ended input, differential output, and PD = +Vs, unless otherwise noted. See 图 8-1 for an AC-coupled gain of a 2-V/V test circuit, and <a>8-3</a> for a DC-coupled gain of a 2-V/V test circuit.

| PARAMETER                         | TEST CONDITIONS         | SUBGROUP <sup>(1)</sup> | MIN | TYP         | MAX | UNIT        |

|-----------------------------------|-------------------------|-------------------------|-----|-------------|-----|-------------|

| Input impedance differential mode | Input pins at midsupply |                         |     | 110    1.25 |     | kΩ   <br>pF |

Submit Document Feedback

# 7.5 Electrical Characteristics: $V_{S+} - V_{S-} = 5 \text{ V}$ (continued)

The specifications shown below correspond to the respectively identified subgroup temperature (see  $\dagger$  7.7), unless otherwise noted. VOCM = open (defaults midsupply),  $V_{OUT}$  = 2  $V_{PP}$ , Rf = 402  $\Omega$ , Rload = 499  $\Omega$ , 50- $\Omega$  input match, G = 2 V/V, single-ended input, differential output, and  $\overline{PD}$  = +Vs, unless otherwise noted. See  $\underline{\mathbb{R}}$  8-1 for an AC-coupled gain of a 2-V/V test circuit, and  $\underline{\mathbb{R}}$  8-3 for a DC-coupled gain of a 2-V/V test circuit.

|        | PARAMETER                                           | TEST CONDITIONS                                    | SUBGROUP <sup>(1)</sup> | MIN              | TYP              | MAX               | UNIT        |

|--------|-----------------------------------------------------|----------------------------------------------------|-------------------------|------------------|------------------|-------------------|-------------|

| OUTPU  | Т                                                   |                                                    |                         |                  |                  |                   |             |

|        | Output voltage low                                  |                                                    | [1, 2, 3]               |                  | (Vs - ) +<br>0.2 | (Vs - ) +<br>0.25 | V           |

|        | Output voltage high                                 |                                                    | [1, 2, 3]               | (Vs+) -<br>0.25  | (Vs+) -<br>0.2   |                   | V           |

|        | Output current drive                                |                                                    | [1, 2, 3]               | ±75              | ±100             |                   | mA          |

| POWER  | SUPPLY                                              |                                                    |                         |                  |                  |                   |             |

|        | Specified operating voltage                         |                                                    | [1, 2, 3]               | 2.7              | 5                | 5.1               | V           |

|        | Quiescent operating current                         |                                                    | [1, 2, 3]               | 9.2              | 10.1             | 11                | mA          |

| ±PSRR  | Power-supply rejection ratio                        | Either supply pin to differential Vout             | [1, 2, 3]               | 82               | 100              |                   | dB          |

| POWER  | DOWN                                                |                                                    |                         |                  |                  |                   |             |

|        | Enable voltage threshold                            |                                                    | [1, 2, 3]               | (Vs - ) +<br>1.7 |                  |                   | V           |

|        | Disable voltage threshold                           |                                                    | [1, 2, 3]               |                  |                  | (Vs - ) +<br>0.7  | V           |

|        | Disable pin bias current                            | <u>PD</u> = Vs - → Vs+                             | [1, 2, 3]               |                  | 20               | 50                | nA          |

|        | 5                                                   | <del>PD</del> = (Vs - ) + 0.7 V                    | [1, 2, 3]               | ,                | 6                | 30                | μA          |

|        | Power-down quiescent current                        | PD = Vs -                                          | [1, 2, 3]               |                  | 2                | 8                 | μA          |

|        | Turnon-time delay                                   | Time from PD = low to<br>Vout = 90% of final value |                         |                  | 100              |                   | ns          |

|        | Turnoff time delay                                  | Time from PD = low to<br>Vout = 10% of final value |                         |                  | 60               |                   | ns          |

| OUTPU' | T COMMON-MODE VOLTAGE O                             | CONTROL <sup>(4)</sup>                             |                         |                  |                  |                   |             |

|        | Small-signal bandwidth                              | Vocm = 100 mV <sub>PP</sub>                        |                         |                  | 150              |                   | MHz         |

|        | Slew rate <sup>(2)</sup>                            | Vocm = 2-V step                                    |                         |                  | 400              |                   | V/µs        |

|        | Gain                                                |                                                    | [1, 2, 3]               | 0.975            | 0.982            | 0.995             | V/V         |

|        | Input bias current                                  | Considered positive out of node                    | [1, 2, 3]               | - 0.8            | 0.1              | 0.8               | μΑ          |

|        | Input impedance                                     | Vocm input driven to midsupply                     |                         |                  | 47    1.2        |                   | kΩ   <br>pF |

|        | Default voltage offset from midsupply               | Vocm pin open                                      | [1, 2, 3]               | - 45             | ±8               | 45                | mV          |

| CM Vos | Common-mode offset voltage                          | Vocm input driven to midsupply                     | [1, 2, 3]               | - 8              | ±2               | 8                 | mV          |

|        | CM V <sub>OS</sub> drift <sup>(3)</sup>             | Vocm input driven to midsupply                     |                         | - 20             | ±4               | +20               | mV/°C       |

|        | Common-mode loop supply headroom to negative supply | < ±15-mV shift from midsupply CM Vos               | [1, 2, 3]               | 0.94             |                  |                   | V           |

|        | Common-mode loop supply headroom to positive supply | < ±15-mV shift from midsupply CM Vos               | [1, 2, 3]               | 1.2              |                  |                   | V           |

<sup>(1)</sup> For subgroup definitions, please see  $\ddagger$  7.7

<sup>(2)</sup> This slew rate is the average of the rising and falling time estimated from the large-signal bandwidth as: (V<sub>P</sub> / √2) · 2 π · f - 3dB.

<sup>(3)</sup> Input offset voltage drift, input bias current drift, input offset current drift, and Vocm drift are average values calculated by taking data at the at the maximum-range ambient-temperature end-points, computing the difference, and dividing by the temperature range.

<sup>(4)</sup> Specifications are from the input Vocm pin to the differential output average voltage.

# 7.6 Electrical Characteristics: $V_{S+} - V_{S-} = 3 \text{ V}$

The specifications shown below correspond to the respectively identified subgroup temperature (see  $\ddagger$  7.7), unless otherwise noted. Vocm = open (defaults midsupply),  $V_{OUT}$  = 2  $V_{PP}$ , Rf = 402  $\Omega$ , Rload = 499  $\Omega$ , 50- $\Omega$  input match, G = 2 V/V, single-ended input, differential output, and  $\overline{PD}$  = +Vs, unless otherwise noted. See  $\underline{\boxtimes}$  8-1 for an AC-coupled gain of a 2-V/V test circuit, and  $\underline{\boxtimes}$  8-3 for a DC-coupled gain of a 2-V/V test circuit.

|                 | PARAMETER                                 | TEST CONI                                          | DITIONS                     | SUBGROUP <sup>(1)</sup> | MIN               | TYP              | MAX  | UNIT        |

|-----------------|-------------------------------------------|----------------------------------------------------|-----------------------------|-------------------------|-------------------|------------------|------|-------------|

| AC PEF          | RFORMANCE                                 |                                                    |                             |                         |                   |                  |      |             |

|                 |                                           | Vout = 100 mV <sub>PP</sub> ,                      | G = 1                       |                         |                   | 510              |      | MHz         |

|                 | Small-signal bandwidth                    | Vout = 100 mV <sub>PP</sub> ,                      | G = 2                       |                         |                   | 475              |      | MHz         |

|                 |                                           | Vout = 100 mV <sub>PP</sub> ,                      | G = 5                       |                         |                   | 240              |      | MHz         |

| GBWP            | Gain-bandwidth product                    | Vout = 100 mV <sub>PP</sub> ,                      | G = 20                      |                         |                   | 850              |      | MHz         |

|                 | Large-signal bandwidth                    | Vout = 2 V <sub>PP</sub>                           |                             |                         |                   | 300              |      | MHz         |

|                 | Bandwidth for 0.1-dB flatness             | Vout = 2 V <sub>PP</sub>                           |                             |                         |                   | 50               |      | MHz         |

|                 | Slew rate <sup>(2)</sup>                  | Vout = 2-V step, F                                 | PBW                         |                         |                   | 1200             |      | V/µs        |

|                 | Rise/fall time                            | Vout = 2-V step, in                                | put ≤ 0.5 ns t <sub>r</sub> |                         |                   | 1.6              |      | ns          |

|                 | 0 - 411: 4:                               | Vout = 2-V step,                                   | To 1%                       |                         |                   | 5                |      | ns          |

|                 | Settling time                             | t <sub>r</sub> = 2 ns                              | To 0.1%                     |                         |                   | 9                |      | ns          |

|                 | Overshoot and undershoot                  | Vout = 2-V step, in                                | put ≤ 0.3 ns t <sub>r</sub> |                         |                   | 25%              |      |             |

|                 | 400 141-1                                 | Vest 2V                                            | HD2                         |                         |                   | - 111            |      | dBc         |

|                 | 100-kHz harmonic distortion               | Vout = 2 V <sub>PP</sub>                           | HD3                         |                         |                   | - 150            |      | dBc         |

|                 |                                           |                                                    | HD2                         |                         |                   | - 80             |      | dBc         |

|                 | 10-MHz harmonic distortion                | Vout = 2 V <sub>PP</sub>                           |                             |                         |                   | - 96             |      | dBc         |

|                 | 2nd-order intermodulation distortion      | f = 10 MHz, 100-kl                                 |                             |                         |                   | - 89             |      | dBc         |

|                 | 3rd-order intermodulation distortion      | spacing, Vout enve<br>(1 V <sub>PP</sub> per tone) | elope = 2 V <sub>PP</sub>   |                         |                   | - 87             |      | dBc         |

|                 | Input voltage noise                       | f > 100 kHz                                        |                             |                         |                   | 2.4              |      | nV/ √<br>Hz |

|                 | Input current noise                       | f > 1 MHz                                          |                             |                         |                   | 1.9              |      | pA/ √<br>Hz |

|                 | Overdrive recovery time                   | 2X output overdriv polarity                        | e, either                   |                         |                   | 20               |      | ns          |

|                 | Closed-loop output impedance              | f = 10 MHz (differe                                | ential)                     |                         |                   | 0.1              |      | Ω           |

| DC PEF          | RFORMANCE                                 |                                                    |                             |                         |                   |                  |      |             |

| A <sub>OL</sub> | Open-loop voltage gain                    |                                                    |                             | [1, 2, 3]               | 97                | 119              |      | dB          |

|                 | Input-referred offset voltage             |                                                    |                             | [1, 2, 3]               | - 900             | ±100             | 900  | μV          |

|                 | Input offset voltage drift(3)             |                                                    |                             |                         | - 2.5             | ±0.5             | 2.5  | μV/°C       |

|                 | Input bias current                        | Positive out of nod                                | le                          | [1, 2, 3]               | 1.7               | 9                | 15   | μA          |

|                 | Input bias current drift(3)               |                                                    |                             |                         |                   | 5                | 15   | nA/°C       |

|                 | Input offset current                      |                                                    |                             | [1, 2, 3]               | - 650             | ±150             | 650  | nA          |

|                 | Input offset current drift <sup>(3)</sup> |                                                    |                             |                         | - 1.5             | ±0.3             | 1.5  | nA/°C       |

| INPUT           |                                           | 1                                                  |                             |                         |                   |                  |      |             |

|                 | Common-mode input low                     | < 3-dB degradation from midsupply                  | n in CMRR                   | [1, 2, 3]               |                   | (Vs - ) -<br>0.2 | Vs - | V           |

|                 | Common-mode input high                    | < 3-dB degradation from midsupply                  | n in CMRR                   | [1, 2, 3]               | (Vs+) -<br>1.3 (V | s+) - 1.2        |      | V           |

|                 | Common-mode rejection ratio               | Input pins at midsu                                | upply                       | [1, 2, 3]               | 82                | 100              |      | dB          |

|                 | Input impedance differential mode         | Input pins at midsu                                | upply                       |                         | 1                 | 10    1.25       |      | kΩ   <br>pF |

Submit Document Feedback

# 7.6 Electrical Characteristics: $V_{S+} - V_{S-} = 3 \text{ V (continued)}$

The specifications shown below correspond to the respectively identified subgroup temperature (see  $\dagger$  7.7), unless otherwise noted. Vocm = open (defaults midsupply),  $V_{OUT}$  = 2  $V_{PP}$ , Rf = 402  $\Omega$ , Rload = 499  $\Omega$ , 50- $\Omega$  input match, G = 2 V/V, single-ended input, differential output, and  $\overline{PD}$  = +Vs, unless otherwise noted. See  $\underline{\mathbb{R}}$  8-1 for an AC-coupled gain of a 2-V/V test circuit, and  $\underline{\mathbb{R}}$  8-3 for a DC-coupled gain of a 2-V/V test circuit.

|        | PARAMETER                                           | TEST CONDITIONS                                    | SUBGROUP <sup>(1)</sup> | MIN              | TYP              | MAX               | UNIT        |

|--------|-----------------------------------------------------|----------------------------------------------------|-------------------------|------------------|------------------|-------------------|-------------|

| OUTPU  | Т                                                   |                                                    |                         |                  |                  |                   |             |

|        | Output voltage low                                  |                                                    | [1, 2, 3]               |                  | (Vs - ) +<br>0.2 | (Vs - ) +<br>0.25 | V           |

|        | Output voltage high                                 |                                                    | [1, 2, 3]               | (Vs+) -<br>0.25  | (Vs+) -<br>0.2   |                   | V           |

|        | Output current drive                                |                                                    | [1, 2, 3]               | ±55              | ±60              |                   | mA          |

| POWER  | SUPPLY                                              |                                                    |                         |                  |                  |                   |             |

|        | Specified operating voltage                         |                                                    | [1, 2, 3]               | 2.7              | 3                | 5.1               | V           |

|        | Quiescent operating current                         |                                                    | [1, 2, 3]               | 9                | 9.7              | 10.6              | mA          |

| ±PSRR  | Power-supply rejection ratio                        | Either supply pin to differential Vout             | [1, 2, 3]               | 82               | 100              |                   | dB          |

| POWER  | DOWN                                                |                                                    |                         |                  |                  |                   |             |

|        | Enable voltage threshold                            |                                                    | [1, 2, 3]               | (Vs - ) +<br>1.7 |                  |                   | V           |

|        | Disable voltage threshold                           |                                                    | [1, 2, 3]               |                  |                  | (Vs - ) +<br>0.7  | V           |

|        | Disable pin bias current                            | PD = Vs - → Vs+                                    | [1, 2, 3]               |                  | 20               | 50                | nA          |

|        | Davis davis suita and sument                        | <del>PD</del> = (Vs - ) + 0.7 V                    | [1, 2, 3]               |                  | 2                | 30                | μΑ          |

|        | Power-down quiescent current                        | PD = Vs -                                          | [1, 2, 3]               |                  | 1                | 8                 | μA          |

|        | Turnon-time delay                                   | Time from PD = low to<br>Vout = 90% of final value |                         |                  | 100              |                   | ns          |

|        | Turnoff time delay                                  | Time from PD = low to<br>Vout = 10% of final value |                         |                  | 60               |                   | ns          |

| OUTPU  | T COMMON-MODE VOLTAGE O                             | CONTROL <sup>(4)</sup>                             |                         |                  |                  |                   |             |

|        | Small-signal bandwidth                              | Vocm = 100 mV <sub>PP</sub>                        |                         |                  | 140              |                   | MHz         |

|        | Slew rate <sup>(2)</sup>                            | Vocm = 1-V step                                    |                         |                  | 350              |                   | V/µs        |

|        | Gain                                                |                                                    | [1, 2, 3]               | 0.975            | 0.987            | 0.990             | V/V         |

|        | Input bias current                                  | Considered positive out of node                    | [1, 2, 3]               | - 0.7            | 0.1              | 0.7               | μΑ          |

|        | Input impedance                                     | Vocm input driven to midsupply                     |                         |                  | 47    1.2        |                   | kΩ   <br>pF |

|        | Default voltage offset from midsupply               | Vocm pin open                                      | [1, 2, 3]               | - 45             | ±10              | 45                | mV          |

| CM Vos | Common-mode offset voltage                          | Vocm input driven to midsupply                     | [1, 2, 3]               | - 8              | ±2               | 8                 | mV          |

|        | CM V <sub>OS</sub> drift <sup>(3)</sup>             | Vocm input driven to midsupply                     |                         | - 20             | ±4               | 20                | mV/°C       |

|        | Common-mode loop supply headroom to negative supply | < ±15-mV shift from midsupply CM Vos               | [1, 2, 3]               | 0.94             |                  |                   | V           |

|        | Common-mode loop supply headroom to positive supply | < ±15-mV shift from midsupply CM Vos               | [1, 2, 3]               | 1.2              |                  |                   | V           |

<sup>(1)</sup> For subgroup definitions, please see  $\ddagger$  7.7

<sup>2)</sup> This slew rate is the average of the rising and falling time estimated from the large-signal bandwidth as: (V<sub>P</sub> / √2) · 2 π · f - 3db.

<sup>(3)</sup> Input offset voltage drift, input bias current drift, input offset current drift, and Vocm drift are average values calculated by taking data at the at the maximum-range ambient-temperature end-points, computing the difference, and dividing by the temperature range.

Maximum drift set by distribution of a large sampling of devices. Drift is not specified by test or QA sample test.

<sup>4)</sup> Specifications are from input Vocm pin to differential output average voltage.

# 7.7 Quality Conformance Inspection

| SUBGROUP | DESCRIPTION         | TEMPERATURE (°C) |

|----------|---------------------|------------------|

| 1        | Static tests at     | 25               |

| 2        | Static tests at     | 125              |

| 3        | Static tests at     | - 55             |

| 4        | Dynamic tests at    | 25               |

| 5        | Dynamic tests at    | 125              |

| 6        | Dynamic tests at    | - 55             |

| 7        | Functional tests at | 25               |

| 8A       | Functional tests at | 125              |

| 8B       | Functional tests at | - 55             |

Submit Document Feedback

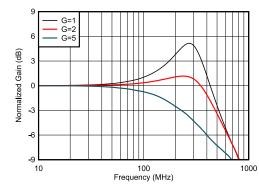

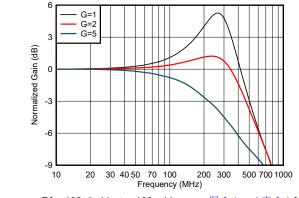

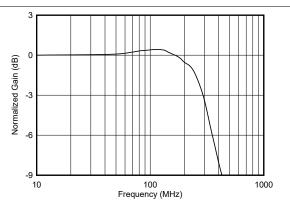

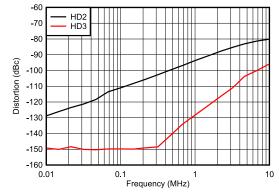

# 7.8 Typical Characteristics: 5 V Single Supply

at Vs+ = 5 V, Vs - = GND, R<sub>F</sub>= 402  $\Omega$ , Vocm is open, 50  $\Omega$  single-ended input to differential output, gain = 2 V/V, Rload = 500  $\Omega$ , and T<sub>A</sub>  $\approx$  25°C (unless otherwise noted)

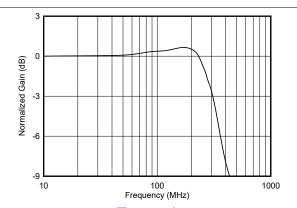

Vo = 100 mVpp, see  ${\ 8\text{-}1}$  and 表 9-1 for resistor values

图 7-1. Small-Signal Frequency Response vs Gain

$V_O$  = 2 Vpp, see  $\boxtimes$  8-1 and  $\gtrless$  9-1 for resistor values

图 7-2. Large-Signal Frequency Response

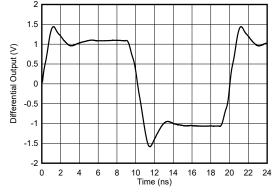

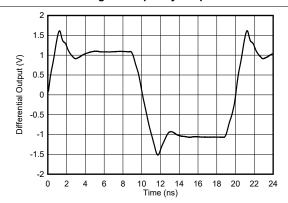

50 MHz input, 0.5-ns input edge rate, single-ended to differential output, split supply, DC-coupled, see 图 8-3

图 7-3. Large-Signal Step Response

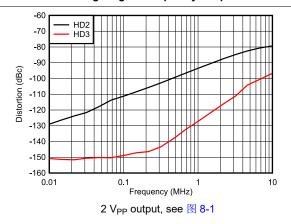

图 7-4. Harmonic Distortion Over Frequency

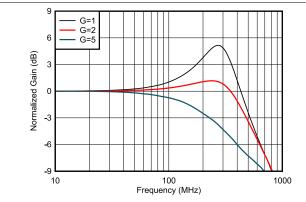

# 7.9 Typical Characteristics: 3 V Single Supply

at Vs+ = 3 V, Vs - = GND, Vocm is open, 50  $\,^{\Omega}$  single-ended input to differential output, gain = 2 V/V, Rload = 500  $\,^{\Omega}$ , and T<sub>A</sub>  $\,^{\infty}$  25°C (unless otherwise noted)

Rf = 402  $\,^{\Omega}$  , Vout = 100 mV<sub>PP</sub>, see  $\,^{\Sigma}$  8-1 and  $\,^{\Xi}$  9-1 for resistor values

#### 图 7-5. Small-Signal Frequency Response vs Gain

50 MHz input, 0.5-ns input edge rate, single-ended input to differential output, split supply, DC coupled, see 图 8-3

图 7-7. Large-Signal Step Response

Rf = 402  $\,^{\Omega}$  , Vout = 2 V<sub>PP</sub>, see  $\,^{\Sigma}$  8-1 and  $\,^{\Xi}$  9-1 for resistor values

#### 图 7-6. Large-Signal Frequency Response

2  $V_{PP}$  output, see 8-1 with  $V_{S+} = 3$  V,  $V_{OCM} = 1.5$  V

图 7-8. Harmonic Distortion Over Frequency

Submit Document Feedback

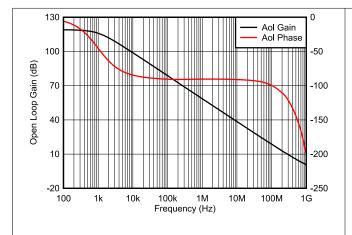

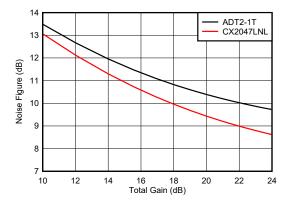

### 7.10 Typical Characteristics: 3 V to 5 V Supply Range

at Vs+ = 3 V and 5 V, Vs - = GND, Vocm is open, 50 Ω single-ended input to differential output, gain = 2 V/V, Rload = 500  $\Omega$  , and T<sub>A</sub>  $\approx$  25°C (unless otherwise noted)

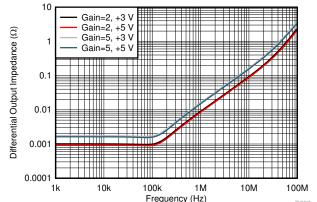

Single-ended input to differential output, simulated differential output impedance, see 图 8-1

图 7-9. Main Amplifier Differential Open-Loop Gain and Phase vs Frequency

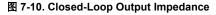

图 7-11. Input Spot Noise Over Frequency

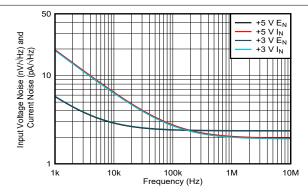

Single-ended input to differential output, gain of 2 (see 8-1), simulated with 1% resistor, worst-case mismatch

#### 图 7-12. Output Balance Error Over Frequency

Frequency (Hz)

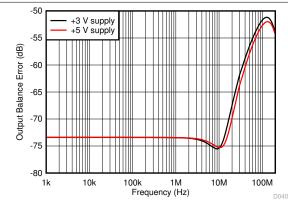

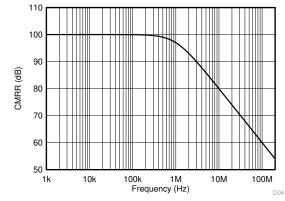

图 7-13. CMRR Over Frequency

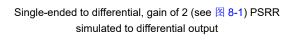

图 7-14. PSRR Over Frequency

+5 V +Vs

+3 V -Vs

100M

85

80 75

70

60

55 50

45

40

10k

PSRR (dB) 65

# 7.10 Typical Characteristics: 3 V to 5 V Supply Range (continued)

at Vs+ = 3 V and 5 V, Vs - = GND, Vocm is open, 50  $\Omega$  single-ended input to differential output, gain = 2 V/V, Rload = 500  $\Omega$ , and T<sub>A</sub>  $\approx$  25°C (unless otherwise noted)

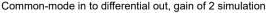

Vocm input either driven to mid-supply by low impedance source, or allowed to float and default to mid-supply

图 7-15. Output Common-Mode Noise

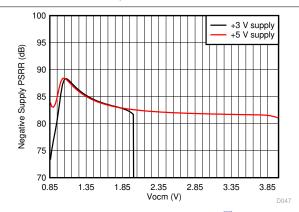

Single-ended to differential gain of 2 (see <a>\bar{8}</a> 8-1), PSRR for negative supply to differential output (1-kHz simulation)

图 7-17. - PSRR vs Vocm Approaching Vs -

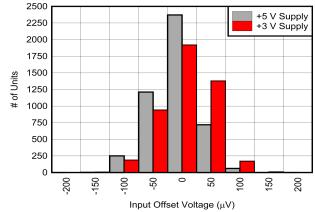

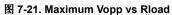

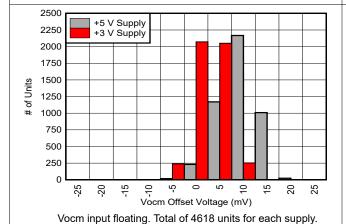

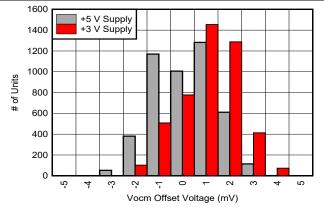

Total of 4618 units for each supply. For Vs = 5 V:  $\,\mu$  = -35.1  $\,\mu$  V,  $\,\sigma$  = 38.9  $\,\mu$  V

图 7-19. Input Offset Voltage

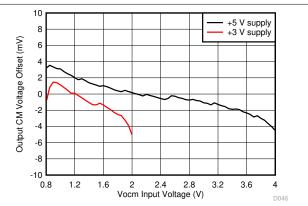

Average Vocm output offset of 37 units, Standard deviation < 2.5 mV, see 8 8-3

图 7-16. Vocm Offset vs Vocm Setting

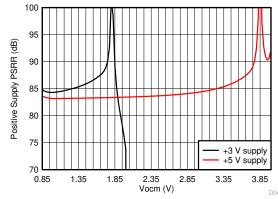

Single-ended to differential gain of 2 (see 图 8-1), PSRR for positive supply to differential output (1-kHz simulation)

图 7-18. +PSRR vs Vocm Approaching Vs+

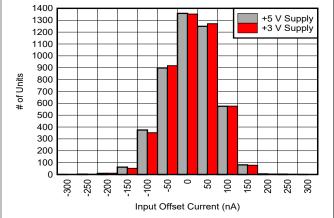

Total of 4618 units for each supply. For Vs = 5 V:  $\,\mu$  = 16.7 nA,  $\,\sigma$  = 62.3 nA

图 7-20. Input Offset Current

Submit Document Feedback

# 7.10 Typical Characteristics: 3 V to 5 V Supply Range (continued)

at Vs+ = 3 V and 5 V, Vs - = GND, Vocm is open, 50  $\Omega$  single-ended input to differential output, gain = 2 V/V, Rload = 500  $\Omega$ , and T<sub>A</sub>  $\approx$  25°C (unless otherwise noted)

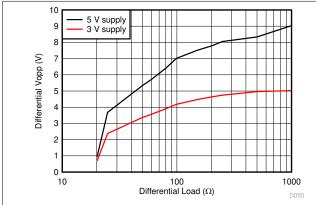

Maximum differential output swing, Vocm at mid-supply

For Vs = 5 V:  $\mu$  = 6.8 mV,  $\sigma$  = 3.9 mV **T-23. Common-Mode Output Offset from Vs+ / 2 Default Value**

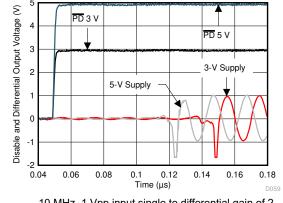

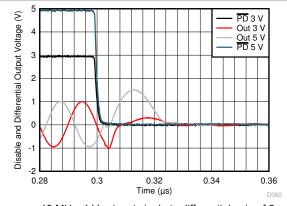

图 7-25. PD Turn On Waveform

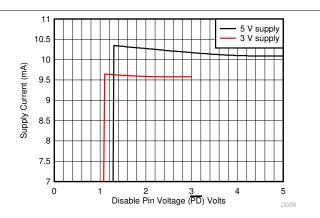

图 7-22. Supply Current vs PD Voltage

Total of 4618 units for each supply. For Vs = 5 V:  $\,\mu$  = 0.3 mV,  $\,\sigma$  = 1.3 mV

#### 图 7-24. Common-Mode Output Offset from Driven Vocm

10 MHz, 1 V<sub>PP</sub> input single to differential gain of 2, see <a>§</a> 8-3

图 7-26. PD Turn Off Waveform

### **8 Parameter Measurement Information**

## **8.1 Example Characterization Circuits**

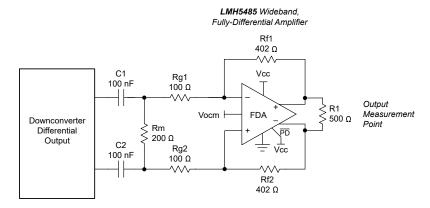

The LMH5485-SP offers the advantages of a fully differential amplifier (FDA) design, with the trimmed input offset voltage of a precision op amp. The FDA is an extremely flexible device that provides a purely differential output signal centered on a settable output common-mode level. The primary options revolve around the choices of single-ended or differential inputs, AC-coupled or DC-coupled signal paths, gain targets, and resistor Value selections. Differential sources can certainly be supported and are often simpler to both implement and analyze.

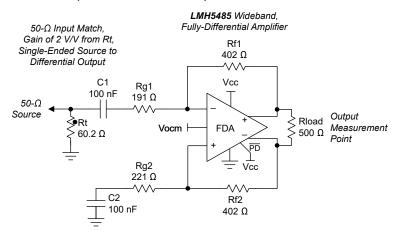

Because most lab equipment is single-ended, the characterization circuits typically operate with a single-ended, matched, 50  $\Omega$  input termination to a differential output at the FDA output pins. That output is then translated back to single-ended through a variety of baluns (or transformers) depending on the test and frequency range. DC-coupled, step-response testing uses two 50  $\Omega$  scope inputs with trace math. The starting point for any single-ended-to-differential, AC-coupled characterization plot is shown in  $\mathbb{Z}$  8-1.

图 8-1. AC-Coupled, Single-Ended Source to a Differential Gain of a 2 V/V Test Circuit

8-1 shows how most characterization plots fix the  $R_f$  ( $R_{f1}$  =  $R_{f2}$ ) value at 402  $\Omega$ . This element value is completely flexible in application, but the 402  $\Omega$  provides a good compromise for the parasitic issues linked to this value, specifically:

- Added output loading. The FDA appears like an inverting op amp design with both feedback resistors as an added load across the outputs (approximate total differential load in  $\boxtimes$  8-1 is 500  $\Omega$  || 804  $\Omega$  = 308  $\Omega$ ).

- Noise contributions because of the resistor values. The resistors contribute both a 4kTR term and provide gain for the input current noise.

- Parasitic feedback pole at the input summing nodes. This pole created by the feedback R value and the 1.25-pF 0.9-pF differential input capacitance (as well as any board layout parasitic) introduces a zero in the noise gain, decreasing the phase margin in most situations. This effect must be managed for best frequency response flatness or step response overshoot. The 402  $\,^{\Omega}$  value selected does degrade the phase margin slightly over a lower value, but does not decrease the loading significantly from the nominal 500  $\,^{\Omega}$  value across the output pins.

Submit Document Feedback

**ADVANCE INFORMATION**

The frequency domain characterization curves start with the selections of 8-1. Then, various elements are modified to show their impact over a range of design targets, specifically:

- Gain setting is changed by adjusting R<sub>t</sub> and the 2  $^-$  R<sub>g</sub> elements (holding a 50  $^{\Omega}$  input match).

- · Output loading, including both resistive and capacitive load testing.

- Power-supply settings. Most often, a single +5 V test uses a ±2.5 V supply, and a +3 V test uses ±1.5 V supplies.

- The disable control pin is tied to Vs+ for any active channel test.

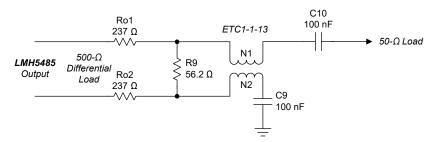

Because most network and spectrum analyzers are a single-ended input, the output network on the LMH5485-SP characterization tests typically show the desired load connected through a balun to a single-ended,  $50^{\circ}\Omega$  load, while presenting a  $50^{\circ}\Omega$  source from the balun output back into the balun. For instance, 8 8-2 shows a wideband MA/Com balun used for 8 8-1. This network shows a  $500^{\circ}\Omega$  differential load to the LMH5485-SP, but an AC-coupled,  $50^{\circ}\Omega$  source to the network analyzer. Distortion testing typically uses a lower-frequency, DC-isolated balun (such as the TT1-6T) that is rotated  $90^{\circ}$  from the wider band interface of 8 8-2.

图 8-2. Example 500  $\Omega$  Load to a Single-Ended, Doubly-Terminated, AC-Coupled, 50  $\Omega$  Interface

This approach allows a higher differential load, but with a wideband 50  $\,^{\Omega}$  output match at the cost of considerable signal-path insertion loss. This loss is acceptable for characterization, and is normalized out to show the characterization curves.

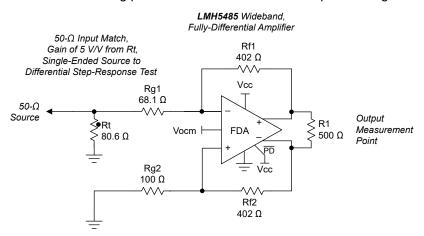

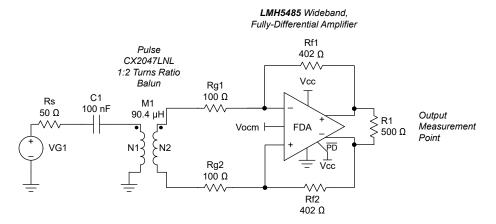

⊠ 8-3 shows the circuit used as a starting point for time-domain or DC-coupled testing.

图 8-3. DC-Coupled, Single-Ended-to-Differential, Basic Test Circuit Set for a Gain of 5 V/V

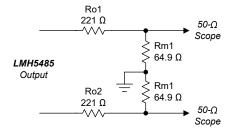

In this case, the input is DC-coupled, showing a 50  $\,^{\Omega}$  input match to the source, gain of 5 V/V to a differential output, again driving a nominal 500  $\,^{\Omega}$  load. Using a single supply, the Vocm control input can either be floated (defaulting to mid-supply) or be driven within the allowed range for the Vocm loop (see the headroom limits on Vocm in the *Electrical Characteristics: VS+ -VS = 5 V* tables). To use this circuit for step-response measurements, load each of the two outputs with a 250  $\,^{\Omega}$  network, translating to a 50  $\,^{\Omega}$  source impedance driving into two 50  $\,^{\Omega}$  scope inputs. Then, difference the scope inputs to generate the step responses.  $\,^{\square}$  8-4 shows the output interface circuit. This grounded interface pulls a DC load current from the output Vocm voltage for single-supply operation. Running this test with balanced bipolar power supplies eliminates this DC load current and gives similar waveform results.

图 8-4. Example 500  $\Omega$  Load to Differential, Doubly-Terminated, DC-Coupled 50  $\Omega$  Scope Interface

## 9 Detailed Description

#### 9.1 Overview

The LMH5485-SP is a voltage-feedback (VFA) based, fully-differential amplifier (FDA) offering greater than 490 MHz, small-signal bandwidth at a gain of 2 V/V with trimmed supply current and input offset voltage. The core differential amplifier is a slightly decompensated voltage-feedback design with a high slew-rate, precision input stage. This design gives the 490 495 MHz gain of 2 V/V small-signal bandwidth shown in the characterization curves, with a 1400 1300 V/ $\mu$ s slew rate, yielding approximately a 315 295 MHz, 2 V<sub>PP</sub>, large-signal bandwidth in the same circuit configuration.

The outputs offer near rail-to-rail output swing (0.2 V headroom to either supply), while the device inputs are negative rail inputs with approximately 1.2 V of headroom required to the positive supply. 8-3 shows how this negative rail input directly supports a bipolar input around ground in a DC-coupled, single-supply design. Similar to all FDA devices, the output average voltage (common-mode) is controlled by a separate common-mode loop. The target for this output average is set by the Vocm input pin that can be either floated to default near mid-supply or driven to a desired output common-mode voltage. The Vocm range extends from a very low 0.91 V above the negative supply to 1.1 V below the positive supply, supporting a wide range of modern analog-to-digital converter (ADC) input common-mode requirements using a single 2.7 V to 5.1 V supply range for the LMH5485-SP.

A power-down pin  $(\overline{PD})$  is included. Pull the  $\overline{PD}$  pin voltage to the negative supply to turn the device off, putting the LMH5485-SP into a very-low quiescent current state. For normal operation, the  $\overline{PD}$  pin must be asserted high. When the device is disabled, remember that the signal path is still present through the passive external resistors. Input signals applied to a disabled LMH5485-SP still appear at the outputs at some level through this passive resistor path as they would for any disabled FDA device.

Submit Document Feedback

### 9.1.1 Terminology and Application Assumptions

Like all widely-used devices, numerous common terms have developed that are unique to this type of device. These terms include:

- Fully differential amplifier (FDA)—In this document, this term is restricted to devices offering what appears similar to a differential inverting op amp design element that requires an input resistor (not high-impedance input) and includes a second internal control-loop setting the output average voltage (Vocm) to a default or set point. This second loop interacts with the differential loop in some configurations.

- The desired output signal at the two output pins is a *differential* signal swinging symmetrically around a *common-mode* voltage where that is the average voltage for the two outputs.

- Single-ended to differential—always use the outputs differentially in an FDA; however, the source signal can be either a single-ended source or differential, with a variety of implementation details for either. When the FDA operation is single-ended to differential, only one of the two input resistors receives the source signal with the other input resistor connected to a DC reference (often ground) or through a capacitor to ground.

To simplify, several features in the application of the LMH5485-SP are not explicitly stated, but are necessary for correct operation. These requirements include:

- Although not always stated, make sure to tie the power disable pin to the positive supply when only an enabled channel is desired.

- Virtually all AC characterization equipment expects a 50  $\,^{\Omega}$  termination from the 50  $\,^{\Omega}$  source, and a 50  $\,^{\Omega}$  single-ended source impedance from the device outputs to the 50  $\,^{\Omega}$  sensing termination. This termination is achieved in all characterizations (often with some insertion loss), but is not necessary for most applications. Matching impedance is most often required when transmitting over longer distances. Tight layouts from a source, through the LMH5485-SP, and on to an ADC input do not require doubly-terminated lines or filter designs; the exception is if the source requires a defined termination impedance for correct operation (for example, a SAW filter source).

- External element values are normally assumed to be accurate and matched. In an FDA, match the feedback resistor values and also match the (DC and AC) impedance from the summing junctions to the source on one side and the reference or ground on the other side. Unbalancing these values introduces nonidealities in the signal path. For the signal path, imbalanced resistor ratios on the two sides create a common-mode to differential conversion. Also, mismatched Rf values and feedback ratios create some added differential output error terms from any common-mode DC, ac signal, or noise terms. Snapping to standard 1% resistor values is a typical approach and generally leads to some nominal feedback ratio mismatch. Mismatched resistors or ratios do not in themselves degrade harmonic distortion. If there is meaningful CM noise or distortion coming in, those errors are converted to a differential error through element or ratio mismatch.

### 9.2 Functional Block Diagram

### 9.3 Feature Description

#### 9.3.1 Differential I/O

The LMH5485-SP combines a core differential I/O, high-gain block with an output common-mode sense that is compared to a reference voltage and then fed back into the main amplifier block to control the average output to that reference. The differential I/O block is a classic, high open-loop gain stage with a dominant pole at approximately 900 Hz. This voltage feedback structure projects a single-pole, unity-gain AoI at 850 MHz (gain bandwidth product). The high-speed differential outputs include an internal averaging resistor network to sense the output common-mode voltage. This voltage is compared by a separate Vcm error amplifier to the voltage on the Vocm pin. If floated, this reference is at half the total supply voltage across the device using two 100-k  $\Omega$  resistors. This Vcm error amplifier transmits a correction signal into the main amplifier to force the output average voltage to meet the target voltage on the Vocm pin. The bandwidth of this error amplifier is approximately the same bandwidth as the main differential I/O amplifier.

The differential outputs are collector outputs to obtain the rail-to-rail output swing. These outputs are relatively high-impedance, open-loop sources; however, closing the loop provides a very low output impedance for load driving. No output current limit or thermal shutdown features are provided in this lower-power device. The differential inputs are PNP inputs to provide a negative-rail input range.

To operate the LMH5485-SP connect the OUT - pin to the IN+ pin through an Rf, and the OUT+ pin to the IN - pin through the same value of Rf. Bring in the inputs through additional resistors to the IN+ and IN - pins. The differential I/O op amp operates similarly to an inverting op amp structure where the source must drive the input resistor and the gain is the ratio of the feedback to the input resistor.

### 9.3.2 Power-Down Control Pin (PD)

The LMH5485-SP includes a power-down control pin,  $\overline{PD}$ . This pin must be asserted high for correct amplifier operation. The  $\overline{PD}$  pin cannot be floated because there is no internal pullup or pulldown resistor on this pin to reduce disabled power consumption. Asserting this pin low (within 0.7 V of the negative supply) puts the LMH5485-SP into a very low quiescent state (approximately 2  $\mu$ A). Switches in the default Vocm resistor string open to eliminate the fixed bias current (25  $\mu$ A) across the supply in this 200-k  $\Omega$  voltage divider to mid-supply.

Submit Document Feedback

### 9.3.2.1 Operating the Power Shutdown Feature

When the  $\overline{PD}$  pin is asserted high, close to the positive supply, the device will be in normal active mode of operation. To disable the device for reduced power consumption,  $\overline{PD}$  pin must be asserted low, close to the negative supply.  $\overline{R}$  7-22 shows the  $\overline{PD}$  pin voltage and the corresponding quiescent current drawn. For applications that require the device to only be powered on when the supplies are present, tie the  $\overline{PD}$  pin to the positive supply voltage.

The disable operation is referenced from the negative supply (normally, ground). For split-supply operation, with the negative supply below ground, a disable control voltage below ground is required to turn the LMH5485-SP off when the negative supply exceeds - 0.7 V.

For single-supply operation, a minimum of 1.7 V above the negative supply (ground, in this case) is required to assure operation. This minimum logic-high level allows for direct operation from 1.8 V supply logic.

### 9.3.3 Input Overdrive Operation

The LMH5485-SP input stage architecture is intrinsically robust to input overdrives with the series input resistor required by all applications. High input overdrives cause the outputs to limit into their maximum swings with the remaining input current through the Rg resistors absorbed by internal, back-to-back protection diodes across the two inputs. These diodes are normally off in application, and only turn on to absorb the currents that a large input overdrive might produce through the source impedance and or the series Rg elements required by all designs.

The internal input diodes can safely absorb up to ±15 mA in an overdrive condition. For designs that require more current to be absorbed, consider adding an external protection diode such as BAV99.

#### 9.4 Device Functional Modes

This wideband FDA requires external resistors for correct signal-path operation. When configured for the desired input impedance and gain setting with these external resistors, the amplifier can be either *on* with the  $\overline{PD}$  pin asserted to a voltage greater than (Vs  $^-$ ) + 1.7 V or turned *off* by asserting  $\overline{PD}$  low. Disabling the amplifier shuts off the quiescent current and stops the correct amplifier operation. The signal path is still present for the source signal through the external resistors.

The Vocm control pin sets the output average voltage. Left open, Vocm defaults to an internal mid-supply value. Driving this high-impedance input with a voltage reference within its valid range sets a target for the internal Vcm error amplifier.

#### 9.4.1 Operation from Single-Ended Sources to Differential Outputs

One of the most useful features supported by the FDA device is an easy conversion from a single-ended input to a differential output centered on a user-controlled, common-mode level. While the output side is relatively straightforward, the device input pins move in a common-mode sense with the input signal. This common-mode voltage at the input pins moving with the input signal acts to increase the apparent input impedance to be greater than the Rg value. This input active impedance issue applies to both AC- and DC-coupled designs, and requires somewhat more complex solutions for the resistors to account for this active impedance, as shown in the following subsections.

#### 9.4.1.1 AC-Coupled Signal Path Considerations for Single-Ended Input to Differential Output Conversion

When the signal path can be AC-coupled, the DC biasing for the LMH5485-SP becomes a relatively simple task. In all designs, start by defining the output common-mode voltage. The AC-coupling issue can be separated for the input and output sides of an FDA design. The input can be AC coupled and the output DC coupled, or the output can be AC coupled and the input DC coupled, or they can both be AC coupled. One situation where the output might be DC coupled (for an AC-coupled input), is when driving directly into an ADC where the Vocm control voltage uses the ADC common-mode reference to directly bias the FDA output common-mode to the required ADC input common-mode. In any case, the design starts by setting the desired Vocm. When an AC-coupled path follows the output pins, the best linearity is achieved by operating Vocm at mid-supply. The Vocm voltage must be within the linear range for the common-mode loop, as specified in the headroom specifications (approximately 0.91 V greater than the negative supply and 1.1 V less than the positive supply). If the output path is also AC coupled, simply letting the Vocm control pin float is usually preferred in order to get a mid-supply default Vocm bias with minimal elements. To limit noise, place a 0.1 µF decoupling capacitor on the Vocm pin to ground.

After Vocm is defined, check the target output voltage swing to ensure that the Vocm plus the positive or negative output swing on each side does not clip into the supplies. If the desired output differential swing is defined as Vopp, divide by 4 to obtain the  $\pm$ Vp swing around Vocm at each of the two output pins (each pin operates 180° out of phase with the other). Check that Vocm  $\pm$ Vp does not exceed the absolute supply rails for this rail-to-rail output (RRO) device.

Going to the device input pins side, because both the source and balancing resistor on the nonsignal input side are DC blocked (see 8-1), no common-mode current flows from the output common-mode voltage, thus setting the input common-mode equal to the output common-mode voltage.

This input headroom also sets a limit for higher Vocm voltages. Because the input Vicm is the output Vocm for AC-coupled sources, the 1.2 V minimum headroom for the input pins to the positive supply overrides the 1.1 V headroom limit for the output Vocm. Also, the input signal moves this input Vicm around the DC bias point, as described in the *Resistor Design Equations for the Single-Ended to Differential Configuration of the FDA* section.

Submit Document Feedback

#### 9.4.1.2 DC-Coupled Input Signal Path Considerations for Single-Ended to Differential Conversion

The output considerations remain the same as for the AC-coupled design. Again, the input can be DC-coupled while the output is AC-coupled. A DC-coupled input with an AC-coupled output might have some advantages to move the input Vicm down if the source is ground referenced. 8-3 shows how when the source is DC-coupled into the LMH5485-SP, both sides of the input circuit must be DC coupled to retain differential balance. Normally, the nonsignal input side has an Rg element biased to whatever the source midrange is expected to be. Providing this midscale reference gives a balanced differential swing around Vocm at the outputs. Often, Rg2 is simply grounded for DC-coupled, bipolar-input applications. This configuration gives a balanced differential output if the source is swinging around ground. If the source swings from ground to some positive voltage, grounding Rg2 gives a unipolar output differential swing from both outputs at Vocm (when the input is at ground) to one polarity of swing. Biasing Rg2 to an expected midpoint for the input signal creates a differential output swing around Vocm.

One significant consideration for a DC-coupled input is that Vocm sets up a common-mode bias current from the output back through Rf and Rg to the source on both sides of the feedback. Without input balancing networks, the source must sink or source this DC current. After the input signal range and biasing on the other Rg element is set, check that the voltage divider from Vocm to Vin through Rf and Rg (and possibly Rs) establishes an input Vicm at the device input pins that is in range. If the average source is at ground, the negative rail input stage for the LMH5485-SP is in range for applications using a single positive supply and a positive output Vocm setting because this DC current lifts the average FDA input summing junctions up off of ground to a positive voltage (the average of the V+ and V - input pin voltages on the FDA).

### 9.4.1.3 Resistor Design Equations for the Single-Ended to Differential Configuration of the FDA

The design equations for setting the resistors around an FDA to convert from a single-ended input signal to differential output can be approached from several directions. Here, several critical assumptions are made to simplify the results:

- The feedback resistors are selected first and set equal on the two sides.

- The DC and AC impedances from the summing junctions back to the signal source and ground (or a bias

voltage on the nonsignal input side) are set equal to retain feedback divider balance on each side of the FDA

Both of these assumptions are typical and aimed to delivering the best dynamic range through the FDA signal path.

ા 8-1 and 8-3 shows how after the feedback resistor values are chosen, the aim is to solve for the Rt (a termination resistor to ground on the signal input side), Rg1 (the input gain resistor for the signal path), and Rg2 (the matching gain resistor on the nonsignal input side). The same resistor solutions can be applied to either AC-or DC-coupled paths. Adding blocking capacitors in the input-signal chain is a simple option. 8 8-1 shows how adding these blocking capacitors after the Rt element has the advantage of removing any DC currents in the feedback path from the output Vocm to ground.

Earlier approaches to the solutions for Rt and Rg1 (when the input must be matched to a source impedance, Rs) follow an iterative approach. This complexity arises from the active input impedance at the Rg1 input. When the FDA is used to convert a single-ended signal to differential, the common-mode input voltage at the FDA inputs must move with the input signal to generate the inverted output signal as a current in the Rg2 element. 方程式 1shows a more recent solution, where a quadratic in Rt can be solved for an exact required value. This quadratic emerges from the simultaneous solution for a matched input impedance and target gain. The only inputs required are the following:

- 1. The selected Rf value.

- 2. The target voltage gain (Av) from the input of Rt to the differential output voltage.

- 3. The desired input impedance at the junction of Rt and Rg1 to match Rs.

As 方程式 1 shows, solving this quadratic for Rt starts the solution sequence.

$$Rt^2 - Rt \frac{2Rs\left(2Rf + \frac{Rs}{2}Av^2\right)}{2Rf\left(2 + Av\right) - RsAv(4 + Av)} - \frac{2RfRs^2Av}{2Rf\left(2 + Av\right) - RsAv(4 + Av)} = 0 \tag{1}$$

Being a quadratic, there are limits to the range of solutions. Specifically, after Rf and Rs are chosen, there is physically a maximum gain beyond which 方程式 1 starts to solve for negative Rt values (if input matching is a requirement). With Rf selected, use 方程式 2 to verify that the maximum gain is greater than the desired gain.

$$Av_{max} = (\frac{Rf}{Rs} - 2) \cdot \left[ 1 + \sqrt{1 + \frac{4\frac{Rf}{Rs}}{(\frac{Rf}{Rs} - 2)^2}} \right]$$

(2)

If the achievable  $Av_{max}$  is less than desired, increase the Rf value. After Rt is derived from 方程式 1, the Rg1 element is given by 方程式 3:

$$Rg1 = \frac{2\frac{Rf}{Av} - Rs}{1 + \frac{Rs}{Rt}}$$

(3)

Then, the simplest approach is to use a single Rg2 = Rt  $\parallel$  Rs + Rg1 on the nonsignal input side. Often, this approach is shown as the separate Rg1 and Rs elements. Using these separate elements provide a better divider match on the two feedback paths, but a single Rg2 is often acceptable. A direct solution for Rg2 is given as 4:

$$Rg2 = \frac{2\frac{Rt}{Av}}{1 + \frac{Rs}{Rt}}$$

(4)

Submit Document Feedback

表 9-1. Required Resistors for a Single-Ended to Differential FDA Design Stepping Gain from 1 V/V to 14 V/V

|                          | 2 22 23 24 25 25 25 25 25 25 25 25 25 25 25 25 25 |       |                      |        |                      |        |                           |               |                |               |  |  |  |

|--------------------------|---------------------------------------------------|-------|----------------------|--------|----------------------|--------|---------------------------|---------------|----------------|---------------|--|--|--|

| <b>Av</b> <sup>(1)</sup> | Rt, EXACT                                         | Rt 1% | Rg1,<br>EXACT<br>(Ω) | Rg1 1% | Rg2,<br>EXACT<br>(Ω) | Rg2 1% | ACTUAL<br>Z <sub>IN</sub> | %ERR TO<br>Rs | ACTUAL<br>GAIN | %ERR TO<br>Av |  |  |  |

| 1                        | 55.2                                              | 54.9  | 395                  | 392    | 421                  | 422    | 49.731                    | - 0.54%       | 1.006          | 0.62%         |  |  |  |

| 2                        | 60.1                                              | 60.4  | 193                  | 191    | 220                  | 221    | 50.171                    | 0.34%         | 2.014          | 0.72%         |  |  |  |

| 3                        | 65.6                                              | 64.9  | 123                  | 124    | 151                  | 150    | 49.572                    | - 0.86%       | 2.983          | - 0.57%       |  |  |  |