LM3632A

ZHCSDN2 - APRIL 2015

#### LM3632A 集成单芯片背光、 偏置电源和 1.5A 闪光灯 LED 驱动器

# 1 特性

- 可驱动多达两个灯串(通常为8个串联的 LED)

- 集成背光升压转换器,最高输出电压达 29V

- 两个低侧恒流 LED 驱动器,最高输出电流达 25mA

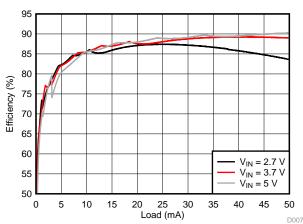

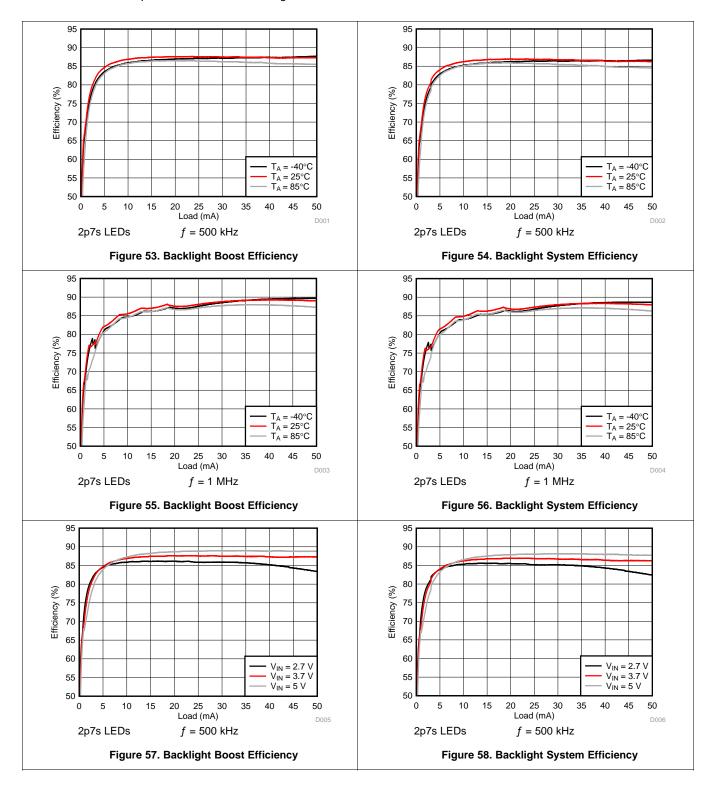

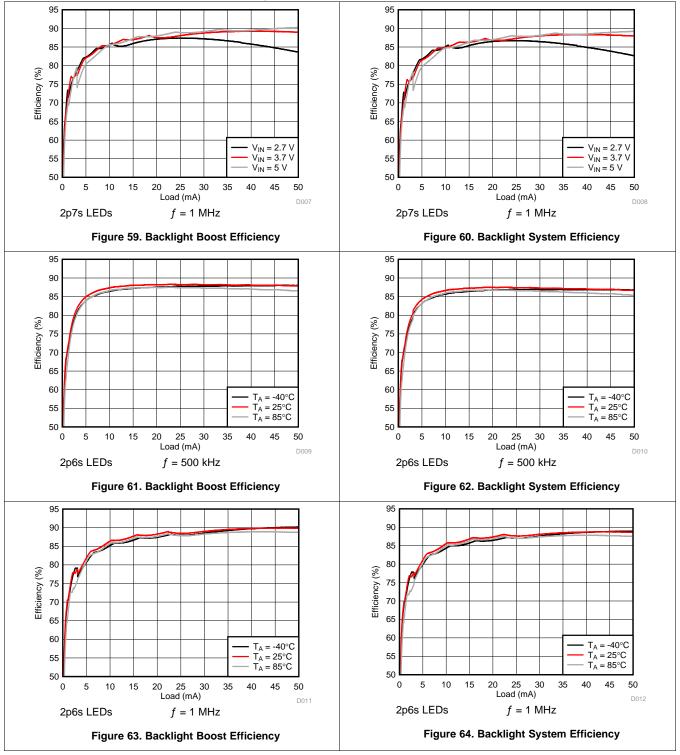

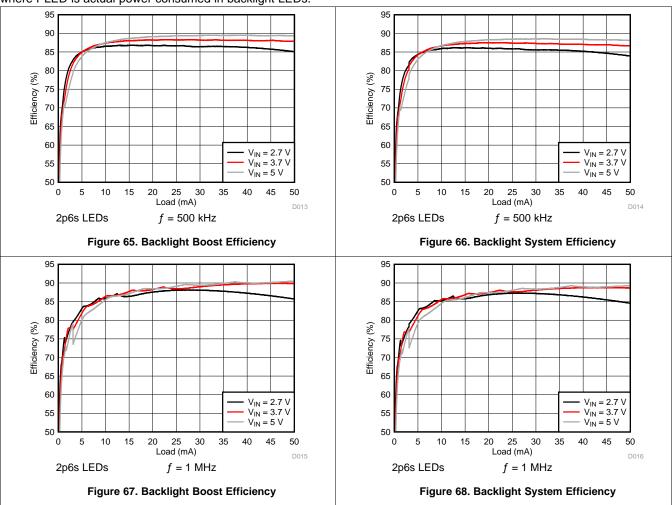

- 背光效率高达 90%

- 11 位指数或线性调光

- 具有外部脉宽调制 (PWM) 输入,可实现内容自适 应背光控制 (CABC) 背光操作

- LCD 偏置电源效率 > 85%

- 可编程的正 LCD 偏置电源(4V至6V),最大输 出电流达 50mA

- 可编程的负 LCD 偏置电源(-6V 至 -4V), 最大输 出电流达 50mA

- 1.5A 闪光灯 LED 升压转换器

- 闪光灯效率 > 85%

- 输入电压范围: 2.7V 至 5V

#### 应用 2

- 智能手机 LCD 背光照明和偏置电源

- 小型平板电脑 LCD 背光照明和偏置电源

# 3 说明

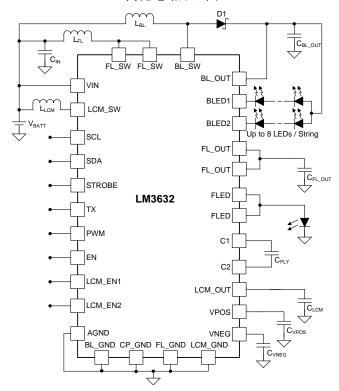

LM3632A 器件集成了用于 LCD 面板背光照明和摄像 机闪光灯的白光发光二极管 (WLED) 驱动器以及用于 LCD 面板的偏置电源。 该器件具备 LED 驱动器所需 的全套安全功能,并且效率高达 90%,正/负偏置电源 轨精度高达 1.5%。 该器件最多能够驱动 16 个背光 LED, 是中小型显示屏的理想选择。 该器件可使用由 同步升压转换器供电的 1.5A 恒流 LED 驱动器来驱动 闪光灯。 高侧闪光灯电流源支持 LED 阴极接地操作。

LM3632A 兼具高集成度和可编程性, 无需修改硬件即 可适应各类应用。

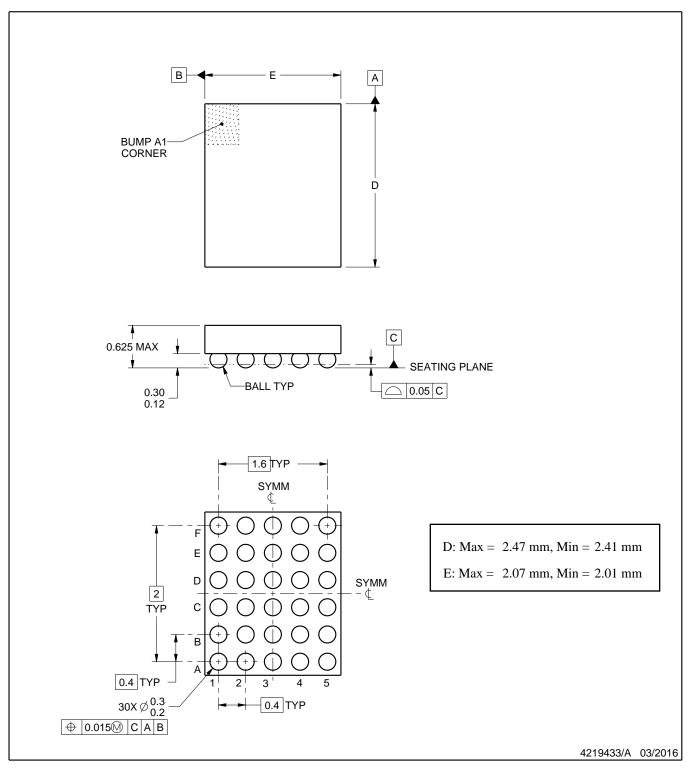

器件信息(1)

| 器件型号    | 封装         | 封装尺寸(最大值)       |

|---------|------------|-----------------|

| LM3632A | DSBGA (30) | 2.47mm x 2.07mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

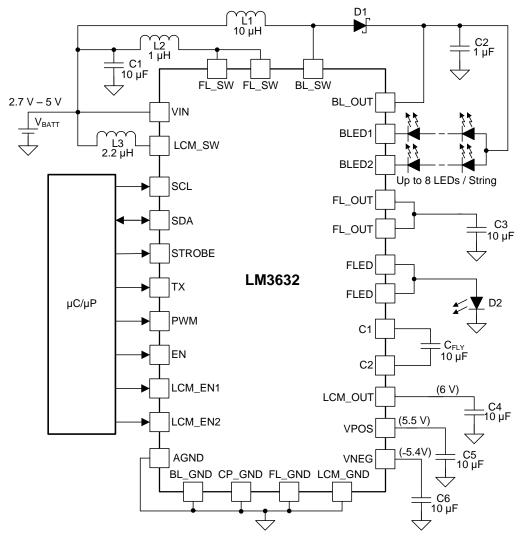

#### 简化电路原理图

# 背光效率,2P7S

|   | # <del>‡</del> <u></u> #                            |    | 7.4 Device Functional Modes    | 26         |

|---|-----------------------------------------------------|----|--------------------------------|------------|

| 1 | 特性 1                                                |    |                                |            |

| 2 | 应用 1                                                |    | 7.5 Programming                |            |

| 3 | 说明 1                                                |    | 7.6 Register Maps              | 31         |

| 4 | 修订历史记录 2                                            | 8  | Application and Implementation | 39         |

| 5 | Pin Configuration and Functions                     |    | 8.1 Application Information    | 39         |

| 6 | Specifications4                                     |    | 8.2 Typical Application        | 39         |

| • | 6.1 Absolute Maximum Ratings                        | 9  | Power Supply Recommendations   | 53         |

|   | 6.2 ESD Ratings                                     | 10 | Layout                         | <u>53</u>  |

|   | 6.3 Recommended Operating Conditions                |    | 10.1 Layout Guidelines         | <u>53</u>  |

|   | 6.4 Thermal Information                             |    | 10.2 Layout Example            | 54         |

|   | 6.5 Electrical Characteristics                      | 11 | 器件和文档支持                        | 55         |

|   | 6.6 I <sup>2</sup> C Timing Requirements (SDA, SCL) |    | 11.1 器件支持                      | <u>5</u> 5 |

|   | 6.7 Typical Characteristics                         |    | 11.2 文档支持                      | 55         |

| 7 | Detailed Description 12                             |    | 11.3 商标                        | 55         |

| - | 7.1 Overview                                        |    | 11.4 静电放电警告                    | <u>55</u>  |

|   | 7.2 Functional Block Diagram                        |    | 11.5 术语表                       | <u>5</u> 5 |

|   | 7.3 Features Description                            | 12 | 机械、封装和可订购信息                    | 55         |

|   | ·                                                   |    |                                |            |

# 4 修订历史记录

| 日期         | 修订版本 | 注释    |

|------------|------|-------|

| 2015 年 4 月 | *    | 最初发布。 |

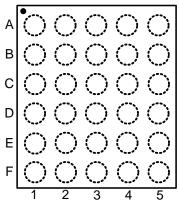

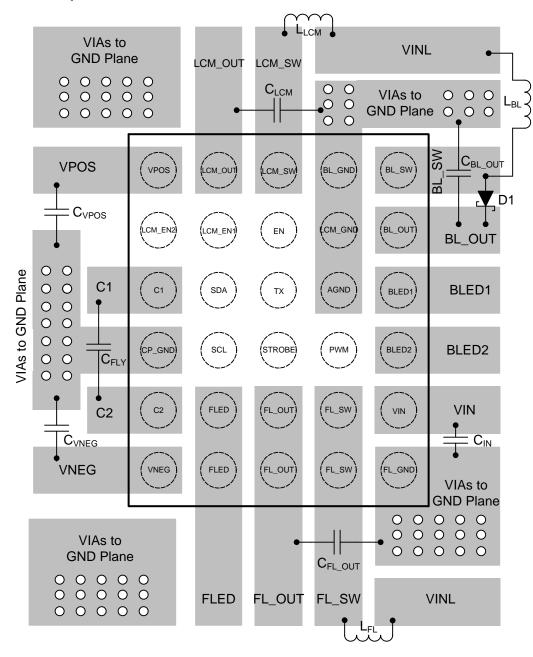

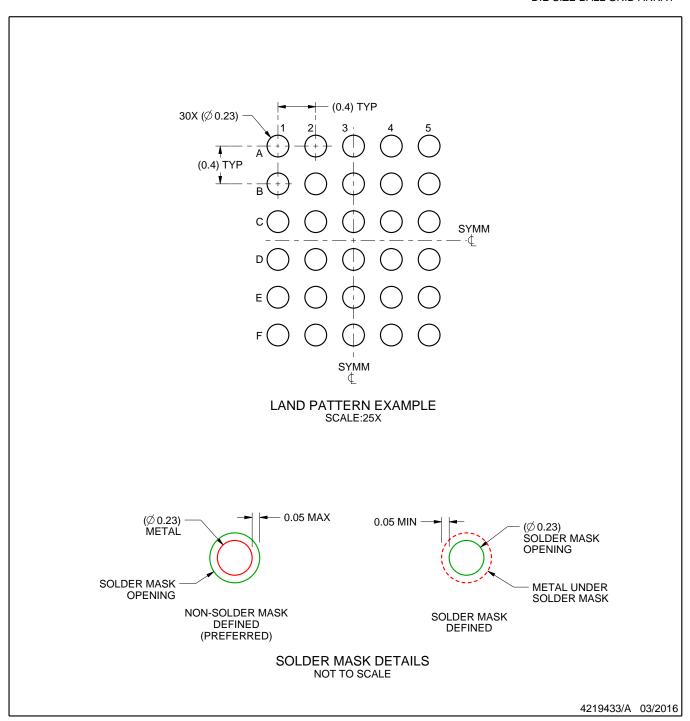

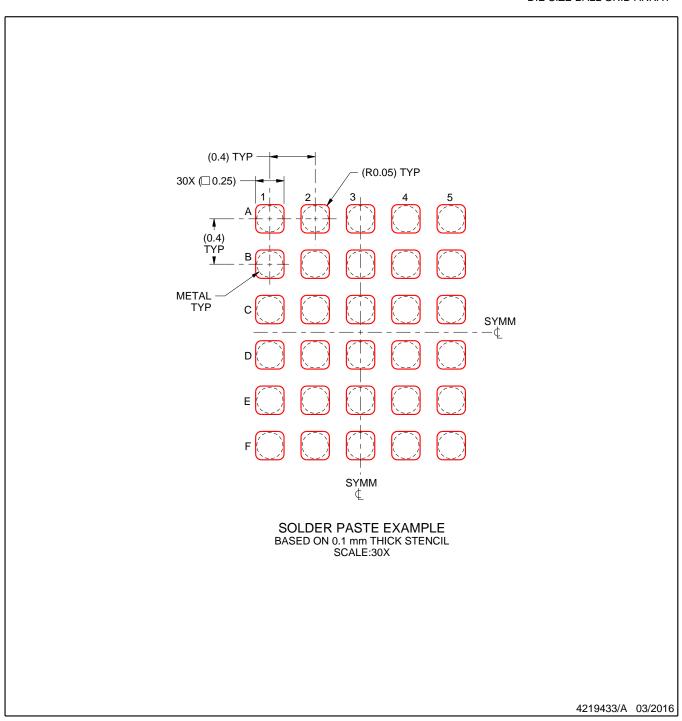

# **5 Pin Configuration and Functions**

**Pin Functions**

|        | PIN     |      | FIII FUNCTIONS                                                     |

|--------|---------|------|--------------------------------------------------------------------|

| NUMBER | NAME    | TYPE | DESCRIPTION                                                        |

| A1     | VPOS    | 0    | Positive LDO output for LCM bias power                             |

| A2     | LCM_OUT | 0    | LCM bias boost output voltage                                      |

| А3     | LCM_SW  | 0    | LCM bias boost switch connection                                   |

| A4     | BL_GND  | -    | Backlight boost ground connection                                  |

| A5     | BL_SW   | 0    | Backlight boost switch connection                                  |

| B1     | LCM_EN2 | Į    | Enable for inverting charge pump output                            |

| B2     | LCM_EN1 | I    | Enable for positive LDO output                                     |

| В3     | EN      | I    | Active high chip enable                                            |

| B4     | LCM_GND | -    | LCM bias boost ground connection                                   |

| B5     | BL_OUT  | 0    | Backlight boost output voltage                                     |

| C1     | C1      | 0    | Inverting charge pump flying capacitor positive connection         |

| C2     | SDA     | I/O  | Serial data connection for I <sup>2</sup> C- compatible interface  |

| C3     | TX      | I    | Flash interrupt input                                              |

| C4     | AGND    | -    | Analog ground connection                                           |

| C5     | BLED1   | 0    | Input pin to internal LED current sink 1                           |

| D1     | CP_GND  | -    | Inverting charge pump ground connection                            |

| D2     | SCL     | I    | Serial clock connection for I <sup>2</sup> C- compatible interface |

| D3     | STROBE  | I    | Flash enable input                                                 |

| D4     | PWM     | I    | PWM input for CABC current control                                 |

| D5     | BLED2   | 0    | Input pin to internal LED current sink 2                           |

| E1     | C2      | 0    | Inverting charge pump flying capacitor negative connection         |

| E2     | FLED    | 0    | High-side current source output for flash LED                      |

| E3     | FL_OUT  | 0    | Flash boost output voltage                                         |

| E4     | FL_SW   | 0    | Flash boost switch connection                                      |

| E5     | VIN     | I    | Input voltage connection                                           |

| F1     | VNEG    | 0    | Inverting charge pump output voltage                               |

| F2     | FLED    | 0    | High-side current source output for flash LED                      |

| F3     | FL_OUT  | 0    | Flash boost output voltage                                         |

| F4     | FL_SW   | 0    | Flash boost switch connection                                      |

| F5     | FL_GND  | -    | Flash boost ground connection                                      |

# TEXAS INSTRUMENTS

# 6 Specifications

# 6.1 Absolute Maximum Ratings<sup>(1)</sup>

Over operating free-air temperature range (unless otherwise noted)

|                                                                                      | MIN  | MAX                | UNIT |

|--------------------------------------------------------------------------------------|------|--------------------|------|

| Voltage on VIN, FL_SW, FL_OUT, FLED, EN, LCM_EN1, LCM_EN2, PWM, STROBE, TX, SCL, SDA | -0.3 | 6                  | V    |

| Voltage on LCM_SW, LCM_OUT, VPOS, C1                                                 | -0.3 | 7                  | V    |

| Voltage on VNEG, C2                                                                  | -7   | 0.3                | V    |

| Voltage on BL_SW, BL_VOUT, BLED1, BLED2                                              | -0.3 | 30                 | V    |

| Continuous power dissipation                                                         |      | Internally limited |      |

| Maximum junction temperature, T <sub>J(MAX)</sub>                                    |      | 150                | °C   |

| Storage temperature, T <sub>stg</sub>                                                | -45  | 150                |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| \/                 |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted).

|                                                              | MIN | MAX | UNIT |

|--------------------------------------------------------------|-----|-----|------|

| Input voltage, V <sub>IN</sub>                               | 2.7 | 5   | V    |

| Operating ambient temperature, T <sub>A</sub> <sup>(1)</sup> | -40 | 85  | °C   |

<sup>(1)</sup> In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to-ambient thermal resistance of the part/package in the application (R<sub>θJA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> - (R<sub>θJA</sub> × P<sub>D-MAX</sub>).

#### 6.4 Thermal Information

|                 | THERMAL METRIC <sup>(1)</sup>                | LM3632A<br>YFF (DSBGA)<br>30 PINS | UNIT |

|-----------------|----------------------------------------------|-----------------------------------|------|

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance       | 58.6                              |      |

| $R_{\theta JC}$ | Junction-to-case (top) thermal resistance    | 0.2                               |      |

| $R_{\theta JB}$ | Junction-to-board thermal resistance         | 8.3                               | °C/W |

| $\Psi_{JT}$     | Junction-to-top characterization parameter   | 1.4                               |      |

| $\Psi_{JB}$     | Junction-to-board characterization parameter | 8.3                               |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.5 Electrical Characteristics

Unless otherwise specified, limits apply over the full operating ambient temperature range ( $-40^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}$ ),  $V_{IN} = 3.7 \text{ V}$ ,  $V_{VPOS} = 5.5 \text{ V}$ ,  $V_{VNEG} = -5.4 \text{ V}$ ,  $V_{LCM}$  OUT = 6 V.

|                        | $V_{\text{VNEG}} = -5.4 \text{ V}, V_{\text{LCM\_OUT}} = 6 \text{ V}.$ <b>PARAMETER</b> | TEST CON                                                                                     | IDITION                                                   | MIN  | TYP   | MAX      | UNIT  |

|------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------|------|-------|----------|-------|

| CURRENT CO             |                                                                                         | 1201 001                                                                                     |                                                           |      |       | 1111/15/ | 0     |

| I <sub>SD</sub>        | Shutdown current                                                                        | EN = 0                                                                                       |                                                           |      | 1     | 4        | μΑ    |

| -                      | Quiescent current, device not                                                           |                                                                                              |                                                           |      |       |          | μΛ    |

| IQ                     | switching                                                                               | $EN = V_{IN}$ , LCD bias b                                                                   | oost disabled                                             |      | 2     | 10       | μΑ    |

| I <sub>LCD_EN</sub>    |                                                                                         | LCD bias boost enable                                                                        | ed, no-load                                               |      | 0.5   |          | mA    |

| DEVICE PROT            | ECTION                                                                                  |                                                                                              |                                                           |      |       |          |       |

| TSD                    | Thermal shutdown                                                                        |                                                                                              |                                                           |      | 140   |          | °C    |

| BACKLIGHT L            | ED CURRENT SINKS                                                                        |                                                                                              |                                                           |      |       |          |       |

| I <sub>LED_MAX</sub>   | Maximum output current in BLED1/2                                                       | $2.7 \text{ V} \leq \text{V}_{\text{IN}} \leq 5 \text{ V}$ , line mode                       | ear or exponential                                        |      | 25    |          | mA    |

| I <sub>LED_MIN</sub>   | Minimum output current in BLED1/2                                                       | $2.7 \text{ V} \le \text{V}_{\text{IN}} \le 5 \text{ V}$ , line mode                         | 2.7 V ≤ V <sub>IN</sub> ≤ 5 V, linear or exponential mode |      | 50    |          | μΑ    |

| I <sub>ACCU</sub>      | LED current accuracy <sup>(1)</sup>                                                     | 2.7 V $\leq$ V <sub>IN</sub> $\leq$ 5 V, 50 mA, linear or exponer                            |                                                           | -3%  | 0.1%  | 3%       |       |

| I <sub>MATCH</sub>     | LED1 to LED2 current matching <sup>(1)</sup>                                            | 2.7 V ≤ V <sub>IN</sub> ≤ 5 V, 300 µA ≤ I <sub>LED</sub> ≤ 25 mA, linear or exponential mode |                                                           | -2%  | 0.1%  | 2%       |       |

| BACKLIGHT B            | OOST CONVERTER                                                                          |                                                                                              | ·                                                         |      |       |          |       |

| V <sub>OVP_BL</sub>    | Backlight boost output overvoltage protection                                           | 2.7 V ≤ V <sub>IN</sub> ≤ 5 V, 29 V option                                                   |                                                           | 28   | 28.75 | 29.5     | V     |

| Efficiency             | Typical efficiency <sup>(2)</sup>                                                       | $I_{LED}$ = 5 mA/string, $V_{IN}$ = 3.7 V (2 x 7 LEDs), $(P_{OUT}/P_{IN})$                   |                                                           |      | 87%   |          |       |

| .,                     | Regulated current sink                                                                  | I <sub>LED</sub> = 25 mA                                                                     |                                                           |      | 250   |          | mV    |

| $V_{HR}$               | headroom voltage                                                                        | I <sub>LED</sub> = 5 mA                                                                      |                                                           |      | 100   |          | mV    |

| V <sub>HR_MIN</sub>    | Current sink minimum headroom voltage                                                   | I <sub>LED</sub> = 95% of nomina                                                             | I, I <sub>LED</sub> = 5 mA                                |      | 30    |          | mV    |

| R <sub>DSON</sub>      | NMOS switch on resistance                                                               | I <sub>SW</sub> = 100 mA                                                                     |                                                           |      | 0.25  |          | Ω     |

| I <sub>CL</sub>        | NMOS switch current limit                                                               | 2.7 V ≤ V <sub>IN</sub> ≤ 5 V                                                                |                                                           | 900  | 1000  | 1100     | mA    |

| $f_{\sf SW\_BLBOOST}$  | Cuitabia a facanca                                                                      | 2.7 V ≤ V <sub>IN</sub> ≤ 5 V                                                                | 500-kHz mode                                              | 450  | 500   | 550      | 1.11= |

|                        | Switching frequency                                                                     |                                                                                              | 1-MHz mode                                                | 900  | 1000  | 1100     | kHz   |

| D <sub>MAX</sub>       | Maximum duty cycle                                                                      |                                                                                              |                                                           |      | 94%   |          |       |

| LCM BIAS BO            | OST CONVERTER                                                                           |                                                                                              | ·                                                         |      |       |          |       |

| V <sub>OVP_LCM</sub>   | LCM bias boost output overvoltage protection                                            | 2.7 V ≤ V <sub>IN</sub> ≤ 5 V                                                                |                                                           |      | 7     |          | V     |

| $f_{\sf SW\_LCMBST}$   | Switching frequency (3)                                                                 | 2.7 V ≤ V <sub>IN</sub> ≤ 5 V                                                                |                                                           |      | 2500  |          | kHz   |

|                        | Bias boost output voltage range                                                         |                                                                                              |                                                           | 4.5  |       | 6.4      | V     |

|                        | Output voltage step size                                                                |                                                                                              |                                                           |      | 50    |          | mV    |

|                        | Peak-to-peak ripple voltage (3)                                                         | $I_{LOAD} = 5 \text{ mA } \& 50 \text{ mA}, C_{BST} = 10 \mu\text{F}$                        |                                                           |      | 50    |          | mVpp  |

| V <sub>LCM_OUT</sub>   | LCM_OUT line transient response (3)                                                     | V <sub>IN</sub> + 500 mVp-p AC<br>100 mV/μs, 200 Hz, 1<br>= 5 mA, C <sub>IN</sub> = 10 μF    | square wave, Tr = 2.5 % duty, I <sub>LOAD</sub>           | -50  | ±25   | 50       | mV    |

|                        | LCM_OUT load transient response (3)                                                     | Load current step 0 m<br>T <sub>RISE/FALL</sub> = 100 mA/µ                                   | nA to $\overline{100}$ mA,<br>us, $C_{IN} = 10 \mu F$     | -150 |       | 150      | mV    |

| I <sub>CL_LCMBST</sub> | Valley current limit                                                                    |                                                                                              |                                                           |      | 1000  |          | mA    |

<sup>(1)</sup> Output Current Accuracy is the difference between the actual value of the output current and programmed value of this current. Matching is the maximum difference from the average. For the constant current sinks on the device (BLED1 and BLED2), the following is determined: the maximum output current (MAX), the minimum output current (MIN), and the average output current of both outputs (AVG). Matching number is calculated: (I<sub>LED1</sub> – I<sub>LED2</sub>)/(I<sub>LED1</sub> + I<sub>LED2</sub>). The typical specification provided is the most likely norm of the matching figure of all parts. Note that some manufacturers have different definitions in use.

<sup>(2)</sup> Typical value only for information.

<sup>(3)</sup> Limits set by characterization and/or simulation only.

# **Electrical Characteristics (continued)**

Unless otherwise specified, limits apply over the full operating ambient temperature range ( $-40^{\circ}C \le T_A \le 85^{\circ}C$ ),  $V_{IN} = 3.7 \text{ V}$ ,  $V_{VPOS} = 5.5 \text{ V}$ ,  $V_{VNEG} = -5.4 \text{ V}$ ,  $V_{LCM\ OUT} = 6 \text{ V}$ .

|                           | PARAMETER                                                              | TEST CON                                                                               | DITION                                                                                            | MIN   | TYP        | MAX  | UNIT |

|---------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------|------------|------|------|

|                           | High-side MOSFET on resistance                                         | $V_{IN} = V_{GS} = 5 \text{ V}, T_A =$                                                 | 25°C                                                                                              |       | 170        |      |      |

| KDSON_LCMBST              | Low-side MOSFET on Resistance                                          | $V_{IN} = V_{GS} = 5 \text{ V}, T_A =$                                                 | $V_{IN} = V_{GS} = 5 \text{ V}, T_A = 25^{\circ}\text{C}$                                         |       | 290        |      | mΩ   |

| EFF <sub>LCMBST</sub>     | Efficiency (2)                                                         | V <sub>LCM_OUT</sub> = 6 V, 5 mA                                                       | A < I <sub>LCMBST</sub> < 100                                                                     |       | 92%        |      |      |

| t <sub>ST_LCMBST</sub>    | Start-up time (LCM_OUT), $V_{LCM_OUT} = 10\%$ to $90\%$ <sup>(3)</sup> | $C_{LCM\_BST} = 10 \mu F$                                                              |                                                                                                   |       |            | 1000 | μs   |

| DISPLAY BIAS              | POSITIVE OUTPUT (VPOS)                                                 |                                                                                        |                                                                                                   |       |            |      |      |

|                           | Programmable output voltage range                                      |                                                                                        |                                                                                                   | 4     |            | 6    | V    |

|                           | Output voltage step size                                               |                                                                                        |                                                                                                   |       | 50         |      | mV   |

|                           | Output voltage accuracy                                                | Output voltage = 5.4                                                                   | /                                                                                                 | -1.5% |            | 1.5% |      |

| V <sub>VPOS</sub>         | VPOS line transient response (3)                                       | V <sub>IN</sub> + 500 mVp-p AC s<br>100 mV/µs, 200 Hz, I <sub>L</sub><br>= 10 µF       | $V_{IN}$ + 500 mVp-p AC square wave, Tr = 100 mV/µs, 200 Hz, $I_{LOAD}$ = 25 mA, $C_{IN}$ = 10 µF |       |            | 50   | mV   |

|                           | VPOS load transient response (3)                                       | 0 to 50 mA load trans<br>μF                                                            | -50                                                                                               |       | 50         | mV   |      |

|                           | DC load regulation (3)                                                 | 0 mA ≤ I <sub>VPOS</sub> ≤ 50 mA                                                       |                                                                                                   |       |            | 20   | mV   |

| I <sub>MAX_VPOS</sub>     | Maximum output current                                                 |                                                                                        |                                                                                                   |       | 50         |      | mA   |

| I <sub>CL_VPOS</sub>      | Output current limit                                                   |                                                                                        |                                                                                                   |       | 80         |      | mA   |

| I <sub>RUSH_PK_VPOS</sub> | Peak start-up inrush current (3)                                       | $V_{LCM\_OUT} = 6.3 \text{ V}, V_{POS} = 5.8 \text{ V}, C_{VPOS} = 10 \mu\text{F}$     |                                                                                                   |       |            | 250  | mA   |

| V <sub>DO_VPOS</sub>      | VPOS dropout voltage (4)                                               | $I_{VPOS} = 50 \text{ mA}, V_{VPOS}$                                                   | = 5.5 V                                                                                           |       |            | 100  | mV   |

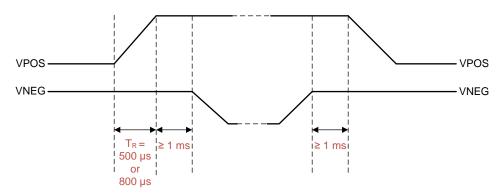

| t <sub>ST_VPOS</sub>      | Start-up time VPOS, $V_{VPOS} = 10\%$ to 90% (3)                       | $C_{VPOS} = 10 \mu F$                                                                  | 500-µs setting                                                                                    |       | 500<br>800 |      | μs   |

| R <sub>PD_VPOS</sub>      | Output pull-down resistor (VPOS)                                       | VPOS disabled                                                                          |                                                                                                   | 30    | 80         | 110  | Ω    |

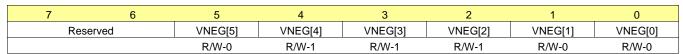

| DISPLAY BIAS              | NEGATIVE OUTPUT (VNEG)                                                 |                                                                                        |                                                                                                   |       |            |      |      |

| V <sub>OVP_VNEG</sub>     | LCM bias negative charge-pump output overvoltage protection            | Below V <sub>VNEG</sub> output v                                                       | oltage target                                                                                     |       | -250       |      | mV   |

| V <sub>SHORT_VNEG</sub>   | LCM bias negative charge-pump output short circuit protection          | VNEG to CP_GND                                                                         |                                                                                                   |       | -750       |      | mV   |

|                           | Programmable output voltage range                                      |                                                                                        |                                                                                                   | -6    |            | -4   | V    |

|                           | Output voltage step size                                               |                                                                                        |                                                                                                   |       | 50         |      | mV   |

|                           | Output accuracy                                                        | Output voltage = -5.4                                                                  | V                                                                                                 | -1.5% |            | 1.5% |      |

| $V_{VNEG}$                | Peak-to-peak ripple voltage <sup>(3)</sup>                             | $I_{LOAD}$ = 5 mA & 50 mA<br>$C_{VNEG}$ = 10 $\mu$ F                                   | λ,                                                                                                |       | 60         |      | mVpp |

| VNEG                      | VNEG line transient response (3)                                       | V <sub>IN</sub> + 500 mVp-p AC s<br>mV/µs 200 Hz, 12.5%                                |                                                                                                   | -50   | ±25        | 50   | mV   |

|                           | VNEG load transient response (3)                                       | 0 to 50 mA load transient,<br>T <sub>RISE/FALL</sub> = 1 μs, C <sub>VNEG</sub> = 10 μF |                                                                                                   |       |            | 100  | mV   |

|                           | Efficiency <sup>(2)</sup>                                              | $V_{IN} = 3.7 \text{ V}, V_{LCM\_OUT}$<br>$V_{VNEG} = -5.4 \text{ V}, I_{VNEG}$        | = 5.8 V,                                                                                          |       | 92%        |      |      |

| I <sub>MAX_VNEG</sub>     | Maximum output current <sup>(3)</sup>                                  | $V_{IN} = 3.7 \text{ V}, V_{LCM\_OUT}$<br>$V_{VNEG} = -5.4 \text{ V}$                  | = 5.8 V,                                                                                          |       | 50         |      | mA   |

| I <sub>CL_VNEG</sub>      | Output current limit (3)                                               |                                                                                        |                                                                                                   |       | 75         |      | mA   |

# **Electrical Characteristics (continued)**

Unless otherwise specified, limits apply over the full operating ambient temperature range ( $-40^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}$ ),  $V_{IN} = 3.7 \text{ V}$ ,  $V_{VPOS} = 5.5 \text{ V}$ ,  $V_{VNEG} = -5.4 \text{ V}$ ,  $V_{LCM\_OUT} = 6 \text{ V}$ .

|                        | PARAMETER                                                            | TEST CONDITION                                                                                | MIN  | TYP | MAX             | UNIT       |  |

|------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------|-----|-----------------|------------|--|

|                        |                                                                      | Q1                                                                                            |      | 350 |                 |            |  |

| R <sub>DSON_VNEG</sub> | Charge FET pump on resistance                                        | Q2                                                                                            |      | 400 |                 | $m\Omega$  |  |

|                        |                                                                      | Q3                                                                                            |      | 400 |                 |            |  |

| t <sub>ST_VNEG</sub>   | Start-up time ( $V_{VNEG}$ ), $V_{VNEG}$ = 10% to 90% <sup>(3)</sup> | $V_{VNEG} = -6 \text{ V}, C_{VNEG} = 10 \mu\text{F}$                                          |      | 1   |                 | ms         |  |

| R <sub>PU_VNEG</sub>   | Output pullup resistor, VNEG <sup>(3)</sup>                          | VNEG Disabled, V <sub>LCM_OUT</sub> > 4.8 V                                                   |      | 20  | 40              | Ω          |  |

| FLASH DRIVE            | R BOOST                                                              |                                                                                               | *    |     | *               |            |  |

| I <sub>LED</sub>       | Current source accuracy                                              | 1.5-A flash, V <sub>FL_OUT</sub> = 4 V                                                        | 1.4  | 1.5 | 1.6             | Α          |  |

| .,                     | Output overvoltage protection                                        | ON threshold                                                                                  | 4.85 | 5   | 5.1             |            |  |

| $V_{OVP}$              | trip point                                                           | OFF threshold                                                                                 | 4.75 | 4.9 | 5               | V          |  |

| V <sub>HR</sub>        | Current source regulation voltage                                    | 1.5-A flash, V <sub>FL_OUT</sub> = 4 V                                                        |      | 275 |                 | mV         |  |

|                        | Custoh aurrant limit                                                 |                                                                                               | 2.45 | 2.8 | 3.15            | ۸          |  |

| I <sub>CL</sub>        | Switch current limit                                                 |                                                                                               | 1.65 | 1.9 | 2.15 A          | Α          |  |

| R <sub>NMOS</sub>      | NMOS switch on resistance                                            | I <sub>NMOS</sub> = 1 A                                                                       |      | 80  |                 | <b>~</b> 0 |  |

| R <sub>PMOS</sub>      | PMOS switch on resistance                                            | I <sub>PMOS</sub> = 1 A                                                                       |      | 100 |                 | mΩ         |  |

| $V_{\text{VINM}}$      | Input voltage monitor trip threshold                                 |                                                                                               | 2.76 | 2.9 | 3.04            | V          |  |

| LOGIC INPUTS           | S (PWM, EN, LCM_EN1, LCM_EN2,                                        | SCL, SDA, TX, STROBE)                                                                         | •    |     | ·               |            |  |

| $V_{IL}$               | Input logic low                                                      |                                                                                               | 0    |     | 0.4             | V          |  |

| V <sub>IH</sub>        | Input logic high                                                     |                                                                                               | 1.2  |     | V <sub>IN</sub> | V          |  |

| LOGIC OUTPL            | JTS (SDA)                                                            |                                                                                               |      |     |                 |            |  |

| V <sub>OL</sub>        | Output logic low                                                     | $2.7 \text{ V} \le \text{V}_{\text{IN}} \le 5 \text{ V}, \text{I}_{\text{OL}} = 3 \text{ mA}$ | 0    |     | 0.4             | V          |  |

| PWM INPUT              |                                                                      |                                                                                               |      |     | *               |            |  |

| $f_{\sf PWM\_INPUT}$   | PWM input frequency (2)                                              |                                                                                               | 100  |     | 20000           | Hz         |  |

|                        | Minimum DIMM ONLOGE (1)                                              | PWM sampling frequency = 1 MHz                                                                | 6    |     |                 |            |  |

|                        | Minimum PWM ON/OFF time (3)                                          | PWM sampling frequency = 4 MHz                                                                | 1.5  |     |                 | μs         |  |

|                        | PWM timeout (3)                                                      | PWM sampling frequency = 1 MHz                                                                |      | 25  |                 |            |  |

|                        | Pyvivi timeout                                                       | PWM sampling frequency = 4 MHz                                                                |      | 3   |                 | ms         |  |

# TEXAS INSTRUMENTS

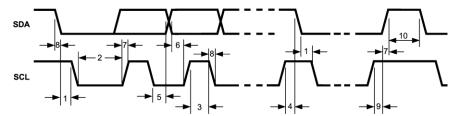

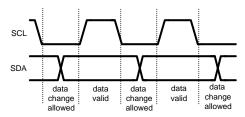

# 6.6 I<sup>2</sup>C Timing Requirements (SDA, SCL) (1)

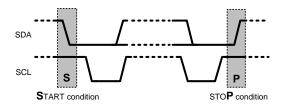

Over operating free-air temperature range (unless otherwise noted)(see Figure 1).

|                |                                                  | MIN                    | NOM | MAX | UNIT |

|----------------|--------------------------------------------------|------------------------|-----|-----|------|

| $f_{SCL}$      | Clock frequency                                  |                        |     | 400 | kHz  |

| 1              | Hold time (repeated) START condition             | 0.6                    |     |     | μs   |

| 2              | Clock low time                                   | 1.3                    |     |     | μs   |

| 3              | Clock high time                                  | 600                    |     |     | ns   |

| 4              | Set-up time for a repeated START condition       | 600                    |     |     | ns   |

| 5              | Data hold time                                   | 50                     |     |     | ns   |

| 6              | Data set-up time                                 | 100                    |     |     | ns   |

| 7              | Rise time of SDA and SCL                         | 20 + 0.1C <sub>b</sub> |     | 300 | ns   |

| 8              | Fall time of SDA and SCL                         | 15 + 0.1C <sub>b</sub> |     | 300 | ns   |

| 9              | Set-Up time between a STOP and a START condition | 1.3                    |     |     | μs   |

| C <sub>b</sub> | Capacitive load for each bus line                | 10                     |     | 200 | pF   |

(1) Limits set by characterization and/or simulation only.

Figure 1. I<sup>2</sup>C Timing Parameters

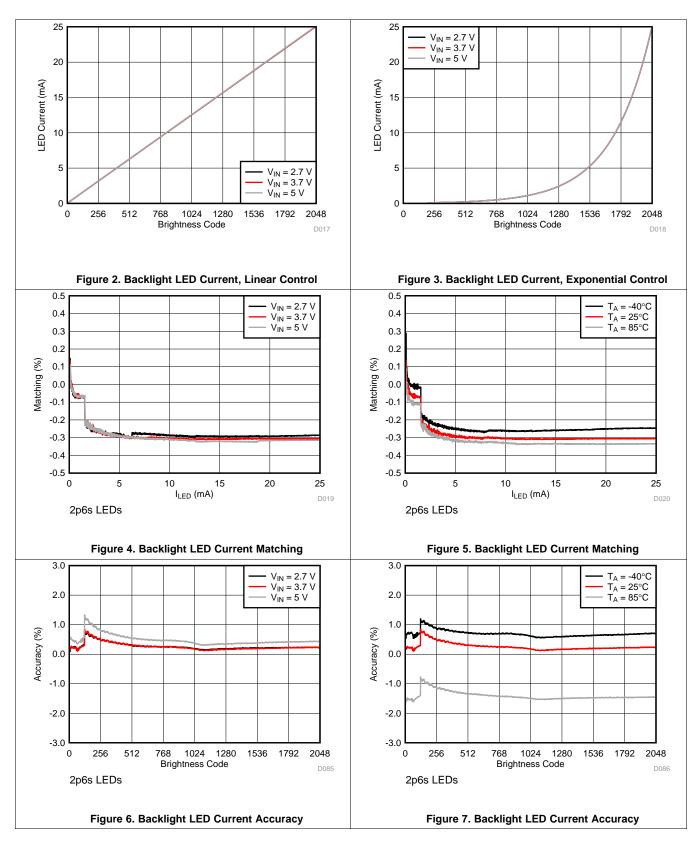

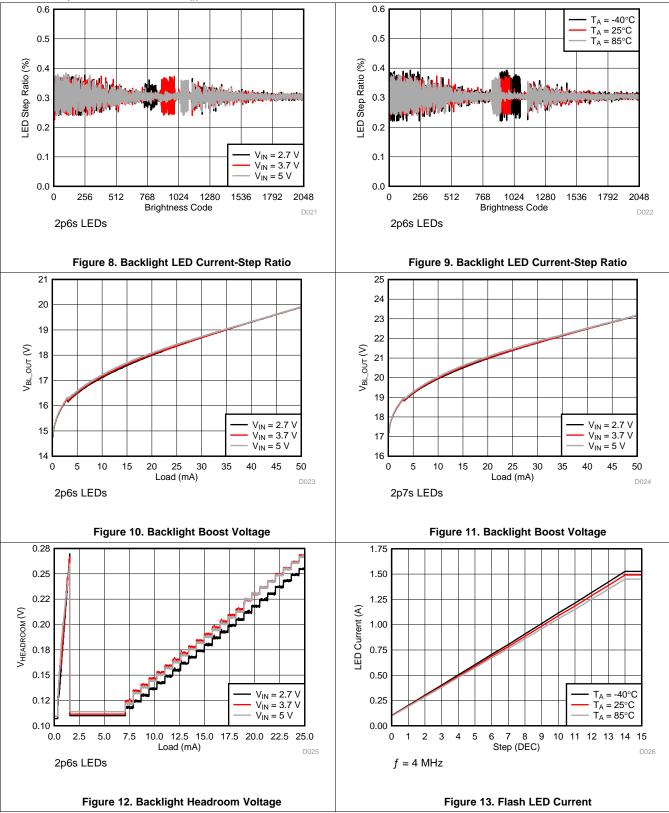

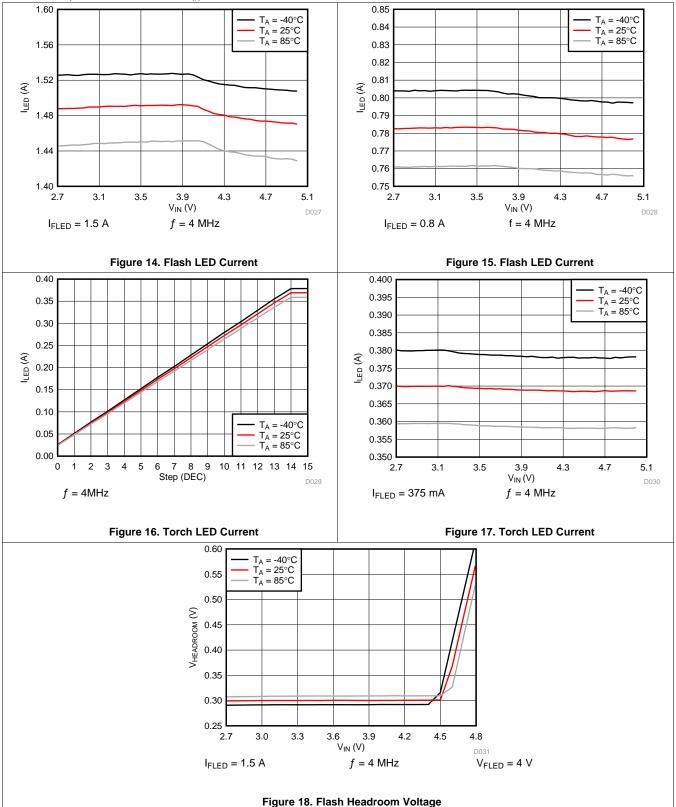

# 6.7 Typical Characteristics

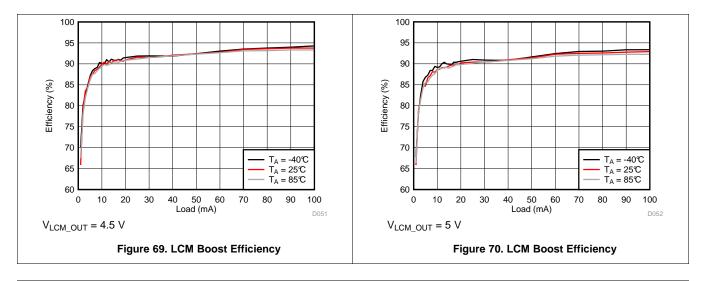

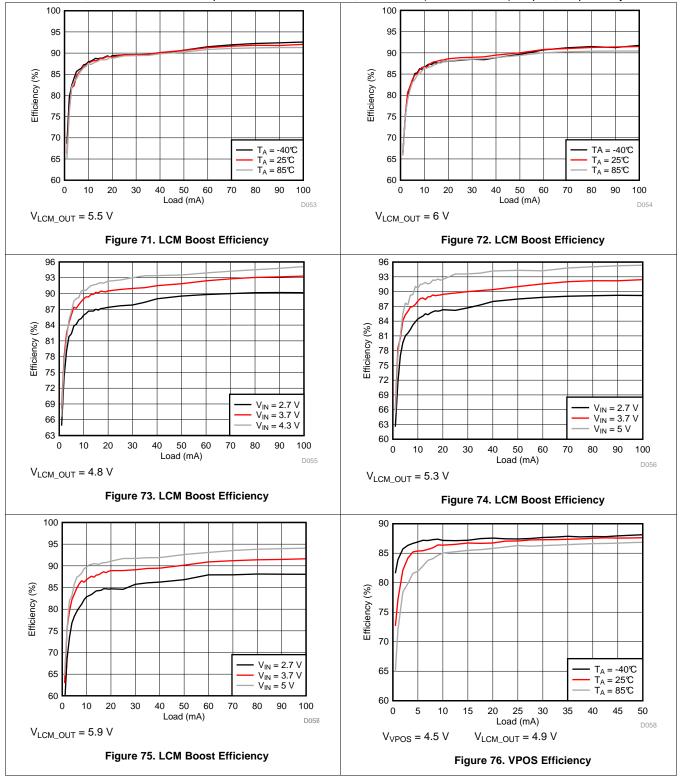

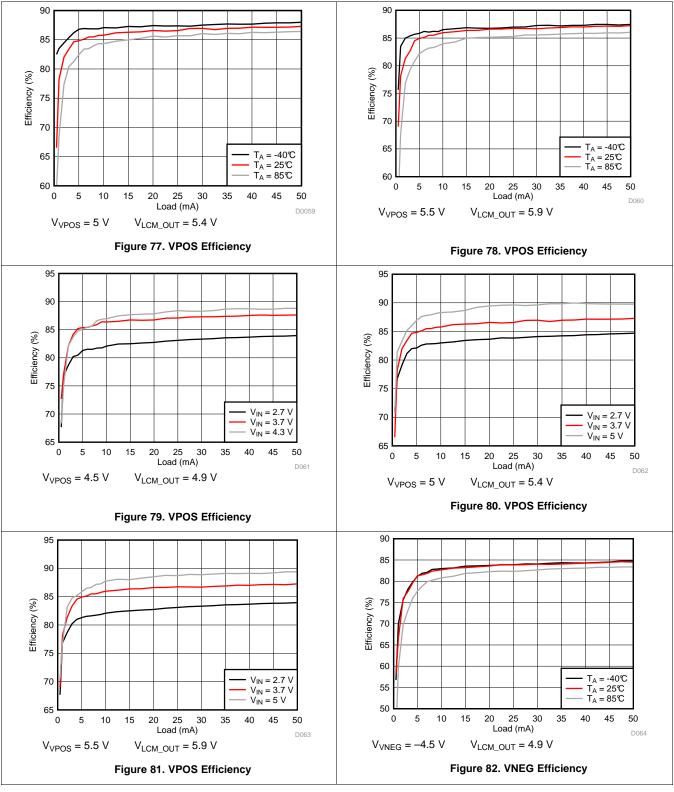

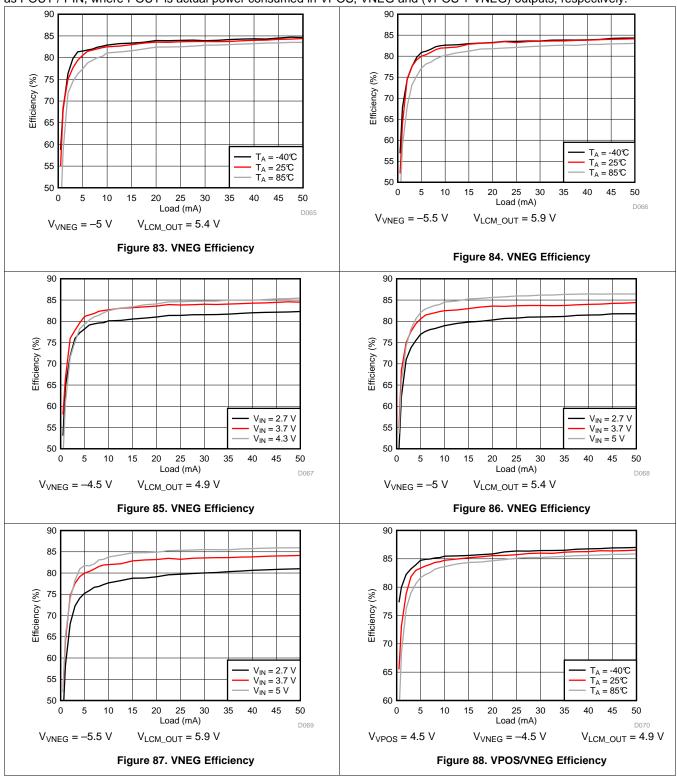

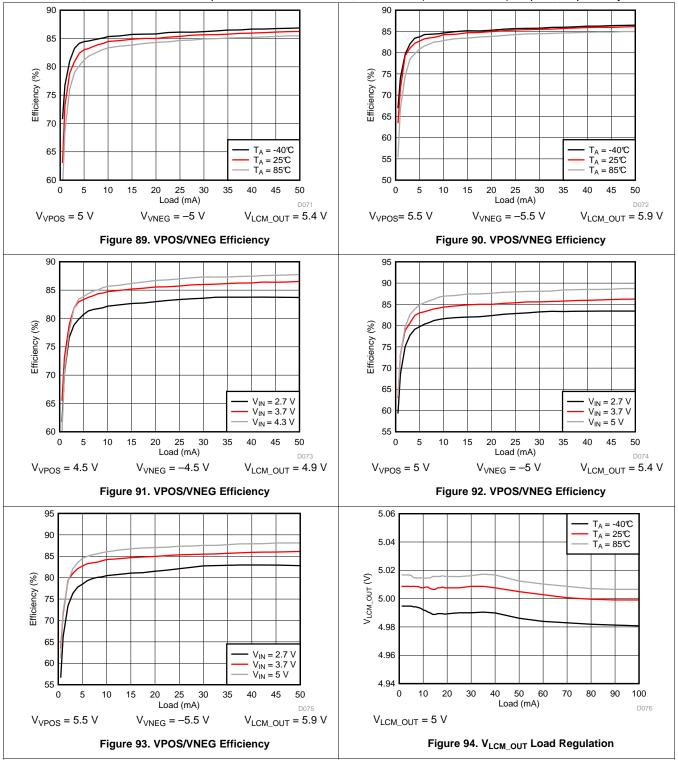

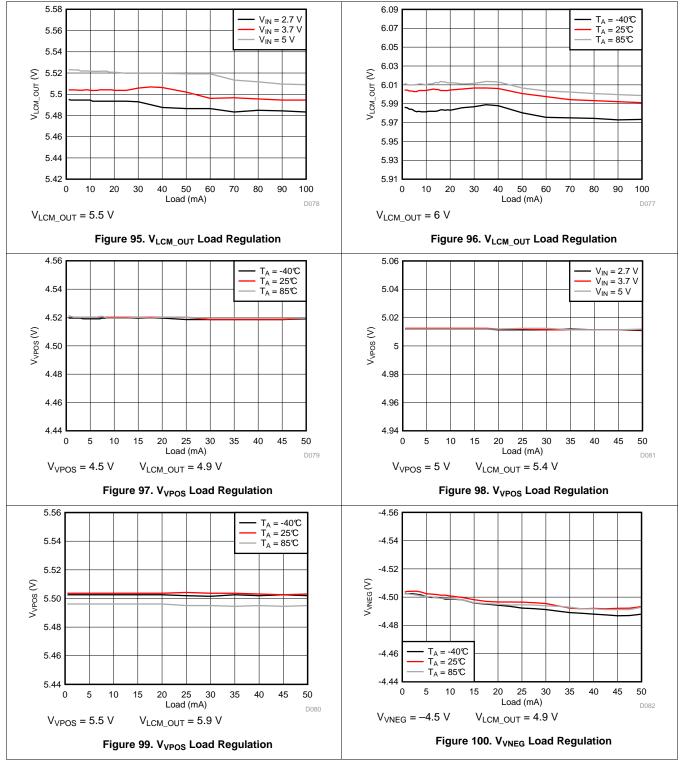

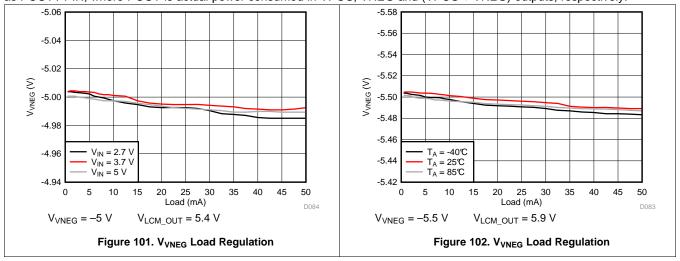

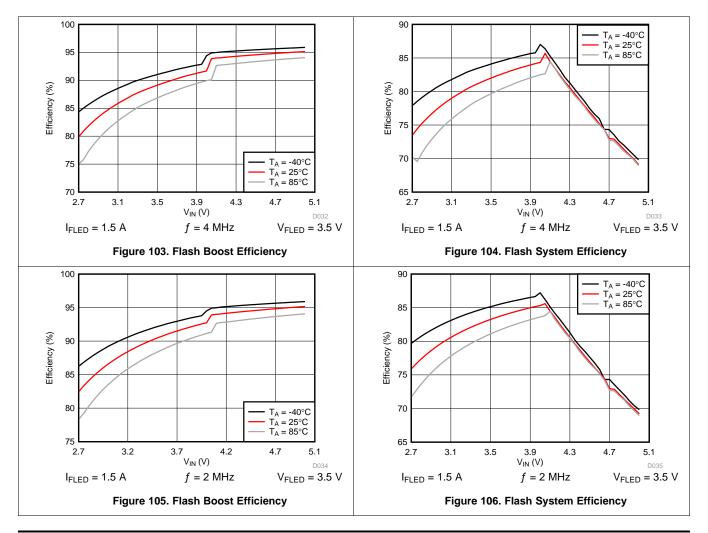

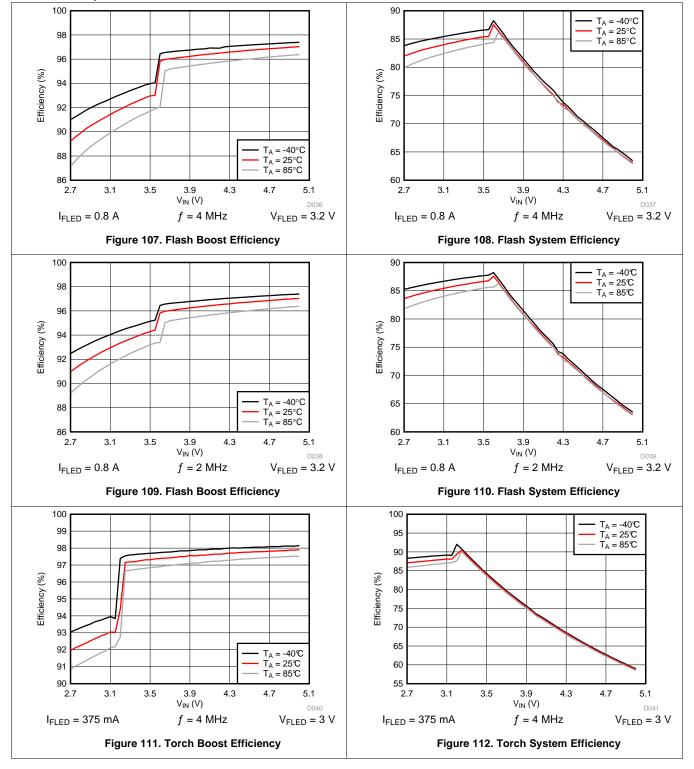

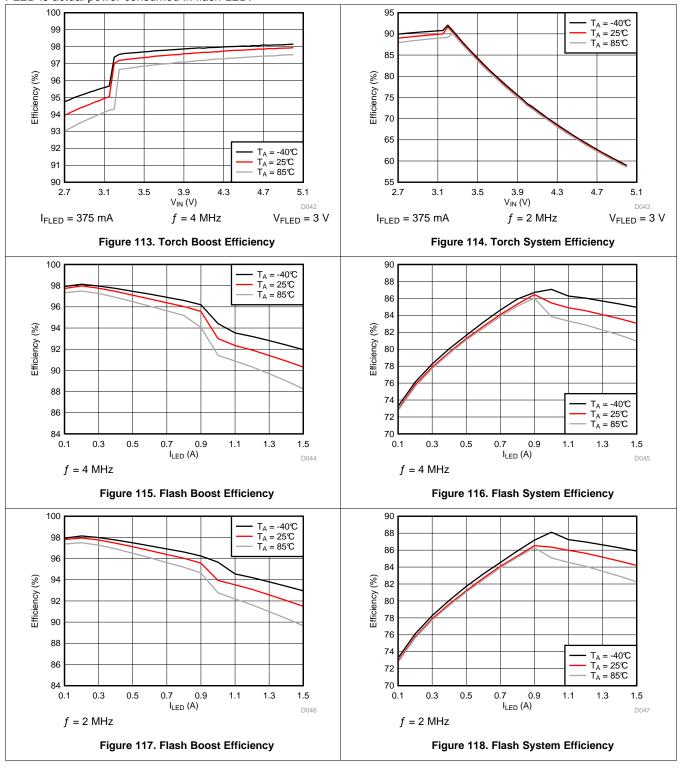

Ambient temperature is 25°C and  $V_{\rm IN}$  is 3.7 V unless otherwise noted.

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

Ambient temperature is 25°C and  $V_{\text{IN}}$  is 3.7 V unless otherwise noted.

www.ti.com.cn ZHCSDN2-APRIL 2015

# **Typical Characteristics (continued)**

Ambient temperature is 25°C and  $V_{\text{IN}}$  is 3.7 V unless otherwise noted.

# TEXAS INSTRUMENTS

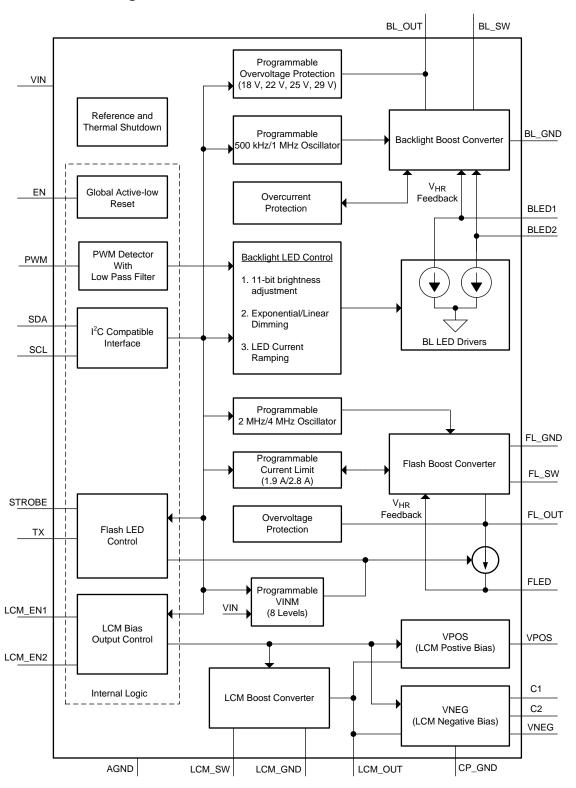

# 7 Detailed Description

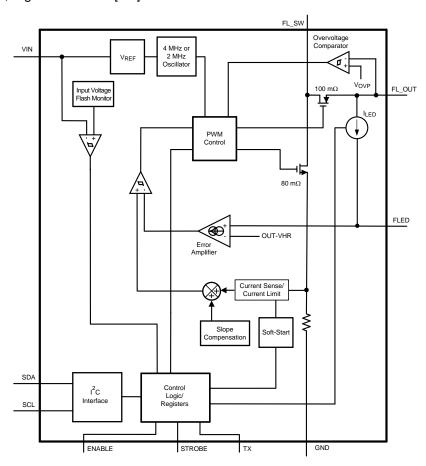

#### 7.1 Overview

The LM3632A is a single-chip complete backlight, LCM power and flash solution. The device operates over the 2.7-V to 5-V input voltage range.

The LM3632A can drive up to two LED strings with up to 8 LEDs each (up to 28 V typical), with a maximum of 25 mA per string. The power for the LED strings comes from a integrated asynchronous backlight boost converter with two selectable switching frequencies to optimize performance or solution area. LED current is regulated by two low-headroom current sinks. Automatic voltage scaling adjusts the output voltage of the backlight boost converter to minimize the LED driver headroom voltage. The 11-bit LED current is set via an I<sup>2</sup>C interface, via a logic level PWM input, or a combination of both.

The LCM bias power portion of the LM3632A consists of a synchronous LCM bias boost converter, inverting charge pump, and an integrated LDO. The LCM positive bias voltage  $V_{POS}$  (up to 6 V) is post-regulated from the LCM bias boost converter output voltage. The LCM negative bias voltage  $V_{NEG}$  (down to –6 V) is generated from the LCM bias boost converter output using a regulated inverting charge pump.

The flash driver consists of a synchronous boost converter and a 1.5-A constant current LED driver. The highside current source allows for grounded cathode LED operation providing flash current up to 1.5 A. An adaptive regulation method ensures the current source remains in regulation and maximizes efficiency.

The LM3632A flexible control interface consists of an EN active low reset input, LCM\_EN1 and LCM\_EN2 inputs for  $V_{POS}$  and  $V_{NEG}$  enable control, PWM input for content adaptive backlight control (CABC), a TX flash interrupt input, and an  $I^2C$ -compatible interface.

Additionally, there are two flag registers with flag and status bits. The user can read back these registers and determine if a fault or warning message has been generated.

# 7.2 Functional Block Diagram

# TEXAS INSTRUMENTS

#### 7.3 Features Description

# 7.3.1 Backlight

The backlight is enabled if the BL\_EN bit (bit[0] in reg[0x0A]) is set to '1', at least one of the backlight sink outputs is enabled (bit[3] and/or bit[4] in reg[0x0A]), and the brightness value is different than 0. When the brightness value is 0 or the BL\_EN bit is '0', the backlight is disabled.

#### 7.3.1.1 Brightness Control

Brightness can be controlled either by the I<sup>2</sup>C brightness register or a combination of the external PWM control and the I<sup>2</sup>C brightness register. The backlight truth table is shown in Table 1.

When controlling brightness through I<sup>2</sup>C, registers 0x04 and 0x05 are used. Registers 0x04 and 0x05 hold the 11-bit brightness data. Register 0x04 contains the 3 LSBs, and register 0x05 contains the 8 MSBs. The LED current transitions to the new level after a write is done to register 0x05.

When controlling brightness through I<sup>2</sup>C, setting the brightness value to '0' shuts down the backlight. When controlling the brightness with PWM input, if PWM input is low for a certain period of time (25 ms typ.), the backlight shuts down. When using the combination of a PWM input and the I<sup>2</sup>C register, either option shuts down the backlight.

| EN PIN | BL_EN<br>0x0A[0] | BLED1_EN<br>0x0A[4] | BLED2_EN<br>0x0A[3] | PWM_EN<br>0x09[6] | ACTION                                                  |

|--------|------------------|---------------------|---------------------|-------------------|---------------------------------------------------------|

| 0      | Х                | Х                   | Х                   | Х                 | Shutdown                                                |

| 1      | 0                | Х                   | Х                   | Х                 | Standby                                                 |

| 1      | 1                | 0                   | 0                   | Х                 | Bias enable                                             |

| 1      | 1                | 1                   | 0                   | 0                 | BLED1 ramp to target current                            |

| 1      | 1                | 0                   | 1                   | 0                 | BLED1 & BLED2 ramp-to-target current                    |

| 1      | 1                | 1                   | 1                   | 0                 | BLED1 & BLED2 ramp-to-target current                    |

| 1      | 1                | 1                   | 0                   | 1                 | BLED1 ramp to (target current × PWM duty cycle)         |

| 1      | 1                | 0                   | 1                   | 1                 | BLED1 & BLED2 ramp to (target current × PWM duty cycle) |

| 1      | 1                | 1                   | 1                   | 1                 | BLED1 & BLED2 ramp to (target current × PWM duty cycle) |

**Table 1. Backlight Truth Table**

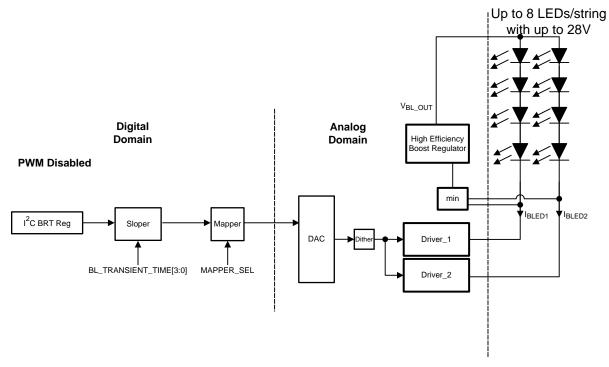

#### 7.3.1.1.1 LED Current with PWM Disabled

When LED brightness is controlled from the I<sup>2</sup>C brightness registers, the 11-bit brightness data directly controls the LED current in BLED1 and BLED2. LED mapping can be selected as either linear or exponential. When this mode is selected, setting the PWM input to 0 does not disable the backlight.

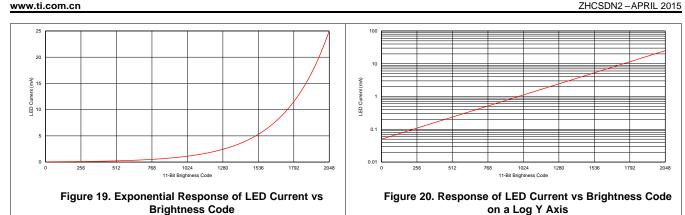

With exponential mapping the 11-bit code-to-current response is approximated by the equation:

$$I_{LED} = 50 \,\mu\text{A} \times 1.003040572^{I2C \, BRGT \, CODE} \, (for \, codes > 0)$$

(1)

Equation 1 is valid for I<sup>2</sup>C brightness codes between 1 and 2047. Code 0 disables the backlight. The Code-to-LED current response realizes a 0.304% change in LED current per LSB of brightness code.

Figure 19 and Figure 20 detail the exponential response of the LED current vs. brightness code. Figure 19 shows the response on a linear Y axis while Figure 20 shows the response on a log Y axis to show the low current levels at the lower codes.

With linear mapping the 11-bit code to current response is approximated by the equation:

$$I_{IED} = 37.8055 \,\mu\text{A} + 12.1945 \,\mu\text{A} \times I2C \,\text{BRGT CODE} \,(\text{for codes} > 0)$$

(2)

Equation 2 is valid for codes between 1 and 2047. Code 0 disables the backlight.

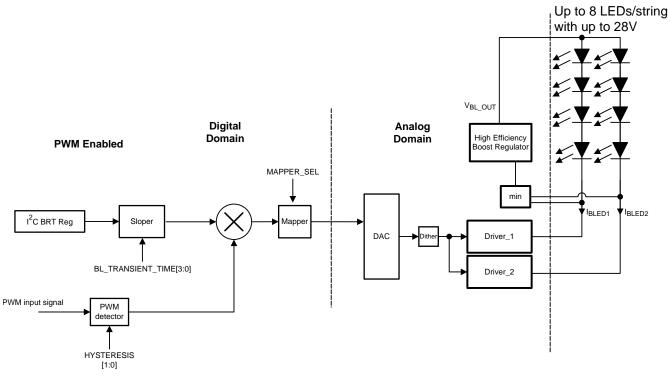

#### 7.3.1.1.2 LED Current with PWM Enabled

When LED brightness is controlled with the combination of I<sup>2</sup>C register and the PWM duty cycle, the multiplication result of I<sup>2</sup>C register value and PWM duty cycle controls the LED current in BLED1 and BLED2. LED mapping can be selected as either linear or exponential.

With exponential mapping the multiplication result-to-current response is approximated by the equation:

$$I_{LED} = 50 \,\mu\text{A} \times 1.003040572^{I2C} \,\text{BRGT CODE} \times \text{PWM D/C}$$

(3)

Equation 3 is valid for brightness values other than 0. Brightness value 0 (PWM D/C or I2C BRGT CODE) disables the backlight.

With linear mapping the PWM duty cycle-to-current response is approximated by the equation:

$$I_{LED} = 37.8055 \,\mu\text{A} + (12.1945 \,\mu\text{A} \times I2C \,\text{BRGT CODE} \times \text{PWM D/C})$$

(4)

Equation 4 is valid for brightness values other than 0. Brightness value 0 (PWM D/C or I2C BRGT CODE) disables the backlight.

Figure 21. Brightness Control with PWM Bit Disabled

Figure 22. Brightness Control with PWM Bit Enabled

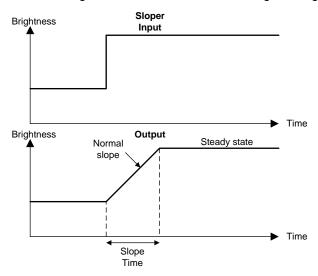

#### 7.3.1.2 Sloper

www.ti.com.cn

The sloper smooths the transition from one brightness value to another. Slope time can be adjusted from 0 ms to 8000 ms with BL\_TRANS[3:0] bits (see Table 9 for details). Transient time is used for sloping up and down. Transient time always remains the same regardless of the amount of change in brightness.

Figure 23. Sloper

#### 7.3.1.3 Mapper

The mapper block maps the digital word set for the LED driver into current code. The user can select whether the mapping is exponential or linear with the BLED\_MAP bit, register 0x02 bit[4].

Exponential control is tailored to the response of the human eye such that the perceived change in brightness during ramp up or ramp down is linear.

#### 7.3.1.4 PWM Input

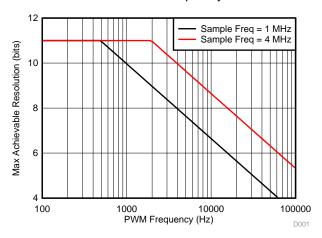

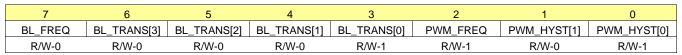

The PWM detector block measures the duty cycle in the PWM pin. The PWM period is measured from the rising edge to the next rising edge. PWM polarity can be changed with bit PWM\_CONFIG, register 0x02 bit[3]. The sample rate for the PWM input can be set to 1 MHz or 4 MHz with bit PWM\_FREQ, register 0x03 bit[2]. The choice of sample rate depends on three factors:

- 1. Required PWM resolution (input duty cycle to brightness code, with 11 bits max)

- 2. PWM input frequency

- 3. Efficiency

The PWM input block timeout is 25 ms for 1-MHz sampling frequency and 3 ms for 4-MHz sampling frequency, measured from the last rising edge. This should be taken into account for 0% and 100% brightness settings (for setting 100% brightness, the high level of PWM input signal should be greater than the PWM input timeout) and for selecting the minimum PWM input signal frequency.

#### 7.3.1.5 PWM Minimum On/Off Time

The minimum PWM input signal allowed for low and high pulse width is 6  $\mu$ s for 1-MHz sampling frequency and 1.5  $\mu$ s for 4-MHz sampling frequency. This should be taken into account when selecting the PWM input signal frequency and maximum or minimum duty cycle. For example, if the PWM input signal frequency is 2 kHz (500  $\mu$ s) and the 4-MHz sampling frequency is used, the maximum allowed on-time is:  $(500 - 1.5) \mu s = 498.5 \mu s$ . The maximum duty cycle allowed is  $100 \times (498.5/500) = 99.7\%$ . By comparison, following similar calculations, with a PWM input signal frequency of 20 kHz the maximum allowed duty cycle is 97%.

#### NOTE

If the Minimum Off Time requirement is violated, there may be a range of duty cycle values in which flickering of the LEDs may occur or the LEDs may turn off completely. As the duty cycle increases farther and approaches 100%, the LEDs will turn on at full brightness level. This is due to the algorithm used by the device to detect 100% duty cycle in conjunction with the minimum low pulse width requirement discussed in this section. To avoid LED flickering and/or the LEDs turning off at high PWM duty cycles, the PWM Minimum On/Off Time requirement should be met.

# 7.3.1.6 PWM Resolution and Input Frequency Range

The PWM input resolution depends on the input signal frequency. To achieve the full 11-bit maximum resolution of PWM duty cycle to the LED brightness code, the input PWM duty cycle must be  $\geq$  11 bits, and the PWM sample period (1/ $f_{SAMPLE}$ ) must be smaller than the minimum PWM input pulse width. Figure 24 shows the possible brightness code resolutions based on the input PWM frequency. The minimum recommended PWM frequency is 100 Hz, and maximum recommended PWM frequency is 20 kHz.

Figure 24. PWM Resolution and PWM Input Frequency

#### 7.3.1.7 PWM Hysteresis

To prevent jitter in the input PWM signal from feeding through the PWM path and causing oscillations in the LED current, the LM3632A offers 4 programmable PWM hysteresis settings. Hysteresis works by forcing a specific number of 11-bit LSB code transitions to occur in the input duty cycle before the LED current changes. Table 9 describes the hysteresis. Hysteresis only applies during the change in direction of brightness currents. Once the change in direction has taken place, the PWM input must overcome the required LSB(s) of the hysteresis setting before the brightness change takes effect. Once the initial hysteresis has been overcome and the direction in brightness change remains the same, the PWM-to-current response changes with no hysteresis. Hysteresis is selected with the PWM\_HYST bits, register 0x03 bits[1:0]. Changing the hysteresis value is recommended when PWM input frequency increases.

#### 7.3.1.8 PWM Timeout

The LM3632A PWM timeout feature turns off the backlight boost output when the PWM input is enabled and there is no PWM pulse detected. The timeout duration depends on the PWM sample rate setting and defines the minimum supported PWM input frequency. Table 2 summarizes the sample rate, timeout, and minimum supported PWM frequency.

Table 2. PWM Timeout and Minimum Supported PWM Frequency vs PWM Sample Rate

| SAMPLE RATE | TIMEOUT | MINIMUM SUPPORTED PWM FREQUENCY |  |  |

|-------------|---------|---------------------------------|--|--|

| 1 MHz       | 25 msec | 48 Hz                           |  |  |

| 4 MHz       | 3 msec  | 400 Hz                          |  |  |

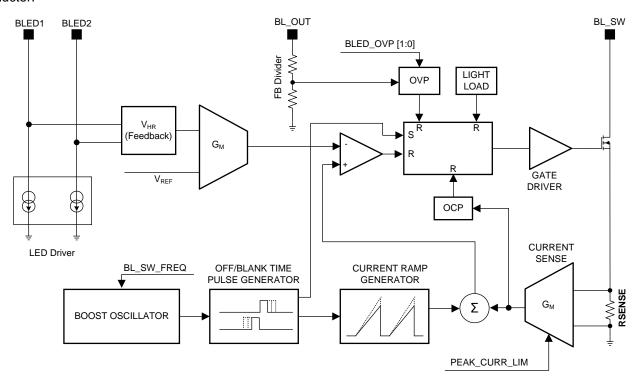

#### 7.3.1.9 Backlight Boost Converter

The high voltage required by the LED strings is generated with an asynchronous backlight boost converter. An adaptive voltage control loop automatically adjusts the output voltage based on the voltage over the LED drivers BLED1 and BLED2.

The LM3632A has two switching frequency modes, 500 kHz and 1 MHz. These are set via the BL\_FREQ Select bit, register 0x03 bit[7]. Operation in low-frequency mode results in better efficiency at lighter load currents due to the decreased switching losses. Operation in high-frequency mode gives better efficiency at higher load currents due to the reduced inductor current ripple and the resulting lower conduction losses in the MOSFETs and inductor.

Figure 25. Backlight Boost Block Diagram

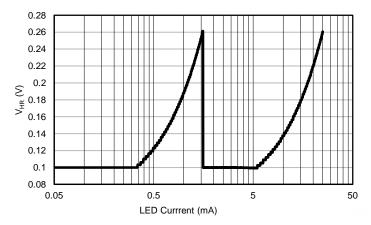

#### 7.3.1.9.1 Headroom Voltage

In order to optimize efficiency, the LED driver-regulated headroom voltage ( $V_{HR}$ ) changes with the programmed LED current. This allows for increased solution efficiency as the dropout voltage of the LED driver changes. Furthermore, in order to ensure that both current sinks remain in regulation when there is a mismatch in string voltages, the minimum headroom voltage between  $V_{BLED1}$  and  $V_{BLED2}$  becomes the regulation point for the boost converter. For example, if the LEDs connected to BLED1 require 25 V at the programmed current, and the LEDs connected to BLED2 require 25.5 V at the programmed current, the voltage at BLED1 is  $V_{HR}$  + 0.5 V, and the voltage at BLED2 is  $V_{HR}$ . In other words, the cathode of the highest voltage LED string becomes the boost output regulation point.

Figure 26. Regulated Headroom vs LED Current

#### 7.3.1.9.2 Backlight Protection and Faults

#### 7.3.1.9.2.1 Overvoltage Protection (OVP) and Open-Load Fault Protection

The LM3632A provides an OVP that monitors the LED boost output voltage ( $V_{BL\_OUT}$ ) and protects BL\_OUT and BL\_SW from exceeding safe operating voltages. The OVP threshold can be set to 18 V, 22 V, 25 V or 29 V with register 0x02 bits[7:5]. Once an OVP event has been detected, the BL\_OVP flag is set in the Flags1 register, and the subsequent behavior depends on the state of bit BL\_OVP\_SET in the Enable Register: If BL\_OVP\_SET is set to '0', as soon as  $V_{BL\_OUT}$  falls below the backlight OVP threshold, the LM3632A begins switching again. If BL\_OVP\_SET is set to '1' and the device detects three occurrences of  $V_{BL\_OUT} > V_{OVP\_BL}$  while any of the enabled current sink headroom voltages drops below 40 mV, the BL\_OVP flag is set, the Backlight Enable bit is cleared, and the LM3632A enters standby mode. When the device is shut down due to a BL\_OVP fault the Flags1 register must be read back before the device can be reenabled.

#### 7.3.1.9.2.2 Overcurrent Protection (OCP) and Overcurrent Protection Flag

The LM3632A has an OCP threshold of 1 A. The OCP threshold is a cycle-by-cycle current limit detected in the low-side NFET. Once the threshold is reached, the NFET turns off for the remainder of the switching period. If enough overcurrent events occur, the BL\_OCP flag (register 0x10 bit[0]) is set. The flag can be cleared upon a readback of register 0x10. To avoid transient conditions from inadvertently setting the BL\_OCP flag, a pulse density counter monitors BL\_OCP events over a 128-µs time window. If 8 consecutive 128-µs windows of at least 2 OCP events are detected, the BL\_OCP flag is set.

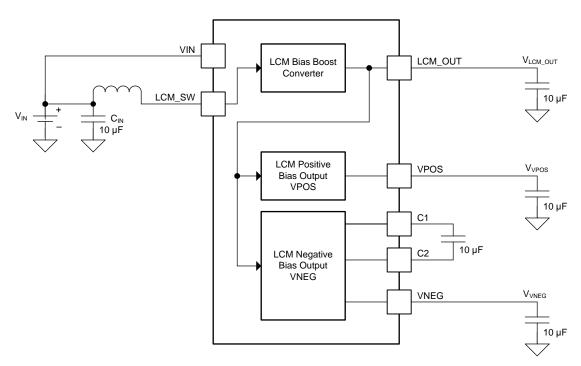

#### 7.3.2 LCM Bias

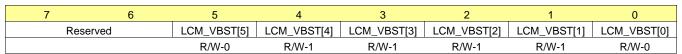

#### 7.3.2.1 Display Bias Boost Converter ( $V_{VPOS}$ , $V_{VNEG}$ )

A single high-efficiency boost converter provides a positive voltage rail,  $V_{LCM\_OUT}$ , which serves as the power rail for the LCM VPOS and VNEG outputs.

- The  $V_{VPOS}$  output LDO has a programmable range from 4 V up to 6 V with 50-mV steps and can supply up to 50 mA.

- The V<sub>VNEG</sub> output is generated from a regulated, inverting charge pump and has an adjustable range of -6 V up to -4 V with 50-mV steps and a maximum load of 50 mA.

Boost voltage also has a programmable range from 4.5 V up to 6.4 V with 50-mV steps. Please refer to Table 19, Table 20 and Table 21 for  $V_{LCM\_OUT}$ ,  $V_{VPOS}$  and  $V_{VNEG}$  voltage settings. When selecting a suitable boost-output voltage, the following estimation can be used:  $V_{LCM\_OUT} = max(V_{VPOS}, |V_{VNEG}|) + V_{HR}$ , where  $V_{HR} = 300$  mV for lower currents and 400 mV for higher currents. When the device input voltage ( $V_{IN}$ ) is greater than the programmed LCM boost output voltage, the boost voltage goes to  $V_{IN} + 100$  mV.  $V_{VPOS}$ , and  $V_{VNEG}$  voltage settings cannot be changed while they are enabled. While the  $V_{LCM\_OUT}$  target changes immediately upon a register write,  $V_{VPOS}$  and  $V_{VNEG}$  register setting targets take effect only after the outputs are disabled and reenabled.

Figure 27. LCM Boost Block Diagram

The LCM Bias outputs can be controlled either by pins LCM\_EN1 and LCM\_EN2 or register bits VPOS\_EN and VNEG\_EN, register 0x0C bits[2:1]. Setting bit EXT\_EN, register 0x0C bit[0], to '0' allows pins LCM\_EN1 and LCM EN2 to control VPOS and VNEG, respectively, while setting this bit to '1' yields control to bits VPOS EN and VNEG EN. Refer to Table 3 for LCM bias control information.

LCM EN2 LCM EN1 **EXT EN** VNEG EN VPOS EN **AUTO SEQ** WAKE-UP **EN PIN ACTION** 0x0C[0] 0x0C[1] 0x0C[2] 0x0C[5] PIN PIN 0x0C[7] Χ 0 Χ Χ Χ Χ Shutdown Χ Χ 0 0 1 Χ Χ Χ Standby 1 0 1 1 Χ Χ External VPOS 0 Χ 0 1 1 0 1 Χ Χ Χ 0 External VNEG External VPOS and VNEG 1 1 1 1 Х Х 0 0 Independent External VPOS and VNEG 1 1 1 1 Χ Χ 1 0 Auto Sequence Χ Χ 0 0 0 Χ 0 Standby 1 Χ 0 0 Χ 0 I<sup>2</sup>C VPOS 1 Χ 1 Χ Χ I<sup>2</sup>C VNEG 1 0 1 0 Χ 0 I<sup>2</sup>C VPOS and VNEG Χ Χ 0 0 0 1 1 1 Independent I<sup>2</sup>C VPOS and VNEG Χ 0 1 Χ 0 1 1 1 Auto Sequence 0 Χ Χ Χ Χ Standby 1 Χ 1 1 1 Χ Χ 0 0 Χ 1 Standby Χ Χ 0 Χ Wake-up VPOS 1 1 1 1 1 1 Χ Χ 1 0 Χ 1 Wake-up VNEG Wake-up VPOS and

**Table 3. LCM Bias Truth Table**

Χ

Χ

1

1

Χ

1

VNEG

1

# TEXAS INSTRUMENTS

#### 7.3.2.2 Auto Sequence Mode

If this mode is selected the LM3632A controls the turn-on and turn-off of VPOS and VNEG as shown in Figure 28.

Figure 28. Auto Sequence Timing

#### 7.3.2.3 Wake-up Mode

If Wake-up mode is selected the LM3632A allows on/off control of both VPOS and VNEG with only one external pin (LCM\_EN2). Any combination of VPOS, VNEG, or both can be turned on based on the state of bits VPOS\_EN and VNEG\_EN in register 0x0C. In this mode the internal shutdown timing of the VPOS and VNEG blocks is modified to allow for lower quiescent current in standby mode, therefore reducing the average current consumption during a sequence of on/off events.

#### 7.3.2.4 Active Discharge

An optional active discharge is available for the VPOS and VNEG output rails. An internal switch resistance for this discharge function is implemented on each output rail. The VPOS active discharge function is enabled with register 0x0C bit[4] and the VNEG active discharge with register 0x0C bit[3].

#### NOTE

To avoid an unsafe operating condition when the active discharge function is enabled, a minimum delay of 1 millisecond needs to be maintained between disabling and reenabling of the VNEG output.

#### 7.3.2.5 LCM Bias Protection and Faults

The LCM Bias block of the LM3632A provides four protection mechanisms in order to prevent damage to the device. Note that none of these have any effect on backlight or flash operation.

#### 7.3.2.5.1 LCM Overvoltage Protection

The LM3632A provides OVP that monitors the LCM Bias boost output voltage (V<sub>LCM\_OUT</sub>) and protects LCM\_OUT and LCM\_SW from exceeding safe operating voltages. The OVP threshold is set to 7 V (typical). If an LCM Bias overvoltage condition is detected, the LCM\_OVP flag, register 0x10 bit[5], is set. The flag can be cleared with an I<sup>2</sup>C read back of the register. An LCM OVP condition will not cause the LCM Bias to shut down; it is a report-only flag.

#### 7.3.2.5.2 VNEG Overvoltage Protection

If the charge-pump voltage goes 250 mV (typical) below its target set-point, the LM3632A provides a mechanism for preventing the voltage from increasing even further and damaging the device and sets the VNEG\_OVP flag, register 0x10 bit[4]. The flag can be cleared with an I<sup>2</sup>C readback of the register. A VNEG OVP condition will not cause the charge pump to shut down; it is a report-only flag.

#### NOTE

The VNEG\_OVP flag may get set during VNEG start-up under light load and low VNEG voltage settings due to VNEG voltage undershoot. After the flag is cleared via register read back, the LM3632A detects VNEG OVP conditions properly.

#### 7.3.2.5.3 VPOS Short Circuit Protection

If the current at VPOS exceeds 80 mA (typical), the LM3632A sets the VPOS\_SHORT flag, register 0x10 bit[3]. A readback of register 0x10 is required to clear the flag. A VPOS\_SHORT condition will not cause the LCM Bias to shut down; it is a report-only flag.

#### 7.3.2.5.4 VNEG Short Circuit Protection

If the voltage at VNEG goes within 750 mV (typical) from ground, the LM3632A sets the VNEG\_SHORT flag, register 0x10 bit[2]. A readback of register 0x10 is required to clear the flag. A VNEG\_SHORT condition will not cause the LCM Bias to shut down; it is a report-only flag.

#### 7.3.3 Flash

#### 7.3.3.1 Flash Boost Converter

The LM3632A incorporates a high-efficiency synchronous current-mode PWM boost converter that switches and boosts the output to maintain at least  $V_{HR}$  across the flash current source (FLED) over the 2.7-V to 5.5-V input voltage range. The flash boost has two switching frequency modes, 2-MHz and 4-MHz. These are set via the FL FREQ Select bits, register 0x07 bits[7:6].

Figure 29. Flash Boost Block Diagram

# TEXAS INSTRUMENTS

#### 7.3.3.2 Start-Up (Enabling The Device)

The flash LED output (FLED) can be enabled in flash or torch mode with the Enable Register and the STROBE pin. The state of bit STROBE\_EN, register 0x09 bit[4], determines if the FLED output is enabled by bit[1] of register 0x0A or the STROBE pin. Table 4 contains the details for flash operation control. While a positive edge is required at the STROBE pin in order to initiate a Torch or Flash event, the STROBE pin is level sensitive. That means that the event is terminated as soon as the STROBE pin transitions low.

**Table 4. Flash Truth Table**

| EN PIN | STROBE_EN<br>0x09[4] | STROBE<br>PIN | FLASH_EN<br>0x0A[1] | FLASH_MODE<br>0x0A[2] | ACTION    |

|--------|----------------------|---------------|---------------------|-----------------------|-----------|

| 0      | X                    | X             | X                   | X                     | Shutdown  |

| 1      | 0                    | X             | 0                   | X                     | Standby   |

| 1      | 0                    | X             | 1                   | 0                     | Int Torch |

| 1      | 0                    | X             | 1                   | 1                     | Int Flash |

| 1      | 1                    | 0             | 0                   | X                     | Standby   |

| 1      | 1                    | 0             | 1                   | X                     | Standby   |

| 1      | 1                    | pos edge      | 0                   | X                     | Standby   |

| 1      | 1                    | pos edge      | 1                   | 0                     | Ext Torch |

| 1      | 1                    | pos edge      | 1                   | 1                     | Ext Flash |

On start-up, when  $V_{OUT}$  is less than  $V_{IN}$  the internal synchronous PFET turns on as a current source and delivers 200 mA (typical) to the output capacitor. During this time the current source (LED) is off. When the voltage across the output capacitor reaches 2.2 V (typical) the current source turns on. At turn-on the current source steps through each flash or torch level until the target LED current is reached. This gives the device a controlled turn-on and limits inrush current from the  $V_{IN}$  supply.

#### 7.3.3.3 Pass Mode

The LM3632A flash boost starts up in pass mode and stays there until boost mode is needed to maintain regulation. If the voltage difference between  $V_{FL\_OUT}$  and  $V_{FLED}$  falls below  $V_{HR}$ , the device switches to boost mode. In pass mode the boost converter does not switch, and the synchronous PFET turns fully on bringing  $V_{FL\_OUT}$  up to  $V_{IN} - I_{FLED} \times RPMOS$ . In pass mode the inductor current is not limited by the peak current limit.

#### 7.3.3.4 Flash Mode

In flash mode, the LED current source (FLED) provides 15 target current levels from 100 mA to 1500 mA in 100 mA increments. The flash currents are adjusted via register 0x06 (see Table 12 for details). Once the flash sequence is activated the current source (FLED) ramps up to the programmed flash current by stepping through all current steps until the programmed current is reached. The headroom in the current source is regulated to provide 100 mA to 1.5 A to the output. Whether the device is enabled in flash mode through the Enable Register or through the STROBE pin, the Flash Enable bit in the Enable Register is cleared at the completion of the flash event and needs to be re-written in order to perform the next internal or external flash event.

#### 7.3.3.5 Torch Mode

In torch mode, the LED current source (FLED) provides 15 target current levels from 25 mA to 375 mA in 25-mA increments. The torch currents are adjusted via register 0x06 (see Table 12 for details). Once the torch sequence is activated the current source (FLED) ramps up to the programmed Torch current by stepping through all current steps until the programmed current is reached. Torch mode is not affected by Flash Timeout or by a TX Interrupt event.

#### 7.3.3.6 Power Amplifier Synchronization (TX)

The TX pin is a Power Amplifier Synchronization input. This is designed to reduce the flash FLED current and thus limit the battery current during high battery-current conditions such as PA transmit events. When the LM3632A is engaged in a flash event, and the TX pin is pulled high, the FLED current is forced into torch mode at the programmed torch current setting. If the TX pin is then pulled low before the flash pulse terminates, the FLED current returns to the previous flash current level. At the end of the flash time-out, whether the TX pin is high or low, the FLED current is turned off.

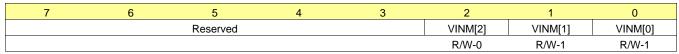

7.3.3.7 VIN Monitor

# The LM3632A has the ability to adjust the flash current based upon the voltage level present at the VIN pin. The adjustable VINM threshold ranges from 2.6 V to 3.3 V in 100-mV steps. The Flags1 Register (0x0B) has the fault flag set when the input voltage crosses the VINM value. Additionally, the VINM threshold sets the input voltage boundary that forces the device to either transition into torch mode at the programmed torch current setting or turn off the FLED current for the remaining flash duration. This decision is made based on the status of bit VINM\_MODE, register 0x09 bit[1]. In order to re-enable the LM3632A in torch or flash mode the VINM flag has to be cleared. If the VINM flag is tripped during flash current ramp-up, and VINM mode is set to torch, the FLED current is reduced not to the torch current setting but to the same percentage of the last flash current that was reached during fash current ramp-up. For example, if the flash current setting is 1 A, the torch current setting is 100 mA and the maximum flash current that was reached before the VINM threshold was crossed is 700 mA, the device will transition the flash current to 70 mA (70% of 100 mA).

#### 7.3.3.8 Flash Fault Protections

#### 7.3.3.8.1 Fault Operation

If the LM3632A enters a fault condition during flash, the device sets the appropriate flag in the Flags1 and Flags2 Registers (0x0B and 0x10) and places the flash block into standby by clearing the FLASH\_EN bit in the Enable Register. The flash block remains in shutdown until an I<sup>2</sup>C read of the Flag Registers is completed. Upon clearing the flags/faults, flash can be restarted. If the fault is still present, the LM3632A re-enters the fault state and enters standby again. Flash faults have no effect on Backlight or LCM control.

#### 7.3.3.8.2 Flash Time-Out

The Flash Time-Out period sets the amount of time that the Flash Current is being sourced from the current source (FLED). The LM3632A has 32 timeout levels ranging from 32 ms to 1024 ms (see Table 13 for more detail). Once a flash event is completed, the FTO flag in Flags1 register (register 0x0B bit[1]) is set. If a flash event is activated via the STROBE pin and STROBE transitions low after the end of the programmed flash timeout, the flash event is terminated at the programmed flash timeout, and the FTO flag is set. If the STROBE pin transitions low before the end of the programmed flash timeout, the flash event is terminated, and the FTO flag is not set.

#### 7.3.3.8.3 Overvoltage Protection (OVP)

The flash output voltage is limited to typically 4.9 V (see  $V_{\text{OVP}}$  Spec in *Electrical Characteristics*). In situations such as an open FLED, the LM3632A tries to raise the output voltage in order to keep the FLED current at its target value. When  $V_{\text{FL}\_\text{OUT}}$  reaches 4.9 V (typical), the overvoltage comparator trips and turns off the internal NFET. When  $V_{\text{FL}\_\text{OUT}}$  falls below the  $V_{\text{OVP}}$  Off threshold, the LM3632A begins switching again. The Flash Enable bit is cleared, and the FLASH\_OVP flag is set, when an OVP condition is present for three rising OVP edges. This prevents momentary OVP events from forcing the device to shut down.

#### 7.3.3.8.4 Current Limit

The LM3632A features two selectable flash inductor current limits that are programmable through the  $I^2C$ -compatible interface. When the inductor current limit is reached, the device terminates the charging phase of the switching cycle. Switching resumes at the start of the next switching period. If the overcurrent condition persists, the device operates continuously in current limit. Since the current limit is sensed in the NMOS switch, there is no mechanism to limit the current when the device operates in pass mode (current does not flow through the NMOS in pass mode). In boost mode or pass mode if  $V_{FL_OUT}$  falls below 2.3 V, the device stops switching, and the PFET operates as a current source limiting the current to 200 mA. This prevents damage to the LM3632A and excessive current draw from the battery during output short-circuit conditions. The Flash Enable bit is not cleared upon a current limit event, but the FLASH\_OCP flag (register 0x10 bit[1]) is set.

# TEXAS INSTRUMENTS

#### 7.3.3.8.5 FLED and/or FL\_OUT Short Fault

The FLED short flag (FLED\_SHORT) reads back a '1' if the device is active in flash or torch mode and the FLED output experiences a short condition. The flash output short flag (FOUT\_SHORT) reads back a '1' if the device is active in flash or torch mode and the flash boost output experiences a short condition. A FLED short condition is determined if the voltage at FLED goes below 500 mV (typical) while the device is in torch or flash mode. There is a deglitch time of 256 µs before the LED Short flag is valid and a deglitch time of 2.048 ms before the FL\_OUT Short flag is valid. The FLED Short Fault can only be reset to '0' by removing power to the LM3632A, setting EN to '0', setting the SW RESET bit to a '1', or by reading back the Flags1 Register (0x0B on device). The Flash Enable bit is cleared upon a FLED and/or FL\_OUT short fault.

#### 7.3.4 Software RESET

Bit[7] (SWR\_RESET) of the Enable Register (0x0A) is a software reset bit. Writing an '1' to this bit resets all  $I^2C$  register values to their default values. Once the LM3632A has finished resetting all registers, it auto-clears the SWR\_RESET bit.

#### **7.3.5 EN Input**

The EN pin is a global hardware enable for the LM3632A. This pin must be pulled to logic HIGH to enable the device and the  $I^2C$ -compatible interface. There is a 300-k $\Omega$  internal resistor between EN and GND. When this pin is at logic LOW, the LM3632A is placed in shutdown, the  $I^2C$ -compatible interface is disabled, and the internal registers are reset to their default state. It is recommended that  $V_{IN}$  has risen above 2.7 V before setting EN HIGH.

#### 7.3.6 Thermal Shutdown (TSD)

The LM3632A has TSD protection which shuts down the backlight boost, both backlight current sinks, LCM Bias Boost and outputs, inverting charge pump, flash boost, and flash current source when the die temperature reaches or exceeds 140°C (typical). The I<sup>2</sup>C interface remains active during a TSD event. If a TSD fault occurs the TSD fault is set, register 0x0B bit[0]. The fault is cleared by an I<sup>2</sup>C read of register 0x0B or by toggling the EN pin.

#### 7.4 Device Functional Modes

#### 7.4.1 Modes of Operation

**Shutdown:** The LM3632A is in shutdown when the EN pin is low.

**Standby:** After the EN pin is set high the LM3632A goes into standby mode. In standby mode, I<sup>2</sup>C writes are

allowed but references, bias currents, the oscillator, LCM powers, backlight and flash are all

disabled, to keep the guiescent supply current low (2 µA typ.).

Normal mode: All three main blocks of the LM3632A are independently controlled. For enabling each of the

blocks in all available modes, see Table 1, Table 3, and Table 4.

## 7.5 Programming

## 7.5.1 I<sup>2</sup>C-Compatible Serial Bus Interface

#### 7.5.1.1 Interface Bus Overview

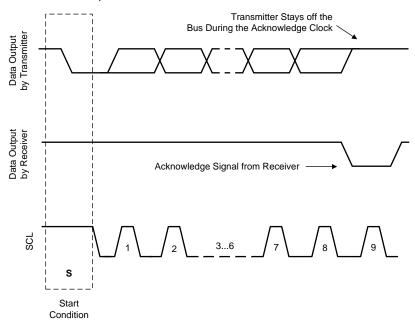

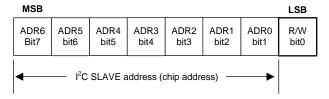

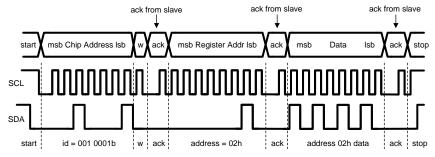

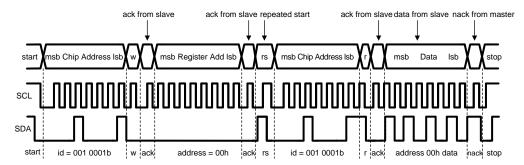

The I<sup>2</sup>C-compatible synchronous serial interface provides access to the programmable functions and registers on the device. This protocol uses a two-wire interface for bidirectional communications between the IC's connected to the bus. The two interface lines are the Serial Data Line (SDA) and the Serial Clock Line (SCL). These lines should be connected to a positive supply via a pull-up resistor and remain HIGH even when the bus is idle.

Every device on the bus is assigned a unique address and acts as either a Master or a Slave, depending whether it generates or receives the serial clock (SCL).

# **Programming (continued)**

#### 7.5.1.2 Data Transactions