# LM359 Dual, High Speed, Programmable, Current Mode (Norton) Amplifiers

Check for Samples: LM359

### **FEATURES**

- **User Programmable Gain Bandwidth Product**, Slew Rate, Input Bias Current, Output Stage **Biasing Current and Total Device Power** Dissipation

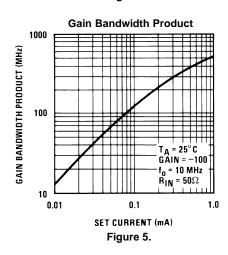

- High Gain Bandwidth Product ( $I_{SET} = 0.5 \text{ mA}$ )

- 400 MHz for  $A_V = 10$  to 100

- 30 MHz for  $A_V = 1$

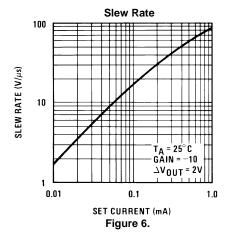

- High Slew Rate ( $I_{SET} = 0.5 \text{ mA}$ )

- 60 V/µs for A<sub>V</sub> = 10 to 100

- 30 V/µs for A<sub>V</sub> = 1

- **Current Differencing Inputs Allow High Common-Mode Input Voltages**

- Operates from a Single 5V to 22V Supply

- Large Inverting Amplifier Output Swing, 2 mV to V<sub>CC</sub> - 2V

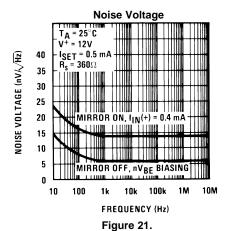

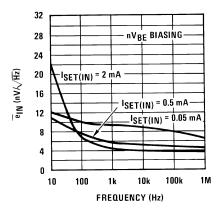

- Low Spot Noise, 6 nV  $/\sqrt{Hz}$ , for f > 1 kHz

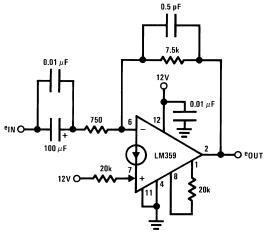

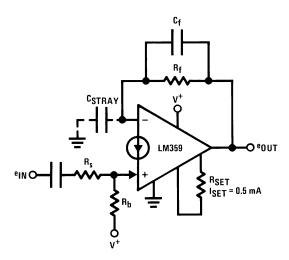

## **Typical Application**

- $A_V = 20 \text{ dB}$

- -3 dB bandwidth = 2.5 Hz to 25 MHz

- Differential phase error < 1° at 3.58

- Differential gain error < 0.5% at 3.58 MHz

## **APPLICATIONS**

- **General Purpose Video Amplifiers**

- High Frequency, High Q Active Filters

- **Photo-Diode Amplifiers**

- **Wide Frequency Range Waveform Generation** Circuits

- All LM3900 AC Applications Work to Much **Higher Frequencies**

### DESCRIPTION

The LM359 consists of two current differencing (Norton) input amplifiers. Design emphasis has been placed on obtaining high frequency performance and providing user programmable amplifier operating characteristics. Each amplifier is broadbanded to provide a high gain bandwidth product, fast slew rate and stable operation for an inverting closed loop gain of 10 or greater. Pins for additional external frequency compensation are provided. The amplifiers are designed to operate from a single supply and can accommodate input common-mode voltages greater than the supply.

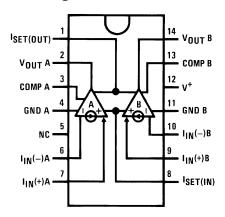

## **Connection Diagram**

Figure 1. PDIP/SOIC Package Top View See Package Number D0014A or NFF0014A

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Absolute Maximum Ratings (1)(2)

| Supply Voltage                                              |              |                           | 22 V <sub>DC</sub> or ±11 V <sub>DC</sub> |

|-------------------------------------------------------------|--------------|---------------------------|-------------------------------------------|

| D(3)                                                        |              | D Package                 | 1W                                        |

| Power Dissipation (3)                                       |              | NFF Package               | 750 mW                                    |

| Mariana T                                                   |              | D Package                 | +150°C                                    |

| Maximum T <sub>J</sub>                                      |              | NFF Package               | +125°C                                    |

|                                                             |              |                           | 147°C/W still air                         |

|                                                             |              | D Package θ <sub>jA</sub> | 110°C/W with 400 linear feet/min air flow |

| Thermal Resistance                                          |              |                           | 100°C/W still air                         |

|                                                             |              | NFF Package $\theta_{jA}$ | 75°C/W with 400 linear feet/min air flow  |

| Input Currents, I <sub>IN</sub> (+) or I <sub>IN</sub> (-)  |              |                           | 10 mA <sub>DC</sub>                       |

| Set Currents, I <sub>SET(IN)</sub> or I <sub>SET(OUT)</sub> |              |                           | 2 mA <sub>DC</sub>                        |

| Operating Temperature Range                                 |              |                           | 0°C to +70°C                              |

| Storage Temperature Range                                   |              |                           | -65°C to +150°C                           |

| Lead Temperature                                            |              | (Soldering, 10 sec.)      | 260°C                                     |

|                                                             | PDIP Package | Soldering (10 sec.)       | 260°C                                     |

| Soldering Information                                       | SOIC Paskage | Vapor Phase (60 sec.)     | 215°C                                     |

|                                                             | SOIC Package | Infrared (15 sec.)        | 220°C                                     |

<sup>(1) &</sup>quot;Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits.

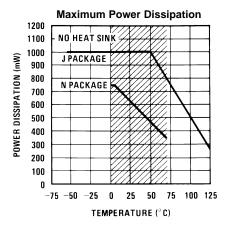

(3) See Figure 22.

### **Electrical Characteristics**

$I_{SET(IN)} = I_{SET(OUT)} = 0.5$  mA,  $V_{supply} = 12V$ ,  $T_A = 25$ °C unless otherwise noted

| Parameter                                    | Condition                                                                  | s                                                      | Min | Тур | Max   | Units |  |

|----------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------|-----|-----|-------|-------|--|

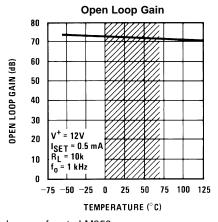

| Open Loop Voltage                            | $V_{\text{supply}} = 12V$ , $R_L = 1k$ , $f = 100 \text{ Hz}$              |                                                        | 62  | 72  |       | dB    |  |

| Gain                                         | T <sub>A</sub> = 125°C                                                     |                                                        |     | 68  |       | dB    |  |

| Bandwidth Unity Gain                         | $R_{IN} = 1 \text{ k}\Omega, C_{comp} = 10 \text{ pF}$                     |                                                        | 15  | 30  |       | MHz   |  |

| Gain Bandwidth Product,<br>Gain of 10 to 100 | $R_{IN} = 50\Omega$ to $200\Omega$                                         |                                                        | 200 | 400 |       | MHz   |  |

| Claw Data                                    | Unity Gain                                                                 | $R_{IN} = 1 \text{ k}\Omega, C_{comp} = 10 \text{ pF}$ |     | 30  |       | 1//// |  |

| Slew Rate                                    | Gain of 10 to 100                                                          | $R_{IN} < 200\Omega$                                   |     | 60  | V/µs  |       |  |

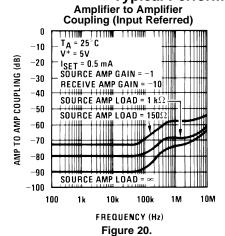

| Amplifier to Amplifier Coupling              | f = 100 Hz to 100 kHz, R <sub>L</sub> = 1k                                 |                                                        | -80 |     | dB    |       |  |

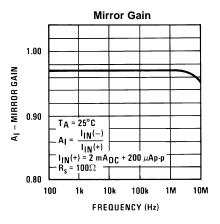

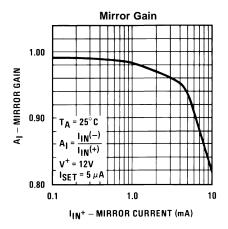

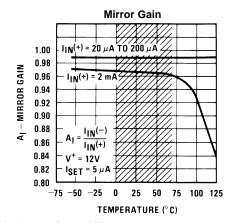

|                                              | at 2 mA $I_{IN}(+)$ , $I_{SET} = 5 \mu A$ , $T_A = 25^{\circ}C$            | 0.9                                                    | 1.0 | 1.1 | μΑ/μΑ |       |  |

| Mirror Gain (1)                              | at 0.2 mA $I_{IN}(+)$ , $I_{SET} = 5 \mu A$ Over Temp.                     | 0.9                                                    | 1.0 | 1.1 | μΑ/μΑ |       |  |

|                                              | at 20 $\mu$ A I <sub>IN</sub> (+), I <sub>SET</sub> = 5 $\mu$ A Over Temp. | 0.9                                                    | 1.0 | 1.1 | μΑ/μΑ |       |  |

| ΔMirror Gain <sup>(1)</sup>                  | at 20 $\mu A$ to 0.2 mA I <sub>IN</sub> (+) Over Temp, I <sub>SE</sub>     | ΕΤ = 5 μΑ                                              |     | 3   | 5     | %     |  |

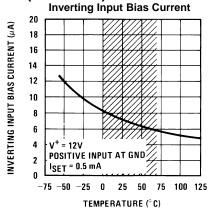

| Innut Ding Current                           | Inverting Input, T <sub>A</sub> = 25°C                                     |                                                        | 8   | 15  | μA    |       |  |

| Input Bias Current                           | Over Temp.                                                                 |                                                        |     | 30  | μA    |       |  |

| Input Resistance (βre)                       | Inverting Input                                                            |                                                        | 2.5 |     | kΩ    |       |  |

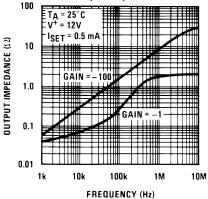

| Output Resistance                            | I <sub>OUT</sub> = 15 mA rms, f = 1 MHz                                    |                                                        |     | 3.5 |       | Ω     |  |

(1) Mirror gain is the current gain of the current mirror which is used as the non-inverting input. (A<sub>I</sub> = (I<sub>IN</sub>(-)) ΔMirror Gain is the % change in A<sub>I</sub> for two different mirror currents at any given temperature.

Submit Documentation Feedback

Copyright © 1999–2013, Texas Instruments Incorporated

<sup>(2)</sup> If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

# **Electrical Characteristics (continued)**

$I_{SET(IN)} = I_{SET(OLIT)} = 0.5 \text{ mA}, V_{Supply} = 12V, T_A = 25^{\circ}\text{C}$  unless otherwise noted

| Parameter                  | Conditions                                       | Min                                                             | Тур | Max  | Units |    |

|----------------------------|--------------------------------------------------|-----------------------------------------------------------------|-----|------|-------|----|

| Output Voltage Swing (R    | V <sub>OUT</sub> High                            | I <sub>IN</sub> (-) and I <sub>IN</sub> (+) Grounded            | 9.5 | 10.3 |       | V  |

| = 600Ω)                    | V <sub>OUT</sub> Low                             | $I_{IN}(-) = 100 \mu A, I_{IN}(+) = 0$                          |     | 2    | 50    | mV |

|                            | Source                                           | $I_{IN}(-)$ and $I_{IN}(+)$<br>Grounded, $R_L = 100\Omega$      | 16  | 40   |       |    |

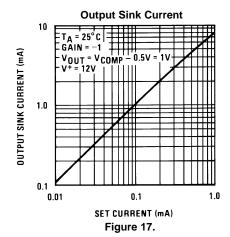

| Output Currents            | Sink (Linear Region)                             | $V_{comp}$ -0.5V = $V_{OUT}$ = 1V,<br>$I_{IN}$ (+) = 0          |     | 4.7  |       | mA |

|                            | Sink (Overdriven)                                | $I_{IN}(-) = 100 \mu A, I_{IN}(+) = 0,$<br>$V_{OUT}$ Force = 1V | 1.5 | 3    |       |    |

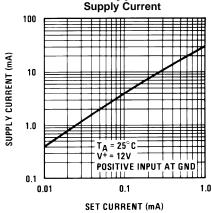

| Supply Current             | Non-Inverting Input Grounded, R <sub>L</sub> = ∞ |                                                                 |     | 18.5 | 22    | mA |

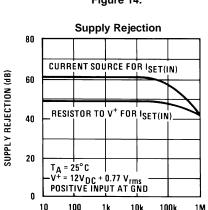

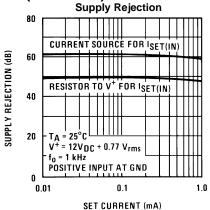

| Power Supply Rejection (2) | f = 120 Hz, I <sub>IN</sub> (+) Grounded         |                                                                 | 40  | 50   |       | dB |

<sup>(2)</sup> See Figure 15 and Figure 16.

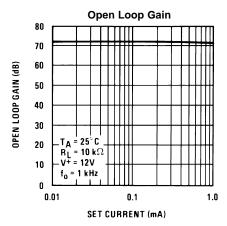

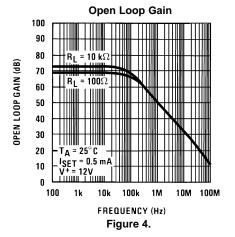

# **Typical Performance Characteristics**

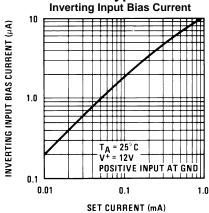

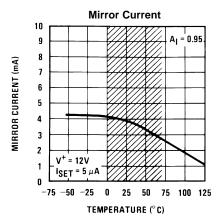

Figure 2.

**Note:** Shaded area refers to LM359 **Figure 3.**

## **Typical Performance Characteristics (continued)**

Figure 8.

Figure 10.

Figure 12.

Note: Shaded area refers to LM359

Figure 9.

**Note:** Shaded area refers to LM359

Figure 11.

Note: Shaded area refers to LM359

Figure 13.

## Typical Performance Characteristics (continued)

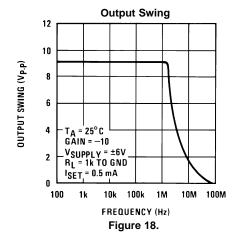

FREQUENCY (Hz) Figure 16.

10k

100k

1M

100

Figure 15.

**Output Impedance**

Figure 19.

# **Typical Performance Characteristics (continued)**

Note: Shaded area refers to LM359J/LM359N

Figure 22.

#### **APPLICATION HINTS**

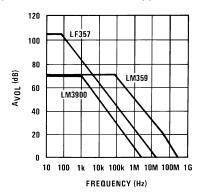

The LM359 consists of two wide bandwidth, decompensated current differencing (Norton) amplifiers. Although similar in operation to the original LM3900, design emphasis for these amplifiers has been placed on obtaining much higher frequency performance as illustrated in Figure 23.

This significant improvement in frequency response is the result of using a common-emitter/common-base (cascode) gain stage which is typical in many discrete and integrated video and RF circuit designs. Another versatile aspect of these amplifiers is the ability to externally program many internal amplifier parameters to suit the requirements of a wide variety of applications in which this type of amplifier can be used.

Figure 23.

#### DC BIASING

The LM359 is intended for single supply voltage operation which requires DC biasing of the output. The current mirror circuitry which provides the non-inverting input for the amplifier also facilitates DC biasing the output. The basic operation of this current mirror is that the current (both DC and AC) flowing into the non-inverting input will force an equal amount of current to flow into the inverting input. The mirror gain (A<sub>I</sub>) specification is the measure of how closely these two currents match. For more details see TI Application Note AN-72 (Literature Number SNOA666).

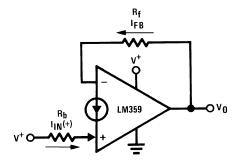

DC biasing of the output is accomplished by establishing a reference DC current into the (+) input,  $I_{IN}(+)$ , and requiring the output to provide the (-) input current. This forces the output DC level to be whatever value necessary (within the output voltage swing of the amplifier) to provide this DC reference current, Figure 24.

Figure 24.

$$\begin{split} &V_{O(DC)} = V_{BE}(-) + I_{FB} \; R_f \\ &I_{FB} = I_{IN}(+) \; A_I + I_b(-) \\ &I_{IN}(+) = \frac{V^+ - V_{BE}(+)}{R_b} \end{split}$$

Ib(-) is the inverting input bias current

Submit Documentation Feedback

Copyright © 1999–2013, Texas Instruments Incorporated

The DC input voltage at each input is a transistor  $V_{BE}(\approx 0.6\ V_{DC})$  and must be considered for DC biasing. For most applications, the supply voltage,  $V^+$ , is suitable and convenient for establishing  $I_{IN}(+)$ . The inverting input bias current,  $I_b(-)$ , is a direct function of the programmable input stage current (see OPERATING CURRENT PROGRAMMABILITY ( $I_{SET}$ )) and to obtain predictable output DC biasing set  $I_{IN}(+) \ge 10I_b(-)$ .

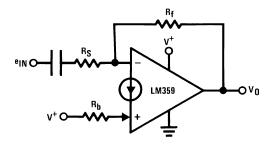

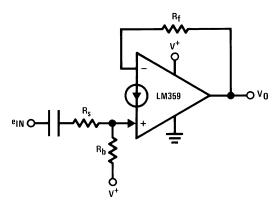

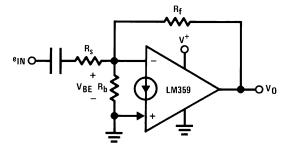

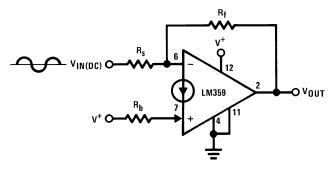

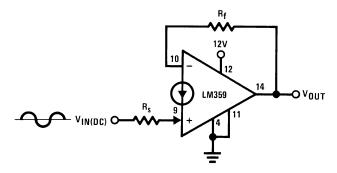

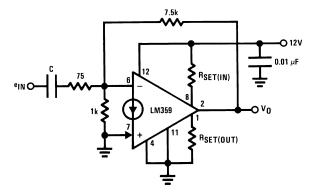

The following figures illustrate typical biasing schemes for AC amplifiers using the LM359:

Figure 25. Biasing an Inverting AC Amplifier

$$\begin{split} A_{V(AC)} &= -\frac{R_f}{R_s} \\ V_{o(DC)} &= V_{BE}(-) + R_f \left[ \frac{V^+ - V_{BE}(+)}{R_b} + I_b(-) \right] \end{split}$$

Figure 26. Biasing a Non-Inverting AC Amplifier

$$\begin{split} A_{V(AC)} &= \, + \frac{R_f}{R_s + \, r_e} \\ V_{o(DC)} &= \, V_{BE}(-) + \, R_f \left[ \frac{V^+ \, - \, V_{BE}(+)}{R_h} + \, I_b(-) \right] \end{split}$$

Figure 27. nV<sub>BE</sub> Biasing

$$\begin{split} A_{V(AC)} &= -\frac{R_f}{R_s} \\ V_{o(DC)} &= V_{BE}(-) \left(1 + \frac{R_f}{R_B}\right) + I_b(-)R_f \end{split}$$

Copyright © 1999–2013, Texas Instruments Incorporated

The nV<sub>BE</sub> biasing configuration is most useful for low noise applications where a reduced input impedance can be accommodated (see Typical Applications section).

## OPERATING CURRENT PROGRAMMABILITY (I<sub>SET</sub>)

The input bias current, slew rate, gain bandwidth product, output drive capability and total device power consumption of both amplifiers can be simultaneously controlled and optimized via the two programming pins  $I_{SET(OUT)}$  and  $I_{SET(IN)}$ .

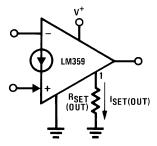

#### I<sub>SET(OUT)</sub>

The output set current (I<sub>SET(OUT)</sub>) is equal to the amount of current sourced from pin 1 and establishes the class A biasing current for the Darlington emitter follower output stage. Using a single resistor from pin 1 to ground, as shown in Figure 28, this current is equal to:

Figure 28. Establishing the Output Set Current

$$I_{SET(OUT)} = \frac{V^{+} - V_{BE}}{R_{SET(OUT)} + 500\Omega}$$

The output set current can be adjusted to optimize the amount of current the output of the amplifier can sink to drive load capacitance and for loads connected to  $V^+$ . The maximum output sinking current is approximately 10 times  $I_{SET(OUT)}$ . This set current is best used to reduce the total device supply current if the amplifiers are not required to drive small load impedances.

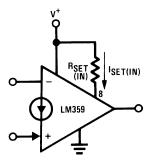

#### ISET(IN

The input set current  $I_{SET(IN)}$  is equal to the current flowing into pin 8. A resistor from pin 8 to V<sup>+</sup> sets this current to be:

Figure 29. Establishing the Input Set Current

$$I_{SET(IN)} = \frac{V^{+} - V_{BE}}{R_{SET(IN)} + 500\Omega}$$

$I_{\text{SET(IN)}}$  is most significant in controlling the AC characteristics of the LM359 as it directly sets the total input stage current of the amplifiers which determines the maximum slew rate, the frequency of the open loop dominant pole, the input resistance of the (–) input and the biasing current  $I_b$ (–). All of these parameters are significant in wide band amplifier design. The input stage current is approximately 3 times  $I_{\text{SET(IN)}}$  and by using this relationship the following first order approximations for these AC parameters are:

$$\begin{split} S_{\text{r(MAX)}} &= \text{max slew rate} \cong \frac{3 \text{ I}_{\text{SET(IN)}} (10^{-6})}{C_{\text{comp}}} (\text{V}/\mu\text{s}) \\ &\text{frequency of dominant pole} \cong \frac{3 \text{ I}_{\text{SET(IN)}}}{2\pi \, C_{\text{comp}} \, \text{A}_{\text{VOL}} (0.026\text{V})} (\text{Hz}) \\ &\text{input resistance} = \beta \text{re} \cong \frac{150 \, (0.026\text{V})}{3 \text{ I}_{\text{SET(IN)}}} (\Omega) \end{split} \tag{1}$$

where C<sub>comp</sub> is the total capacitance from the compensation pin (pin 3 or pin 13) to ground, A<sub>VOL</sub> is the low frequency open loop voltage gain in V/V and an ambient temperature of 25°C is assumed (KT/q = 26 mV and  $\beta_{tvo}$  = 150).  $I_{SET(IN)}$  also controls the DC input bias current by the expression:

$$I_b(-) = \frac{3I_{\text{SET}}}{\beta} \cong \frac{I_{\text{SET}}}{50} \text{ for NPN } \beta = 150$$

(2)

which is important for DC biasing considerations.

The total device supply current (for both amplifiers) is also a direct function of the set currents and can be approximated by:

$$I_{\text{supply}} \approx 27 \times I_{\text{SET(OUT)}} + 11 \times I_{\text{SET(IN)}} \tag{3}$$

with each set current programmed by individual resistors.

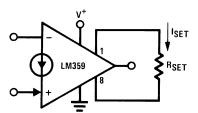

#### PROGRAMMING WITH A SINGLE RESISTOR

Operating current programming may also be accomplished using only one resistor by letting I<sub>SET(IN)</sub> equal  $I_{\text{SET}(OUT)}$ . The programming current is now referred to as  $I_{\text{SET}}$  and it is created by connecting a resistor from pin 1 to pin 8 (Figure 30).

$$I_{SET} = \frac{V^+ - 2 V_{BE}}{R_{SET} + 1 k\Omega}$$

where  $V_{BE} \cong 0.6V$  (4)

$I_{SET(IN)} = I_{SET(OUT)} = I_{SET}$

Figure 30. Single Resistor Programming of I<sub>SET</sub>

This configuration does not affect any of the internal set current dependent parameters differently than previously discussed except the total supply current which is now equal to:

$$I_{\text{supply}} \approx 37 \times I_{\text{SET}} \tag{5}$$

Care must be taken when using resistors to program the set current to prevent significantly increasing the supply voltage above the value used to determine the set current. This would cause an increase in total supply current due to the resulting increase in set current and the maximum device power dissipation could be exceeded. The set resistor value(s) should be adjusted for the new supply voltage.

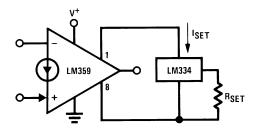

One method to avoid this is to use an adjustable current source which has voltage compliance to generate the set current as shown in Figure 31.

Figure 31. Current Source Programming of I<sub>SET</sub>

$$I_{SET} = \frac{67.7 \text{ mV}}{R_{SET}} @25^{\circ}\text{C}$$

This circuit allows I<sub>SET</sub> to remain constant over the entire supply voltage range of the LM359 which also improves power supply ripple rejection as illustrated in the Typical Performance Characteristics. It should be noted, however, that the current through the LM334 as shown will change linearly with temperature but this can be compensated for (see LM334 data sheet).

Pin 1 must never be shorted to ground or pin 8 never shorted to V<sup>+</sup> without limiting the current to 2 mA or less to prevent catastrophic device failure.

#### CONSIDERATIONS FOR HIGH FREQUENCY OPERATION

The LM359 is intended for use in relatively high frequency applications and many factors external to the amplifier itself must be considered. Minimization of stray capacitances and their effect on circuit operation are the primary requirements. The following list contains some general guidelines to help accomplish this end:

- 1. Keep the leads of all external components as short as possible.

- 2. Place components conducting signal current from the output of an amplifier away from that amplifier's non-inverting input.

- 3. Use reasonably low value resistances for gain setting and biasing.

- 4. Use of a ground plane is helpful in providing a shielding effect between the inputs and from input to output. Avoid using vector boards.

- 5. Use a single-point ground and single-point supply distribution to minimize crosstalk. Always connect the two grounds (one from each amplifier) together.

- 6. Avoid use of long wires (> 2") but if necessary, use shielded wire.

- 7. Bypass the supply close to the device with a low inductance, low value capacitor (typically a 0.01  $\mu$ F ceramic) to create a good high frequency ground. If long supply leads are unavoidable, a small resistor ( $\sim$ 10 $\Omega$ ) in series with the bypass capacitor may be needed and using shielded wire for the supply leads is also recommended.

#### **COMPENSATION**

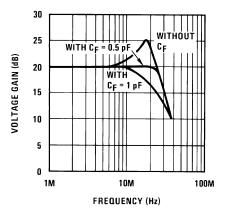

The LM359 is internally compensated for stability with closed loop inverting gains of 10 or more. For an inverting gain of less than 10 and all non-inverting amplifiers (the amplifier always has 100% negative current feedback regardless of the gain in the non-inverting configuration) some external frequency compensation is required because the stray capacitance to ground from the (–) input and the feedback resistor add additional lagging phase within the feedback loop. The value of the input capacitance will typically be in the range of 6 pF to 10 pF for a reasonably constructed circuit board. When using a feedback resistance of 30 k $\Omega$  or less, the best method of compensation, without sacrificing slew rate, is to add a lead capacitor in parallel with the feedback resistor with a value on the order of 1 pF to 5 pF as shown in Figure 32.

$C_f = 1 pF to 5 pF for stability$

Figure 32. Best Method of Compensation

Another method of compensation is to increase the effective value of the internal compensation capacitor by adding capacitance from the COMP pin of an amplifier to ground. An external 20 pF capacitor will generally compensate for all gain settings but will also reduce the gain bandwidth product and the slew rate. These same results can also be obtained by reducing  $I_{\text{SET(IN)}}$  if the full capabilities of the amplifier are not required. This method is termed over-compensation.

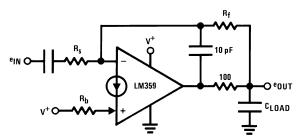

Another area of concern from a stability standpoint is that of capacitive loading. The amplifier will generally drive capacitive loads up to 100 pF without oscillation problems. Any larger C loads can be isolated from the output as shown in Figure 33. Over-compensation of the amplifier can also be used if the corresponding reduction of the GBW product can be afforded.

Figure 33. Isolating Large Capacitive Loads

In most applications using the LM359, the input signal will be AC coupled so as not to affect the DC biasing of the amplifier. This gives rise to another subtlety of high frequency circuits which is the effective series inductance (ESL) of the coupling capacitor which creates an increase in the impedance of the capacitor at high frequencies and can cause an unexpected gain reduction. Low ESL capacitors like solid tantalum for large values of C and ceramic for smaller values are recommended. A parallel combination of the two types is even better for gain accuracy over a wide frequency range.

#### **AMPLIFIER DESIGN EXAMPLES**

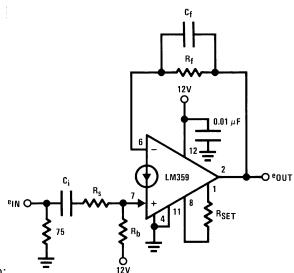

The ability of the LM359 to provide gain at frequencies higher than most monolithic amplifiers can provide makes it most useful as a basic broadband amplification stage. The design of standard inverting and non-inverting amplifiers, though different than standard op amp design due to the current differencing inputs, also entail subtle design differences between the two types of amplifiers. These differences will be best illustrated by design examples. For these examples a practical video amplifier with a passband of 8 Hz to 10 MHz and a gain of 20 dB will be used. It will be assumed that the input will come from a  $75\Omega$  source and proper signal termination will be considered. The supply voltage is 12  $V_{DC}$  and single resistor programming of the operating current,  $I_{SET}$ , will be used for simplicity.

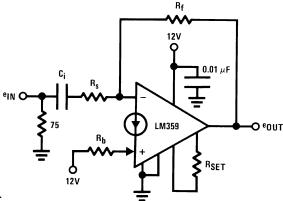

#### AN INVERTING VIDEO AMPLIFIER

- 1. Basic circuit configuration:

- 2. Determine the required I<sub>SET</sub> from the characteristic curves for gain bandwidth product.GBW<sub>MIN</sub>= 10 x 10 MHz = 100 MHzFor a flat response to 10 MHz a closed loop response to two octaves above 10 MHz (40 MHz) will be sufficient.

$Actual~GBW = 10 \times 40~MHz = 400~MHz~I_{SET}~required = 0.5~mA \\ ^{R_{SET}} = \frac{v^{+} - 2\,v_{BE}}{I_{SET}} - 1\,k\Omega = \frac{10.8V}{0.5\,mA} - 1\,k\Omega = 20.6\,k\Omega = 10.8V$

3. Determine maximum value for  $R_f$  to provide stable DC biasing  $l_{f(MIN)} \ge 10 \times \frac{3 l_{SET}}{\beta} = \frac{100 \ \mu A \ minimum \ DC}{feedback \ current}$  Optimum

$$\begin{split} V_{\text{oDC(opt)}} &= \frac{V_{\text{o(MAX)}} - V_{\text{o(MIN)}}}{2} + V_{\text{o(MIN)}} \\ &\approx \frac{(V^+ - 3 \, V_{\text{BE}}) - 2 \, \text{mV}}{2} \end{split}$$

output DC level for maximum symmetrical swing without clipping is:  $V_{oDC(opt)} \simeq \frac{12-1.8V}{2} = \frac{10.2V}{2} = 5.1 V_{DC} R_{f(MAX)}$  can now be found:  $R_{f(MAX)} = \frac{V_{oDC(opt)} - V_{BE}(-)}{I_{f(MIN)}} = \frac{5.1V - 0.6V}{100 \ \mu A} = 45 \ k\Omega$  This value should not be exceeded for Table 1.1. DC biasing.

- 4. Select  $R_s$  to be large enough so as not to appreciably load the input termination resistance:  $R_s \ge 750\Omega$ ; Let  $R_s$

- 5. Select  $R_f$  for appropriate gain:  $A_V = -\frac{R_f}{R_s} so; R_f = 10 R_s = 7.5 k\Omega$  7.5 k $\Omega$  is less than the calculated  $R_{f(MAX)}$  so DC predictability is insured.

- 6. Since  $R_f = 7.5k$ , for the output to be biased to 5.1  $V_{DC}$ ,

the reference current  $I_{IN}(+)$  must be:  $I_{IN}(+)=\frac{5.1V-V_{BE}(-)}{R_f}=\frac{5.1V-0.6V}{7.5\,\mathrm{k}\Omega}=600\,\mu\mathrm{A}$

Now R<sub>b</sub> can be found by:  $R_b = \frac{V^+ - V_{BE}(+)}{I_{IN}(+)} = \frac{12-0.6}{600~\mu\text{A}} = 19~\text{k}\Omega$

7. Select C<sub>i</sub> to provide the proper gain for the 8 Hz minimum input frequency:

$C_{i} \geq \frac{1}{2\pi \; R_{s} \; (f_{low})} = \frac{1}{2\pi \; (750\Omega) \; (8 \; Hz)} = 26 \; \mu F \\ \text{A larger value of } C_{i} \; \text{will allow a flat frequency response down to 8 Hz and a}$ 0.01 µF ceramic capacitor in parallel with C<sub>i</sub> will maintain high frequency gain accuracy.

8. Test for peaking of the frequency response and add a feedback "lead" capacitor to compensate if necessary.

Figure 34. Final Circuit Using Standard 5% **Tolerance Resistor Values**

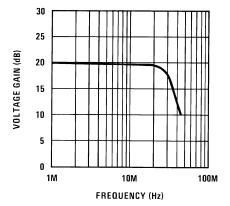

$V_{o(DC)} = 5.1V$ Differential phase error < 1° for 3.58 MHz f<sub>IN</sub> Differential gain error < 0.5% for 3.58 MHz f<sub>IN</sub>  $f_{-3 \text{ dB}} \text{ low} = 2.5 \text{ Hz}$

Figure 35. Circuit Performance

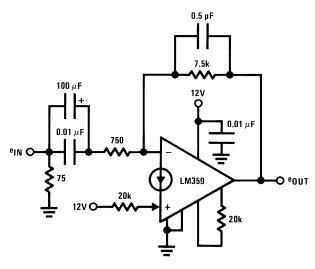

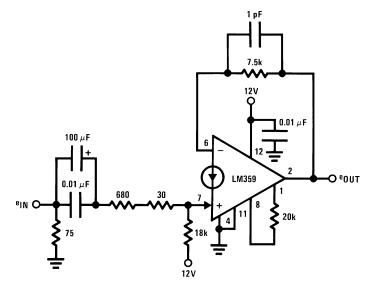

### A NON-INVERTING VIDEO AMPLIFIER

For this case several design considerations must be dealt with.

- The output voltage (AC and DC) is strictly a function of the size of the feedback resistor and the sum of AC and DC "mirror current" flowing into the (+) input.

- The amplifier always has 100% current feedback so external compensation is required. Add a small (1 pF-5 pF) feedback capacitance to leave the amplifier's open loop response and slew rate unaffected.

- To prevent saturating the mirror stage the total AC and DC current flowing into the amplifier's (+) input should be less than 2 mA.

- The output's maximum negative swing is one diode above ground due to the V<sub>BE</sub> diode clamp at the (-) input.

#### **DESIGN EXAMPLE**

$e_{IN}$  = 50 mV (MAX),  $f_{IN}$  = 10 MHz (MAX), desired circuit BW = 20 MHz,  $A_V$  = 20 dB, driving source impedance =  $75\Omega$ , V<sup>+</sup> = 12V.

- 1. Basic circuit configuration:

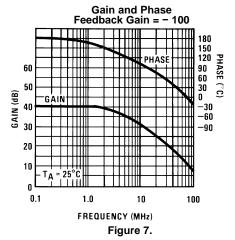

- 2. Select I<sub>SET</sub> to provide adequate amplifier bandwidth so that the closed loop bandwidth will be determined by R<sub>f</sub> and C<sub>f</sub>. To do this, the set current should program an amplifier open loop gain of at least 20 dB at the desired closed loop bandwidth of the circuit. For this example, an I<sub>SET</sub> of 0.5 mA will provide 26 dB of open loop gain at 20 MHz which will be sufficient. Using single resistor programming for

$$I_{SET} = \frac{V^+ - 2 V_{BE}}{I_{SET}} - 1 k\Omega = 20.6 k\Omega$$

3. Since the closed loop bandwidth will be determined by  $R_f$  and  $C_f$   $\left(f_{-3 \text{ dB}} = \frac{1}{2\pi R_f C_f}\right)$  to obtain a 20 MHz bandwidth, both  $R_f$  and  $C_f$  should be kept small. It can be assumed that  $C_f$  can be in the range of 1 pF to 5 pF for carefully constructed circuit boards to insure stability and allow a flat frequency response. This will limit the

$$\frac{1}{2\pi~5~\text{pF 20 MHz}} \leq \, R_{f} \leq \frac{1}{2\pi~1~\text{pF 20 MHz}}$$

value of  $R_f$  to be within the range of: or 1.6  $k\Omega \le R_f \le 7.96 \, k\Omega$ Also, for a closed loop gain of +10, R<sub>f</sub> must be 10 times  $R_s + r_e$  where  $r_e$  is the mirror diode resistance.

- 4. So as not to appreciably load the  $75\Omega$  input termination resistance the value of  $(R_s + r_e)$  is set to  $750\Omega$ .

- 5. For  $A_v = 10$ ;  $R_f$  is set to 7.5 k $\Omega$ .

$$\begin{split} V_{\text{oDC(opt)}} &= \frac{V_{\text{o(MAX)}} - V_{\text{o(MIN)}}}{2} + V_{\text{o(MIN)}} \\ &= \frac{(12 - 1.8)V - 0.6V}{2} + 0.6V = 5.4 \, V_{\text{DC}} \end{split}$$

6. The optimum output DC level for symmetrical AC swing is:

$$\begin{split} I_{FB} &= \frac{V_{oDC(opt)} - V_{BE}(-)}{R_f} = \frac{5.4V - 0.6V}{7.5k} \\ &= 640~\mu A = I_{IN}(+) \end{split}$$

- 7. The DC feedback current must be: DC biasing predictability will be insured because 640  $\mu$ A is greater than the minimum of I<sub>SET</sub>/5 or 100  $\mu$ A.

- 8. For gain accuracy the total AC and DC mirror current should be less than 2 mA. For this example the  $\frac{\pm e_{\text{in peak}}}{R_{\text{S}} + r_{\text{e}}} = \frac{\pm 50 \text{ mV}}{750\Omega} = \pm 66 \,\mu\text{A}$  therefore the total mirror current range will be 574 maximum AC mirror current will be: R<sub>s</sub> + r<sub>e</sub>

μA to 706 μA which will insure gain accuracy.

9.

$$R_b$$

can now be found:  $R_b = \frac{V^+ - V_{BE}(+)}{I_{IN}(+)} = \frac{12 - 0.6}{640 \ \mu A} = 17.8 \ k\Omega$

10. Since  $R_s + r_e$  will be 750 $\Omega$  and  $r_e$  is fixed by the DC mirror current to be:  $r_e = \frac{KT}{q l_{IN(+)}} = \frac{26 \, mV}{640 \, \mu A} \cong 40 \Omega$  at 25°C  $R_s$  must be  $750\Omega-40\Omega$  or  $710\Omega$  which can be a  $680\Omega$  resistor in series with a  $30\Omega$  resistor which are standard 5% tolerance resistor values.

11. As a final design step,  $C_i$  must be selected to pass the lower passband frequency corner of 8 Hz for this example.  $C_i = \frac{1}{2\pi \, (R_S + r_e) \, f_{low}} = \frac{1}{2\pi \, (750 \, \Omega) \, (8 \, Hz)} = 26.5 \, \mu F$ A larger value may be used and a 0.01  $\mu F$  ceramic capacitor in parallel with  $C_i$  will maintain high frequency gain accuracy.

Figure 36. Final Circuit Using Standard 5% Tolerance Resistor Values

$V_{o(DC)} = 5.4V$ Differential phase error < 0.5° Differential gain error < 2%  $f_{-3~dB}$  low = 2.5 Hz

Figure 37. Circuit Performance

## **GENERAL PRECAUTIONS**

The LM359 is designed primarily for single supply operation but split supplies may be used if the negative supply voltage is well regulated as the amplifiers have no negative supply rejection.

The total device power dissipation must always be kept in mind when selecting an operating supply voltage, the programming current,  $I_{SET}$ , and the load resistance, particularly when DC coupling the output to a succeeding stage. To prevent damaging the current mirror input diode, the mirror current should always be limited to 10 mA, or less, which is important if the input is susceptible to high voltage transients. The voltage at any of the inputs must not be forced more negative than -0.7V without limiting the current to 10 mA.

The supply voltage must never be reversed to the device; however, plugging the device into a socket backwards would then connect the positive supply voltage to the pin that has no internal connection (pin 5) which may prevent inadvertent device failure.

# **Typical Applications**

## **DC Coupled Inputs**

Figure 38. Inverting

$$\begin{split} V_{o(DC)} &= \left[\frac{V^+ - V_{BE}(+)}{R_b} - \frac{V_{IN(DC)} - V_{BE}(-)}{R_s}\right] R_f + V_{BE}(-) \\ A_{V(AC)} &= \frac{R_f}{R_s} \end{split}$$

Figure 39. Non-Inverting

$$\begin{split} &V_{O(DC)} = V_{BE}(-) + \frac{(V_{IN(DC)} - V_{BE}(+)) \, R_f}{R_s} \\ &A_{V(AC)} = + \frac{R_f}{R_s + r_e(+)} \end{split}$$

- · Eliminates the need for an input coupling capacitor

- Input DC level must be stable and can exceed the supply voltage of the LM359 provided that maximum input currents are not exceeded.

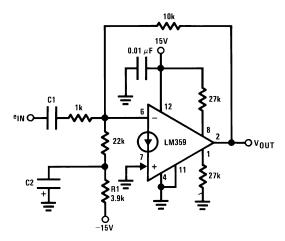

Figure 40. Noise Reduction using  $nV_{BE}$  Biasing

• R1 and C2 provide additional filtering of the negative biasing supply

Figure 41.  $nV_{BE}$  Biasing with a Negative Supply

Figure 42. Typical Input Referred Noise Performance

- FET input voltage mode op amp

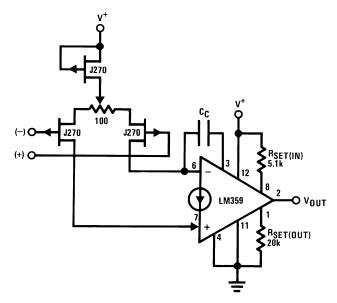

- For  $A_V$  = +1; BW = 40 MHz,  $S_r$  = 60 V/ $\mu$ s;  $C_C$  = 51 pF

- For  $A_V$  = +11; BW = 24 MHz,  $S_r$  = 130 V/ $\mu$ s;  $C_C$  = 5 pF

- For  $A_V$  = +100; BW = 4.5 MHz,  $S_r$  = 150 V/ $\mu$ s;  $C_C$  = 2 pF

- V<sub>OS</sub> is typically <25 mV; 100Ω potentiometer allows a V<sub>OS</sub> adjust range of ≈ ±200 mV

- Inputs must be DC biased for single supply operation

Figure 43. Adding a JFET Input Stage

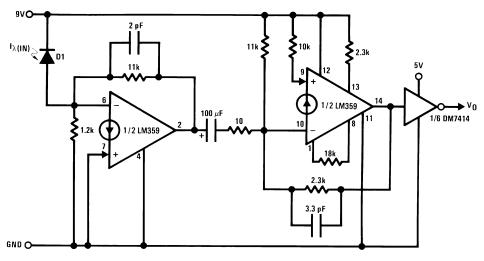

D1 ~ RCA N-Type Silicon P-I-N Photodiode

- Frequency response of greater than 10 MHz

- If slow rise and fall times can be tolerated the gate on the output can be removed. In this case the rise and the fall time of the LM359 is 40 ns.

- $T_{PDL} = 45 \text{ ns}, T_{PDH} = 50 \text{ ns} T^2L \text{ output}$

Figure 44. Photo Diode Amplifier

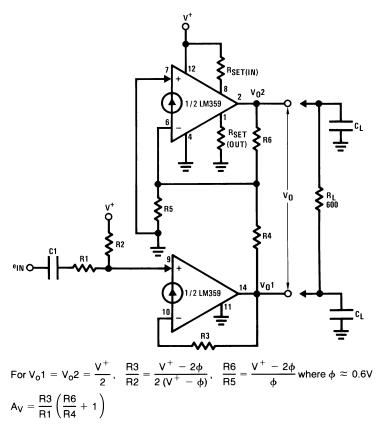

- 1 MHz-3 dB bandwidth with gain of 10 and 0 dbm into 600Ω

- 0.3% distortion at full bandwidth; reduced to 0.05% with bandwidth of 10 kHz

- Will drive  $C_L = 1500 \text{ pF}$  with no additional compensation,  $\pm 0.01 \text{ }\mu\text{F}$  with  $C_{comp} = 180 \text{ pF}$

- 70 dB signal to noise ratio at 0 dbm into  $600\Omega$ , 10 kHz bandwidth

Figure 45. Balanced Line Driver

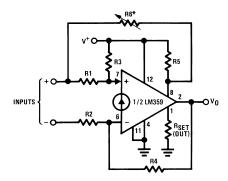

$$V_{O(DC)} = \frac{R4}{R3} (V^+ - \phi) \mbox{ where } \phi = 0.6V$$

$$A_V = \frac{R4}{R1} \mbox{for R1} = R2$$

CMRR is adjusted for max at expected CM input signal

$$R6 \approx \frac{R5}{5}$$

, for  $R5 = 100 \text{ k}\Omega$

- Wide bandwidth

- 70 dB CMRR typ

- Wide CM input voltage range

Figure 46. Difference Amplifier

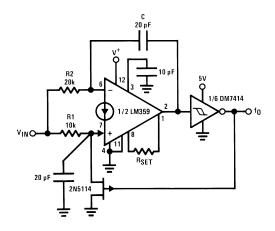

$$\begin{split} f_0 &= \frac{V_{IN} - \varphi}{4 \text{ C} \Delta \text{V R1}} \\ \text{where: R2} &= 2 \text{R1} \\ \phi &= \text{amplifier input voltage} = 0.6 \text{V} \\ \Delta \text{V} &= \text{DM7414 hysteresis, typ 1V} \end{split}$$

- 5 MHz operation

- T<sup>2</sup>L output

Figure 47. Voltage Controlled Oscillator

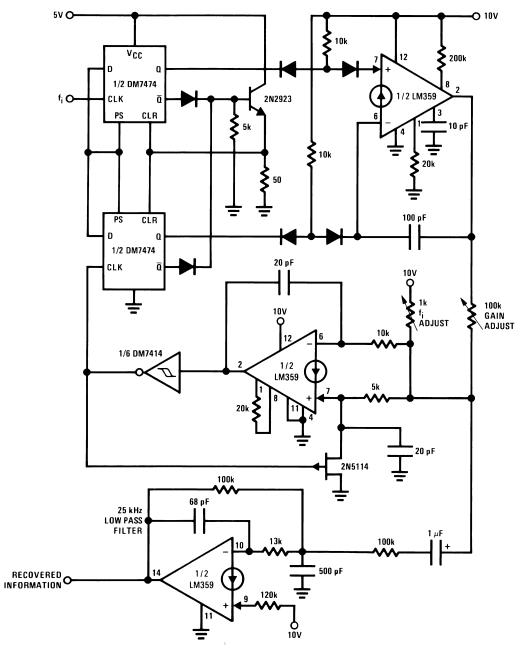

- Up to 5 MHz operation

- T<sup>2</sup>L compatible input

All diodes = 1N914

Figure 48. Phase Locked Loop

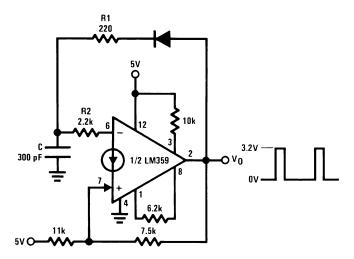

f = 1 MHz Output is TTL compatible Frequency is adjusted by R1 & C (R1  $\ll$  R2)

Figure 49. Squarewave Generator

Output is TTL compatible Duty cycle is adjusted by R1 Frequency is adjusted by C f = 1 MHz Duty cycle = 20%

Figure 50. Pulse Generator

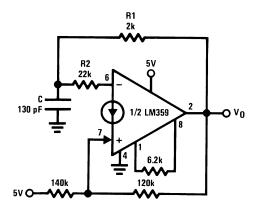

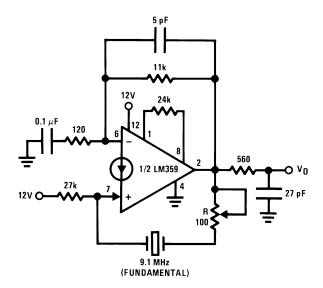

$V_o = 500 \text{ mVp-p}$  f = 9.1 MHz THD < 2.5%

Figure 51. Crystal Controlled Sinewave Oscillator

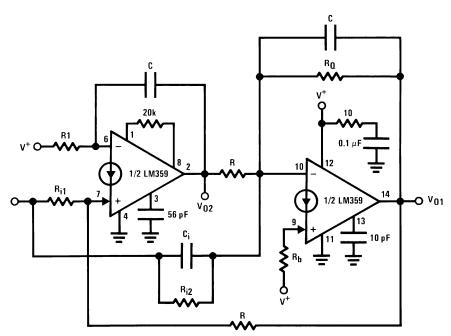

- The high speed of the LM359 allows the center frequency  $Q_0$  product of the filter to be:  $f_0 \times Q_0 \le 5$  MHz

- The above filter(s) maintain performance over wide temperature range

- One half of LM359 acts as a true non-inverting integrator so only 2 amplifiers (instead of 3 or 4) are needed for the biquad filter structure

Figure 52. High Performance 2 Amplifier Biquad Filter(s)

# Table 1. DC Biasing Equations for $V_{01(DC)} \simeq V_{02(DC)} \simeq V^{+}/2$

| Type I   | $\frac{2 V_{IN(DC)}}{V^{+}(R_{i2})} + \frac{1}{R} + \frac{1}{R_{Q}} = \frac{2}{R_{b}}; R1 = 2R$                            |

|----------|----------------------------------------------------------------------------------------------------------------------------|

| Type II  | $\frac{1}{R} + \frac{1}{R_Q} = \frac{2}{R_b}$ ; R1 = 2R                                                                    |

| Type III | $\frac{1}{R} + \frac{1}{R_Q} = \frac{2}{R_b}; \frac{1}{R1} = \frac{V_{\text{IN(DC)}}}{V^+ (R_{\text{i1}})} + \frac{1}{2R}$ |

# **Table 2. Analysis and Design Equations**

| Туре | V <sub>01</sub> | V <sub>O2</sub> | Ci | R <sub>i2</sub> | R <sub>i1</sub> | fo     | $Q_{o}$           | f <sub>Z</sub> (notch)               | H <sub>o(LP)</sub> | H <sub>o(BP)</sub>                | H <sub>o(HP)</sub> | H <sub>o(BR)</sub>                 |

|------|-----------------|-----------------|----|-----------------|-----------------|--------|-------------------|--------------------------------------|--------------------|-----------------------------------|--------------------|------------------------------------|

| I    | BP              | LP              | 0  | R <sub>i2</sub> | 8               | 1/2πRC | R <sub>Q</sub> /R |                                      | R/R <sub>i2</sub>  | R <sub>Q</sub> /R <sub>i2</sub>   | _                  | _                                  |

| II   | HP              | BP              | Ci | ∞               | ∞               | 1/2πRC | R <sub>Q</sub> /R | _                                    | _                  | R <sub>Q</sub> C <sub>i</sub> /RC | C <sub>i</sub> /C  | _                                  |

| Ш    | Notch/<br>BR    | _               | Ci | 8               | R <sub>i1</sub> | 1/2πRC | R <sub>Q</sub> /R | 1/2π√RR <sub>i</sub> CC <sub>i</sub> | _                  | _                                 |                    | $H_0 \Big _{f \to \infty} = C_i/C$ |

|      |                 |                 |    |                 |                 |        |                   |                                      |                    |                                   |                    | $H_0 \Big _{f \to 0} = C/R_i$      |

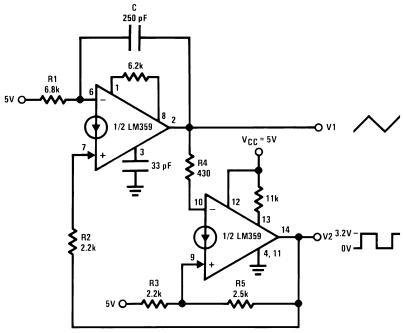

V2 output is TTL compatible R2 adjusts for symmetry of the triangle waveform Frequency is adjusted with R5 and C

Figure 53. Triangle Waveform Generator

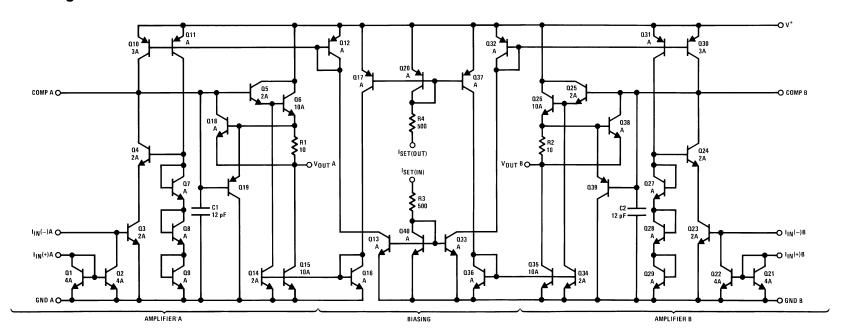

# **Schematic Diagram**

# **REVISION HISTORY**

| Changes from Revision D (March 2013) to Revision E     Changed layout of National Data Sheet to TI format |                                                    |  | ge |

|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|----|

| •                                                                                                         | Changed layout of National Data Sheet to TI format |  | 27 |

28

Product Folder Links: LM359

www.ti.com 11-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|----------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       | (-)    | (=/           |                |                       | (=)  | (4)                           | (5)                        |              | (-)              |

| LM359M/NOPB           | Active | Production    | SOIC (D)   14  | 55   TUBE             | Yes  | SN                            | Level-1-260C-UNLIM         | 0 to 70      | LM359M           |

| LM359M/NOPB.B         | Active | Production    | SOIC (D)   14  | 55   TUBE             | Yes  | SN                            | Level-1-260C-UNLIM         | 0 to 70      | LM359M           |

| LM359MX/NOPB          | Active | Production    | SOIC (D)   14  | 2500   LARGE T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | 0 to 70      | LM359M           |

| LM359MX/NOPB.B        | Active | Production    | SOIC (D)   14  | 2500   LARGE T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | 0 to 70      | LM359M           |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-May-2025

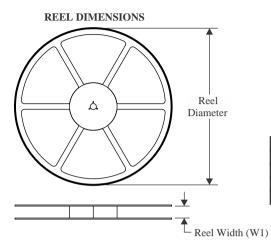

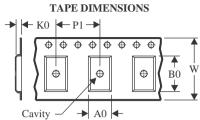

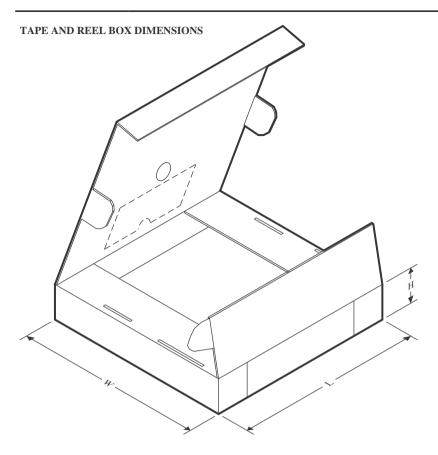

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

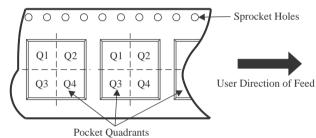

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | U    | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM359MX/NOPB | SOIC | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.35       | 2.3        | 8.0        | 16.0      | Q1               |

www.ti.com 23-May-2025

## \*All dimensions are nominal

|   | Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| ı | LM359MX/NOPB | SOIC         | D               | 14   | 2500 | 367.0       | 367.0      | 35.0        |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-May-2025

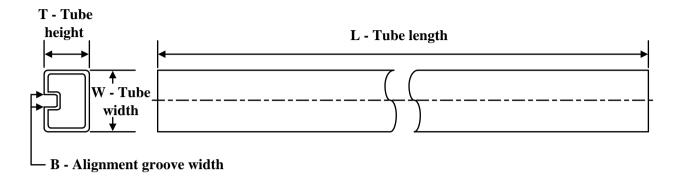

## **TUBE**

\*All dimensions are nominal

| Device        | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|---------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| LM359M/NOPB   | D            | SOIC         | 14   | 55  | 495    | 8      | 4064   | 3.05   |

| LM359M/NOPB.B | D            | SOIC         | 14   | 55  | 495    | 8      | 4064   | 3.05   |

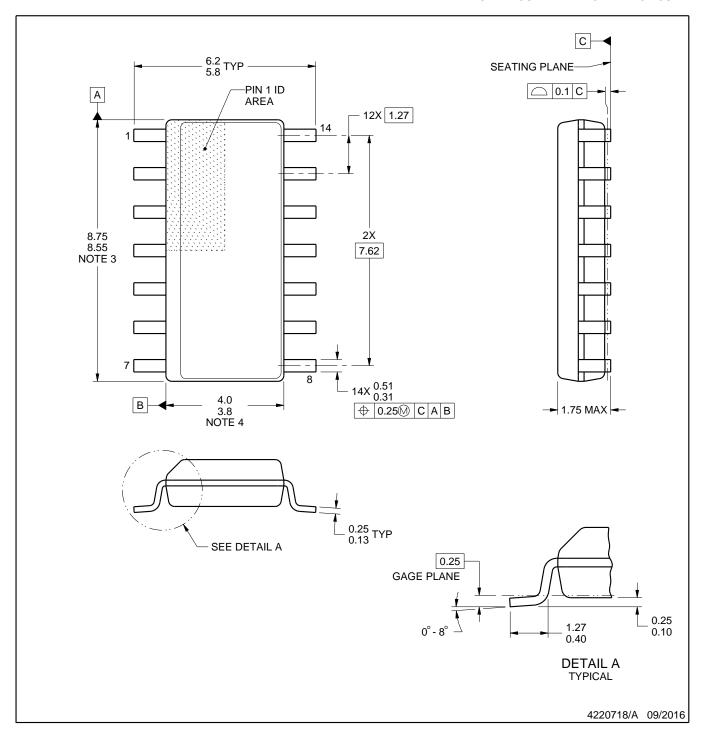

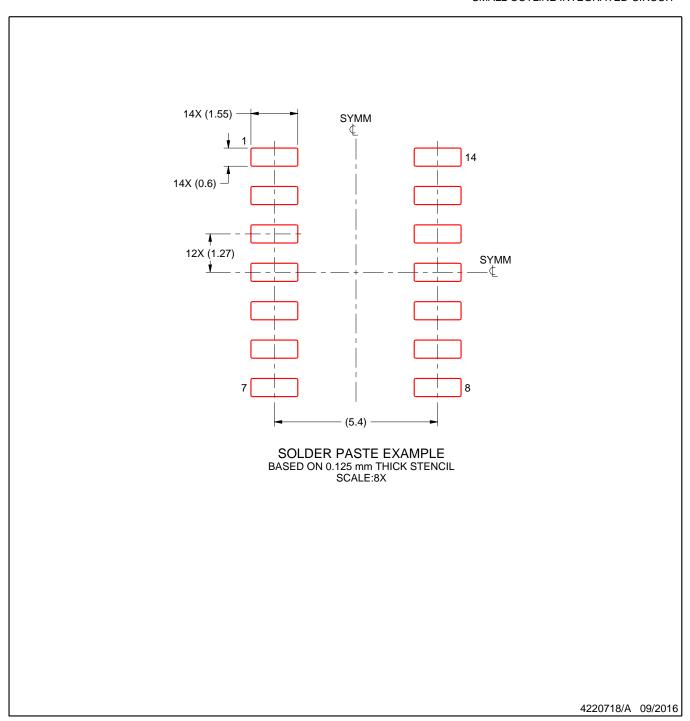

SMALL OUTLINE INTEGRATED CIRCUIT

### NOTES:

- 1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm, per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.43 mm, per side.

- 5. Reference JEDEC registration MS-012, variation AB.

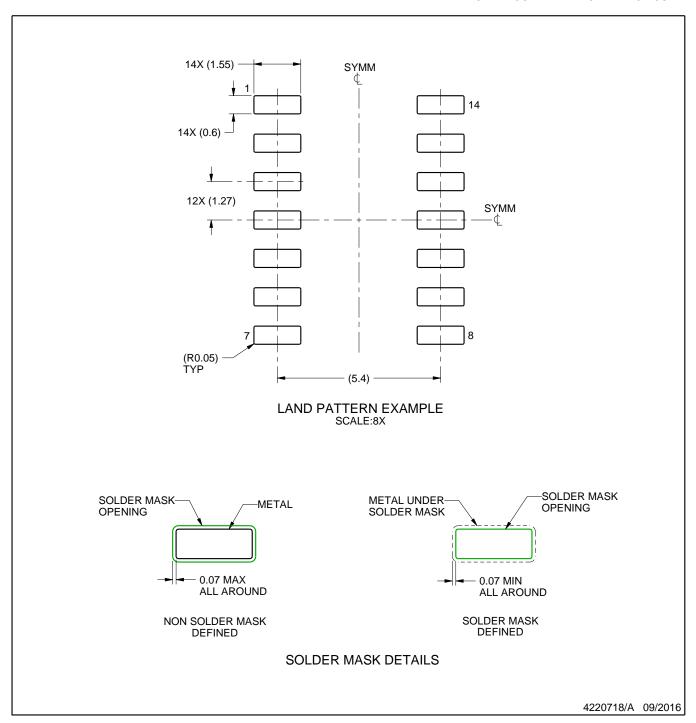

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025