# 用于 **LED** 照明的相位调光,初级侧电源调节功率因数校正 **(PFC)** 反激转换 控制器

查询样品: LM3447

## 特性

- 集成型相位角度解码

- 可以同时兼容前斩波和后斩波

- 超过 50:1 的调光范围

- 总谐波失真较低的功率因数校正

- 使用输入电压前馈技术实现的初级侧控制

- 带有改进线路调节的输入功率调节机制

- LED 的恒定功率运行用来补偿温度和使用寿命范围内的前馈电压变化

- 定频不连续电感模式运行

- 谷底开关操作以实现高效率和低电磁干扰 (EMI)

- 高效三端双向交流开关 (TRIAC) 保持电流管理

- 用于 LED 保护的热折返功能

- LED 开电路和短路保护

# 应用范围

- 亮度可调节 A19, R20, PAR30/38 LED 灯

- 嵌入式 LED 射灯和吊灯

- 工业用和商用固态照明

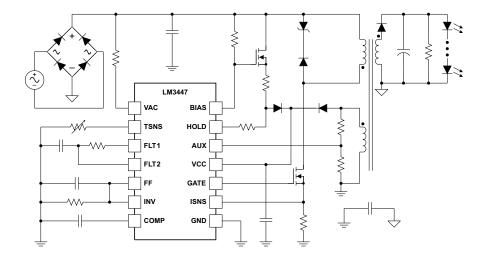

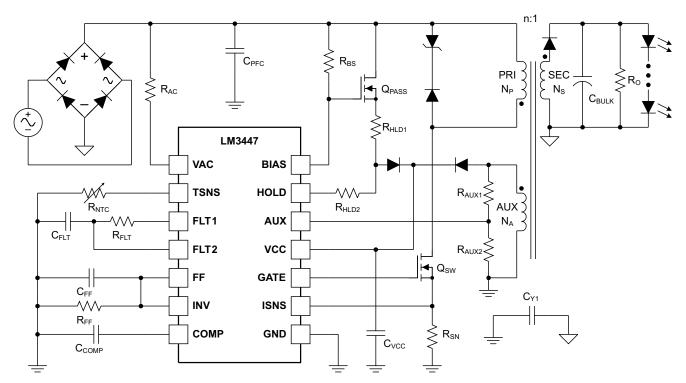

# 典型应用图

## 说明

LM3447 是一款多用途功率因数校正 (PFC) 控制器,此控制器设计用于满足与切相调光器兼容的住宅和商用 LED 灯驱动器性能需求。此器件集成有一个相位解码电路和一个可调保持电流电路来提供顺畅且无闪光的亮度调节操作。基于输入电压前馈的私有初级侧控制技术被用于调节取自 LED 驱动器的输入功率并且实现宽输入电压范围上的线路调节功能。执行谷底开关操作可大大减少开关损失和 EMI。根据一个单外部负温度系数 (NTC) 热敏电阻器上感测到的温度,一个内部热折返电路可保护 LED 不受过热损坏。额外的特性还包括 LED 开电路和短路保护、逐周期场效应管 (FET) 过流保护、使用一个内部 812ms 故障定时器的突发模式故障操作和内部热关断。

LM3447 是亮度可调、隔离式单级 LED 灯驱动器应用的理想选择,在此类应用中,简单性、低组件数量和较小的解决方案尺寸是首要的。目前,此器件采用薄型小外形尺寸 (TSSOP) 14 引脚封装。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

# ORDERING INFORMATION(1)

| TEMPERATURE<br>RANGE<br>(T <sub>J</sub> ) | PACKAGE <sup>(2)</sup> | PINS | PACKAGE DRAWING | ORDERABLE DEVICE<br>NUMBER | TRANSPORT<br>MEDIA | QUANTITY |

|-------------------------------------------|------------------------|------|-----------------|----------------------------|--------------------|----------|

|                                           |                        |      |                 | LM3447MT                   | Tube               | 94       |

| -40°C to 125°C                            | TSSOP                  | 14   | MTC14           | MTC14 LM3447MTE Tape a     | Tape and Reel      | 250      |

|                                           |                        |      |                 | LM3447MTX                  | Tape and Reel      | 2500     |

- (1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

- Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

# **ABSOLUTE MAXIMUM RATINGS**(1)

All voltages are with respect to GND,  $-40^{\circ}$ C <  $T_J = T_A < 125^{\circ}$ C, all currents are positive into and negative out of the specified terminal (unless otherwise noted)

|                                          |                                            | VALUE |     | UNIT |

|------------------------------------------|--------------------------------------------|-------|-----|------|

|                                          |                                            | MIN   |     |      |

| Supply voltage                           | VCC <sup>(2)</sup>                         | -0.3  | 22  | V    |

| land deltana name                        | HOLD <sup>(3)</sup>                        | -0.3  | 22  | V    |

| Input voltage range                      | VAC <sup>(4)</sup>                         | -0.3  | 6   | V    |

|                                          | TSNS, FLT1, FLT2, FF, INV, COMP, ISNS, AUX | -0.3  | 6   | V    |

| Output voltage range                     | GATE <sup>(2)</sup> (Pulse < 20ns)         | -1.5  | 19  | V    |

| Continuous input current                 | l <sub>BIAS</sub> <sup>(4)</sup>           |       | 10  | mA   |

| Junction temperature                     | T <sub>J</sub> <sup>(5)</sup>              |       | 165 | °C   |

| Storage temperature range <sup>(5)</sup> | T <sub>STG</sub>                           | -65   | 150 | °C   |

| Lead temperature                         | Soldering, 10s                             |       | 260 | °C   |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) VCC is internally limited to approximately 18.9V. See ELECTRICAL CHARACTERISTICS table.

- (3) HOLD current is limited by the internal power dissipation of the device.

- 4) Voltage on VAC and BIAS is internally clamped. The clamp level varies with operating conditions. In normal use, VAC and BIAS are current fed with the voltage internally limited.

- (5) Maximum junction temperature is internally limited.

#### PACKAGE DISSIPATION RATINGS(1) (2)

| PACKAGE        | θ <sub>JA</sub> , THERMAL IMPEDANCE JUNCTION | T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C | T <sub>A</sub> = 85°C |

|----------------|----------------------------------------------|-----------------------|-----------------------|-----------------------|

|                | TO AMBIENT,NO AIRFLOW                        | POWER RATING          | POWER RATING          | POWER RATING          |

|                | (°C/W)                                       | (mW)                  | (mW)                  | (mW)                  |

| TSSOP-14 (MTC) | 155 <sup>(1)</sup>                           | 645 <sup>(3)</sup>    | 355 <sup>(3)</sup>    | 258 <sup>(3)</sup>    |

- (1) Tested per JEDEC EIA/JESD51-1. Thermal resistance is a function of board construction and layout. Air flow reduces thermal resistance. This number is included only as a general guideline; see TI document (SPRA953) device Package Thermal Metrics.

- (2) Thermal resistance to the circuit board is lower. Measured with standard single-sided PCB construction. Board temperature, TB, measured approximately 1 cm from the lead to board interface. This number is provided only as a general guideline.

- (3) Maximum junction temperature, T<sub>J</sub>, equal to 125°C

# **RECOMMENDED OPERATING CONDITIONS<sup>(1)</sup>**

over operating free-air temperature range (unless otherwise noted)

|                   |                                           | MIN | TYP | MAX  | UNIT |

|-------------------|-------------------------------------------|-----|-----|------|------|

| $V_{CC}$          | Input Voltage                             | 7.5 | 14  | 17.5 | ٧    |

| I <sub>BIAS</sub> | BIAS current from a high impedance source |     |     | 500  | μA   |

| I <sub>VAC</sub>  | VAC current from a high impedance source  |     |     | 500  | μA   |

| T <sub>J</sub>    | Operating junction temperature            | -40 | 25  | 125  | °C   |

<sup>(1)</sup> For specified performance limits and associated test conditions, see the Electrical Characteristics table.

# **ELECTROSTATIC DISCHARGE (ESD) PROTECTION**

|                                            | MAX | UNIT |

|--------------------------------------------|-----|------|

| Human Body Model (HBM)                     | 2   | kV   |

| Field Induced Charged Device Model (FICDM) | 750 | V    |

# **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified  $-40^{\circ}\text{C} < \text{T}_{\text{J}} = \text{T}_{\text{A}} < 125^{\circ}\text{C}, \text{ VCC} = 14\text{V}, \text{ V}_{\text{TSNS}} = 1.75\text{V}, \text{ V}_{\text{FLT2}} = 1.75\text{V}, \text{ V}_{\text{AUX}} = 0.5\text{V}, \text{ V}_{\text{INV}} = 0\text{V}, \text{ V}_{\text{INV}} = 0\text{V}, \text{ V}_{\text{VAC}} = 100\mu\text{A}, \text{ I}_{\text{BIAS}} = 100\mu\text{A}, \text{ C}_{\text{VCC}} = 10\mu\text{F}, \text{ C}_{\text{COMP}} = 0.047\mu\text{F}, \text{ R}_{\text{HLD}} = 10\text{k}\Omega.$

|                           | PARAMETER                       | TEST CONDITIONS                                    | MIN  | TYP   | MAX  | UNIT |

|---------------------------|---------------------------------|----------------------------------------------------|------|-------|------|------|

| INPUT SUPPLY (V           | (CC)                            |                                                    |      |       |      |      |

|                           | Rising threshold                |                                                    | 9.5  | 10.5  | 11.5 | V    |

| VCC <sub>(UVLO)</sub>     | Falling threshold               |                                                    | 6.8  | 7.5   | 8.3  | V    |

|                           | Hysteresis                      |                                                    |      | 3     |      | V    |

|                           | Rising threshold                |                                                    | 17.7 | 18.89 | 20.1 | V    |

| VCC <sub>(OVP)</sub>      | Falling threshold               |                                                    | 17.5 | 18.72 | 19.9 | V    |

|                           | Hysteresis                      |                                                    |      | 175   |      | mV   |

|                           | Startup current                 | VCC = 6.7V, V <sub>INV</sub> = 0 V                 |      | 180   |      | μΑ   |

| I <sub>VCC</sub>          | Standby current                 | V <sub>INV</sub> = 1.75V, V <sub>AUX</sub> = 1 V   |      | 1.6   |      | mA   |

|                           | Switching current               | C <sub>GATE</sub> = 1 nF                           |      | 3.3   |      | mA   |

| INPUT VOLTAGE             | FEEDFORWARD and ANGLE DETECTION | (VAC, FF)                                          | 1    |       |      |      |

| VAC <sub>(CLAMP)</sub>    | VAC clamp voltage               |                                                    |      | 1.24  |      | V    |

| I <sub>VAC(ANGLE)</sub>   | Dimmer angle detect threshold   | Sweep I <sub>VAC</sub>                             |      | 66    |      | μΑ   |

| I <sub>VAC(HOLD)</sub>    | HOLD FET turn-on threshold      | Sweep I <sub>VAC</sub> , V <sub>FLT2</sub> = 0 V   |      | 95    |      | μΑ   |

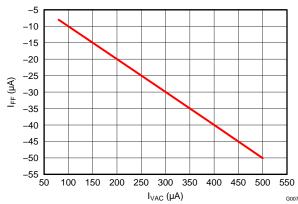

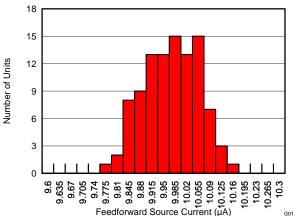

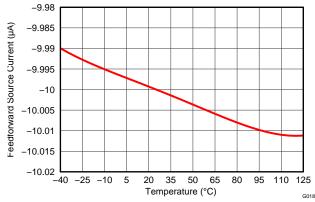

| I <sub>FF</sub>           | Feedforward source current      | V <sub>GATE</sub> = VCC, I <sub>VAC</sub> = 100 μA |      | 10    |      | μΑ   |

| DIMMING DECODI            | ER CIRCUIT (FLT1, FLT2)         |                                                    |      |       |      |      |

| FLT1 <sub>(HIGH)</sub>    | FLT1 voltage high               | FLT1 open                                          | 1.67 | 1.75  | 1.83 | V    |

| FLT2 <sub>(MIN)</sub>     | Minimum dimming decode voltage  | V <sub>FLT2</sub> falling                          | 263  | 290   | 315  | mV   |

| G <sub>(DECODE)</sub>     | Decode gain, VINV/VFLT2         |                                                    |      | 0.877 |      |      |

| FLT2 <sub>HOLD(EN)</sub>  | HOLD circuit enable threshold   | V <sub>FLT2</sub> falling                          |      | 1     |      | V    |

| FLT2 <sub>HOLD(DIS)</sub> | HOLD circuit disable threshold  | V <sub>FLT2</sub> rising                           |      | 1.2   |      | V    |

| HOLD CIRCUIT (H           | OLD)                            |                                                    |      |       |      |      |

| R <sub>DS(ON)</sub>       | HOLD MOSFET on-resistance       | I <sub>VAC</sub> = 50 μA, V <sub>FLT2</sub> = 1 V  |      | 24    |      | Ω    |

| PRE-REGULATOR             | GATE BIAS CIRCUIT (BIAS)        |                                                    |      |       |      |      |

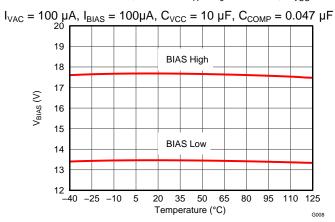

| BIAS <sub>(HIGH)</sub>    | BIAS high voltage clamp         | VCC < VCC <sub>(UVLO)</sub>                        | 16.1 | 17.7  | 19.3 | V    |

| BIAS(LOW)                 | BIAS low voltage clamp          | VCC > VCC <sub>(UVLO)</sub>                        | 12.3 | 13.5  | 14.7 | V    |

# **ELECTRICAL CHARACTERISTICS (continued)**

Unless otherwise specified  $-40^{\circ}\text{C} < T_J = T_A < 125^{\circ}\text{C}, \text{ VCC} = 14\text{V}, \text{ V}_{TSNS} = 1.75\text{V}, \text{ V}_{FLT2} = 1.75\text{V}, \text{ V}_{AUX} = 0.5\text{V}, \text{ V}_{INV} = 0\text{V}, \text{ I}_{VAC} = 100\mu\text{A}, \text{ I}_{BIAS} = 100\mu\text{A}, \text{ C}_{VCC} = 10\mu\text{F}, \text{ C}_{COMP} = 0.047\mu\text{F}, \text{ R}_{HLD} = 10\text{k}\Omega.$

|                                     | PARAMETER                    | TEST CONDITIONS                                       | MIN   | TYP  | MAX   | UNIT |

|-------------------------------------|------------------------------|-------------------------------------------------------|-------|------|-------|------|

| CURRENT SENSE COM                   | MPARATOR (ISNS)              |                                                       |       |      |       |      |

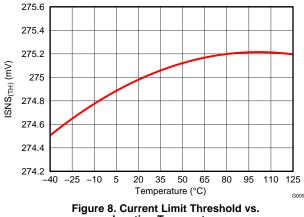

| I <sub>SNS(TH)</sub>                | Current limit threshold      |                                                       | 239   | 275  | 305   | mV   |

| R <sub>ISNS(LEB)</sub>              | ISNS pull down impedance     |                                                       |       | 1.13 |       | kΩ   |

| t <sub>ISNS(LEB)</sub>              | Leading edge blanking time   |                                                       |       | 170  |       | ns   |

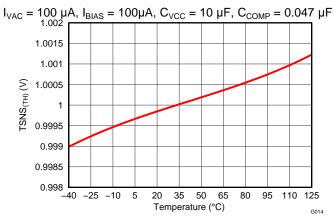

| ERROR AMPLIFIER (IN                 | IV, COMP)                    | ,                                                     | ·     |      |       |      |

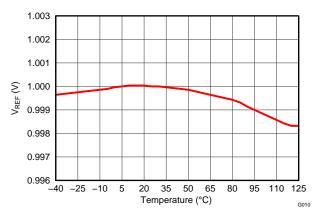

| $V_{REF}$                           | Reference voltage            | V <sub>FLT2</sub> = 1.5 V, V <sub>TSNS</sub> = 1.75 V | 0.95  | 1    | 1.05  | V    |

| I <sub>INV(BIAS)</sub>              | Input bias current           | V <sub>INV</sub> = V <sub>REF</sub>                   |       | 45   |       | nA   |

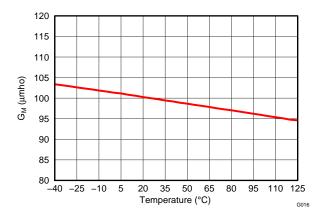

| G <sub>M</sub>                      | Transconductance             | $V_{COMP} = V_{REF}$                                  |       | 100  |       | µmho |

|                                     | Current source capacity      | V <sub>INV</sub> = 0 V                                |       | 77   | 104   | μA   |

| I <sub>COMP</sub>                   | Current sink capacity        | V <sub>INV</sub> = 2V                                 | 50    | 77   |       | μA   |

| COMP(LOW)                           | Minimum PWM ramp voltage     | I <sub>VAC</sub> = 110 μA, V <sub>INV</sub> = 1 V     |       | 280  |       | mV   |

| D <sub>(MAX)</sub>                  | Maximum duty cycle           | I <sub>VAC</sub> = 110 μA, V <sub>INV</sub> = 0 V     |       |      | 76.5% |      |

| VALLEY DETECT CIRC                  | CUIT (AUX)                   |                                                       |       |      |       |      |

| AUX <sub>(OVP)</sub>                | Overvoltage protection       | V <sub>AUX</sub> rising                               | 1.67  | 1.75 | 1.83  | V    |

| t <sub>AUX(LEB)</sub>               | AUX leading edge blanking    |                                                       |       | 1.84 |       | μs   |

| I <sub>AUX(SOURCE)</sub>            | AUX source current           | V <sub>AUX</sub> = -0.3 V                             |       | 207  |       | μA   |

| t <sub>AUX(TO)</sub>                | Valley detect timeout        | V <sub>AUX</sub> = 1 V                                |       | 4    |       | μs   |

| PWM OSCILLATOR AN                   | ID FAULT TIMER               |                                                       |       |      |       |      |

| tosc                                | Oscillator period            |                                                       | 13.9  | 14.5 | 15.1  | μs   |

| t <sub>FAULT</sub>                  | Fault timer                  |                                                       |       | 812  |       | ms   |

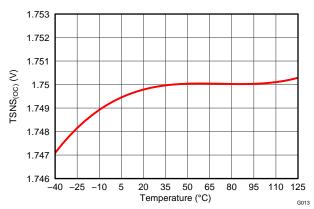

| THERMAL FOLDBACK                    | (TSNS)                       |                                                       |       |      |       |      |

| T <sub>SNS(OC)</sub>                | Open circuit voltage         |                                                       | 1.67  | 1.75 | 1.83  | V    |

| T <sub>SNS(TH)</sub>                | Thermal foldback threshold   | V <sub>TSNS</sub> falling                             | 0.955 | 1    | 1.045 | V    |

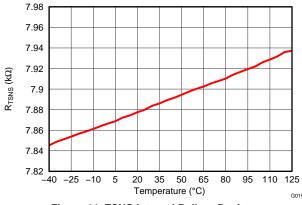

| R <sub>TSNS</sub> <sup>(1)</sup>    | Internal pull-up resistor    | $T_J = 25$ °C                                         | 7.09  | 7.88 | 8.67  | kΩ   |

| THERMAL SHUTDOWN                    | ı                            | •                                                     | ·     |      |       |      |

| T <sub>SD(TH)</sub> (2)             | Thermal shutdown temperature |                                                       |       | 165  |       | °C   |

| T <sub>SD(HYS)</sub> <sup>(2)</sup> | Thermal shutdown hysteresis  |                                                       |       | 25   |       | °C   |

<sup>(1)</sup> Resistance varies with junction temperature and has typical temperature coefficient of 25ppm/°C.

<sup>(2)</sup> Device performance at or near thermal shutdown temperature is not specified or assured.

## **DEVICE INFORMATION**

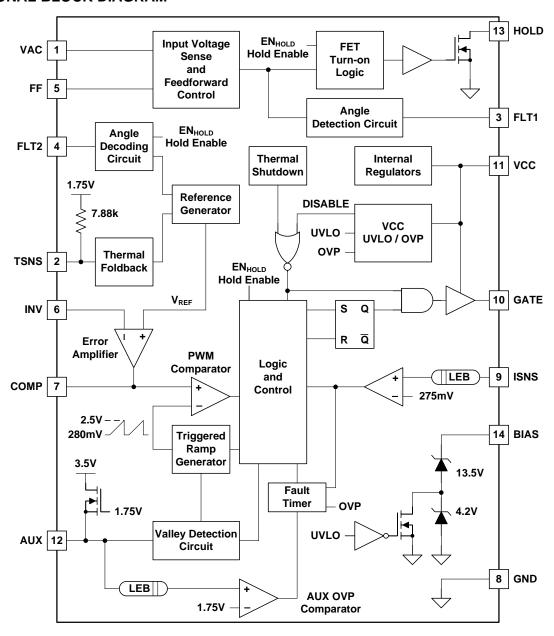

## **FUNCTIONAL BLOCK DIAGRAM**

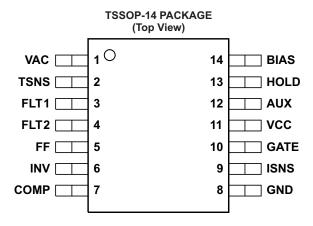

## **PIN CONFIGURATION**

# **PIN FUNCTIONS**

| NO. | NAME | I/O | DESCRIPTION                                                                                                                                                                                                                                        |

|-----|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VAC  | I   | The current at this pin sets the input power level during normal operation. Connect through a resistor to rectified input line voltage.                                                                                                            |

| 2   | TSNS | I   | To implement thermal foldback, connect this pin to an external negative temperature coefficient (NTC) resistor.                                                                                                                                    |

| 3   | FLT1 | 0   | This pin is the output of angle sense comparator. Connect a series resistor from this pin to a capacitor to ground to establish the low pass filter bandwidth.                                                                                     |

| 4   | FLT2 | I   | Connect this pin to the output of low pass filter from FLT1 pin to enable dimming. This pin is an input to the internal dim decoder circuitry. For non-dimming applications connect this pin to TSNS.                                              |

| 5   | FF   | 0   | Connect a parallel resistor and capacitor from this pin to ground to filter twice the line frequency ripple. This is the output of the input voltage feedforward circuitry.                                                                        |

| 6   | INV  | I   | This pin is the input of the internal Gm error amplifier. To implement primary side power regulation, connect this to the FF. To implement secondary side current regulation, connect this pin to the output of opto-isolator circuit.             |

| 7   | COMP | I/O | Output of the Gm error amplifier. Connect a capacitor to ground set desired integral loop compensation bandwidth.                                                                                                                                  |

| 8   | GND  |     | Ground return                                                                                                                                                                                                                                      |

| 9   | ISNS | I   | Connect to the source of the switching MOSEFT and a resistor ground to sense transistor current. Overcurrent protection is engaged when the voltage exceeds 275mV threshold.                                                                       |

| 10  | GATE | 0   | This output provides the gate drive for the power switching MOSEFT.                                                                                                                                                                                |

| 11  | VCC  |     | This is the input to the internal pre-regulator. Connect a bypass capacitor to ground. This pin enables and disables general functions of the LM3447 using the UVLO feature. Device enters overvoltage protection mode when the voltage is >18.9V. |

| 12  | AUX  | I   | This pin is used to sense the auxiliary winding voltage and perform valley switching operation. Overvoltage protection is engaged when the voltage exceeds the threshold of 1.75V during off time.                                                 |

| 13  | HOLD |     | Connect to a holding resistor from the drain of the pre-regulator to this pin. The pin draws current during the zero crossings of the rectified input line voltage.                                                                                |

| 14  | BIAS |     | Connect to external pre-regulator transistor to enable startup. When VCC is below UVLO threshold the pin is clamped to 17.7V. After VCC crosses UVLO threshold the pin is clamped to 13.5V.                                                        |

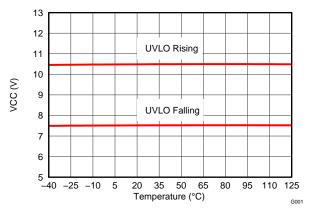

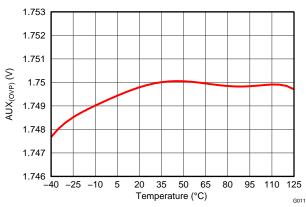

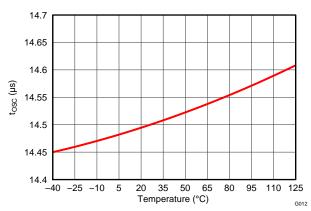

#### TYPICAL CHARACTERISTICS

Unless otherwise stated,  $-40^{\circ}C \leq T_{A} = T_{J} \leq +125^{\circ}C$ ,  $V_{VCC} = 14$  V,  $V_{TSNS} = 1.75$ V,  $V_{FLT2} = 1.75$ V,  $V_{AUX} = 0.5$ V,  $V_{INV} = 0$ V,  $I_{VAC} = 100$   $\mu$ A,  $I_{BIAS} = 100$  $\mu$ A,  $I_{CC} = 10$   $\mu$ F,  $I_{COMP} = 0.047$   $\mu$ F

Figure 1. VCC UVLO vs. Junction Temperature

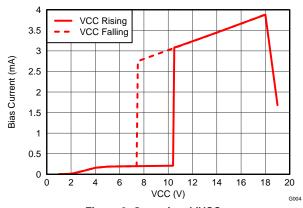

Figure 3. Operational IVCC vs. VCC Voltage

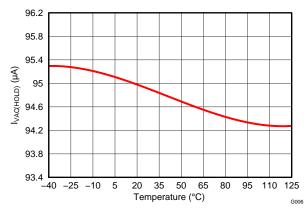

Figure 5. Hold MOSFET Turn-on Threshold Current vs. Junction Temperature

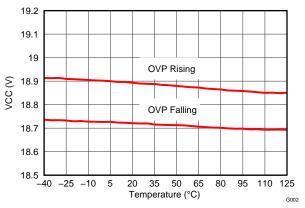

Figure 2. VCC OVP vs. Junction Temperature

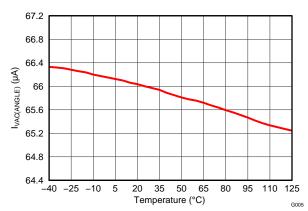

Figure 4. Dimmer Angle Detect Threshold Current vs.

Junction Temperature

Figure 6. Feedforward Source Current ( $I_{FF}$ ) vs. VAC Current ( $I_{VAC}$ )

# **TYPICAL CHARACTERISTICS (continued)**

$Unless \ otherwise \ stated, -40^{\circ}C \leq T_{A} = T_{J} \leq +125^{\circ}C, \ V_{VCC} = 14 \ V, \ V_{TSNS} = 1.75 V, \ V_{FLT2} = 1.75 V, \ V_{AUX} = 0.5 V, \ V_{INV} = 0 V, \ V_{INV}$

Figure 7. BIAS Clamp Voltage vs. **Junction Temperature**

**Junction Temperature**

Figure 9. VREF vs. Junction Temperature

Figure 10. AUX OVP vs. Junction Temperature

Figure 11. Oscillator Period vs. Junction Temperature

Figure 12. TSNS Open Circuit Voltage vs. **Junction Temperature**

# **TYPICAL CHARACTERISTICS (continued)**

Unless otherwise stated,  $-40^{\circ}\text{C} \le \text{T}_{\text{A}} = \text{T}_{\text{J}} \le +125^{\circ}\text{C}, \ \text{V}_{\text{VCC}} = 14 \ \text{V}, \ \text{V}_{\text{TSNS}} = 1.75 \ \text{V}, \ \text{V}_{\text{FLT2}} = 1.75 \ \text{V}, \ \text{V}_{\text{AUX}} = 0.5 \ \text{V}, \ \text{V}_{\text{INV}} = 0 \ \text{V}, \ \text{V}_{\text{INV}} = 0 \ \text{V}$

Figure 13. Thermal Foldback Thershold vs. Junction Temperature

Figure 14. TSNS Internal Pull-up Resistor vs. Junction Temperature

Figure 15. G<sub>M</sub> vs. Junction Temperature

Figure 16. Feedforward Source Current (IFF) Variation (IVAC=100 $\mu$ A, Temperautre = 25°C)

Figure 17. Feedforward Source Current (I<sub>FF</sub>) vs. Junction Temperature

Figure 18. Typical Primary Side Power Regulated Flyback LED Driver

## APPLICATION INFORMATION

#### **DESCRIPTION**

LM3447 is an AC-DC power factor correction (PFC) controller for phase-cut dimmer compatible LED lighting applications. The device incorporates an innovative primary side input power regulation technique for controlling the LED light output over a wide input AC voltage and ambient temperature range. Operating LEDs with constant power allows the controller to compensates for the LED forward voltage variations caused by temperature modulation and LED aging. This also provides improved lamp lumen output maintenance and higher luminous efficacy.

Smooth, flicker free LED dimming is performed by varying the power regulation set-point based on the dimmer phase angle. The device includes internal angle detection and decoding circuitry to accurately interpret the phase angle from a forward phase (leading edge) and reverse phase (trailing edge) based dimmers Power factor correction (PFC) with low input current total harmonic distortion (THD) is maintained by forcing discontinuous conduction mode (DCM) using a trimmed internal oscillator and valley detect circuitry.

These features, along with LED open circuit and short circuit protection, LED thermal foldback and cycle-by-cycle FET overcurrent protection, make the LM3447 an ideal device for implementing a compact single stage isolated Flyback AC-DC LED driver for 5–30W power output range. In addition, it is also possible to configure LM3447 with minor modifications to control SEPIC and Cúk based dimmable AC-DC PFC LED drivers. In this datasheet, a discussion of the LM3447 functionality is presented using a typical Flyback LED driver circuit, as shown in Figure 18.

#### VCC BIAS SUPPLY AND START-UP

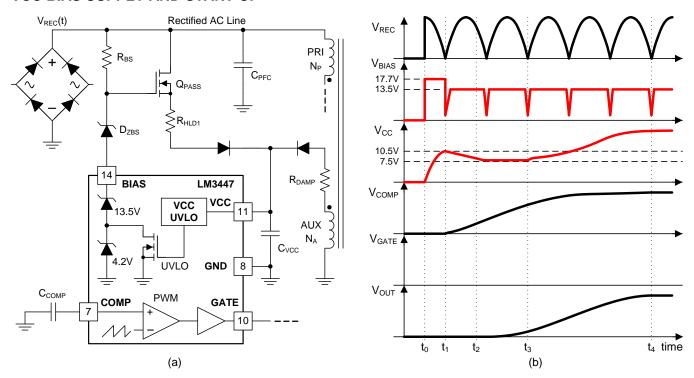

Figure 19. (a) Bias Circuit and (b) Typical Startup Waveforms

The LM3447 is designed to achieve instant turn-on using an external linear regulator circuit, shown in Figure 19 (a). The start-up sequence is internally controlled by the BIAS voltage and VCC undervoltage lockout (UVLO) circuit and is illustrated in Figure 19 (b). The BIAS input is a low current voltage clamp circuit that provides a reference to the linear pass transistor,  $Q_{PASS}$ . The clamp circuit current is set by connecting resistor,  $R_{BS}$ , between the input rectified AC voltage,  $V_{REC}$  and BIAS. When power is applied, the BIAS voltage set to 17.7V and the capacitor,  $C_{VCC}$  is rapidly charged by transistor  $Q_{PASS}$ . Resistor  $R_{HLD1}$  is used to limit the maximum allowable current, based on the safe operating area (SOA) rating of the transistor. The LM3447 starts operating when VCC exceeds the UVLO rising threshold of 10.5V, after which the BIAS voltage is reduced to 13.5V. The GATE drive output is enabled when the COMP voltage exceeds the minimum internal PWM ramp threshold of 280mV. As the output voltage,  $V_{OUT}$ , increases, the bootstrap circuit based on an auxiliary winding of the transformer is energized and begins delivering power to the device. At any time, if VCC falls below 7.5V the device enters a UVLO state forcing BIAS to step back to 17.7V to initiate a new start-up sequence. The switching of BIAS voltage between two thresholds, 17.7V to 13.5V, is performed in association with a large VCC UVLO hysteresis of 3V to allow for a larger variation in auxiliary output voltage.

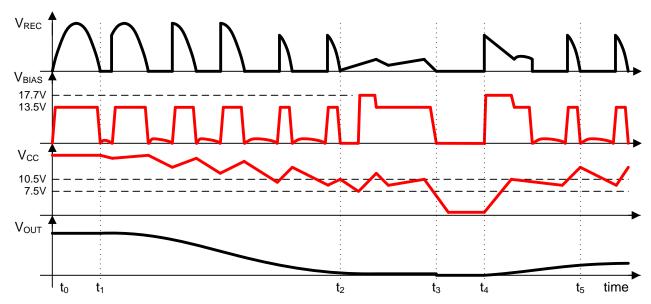

The key waveforms illustrating the bias circuit operation and start-up sequence under dimming are shown in Figure 20. The impact of phase-cut dimming on BIAS, V<sub>OUT</sub> and VCC behavior is highlighted. The chopping of the input voltage by an external dimmer causes the output voltage, V<sub>OUT</sub>, to vary along with LED current. As VCC voltage tracks the output voltage, V<sub>OUT</sub>, it too fluctuates based on the dimming command. At low dimming levels, UVLO is engaged as VCC falls below 7.5V and the BIAS switches to 17.7V, initiating a start-up sequence. The BIAS behavior interacts with the external dimmer circuit, causing the device to enter into a re-start condition, where VCC fluctuates between UVLO high and low thresholds. With this mode of operation, the LM3447 is capable of providing quick response to any changes in the dimming command. In the case where the external dimmer is switched off, VCC is discharged and all of the device operation is ceased. A new start-up cycle is initiated, when the dimmer is switched on and the device responds in the manner illustrated in Figure 19 (b).

Figure 20. Typical Waveforms and Start-up Sequence Under Dimming Conditions

The value of capacitor  $C_{VCC}$  is critical design parameter as it determines VCC ripple voltage during dimming operation. A X7R ceramic capacitor with value ranging from  $22\mu F$  to  $47\mu F$  and 25V voltage rating is recommended for  $C_{VCC}$  as trade-off between size and performance in space constraint applications. At low dimming levels, large VCC voltage ripple and  $Q_{PASS}$  threshold voltage variations can intefere with smooth dimming performance. An external zener doide,  $D_{ZBS}$ , can be placed in series with BIAS to boost VCC voltage and eliminate any observable dimming discontinuities. A low power zener diode ( 200mW) with reverse breakdown voltage ranging from 1.8V to 4.5V is recommended for most dimming application.

#### VCC OVERVOLTAGE PROTECTION

Figure 21. VCC Overvoltage Protection Circuit

The LM3447 has a built-in overvoltage protection (OVP) mode to protect VCC from exceeding its ABS MAX rating under fault conditions. The VCC voltage is monitored by a comparator with a rising threshold of 18.9V and 175mV of hysteresis. Upon detecting an overvoltage condition, GATE is pulled low for duration of 812ms, determined by the internal fault timer. On clearance of the fault, the timer is disabled and normal device operation resumes. An optional damping resistor,  $R_{DAMP}$  in series with the auxiliary winding can be used to prevent transformer leakage current from peak charging  $C_{VCC}$  and false triggering the OVP circuit. Based on the magnitude of leakage inductance a resistor of  $10\Omega$  to  $47\Omega$  should provide proper damping.

#### POWER FACTOR CORRECTION

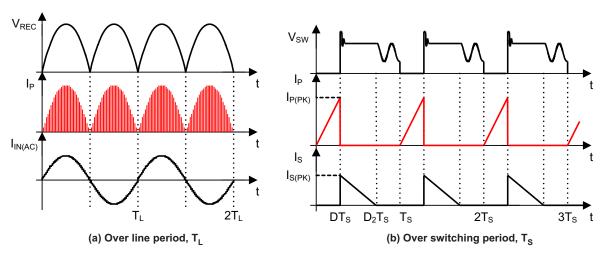

Figure 22. DCM Flyback PFC Waveforms

Power factor correction is performed by operating the Flyback converter in discontinuous conduction mode (DCM). In this mode, the peak primary current, I<sub>P(PK)</sub> is given by

$$I_{P(PK)} = \frac{v_{REC}(t)}{L_{M}}DT_{S} = \frac{\|v_{in}(t)\|}{L_{M}}DT_{S}, \text{ for}$$

$$v_{s}(t) = V_{torus}\sin(\frac{2\pi}{L_{M}}t)$$

(1)

$$v_{in}(t) = V_{IN(PK)} \sin(\frac{2\pi}{T_L}t), \tag{2}$$

where  $v_{IN}(t)$  is the input voltage,  $v_{REC} = ||v_{in}||$  is the rectified input voltage,  $L_M$  is the transformer magnetizing inductance referred to the primary winding, D is the duty cycle,  $T_S$  is the switching period and  $T_L$  is the line period. For a fixed switching frequency controller, if duty cycle D, is held constant over a line cycle, then the peak primary current, I<sub>P(PK)</sub>, varies in proportion to input voltage, v<sub>IN</sub>(t), as shown in Figure 22 (a). The resulting input current, I<sub>IN</sub>, is obtained by averaging the area under primary current, I<sub>P</sub>, shown in Figure 22 (b),

$$i_{in}(t) = \text{Average } (I_P)|_{T_S} = \frac{1}{2} \frac{v_{in}(t)}{L_M} D^2 T_S,$$

(3)

is sinusoidal and in-phase with input voltage, v<sub>IN</sub>(t). As a result, the DCM Flyback converter behaves much like a resistor and exhibits a power factor close to unity.

The input power, P<sub>IN(AVG)</sub> drawn by the Flyback PFC is derived by averaging the product of input voltage, v<sub>in</sub>(t) and input current,  $i_{in}(t)$ , over half line cycle  $T_L/2$ ,

$$\begin{split} P_{\text{IN}(\text{AVG})} &= \frac{2}{T_{L}} \int_{0}^{T_{L/2}} v_{\text{in}}(t) \times i_{\text{in}}(t) dt = \frac{2}{T_{L}} \int_{0}^{T_{L}} \frac{1}{2} \frac{V_{\text{IN}(\text{PK})}^{2} D^{2} T_{\text{S}}}{L_{M}} \sin^{2}(\frac{2\pi}{T_{L}} t) dt; \\ P_{\text{IN}(\text{AVG})} &= \frac{1}{4} \frac{V_{\text{IN}(\text{PK})}^{2} D^{2} T_{\text{S}}}{L_{M}} = \frac{V_{\text{IN}(\text{RMS})}^{2}}{\left(\frac{2L_{M}}{D^{2}T_{\text{S}}}\right)} = \frac{V_{\text{IN}(\text{RMS})}^{2}}{R_{e}}; \ R_{e} = \frac{2L_{M}}{D^{2}T_{\text{S}}}, \end{split}$$

(4)

(5)

The low frequency behavior of the DCM Flyback is defined by an effective resistance, Re. The expression for average input power is given by Equation 5 and is based on Re and the input RMS voltage V<sub>IN(RMS)</sub>. For a single stage Flyback PFC driver, the output power, Pour, delivered to the LED load is a function of the converter efficiency,  $\eta_{FLY}$ , and is given by

$$P_{OUT} = \eta_{FLY} P_{IN}. \tag{6}$$

The average LED current through the string with forward voltage drop V<sub>LED</sub> = V<sub>OUT</sub> is

$$I_{LED(AVG)} = \frac{P_{OUT(AVG)}}{V_{OUT}} = \eta_{FLY} \frac{P_{IN(AVG)}}{V_{OUT}} = \eta_{FLY} \frac{V_{IN(RMS)}^2}{V_{OUT}R_e}, \tag{7}$$

The LED current will have a ripple component varying at twice line frequency due to the PFC operation. The magnitude of the ripple component is based on the energy storage capacitor connected in parallel with the LED string at the output of Flyback PFC. In typical application, a low voltage aluminum electrolytic bulk capacitor is used as an energy storage device and is connected across the LED string to limit the ripple current within an acceptable range.

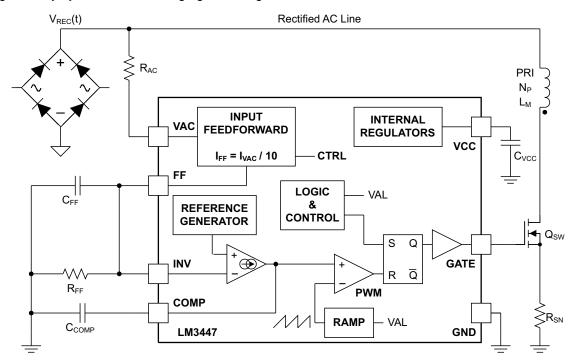

#### INPUT POWER REGULATION AND INPUT VOLTAGE FEEDFORWARD CONTROL

Using the LM3447, it is possible to regulate the LED current by implementing a control scheme using the duty cycle, D, as the control variable. The duty cycle is generated using an internal GM error-amplifier and a fixed frequency, triggered ramp generator, as shown in Figure 23. This technique should not be confused with other current mode control schemes where switch current,  $I_{SW}$ , is used for control.

With the LM3447, LED current can be directly controlled using a series sense resistor and a conventional closed-loop feedback control scheme. Typically, for systems that need galvanic isolation between primary and secondary sides of the transformer, feedback control is complicated and expensive as it requires an additional signal processing amplifier and an opto-isolator. For improved luminous efficacy and simplicity, the LM3447 incorporates an innovative primary side input power regulation scheme based on input voltage feedforward control techniques. By commanding input power, the DCM Flyback PFC output is matched with the LED load characteristics to achieve indirect control of LED string current. The feedforward loop, consisting of input voltage sensing circuitry, the G<sub>M</sub> error amplifier and PWM comparator, is able to reject any input voltage disturbance by adjusting the duty cycle, thus achieving tight line regulation.

Figure 23. Feedforward Control Circuit

The reference power level,  $P_{IN}$ , for the LM3447, is set choosing resistors,  $R_{FF}$  and  $R_{AC}$ , based on the magnetizing inductance,  $L_{M}$ , the internal reference voltage,  $V_{REF}$ , the switching frequency,  $f_{S}$  and the feedforward gain,  $G_{FF}$ , such that

$$\frac{R_{FF}}{R_{AC}} = \frac{\pi}{4} \frac{G_{FF} V_{REF}}{\sqrt{L_M P_{IN} f_S}}$$

(8)

The feedforward gain,  $G_{FF} = I_{VAC}/I_{FF} = 10$  and internal reference voltage  $V_{REF} = 1$  V.

For the above relationship to be valid and for PFC, it is necessary to ensure that the energy in the magnetizing inductor,  $L_{\rm M}$ , is reset every switching cycle and the power stage operates in DCM for the reference power level,  $P_{\rm IN}$ , over the entire range of input voltages. Based on this constraint, the transformer magnetizing inductor should be chosen as

$$L_{M} \leq \frac{V_{REF}}{4P_{IN}f_{S}\left(\frac{1}{nV_{OUT}} + \frac{1}{V_{REC(PK,MIN)}}\right)^{2}},$$

(9)

where n is the transformer primary to secondary turns-ratio,  $V_{OUT} = V_{LED}$  is the LED string voltage and  $V_{REC(PK,MIN)}$  is the minimum peak rectified input voltage. For the LM3447 internal circuit implementation, shown in Figure 23, the reference voltage,  $V_{REF} = 1V$  and the feedforward gain,  $G_{FF} = 10$ . To ensure a robust design and to reject manufacturing variations, a margin of 2% to 10% should be provided when designing the transformer for magnetizing inductance calculated using Equation 9.

A small capacitor,  $C_{FF}$  is connected in parallel with the resistor  $R_{FF}$ , to create a low pass filter that can attenuate twice the line frequency component from the sensed input voltage. It is recommended to set the filter pole frequency between 10–12Hz to provide 20dB attenuation, such that

$$C_{FF} \ge \frac{1}{2\pi (10 \text{ Hz} - 12 \text{ Hz})R_{FF}},$$

(10)

Slow integral compensation is achieved by placing a compensation capacitor  $C_{COMP}$  at the output of the  $G_{M}$  amplifier. A capacitor value ranging from 4.7 $\mu$ F to 10 $\mu$ F is recommended to achieve a low bandwidth loop of 1Hz to 10Hz, based on the power level and transient response.

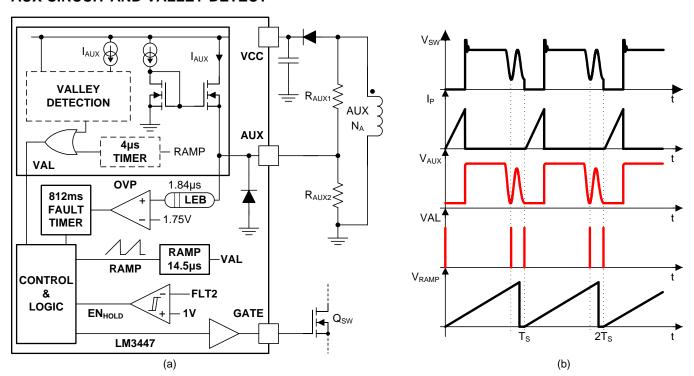

#### **AUX CIRCUIT AND VALLEY DETECT**

Figure 24. (a) AUX Circuit; (b) Valley Switching Waveforms

Valley switching is implemented by connecting the transformer auxiliary winding to the AUX input of LM3447 through a resistor divider network,  $R_{AUX1}$  and  $R_{AUX2}$ , as shown in Figure 24 (a). The valley level is detected by monitoring the current sourced out of the AUX pin when the voltage at the auxiliary winding of the transformer is negative with respect to the GND node. The voltage at this node is clamped at approximately 100mV by the internal circuitry to protect the device during negative voltage excursions of the auxiliary winding. The waveforms in Figure 24(b) illustrate the sequence of events that have to occur for the LM3447 to initiate a new switching cycle.

An internal 14.5 $\mu$ s timer is started at the same time as the switching FET ( $Q_{SW}$ ) is turned on. This 14.5 $\mu$ s timer, set by the internal ramp rise time, is used to set the maximum frequency. After this timer expires the switching FET (QSW) is allowed to turn back on if a valley is detected (VAL) or the 4 $\mu$ s ( $t_{AUX(TO)}$ ) catch timer expires. The catch timer starts immediately after the Ramp signal drops and sets the lowest operating frequency.

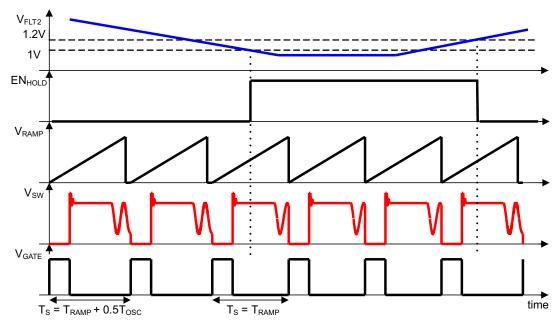

The particular valley (1<sup>st</sup>, 2<sup>nd</sup> ...) in the ringing waveform, where the switch is enabled is a function of the input voltage and varies over the half line cycle. As a result, the AUX circuit shows increased sensitivity where the valley detect signal, VAL, overlaps the Ramp period. Here, the switching point is observed to randomly jump between two adjacent valleys, causing a discrete change in the switching period. Such perturbations in switching frequency cause the switching ripple component of the input current to increase and interfere with phase dimming performance. Therefore, valley switching is disabled and hard switching operation with fixed Ramp period is initiated on detection of external phase dimmers, as shown in Figure 25. The valley switching operation is controlled by the FLT2 input. The operation is disabled when the VFLT2 falls below 1V and is enabled again when it rises above 1.2V. A 200mV hysteresis is provided for noise immunity.

A second function of AUX pin is to program the output overvoltage protection or open-LED detection feature. The output voltage is monitored by sampling the voltage at the auxiliary winding. The voltage is sampled after a fixed delay of 1.84 $\mu$ s, from the falling edge of the GATE drive signal. The leading edge blanking circuit helps reject the voltage transients caused by the leakage energy of the transformer thus preventing false tripping of OVP. The fault condition is detected when the AUX voltage exceeds the internal threshold,  $V_{AUX(OVP)}$  (1.75V). In the case of an overvoltage fault, the switch is turned off for 812ms before attempting to restart the circuit. During this fault period, the compensation capacitor ( $C_{COMP}$ ) is discharged, and the control loop is disabled. When the fault is cleared, the 812ms fault timer is disengaged and the control loop is activated to resume normal operation.

Figure 25. Waveforms Illustrating Valley Switching Enable and Disable Sequence

The sizing of resistor  $R_{AUX1}$  and  $R_{AUX2}$  govern the AUX circuit behavior. Resistor  $R_{AUX1}$  is also used to limit the maximum source current from the AUX pin to 200 $\mu$ A and is based on the maximum input voltage and the transformer primary to auxiliary turns-ratio;

$$R_{AUX1} = \frac{N_A}{N_P} \frac{V_{REC(PK,MAX)}}{200 \times 10^{-6}},$$

(11)

Resistor  $R_{AUX2}$  is then selected to set the desired output overvoltage threshold,  $V_{OUT(OVP)}$  based on the secondary to auxiliary turns-ratio

$$R_{AUX2} = \left(\frac{1.75}{\frac{N_A}{N_S} V_{OUT(OVP)} - 1.75}\right) R_{AUX1},$$

(12)

It is necessary to select the transformer's secondary to auxiliary turns-ratio ( $N_A/N_S$ ) to ensure that  $V_{AUX(OVP)}$  is tripped before  $VCC_{(OVP)}$ .

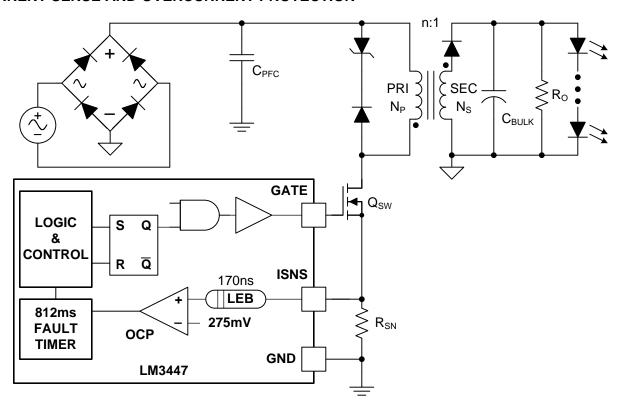

#### **CURRENT SENSE AND OVERCURRENT PROTECTION**

Figure 26. Current Sense Circuit

The LM3447 provides switch overcurrent and LED short circuit protection by sensing the current through the switching transistor,  $Q_{SW}$  via a series connected sense resistor,  $R_{SN}$ , as shown in Figure 26. At the beginning of each switching cycle, the Leading Edge Blanking (LEB) circuit pulls the ISNS input low for approximately 170ns. This prevents false tripping of the protection circuit due to voltage spikes caused by switch turn on transients. The cycle-by-cycle current limit is realized by comparing the sensed voltage at ISNS with the internal 275mV overcurrent protection threshold. When the sense voltage exceeds 275mV, the switch is immediately turned off for a duration of 812ms, set by the fault timer and the COMP capacitor,  $C_{COMP}$  is discharged. Under fault conditions, the LM3447 enters a hiccup mode, attempting to restart the circuit after a duration of 812ms. Upon clearance of the fault, normal operation resumes.

The overcurrent limit is set by selecting the sense resistor,  $R_{SN}$ . It is typical to limit the switch current to two times the maximum peak primary current,  $I_{P(PK,MAX)}$ , where

$$I_{P(PK, MAX)} = 2\sqrt{\frac{P_{IN}T_{S}}{L_{M}}},$$

(13)

and

$$R_{SN} = \frac{275 \times 10^{-3}}{2I_{P(PK,MAX)}}$$

(14)

For R<sub>SN</sub> It is recommended to use a film type SMD resistor, with power rating greater than P<sub>SN</sub> and with low ESL.

# **ANGLE DETECT CIRCUIT**

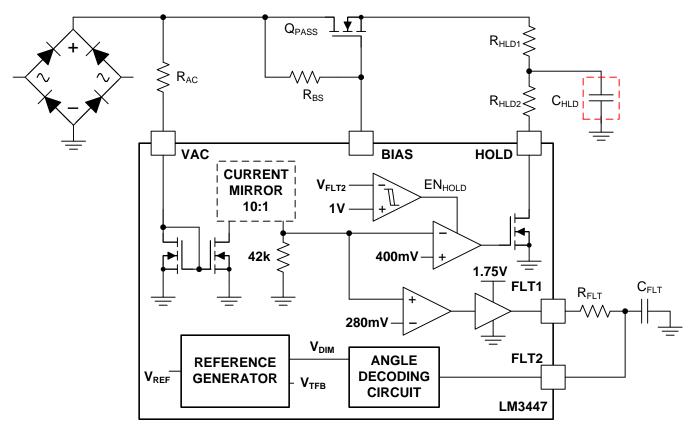

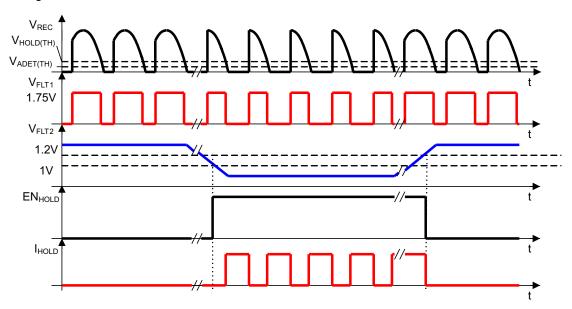

Figure 27. Phase Angle Detection and HOLD Current Circuit

The LM3447 uses the input voltage,  $V_{REC}$ , to detect the conduction phase angle. Figure 27 shows the LM3447 angle detect circuit, where the input voltage,  $V_{REC}$ , is scaled by the current mirror circuits and re-generated across an internal  $42k\Omega$  resistor. This replica of the input voltage is compared with internal 280mV reference to obtain the conduction information. The resulting PWM signal, with its on-time proportional to the conduction period, is buffered and supplied through the FLT1 pin, as shown in Figure 28. To match the external phase dimmer characteristics with the LM3447 decoding circuit and prevent EMI filter capacitors from interfering with dimming operation, it is necessary to select an angle detection threshold,  $V_{ADET(TH)}$ . This threshold can then be programmed using the resistor,  $R_{AC}$ , such that

programmed using the resistor, R<sub>AC</sub>, such that

$$R_{AC} = \frac{V_{ADET}}{I_{VAC(ANGLE)}} = \frac{V_{ADET}}{66 \times 10^{-6}}.$$

(15)

For best results, set V<sub>ADET(TH)</sub> as follows:

- 25V to 40V for 120V systems

- 50V to 80V for 230V systems

Resistor  $R_{AC}$  should also limit the VAC current under worst case operating conditions. The value of  $R_{AC}$  should be optimized to meet both angle detect,  $V_{ADET}$ , and VAC current,  $I_{VAC}$  constraints.

#### HOLD CURRENT CIRCUIT

The LM3447 incorporates an efficient hold current circuit to enhance compatibility with TRIAC based leading edge dimmers. Holding current from an external dimmer is drawn before the Flyback PFC circuit through the pass transistor,  $Q_{PASS}$  and limited by resistors  $R_{HLD1}$  and  $R_{HLD2}$ , as shown in Figure 27. It should be noted that the additional current drawn has no effect on the rectified input voltage and therefore does not interfere with the input power regulation control scheme.

Figure 28. Angle Detection Circuit and Hold Current Circuit Operation

To provide high efficiency, the hold circuit is enabled only when the presence of an external dimmer is detected based on the FLT2 input. The EN<sub>HOLD</sub> signal is asserted and hold operation is permitted when  $V_{FLT2}$  falls below 1V. The hold operation is halted when  $V_{FLT2}$  rises above 1.2V. During dimming, the hold current is drawn during the interval when rectified input voltage is below the  $V_{HOLD(TH)}$ , based on the external resistor  $R_{AC}$ . The FET turnon is controlled by an internal comparator with a reference of 400mV (higher than angle detect reference), such that hold current is always asserted before angle detect threshold  $V_{ADET(TH)}$ . The hold circuit operation is summarized in Figure 28. The hold trun-on threshold,  $V_{HOLD(TH)}$  is given by

$$V_{HOLD(TH)} = R_{AC}I_{VAC(HOLD)} = 95 \times 10^{-6}R_{AC}. \tag{16}$$

The hold current is based on the BIAS voltage and set by the sum of resistors R<sub>HLD1</sub> and R<sub>HLD2</sub>,

$$I_{HOLD} = \frac{13.5 - V_{GS(PASS)}}{(R_{HLD1} + R_{HLD2})}.$$

(17)

In selecting the hold current level, it is critical to consider its impact on the average power dissipation and the operating junction temperature of pass transistor,  $Q_{PASS}$  under worst case operating conditions. The current should be limited to a safe value based on the pass transistor specifications or the ABS MAX rating of LM3447 (70mA). For best performance, it is recommended to set the hold current magnitude between 5mA and 20mA. A capacitor,  $C_{HLD}$  of 2.2 $\mu$ F to 10 $\mu$ F, from  $R_{HLD2}$  to GND is connected to limit the rate of change of input current (di<sub>in</sub>/dt) caused by the step insertion of holding current. This prevents TRIAC based dimmers from misfiring at low dimming level.

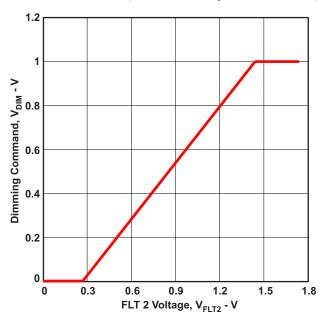

#### ANGLE DECODING CIRCUIT AND DIMMING

The LM3447 incorporates a linear decoding circuit that translates the sensed conduction angle into an internal dimming command,  $V_{DIM}$ . The conduction angle information, represented by the PWM signal at FLT1 output, is processed by an external low pass filter consisting of resistor,  $R_{FLT}$  and capacitor,  $C_{FLT}$ , which attenuates the twice line frequency component from the signal. The resulting analog signal at FLT2 is converted into the dimming command by a linear analog processing circuit. The piecewise linear relationship between the FLT2 input and the dimming command is shown graphically in Figure 29.

The dimming command, V<sub>DIM</sub> is

- held constant at 1V for V<sub>FLT2</sub> ranging from 1.75V to 1.45V (conduction angle 180° to 150°)

- linearly varied with gain of 0.877 for V<sub>FLT2</sub> ranging from 1.45V to 280mV (conduction angle 150° to 30°)

- saturated at 13mV for V<sub>FLT2</sub> lower than 280mV (conduction angle less than 30°)

Figure 29. Relationship Between  $V_{FLT2}$  and  $V_{DIM}$

The relationship implemented by the angle decoding circuit is designed to map the non-linear power behavior of external phase dimmer circuits and enhance Flyback PFC power stage compatibility.

Under normal operating conditions, the dimming command,  $V_{DIM}$  is translated into a reference voltage,  $V_{REF}$ , where  $V_{REF} = V_{DIM}$ . As dimming progresses, the input power commanded by the feedforward loop is modulated in accordance with  $V_{REF}$ . This causes the output power and hence the LED current to vary based on the input conduction angle. Using this feedforward control scheme and the internal angle decoding circuit of the LM3447, it is possible to achieve monotonic, smooth and flicker free dimming with a dimming ratio of more than 50:1.

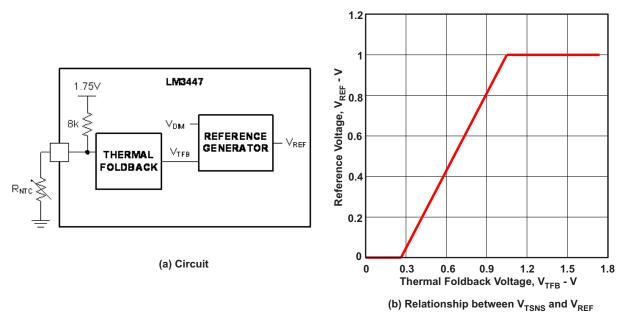

#### THERMAL FOLDBACK CIRCUIT

Thermal protection is necessary to prevent the LEDs and other power supply components from sustaining damage when operated at elevated ambient temperatures. A thermal foldback circuit is incorporated into the LM3447 to limit the maximum operating temperature of the LEDs by scaling the output power based on the heatsink temperature. The LED temperature is sensed using an external NTC resistor,  $R_{NTC}$ , connected between the TSNS pin and GND, as shown in Figure 30(a). The thermal protection is engaged when the TSNS voltage decreases below the thermal foldback threshold voltage,  $V_{TSNS(TH)}$ , of 1V. The power is scaled by adjusting the reference voltage,  $V_{REF}$ , based on the thermal foldback output voltage,  $V_{TFB}$ , according to the relationship shown in Figure 30(b). The resistor value,  $R_{NTC(BK)}$ , at which the device enters thermal protection is fixed by the internal 7.88k $\Omega$  pull-up resistor and the TSNS reference voltage,  $V_{TSNS(REF)}$  and is given by

$$R_{NTC} = \frac{7.88 \text{ k}\Omega}{V_{TSNS(REF)} - V_{TSNS(TH)}} = 10.5 \text{ k}\Omega$$

(18)

The temperature break-point,  $T_{BK}$  and rate-of-change (slope) are governed by the non-linear characteristics of the NTC resistor,  $R_{NTC}$ , given by its  $\beta$ -value. To achieve a break-point temperature,  $T_{BK}$ , the NTC resistor,  $R_{NTC}$  should selected as

$$R_{NTC(T_0)} = \frac{R_{NTC(BK)}}{\exp\left[\beta\left(\frac{1}{T_{BK}} - \frac{1}{T_0}\right)\right]}.$$

(19)

where,  $T_o$  is the room temperature in Kelvin, and  $R_{NTC(To)}$  is the NTC value at room temperature. A temperature break-point ranging from 70°C (343K) to 90°C (363K) can be achieved by selecting an NTC resistance ranging from 100k $\Omega$  to 220k $\Omega$  and  $\beta$ -value of 3500K to 4500K.

Figure 30. Thermal Foldback

The precedence between the thermal foldback input,  $V_{TFB}$  and the dimming input,  $V_{DIM}$ , is decided by the reference generator circuit. This allows dimming operation to be performed when thermal protection is engaged. Dimming operation is allowed when the input power demanded by the decoder circuit,  $V_{DIM}$ , is lower than the maximum power limit set by the thermal protection circuit,  $V_{TFB}$ . This feature provides optimal lamp utilization under adverse operating conditions.

#### **OUTPUT BULK CAPACITOR**

The output bulk capacitor, C<sub>BULK</sub>, is required to store energy during the input voltage zero crossing interval and limit twice the line frequency ripple component flowing through the LEDs. The value of output capacitor is given by

$$C_{BULK} \ge \frac{P_{IN}}{2\pi f_L R_{LED} V_{OUT} I_{LED(RIP)}},$$

(20)

where,  $R_{LED}$  is the dynamic resistance of LED string,  $I_{LED(RIP)}$  is the average to peak LED ripple current and  $f_L$  is line frequency. In typical applications, the solution size becomes a limiting factor and dictates the maximum dimensions of the bulk capacitor. When selecting an electrolytic capacitor, manufacturer recommended de-rating factors should be applied based on the worst case capacitor ripple current, output voltage and operating temperature to achieve the desired operating lifetime.

It is essential to provide a minimum load at the output of the PFC to discharge the capacitor after the power is switched off or during LED open circuit failures. A  $20k\Omega$  resistor,  $R_0$ , is recommended for best performance.

# DESIGN PROCEDURE (1)(2)

| STEP | VARIABLE               | DESCRIPTION                                                                                                                                                                                                                                |

|------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | P <sub>IN</sub>        | $P_{IN} = \frac{V_{OUT}I_{LED}}{\eta_{ELY}}$                                                                                                                                                                                               |

|      |                        | where $V_{OUT} = V_{LED} = Typical LED string voltage,$                                                                                                                                                                                    |

|      |                        | I <sub>LED</sub> is the average LED current,                                                                                                                                                                                               |

|      |                        | $ \eta_{\text{TOT}} = \eta_{\text{EMI}} \times \eta_{\text{FLY}}, $ in the LED divine efficiency $\eta_{\text{TOT}}$ in the EMI input filter efficiency and $\eta_{\text{TOT}}$ in the EMI input filter efficiency and $\eta_{\text{TOT}}$ |

| 2    | D <sub>MAX</sub>       | $\eta_{TOT}$ is the LED driver efficiency, $\eta_{EMI}$ is the EMI input filter efficiency and $\eta_{FLY}$ is the Flyback PFC efficiency.  0.4 < $D_{MAX}$ < 0.5                                                                          |

| 2    | DMAX                   | where DMAX is the maximum allowable Flyback PFC duty cycle                                                                                                                                                                                 |

| 3    | n:1                    | $n = \frac{D_{MAX}}{1 - D_{MAX}} \frac{V_{REC(PK,MIN)}}{V_{OUT}},$                                                                                                                                                                         |

|      |                        |                                                                                                                                                                                                                                            |

|      |                        | $V_{SW} = nV_{OUT} + V_{REC(PK,MAX)} + V_{OS}$ and $V_{SW} < Maximum FET$ (Q1) breakdown voltage.                                                                                                                                          |

|      |                        | n is the transformer turns-ratio,                                                                                                                                                                                                          |

|      |                        | V <sub>REC(PK,MIN)</sub> is the minimum peak rectified input voltage,<br>V <sub>REC(PK,MAX)</sub> is the maximum peak rectified input voltage,                                                                                             |

|      |                        | V <sub>IN(RMS,MIN)</sub> is the minimum input RMS voltage,                                                                                                                                                                                 |

|      |                        | V <sub>IN(RMS,MAX)</sub> is the maximum input RMS voltage, V <sub>SW</sub> is the switch drain to source voltage,                                                                                                                          |

|      |                        | V <sub>OS</sub> is the overshoot voltage because of leakage inductance.                                                                                                                                                                    |

| 4    | L <sub>M</sub>         | $L_{M} \leq \frac{V_{REF}}{4P_{IN}f_{S}\left(\frac{1}{nV} + \frac{1}{V}\right)^{2}},$                                                                                                                                                      |

|      |                        | $\frac{4P_{IN}J_{S}}{nV_{OUT}} + \frac{1}{V_{REC(PK,MIN)}}$                                                                                                                                                                                |

|      |                        | where $V_{REF}$ is the internal reference voltage; $V_{REF} = 1V$ ,                                                                                                                                                                        |

|      |                        | $f_S$ is the fixed switching frequency; $f_S = 70$ kHz.                                                                                                                                                                                    |

| 5    | I <sub>P(PK,MAX)</sub> | $I_{P(PK,MAX)} = 2\sqrt{\frac{P_{IN}T_{S}}{L_{M}}},$                                                                                                                                                                                       |

|      |                        | where                                                                                                                                                                                                                                      |

|      |                        | $T_S$ is the switching period, $T_S = 1/f_S$                                                                                                                                                                                               |

| 8    | $N_P$ , $N_A$ , $N_S$  | Transformer Design                                                                                                                                                                                                                         |

|      |                        | Core geometry (EE, PQ, RM)                                                                                                                                                                                                                 |

|      |                        | Bobbin (UL Class B or Class F)                                                                                                                                                                                                             |

|      |                        | L <sub>M</sub> is the magnetizing inductance referred to primary side n:1 = N <sub>P</sub> :N <sub>S</sub> , primary to secondary winding turns-ratio                                                                                      |

|      |                        | $N_A = \frac{VCC}{V_{OUT}} N_S$ , where $N_A$ is the auxiliary winding turns                                                                                                                                                               |

|      |                        | $B_{MAX}$ < 0.3T, where $B_{MAX}$ is the maximum operating flux density corresponding to $I_{P(PK,MAX)}$                                                                                                                                   |

<sup>(1)</sup> See the Electrical Characteristics Table for all constants and measured values, unless otherwise noted.

(2) See Figure 18 for all component locations in the Design Procedure Table.

## www.ti.com.cn

| STEP | VARIABLE                              | DESCRIPTION                                                                                                         |

|------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 6    | $R_{AC}$                              | $R_{AC} = \frac{V_{ADET}}{I}$                                                                                       |

|      |                                       | IVAC(ANGLE)                                                                                                         |

|      |                                       | where                                                                                                               |

|      |                                       | V <sub>ADET</sub> is the angle detection voltage;  • 25V to 40V for 120V system                                     |

|      |                                       | • 50V to 80V for 230V system                                                                                        |

|      |                                       | I <sub>VAC(ANGLE)</sub> is the angle detection threshold,                                                           |

|      |                                       | and $\frac{V_{REC(PK,MAX)}}{R_{AC}} \le 500 \mu\text{A}$                                                            |

| 7    | R <sub>FF</sub>                       | $R_{FF} = \frac{\pi}{4} \frac{G_{FF} V_{REF}}{\sqrt{L_M P_{IN} f_S}} R_{AC},$                                       |

|      |                                       | where                                                                                                               |

|      |                                       | $G_{FF}$ is the gain of Feedforward circuit; $G_{FF} = 10$ .                                                        |

| 8    | $C_{FF}$                              | $C_{FF} \leq \frac{1}{2\pi (10 \text{ Hz} - 12 \text{ Hz})R_{FF}},$                                                 |

|      |                                       | $2\pi (10 \text{ Hz} - 12 \text{ Hz})R_{\text{FF}}$                                                                 |

| 9    | $C_{COMP}$                            | $4.7\mu\text{F} \le C_{\text{COMP}} \le 10\mu\text{F}$                                                              |

| 10   | $Q_{PASS}$ , $R_{HLD1}$               | $V_{DS(PASS)} = 1.2 V_{REC(PK,MAX)}$                                                                                |

|      |                                       | $R_{HLD1} = \frac{V_{BIAS(HIG)} - V_{GS(PASS)}}{I_{SOA(PASS)}},$                                                    |

|      |                                       | where                                                                                                               |

|      |                                       | V <sub>GS(PASS)</sub> is the drain to source withstand voltage of pass transistor, Q <sub>PASS</sub> ,              |

| 44   |                                       | I <sub>SOA(PASS)</sub> is the maximum current through pass transistor based on safe operating area characteristics. |

| 11   | $R_{BS}$                              | $R_{BS} = \frac{V_{REC(PKMAX)}}{I}$                                                                                 |

|      |                                       | I <sub>BIAS</sub>                                                                                                   |

|      |                                       | where, $I_{BIAS}$ is the BIAS current and $I_{BIAS} \le 500 \mu A$                                                  |

| 12   | R <sub>AUX1</sub> , R <sub>AUX2</sub> |                                                                                                                     |

|      |                                       | $R_{AUX1} = \frac{N_A}{N_P} \frac{V_{\text{REC}(PK, MAX)}}{200 \times 10^6},$                                       |

|      |                                       |                                                                                                                     |

|      |                                       | $R_{AUX2} = \left(\frac{1.75}{N}\right) R_{AUX1},$                                                                  |

|      |                                       | $\left(\frac{N_A}{N_c}V_{OUT(OVP)}-1.75\right)^{(AUX1)}$                                                            |

|      |                                       | , s                                                                                                                 |

|      |                                       | where, V <sub>OUT(OVP)</sub> is the maximum output voltage under OVP condition                                      |

| 13   | R <sub>SN</sub>                       | $275 \times 10^{-3}$                                                                                                |

|      |                                       | $R_{SN} = \frac{210 \text{ M}}{2I_{P(PK,MAX)}}$                                                                     |

| 14   | R <sub>FLT</sub> , C <sub>FLT</sub>   | $R_{FLT} = 280 \text{ k}\Omega, C_{FLT} = 0.1 \mu\text{F}$                                                          |

| 15   | R <sub>HOLD</sub>                     |                                                                                                                     |

|      |                                       | $R_{HLD2} = \frac{13.5 - V_{GS(PASS)}}{I_{HOLD}} - R_{HLD1}$                                                        |

|      |                                       | where,                                                                                                              |

|      |                                       | I <sub>HOLD</sub> is the holding current drawn through the external phase dimmer circuit                            |

# ZHCS867 A -APRIL 2012-REVISED MAY 2012

| STEP | VARIABLE                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16   | R <sub>NTC</sub>                   | $R_{NTC(T_o)} = \frac{R_{NTC(BK)}}{exp\left[\beta\left(\frac{1}{T_{BK}} - \frac{1}{T_o}\right)\right]},$ where,                                                                                                                                                                                                                                                                                                                                      |

|      |                                    | $R_{NTC(BK)} = 10.5 \text{ k}\Omega$ , is the fixed break point resistance, $T_{BK}$ is the break point temperature in Kelvin, $T_{O}$ is the room temperature in Kelvin, $R_{NTC(To)}$ is the manufacturer specified NTC resistance at room temperature, $\beta$ is the NTC resistor characteristics specified by the manufacturer.                                                                                                                 |

| 17   | C <sub>BULK</sub> , R <sub>O</sub> | $C_{\text{BULK}} \leq \frac{P_{\text{IN}}}{2\pi \int_{L} R_{\text{LED}} V_{\text{OUT}} I_{\text{LED(RIP)}}},$ where, $I_{\text{LED(RIP)}} \text{ is the average to peak magnitude of twice the line frequency current ripple through LED,} \\ R_{\text{LED}} \text{ is the dynamic resistance of the LED string,} \\ f_{\text{L}} \text{ is the line frequency} \\ R_{\text{O}} = 20 \text{ k}\Omega, \text{ is the recommended bleeder resistance}$ |

# **REVISION HISTORY**

| Changes from Original (April 2012) to Revision A |                  |   |  |  |  |

|--------------------------------------------------|------------------|---|--|--|--|

| •                                                | 将器件状态从:产品预览改为:生产 | 1 |  |  |  |

www.ti.com 11-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/               | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|-----------------|-----------------------|------|---------------|---------------------------|--------------|--------------|

|                       | (1)    | (2)           |                 |                       | (3)  | Ball material | Peak reflow               |              | (6)          |

| LM3447MT/NOPB         | Active | Production    | TSSOP (PW)   14 | 94   TUBE             | Yes  | NIPDAU   SN   | (5)<br>Level-1-260C-UNLIM | -40 to 125   | L3447<br>MT  |

| LM3447MT/NOPB.A       | Active | Production    | TSSOP (PW)   14 | 94   TUBE             | Yes  | NIPDAU        | Level-1-260C-UNLIM        | -40 to 125   | L3447<br>MT  |

| LM3447MTE/NOPB        | Active | Production    | TSSOP (PW)   14 | 250   SMALL T&R       | Yes  | NIPDAU   SN   | Level-1-260C-UNLIM        | -40 to 125   | L3447<br>MT  |

| LM3447MTE/NOPB.A      | Active | Production    | TSSOP (PW)   14 | 250   SMALL T&R       | Yes  | NIPDAU        | Level-1-260C-UNLIM        | -40 to 125   | L3447<br>MT  |

| LM3447MTX/NOPB        | Active | Production    | TSSOP (PW)   14 | 2500   LARGE T&R      | Yes  | NIPDAU   SN   | Level-1-260C-UNLIM        | -40 to 125   | L3447<br>MT  |

| LM3447MTX/NOPB.A      | Active | Production    | TSSOP (PW)   14 | 2500   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM        | -40 to 125   | L3447<br>MT  |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# PACKAGE OPTION ADDENDUM

www.ti.com 11-Nov-2025

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 31-Jul-2025

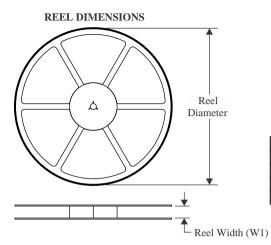

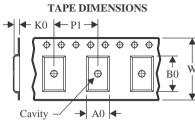

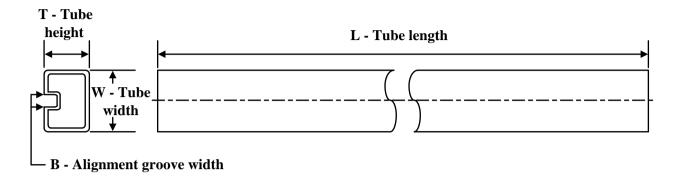

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

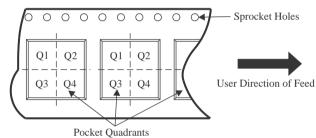

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM3447MTE/NOPB | TSSOP           | PW                 | 14 | 250  | 177.8                    | 12.4                     | 6.95       | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| LM3447MTX/NOPB | TSSOP           | PW                 | 14 | 2500 | 330.0                    | 12.4                     | 6.95       | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

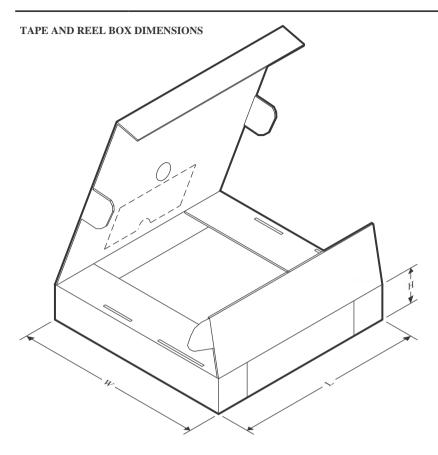

**PACKAGE MATERIALS INFORMATION**

www.ti.com 31-Jul-2025

# \*All dimensions are nominal

| Device Package Type |       | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---------------------|-------|-----------------|------|------|-------------|------------|-------------|--|

| LM3447MTE/NOPB      | TSSOP | PW              | 14   | 250  | 208.0       | 191.0      | 35.0        |  |

| LM3447MTX/NOPB      | TSSOP | PW              | 14   | 2500 | 367.0       | 367.0      | 35.0        |  |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 31-Jul-2025

# **TUBE**

\*All dimensions are nominal

| Device          | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|-----------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| LM3447MT/NOPB   | PW           | TSSOP        | 14   | 94  | 495    | 8      | 2514.6 | 4.06   |

| LM3447MT/NOPB   | PW           | TSSOP        | 14   | 94  | 530    | 10.2   | 3600   | 3.5    |

| LM3447MT/NOPB.A | PW           | TSSOP        | 14   | 94  | 495    | 8      | 2514.6 | 4.06   |

| LM3447MT/NOPB.A | PW           | TSSOP        | 14   | 94  | 530    | 10.2   | 3600   | 3.5    |

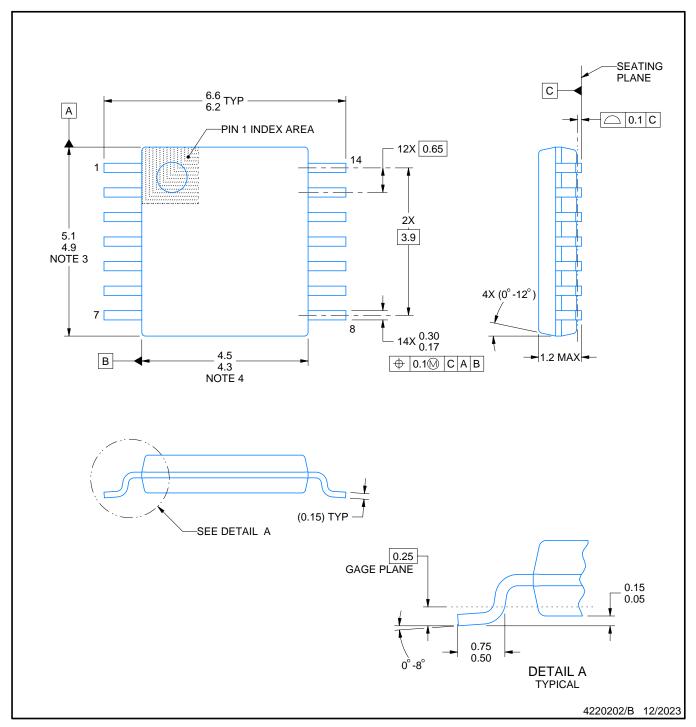

SMALL OUTLINE PACKAGE

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

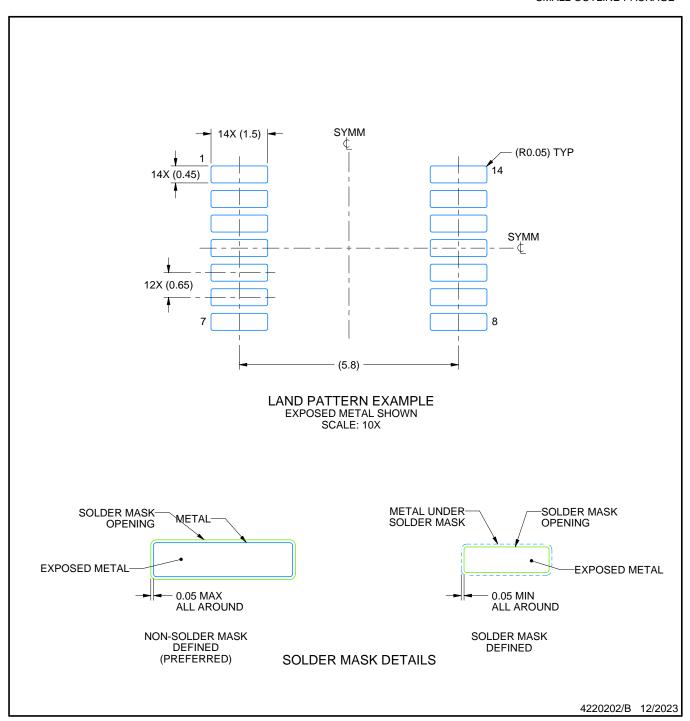

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

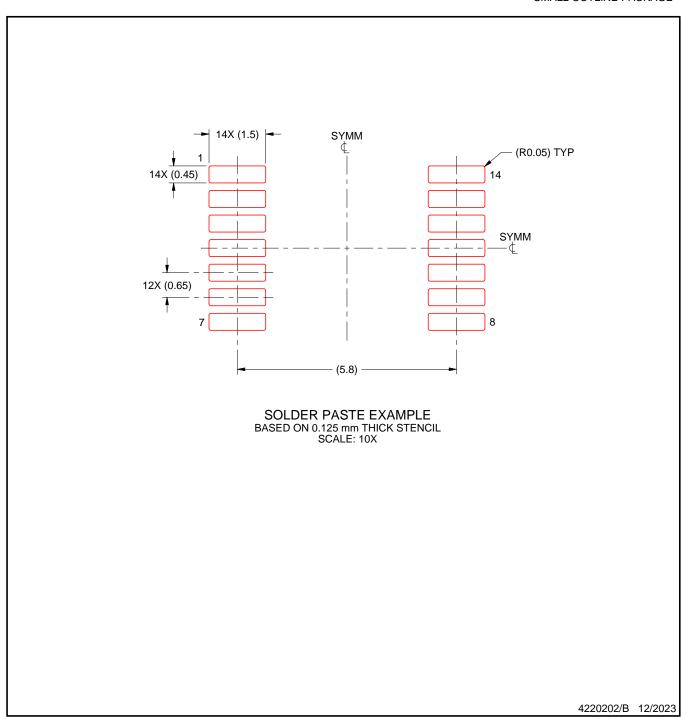

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

# 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月