**ISO124**

ZHCSID3E - SEPTEMBER 1997-REVISED JUNE 2018

# ISO124 ±10V 输入精密隔离放大器

#### 特性

- 100% 经过高电压击穿测试

- 额定 1500Vrms

- 高 IMR: 频率 60Hz 时为 140dB

- 非线性: 0.010% (最大值)

- 双极运算:  $V_0 = \pm 10V$

- 封装: PDIP-16 和 SOIC-28

- 易用性: 固定单位增益配置

- 电源范围: ±4.5V 至 ±18V

## 2 应用

- 工业过程控制:

- 变送器隔离器、热电偶隔离器、RTD、压力电 桥和流量计,4mA 至 20mA 环路隔离

- 消除接地环路

- 电机和 SCR 控制

- 电源监控

- 基于 PC 的数据采集

- 测试设备

## 3 说明

ISO124 是一款高精度隔离放大器,该放大器采用了全 新的占空比调制-解调技术。信号以数字的形式通过 2pF 差动电容隔离层进行传输。通过数字调制,其隔 离层特点不但不会影响信号完整性,而且为隔离层提供 出色的可靠性和优秀的高频瞬变抗扰性。两种隔离层电 容器都嵌入到封装的塑料主体内。

ISO124 易于使用。无需外部组件即可运行。以下是其 重要规格: 最大 0.010% 的非线性值、50kHz 信号带 宽和 200μV/°C V<sub>OS</sub> 漂移。ISO124 器件提供 ±4.5V 至 ±18V 的电源范围, ±5mA(采用 V<sub>S1</sub> 时)和 ±5.5mA (采用 V<sub>S2</sub> 时)静态电流,广泛适用于各种应用。

ISO124 采用 16 引脚 PDIP 和 28 引线 SOIC 塑料表 面贴装封装。

#### 器件信息(1)

| 器件型号   | 封装        | 封装尺寸 (标称值)       |  |  |  |

|--------|-----------|------------------|--|--|--|

| ISO124 | PDIP (16) | 17.90mm × 7.50mm |  |  |  |

| 150124 | SOIC (28) | 20.01mm × 6.61mm |  |  |  |

(1) 要了解所有可用封装,请参见数据表末尾的封装选项附录。

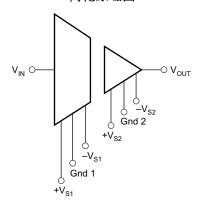

#### 简化原理图

| 714 |

|-----|

| 7   |

| 1 | 特性1                                  | 8 Application and Implementation 1  |

|---|--------------------------------------|-------------------------------------|

| 2 | 应用 1                                 | 8.1 Application Information 1       |

| 3 | 说明1                                  | 8.2 Typical Applications 1          |

| 4 | 修订历史记录                               | 9 Power Supply Recommendations 1    |

| 5 | Pin Configuration and Functions      | 9.1 Signal and Supply Connections 1 |

| 6 | Specifications4                      | 10 Layout 2                         |

| • | 6.1 Absolute Maximum Ratings         | 10.1 Layout Guidelines2             |

|   | 6.2 ESD Ratings                      | 10.2 Layout Example2                |

|   | 6.3 Recommended Operating Conditions | 11 器件和文档支持 2                        |

|   | 6.4 Thermal Information              | 11.1 文档支持 2                         |

|   | 6.5 Electrical Characteristics5      | 11.2 接收文档更新通知2                      |

|   | 6.6 Typical Characteristics6         | 11.3 社区资源2                          |

| 7 | Detailed Description8                | 11.4 商标 2                           |

|   | 7.1 Overview 8                       | 11.5 静电放电警告 2                       |

|   | 7.2 Functional Block Diagram9        | 11.6 术语表 2                          |

|   | 7.3 Feature Description9             | <b>12</b> 机械、封装和可订购信息2              |

|   | 7.4 Device Functional Modes9         |                                     |

# 4 修订历史记录

## Changes from Revision D (July 2016) to Revision E

## Page

| • | 已更改 将 16 引脚 SOIC 封装更改为 16 引脚 PDIP 封装,以便与数据表最后的封装选项附录中显示的产品相匹配                                                                                                                                      | 1   |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| • | Changed DVA and NVF pin configuration labels to match content shown in the package option addendum at the end of the data sheet                                                                    | . 3 |

| • | Changed parameter name from "vs temperature" to "Input offset drift" in Electrical Characteristics table                                                                                           | 5   |

| • | Changed parameter name from "vs power supply" to "Power-supply rejection ratio" in <i>Electrical Characteristics</i> table                                                                         | 5   |

| • | Changed location of supply voltage specifications from the <i>Electrical Characteristics</i> table to the <i>Recommended Operating Conditions</i> table                                            | 5   |

| • | Changed parameter name from "Quiescent current" to "High-side analog supply current", and changed symbol from "V <sub>S1</sub> " to "I <sub>VS1</sub> " in <i>Electrical Characteristics</i> table | 5   |

| • | Changed parameter name from "Quiescent current" to "Low-side analog supply current", and changed symbol from "V <sub>S2</sub> " to "I <sub>VS2</sub> " in Electrical Characteristics table         | 5   |

| • | Changed location of Temperature specifications from the <i>Electrical Characteristics</i> table to the <i>Recommended Operating Conditions</i> table                                               | 5   |

| • | Deleted Thermal resistance parameters from <i>Electrical Characteristics</i> table; see <i>Thermal Information</i> table                                                                           | 5   |

## Changes from Revision C (September 2005) to Revision D

Page

# 5 Pin Configuration and Functions

## **Pin Functions**

|                  | PIN  |      | I/O | DESCRIPTION                      |  |  |

|------------------|------|------|-----|----------------------------------|--|--|

| NAME             | PDIP | SOIC | 1/0 | DESCRIPTION                      |  |  |

| Gnd 1            | 16   | 28   | _   | High-side ground reference       |  |  |

| Gnd 2            | 8    | 14   | _   | Low-side ground reference        |  |  |

| V <sub>IN</sub>  | 15   | 27   | ı   | High-side analog input           |  |  |

| V <sub>OUT</sub> | 7    | 13   | 0   | Low-side analog output           |  |  |

| +V <sub>S1</sub> | 1    | 1    | _   | High-side positive analog supply |  |  |

| -V <sub>S1</sub> | 2    | 2    | _   | High-side negative analog supply |  |  |

| +V <sub>S2</sub> | 9    | 15   | _   | Low-side positive analog supply  |  |  |

| -V <sub>S2</sub> | 10   | 16   | _   | Low-side negative analog supply  |  |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                       | MIN | MAX        | UNIT |

|---------------------------------------|-----|------------|------|

| Supply voltage                        |     | ±18        | V    |

| Analog input voltage, V <sub>IN</sub> |     | 100        | V    |

| Continuous isolation voltage          |     | 1500       | Vrms |

| Junction temperature                  |     | 125        | °C   |

| Output short to common                |     | Continuous |      |

| Storage temperature, T <sub>stg</sub> | -40 | 125        | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| V                  | Floatractatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±1000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                                            | MIN  | NOM | MAX | UNIT |

|----------------|------------------------------------------------------------|------|-----|-----|------|

| $V_{S1}$       | High-side analog supply voltage (±V <sub>S1</sub> to GND1) | ±4.5 | ±15 | ±18 | V    |

| $V_{S2}$       | Low-side analog supply voltage (±V <sub>S2</sub> to GND2)  | ±4.5 | ±15 | ±18 | ٧    |

| $V_{IN}$       | Analog input voltage                                       |      | ±10 |     | ٧    |

| T <sub>A</sub> | Operating temperature                                      | -25  |     | 85  | °C   |

#### 6.4 Thermal Information

|                      |                                              | ISO124     |            |      |  |

|----------------------|----------------------------------------------|------------|------------|------|--|

|                      | THERMAL METRIC <sup>(1)</sup>                | DVA (SOIC) | NVF (PDIP) | UNIT |  |

|                      |                                              | 28 PINS    | 16 PINS    |      |  |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 79.8       | 51.0       | °C/W |  |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 32.9       | 32.4       | °C/W |  |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 42.2       | 29.5       | °C/W |  |

| ΨЈТ                  | Junction-to-top characterization parameter   | 6.6        | 10.4       | °C/W |  |

| ΨЈВ                  | Junction-to-board characterization parameter | 40.9       | 29.0       | °C/W |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.5 Electrical Characteristics

at  $T_A$  = +25°C ,  $V_{S1}$  =  $V_{S2}$  = ±15 V, and  $R_L$  = 2 k $\Omega$  (unless otherwise noted)

|                  | PARAMETER                       | TEST CONDITIONS                           | MIN      | TYP                   | MAX    | UNIT                  |

|------------------|---------------------------------|-------------------------------------------|----------|-----------------------|--------|-----------------------|

| ISOL             | ATION                           |                                           | <u> </u> |                       |        |                       |

|                  | Rated voltage                   | Continuous ac 60 Hz                       | 1500     |                       |        | Vac                   |

|                  | 100% test <sup>(1)</sup>        | Test time = 1 s, partial discharge ≤ 5 pC | 2400     |                       |        | Vac                   |

|                  | Isolation mode rejection        | 60 Hz                                     |          | 140                   |        | dB                    |

|                  | Barrier impedance               |                                           |          | 10 <sup>14</sup>    2 |        | $\Omega \parallel pF$ |

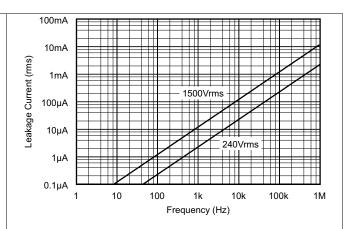

|                  | Leakage current at 60 Hz        | V <sub>ISO</sub> = 240 Vrms               |          | 0.18                  | 0.5    | μArms                 |

| GAIN             |                                 |                                           | -        |                       | •      |                       |

|                  | Nominal gain                    | V <sub>O</sub> = ±10 V                    |          | 1                     |        | V/V                   |

|                  | Gain error                      | V <sub>O</sub> = ±10 V                    |          | ±0.05                 | ±0.50  | %FSR                  |

|                  | Gain vs temperature             |                                           |          | ±10                   |        | ppm/°C                |

|                  | Nonlinearity (2)                |                                           |          | ±0.005                | ±0.010 | %FSR                  |

| INPU             | T OFFSET VOLTAGE                |                                           |          |                       |        |                       |

|                  | Initial offset                  |                                           |          | ±20                   | ±50    | mV                    |

|                  | Input offset drift              |                                           |          | ±200                  |        | μV/°C                 |

| PSR<br>R         | Power-supply rejection ratio    |                                           |          | ±2                    |        | mV/V                  |

|                  | Noise                           |                                           |          | 4                     |        | μV/√ <del>Hz</del>    |

| INPU             | т                               |                                           |          |                       |        |                       |

|                  | Input voltage                   |                                           | ±10      | ±12.5                 |        | V                     |

|                  | Resistance                      |                                           |          | 200                   |        | kΩ                    |

| OUTF             | PUT                             |                                           |          |                       |        |                       |

|                  | Output voltage                  |                                           | ±10      | ±12.5                 |        | V                     |

|                  | Current drive                   |                                           | ±5       | ±15                   |        | mA                    |

|                  | Capacitive load drive           |                                           |          | 0.1                   |        | μF                    |

|                  | Ripple voltage <sup>(3)</sup>   |                                           |          | 20                    |        | mVp-p                 |

| FREG             | QUENCY RESPONSE                 |                                           |          |                       |        |                       |

|                  | Small-signal bandwidth          |                                           |          | 50                    |        | kHz                   |

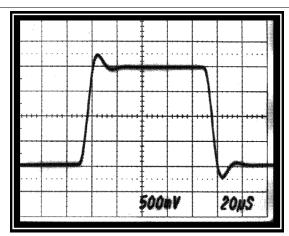

|                  | Slew rate                       |                                           |          | 2                     |        | V/µs                  |

|                  | Settling Time 0.10%             | $V_O = \pm 10 \text{ V}$                  |          | 50                    |        | μs                    |

|                  | Settling Time 0.01%             | V <sub>O</sub> = ±10 V                    |          | 350                   |        | μs                    |

|                  | Overload recovery time          |                                           |          | 150                   |        | μs                    |

| POW              | ER SUPPLIES                     |                                           |          |                       |        |                       |

| I <sub>VS1</sub> | High-side analog supply current |                                           |          | ±5.0                  | ±7.0   | mA                    |

| I <sub>VS2</sub> | Low-side analog supply current  |                                           |          | ±5.5                  | ±7.0   | mA                    |

<sup>(1)</sup> Tested at 1.6x rated, fail on 5-pC partial discharge.

<sup>(2)</sup> Nonlinearity is the peak deviation of the output voltage from the best-fit straight line, and is expressed as the ratio of deviation to FSR.

<sup>(3)</sup> Ripple frequency is at carrier frequency (500 kHz).

## TEXAS INSTRUMENTS

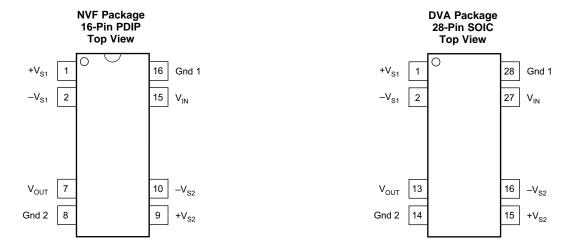

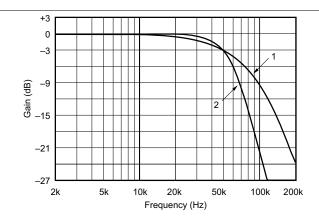

## 6.6 Typical Characteristics

at  $T_A = +25$ °C, and  $V_S = \pm 15$  V (unless otherwise noted)

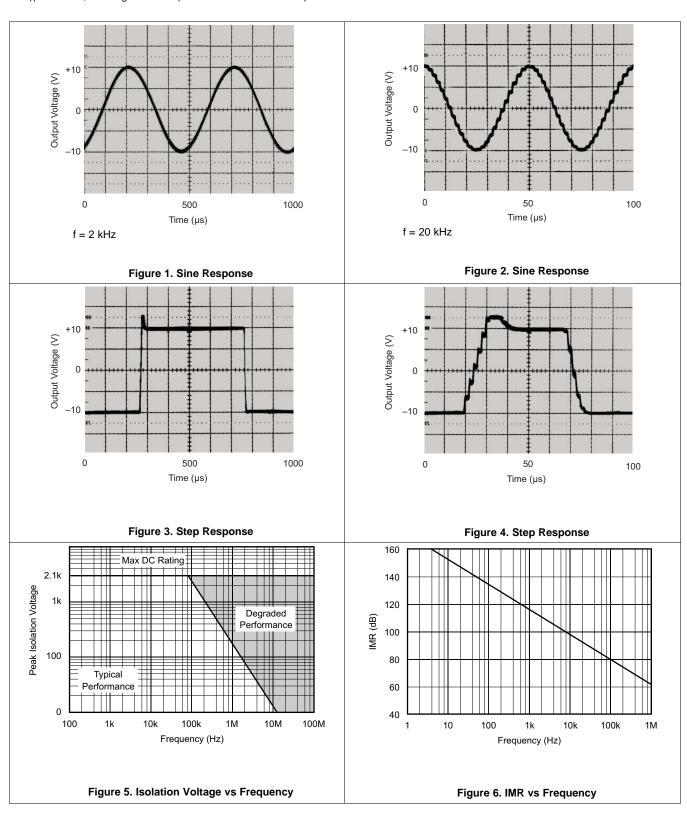

## **Typical Characteristics (continued)**

at  $T_A = +25$ °C, and  $V_S = \pm 15$  V (unless otherwise noted)

Figure 7. PSRR vs Frequency

Figure 8. Isolation Leakage Current vs Frequency

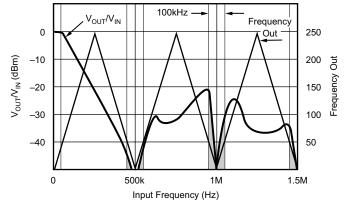

NOTE: Shaded area shows aliasing frequencies that cannot be removed by a low-pass filter at the output.

Figure 9. Signal Response to Inputs Greater than 250 kHz

## 7 Detailed Description

#### 7.1 Overview

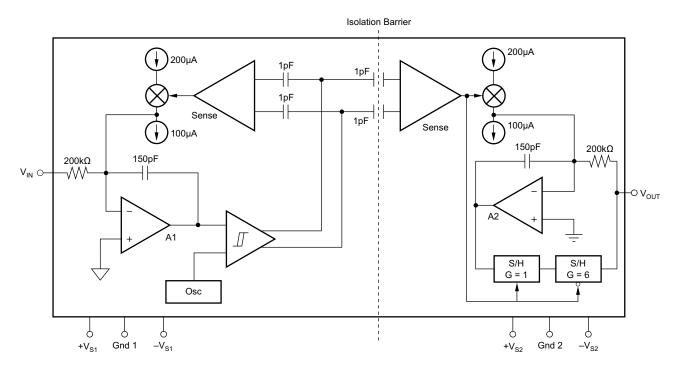

The ISO124 isolation amplifier uses an input and an output section galvanically isolated by matched 1-pF isolating capacitors built into the plastic package. The input is duty-cycle modulated and transmitted digitally across the barrier. The output section receives the modulated signal, converts it back to an analog voltage and removes the ripple component inherent in the demodulation. Input and output sections are fabricated, then laser trimmed for exceptional circuitry matching common to input and output sections. The sections are then mounted on opposite ends of the package with the isolating capacitors mounted between the two sections. The ISO124 contains 250 transistors.

#### 7.1.1 Modulator

An input amplifier (A1, as shown in *Functional Block Diagram*) integrates the difference between the input current  $(V_{IN}/200 \text{ k}\Omega)$  and a switched  $\pm 100$ - $\mu$ A current source. This current source is implemented by a switchable 200- $\mu$ A source and a fixed 100- $\mu$ A current sink. To understand the basic operation of the modulator, assume that  $V_{IN}=0$  V. The integrator will ramp in one direction until the comparator threshold is exceeded. The comparator and sense amp will force the current source to switch; the resultant signal is a triangular waveform with a 50% duty cycle. The internal oscillator forces the current source to switch at 500 kHz. The resultant capacitor drive is a complementary duty-cycle modulation square wave

#### 7.1.2 Demodulator

The sense amplifier detects the signal transitions across the capacitive barrier and drives a switched current source into integrator A2. The output stage balances the duty-cycle modulated current against the feedback current through the 200-k $\Omega$  feedback resistor, resulting in an average value at the  $V_{OUT}$  pin equal to  $V_{IN}$ . The sample-and-hold amplifiers in the output feedback loop serve to remove undesired ripple voltages inherent in the demodulation process.

## 7.2 Functional Block Diagram

## 7.3 Feature Description

## 7.3.1 Isolation Amplifier

The ISO124 is a precision analog isolation amplifier. The input signal is transmitted digitally across a high-voltage differential capacitive barrier. With digital modulation, the barrier characteristics do affect signal integrity, resulting in excellent reliability and high-frequency transient immunity.

## 7.4 Device Functional Modes

The ISO124 device does not have any additional functional modes.

## 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

#### 8.1.1 Carrier Frequency Considerations

The ISO124 amplifier transmits the signal across the isolation barrier by a 500-kHz duty-cycle modulation technique. For input signals having frequencies below 250 kHz, this system works like any linear amplifier. But for frequencies above 250 kHz, the behavior is similar to that of a sampling amplifier. Figure 9 shows this behavior graphically; at input frequencies above 250 kHz, the device generates an output signal component of reduced magnitude at a frequency below 250 kHz. This is the aliasing effect of sampling at frequencies less than two times the signal frequency (the Nyquist frequency). At the carrier frequency and its harmonics, both the frequency and amplitude of the aliasing go to zero.

#### 8.1.2 Isolation Mode Voltage Induced Errors

IMV can induce errors at the output as indicated by the plots of IMV vs Frequency. It should be noted that if the IMV frequency exceeds 250 kHz, the output also will display spurious outputs (aliasing) in a manner similar to that for  $V_{IN} > 250$  kHz and the amplifier response will be identical to that shown in Figure 9. This occurs because IMV-induced errors behave like input-referred error signals. To predict the total error, divide the isolation voltage by the IMR shown in Figure 11 and compute the amplifier response to this input-referred error signal from the data shown in Figure 9. For example, if a 800-kHz 1000-Vrms IMR is present, then a total of [(-60 dB) + (-30 dB)] x (1000 V) = 32-mV error signal at 200 kHz plus a 1-V, 800-kHz error signal will be present at the output.

#### 8.1.3 High IMV dV/dt Errors

As the IMV frequency increases and the dV/dt exceeds 1000 V $\mu$ s, the sense amp may start to false trigger, and the output will display spurious errors. The common-mode current being sent across the barrier by the high slew rate is the cause of the false triggering of the sense amplifier. Lowering the power-supply voltages below  $\pm 15$  V may decrease the dV/dt to 500 V/Ms for typical performance.

#### 8.1.4 High Voltage Testing

TI has adopted a partial discharge test criterion that conforms to the German VDE0884 Optocoupler Standards. This method requires the measurement of minute current pulses (< 5 pC) while applying 2400-Vrms, 60-Hz high-voltage stress across every ISO124 isolation barrier. No partial discharge may be initiated to pass this test. This criterion confirms transient overvoltage (1.6  $\times$  1500 Vrms) protection without damage to the ISO124. Lifetest results verify the absence of failure under continuous rated voltage and maximum temperature.

This new test method represents the "state-of-the art" for nondestructive high-voltage reliability testing. It is based on the effects of nonuniform fields that exist in heterogeneous dielectric material during barrier degradation. In the case of void nonuniformities, electric field stress begins to ionize the void region before bridging the entire high-voltage barrier. The transient conduction of charge during and after the ionization can be detected externally as a burst of 0.01–0.1-µs current pulses that repeat on each ac voltage cycle. The minimum ac barrier voltage that initiates partial discharge is defined as the "inception voltage." Decreasing the barrier voltage to a lower level is required before partial discharge ceases and is defined as the "extinction voltage." The package insulation processes have been characterized and developed to yield an inception voltage in excess of 2400 Vrms so that transient overvoltages below this level will not damage the ISO124. The extinction voltage is above 1500 Vrms so that even overvoltage induced partial discharge will cease once the barrier voltage is reduced to the 1500-Vrms (rated) level. Older high-voltage test methods relied on applying a large enough overvoltage (above rating) to break down marginal parts, but not so high as to damage good ones. Our new partial discharge testing gives us more confidence in barrier reliability than breakdown/no breakdown criteria.

#### 8.2 Typical Applications

#### 8.2.1 Output Filters

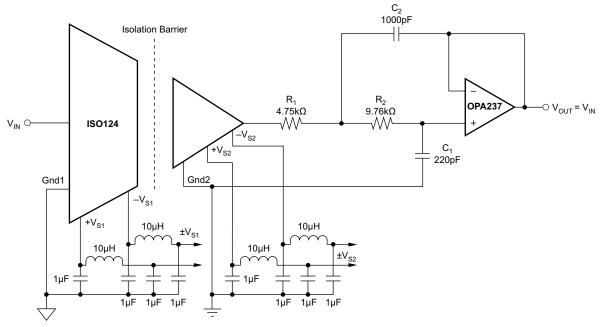

For more information concerning output filters, see Simple Output Filter Elminiates ISO Amp Output Ripple and Keeps Full Bandwidth and FilterPro™ MFB and Sallen-Key Low-Pass Filter Design Program User Guide.

Figure 10. ISO124 With Output Filter for Improved Ripple

#### 8.2.1.1 Design Requirements

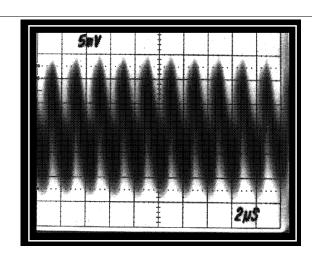

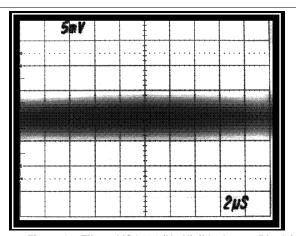

The ISO124 isolation amplifiers (ISO amps) have a small (10 to 20 mVp-p typical) residual demodulator ripple at the output. A simple filter can be added to eliminate the output ripple without decreasing the 50kHz signal bandwidth of the ISO amp.

#### 8.2.1.2 Detailed Design Procedure

The ISO124 device is designed to have a 50-kHz single-pole (Butterworth) signal response. By cascading the ISO amp with a simple 50-kHz, Q = 1, two-pole, low-pass filter, the overall signal response becomes three-pole Butterworth. The result is a maximally flat 50-kHz magnitude response and the output ripple reduced below the noise level. Figure 10 shows the complete circuit. The two-pole filter is a unity-gain Sallen-Key type consisting of A1, R1, R2, C1, and C2. The values shown give Q = 1 and f-3dB bandwidth = 50 kHz. Because the op amp is connected as a unity-gain follower, gain and gain accuracy of the ISO amp are unaffected. Using a precision op amp such as the OPA602 also preserves the DC accuracy of the ISO amp.

# TEXAS INSTRUMENTS

## **Typical Applications (continued)**

## 8.2.1.3 Application Curves

- 1) Standard ISO124 has 50kHz single-pole (Butterworth) response.

- 2) ISO124 with cascaded 50kHz, Q = 1, two-pole, low-pass filter has three-pole Butterworth response.

Figure 11. Gain vs. Frequency

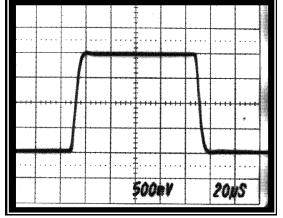

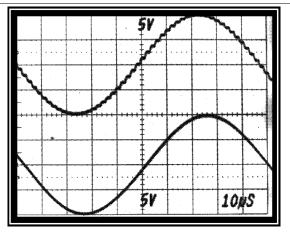

Figure 12. Standard ISO124 (Approximately 20-mVp-p Output Ripple)

Figure 13. Filtered ISO124 (No Visible Output Ripple)

Figure 14. Step Response of Standard ISO124

Figure 15. Step Response of ISO124 With Added Twopole Output Filter

Figure 16. Large-signal, 10-kHz Sine-wave Response of ISO124 With and Without Output Filter

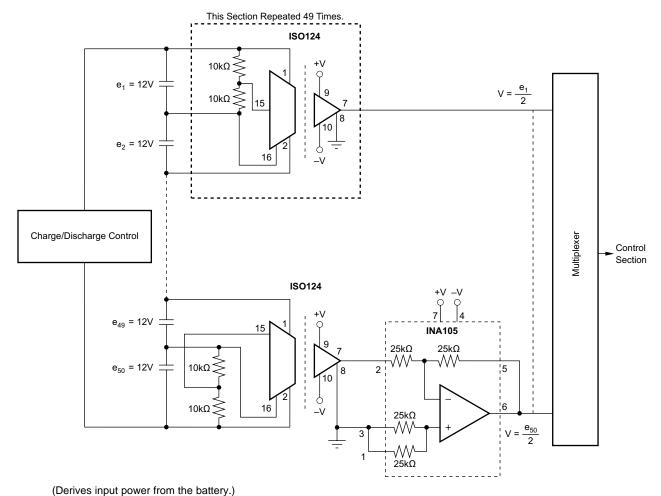

## 8.2.2 Battery Monitor

Figure 17 provides a means to monitor the cell voltage on a 600-V battery stack by using the battery as a power source for the isolated voltage.

Figure 17. Battery Monitor for a 600-V Battery Power System

## 8.2.3 Programmable Gain Amplifier

In applications where variable gain configurations are required, a programmable gain amplifier like the PGA102 can be used with the ISO124 device. Figure 18 uses an ISO150 device to provide gain pin selection options to the PGA102 device.

Figure 18. Programmable-Gain Isolation Channel With Gains of 1, 10, and 100

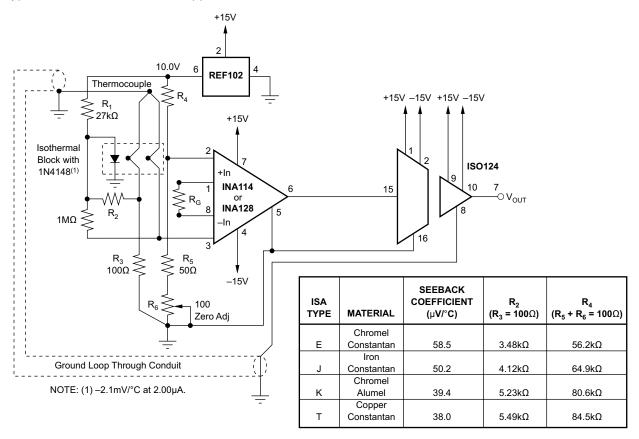

#### 8.2.4 Thermocouple Amplifier

For isolated temperature measurements, Figure 19 provides an application solution using the INA114 or INA128 devices, feeding the input stage of the ISO124 device. The table provides suggested resistor values based on the type of thermistor used in the application.

Figure 19. Thermocouple Amplifier With Ground Loop Elimination, Cold Junction Compensation, and Up-scale Burn-out

#### 8.2.5 Isolated 4-mA to 20-mA Instrument Loop

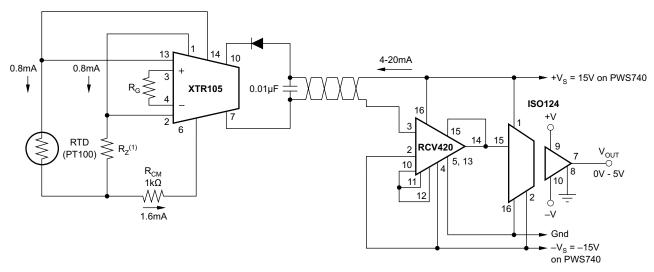

For isolated temperature measurements in a 4-mA to 20-mA loop, Figure 20 provides a solution using the XTR101 and RCV420 devices. A high-performance PT100 resistance temperature detector (RTD) provides the user with an isolated 0-V to 5-V representation of the isolated temperature measurement.

Figure 20. Isolated 4- to 20-mA Instrument Loop (RTD Shown)

## 8.2.6 Single-Supply Operation of the ISO124 Isolation Amplifier

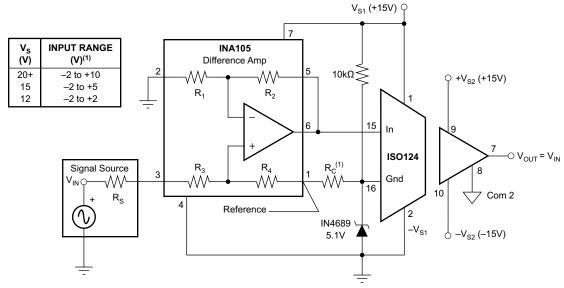

The circuit shown in Figure 21 uses a 5.1-V Zener diode to generate the negative supply for an ISO12x from a single supply on the high-voltage side of the isolation amplifier. The input measuring range will be dependent on the applied voltage as noted in the accompanying table.

NOTE: Because the amplifier is unity gain, the input range is also the output range. The output can go to -2 V because the output section of the ISO amp operates from dual supplies.

For additional information see Single-Supply Operation of Isolation Amplifiers.

Figure 21. Single-Supply Operation of the ISO124 Isolation Amplifier Schematic

## 8.2.7 Input-Side Powered ISO Amplifier

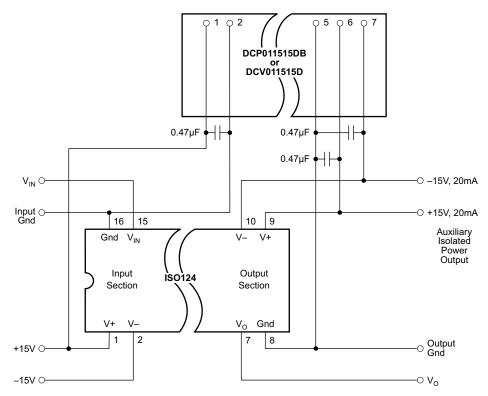

The user side of the ISO124 device can be powered from the high voltage side using an isolated DC-DC converter as shown in Figure 22.

Figure 22. Input-Side Powered ISO Amplifier Schematic

## 8.2.8 Powered ISO Amplifier With Three-Port Isolation

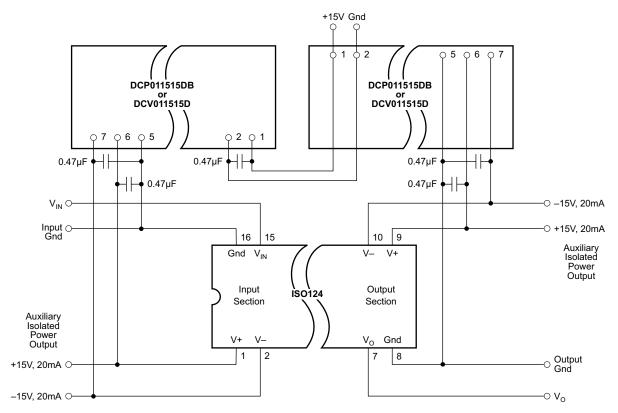

Figure 23 illustrates an application solution that provides isolated power to both the user and high-voltage sides of the ISO124 amplifier.

Figure 23. Powered ISO Amplifier With Three-Port Isolation Schematic

## 9 Power Supply Recommendations

#### 9.1 Signal and Supply Connections

Each power-supply pin should be bypassed with 1- $\mu$ F tantalum capacitors located as close to the amplifier as possible. The internal frequency of the modulator/demodulator is set at 500 kHz by an internal oscillator. Therefore, if it is desired to minimize any feedthrough noise (beat frequencies) from a DC-DC converter, use a  $\pi$  filter on the supplies (see Figure 10). The ISO124 output has a 500-kHz ripple of 20 mV, which can be removed with a simple 2-pole low-pass filter with a 100-kHz cutoff using a low-cost op amp (see Figure 10).

The input to the modulator is a current (set by the 200-k $\Omega$  integrator input resistor) that makes it possible to have an input voltage greater than the input supplies, as long as the output supply is at least ±15 V. It is therefore possible, when using an unregulated DC-DC converter, to minimize PSR related output errors with ±5-V voltage regulators on the isolated side and still get the full ±10-V input and output swing.

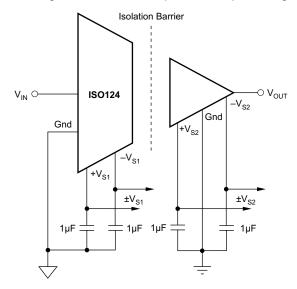

Figure 24. Basic Signal and Power Connections

## 10 Layout

## 10.1 Layout Guidelines

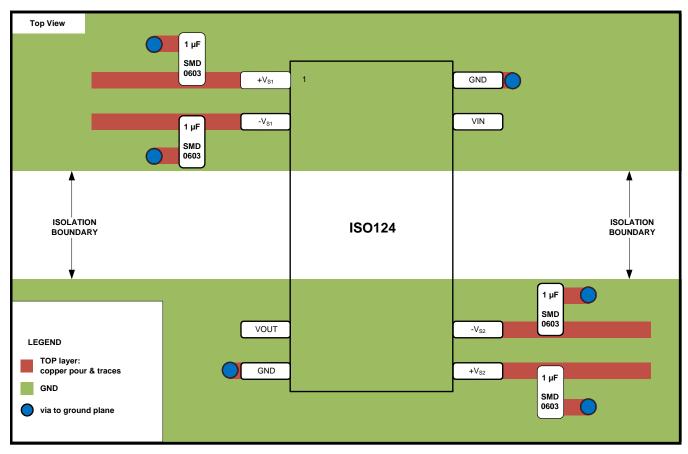

To maintain the isolation barrier of the device, the distance between the high-side ground (pin 16 or 28) and the low-side ground (pin 8 or 14) should be kept at maximum; that is, the entire area underneath the device should be kept free of any conducting materials.

## 10.2 Layout Example

Figure 25. ISO124 Layout Example

#### 11 器件和文档支持

#### 11.1 文档支持

#### 11.1.1 相关文档

请参阅如下相关文档:

- 隔离放大器的单电源操作。

- 简单输出滤波器消除 ISO 放大器输出波纹并保持满带宽。

- FilterPro™ 用户指南。

#### 11.2 接收文档更新通知

要接收文档更新通知,请导航至 ti.com.cn 上的器件产品文件夹。单击右上角的通知我 进行注册,即可每周接收产品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

#### 11.3 社区资源

下列链接提供到 TI 社区资源的连接。链接的内容由各个分销商"按照原样"提供。这些内容并不构成 TI 技术规范,并且不一定反映 TI 的观点;请参阅 TI 的 《使用条款》。

TI E2E™ 在线社区 TI 的工程师对工程师 (E2E) 社区。此社区的创建目的在于促进工程师之间的协作。在 e2e.ti.com 中,您可以咨询问题、分享知识、拓展思路并与同行工程师一道帮助解决问题。

设计支持 71 参考设计支持 可帮助您快速查找有帮助的 E2E 论坛、设计支持工具以及技术支持的联系信息。

#### 11.4 商标

FilterPro. E2E are trademarks of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 11.5 静电放电警告

ESD 可能会损坏该集成电路。德州仪器 (TI) 建议通过适当的预防措施处理所有集成电路。如果不遵守正确的处理措施和安装程序,可能会损坏集成电路。

**▲『☆▲ ESD** 的损坏小至导致微小的性能降级,大至整个器件故障。 精密的集成电路可能更容易受到损坏,这是因为非常细微的参数更改都可能会导致器件与其发布的规格不相符。

#### 11.6 术语表

SLYZ022 — TI 术语表。

这份术语表列出并解释术语、缩写和定义。

## 12 机械、封装和可订购信息

以下页面包含机械、封装和可订购信息。这些信息是指定器件的最新可用数据。数据如有变更,恕不另行通知,且不会对此文档进行修订。如需获取此产品说明书的浏览器版本,请查看左侧的导航栏。

www.ti.com

10-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|----------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                |                       |                 | (4)                           | (5)                        |              |                  |

| ISO124P               | Active | Production    | PDIP (NVF)   8 | 25   TUBE             | Yes             | NIPDAU                        | N/A for Pkg Type           | -25 to 85    | ISO124P          |

| ISO124P.A             | Active | Production    | PDIP (NVF)   8 | 25   TUBE             | Yes             | NIPDAU                        | N/A for Pkg Type           | -25 to 85    | ISO124P          |

| ISO124P.B             | Active | Production    | PDIP (NVF)   8 | 25   TUBE             | -               | Call TI                       | Call TI                    | -25 to 85    |                  |

| ISO124U               | Active | Production    | SOIC (DVA)   8 | 20   TUBE             | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -25 to 85    | ISO<br>124U      |

| ISO124U.A             | Active | Production    | SOIC (DVA)   8 | 20   TUBE             | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -25 to 85    | ISO<br>124U      |

| ISO124U.B             | Active | Production    | SOIC (DVA)   8 | 20   TUBE             | -               | Call TI                       | Call TI                    | -25 to 85    |                  |

| ISO124U/1K            | Active | Production    | SOIC (DVA)   8 | 1000   LARGE T&R      | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -25 to 85    | ISO<br>124U      |

| ISO124U/1K.A          | Active | Production    | SOIC (DVA)   8 | 1000   LARGE T&R      | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -25 to 85    | ISO<br>124U      |

| ISO124U/1K.B          | Active | Production    | SOIC (DVA)   8 | 1000   LARGE T&R      | -               | Call TI                       | Call TI                    | -25 to 85    |                  |

| ISO124U/1KE4          | Active | Production    | SOIC (DVA)   8 | 1000   LARGE T&R      | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -25 to 85    | ISO<br>124U      |

| ISO124UE4             | Active | Production    | SOIC (DVA)   8 | 20   TUBE             | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -25 to 85    | ISO<br>124U      |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

## **PACKAGE OPTION ADDENDUM**

www.ti.com 10-Nov-2025

(6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 22-Sep-2025

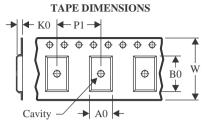

## TAPE AND REEL INFORMATION

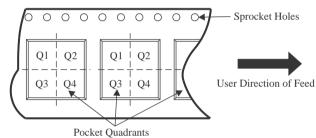

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device     | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| ISO124U/1K | SOIC            | DVA                | 8 | 1000 | 330.0                    | 24.4                     | 10.9       | 18.3       | 3.2        | 12.0       | 24.0      | Q1               |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 22-Sep-2025

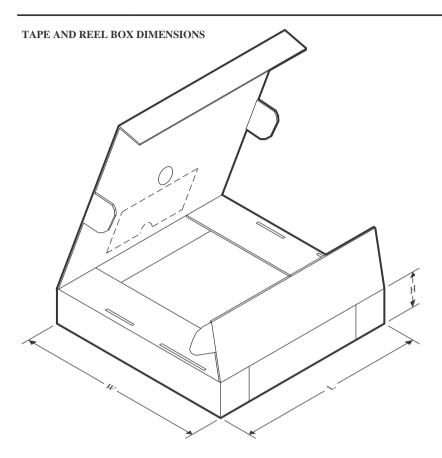

#### \*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| ISO124U/1K | SOIC         | DVA             | 8    | 1000 | 356.0       | 356.0      | 45.0        |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 22-Sep-2025

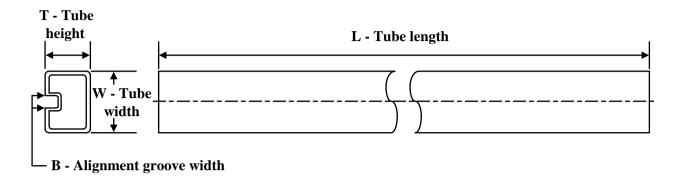

## **TUBE**

\*All dimensions are nominal

| Device    | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |  |  |

|-----------|--------------|--------------|------|-----|--------|--------|--------|--------|--|--|

| ISO124P   | NVF          | PDIP         | 8    | 25  | 506    | 13.97  | 11230  | 4.32   |  |  |

| ISO124P.A | NVF          | PDIP         | 8    | 25  | 506    | 13.97  | 11230  | 4.32   |  |  |

| ISO124U   | DVA          | SOIC         | 8    | 20  | 507    | 12.83  | 5080   | 6.6    |  |  |

| ISO124U.A | DVA          | SOIC         | 8    | 20  | 507    | 12.83  | 5080   | 6.6    |  |  |

| ISO124UE4 | DVA          | SOIC         | 8    | 20  | 507    | 12.83  | 5080   | 6.6    |  |  |

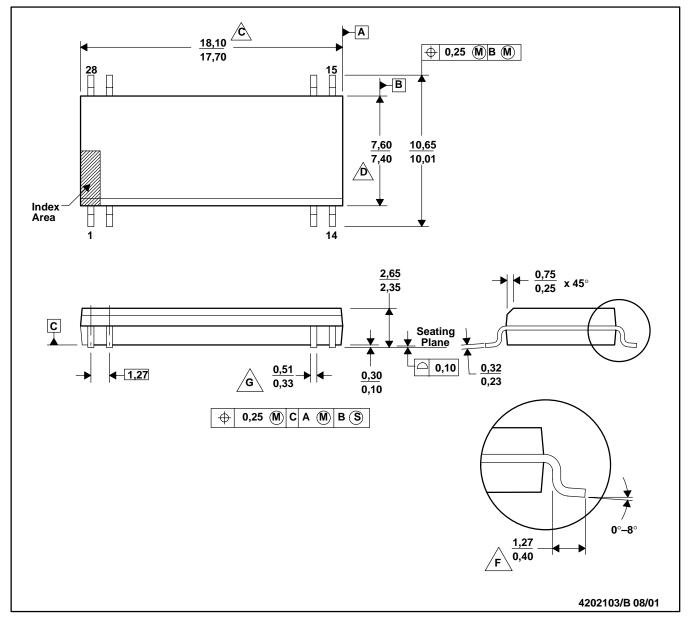

#### **DVA (R-PDSO-G8/28)**

#### PLASTIC SMALL-OUTLINE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

Body length dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, and gate burrs shall not exceed 0,15 mm per side.

Body width dimension does not include inter-lead flash or portrusions. Inter-lead flash and protrusions shall not exceed 0,25 mm per side.

E. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the cross-hatched area.

Lead dimension is the length of terminal for soldering to a substrate.

Lead width, as measured 0,36 mm or greater above the seating plane, shall not exceed a maximum value of 0,61 mm.

- H. Lead-to-lead coplanarity shall be less than 0,10 mm from seating plane.

- Falls within JEDEC MS-013-AE with the exception of the number of leads.

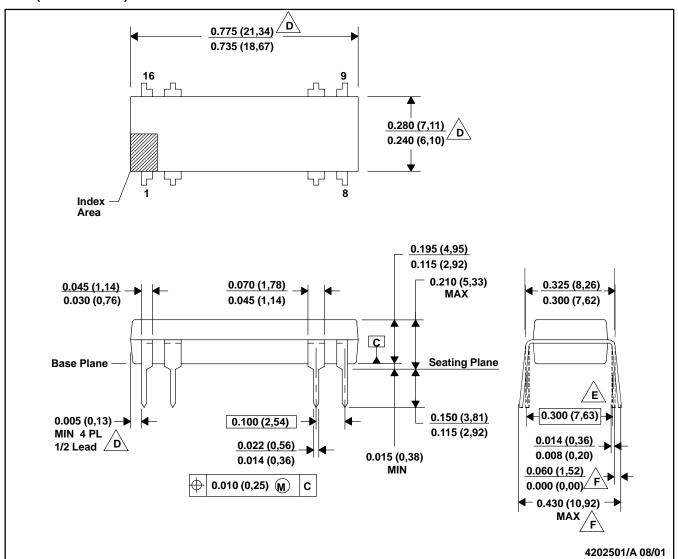

#### NVF (R-PDIP-T8/16)

#### PLASTIC DUAL-IN-LINE

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-001-BB with the exception of lead count.

- Dimensions do not include mold flash or protrusions.

- Mold flash or protrusions shall not exceed 0.010 (0,25).

- \( \) Dimensions measured with the leads constrained to be perpendicular to Datum C.

- Dimensions are measured at the lead tips with the leads unconstrained.

- G. A visual index feature must be located within the cross-hatched area.

## 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月