🕳 Order

Now

DS250DF810

ZHCSKE9C-DECEMBER 2015-REVISED OCTOBER 2019

# DS250DF810 25Gbps 多速率 8 通道重定时器

#### 特性 1

- 具有集成信号调节功能的八通道多速率重定时器

- 所有通道均可独立锁定在 20.2752 至 25.8Gbps 的 范围内(包括 10.3125Gbps、12.5Gbps 等子速 率)

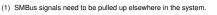

- 超低延迟: 25.78125Gbps 数据速率下的典型延迟 < 500ps

- 单电源,无需低抖动参考时钟,集成交流耦合电容 器以降低电路板布线复杂程度并节省物料清单 (BOM) 成本

- 集成 2×2 交叉点

- 自适应性连续时间线性均衡器 (CTLE)

- 自适应判决反馈均衡器 (DFE)

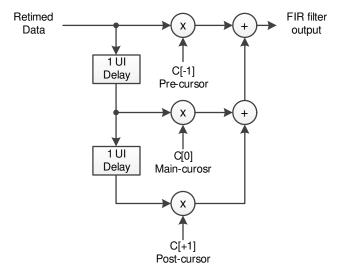

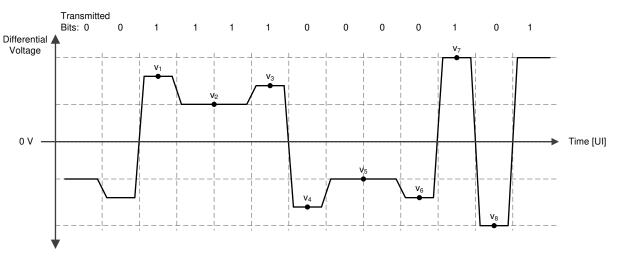

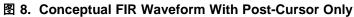

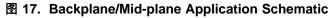

- 带有 3 抽头有限脉冲响应 (FIR) 滤波器的低抖动发 . 射器

- 组合式均衡,在 12.9GHz 频率下支持 35dB 以上的 诵道损耗

- 可调节发送幅值: 205mVppd 至 1225mVppd (典 ٠ 型值)

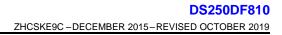

- 片上眼图张开度监视器 (EOM), PRBS 模式校验器 /发生器小型 8mm × 13mm BGA 封装,可轻松实现 直通布线

- 独特引脚可实现在封装下方布置高速信号布线

- 支持兼容引脚的中继器

- 2 应用

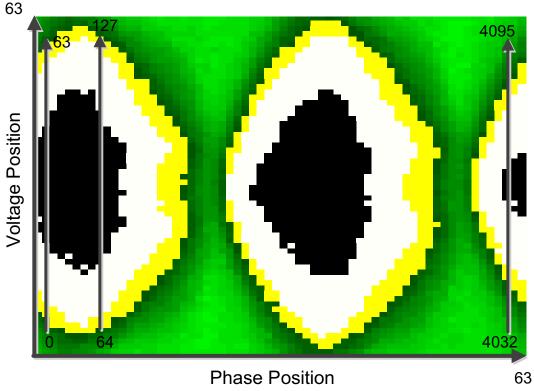

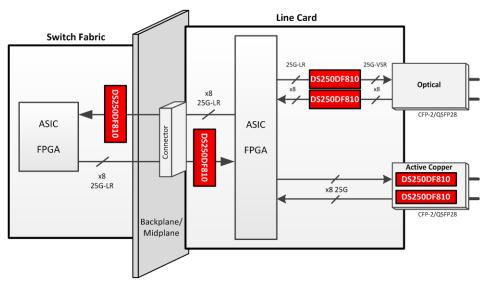

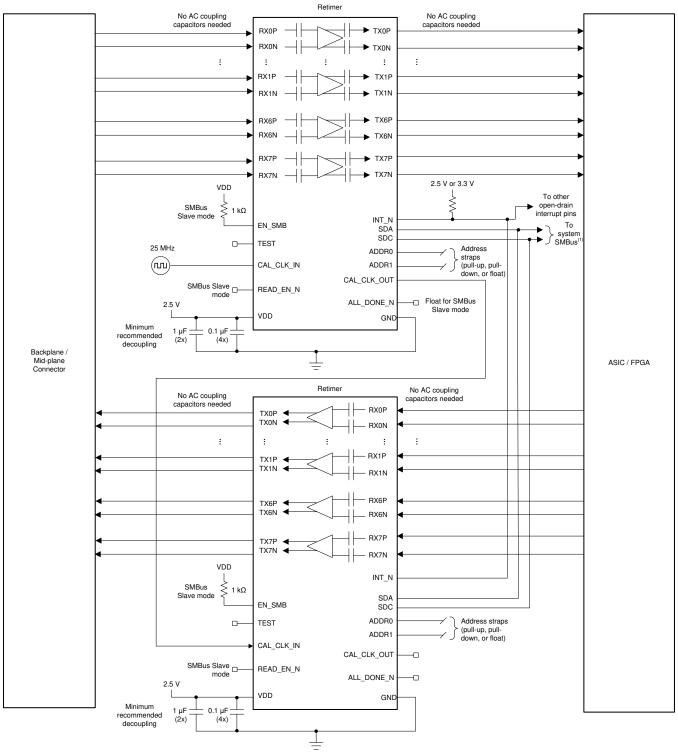

- 背板/中板长度延长

🥭 Tools &

- 针对前端口光学模块的抖动消除 •

- IEEE802.3bj 100GbE、Infiniband EDR 和 OIF-CEI-25G-LR/MR/SR/VSR 电气接口

- SFP28、QSFP28、CFP2/CFP4、CDFP ٠

## 3 说明

DS250DF810 是一款具有集成信号调节功能的八通道 多速率重定时器。该器件用于扩展有损且存在串扰的远 距离高速串行链路的延伸长度并提升稳定性,同时实现 不高于 10<sup>-15</sup> 的比特误码率 (BER)。

DS250DF810 各通道的串行数据速率均可独立锁定在 20.6Gbps 至 25.8Gbps 的连续范围内或者支持的任意 子速率(速率的一半和四分之一),包括

10.3125Gbps 和 12.5Gbps 等关键数据速率,从而允 许 DS280BR810 进行独立通道前向纠错 (FEC)。

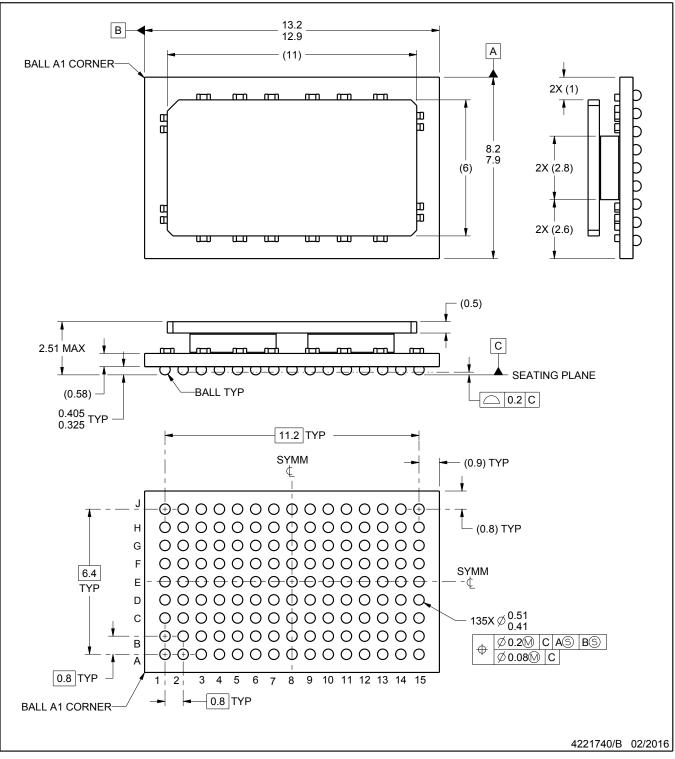

器件信息(1)

| 器件型号       | 封装                    | 封装尺寸(标称值)      |

|------------|-----------------------|----------------|

| DS250DF810 | 135 引脚 FCBGA<br>(135) | 8.0mm x 13.0mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

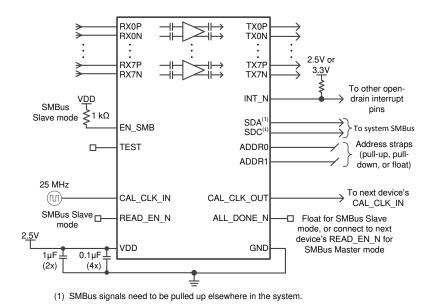

#### 简化原理图 4

Æ

# 目录

9

| 1 | 特性   |                                                                      |

|---|------|----------------------------------------------------------------------|

| 2 | 应用   |                                                                      |

| 3 | 说明   |                                                                      |

| 4 | 简化   | 原理图1                                                                 |

| 5 | 修订   | 历史记录                                                                 |

| 6 | 说明   | (续)3                                                                 |

| 7 | Pin  | Configuration and Functions 4                                        |

| 8 | Spe  | cifications7                                                         |

|   | 8.1  | Absolute Maximum Ratings 7                                           |

|   | 8.2  | ESD Ratings7                                                         |

|   | 8.3  | Recommended Operating Conditions7                                    |

|   | 8.4  | Thermal Information 8                                                |

|   | 8.5  | Electrical Characteristics8                                          |

|   | 8.6  | Timing Requirements, Retimer Jitter<br>Specifications                |

|   | 8.7  | Timing Requirements, Retimer Specifications 13                       |

|   | 8.8  | Timing Requirements, Recommended Calibration<br>Clock Specifications |

|   | 8.9  | Recommended SMBus Switching Characteristics<br>(Slave Mode)          |

|   | 8.10 | Recommended SMBus Switching Characteristics<br>(Master Mode)         |

|   | 8.11 |                                                                      |

|    | 9.2  | Functional Block Diagram   | . 17 |

|----|------|----------------------------|------|

|    | 9.3  | Feature Description        | . 18 |

|    | 9.4  | Device Functional Modes    | . 29 |

|    | 9.5  | Programming                | . 30 |

|    | 9.6  | Register Maps              | . 32 |

| 10 | App  | ication and Implementation | 77   |

|    | 10.1 | Application Information    | . 77 |

|    | 10.2 | Typical Application        | . 77 |

| 11 | Pow  | er Supply Recommendations  | 82   |

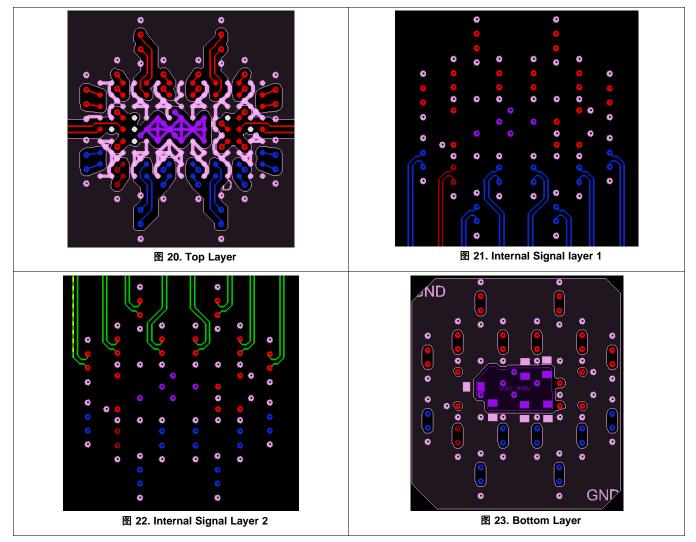

| 12 | Layo | out                        | 82   |

|    | 12.1 | Layout Guidelines          | . 82 |

|    | 12.2 | Layout Example             | . 82 |

| 13 | 器件   | 和文档支持                      | 84   |

|    | 13.1 | 器件支持                       | . 84 |

|    | 13.2 | 文档支持                       | . 84 |

|    | 13.3 | 接收文档更新通知                   | . 84 |

|    | 13.4 | 支持资源                       | . 84 |

|    | 13.5 | 商标                         | . 84 |

|    | 13.6 | 静电放电警告                     |      |

|    | 13.7 | Glossary                   | . 84 |

| 14 | 机械   | 、封装和可订购信息                  | 84   |

|    |      |                            |      |

Detailed Description ...... 16

# 5 修订历史记录

Changes from Revision B (June 2019) to Revision C

• 首次公开发布 ...... 1

ISTRUMENTS

EXAS

#### Page

#### www.ti.com.cn

6 说明 (续)

印刷电路板 (PCB) 上集成了物理交流耦合电容(TX 与 RX),无需使用外部电容。DS250DF810 具备一个单电源,能够最大限度地减少外部组件的数量。这些 特性 可降低 PCB 布线的复杂程度并节省 BOM 成本。

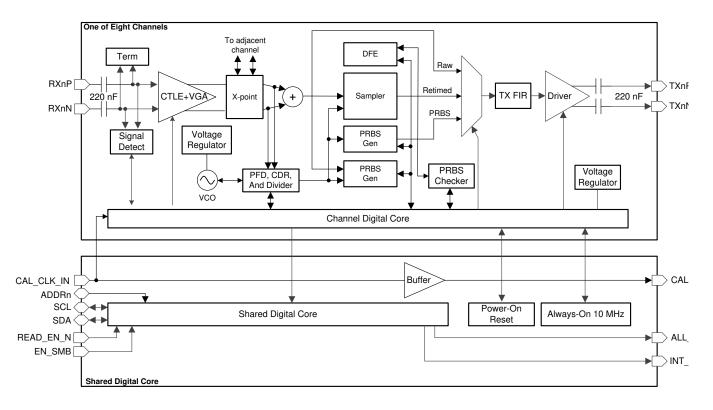

DS250DF230 的高级均衡 特性 包括: 一个低抖动 3 抽头发送有限冲激响应 (FIR) 滤波器、一个自适应连续时间线 性均衡器 (CTLE) 以及一个自适应判决反馈均衡器 (DFE)。支持针对具有多个连接器且存在串扰的有损互连和背板 进行扩展。集成的时钟和数据恢复 (CDR) 功能可重置抖动预算并对高速串行数据进行重定时, 非常适用于前端口 光学模块 应用。DS250DF810 对每个通道对采用 2x2 交叉点,可为主机同时提供通道交叉和扇出选项。

DS250DF810 可通过 SMBus 或外部 EEPROM 进行配置。单个 EEPROM 最多可由 16 个器件共享。非破坏性片 上眼图监视器和 PRBS 发生器/校验器为系统内诊断提供支持。

# 7 Pin Configuration and Functions

|   |                     |       |               |       |      |     |      |     | -    |     |      |       |                |       |                |   |

|---|---------------------|-------|---------------|-------|------|-----|------|-----|------|-----|------|-------|----------------|-------|----------------|---|

|   | 15                  | 14    | 13            | 12    | 11   | 10  | 9    | 8   | 7    | 6   | 5    | 4     | 3              | 2     | 1              |   |

| J | GND                 | GND   | TX1N          | GND   | TX2N | GND | TX3N | GND | TX4N | GND | TX5N | GND   | TX6N           | GND   | GND            | J |

| Н | TXON                | GND   | TX1 P         | GND   | TX2P | GND | ТХЗР | GND | TX4P | GND | TX5P | GND   | TX6P           | GND   | TX7N           | н |

| G | TX0P                | GND   | GND           | GND   | GND  | GND | GND  | GND | GND  | GND | GND  | GND   | GND            | GND   | TX7P           | G |

| F | GND                 | GND   | READ_<br>EN_N | SDC   | GND  | VDD | GND  | VDD | GND  | VDD | GND  | TEST4 | INT_N          | GND   | GND            | F |

| Е | CAL_C<br>LK_OU<br>T | TEST1 | ADDR1         | SDA   | GND  | VDD | VDD  | VDD | VDD  | VDD | VDD  | TEST5 | EN_SM<br>B     | TEST0 | CAL_C<br>LK_IN | E |

| D | GND                 | GND   | ADDR0         | TEST7 | GND  | VDD | GND  | VDD | GND  | VDD | GND  | TEST6 | ALL_D<br>ONE_N | GND   | GND            | D |

| С | RX0P                | GND   | GND           | GND   | GND  | GND | GND  | GND | GND  | GND | GND  | GND   | GND            | GND   | RX7P           | С |

| В | RX0N                | GND   | RX1P          | GND   | RX2P | GND | RX3P | GND | RX4P | GND | RX5P | GND   | RX6P           | GND   | RX7N           | в |

| A | GND                 | GND   | RX1N          | GND   | RX2N | GND | RX3N | GND | RX4N | GND | RX5N | GND   | RX6N           | GND   | GND            | A |

|   | 15                  | 14    | 13            | 12    | 11   | 10  | 9    | 8   | 7    | 6   | 5    | 4     | 3              | 2     | 1              |   |

# LegendControl/<br/>statusHigh-SpeedGroundPowerTi Test pins<br/>/ Reserved

#### **Pin Functions**

| PIN          |                   |        | INTERNAL              |                                                                                                                                     |

|--------------|-------------------|--------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| NAME         | NO.               | TYPE   | PULL-UP/<br>PULL-DOWN | DESCRIPTION                                                                                                                         |

| HIGH SPEED I | DIFFERENTIAL I/Os | 6      |                       |                                                                                                                                     |

| RX0P         | C15               | Input  | None                  | Inverting and non-inverting differential inputs to the equalizer. An                                                                |

| RX0N         | B15               | Input  | None                  | on-chip 100- $\Omega$ termination resistor connects RXP to RXN. These inputs are AC coupled on-chip with physical 220nF capacitors. |

| RX1P         | B13               | Input  | None                  | Inverting and non-inverting differential inputs to the equalizer. An                                                                |

| RX1N         | A13               | Input  | None                  | on-chip 100- $\Omega$ termination resistor connects RXP to RXN. These inputs are AC coupled on-chip with physical 220nF capacitors. |

| RX2P         | B11               | Input  | None                  | Inverting and non-inverting differential inputs to the equalizer. An                                                                |

| RX2N         | A11               | Input  | None                  | on-chip 100- $\Omega$ termination resistor connects RXP to RXN. These inputs are AC coupled on-chip with physical 220nF capacitors. |

| RX3P         | B9                | Input  | None                  | Inverting and non-inverting differential inputs to the equalizer. An                                                                |

| RX3N         | A9                | Input  | None                  | on-chip 100- $\Omega$ termination resistor connects RXP to RXN. These inputs are AC coupled on-chip with physical 220nF capacitors. |

| RX4P         | B7                | Input  | None                  | Inverting and non-inverting differential inputs to the equalizer. An                                                                |

| RX4N         | A7                | Input  | None                  | on-chip 100- $\Omega$ termination resistor connects RXP to RXN. These inputs are AC coupled on-chip with physical 220nF capacitors. |

| RX5P         | B5                | Input  | None                  | Inverting and non-inverting differential inputs to the equalizer. An                                                                |

| RX5N         | A5                | Input  | None                  | on-chip 100- $\Omega$ termination resistor connects RXP to RXN. These inputs are AC coupled on-chip with physical 220nF capacitors. |

| RX6P         | B3                | Input  | None                  | Inverting and non-inverting differential inputs to the equalizer. An                                                                |

| RX6N         | A3                | Input  | None                  | on-chip 100- $\Omega$ termination resistor connects RXP to RXN. These inputs are AC coupled on-chip with physical 220nF capacitors. |

| RX7P         | C1                | Input  | None                  | Inverting and non-inverting differential inputs to the equalizer. An                                                                |

| RX7N         | B1                | Input  | None                  | on-chip 100- $\Omega$ termination resistor connects RXP to RXN. These inputs are AC coupled on-chip with physical 220nF capacitors. |

| TX0P         | G15               | Output | None                  | Inverting and non-inverting $50\Omega$ driver outputs. These outputs are                                                            |

| TX0N         | H15               | Output | None                  | AC coupled on-chip with physical 220nF capacitors.                                                                                  |

www.ti.com.cn

## Pin Functions (continued)

| PIN         |              |                                    | INTERNAL              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|-------------|--------------|------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME        | NO.          | TYPE                               | PULL-UP/<br>PULL-DOWN | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| TX1P        | H13          | Output                             | None                  | Inverting and non-inverting $50\Omega$ driver outputs. These outputs are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| TX1N        | J13          | Output                             | None                  | AC coupled on-chip with physical 220nF capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| TX2P        | H11          | Output                             | None                  | Inverting and non-inverting $50\Omega$ driver outputs. These outputs are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| TX2N        | J11          | Output                             | None                  | AC coupled on-chip with physical 220nF capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| TX3P        | H9           | Output                             | None                  | Inverting and non-inverting $50\Omega$ driver outputs. These outputs are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| TX3N        | J9           | Output                             | None                  | AC coupled on-chip with physical 220nF capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| TX4P        | H7           | Output                             | None                  | Inverting and non-inverting $50\Omega$ driver outputs. These outputs are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| TX4N        | J7           | Output                             | None                  | AC coupled on-chip with physical 220nF capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| TX5P        | H5           | Output                             | None                  | Inverting and non-inverting $50\Omega$ driver outputs. These outputs are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| TX5N        | J5           | Output                             | None                  | AC coupled on-chip with physical 220nF capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| TX6P        | H3           | Output                             | None                  | Inverting and non-inverting $50\Omega$ driver outputs. These outputs are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| TX6N        | J3           | Output                             | None                  | AC coupled on-chip with physical 220nF capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| TX7P        | G1           | Output                             | None                  | Inverting and non-inverting $50\Omega$ driver outputs. These outputs are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| TX7N        | H1           | Output                             | None                  | AC coupled on-chip with physical 220nF capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| CALIBRATION | CLOCK PINS   |                                    |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| CAL_CLK_IN  | E1           | Input, 2.5V<br>CMOS                | None                  | 25 MHz (±100 PPM) 2.5 V single-ended clock from external oscillator. No stringent phase noise or jitter requirements on this clock. Used to calibrate VCO frequency range. This clock is not used to recover data.                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| CAL_CLK_OUT |              | Output, 2.5V<br>CMOS               | None                  | 2.5 V buffered replica of calibration clock input (pin E1) for connecting multiple devices in a daisy-chained fashion.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| SYSTEM MANA | GEMENT BUS ( | SMBUS) PINS                        |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| ADDR0       | D13          | Input, 4-level                     | None                  | 4-level strap pins used to set the SMBus address of the device.<br>The pin state is read on power-up. The multi-level nature of these                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| ADDR1       | E13          | Input, 4-level                     | None                  | The pin state is read on power-up. The multi-level nature of these pins allows for 16 unique device addresses. The four strap options include:<br>0: 1 k $\Omega$ to GND<br>R: 10 k $\Omega$ to GND<br>F: Float<br>1: 1 k $\Omega$ to VDD                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| EN_SMB      | E3           | Input, 4-level                     | None                  | Four-level 2.5 V input used to select between SMBus master mode<br>(float) and SMBus slave mode (high). The four defined levels are:<br>0: 1 k $\Omega$ to GND - RESERVED<br>R: 10 k $\Omega$ to GND - RESERVED, TI test mode<br>F: Float - SMBus Master Mode<br>1: 1 k $\Omega$ to VDD - SMBus Slave Mode                                                                                                                                                                                                                                                   |  |  |  |  |

| SDA         | E12          | I/O, 3.3V<br>LVCMOS, Open<br>Drain | None                  | SMBus data input / open drain output. External 2 k $\Omega$ to 5 k $\Omega$ pull-<br>up resistor is required as per SMBus interface standard. This pin is<br>3.3 V LVCMOS tolerant.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| SDC         | F12          | I/O, 3.3V<br>LVCMOS, Open<br>Drain | None                  | SMBus clock input / open drain clock output. External 2 k $\Omega$ to 5 k $\Omega$ pull-up resistor is required as per SMBus interface standard. This pin is 3.3 V LVCMOS tolerant.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| SMBUS MASTE | R MODE PINS  |                                    |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| READ_EN_N   | F13          | Input, 3.3V<br>LVCMOS              | weak pull-up          | SMBus Master Mode (EN_SMB=Float): When asserted low,<br>initiates the SMBus master mode EEPROM read function. Once<br>EEPROM read is complete (indicated by assertion of<br>ALL_DONE_N low), this pin can be held low for normal device<br>operation. This pin is 3.3 V tolerant.<br>SMBus Slave Mode (EN_SMB=1): When asserted low, this causes<br>the device to be held in reset (I2C state machine reset and register<br>reset). This pin should be pulled high or left floating for normal<br>operation in SMBus Slave Mode. This pin is 3.3 V tolerant. |  |  |  |  |

DS250DF810 ZHCSKE9C – DECEMBER 2015–REVISED OCTOBER 2019

www.ti.com.cn

## Pin Functions (continued)

| P           | PIN                                                                                                                                                                                                                                                                                                                                                                                                         |                                  | INTERNAL              |                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO.                                                                                                                                                                                                                                                                                                                                                                                                         | TYPE                             | PULL-UP/<br>PULL-DOWN | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                               |

| ALL_DONE_N  | D3                                                                                                                                                                                                                                                                                                                                                                                                          | Output,<br>LVCMOS                | None                  | Indicates the completion of a valid EEPROM register load operation<br>when in SMBus Master Mode (EN_SMB=Float):<br>High = External EEPROM load failed or incomplete<br>Low = External EEPROM load successful and complete<br>When in SMBus slave mode (EN_SMB=1), this output will be high-<br>z until READ_EN_N is driven low, at which point ALL_DONE_N will<br>be driven low.                                          |

| MISCELLANEO | US PINS                                                                                                                                                                                                                                                                                                                                                                                                     |                                  |                       |                                                                                                                                                                                                                                                                                                                                                                                                                           |

| INT_N       | F3                                                                                                                                                                                                                                                                                                                                                                                                          | Output,<br>LVCMOS,<br>Open-Drain | None                  | Open-drain 3.3 V tolerant active-low interrupt output. It pulls low when an interrupt occurs. The events which trigger an interrupt are programmable through SMBus registers. This pin can be connected in a wired-OR fashion with other device's interrupt pin. A single pull-up resistor in the 2 k $\Omega$ to 5 k $\Omega$ range is adequate for the entire INT_N net.                                                |

| TEST0       | E2                                                                                                                                                                                                                                                                                                                                                                                                          | Input, LVCMOS                    | weak pull-up          | Reserved TI test pin. During normal (non-test-mode) operation,                                                                                                                                                                                                                                                                                                                                                            |

| TEST1       | E14                                                                                                                                                                                                                                                                                                                                                                                                         | Input, LVCMOS                    | weak pull-up          | these pins are configured as inputs and therefore are not affected<br>by the presence of a signal. These pins may be left floating, tied to<br>GND, or connected to a 2.5V (max) output.                                                                                                                                                                                                                                  |

| TEST4       | F4                                                                                                                                                                                                                                                                                                                                                                                                          | Input, LVCMOS                    | None                  | Reserved TI test pin. During normal (non-test-mode) operation, this<br>pin is configured as an input and therefore is not affected by the<br>presence of a signal. This pin should be tied to GND or left floating<br>to support both the Repeater and Retimer device.                                                                                                                                                    |

| TEST5       | E4                                                                                                                                                                                                                                                                                                                                                                                                          | Input, LVCMOS                    | None                  | Reserved TI test pin. During normal (non-test-mode) operation, this                                                                                                                                                                                                                                                                                                                                                       |

| TEST6       | D4                                                                                                                                                                                                                                                                                                                                                                                                          | Input, LVCMOS                    | None                  | pin is configured as an input and therefore is not affected by the presence of a signal. This pin may be left floating, tied to GND, or                                                                                                                                                                                                                                                                                   |

| TEST7       | D12                                                                                                                                                                                                                                                                                                                                                                                                         | Input, LVCMOS                    | None                  | connected to a 2.5V (max) output.                                                                                                                                                                                                                                                                                                                                                                                         |

| VDD         | D6, D8, D10,<br>E5, E6, E7, E8,<br>E9, E10, F6,<br>F8, F10                                                                                                                                                                                                                                                                                                                                                  | Power                            | None                  | Power supply, VDD = 2.5 V ±5%. TI recommends connecting at least six de-coupling capacitors between the Retimer's VDD plane and GND as close to the Retimer as possible. For example, four 0.1 $\mu$ F capacitors and two 1 $\mu$ F capacitors directly beneath the device or as close to the VDD pins as possible. The VDD pins on this device should be connected through a low-resistance path to the board VDD plane. |

| GND         | A1, A2, A4, A6,<br>A8, A10, A12,<br>A14, A15, B2,<br>B4, B6, B8,<br>B10, B12, B14,<br>C2, C3, C4, C5,<br>C6, C7, C8, C9,<br>C10, C11, C12,<br>C13, C14, D1,<br>D2, D5, D7, D9,<br>D11, D14, D15,<br>E11, F1, F2,<br>F5, F7, F9, F11,<br>F14, F15, G2,<br>G3, G4, G5,<br>G6, G7, G8,<br>G9, G10, G11,<br>G12, G13, G14,<br>H2, H4, H6, H8,<br>H10, H12, H14,<br>J1, J2, J4, J6,<br>J8, J10, J12,<br>J14, J15 | Power                            | None                  | Ground reference. The GND pins on this device should be connected through a low-resistance path to the board GND plane.                                                                                                                                                                                                                                                                                                   |

## 8 Specifications

### 8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                            |                                                                           | MIN  | MAX  | UNIT |

|----------------------------|---------------------------------------------------------------------------|------|------|------|

| VDD <sub>ABSMAX</sub>      | Supply voltage (VDD)                                                      | -0.5 | 2.75 | V    |

| VIO <sub>2.5V,ABSMAX</sub> | 2.5 V I/O voltage (LVCMOS, CMOS and Analog)                               | -0.5 | 2.75 | V    |

| VIO <sub>3.3V,ABSMAX</sub> | Open Drain Voltage (SDA, SDC, INT_N) and LVCMOS Input Voltage (READ_EN_N) | -0.5 | 4.0  | V    |

| VINABSMAX                  | Signal input voltage (RXnP, RXnN)                                         | -0.5 | 2.75 | V    |

| VOUT <sub>ABSMAX</sub>     | Signal output voltage (TXnP, TXnN)                                        | -0.5 | 2.75 | V    |

| TJ <sub>ABSMAX</sub>       | Junction temperature                                                      |      | 150  | °C   |

| Tstg                       | Storage temperature                                                       | -40  | 150  | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 8.2 ESD Ratings

|                    |                                                                   |                                                                                     | VALUE | UNIT |

|--------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------|------|

|                    | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2                                                                                  | kV    |      |

| V <sub>(ESD)</sub> | Electrostatic discharge                                           | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{\left(2\right)}$ | ±1    | kV   |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions. Pins listed as ±2 kV may actually have higher performance.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions. Pins listed as ±1 kV may actually have higher performance.

### 8.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                           |                                                                              | MIN   | MAX               | UNIT |

|---------------------------|------------------------------------------------------------------------------|-------|-------------------|------|

| VDD                       | Supply voltage, VDD to GND. DC plus AC power should not exceed these limits. | 2.375 | 2.625             | V    |

| NVDD                      | Supply noise, DC to < 50 Hz, sinusoidal <sup>(1)</sup>                       |       | 250               | mVpp |

| NVDD                      | Supply noise, 50 Hz to 10 MHz, sinusoidal <sup>(1)</sup>                     |       | 20                | mVpp |

| NVDD                      | Supply noise, >10 MHz, sinusoidal <sup>(1)</sup>                             |       | 10                | mVpp |

| T <sub>rampVDD</sub>      | VDD supply ramp time, from 0V to 2.375V                                      | 150   |                   | μS   |

| TJ                        | Operating junction temperature                                               | -40   | 110               | °C   |

| T <sub>A</sub>            | Operating ambient temperature                                                | -40   | 85 <sup>(2)</sup> | °C   |

| VIO <sub>2.5V</sub>       | 2.5 V I/O voltage (LVCMOS, CMOS and Analog)                                  | 2.375 | 2.625             | V    |

| VIO <sub>3.3V,INT_N</sub> | Open Drain LVCMOS I/O voltage (INT_N)                                        |       | 3.6               | V    |

| VIO <sub>3.3V</sub>       | Open Drain LVCMOS I/O voltage (SDA, SDC)                                     | 2.375 | 3.6               | V    |

(1) Steps must be taken to ensure the combined AC plus DC supply noise meets the specified VDD supply voltage limits.

(2) Steps must be taken to ensure the operating junction temperature range is met.

ZHCSKE9C-DECEMBER 2015-REVISED OCTOBER 2019

www.ti.com.cn

STRUMENTS

XAS

#### 8.4 Thermal Information

|                       |                                              | CONDITIONS/ A |                             |                             |                             |      |

|-----------------------|----------------------------------------------|---------------|-----------------------------|-----------------------------|-----------------------------|------|

| THERMAL ME            | HERMAL METRIC <sup>(1)</sup>                 |               | 10-layer 8in x<br>6in Board | 20-layer 8in x<br>6in Board | 30-layer 8in x<br>6in Board | UNIT |

| $R_{	ext{	heta}JA}$   | Junction-to-ambient thermal resistance       | 26.4          | 9.3                         | 8.5                         | 8.2                         |      |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 1.6           | -                           | -                           | -                           |      |

| $R_{	extsf{	heta}JB}$ | Junction-to-board thermal resistance         | 9.3           | -                           | -                           | -                           | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.1           | 0.1                         | 0.1                         | 0.1                         |      |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 9.3           | 5                           | 4.9                         | 4.6                         |      |

(1) For more information about traditional and new thermal metrics, see the IC Package-Thermal Metrics application report, SPRA953.

(2) No heat sink or airflow was assumed for these estimations. Depending on the application, a heat sink, faster airflow, and/or reduced ambient temperature (<85 C) may be required in order to meet the maximum junction temperature specification per the Recommended Operating Conditions section.

#### 8.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                      | TEST CONDITIONS                                                                                                                                                                                                         | MIN     | ТҮР | MAX               | UNIT |

|---------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|-------------------|------|

| Rbaud               | Input data rate                | Full-rate                                                                                                                                                                                                               | 20.2752 |     | 25.8              | Gbps |

| Rbaud               |                                | Half-rate                                                                                                                                                                                                               | 10.1376 |     | 12.9              | Gbps |

| Rbaud               |                                | Quarter-rate                                                                                                                                                                                                            | 5.0688  |     | 6.45              | Gbps |

| t <sub>eeprom</sub> | EEPROM configuration load time | Single device reading its<br>configuration from an EEPROM.<br>Common channel configuration. This<br>time scales with the number of<br>devices reading from the same<br>EEPROM.                                          |         |     | 15 <sup>(1)</sup> | ms   |

| t <sub>eeprom</sub> | EEPROM configuration load time | Single device reading its<br>configuration from an EEPROM.<br>Unique channel configuration. This<br>time scales with the number of<br>devices reading from the same<br>EEPROM.                                          |         |     | 40 <sup>(1)</sup> | ms   |

| t <sub>POR</sub>    | Power-on reset assertion time  | Internal power-on reset (PoR)<br>stretch between stable power supply<br>and de-assertion of internal PoR.<br>The SMBus address is latched on<br>the completion of the PoR stretch,<br>and SMBus accesses are permitted. |         |     | 50                | ms   |

(1) From low assertion of READ\_EN\_N to low assertion of ALL\_DONE\_N. Does not include Power-On Reset time.

## **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

| •                         | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TEST CONDITIONS                                                                                                                                            | MIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TYP  | MAX  | UNIT |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--|

| POWER SL                  | IPPLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |      |      |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | With CTLE, full DFE, Tx FIR,<br>Driver, and Crosspoint enabled. Idle<br>power consumption not included.                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 241  | 305  | mW   |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | With CTLE, full DFE, Tx FIR, and<br>Driver enabled; Crosspoint disabled.<br>Idle power consumption not<br>included.                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 233  |      | mW   |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | With CTLE, partial DFE (taps 1-2<br>only), Tx FIR, and Driver enabled;<br>Crosspoint and DFE taps 3-5<br>disabled. Idle power consumption<br>not included. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 220  |      | mW   |  |

| W <sub>channel</sub>      | Power consumption per active<br>channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | With CTLE, Tx FIR, Driver, and<br>Crosspoint enabled; DFE disabled.<br>Idle power consumption not<br>included.                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 211  | 290  | mW   |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Assuming CDR acquiring lock with<br>CTLE, full DFE, Tx FIR, Driver, and<br>Crosspoint enabled. Idle power<br>consumption not included.                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 365  | 430  | mW   |  |