DCPA10505, DCPA10505D DCPA10512, DCPA10512D DCPA10515, DCPA10515D

ZHCSG81 - APRIL 2017

# DCPA1 系列 1W、隔离式非稳压直流/直流转换器模块

# 1 特性

- 2.0kV 直流隔离(运行)

- 具有软启动,可减小浪涌电流

- 频率同步

- EN55022 B 类 EMC 性能

- UL1950 认证组件

- 7 引脚 PDIP 和 7 引脚 SOP 封装

### 2 应用

- 信号路径隔离

- 消除接地环路

- 数据采集

- 工业控制和仪器

- 测试设备

# 3 说明

DCPA1 系列是一系列 1W、隔离式非稳压直流/直流转换器模块。DCPA1 系列器件需要至少两个外部组件,其包含片上器件保护装置,且能够同步至外部时钟。

DCPA1 系列器件集 这些特性 和小型尺寸于一体,适合各种 应用且在需要信号路径隔离的 应用中 是一种易于使用的解决方案。

警告:此产品具有运行隔离功能,仅可用于信号隔离。 不可作为需要增强型隔离的安全隔离电路的一部分使 用。请参见*功能 描述*部分中的定义。

#### 器件信息(1)

| 部件号       | 封装       | 封装尺寸(标称值)         |

|-----------|----------|-------------------|

| DCPA1xxxx | PDIP (7) | 19.18mm × 10.60mm |

| DCPATXXXX | SOP (7)  | 19.16mm × 10.60mm |

(1) 要了解所有可用封装,请参见数据表末尾的可订购产品附录。

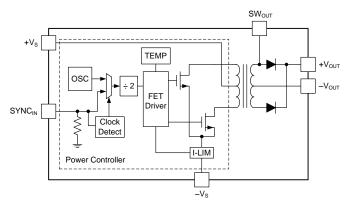

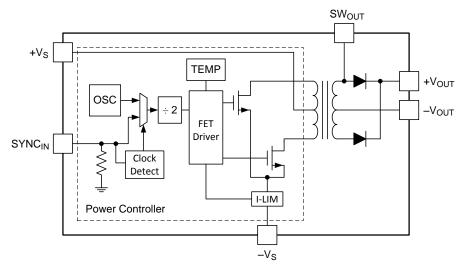

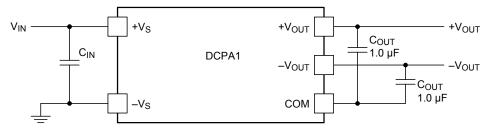

#### 单路输出方框图

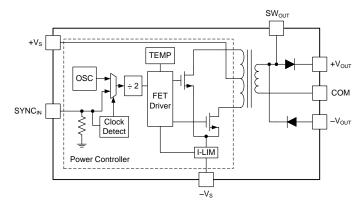

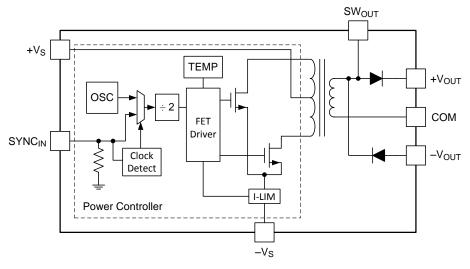

#### 双路输出方框图

# 目录

| 4 | <b>杜州</b>                                   |    | 7.2 Functional Block Diagrams  | 13 |

|---|---------------------------------------------|----|--------------------------------|----|

| I | 特性                                          |    | S S                            |    |

| 2 | 应用 1                                        | _  | 7.3 Feature Description        |    |

| 3 | 说明 1                                        | 8  | Application and Implementation |    |

| 4 | 修订历史记录 2                                    |    | 8.1 Application Information    | 17 |

| 5 | Pin Configuration and Functions3            |    | 8.2 Typical Application        | 18 |

| 6 | Specifications4                             | 9  | Power Supply Recommendations   | 19 |

| • | 6.1 Absolute Maximum Ratings                | 10 | Layout                         | 20 |

|   | 6.2 ESD Ratings                             |    | 10.1 Layout Guidelines         | 20 |

|   | 6.3 Recommended Operating Conditions        |    | 10.2 Layout Example            |    |

|   | 6.4 Electrical Characteristics              | 11 | 器件和文档支持                        |    |

|   |                                             |    | 11.1 器件支持                      |    |

|   | 6.5 Switching Characteristics 6             |    | 11.2 文档支持                      |    |

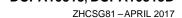

|   | 6.6 Typical Characteristics (DCPA10505)     |    | 11.3 社区资源                      |    |

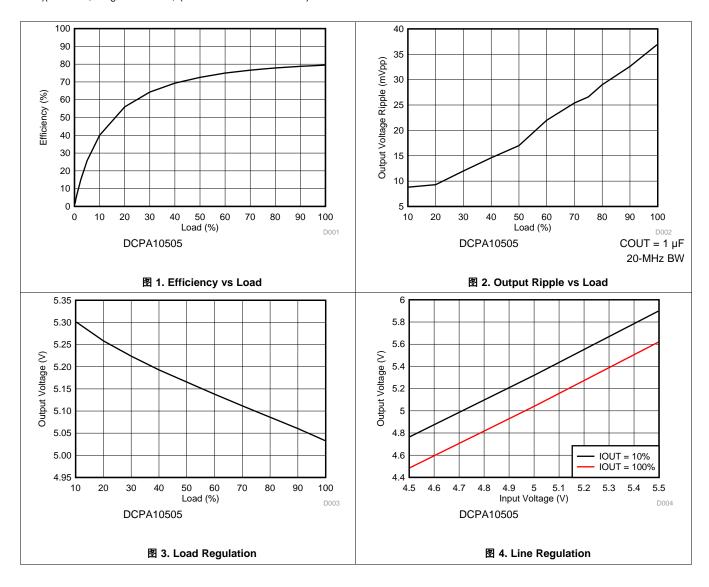

|   | 6.7 Typical Characteristics (DCPA10512)     |    | 11.4 相关链接                      |    |

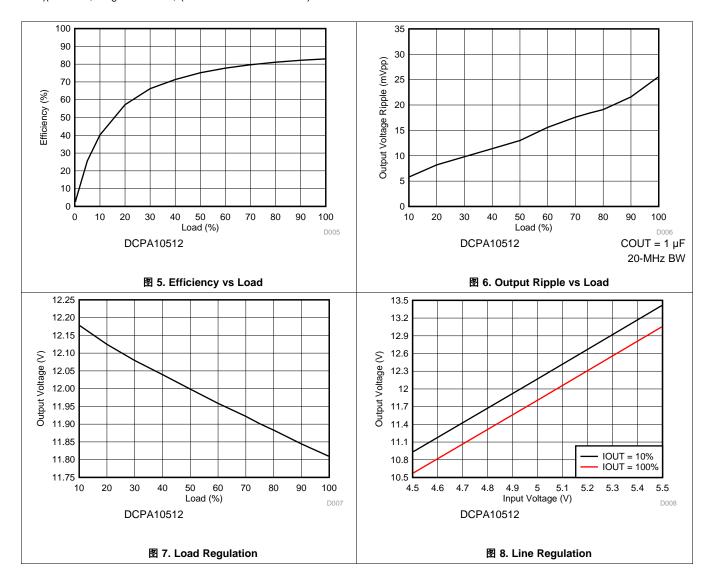

|   | 6.8 Typical Characteristics (DCPA10515)9    |    |                                |    |

|   | 6.9 Typical Characteristics (DCPA10505D)10  |    | 11.5 商标                        |    |

|   | 6.10 Typical Characteristics (DCPA10512D)11 |    | 11.6 静电放电警告                    |    |

|   | 6.11 Typical Characteristics (DCPA10515D)12 |    | 11.7 Glossary                  |    |

| 7 | Detailed Description 13                     | 12 | 机械、封装和可订购信息                    | 22 |

|   | 7.1 Overview 13                             |    |                                |    |

|   |                                             |    |                                |    |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| 日期         | 修订版本 | 注释    |

|------------|------|-------|

| 2017 年 4 月 | *    | 首次发布。 |

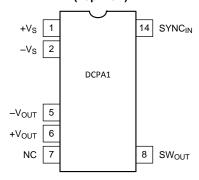

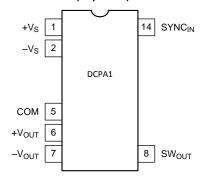

# 5 Pin Configuration and Functions

**INSTRUMENTS**

#### NVA and DUA Package 7-Pin PDIP and SOP (Single Output) (Top View)

### NVA and DUA Package 7-Pin PDIP and SOP (Dual Output) (Top View)

# **Pin Functions**

| 1 1 1 1            |                   |                 |                    |                                                                                                                                                                                                       |  |  |  |  |

|--------------------|-------------------|-----------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                    | PIN NUMBER        |                 |                    |                                                                                                                                                                                                       |  |  |  |  |

| PIN NAME           | SINGLE-<br>OUTPUT | DUAL-<br>OUTPUT | I/O <sup>(1)</sup> | Description                                                                                                                                                                                           |  |  |  |  |

| COM                | _                 | 5               | 0                  | Output side common                                                                                                                                                                                    |  |  |  |  |

| NC                 | 7                 | _               | _                  | No connection                                                                                                                                                                                         |  |  |  |  |

| SYNC <sub>IN</sub> | 14                | 14              | I                  | Synchronization. This pin is used to synchronize to an external clock. Internally it is pulled to GND. If valid clock is not detected on this pin, the SN6505 shifts automatically to internal clock. |  |  |  |  |

| SW <sub>OUT</sub>  | 8                 | 8               | 0                  | Unrectified transformer output.                                                                                                                                                                       |  |  |  |  |

| +V <sub>OUT</sub>  | 6                 | 6               | 0                  | Positive output voltage                                                                                                                                                                               |  |  |  |  |

| +V <sub>S</sub>    | 1                 | 1               | I                  | Input voltage                                                                                                                                                                                         |  |  |  |  |

| -V <sub>OUT</sub>  | 5                 | 7               | 0                  | Negative output voltage                                                                                                                                                                               |  |  |  |  |

| -V <sub>S</sub>    | 2                 | 2               | I                  | Input side common                                                                                                                                                                                     |  |  |  |  |

(1) I = Input, O = Output

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                       |                    |                | MIN  | MAX             | UNIT |

|---------------------------------------|--------------------|----------------|------|-----------------|------|

|                                       | +V <sub>S</sub>    |                | -0.5 | 6               | V    |

| lanut valtaga                         |                    | 50ns transient | -1.0 | 7               | V    |

| Input voltage                         | SYNC <sub>IN</sub> |                | -0.5 | +V <sub>S</sub> | V    |

|                                       |                    | 50ns transient | -1.0 | 6               | V    |

| Lead temperature (soldering, 10 s)    |                    |                |      |                 | °C   |

| Storage temperature, T <sub>stg</sub> |                    |                | -60  | 125             | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|   |                 |                                                                     | VALUE | UNIT |

|---|-----------------|---------------------------------------------------------------------|-------|------|

|   |                 | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±1000 | \/   |

| V | (ESD) discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

| 1 0 1                               |      |     |     |      |

|-------------------------------------|------|-----|-----|------|

|                                     | MIN  | NOM | MAX | UNIT |

| Input voltage                       | 4.5  | 5   | 5.5 | V    |

| Output power                        | 0.05 |     | 1   | W    |

| Operating ambient temperature range | -40  |     | 100 | °C   |

#### 6.4 Electrical Characteristics

$T_A = 25$ °C, + $V_S =$  nominal,  $C_{IN} = 2.2 \ \mu F$ ,  $C_{OUT} = 1.0 \ \mu F$ , (unless otherwise noted)

|                  | PARAMETER      | TEST CONDITIONS                                                 | MIN | TYP | MAX                | UNIT |

|------------------|----------------|-----------------------------------------------------------------|-----|-----|--------------------|------|

| OUTPU            | IT             |                                                                 | ·   |     |                    |      |

| P <sub>OUT</sub> | Output power   | Over +V <sub>S</sub> range, I <sub>OUT</sub> = 100% (full load) |     |     | 1                  | W    |

|                  |                | DCPA10505                                                       |     |     | 200                | mA   |

|                  | Output current | DCPA10505D                                                      |     |     | 200 <sup>(1)</sup> | mA   |

| ١.               |                | DCPA10512                                                       |     |     | 83                 | mA   |

| I <sub>OUT</sub> |                | DCPA10512D                                                      |     |     | 83 <sup>(1)</sup>  | mA   |

|                  |                | DCPA10515                                                       | ·   |     | 66                 | mA   |

|                  |                | DCPA10515D                                                      |     |     | 66 <sup>(1)</sup>  | mA   |

**STRUMENTS**

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

www.ti.com.cn

# **Electrical Characteristics (continued)**

$T_A = 25$ °C, + $V_S =$  nominal,  $C_{IN} = 2.2 \ \mu F$ ,  $C_{OUT} = 1.0 \ \mu F$ , (unless otherwise noted)

| PARAMETER        |                                      | TEST CON                                                                                     | IDITIONS      | MIN         | TYP   | MAX  | UNIT    |

|------------------|--------------------------------------|----------------------------------------------------------------------------------------------|---------------|-------------|-------|------|---------|

|                  |                                      |                                                                                              | DCPA10505     |             | 5.0   |      | V       |

|                  |                                      |                                                                                              | DCPA10505D    |             | ±5.0  |      | V       |

|                  | Output valtage                       | I <sub>OUT</sub> = 100% load <sup>(2)</sup>                                                  | DCPA10512     |             | 12.0  |      | V       |

|                  | Output voltage                       | I <sub>OUT</sub> = 100% load (-)                                                             | DCPA10512D    | ·           | ±12.0 |      | V       |

|                  |                                      |                                                                                              | DCPA10515     | ·           | 15.0  |      | V       |

| V <sub>OUT</sub> |                                      |                                                                                              | DCPA10515D    | ·           | ±15.0 |      | V       |

|                  | Temperature variation                | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le 100^{\circ}\text{C}, \text{ I}_{\text{OU}}$ | r = 100% load | ·           | 0.02  |      | %/°C    |

|                  | Line regulation                      | $+V_S(MIN)$ to $+V_S(TYP)$ , $I_{OUT} = 10\%$ load                                           |               |             | 10%   |      |         |

|                  | Line regulation                      | $+V_S(TYP)$ to $+V_S(MAX)$ , $I_{OUT} = 10\%$ load                                           |               | ·           | 10%   |      |         |

|                  | Load regulation (3)                  | 10% to 100% load                                                                             |               |             | 5%    |      |         |

| $V_{RIPPLE}$     | Output voltage ripple (4)            | C <sub>OUT</sub> = 1 μF, I <sub>OUT</sub> = 50%                                              |               |             | 20    |      | $mV_PP$ |

| INPUT            |                                      |                                                                                              |               |             |       |      |         |

| +V <sub>S</sub>  | Input voltage range                  |                                                                                              |               | 4.5         |       | 5.5  | V       |

| 111/1/0          | 1)/ I ladomioltogo logicout          | +V <sub>S</sub> increasing threshold                                                         |               |             |       | 2.25 | V       |

| UVLO             | +V <sub>S</sub> Undervoltage lockout | +V <sub>S</sub> decreasing threshold                                                         | 1             | 1.7         |       |      | V       |

|                  |                                      |                                                                                              | DCPA10505     |             | 35    |      | mA      |

|                  |                                      |                                                                                              | DCPA10505D    |             | 25    |      | mA      |

|                  | Quiescient current                   | 1 - 0% load                                                                                  | DCPA10512     |             | 29    |      | mA      |

| IQ               | Quiescient current                   | I <sub>OUT</sub> = 0% load                                                                   | DCPA10512D    |             | 36    |      | mA      |

|                  |                                      |                                                                                              | DCPA10515     | <del></del> | 31    |      | mA      |

|                  |                                      |                                                                                              | DCPA10515D    | ·           | 38    |      | mA      |

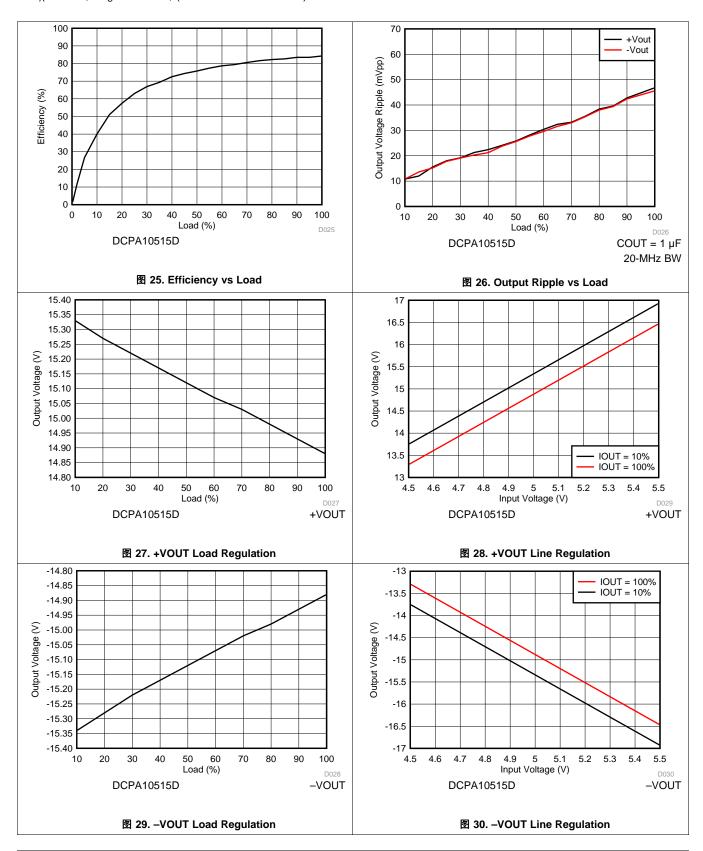

See Load Regulation graphs in the Typical Characterization section for typical voltage at all load conditions. Load regulation =  $(V_{OUT}$  at 10% load –  $V_{OUT}$  at 100%)/ $V_{OUT}$  at 75% load Guaranteed by design. Not production tested.

# **Electrical Characteristics (continued)**

$T_A = 25$ °C, +V<sub>S</sub> = nominal,  $C_{IN} = 2.2 \mu F$ ,  $C_{OUT} = 1.0 \mu F$ , (unless otherwise noted)

| PARAMETER                                    | TEST COM                             | NDITIONS    | MIN                   | TYP  | MAX  | UNIT  |

|----------------------------------------------|--------------------------------------|-------------|-----------------------|------|------|-------|

| ISOLATION                                    |                                      |             |                       |      |      | -     |

|                                              | 1-second flash test,                 | DC          | 2.0 <sup>(5)(4)</sup> |      |      | kVDC  |

|                                              | voltage                              | AC          | 1.5 <sup>(5)</sup>    |      |      | kVrms |

| V Lastagas                                   | 1-second flash test, leaka           | age current |                       |      | 30   | μA    |

| V <sub>ISO</sub> Isolation                   | Continuous working                   | DC          |                       |      | 60   | VDC   |

|                                              | voltage across isolation             | AC          |                       |      | 42.5 | VAC   |

|                                              | barrier                              | dV/dt       |                       |      | 50   | V/ms  |

| C <sub>ISO</sub> Barrier capacitance         | V <sub>ISO</sub> = 750 Vrms          |             |                       | 28   |      | pF    |

| PERFORMANCE                                  |                                      |             |                       |      |      |       |

|                                              |                                      | DCPA10505   |                       | 85%  |      |       |

|                                              |                                      | DCPA10505D  |                       | 85%  |      |       |

| Efficiency                                   | 1 – 1009/                            | DCPA10512   |                       | 87%  |      |       |

| Efficiency                                   | I <sub>OUT</sub> = 100%              | DCPA10512D  |                       | 88%  |      |       |

|                                              |                                      | DCPA10515   |                       | 86%  |      |       |

|                                              |                                      | DCPA10515D  |                       | 86%  |      |       |

|                                              |                                      | DCPA10505   |                       | 3.0% |      |       |

|                                              | 50% to 100% load step                | DCPA10512   |                       | 1.9% |      |       |

| Transient response (4)                       |                                      | DCPA10515   |                       | 2.0% |      |       |

| Transient response                           |                                      | DCPA10505D  |                       | 2.7% |      |       |

|                                              | 50% to 100% load step per output (6) | DCPA10512D  |                       | 2.0% |      |       |

|                                              | por output                           | DCPA10515D  |                       | 1.6% |      |       |

| RELIABILITY                                  |                                      |             |                       |      |      | •     |

| Demonstrated                                 | $T_A = 55^{\circ}C$                  |             |                       | 55   |      | FITS  |

| CAPACITANCE                                  | ·                                    |             | ·                     |      | ·    |       |

| C <sub>IN</sub> External input capacitance   | Ceramic                              |             | 2.2                   |      |      | μF    |

| C <sub>OUT</sub> External output capacitance | Ceramic                              |             | 0.1                   | 1.0  | 200  | μF    |

| THERMAL SHUTDOWN                             |                                      |             |                       |      |      |       |

| T <sub>SD</sub> Die temperature at shutdown  |                                      |             |                       | 168  |      | °C    |

| I <sub>SD</sub> Shutdown current             |                                      |             |                       | 3    |      | mA    |

<sup>(5)</sup> See Isolation Voltage section for more information.

# 6.5 Switching Characteristics

at  $T_A$  = +25°C, +V<sub>S</sub> = nominal,  $C_{IN}$  = 2.2  $\mu$ F,  $C_{OUT}$  = 1.0  $\mu$ F, (unless otherwise noted)

|                   | PARAMETER                                      | TEST CONDITIONS      | MIN | TYP | MAX  | UNIT |

|-------------------|------------------------------------------------|----------------------|-----|-----|------|------|

| fosc              | Oscillator frequency                           | $f_{SW} = f_{OSC}/2$ |     | 850 |      | kHz  |

| f <sub>SYNC</sub> | Synchronization frequency range                |                      | 750 |     | 1000 | kHz  |

| V <sub>IH</sub>   | High-level input threshold, SYNC <sub>IN</sub> |                      | 0.7 |     |      | V    |

| V <sub>IL</sub>   | Low-level input threshold, SYNC <sub>IN</sub>  |                      |     |     | 0.3  | V    |

<sup>(6)</sup> Transient testing for dual output devices are tested with one output loaded with a 50% static load and the other output loaded with a 50% to 100% dynamic load step.

www.ti.com.cn

# 6.6 Typical Characteristics (DCPA10505)

# TEXAS INSTRUMENTS

# 6.7 Typical Characteristics (DCPA10512)

# 6.8 Typical Characteristics (DCPA10515)

**NSTRUMENTS**

# TEXAS INSTRUMENTS

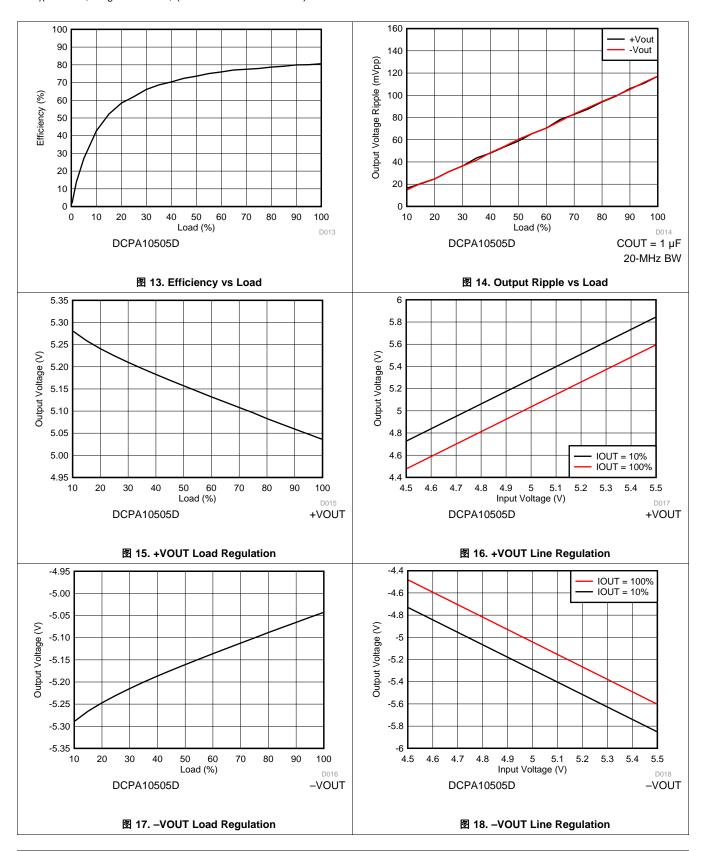

# 6.9 Typical Characteristics (DCPA10505D)

www.ti.com.cn

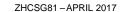

# 6.10 Typical Characteristics (DCPA10512D)

# TEXAS INSTRUMENTS

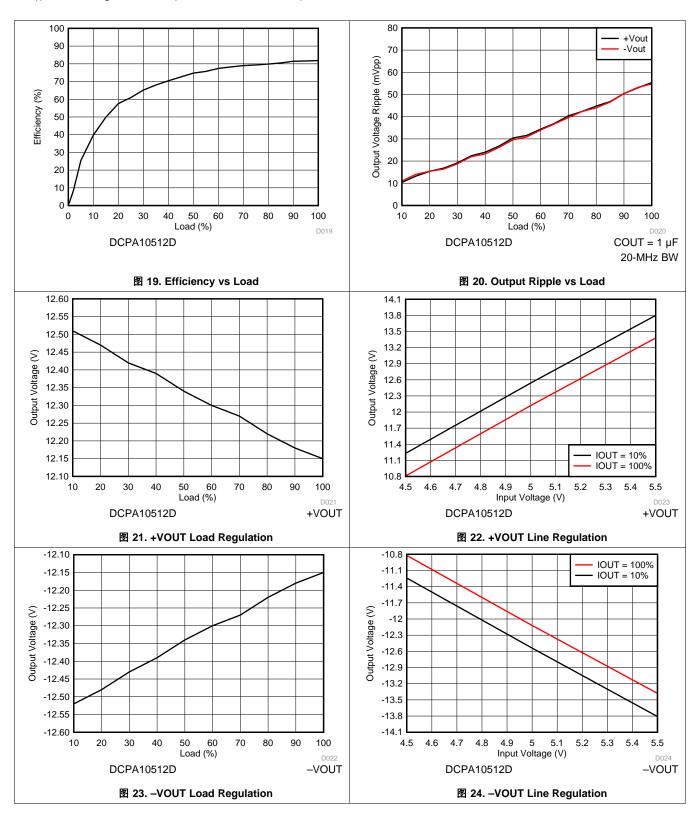

# 6.11 Typical Characteristics (DCPA10515D)

# 7 Detailed Description

INSTRUMENTS

### 7.1 Overview

The DCPA1 offers up to 1 W of isolated, unregulated output power from a 5-V input source with a typical efficiency of up to 87%. This efficiency is achieved through highly integrated packaging technology and the implementation of a custom power stage and control device. The DCPA1 devices are specified for operational isolation only. The circuit design uses an advanced BiCMOS and DMOS process.

# 7.2 Functional Block Diagrams

图 31. Single Output Device

图 32. Dual Output Device

#### 7.3 Feature Description

#### 7.3.1 Isolation

Underwriters Laboratories, UL™ defines several classes of isolation that are used in modern power supplies.

Safety extra low voltage (SELV) is defined by UL (UL1950 E199929) as a secondary circuit which is so designated and protected that under normal and single fault conditions the voltage between any two accessible parts, or between an accessible part and the equipment earthing terminal for operational isolation does not exceed steady state 42 V peak or  $60 \text{ V}_{DC}$  for more than 1 second.

#### 7.3.1.1 Operation or Functional Isolation

Operational or functional isolation is defined by the use of a high-potential (hipot) test only. Typically, this isolation is defined as the use of insulated wire in the construction of the transformer as the primary isolation barrier. The hipot one-second duration test (dielectric voltage, withstand test) is a production test used to verify that the isolation barrier is functioning. Products with operational isolation should never be used as an element in a safety-isolation system.

#### 7.3.1.2 Basic or Enhanced Isolation

Basic or enhanced isolation is defined by specified creepage and clearance limits between the primary and secondary circuits of the power supply. Basic isolation is the use of an isolation barrier in addition to the insulated wire in the construction of the transformer. Input and output circuits must also be physically separated by specified distances.

#### 7.3.1.3 Continuous Voltage

For a device that has no specific safety agency approvals (operational isolation), the continuous voltage that can be applied across the part in normal operation is less than 42.4  $V_{RMS}$ , or 60  $V_{DC}$ . Ensure that both input and output voltages maintain normal SELV limits. The isolation test voltage represents a measure of immunity to transient voltages.

#### **WARNING**

Do not use the device as an element of a safety isolation system that exceeds the SELV limit.

If the device is expected to function correctly with more than  $42.4~V_{RMS}$  or  $60~V_{DC}$  applied continuously across the isolation barrier, then the circuitry on both sides of the barrier must be regarded as operating at an unsafe voltage, and further isolation or insulation systems must form a barrier between these circuits and any user-accessible circuitry according to safety standard requirements.

#### 7.3.1.4 Isolation Voltage

The terms *Hipot test, flash-tested, withstand voltage, proof voltage, dielectric withstand voltage,* and *isolation test voltage* all describe the same spec. The terms describe a test voltage applied for a specified time across a component designed to provide electrical isolation to verify the integrity of that isolation. TI's DCPA1 series of dc-dc converters are all 100% production tested at 1.5 kV<sub>AC</sub> for one second.

#### 7.3.1.5 Repeated High-Voltage Isolation Testing

Repeated high-voltage isolation testing of a barrier component can degrade the isolation capability, depending on materials, construction, and environment. The DCPA1 series of dc-dc converters have toroidal, enameled, wire isolation transformers with no additional insulation between the primary and secondary windings. While a device can be expected to withstand several times the stated test voltage, the isolation capability depends on the wire insulation. Any material, including this enamel (typically polyurethane), is susceptible to eventual chemical degradation when subject to very-high applied voltages. Therefore, strictly limit the number of high-voltage tests and repeated high-voltage isolation testing. However, if it is absolutely required, reduce the voltage by 20% from specified test voltage with a duration limit of one second per test.

# Feature Description (接下页)

#### 7.3.2 Power Stage

The DCPA1 series of devices uses a push-pull, center-tapped topology. The DCPA1 devices switch at 425 kHz (divide-by-2 from an 850-kHz oscillator).

#### 7.3.3 Input and Output Capacitors

For all DCPA1 designs, a minimum 2.2-μF, low-ESR, ceramic input capacitor is required. Place the input capacitor as close as possible to the device input pins, +V<sub>S</sub> and -V<sub>S</sub>, to ensure good startup performance.

The recommended typical output capacitance for each output of any DCPA1 device is 1.0-μF of low-ESR, ceramic capacitance. Adding additional output capacitance will aid in ripple reduction, however, any additional capacitance will also require additional input current at start-up.

#### 7.3.4 Oscillator And Watchdog Circuit

The onboard, 850-kHz oscillator generates the switching frequency via a divide-by-2 circuit. The oscillator can be synchronized to an external source, and is used to minimize system noise. A watchdog circuit checks the operation of the oscillator circuit.

#### 7.3.5 Synchronization

When more than one DC/DC converter is needed onboard, beat frequencies and other electrical interference can be generated. This interference occurs because of the small variations in switching frequencies between the DC/DC converters.

The DCPA1 series of devices overcomes this interference by allowing devices to synchronize to an external clock. The SYNC<sub>IN</sub> pin responds to the rising edge of the external clock. If the external clock is removed, the DCPA1 will return to the frequency of the internal oscillator. If unused, it is recommended to connect this pin to the input side common, -V<sub>S</sub>.

### 7.3.6 SW<sub>OUT</sub>

The SW<sub>OLIT</sub> pin is directly connected to one winding of the transformer secondary prior to the output rectifier. It is not recommended to pull current from this pin. Do not connect capacitance directly to this pin as it will degrade performance. The SW<sub>OUT</sub> pin is not compatible with the SYNC<sub>IN</sub> pin, therefore these two pins should not be connected together.

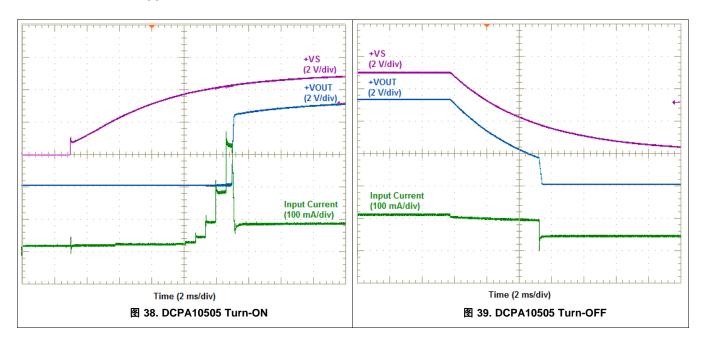

## 7.3.7 Soft Start

The DCPA1 series of devices includes a soft-start feature that prevents high in-rush current during power up. Once input power is applied, there is a delay of typically 10 ms before the output voltage begins to rise. Once the output voltage begins to rise, the soft start time is typically 5 ms.

## 7.3.8 Load Regulation

The load regulation of the DCPA1 series of devices is specified at 10% to 100% load. Operation below 10% load may cause the output voltage to increase up to 40% higher than the typical output voltage. Placing a minimum 10% load will ensure the output voltage is within the range specified in the *Electrical Characteristics* table.

# TEXAS INSTRUMENTS

## Feature Description (接下页)

#### 7.3.9 Thermal Performance

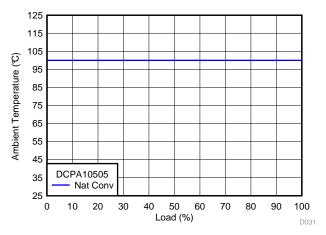

The DCPA1 family of devices have been characterized to operate over an ambient temperature range of −40°C to +100°C. The Safe Operating Area curve shown below in 33, represents the operating conditions of the DCPA1 devices where the maximum thermal ratings will not be exceeded. 33 shows that all DCPA1 devices can safely operate over the full ambient temperature range, without airflow, to the full current rating of the device.

图 33. Thermal Safe Operating Area

#### 7.3.9.1 Thermal Protection

The DCPA1 series of devices are protected by a thermal-shutdown circuit.

If the on-chip temperature rises above 150°C, the device shuts down. Normal operation resumes as soon as the temperature falls below 150°C. While the overtemperature condition continues, operation randomly cycles on and off. This cycling continues until the temperature is reduced.

### 7.3.10 Current Limit

For protection against a short circuit on the output, the DCPA1 series of devices have a built in current limit protection threshold of 1.75A (typical). These devices are not intended to be used at output currents greater than the device's output current rating as shown in the *Electrical Characteristics* table. Operating at currents greater than the device's current rating, but less than current limit threshold will cause excessive stress to the internal components. For protection against a partial short circuit condition, an input fuse or output fuse is recommended.

#### 7.3.11 Construction

The basic construction of the DCPA1 series of devices is the same as standard integrated circuits. The molded package contains no substrate. The DCPA1 series of devices are constructed using an IC, rectifier diodes, and a wound magnetic toroid on a leadframe. Because the package contains no solder, the devices do not require any special printed circuit board (PCB) assembly processing. This architecture results in an isolated DC/DC converter with inherently high reliability.

# 8 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1 Application Information

# 8.1.1 Ripple Reduction

INSTRUMENTS

The high switching frequency of 425 kHz allows simple filtering. To reduce output voltage ripple, it is recommended that a minimum of 1- $\mu$ F capacitor be used on the +V<sub>OUT</sub> pin. For dual output devices, decouple both of the outputs to the COM pin. The required 2.2- $\mu$ F, low ESR ceramic input capacitor also helps to reduce ripple and noise. See *DC-to-DC Converter Noise Reduction* (SBVA012).

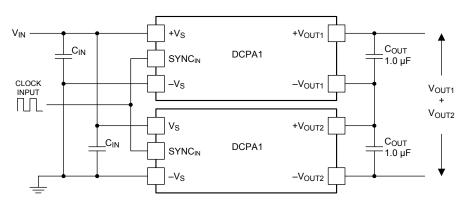

#### 8.1.2 Connecting the DCPA1 in Series

Multiple DCPA1 isolated 1-W DC/DC converters can be connected in series to provide non-standard voltage rails. This configuration is possible by using the floating outputs provided by the galvanic isolation of the DCPA1 devices by connecting the  $+V_{OUT}$  from one DCPA1 to the  $-V_{OUT}$  of another as shown in 34. The synchronization feature allows easy synchronization to prevent power-rail beat frequencies at no additional filtering cost.

图 34. Multiple DCPA1 Devices Connected in Series

The outputs of a dual-output DCPA1 device can also be connected in series to provide two times the magnitude of +V<sub>OUT</sub>, as shown in ₹ 35. For example, connect a dual-output, ±15-V, DCPA10515D device to provide a 30-V rail.

图 35. Dual Output Devices Connected in Series

# TEXAS INSTRUMENTS

## 8.1.3 Connecting the DCPA1 in Parallel

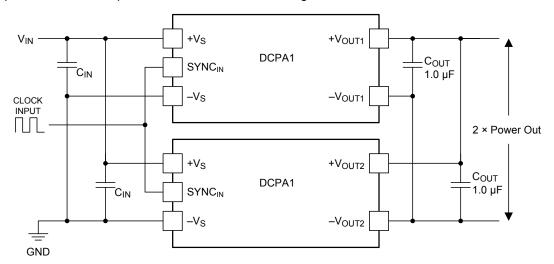

If the output power from one DCPA1 is not sufficient, it is possible to parallel the outputs of multiple DCPA1s, as shown in 🛭 36, (applies to single output devices only). The synchronization feature allows easy synchronization to prevent power-rail beat frequencies at no additional filtering cost.

图 36. Multiple DCPA1 Devices Connected in Parallel

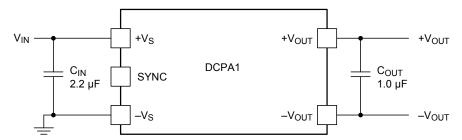

# 8.2 Typical Application

图 37. Typical DCPA10505 Application

### 8.2.1 Design Requirements

For this design example, use the parameters listed in 表 1 and follow the design procedures shown in *Detailed Design Procedure* section.

| 表 1. | Design | Example | Paran | neters |

|------|--------|---------|-------|--------|

|      |        | _       |       |        |

|                      | PARAMETER             | VALUE | UNIT |

|----------------------|-----------------------|-------|------|

| V <sub>(+VS)</sub>   | Input voltage         | 5     | V    |

| V <sub>(+VOUT)</sub> | Output voltage        | 5     | V    |

| I <sub>OUT</sub>     | Output current rating | 200   | mA   |

| f <sub>SW</sub>      | Operating frequency   | 425   | kHz  |

www.ti.com.cn

#### 8.2.2 DCPA10505 Application Curves

#### 8.2.3 Detailed Design Procedure

#### 8.2.3.1 Input Capacitor

For all DCPA1, 5-V input voltage designs, select a 2.2-µF low-ESR ceramic input capacitor to ensure a good startup performance.

#### 8.2.3.2 Output Capacitor

For any DCPA1 design, select a 1.0-μF low-ESR ceramic output capacitor to reduce output ripple.

#### 8.2.3.3 SYNC<sub>IN</sub> Pin

In a stand-alone application, it is recommended to connect this pin to the input side common, -V<sub>S</sub>.

#### 8.2.4 PCB Design

The copper losses (resistance and inductance) can be minimized by the use of mutual ground and power planes where possible. If that is not possible, use wide traces to reduce the losses. If several devices are being powered from a common power source, a star-connected system for the traces must be deployed. Do not connect the devices in series, because that type of connection cascades the resistive losses. The position of the decoupling capacitors is important. They must be as close to the devices as possible in order to reduce losses. See the *PCB Layout* section for more details.

# 9 Power Supply Recommendations

The DCPA1 is a switching power supply, and as such can place high peak current demands on the input supply. In order to avoid the supply falling momentarily during the fast switching pulses, ground and power planes should be used to connect the power to the input of DCPA1 device. If this connection is not possible, then the supplies must be connected in a star formation with the traces made as wide as possible.

# 10 Layout

### 10.1 Layout Guidelines

Due to the high power density of these devices, provide ground planes on the input and output rails.

Including input power and ground planes provides a low-impedance path for the input power. For the output, the COM signal connects via a ground plane, while the connections for the positive and negative voltage outputs conduct via wide traces in order to minimize losses.

The output should be taken from the device using ground and power planes, thereby ensuring minimum losses.

The location of the decoupling capacitors in close proximity to their respective pins ensures low losses due to the effects of stray inductance, thus improving the ripple performance. This location is of particular importance to the input decoupling capacitor, because this capacitor supplies the transient current associated with the fast switching waveforms of the power drive circuits.

If the  $SYNC_{IN}$  pin is unused, it is recommended to connect this pin to the input side common,  $-V_S$ . Allow the  $SW_{OUT}$  pin, to remain configured as a floating pad.

# 10.2 Layout Example

图 40. Typical Layout

## 11 器件和文档支持

**NSTRUMENTS**

### 11.1 器件支持

### 11.1.1 器件命名规则

图 41. 补充订购信息

## 11.2 文档支持

#### 11.2.1 相关文档

直流到直流转换器降噪 (SBVA012)

DCP01/02 系列直流/直流转换器的外部同步 (SBAA035)

优化 DCP01/02 系列直流/直流转换器的性能 (SBVA013)

### 11.3 社区资源

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

### 11.4 相关链接

以下表格列出了快速访问链接。范围包括技术文档、支持与社区资源、工具和软件,并且可以快速访问样片或购买链接。

| 器件         | 产品文件夹 | 样片与购买 | 技术文档  | 工具与软件 | 支持与社区 |

|------------|-------|-------|-------|-------|-------|

| DCPA10505  | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |

| DCPA10505D | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |

| DCPA10512  | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |

| DCPA10512D | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |

| DCPA10515  | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |

| DCPA10515D | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |

表 2. 相关链接

### 11.5 商标

E2E is a trademark of Texas Instruments.

Underwriters Laboratories, UL are trademarks of UL LLC.

All other trademarks are the property of their respective owners.

# TEXAS INSTRUMENTS

# 11.6 静电放电警告

这些装置包含有限的内置 ESD 保护。 存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

# 11.7 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# 12 机械、封装和可订购信息

以下页中包括机械、封装和可订购信息。这些信息是针对指定器件可提供的最新数据。这些数据会在无通知且不对本文档进行修订的情况下发生改变。欲获得该数据表的浏览器版本,请查阅左侧的导航栏。

www.ti.com

10-Nov-2025

### **PACKAGING INFORMATION**

| Orderable part number | Status (1) | Material type | Package   Pins | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|------------|---------------|----------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

| DCPA10505DP           | Active     | Production    | PDIP (NVA)   7 | 25   TUBE             | Yes             | NIPDAU                        | N/A for Pkg Type           | -40 to 100   | DCPA10505DP      |

| DCPA10505DP-U/700     | Active     | Production    | SOP (DUA)   7  | 700   LARGE T&R       | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 100   | DCPA10505DP-U    |

| DCPA10505DP-U/700.A   | Active     | Production    | SOP (DUA)   7  | 700   LARGE T&R       | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 100   | DCPA10505DP-U    |

| DCPA10505DP.A         | Active     | Production    | PDIP (NVA)   7 | 25   TUBE             | Yes             | NIPDAU                        | N/A for Pkg Type           | -40 to 100   | DCPA10505DP      |

| DCPA10505P            | Active     | Production    | PDIP (NVA)   7 | 25   TUBE             | Yes             | NIPDAU                        | N/A for Pkg Type           | -40 to 100   | DCPA10505P       |

| DCPA10505P-U/700      | Active     | Production    | SOP (DUA)   7  | 700   LARGE T&R       | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 100   | DCPA10505P-U     |

| DCPA10505P-U/700.A    | Active     | Production    | SOP (DUA)   7  | 700   LARGE T&R       | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 100   | DCPA10505P-U     |

| DCPA10505P.A          | Active     | Production    | PDIP (NVA)   7 | 25   TUBE             | Yes             | NIPDAU                        | N/A for Pkg Type           | -40 to 100   | DCPA10505P       |

| DCPA10512DP           | Active     | Production    | PDIP (NVA)   7 | 25   TUBE             | Yes             | NIPDAU                        | N/A for Pkg Type           | -40 to 100   | DCPA10512DP      |

| DCPA10512DP-U/700     | Active     | Production    | SOP (DUA)   7  | 700   LARGE T&R       | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 100   | DCPA10512DP-U    |

| DCPA10512DP-U/700.A   | Active     | Production    | SOP (DUA)   7  | 700   LARGE T&R       | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 100   | DCPA10512DP-U    |

| DCPA10512DP.A         | Active     | Production    | PDIP (NVA)   7 | 25   TUBE             | Yes             | NIPDAU                        | N/A for Pkg Type           | -40 to 100   | DCPA10512DP      |

| DCPA10512P            | Active     | Production    | PDIP (NVA)   7 | 25   TUBE             | Yes             | NIPDAU                        | N/A for Pkg Type           | -40 to 100   | DCPA10512P       |

| DCPA10512P-U/700      | Active     | Production    | SOP (DUA)   7  | 700   LARGE T&R       | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 100   | DCPA10512P-U     |

| DCPA10512P-U/700.A    | Active     | Production    | SOP (DUA)   7  | 700   LARGE T&R       | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 100   | DCPA10512P-U     |

| DCPA10512P.A          | Active     | Production    | PDIP (NVA)   7 | 25   TUBE             | Yes             | NIPDAU                        | N/A for Pkg Type           | -40 to 100   | DCPA10512P       |

| DCPA10515DP           | Active     | Production    | PDIP (NVA)   7 | 25   TUBE             | Yes             | NIPDAU                        | N/A for Pkg Type           | -40 to 100   | DCPA10515DP      |

| DCPA10515DP-U/700     | Active     | Production    | SOP (DUA)   7  | 700   LARGE T&R       | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 100   | DCPA10515DP-U    |

| DCPA10515DP-U/700.A   | Active     | Production    | SOP (DUA)   7  | 700   LARGE T&R       | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 100   | DCPA10515DP-U    |

| DCPA10515DP.A         | Active     | Production    | PDIP (NVA)   7 | 25   TUBE             | Yes             | NIPDAU                        | N/A for Pkg Type           | -40 to 100   | DCPA10515DP      |

| DCPA10515P            | Active     | Production    | PDIP (NVA)   7 | 25   TUBE             | Yes             | NIPDAU                        | N/A for Pkg Type           | -40 to 100   | DCPA10515P       |

| DCPA10515P-U/700      | Active     | Production    | SOP (DUA)   7  | 700   LARGE T&R       | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 100   | DCPA10515P-U     |

| DCPA10515P-U/700.A    | Active     | Production    | SOP (DUA)   7  | 700   LARGE T&R       | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 100   | DCPA10515P-U     |

| DCPA10515P.A          | Active     | Production    | PDIP (NVA)   7 | 25   TUBE             | Yes             | NIPDAU                        | N/A for Pkg Type           | -40 to 100   | DCPA10515P       |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 10-Nov-2025

- (3) RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

- (4) Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

- (5) MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

- (6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

NOTES:

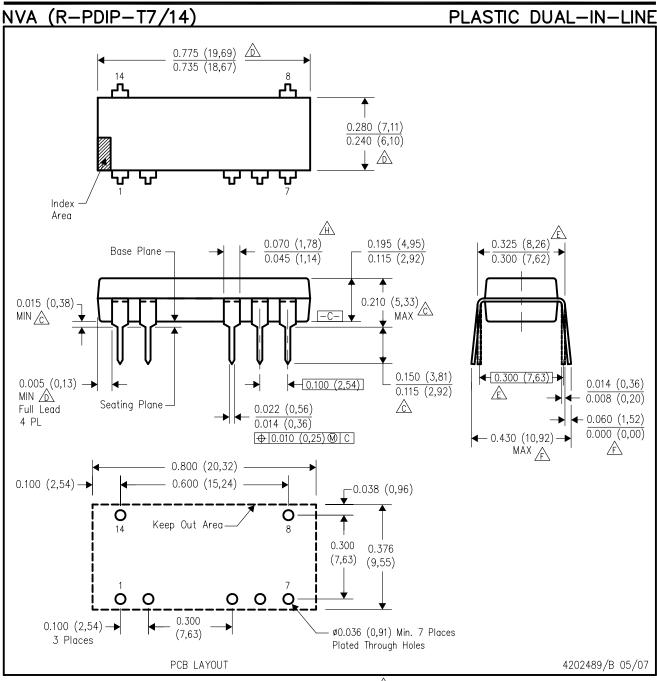

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Dimensions are measured with the package seated in JEDEC seating plane gauge GS-3.

- Dimensions do not include mold flash or protrusions.

Mold flash or protrusions shall not exceed 0.010 (0,25).

- Dimensions measured with the leads constrained to be perpendicular to Datum C.

- Dimensions are measured at the lead tips with the leads unconstrained.

- G. Pointed or rounded lead tips are preferred to ease insertion.

- Lead shoulder maximum dimension does not include dambar protrusions. Dambar protrusions shall not exceed 0.010 (0,25).

- I. Distance between leads including dambar protrusions to be 0.005 (0,13) minimum.

- J. A visual index feature must be located within the cross—hatched area.

- K. For automatic insertion, any raised irregularity on the top surface (step, mesa, etc.) shall be symmetrical about the lateral and longitudinal package centerlines.

- L. Falls within JEDEC MS-001-AA.

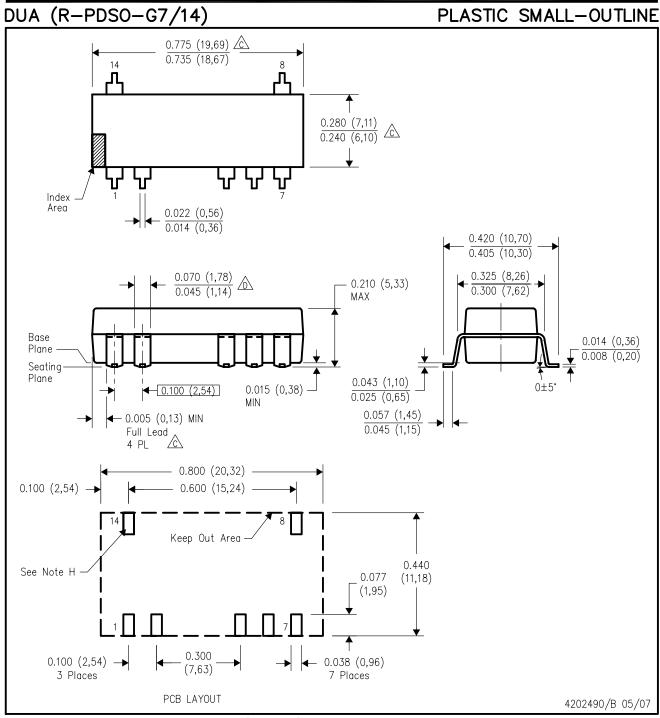

- NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Dimensions do not include mold flash or protrusions.

Mold flash or protrusions shall not exceed 0.010 (0,25).

- Lead shoulder maximum dimension does not include dambar protrusions. Dambar protrusions shall not exceed exceed 0.010 (0,25).

- E. Distance between leads including dambar protrusions to be 0.005 (0,13) minimum.

- F. A visual index feature must be located within the cross—hatched area.

- G. For automatic insertion, any raised irregularity on the top surface (step, mesa, etc.) shall be symmetrical about the lateral and longitudinal package centerlines.

- H. Power pin connections should be two or more vias per input, ground and output pin.

# 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月