CDCUN1208LP

ZHCS887D -MAY 2012-REVISED APRIL 2019

# 具有通用输入和输出的 CDCUN1208LP 400MHz 低功耗 2:8 扇出缓冲器

#### 1 特性

- 支持 PCIe 1/2/3 代

- 配置选项(通过引脚或 SPI/I<sup>2</sup>C):

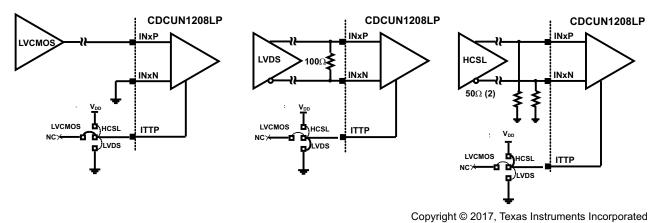

- 输入类型(高速电流驱动能力 (HCSL),低压差分信号 (LVDS),低压 COMS (LVCOMS))

- 输出类型 (HCSL, LVDS, LVCOMS)

- 信号边沿速率(慢、中、快)

- 时钟输入分配值 (/1, /2, /4, /8) 只适用于 IN2

- 低功耗与电源管理 特性,包括 1.8V 运行和输出使 能控制

- 具有集成稳压器,可改进 PSNR

- 卓越的附加抖动性能

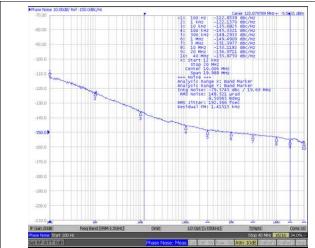

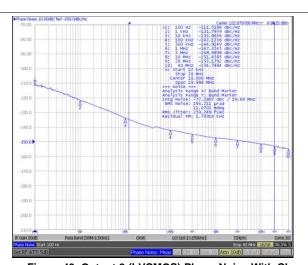

- LVDS 在 100MHz 时具有 200 fs RMS(10kHz 至 20MHz)

- HCSL 在 100MHz 时具有 160 fs RMS (10kHz 至 20MHz)

- 最大工作频率:

- 差分模式: 高达 400MHz

- LVCOMS 模式: 高达 250MHz

- ESD 保护超过 2kV HBM、500V CDM

- 工业温度范围 (-40°C 至 85°C)

- 宽电源范围(1.8V、2.5V或者 3.3V)

#### 2 应用

- 通信和计算系统

- 工厂自动化和控制

- 医疗成像

- 专业音频、视频和标牌

- 电机驱动器

## 3 说明

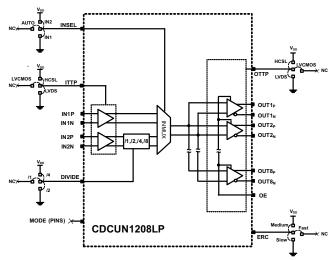

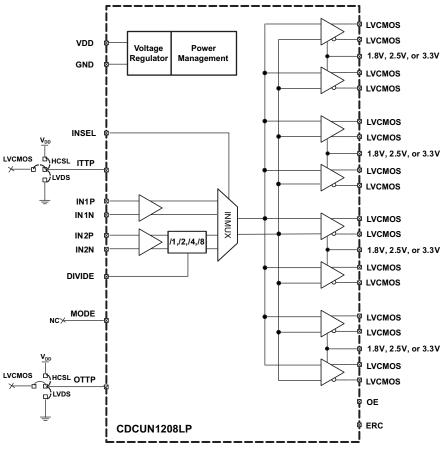

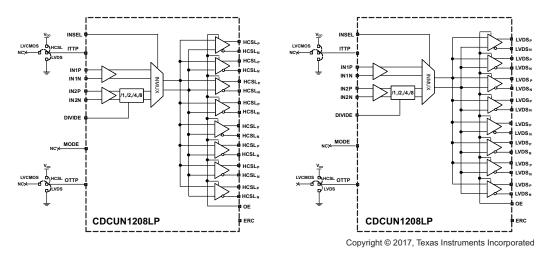

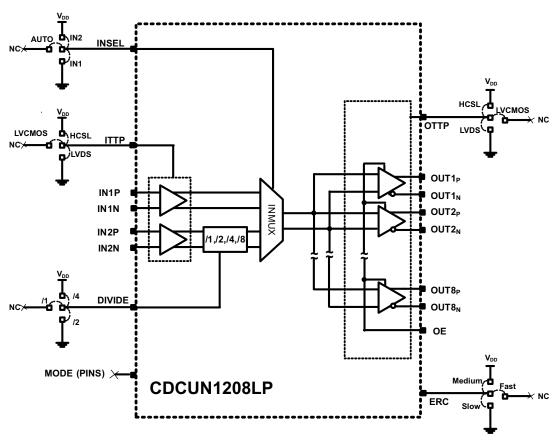

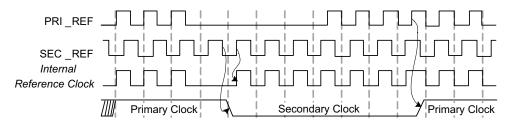

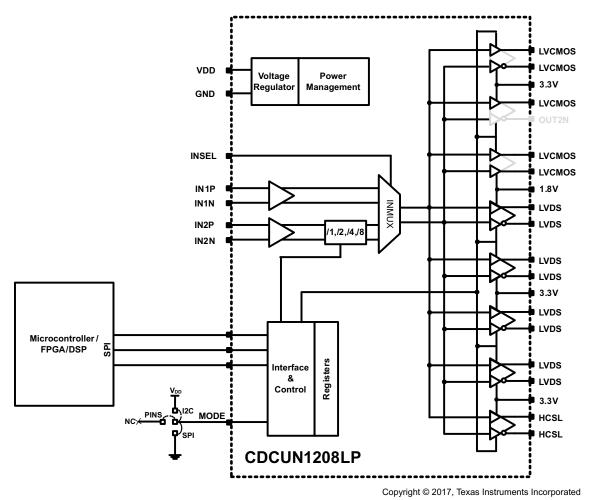

CDCUN1208LP 是一款 2:8 扇出缓冲器,具有宽工作电源电压范围、两个通用差分/单端输入以及具有边沿速率控制的通用输出(HCSL、LVDS 或

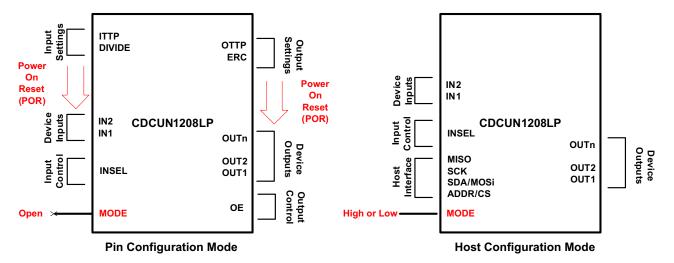

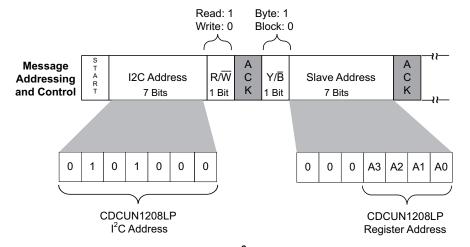

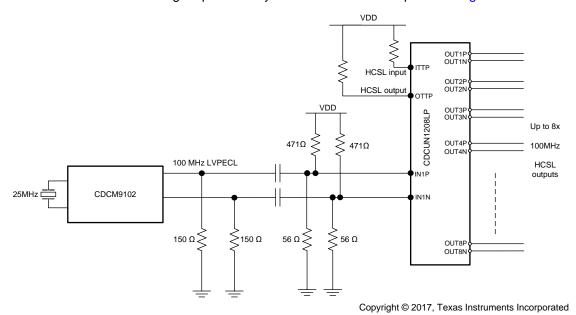

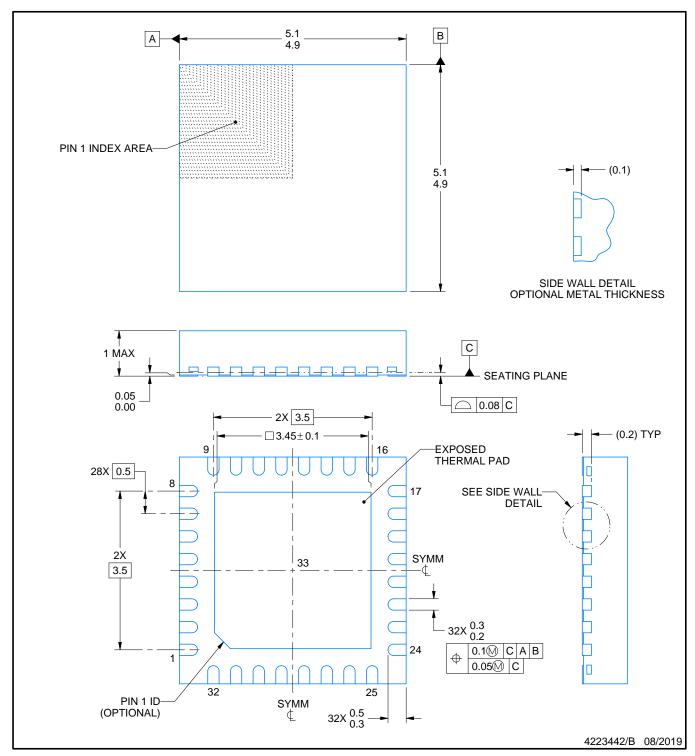

LVCMOS)。时钟缓冲器支持 PCIe 1/2/3 代。其中一个器件输入包括可提供 /1、/2、/4 或 /8 分频值的分频器。CDCUN1208LP 采用 32 引脚 QFN 封装,从而减小了解决方案的尺寸。此器件非常灵活并易于使用。某些特定引脚的状态决定了器件在加电时的配置。或者,CDCUN1208P 提供一个 SPI/I<sup>2</sup>C 端口,在此端口上有一个主机处理器来控制器件的设置。

CDCUN1208P 提供出色的附加抖动性能且功耗很低。输出部分包括四个专用电源引脚,这些引脚能够启用来自不同电源域的输出端口。这一功能使得时钟器件能够在不同的 LVCOMS 电平上切换,而无需外部逻辑电平转换电路。

#### 器件信息(1)

| 器件型号        | 封装        | 封装尺寸 (标称值)      |

|-------------|-----------|-----------------|

| CDCUN1208LP | VQFN (32) | 5.00mm x 5.00mm |

(1) 如需了解所有可用封装,请参阅产品说明书末尾的可订购产品 附录

#### 引脚配置概述

Copyright © 2017, Texas Instruments Incorporate

#### 目录

| 1 | 特性1                                                             | 8  | Detailed Description                     | 22 |

|---|-----------------------------------------------------------------|----|------------------------------------------|----|

| 2 | 应用 1                                                            |    | 8.1 Overview                             | 22 |

| 3 | 说明 1                                                            |    | 8.2 Functional Block Diagrams            | 22 |

| 4 | 修订历史记录 2                                                        |    | 8.3 Feature Description                  | 23 |

| 5 | Pin Configuration and Functions4                                |    | 8.4 Device Functional Modes              | 28 |

| 6 | Specifications6                                                 |    | 8.5 Programming                          |    |

| • | 6.1 Absolute Maximum Ratings 6                                  |    | 8.6 Register Maps                        | 37 |

|   | 6.2 ESD Ratings                                                 | 9  | Application and Implementation           | 39 |

|   | 6.3 Recommended Operating Conditions                            |    | 9.1 Application Information              | 39 |

|   | 6.4 Thermal Information                                         |    | 9.2 Typical Application                  | 39 |

|   | 6.5 Digital Input Electrical Characteristics – OE (SCL),        |    | 9.3 Systems Examples                     | 41 |

|   | INSEL, ITTP, OTTP, Divide (SDA/MOSI),                           | 10 | Power Supply Recommendations             | 42 |

|   | ERC(ADDR/CS), Mode7                                             |    | 10.1 CDCUN1208LP Power Consumption       | 42 |

|   | 6.6 Universal Input (IN1, IN2) Characteristics 8                |    | 10.2 Device Power Supply Connections and |    |

|   | 6.7 Clock Output Buffer Characteristics (Output Mode =          |    | Sequencing                               |    |

|   | LVDS)                                                           |    | 10.3 Device Inputs (IN1, IN2)            |    |

|   | 6.8 Clock Output Buffer Characteristics (Output Mode = HCSL) 10 | 11 | Layout                                   |    |

|   | 6.9 Clock Output Buffer Electrical Characteristics (Output      |    | 11.1 Layout Guidelines                   |    |

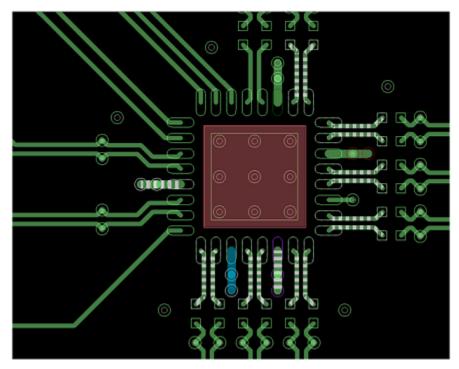

|   | Mode = LVCMOS)                                                  |    | 11.2 Layout Example                      |    |

|   | 6.10 Clock Output Buffer Electrical Characteristics             | 12 | 器件和文档支持                                  |    |

|   | (Output Mode = LVCMOS) (Continued) 12                           |    | 12.1 接收文档更新通知                            |    |

|   | 6.11 Clock Output Buffer Electrical Characteristics             |    | 12.2 社区资源                                |    |

|   | (Output Mode = LVCMOS) (Continued)                              |    | 12.3 商标                                  |    |

| _ | 6.12 Typical Characteristics                                    |    | 12.4 静电放电警告                              |    |

| 7 | Parameter Measurement Information                               |    | 12.5 术语表                                 |    |

|   | 7.1 Test Configurations                                         | 13 | 机械、封装和可订购信息                              | 45 |

|   |                                                                 |    |                                          |    |

#### 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

## Changes from Revision C (March 2017) to Revision D Page Added type descriptions to the Pin Functions table \_\_\_\_\_\_\_4 Changed the output current unit from mA °C to mA and moved the °C unit to the storage temperature parameter in Changed description to reflect that the I<sup>2</sup>C address is 7b'0101000 in CDCUN1208LP Device Addressing (FC

| <ul> <li>Added slew rate note to Recommended Operating Conditions.</li> <li>Changed V<sub>IOPEN1.8</sub> from 0.9 V to 0.75 V in <i>Digital Input Electrical Characteristics – OE (SCL), INSEL, ITTP, OTTP, DIVIDE (SDA/MOSI), ERC(ADDR/CS), Mode.</i></li> <li>Changed Fast to Medium and Medium to Fast in <i>Figure 28</i>.</li> <li>Changes from Original (May 2012) to Revision A</li> <li>Pa</li> <li>添加了特性: 100MHz 下实现 160fs RMS (10kHz-20MHz)、HCSL。</li> <li>添加了特性: 支持 PCIE 1/2/3 代。</li> <li>向 说明部分添加了"此时钟缓冲器支持 PCIE 1/2/3 代"。</li> <li>Added text to the Clock Output Buffer Characteristics table: "Supporting PCIe gen1, gen2, gen3."</li> <li>Changed Table 4 From: DISABLED To: DISABLED in Tri_State</li> <li>Changed Table 11 From: Disabled To: Disabled in Tri_State for OUTx_PD.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Changes from Revision B (July 2013) to Revision C                                                          | Page |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|

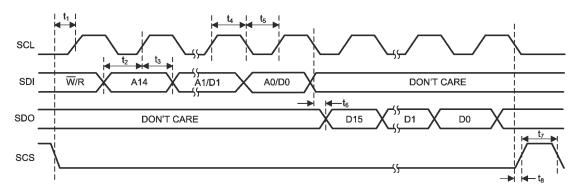

| <ul> <li>Added text "note that CDCUN1208LP supports only single-device" to the first paragraph of SPI Communication.</li> <li>Added text "At no time should the clock be toggled while SCS is high. CDCUN1208LP should always be used in single-slave SPI configuration." to Writing to the CDCUN1208LP.</li> <li>Added text "At no time should the clock be toggled while SCS is high. CDCUN1208LP should always be used in single-slave SPI configuration." to Reading From the CDCUN1208LP.</li> <li>Changes from Revision A (January 2013) to Revision B</li> <li>Added slew rate note to Recommended Operating Conditions.</li> <li>Changed V<sub>IOPEN1.8</sub> from 0.9 V to 0.75 V in Digital Input Electrical Characteristics – OE (SCL), INSEL, ITTP, OTTP, DIVIDE (SDA/MOSI), ERC(ADDR/CS), Mode.</li> <li>Changed Fast to Medium and Medium to Fast in Figure 28.</li> <li>Changes from Original (May 2012) to Revision A</li> <li>Pamp The the tomation of the Clock Output Buffer Characteristics table: "Supporting PCle gen1, gen2, gen3."</li> <li>Added text to the Clock Output Buffer Characteristics table: "Supporting PCle gen1, gen2, gen3."</li> <li>Changed Table 4 From: DISABLED To: DISABLED in Tri_State</li> <li>Changed Table 11 From: Disabled To: Disabled in Tri_State for OUTx_PD.</li> </ul> |                                                                                                            | 1    |

| <ul> <li>Added text "At no time should the clock be toggled while SCS is high. CDCUN1208LP should always be used in single-slave SPI configuration." to Writing to the CDCUN1208LP.</li> <li>Added text "At no time should the clock be toggled while SCS is high. CDCUN1208LP should always be used in single-slave SPI configuration." to Reading From the CDCUN1208LP.</li> <li>Changes from Revision A (January 2013) to Revision B</li> <li>Added slew rate note to Recommended Operating Conditions.</li> <li>Changed V<sub>IOPEN1.8</sub> from 0.9 V to 0.75 V in Digital Input Electrical Characteristics — OE (SCL), INSEL, ITTP, OTTP, DIVIDE (SDAMOSI), ERC(ADDR/CS), Mode.</li> <li>Changed Fast to Medium and Medium to Fast in Figure 28.</li> <li>Changes from Original (May 2012) to Revision A</li> <li>添加了特性: 支持 PCIE 1/2/3 代。</li> <li>前 说明部分添加了"此时钟缓冲器支持 PCIE 1/2/3 代"。</li> <li>Added text to the Clock Output Buffer Characteristics table: "Supporting PCIe gen1, gen2, gen3."</li> <li>Changed Table 4 From: DISABLED To: DISABLED in Tri_State</li> <li>Changed Table 11 From: Disabled To: Disabled in Tri_State for OUTx_PD.</li> </ul>                                                                                                                                                                | Added ΔV/ΔT² to the Recommended Operating Conditions table.                                                | 6    |

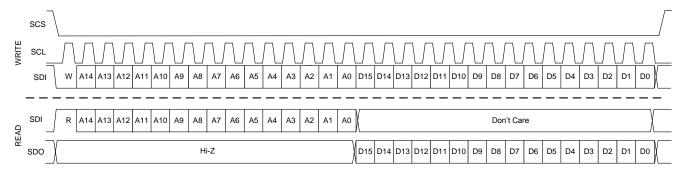

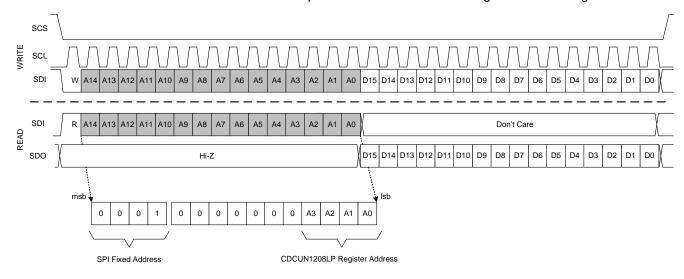

| single-slave SPI configuration." to Writing to the CDCUN1208LP.  Added text "At no time should the clock be toggled while SCS is high. CDCUN1208LP should always be used in single-slave SPI configuration." to Reading From the CDCUN1208LP.  Changes from Revision A (January 2013) to Revision B  Added slew rate note to Recommended Operating Conditions.  Changed V <sub>IOPEN1.8</sub> from 0.9 V to 0.75 V in Digital Input Electrical Characteristics — OE (SCL), INSEL, ITTP, OTTP, DIVIDE (SDA/MOSI), ERC(ADDR/CS), Mode.  Changed Fast to Medium and Medium to Fast in Figure 28.  Changes from Original (May 2012) to Revision A  Pa  添加了特性: 100MHz 下实现 160fs RMS (10kHz-20MHz)、HCSL。  添加了特性: 支持 PCIE 1/2/3 代。  向 说明部分添加了"此时钟缓冲器支持 PCIE 1/2/3 代"。  Added text to the Clock Output Buffer Characteristics table: "Supporting PCIe gen1, gen2, gen3."                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Added text "note that CDCUN1208LP supports only single-device" to the first paragraph of SPI Communication | 30   |

| Changes from Revision A (January 2013) to Revision B  Added slew rate note to Recommended Operating Conditions.  Changed V <sub>IOPEN1.8</sub> from 0.9 V to 0.75 V in <i>Digital Input Electrical Characteristics — OE (SCL), INSEL, ITTP, OTTP, DIVIDE (SDA/MOSI), ERC(ADDR/CS), Mode.</i> Changed Fast to Medium and Medium to Fast in <i>Figure 28</i> .  Changes from Original (May 2012) to Revision A  Amalon Revision A  Particular State (100MHz 下实现 160fs RMS (10kHz-20MHz)、HCSL。  添加了特性: 支持 PCIE 1/2/3 代。  向说明部分添加了"此时钟缓冲器支持 PCIE 1/2/3 代"。  Added text to the Clock Output Buffer Characteristics table: "Supporting PCIe gen1, gen2, gen3."  Changed Table 11 From: Disabled To: Disabled in Tri_State  Changed Table 11 From: Disabled To: Disabled in Tri_State for OUTx_PD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                            | 31   |

| <ul> <li>Added slew rate note to Recommended Operating Conditions.</li> <li>Changed V<sub>IOPEN1.8</sub> from 0.9 V to 0.75 V in <i>Digital Input Electrical Characteristics – OE (SCL), INSEL, ITTP, OTTP, DIVIDE (SDA/MOSI), ERC(ADDR/CS), Mode.</i></li> <li>Changed Fast to Medium and Medium to Fast in <i>Figure 28</i>.</li> <li>Changes from Original (May 2012) to Revision A</li> <li>Pa</li> <li>添加了特性: 100MHz 下实现 160fs RMS (10kHz-20MHz)、HCSL。</li> <li>添加了特性: 支持 PCIE 1/2/3 代。</li> <li>向 说明部分添加了"此时钟缓冲器支持 PCIE 1/2/3 代"。</li> <li>Added text to the Clock Output Buffer Characteristics table: "Supporting PCIe gen1, gen2, gen3."</li> <li>Changed Table 4 From: DISABLED To: DISABLED in Tri_State</li> <li>Changed Table 11 From: Disabled To: Disabled in Tri_State for OUTx_PD.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                            | 31   |

| <ul> <li>Changed V<sub>IOPEN1.8</sub> from 0.9 V to 0.75 V in Digital Input Electrical Characteristics – OE (SCL), INSEL, ITTP, OTTP, DIVIDE (SDA/MOSI), ERC(ADDR/CS), Mode.</li> <li>Changed Fast to Medium and Medium to Fast in Figure 28.</li> <li>Changes from Original (May 2012) to Revision A</li> <li>添加了特性: 100MHz 下实现 160fs RMS (10kHz-20MHz)、HCSL。</li> <li>添加了特性: 支持 PCIE 1/2/3 代。</li> <li>向 说明部分添加了"此时钟缓冲器支持 PCIE 1/2/3 代"。</li> <li>Added text to the Clock Output Buffer Characteristics table: "Supporting PCIe gen1, gen2, gen3."</li> <li>Changed Table 4 From: DISABLED To: DISABLED in Tri_State</li> <li>Changed Table 11 From: Disabled To: Disabled in Tri_State for OUTx_PD.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Changes from Revision A (January 2013) to Revision B                                                       | Page |

| DIVIDE (SDA/MOSI), ERC(ADDR/CS), Mode.  Changed Fast to Medium and Medium to Fast in Figure 28.  Changes from Original (May 2012) to Revision A  Famury 特性: 100MHz 下实现 160fs RMS (10kHz-20MHz)、HCSL。  添加了特性: 支持 PCIE 1/2/3 代。  问说明部分添加了"此时钟缓冲器支持 PCIE 1/2/3 代"。  Added text to the Clock Output Buffer Characteristics table: "Supporting PCIe gen1, gen2, gen3."  Changed Table 4 From: DISABLED To: DISABLED in Tri_State  Changed Table 11 From: Disabled To: Disabled in Tri_State for OUTx_PD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Added slew rate note to Recommended Operating Conditions.                                                  | 6    |

| Changes from Original (May 2012) to Revision A  • 添加了特性: 100MHz 下实现 160fs RMS (10kHz-20MHz)、HCSL。  • 添加了特性: 支持 PCIE 1/2/3 代。  • 向 说明部分添加了"此时钟缓冲器支持 PCIE 1/2/3 代"。  • Added text to the Clock Output Buffer Characteristics table: "Supporting PCIe gen1, gen2, gen3."  • Changed Table 4 From: DISABLED To: DISABLED in Tri_State  • Changed Table 11 From: Disabled To: Disabled in Tri_State for OUTx_PD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                            | 7    |

| <ul> <li>添加了特性: 100MHz 下实现 160fs RMS (10kHz-20MHz)、HCSL。</li> <li>添加了特性: 支持 PCIE 1/2/3 代。</li> <li>向 说明部分添加了"此时钟缓冲器支持 PCIE 1/2/3 代"。</li> <li>Added text to the Clock Output Buffer Characteristics table: "Supporting PCIe gen1, gen2, gen3."</li> <li>Changed Table 4 From: DISABLED To: DISABLED in Tri_State</li> <li>Changed Table 11 From: Disabled To: Disabled in Tri_State for OUTx_PD.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Changed Fast to Medium and Medium to Fast in Figure 28.                                                    | 24   |

| <ul> <li>添加了特性: 支持 PCIE 1/2/3 代。</li> <li>向 说明部分添加了"此时钟缓冲器支持 PCIE 1/2/3 代"。</li> <li>Added text to the Clock Output Buffer Characteristics table: "Supporting PCIe gen1, gen2, gen3."</li> <li>Changed Table 4 From: DISABLED To: DISABLED in Tri_State</li> <li>Changed Table 11 From: Disabled To: Disabled in Tri_State for OUTx_PD.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Changes from Original (May 2012) to Revision A                                                             | Page |

| <ul> <li>向 说明部分添加了"此时钟缓冲器支持 PCIE 1/2/3 代"。</li> <li>Added text to the Clock Output Buffer Characteristics table: "Supporting PCIe gen1, gen2, gen3."</li> <li>Changed Table 4 From: DISABLED To: DISABLED in Tri_State</li> <li>Changed Table 11 From: Disabled To: Disabled in Tri_State for OUTx_PD.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 添加了特性: 100MHz 下实现 160fs RMS (10kHz-20MHz)、HCSL。                                                            | 1    |

| <ul> <li>Added text to the Clock Output Buffer Characteristics table: "Supporting PCle gen1, gen2, gen3."</li> <li>Changed Table 4 From: DISABLED To: DISABLED in Tri_State</li> <li>Changed Table 11 From: Disabled To: Disabled in Tri_State for OUTx_PD.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 添加了特性: 支持 PCIE 1/2/3 代。                                                                                    | 1    |

| <ul> <li>Changed Table 4 From: DISABLED To: DISABLED in Tri_State</li> <li>Changed Table 11 From: Disabled To: Disabled in Tri_State for OUTx_PD.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 向 说明部分添加了"此时钟缓冲器支持 PCIE 1/2/3 代"。                                                                          | 1    |

| Changed Table 11 From: Disabled To: Disabled in Tri_State for OUTx_PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Added text to the Clock Output Buffer Characteristics table: "Supporting PCIe gen1, gen2, gen3."           | 10   |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Changed Table 4 From: DISABLED To: DISABLED in Tri_State                                                   | 25   |

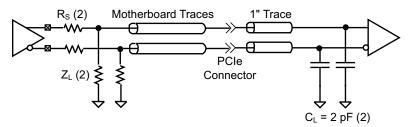

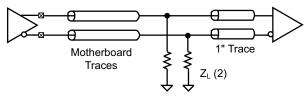

| Added text and Figure 41 to the PCI Express Applications section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Changed Table 11 From: Disabled To: Disabled in Tri_State for OUTx_PD.                                     | 37   |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Added text and Figure 41 to the PCI Express Applications section.                                          | 39   |

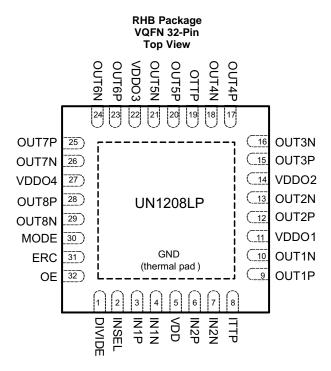

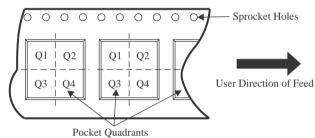

## 5 Pin Configuration and Functions

Pin Functions<sup>(1)</sup>

| Р      | IN                                                                                      | TYPE   | DESCRIPTION                                                                                                                                                                                                    |

|--------|-----------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO.                                                                                     | ITFE   | DESCRIPTION                                                                                                                                                                                                    |

| GND    | Thermal<br>Pad                                                                          | Power  | Power supply ground and thermal relief                                                                                                                                                                         |

| DIVIDE | 1                                                                                       | Input  | Input divider pin control (HIGH = /4, LOW = /2, OPEN = /1)                                                                                                                                                     |

| INSEL  | 2 Input Input multiplexer control                                                       |        |                                                                                                                                                                                                                |

| IN1P   | 3                                                                                       | Input  | Universal input 1 – positive terminal                                                                                                                                                                          |

| IN1N   | 4 Input Universal input 1 – negative terminal, ground if using IN1 in single-ended mode |        | Universal input 1 – negative terminal, ground if using IN1 in single-ended mode                                                                                                                                |

| VDD    |                                                                                         |        | Device power supply; provides power to the input section and clock distribution section. Use a power supply voltage that corresponds to the switching levels of clock inputs (such as 1.8 V, 2.5 V, or 3.3 V). |

| IN2P   | 6                                                                                       | Input  | Universal input 2 – positive terminal                                                                                                                                                                          |

| IN2N   | 7                                                                                       | Input  | Universal input 2 – negative terminal, ground if using IN2 in single-ended mode                                                                                                                                |

| ITTP   | 8                                                                                       | Input  | Input type select (HIGH = HCSL, LOW = LVDS, OPEN = LVCMOS)                                                                                                                                                     |

| OUT1P  | 9                                                                                       | Output | Output 1 – positive terminal                                                                                                                                                                                   |

| OUT1N  | 10                                                                                      | Output | Output 1 – negative terminal                                                                                                                                                                                   |

| VDDO1  | 11                                                                                      | Power  | Output power supply – OUT1, OUT2                                                                                                                                                                               |

| OUT2P  | 12                                                                                      | Output | Output 2 – positive terminal                                                                                                                                                                                   |

| OUT2N  | 13                                                                                      | Output | Output 2 – negative terminal                                                                                                                                                                                   |

| VDDO2  | 14                                                                                      | Power  | Output power supply – OUT3, OUT4; output bank OUT1 – OUT4 regulator power supply (apply power if any of OUT1 – OUT4 are needed)                                                                                |

| OUT3P  | 15                                                                                      | Output | Output 3 – positive terminal                                                                                                                                                                                   |

| OUT3N  | 16                                                                                      | Output | Output 3 – negative terminal                                                                                                                                                                                   |

| OUT4P  | 17                                                                                      | Output | Output 4 – positive terminal                                                                                                                                                                                   |

| OUT4N  | 18                                                                                      | Output | Output 4 – negative terminal                                                                                                                                                                                   |

<sup>(1)</sup> This pin list applies to operation of the device in pin mode. In host mode, certain pins take on an alternate function, as outlined in Table 8.

## Pin Functions<sup>(1)</sup> (continued)

| PIN NAME NO.                                                                 |                 | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                       |  |

|------------------------------------------------------------------------------|-----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                              |                 | ITPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                       |  |

| OTTP                                                                         | 19              | Output | Output type select (HIGH = HCSL, LOW = LVDS, OPEN = LVCMOS)                                                                                                                                                                                                                                                       |  |

| OUT5P                                                                        | 20              | Output | Output 5 – positive terminal                                                                                                                                                                                                                                                                                      |  |

| OUT5N                                                                        | 21              | Output | Output 5 – negative terminal                                                                                                                                                                                                                                                                                      |  |

| VDDO3                                                                        | 22              | Power  | Output power supply - OUT5, OUT6                                                                                                                                                                                                                                                                                  |  |

| OUT6P                                                                        | OUT6P 23 Output |        | Output 6 – positive terminal                                                                                                                                                                                                                                                                                      |  |

| OUT6N                                                                        | OUT6N 24 Output |        | Output 6 – negative terminal                                                                                                                                                                                                                                                                                      |  |

| OUT7P                                                                        | OUT7P 25 Output |        | Output 7 – positive terminal                                                                                                                                                                                                                                                                                      |  |

| OUT7N 26 Output                                                              |                 | Output | Output 7 – negative terminal                                                                                                                                                                                                                                                                                      |  |

| VDDO4 27 Power                                                               |                 | Power  | Output power supply – OUT7, OUT8 output bank OUT5 – OUT8 regulator power supply (apply power if any of OUT5 – OUT8 are needed)                                                                                                                                                                                    |  |

| OUT8P                                                                        | 28              | Output | Output 8 – positive terminal                                                                                                                                                                                                                                                                                      |  |

| OUT8N                                                                        | 29              | Output | Output 8 – negative terminal                                                                                                                                                                                                                                                                                      |  |

| MODE                                                                         | 30              | Input  | Device control mode select  OPEN = Device configured through pins (pin mode)  HIGH = Device configured through I <sup>2</sup> C  LOW = Device configured through SPI  Note: For information on control through the serial interface (I <sup>2</sup> C/ SPI), see Device Control Using the Host Interface section. |  |

| ERC 31 Input Output edge rate control HIGH = Medium, LOW = Slow, OPEN = Fast |                 | Input  | 1 0                                                                                                                                                                                                                                                                                                               |  |

| OE                                                                           | 32              | Input  | Device output enable HIGH = Enable, LOW = Disable                                                                                                                                                                                                                                                                 |  |

## 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                  |                               | MIN  | MAX                   | UNIT |

|------------------|-------------------------------|------|-----------------------|------|

| $V_{DDxx}$       | Supply voltage <sup>(2)</sup> | -0.5 | 4.6                   | V    |

| V <sub>IN</sub>  | Input voltage (3)             | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| V <sub>OUT</sub> | Output voltage <sup>(3)</sup> | -0.5 | $V_{DDOx} + 0.5$      | V    |

| I <sub>IN</sub>  | Input current                 | 20   |                       | mA   |

| I <sub>OUT</sub> | Output current                | 50   |                       | mA   |

| $T_J$            | Junction temperature          |      | 125                   | °C   |

| T <sub>stg</sub> | Storage temperature           | -65  | 150                   | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

2) All supply voltages must be supplied simultaneously

#### 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

$T_A = -40$ °C TO 85°C

|                                     |                             |                                             | MIN   | NOM | MAX   | UNIT |  |  |

|-------------------------------------|-----------------------------|---------------------------------------------|-------|-----|-------|------|--|--|

| POWER SUPPLIES <sup>(1)(2)(3)</sup> |                             |                                             |       |     |       |      |  |  |

| $V_{DD}$                            | DC power supply - core      | 1.8-V mode                                  | 1.7   | 1.8 | 1.9   | V    |  |  |

| $V_{DDOx}$                          | DC power supply - output    | 1.8-V mode                                  | 1.7   | 1.8 | 1.9   | V    |  |  |

| $V_{DD}$                            | DC power supply - core      | 2.5-V mode                                  | 2.375 | 2.5 | 2.625 | V    |  |  |

| $V_{DDOx}$                          | DC power supply - output    | 2.5-V mode                                  | 2.375 | 2.5 | 2.625 | V    |  |  |

| $V_{DD}$                            | DC power supply - core      | 3.3-V mode                                  | 2.97  | 3.3 | 3.63  | V    |  |  |

| $V_{DDOx}$                          | DC power supply - output    | 3.3-V mode                                  | 2.97  | 3.3 | 3.63  | V    |  |  |

| $\Delta V/\Delta T^2$               | Core power supply slew rate | 0.4-V to 1.8-V × 0.8 (in all voltage modes) | 6500  |     |       | V/s  |  |  |

| TEMPER                              | ATURE                       |                                             |       |     |       |      |  |  |

| $T_A$                               | Free- air temperature       |                                             | -40   |     | 85    | °C   |  |  |

<sup>(1)</sup> For proper device operation, the core power supply voltage (pin 5) must be applied either before the application of any output power supply, or simultaneously with the application of the output power supplies. The application of an output power supply prior to the application of the core power supply could result in improper device behavior.

<sup>(3)</sup> The input and output negative voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> A minimum V<sub>DD</sub> slew rate of 6500 V/s should be obtained to ensure proper device functionality in pin mode. If the ambient temperature of the device is > 0°C, the slew rate can be as slow as 5000 V/s. In host mode (I<sup>2</sup>C/SPI), the V<sub>DD</sub> slew rate is not limited, if the Reset bit gets toggled after V<sub>DD</sub> ramp.

<sup>(3)</sup> V<sub>DD</sub> and V<sub>DDOx</sub> can be operated from different supply voltages. Refer to Configuration of Output Type (OTTP) for more details.

#### 6.4 Thermal Information

|                        |                                              | CDCUN1208LP |      |

|------------------------|----------------------------------------------|-------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RHB Package | UNIT |

|                        |                                              | 32 PINS     |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 32.5        | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 24.2        | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 6.6         | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.3         | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 6.6         | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 1.6         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report.

## 6.5 Digital Input Electrical Characteristics – OE (SCL), INSEL, ITTP, OTTP, Divide (SDA/MOSI), ERC(ADDR/CS), Mode

$T_{\Lambda} = -40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$

| 1 <sub>A</sub> = -40 C t0 65 C  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |  |  |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|

| PARAMETER                       | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TYP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | UNIT                                                  |  |  |  |

| NPUT                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |  |  |  |

| Low-level LVCMOS input voltage  | V <sub>DD</sub> = 1.8 V                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V                                                     |  |  |  |

| High-level LVCMOS input voltage | V <sub>DD</sub> = 1.8 V                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V                                                     |  |  |  |

| OPEN-level LVCMOS input voltage | V <sub>DD</sub> = 1.8 V                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V                                                     |  |  |  |

| Low-level LVCMOS input voltage  | $V_{DD} = 2.5 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V                                                     |  |  |  |

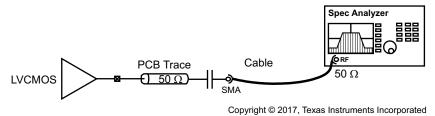

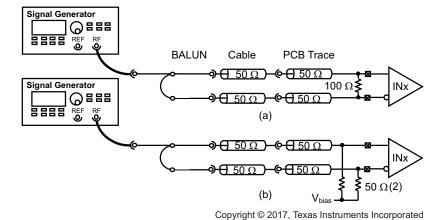

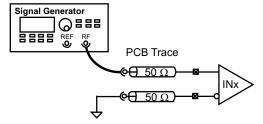

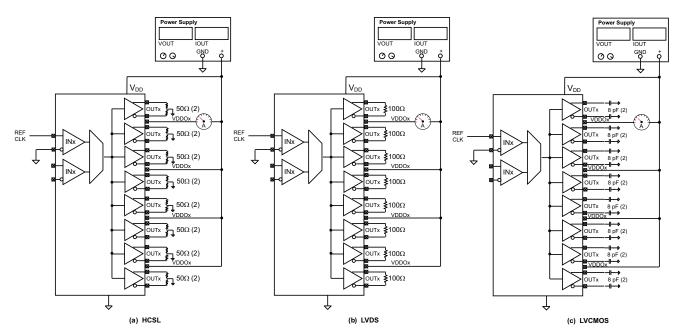

| High-level LVCMOS input voltage | V <sub>DD</sub> = 2.5 V                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V                                                     |  |  |  |