BQ77904, BQ77905 SLUSCM3K - JUNE 2016 - REVISED JULY 2020

# BQ77904, BQ77905 3-Series to 20-Series Ultra Low-Power Voltage, Current, Temperature, and Open-Wire Stackable Lithium-Ion Battery Protector

#### 1 Features

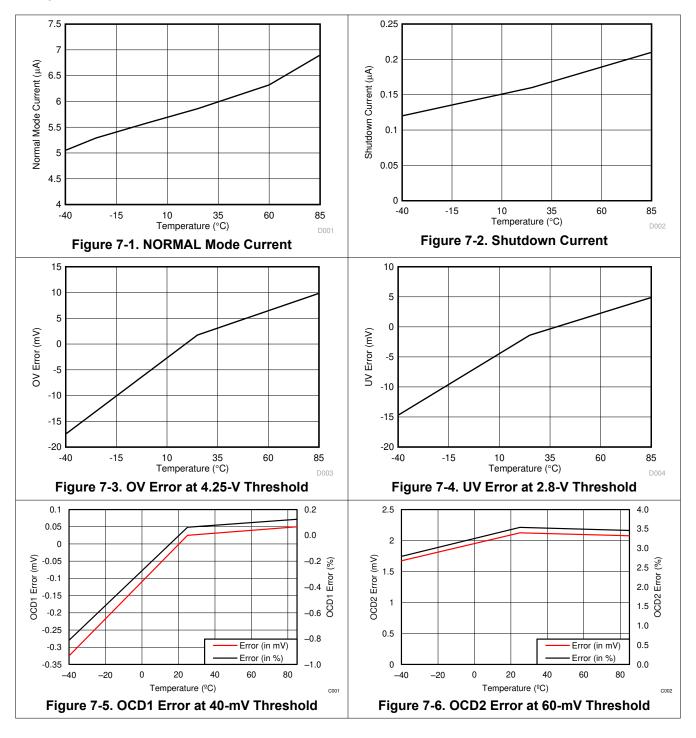

- NORMAL mode: 6 µA (BQ77904 and BQ77905)

- Full suite of voltage, current, and temperature protections

- Scalable cell count from 3 series to 20 series or

- Voltage protection (accuracy ±10 mV)

- Overvoltage: 3 V to 4.575 V

- Undervoltage: 1.2 V to 3 V

- Open cell and open-wire detection (OW)

- **Current Protection**

- Overcurrent discharge 1: –10 mV to –85 mV

- Overcurrent discharge 2: –20 mV to +170 mV

- Short circuit discharge: –40 mV to +340 mV

- Accuracy ±20% for ≤ 20 mV, ±30% for > 20 mV across full temperature

- Temperature protection

- Overtemperature charge: 45°C or 50°C

- Overtemperature discharge: 65°C or 70°C

- Undertemperature charge: –5°C or 0°C

- Undertemperature discharge: –20°C or –10°C

- Additional Features

- Independent charge (CHG) and discharge (DSG) FET drivers

- 36-V absolute maximum rating per cell input

- Built-in-self-test functions for high reliability

- SHUTDOWN mode: 0.5-µA maximum

- Functional Safety-Capable

- Documentation available to aid functional safety system design

# 2 Applications

- Power tools, garden tools

- Start-stop battery packs

- Lead-acid (PbA) replacement batteries

- Light electric vehicles

- Energy storage systems, uninterruptible power supplies (UPS)

- 10.8-V to 72-V packs

# 3 Description

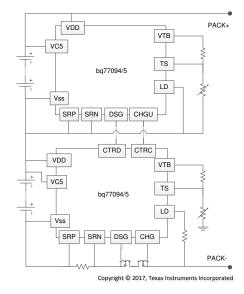

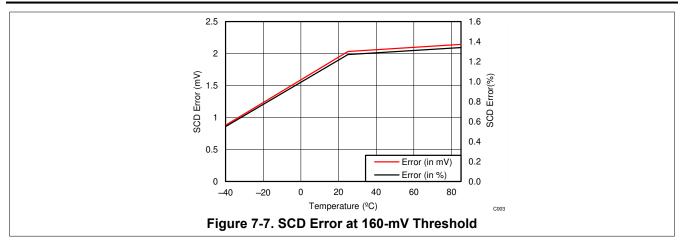

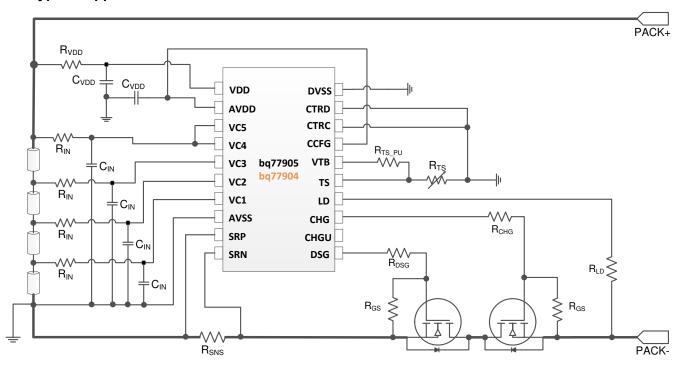

The BQ77904 and BQ77905 devices are low-power battery pack protectors that implement a suite of voltage, current, and temperature protections without microcontroller (MCU) control. The device's stackable interface provides simple scaling to support battery cell applications from 3 series to 20 series or more. Protection thresholds and delays are factory-programmed and available in a variety

of configurations. Separate overtemperature and undertemperature thresholds for discharge (OTD and UTD) and charge (OTC and UTC) are provided for added flexibility.

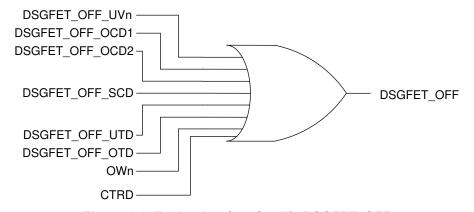

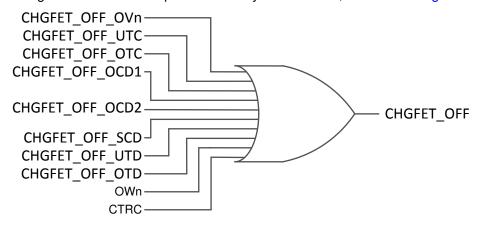

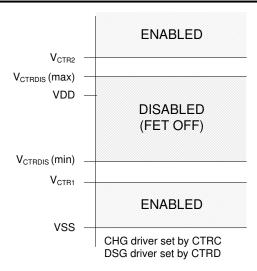

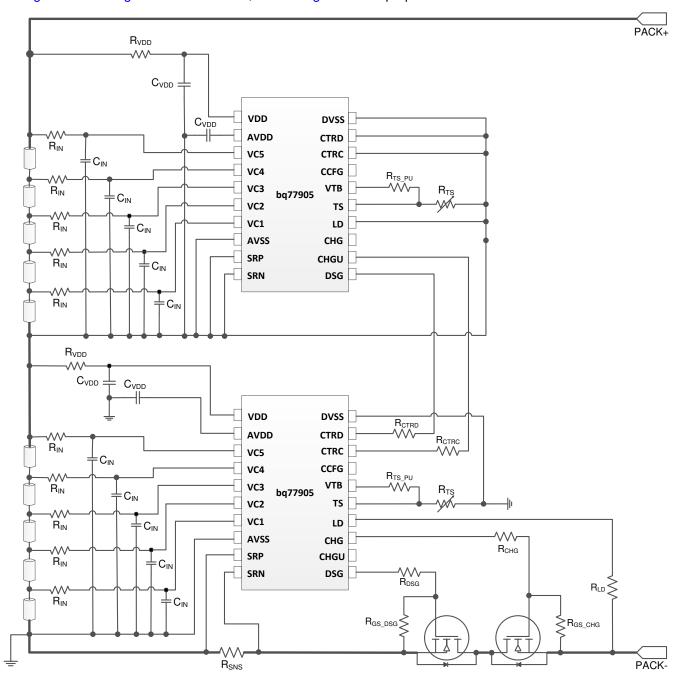

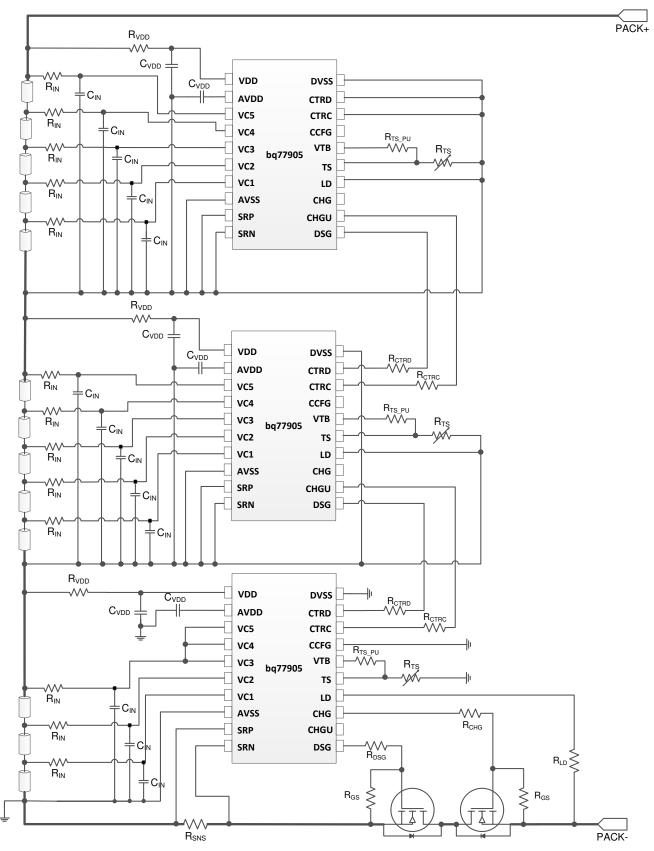

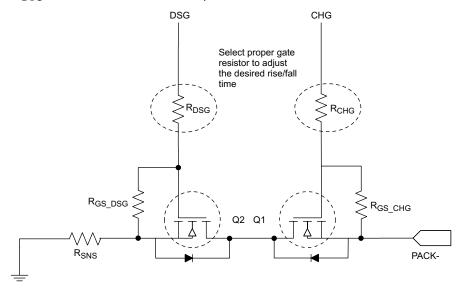

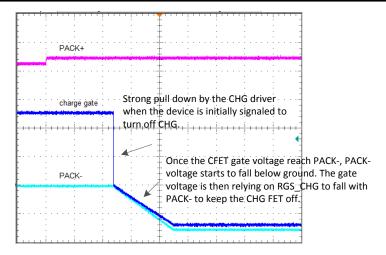

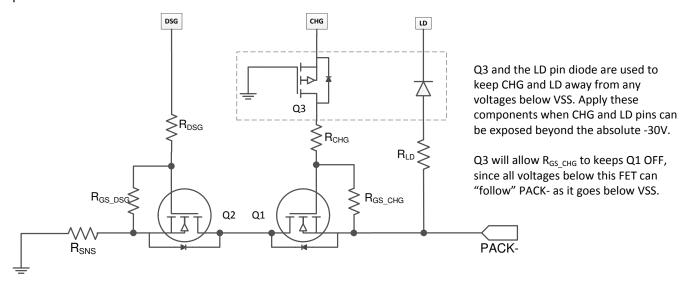

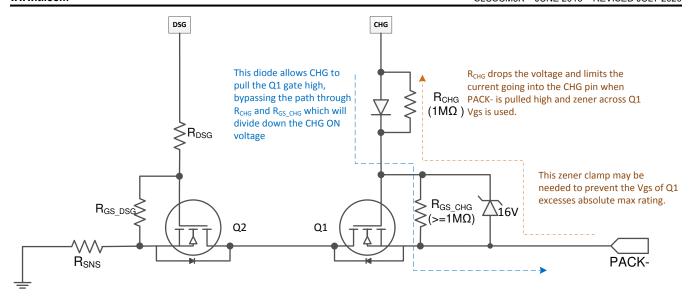

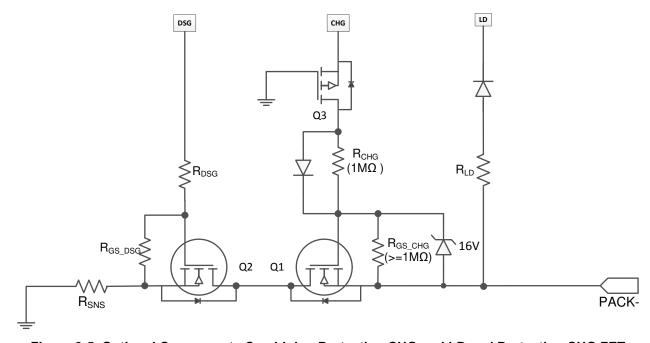

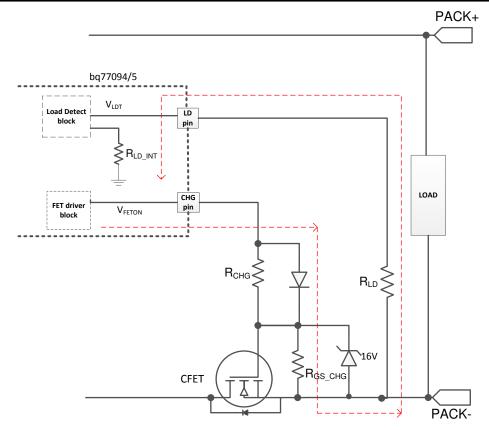

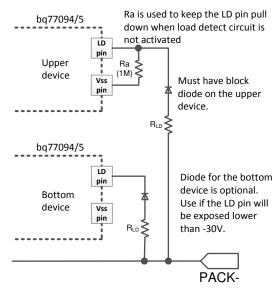

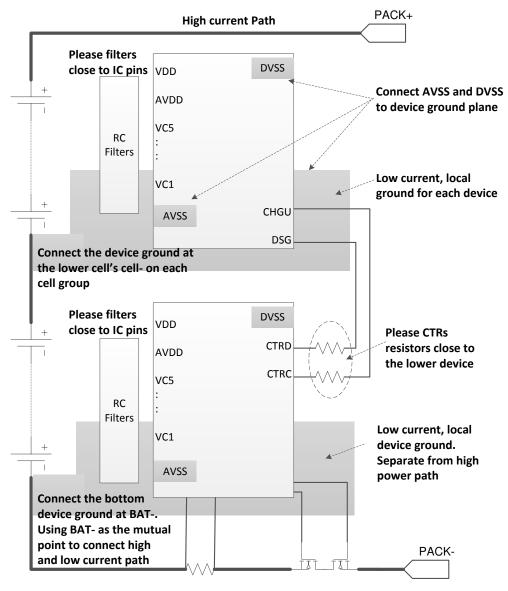

The device achieves pack protection through the integrated independent CHG and DSG low-side NMOS FET drivers, which may be disabled through two control pins. These control pins may also be used to achieve cell protection solutions for higher series (6 series and beyond) in a simple and economical manner. To do this, simply cascade a higher device CHG and DSG outputs to the immediate lower device control pins. For a reduced component count, all protection faults use internal delay timers.

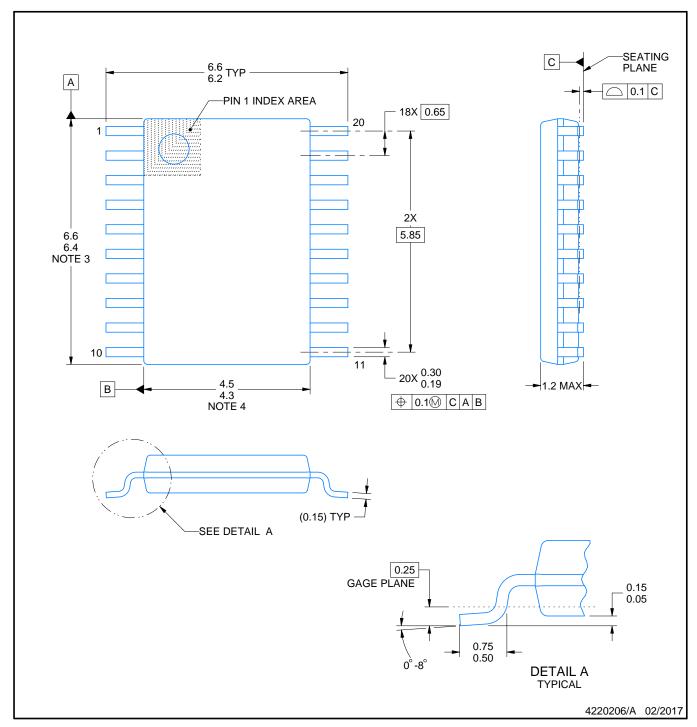

#### **Device Information**

| PART NUMBER <sup>(1)</sup> | PACKAGE    | BODY SIZE (NOM)         |

|----------------------------|------------|-------------------------|

| BQ77904                    | TSSOP (20) | 6.50 mm × 4.40 mm       |

| BQ77905                    | 1330F (20) | 0.50 11111 ^ 4.40 11111 |

For all available packages, see the orderable addendum at the end of the data sheet.

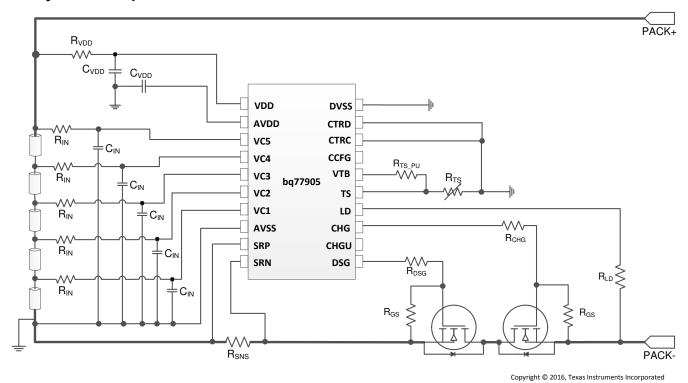

Simplified Schematic

# **Table of Contents**

| 1 Features                                                                           | 1                            | 8.4 Device Functional Modes                  | 26              |

|--------------------------------------------------------------------------------------|------------------------------|----------------------------------------------|-----------------|

| 2 Applications                                                                       |                              | 9 Application and Implementation             | <mark>27</mark> |

| 3 Description                                                                        |                              | 9.1 Application Information                  |                 |

| 4 Revision History                                                                   |                              | 9.2 Typical Application                      |                 |

| 5 Device Comparison                                                                  |                              | 9.3 System Examples                          | 36              |

| 6 Pin Configuration and Functions                                                    |                              | 10 Power Supply Recommendations              |                 |

| Pin Functions                                                                        |                              | 11 Layout                                    |                 |

| 7 Specifications                                                                     |                              | 11.1 Layout Guidelines                       |                 |

| 7.1 Absolute Maximum Ratings                                                         |                              | 11.2 Layout Example                          |                 |

| 7.2 ESD Ratings                                                                      | 6                            | 12 Device and Documentation Support          |                 |

| 7.3 Recommended Operating Conditions                                                 |                              | 12.1 Documentation Support                   |                 |

| 7.4 Thermal Information                                                              |                              | 12.2 Receiving Notification of Documentation |                 |

| 7.5 Electrical Characteristics                                                       |                              | 12.3 Support Resources                       |                 |

| 7.6 Timing Requirements                                                              |                              | 12.4 Trademarks                              |                 |

| 7.7 Typical Characteristics                                                          |                              | 12.5 Electrostatic Discharge Caution         |                 |

| 8 Detailed Description                                                               | 13                           | 12.6 Glossary                                | 38              |

| 8.1 Overview                                                                         | 13                           | 13 Mechanical, Packaging, and Orderable      |                 |

| 8.2 Functional Block Diagram                                                         | 14                           | Information                                  | 38              |

| 8.3 Feature Description                                                              | 14                           |                                              |                 |

| NOTE: Page numbers for previous revisions  Changes from Revision J (April 2020) to F | -                            | · -                                          | Page            |

|                                                                                      |                              | son table                                    |                 |

| Changes from Revision I (December 2019                                               | ) to Revision                | on I (Eabruary 2020)                         | Page            |

|                                                                                      | -                            | in the <i>Device Comparison</i> table        |                 |

|                                                                                      |                              | ·                                            |                 |

| Changes from Revision H (September 202                                               |                              | *                                            | Page            |

| Added the BQ7790522 device to the Dev                                                | rice Compar                  | rison table                                  | 4               |

| Changes from Revision G (September 20                                                | 17) to Revis                 | sion H (September 2018)                      | Page            |

| · Changed some wording throughout the d                                              | ata sheet fo                 | r clarity and conciseness                    | 1               |

| <ul> <li>Added the BQ7790518 device to the BQ7</li> </ul>                            | 77905 <i>Devic</i>           | ce Comparison table                          | 4               |

| Changes from Revision F (May 2017) to R                                              | evision G (                  | (September 2017)                             | Page            |

| <ul> <li>Added BQ7790511 and BQ7790512 to th</li> </ul>                              | e Device C                   | omparison table                              | 4               |

| Changes from Revision E (March 2017) to                                              | Revision I                   | F (May 2017)                                 | Page            |

|                                                                                      |                              | to 2 s. UV from 2800 mV to 2200 mV, UV del   |                 |

|                                                                                      |                              | ry from N to Y. OCD2 from 80 mV to 60 mV, C  |                 |

|                                                                                      |                              |                                              |                 |

|                                                                                      | , 100 IIIV                   |                                              |                 |

| - Added Dall 20000 and Dall 20008 to th                                              |                              | omnarison table                              | 4               |

| Changes from Revision D (March 2017) to                                              |                              | omparison table                              | 4               |

| · · · · · · · · · · · · · · · · · · ·                                                | ne Device Con Revision I     | E (March 2017)                               | 4<br>4<br>Page  |

| Added BQ7790505 to the Device Compa                                                  | ne Device Concept Revision I | E (March 2047)                               | 4<br>4<br>Page  |

65.52 %VTB.......7

# Changes from Revision C (February 2017) to Revision D (March 2017)

Page

# Changes from Revision B (November 2016) to Revision C (February 2017)

Page

# Changes from Revision A (June 2016) to Revision B (November 2016)

Pag

Changed order of listed items in Features

Table 5-1 and Table 5-2, Changed OTC To: UTC in last column under Temperature. Changed BQ7790400 and BQ7790503 to Production Data. Updated the BQ7790503 configuration

Changed pin number from 16-pin to 20-pin

Corrected max value on the UTD at -20°C spec

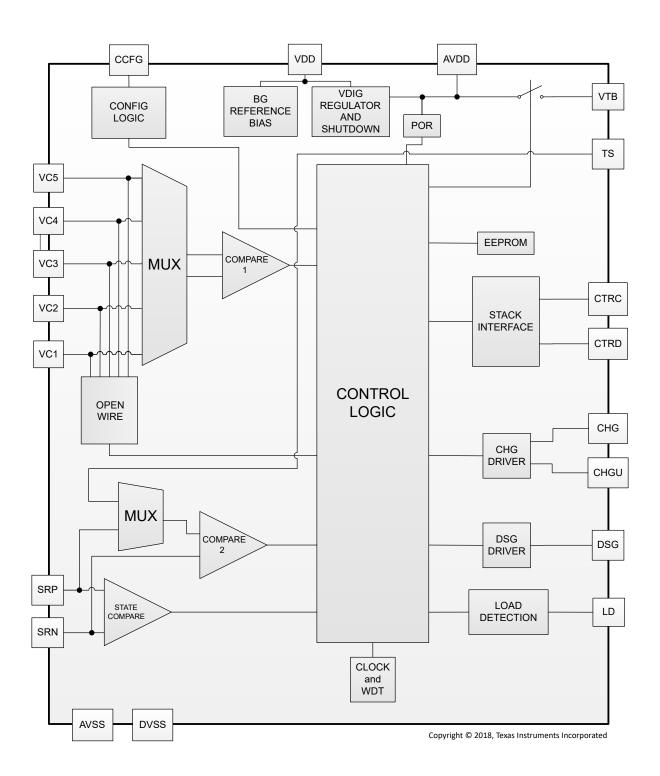

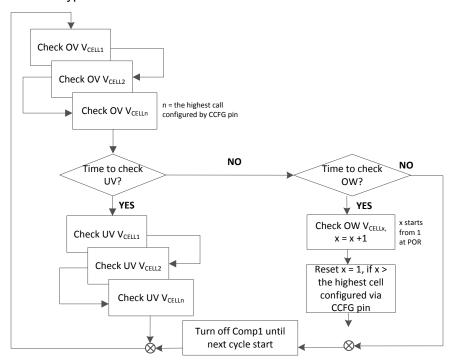

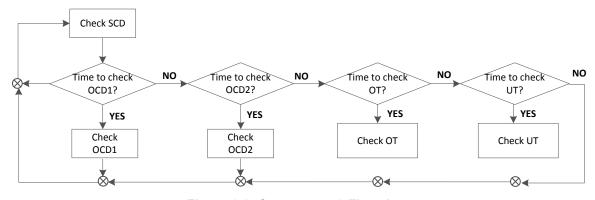

Changed comparator flowcharts with new flowcharts

# Changes from Revision \* (June 2016) to Revision A (June 2016)

# Page

# **5 Device Comparison**

| DEVICE  | NUMBER OF<br>CELLS | PROTECTIONS                           | TYPICAL NORMAL<br>MODE CURRENT (μA) | PACKAGE  |

|---------|--------------------|---------------------------------------|-------------------------------------|----------|

| BQ77904 | 3, 4               | OV, UV, OW, OTD, OTC, UTD, UTC, OCD1, | 6                                   | 20-TSSOP |

| BQ77905 | 3, 4, 5            | OCD2, SCD, CTRC, CTRD                 | 0                                   | 20-1330F |

Unless otherwise specified, the devices in Table 5-1 and Table 5-2 come, by default, with the state comparator enabled with a 2-mV threshold. Filtered fault detection is used by default. Contact Texas Instruments for new configuration options or devices in preview.

Table 5-1. BQ77904 Device Comparison

|             |                | ov       |           |                |          | UV        |                                | ow           | ОС                | D1         |

|-------------|----------------|----------|-----------|----------------|----------|-----------|--------------------------------|--------------|-------------------|------------|

| Part Number | Threshold (mV) | Delay(s) | Hyst (mV) | Thresh<br>(mV) | Delay(s) | Hyst (mV) | Load Removal<br>Recovery (Y/N) | Current (nA) | Threshold<br>(mV) | Delay (ms) |

| BQ7790400   | 4225           | 2        | 100       | 2200           | 2        | 400       | Y                              | 0 (disable)  | 40                | 1420       |

| Part Number | OCD2       | SCD            | Cur       | rent Fault Recovery | Temperature (°C) <sup>(1)</sup> |     |     |     |

|-------------|------------|----------------|-----------|---------------------|---------------------------------|-----|-----|-----|

| (Cont.)     | Delay (ms) | Threshold (mV) | Delay (s) | Method              | OTD                             | отс | UTD | UTC |

| BQ7790400   | 350        | 100            | 0         | Load Removal        | 70                              | 50  | -20 | -5  |

(1) These thresholds are target based on temperature, but they are dependent on external components that could vary based on customer selection. The circuit is based on the 103AT NTC thermistor connected to TS and VSS, and a 10-kΩ resistor connected to VTB and TS. Actual thresholds must be determined in mV. Refers to the overtemperature and undertemperature mV threshold in the Electrical Characteristics table.

Table 5-2. BQ77905 Device Comparison

|             | Table of 21 Ball 1000 Bottles Companion |          |           |                |          |           |                                      |              |                |            |  |

|-------------|-----------------------------------------|----------|-----------|----------------|----------|-----------|--------------------------------------|--------------|----------------|------------|--|

|             | ov                                      |          |           |                | UV       |           |                                      |              | ow occ         |            |  |

| Part Number | Threshold (mV)                          | Delay(s) | Hyst (mV) | Thresh<br>(mV) | Delay(s) | Hyst (mV) | Load<br>Removal<br>Recovery<br>(Y/N) | Current (nA) | Threshold (mV) | Delay (ms) |  |

| BQ7790500   | 4200                                    | 0.5      | 100       | 2600           | 1        | 400       | Y                                    | 100          | 30             | 1420       |  |

| BQ7790502   | 4250                                    | 1        | 200       | 2700           | 1        | 200       | Y                                    | 100          | 85             | 700        |  |

| BQ7790503   | 4200                                    | 1        | 100       | 2700           | 2        | 400       | Y                                    | 100          | 80             | 1420       |  |

| BQ7790505   | 4250                                    | 1        | 200       | 2700           | 1        | 200       | N                                    | 0            | 60             | 10         |  |

| BQ7790508   | 3900                                    | 1        | 200       | 2000           | 1        | 400       | Y                                    | 100          | 50             | 700        |  |

| BQ7790509   | 4250                                    | 1        | 100       | 2500           | 1        | 400       | Y                                    | 100          | 50             | 700        |  |

| BQ7790511   | 4250                                    | 1        | 200       | 2700           | 1        | 200       | Y                                    | 100          | 50             | 350        |  |

| BQ7790512   | 4175                                    | 1        | 100       | 2800           | 1        | 400       | Y                                    | 100          | 75             | 1420       |  |

| BQ7790518   | 4250                                    | 1        | 100       | 2750           | 1        | 200       | Y                                    | 100          | 70             | 180        |  |

| BQ7790521   | 3700                                    | 1        | 200       | 2500           | 1        | 200       | Y                                    | 100          | 70             | 180        |  |

| BQ7790522   | 4250                                    | 1        | 100       | 2800           | 1        | 200       | Y                                    | 100          | 80             | 700        |  |

|             |                                         |          |           |                |          |           |                                      |              |                |            |  |

|                     | (              | OCD2       | SCD            | Cur       | rent Fault Recovery  |     | Temperate | ure (°C) <sup>(1)</sup> |            |

|---------------------|----------------|------------|----------------|-----------|----------------------|-----|-----------|-------------------------|------------|

| Part Number (Cont.) | Threshold (mV) | Delay (ms) | Threshold (mV) | Delay (s) | Method               | OTD | отс       | UTD                     | UTC        |

| BQ7790500           | 50             | 700        | 120            | 1         | Load Removal + Delay | 70  | 50        | -20                     | 0          |

| BQ7790502           | 120            | 350        | 240            | _         | Load Removal         | 70  | 50        | -20                     | -5         |

| BQ7790503           | 160            | 350        | 320            | _         | Load Removal         | 70  | 50        | -20                     | <b>-</b> 5 |

| BQ7790505           | 80             | 5          | 100            | 9         | Load Removal + Delay | 65  | 45        | -20                     | 0          |

| BQ7790508           | 100            | 90         | 200            | 1         | Load Removal + Delay | 70  | 50        | -20                     | <b>-</b> 5 |

| BQ7790509           | 100            | 90         | 200            | 1         | Load Removal + Delay | 70  | 50        | -20                     | <b>-</b> 5 |

| BQ7790511           | 120            | 90         | 280            | _         | Load Removal         | 65  | 45        | -20                     | 0          |

| BQ7790512           | 150            | 350        | 300            | 1         | Load Removal + Delay | 65  | 45        | -20                     | 0          |

| BQ7790518           | 140            | 20         | 300            | 1         | Load Removal         | 70  | 50        | -20                     | 0          |

| BQ7790521           | 140            | 20         | 320            | 1         | Load Removal         | 70  | 50        | -20                     | 0          |

| BQ7790522           | 100            | 350        | 300            | 1         | Load Removal         | 70  | 50        | -20                     | <b>-</b> 5 |

(1) These thresholds are target based on temperature, but they are dependent on external components that could vary based on customer selection. Circuit is based on 103AT NTC thermistor connected to TS and VSS, and a 10-kΩ resistor connected to VTB and TS.

Actual thresholds must be determined in mV. Refers to the overtemperature and undertemperature mV threshold in the Electrical Characteristics table.

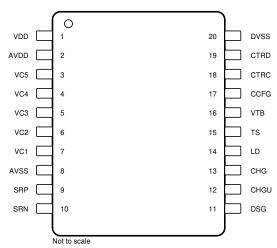

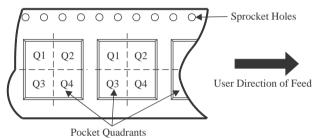

# **6 Pin Configuration and Functions**

Figure 6-1. PW Package 20-Pin TSSOP Top View

# **Pin Functions**

| PIN  | PIN |                      | DESCRIPTION                                                                                                                   |

|------|-----|----------------------|-------------------------------------------------------------------------------------------------------------------------------|

| NAME | NO. | - I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                   |

| AVDD | 2   | 0                    | Analog supply (only connect to a capacitor)                                                                                   |

| AVSS | 8   | Р                    | Analog ground                                                                                                                 |

| CCFG | 17  | I                    | Cell in series-configuration input                                                                                            |

| CHG  | 13  | 0                    | CHG FET driver. Use on a single device or on the bottom device of a stack configuration.                                      |

| CHGU | 12  | 0                    | CHG FET signal. Use for the upper device of a stack configuration to feed the CHG signal to the CTRC pin of the lower device. |

| CTRC | 18  | I                    | CLIC and DCC avarrida innuts                                                                                                  |

| CTRD | 19  | I                    | CHG and DSG override inputs                                                                                                   |

| DSG  | 11  | 0                    | DSG FET driver                                                                                                                |

| DVSS | 20  | Р                    | Digital ground                                                                                                                |

| LD   | 14  | I                    | PACK- load removal detection                                                                                                  |

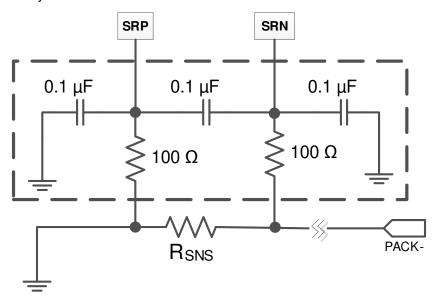

| SRN  | 10  | I                    | Current sense input connecting to the PACK- side of sense resistor                                                            |

| SRP  | 9   | I                    | Current sense input connecting to the battery side of sense resistor                                                          |

| TS   | 15  | I                    | Thermistor measurement input. Connect a 10-k $\Omega$ resistor to AVSS pin if the function is not used.                       |

| VC1  | 7   | I                    |                                                                                                                               |

| VC2  | 6   | I                    | Call valtage copes inputs                                                                                                     |

| VC3  | 5   | I                    | Cell voltage sense inputs                                                                                                     |

| VC4  | 4   | I                    |                                                                                                                               |

| VC5  | 3   | I                    | Cell voltage sense inputs (Pin 3 must be connected to Pin 4 on the BQ77904 device.)                                           |

| VDD  | 1   | Р                    | Supply voltage                                                                                                                |

| VTB  | 16  | 0                    | Thermistor bias output                                                                                                        |

(1) I = Input, O = Output, P = Power

# 7 Specifications

# 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted). All values are referenced to VSS unless otherwise noted. (1)

|                |                               |                                                | MIN  | MAX | UNIT |

|----------------|-------------------------------|------------------------------------------------|------|-----|------|

|                |                               | VDD, VC5, VC4, VC3, VC2, VC1, CCFG, CTRD, CTRC | -0.3 | 36  | V    |

| VI             | Input voltage                 | LD                                             | -30  | 20  | V    |

|                |                               | SRN, SRP, TS, AVDD, CCFG                       | -0.3 | 3.6 | V    |

|                |                               | DSG, CHGU                                      | -0.3 | 20  | V    |

| Vo             | Output voltage range          | CHG                                            | -30  | 20  | V    |

|                |                               | VTB                                            | -0.3 | 3.6 | V    |

| I <sub>I</sub> | Input current                 | LD, CHG                                        |      | 500 | μA   |

| I              | Input current                 | CHGU, DSG                                      |      | 1   | mA   |

| Io             | Output current                | CHG                                            |      | 1   | mA   |

| Io             | Output current                | CHGU, DSG                                      |      | 1   | mA   |

| Storage        | temperature, T <sub>stg</sub> |                                                | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT                                  |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|---------------------------------------|

| V                  | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±1000 | W                                     |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±250  | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

|                  |                           |                                             | MIN  | MAX       | UNIT     |  |

|------------------|---------------------------|---------------------------------------------|------|-----------|----------|--|

| V <sub>BAT</sub> | Supply voltage            | VDD                                         | 3    | 25        | V        |  |

| V <sub>I</sub>   |                           | VC5-VC4, VC4-VC3, VC3-VC2, VC2-VC1, VC1-VSS | 0    | 5         | <u> </u> |  |

|                  |                           | CTRD, CTRC                                  | 0    | (VDD + 5) |          |  |

|                  | Input voltage             | CCFG                                        | 0    | AVDD      | V        |  |

|                  |                           | SRN, SRP                                    | -0.2 | 8.0       |          |  |

|                  |                           | LD                                          | 0    | 16        |          |  |

|                  |                           | TS                                          | 0    | VTB       |          |  |

| V                | Output voltage            | CHG, CHGU, DSG                              | 0    | 16        | V        |  |

| Vo               | Output voltage            | VTB, AVDD                                   | 0    | 3         |          |  |

| T <sub>A</sub>   | Operating free-range temp | erature                                     | -40  | 85        | °C       |  |

# 7.4 Thermal Information

|                       | <b></b>                                      | bq77904<br>bq77905 | =     |

|-----------------------|----------------------------------------------|--------------------|-------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PW (TSSOP)         | UNITS |

|                       |                                              | 20 PINS            |       |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 98.4               | °C/W  |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | 37                 | °C/W  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 49.3               | °C/W  |

| ΨЈТ                   | Junction-to-top characterization parameter   | 2.9                | °C/W  |

| ΨЈВ                   | Junction-to-board characterization parameter | 48.7               | °C/W  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics

Typical values stated at  $T_A$  = 25°C and VDD = 16 V (bq77904) or 20 V (bq77905). MIN and MAX values stated with  $T_A$  = -40°C to +85°C and VDD = 3 to 20 V (bq77904) or VDD = 3 to 25 V (bq77905) unless otherwise noted.

|                          | PARAMETER                                                    | TEST CONDITIONS                                             | MIN    | TYP    | MAX    | UNIT |

|--------------------------|--------------------------------------------------------------|-------------------------------------------------------------|--------|--------|--------|------|

| SUPPLY VOLTAG            | GE                                                           |                                                             |        |        |        |      |

| V <sub>(POR)</sub>       | POR threshold                                                | VDD rising, 0 to 6 V                                        |        |        | 4      | V    |

| V <sub>(SHUT)</sub>      | Shutdown threshold                                           | VDD falling, 6 to 0 V                                       | 2      | ,      | 3.25   | V    |

| V <sub>(AVDD)</sub>      | AVDD voltage                                                 | C <sub>(VDD)</sub> = 1 μF                                   | 2.1    | 2.5    | 3.25   | V    |

|                          | AKAGE CURRENT                                                |                                                             |        |        |        |      |

| I <sub>CC</sub>          | NORMAL mode current<br>(bq77904/bq77905)                     | Cell1 through Cell5 = 4 V,<br>VDD = 20 V (bq77905)          |        | 6      | 9      | μA   |

| I <sub>(CFAULT)</sub>    | Fault condition current                                      | State comparator on                                         |        | 8      | 12     | μΑ   |

| l <sub>OFF</sub>         | SHUTDOWN mode current                                        | VDD < V <sub>SHUT</sub>                                     |        |        | 0.5    | μA   |

| I <sub>LKG(OW_DIS)</sub> | Input leakage current at VCx pins                            | All cell voltages = 4 V,<br>Open-wire disable configuration | -100   | 0      | 100    | nA   |

| I <sub>LKG(100nA)</sub>  | Open-wire sink current at<br>VCx pins                        | All cell voltages = 4 V,<br>100-nA configuration            | 30     | 110    | 175    | nA   |

| I <sub>LKG(200nA)</sub>  | Open-wire sink current at VCx pins                           | All cell voltages = 4 V,<br>200-nA configuration            | 95     | 210    | 315    | nA   |

| I <sub>LKG(400nA)</sub>  | Open-wire sink current at VCx pins                           | All cell voltages = 4 V,<br>400-nA configuration            | 220    | 425    | 640    | nA   |

| PROTECTION A             | CCURACIES                                                    |                                                             |        | ,      | '      |      |

| V <sub>OV</sub>          | Overvoltage programmable threshold range                     |                                                             | 3000   |        | 4575   | mV   |

| V <sub>UV</sub>          | Undervoltage programmable threshold range                    |                                                             | 1200   |        | 3000   | mV   |

|                          |                                                              | T <sub>A</sub> = 25°C, OV detection accuracy                | -10    |        | 10     | mV   |

| <b>.</b>                 | OV, UV, detection accuracy                                   | T <sub>A</sub> = 25°C, UV detection accuracy                | -18    |        | 18     | mV   |

| $V_{(VA)}$               | Ov, Ov, detection accuracy                                   | T <sub>A</sub> = 0 to 60°C                                  | -28    |        | 26     | mV   |

|                          |                                                              | T <sub>A</sub> = -40 to 85°C                                | -40    |        | 40     | mV   |

| V <sub>HYS(OV)</sub>     | OV hysteresis<br>programmable threshold<br>range             |                                                             | 0      |        | 400    | mV   |

| V <sub>HYS(UV)</sub>     | UV hysteresis programmable threshold range                   |                                                             | 200    |        | 800    | mV   |

|                          | Overtemperature in                                           | Threshold for 65°C <sup>(1)</sup>                           | 19.71% | 20.56% | 21.86% | V    |

| $V_{OTD}$                | discharge programmable threshold (ratio of V <sub>TB</sub> ) | Threshold for 70°C (1)                                      | 17.36% | 18.22% | 19.51% | VTB  |

Typical values stated at  $T_A$  = 25°C and VDD = 16 V (bq77904) or 20 V (bq77905). MIN and MAX values stated with  $T_A$  = -40°C to +85°C and VDD = 3 to 20 V (bq77904) or VDD = 3 to 25 V (bq77905) unless otherwise noted.

|                         | PARAMETER                                                                                    | TEST CONDITIONS                                                                           | MIN     | TYP    | MAX    | UNIT |

|-------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------|--------|--------|------|

| .,                      | Overtemperature in                                                                           | Recovery threshold at 55°C for when V <sub>OTD</sub> is at 65°C <sup>(1)</sup>            | 25.24%  | 26.12% | 27.44% | VTB  |

| V <sub>OTD(REC)</sub>   | discharge recovery (ratio of $V_{TB}$ )                                                      | Recovery threshold at 60°C for when V <sub>OTD</sub> is at 70°C <sup>(1)</sup>            | 22.12%  | 23.2%  | 24.24% | VTB  |

|                         | Overtemperature in charge                                                                    | Threshold for 45°C <sup>(1)</sup>                                                         | 32.14%  | 32.94% | 34.54% | VTB  |

| V <sub>OTC</sub>        | programmable threshold (ratio of V <sub>TB</sub> )                                           | Threshold for 50°C <sup>(1)</sup>                                                         | 29.15%  | 29.38% | 31.45% | VTB  |

| V                       | Overtemperature in charge                                                                    | Recovery threshold at 35°C when V <sub>OTD</sub> is at 45°C <sup>(1)</sup>                | 38.63%  | 40.97% | 40.99% | VTB  |

| V <sub>OTC(REC)</sub>   | recovery (ratio of V <sub>TB</sub> )                                                         | Recovery threshold at 40°C when V <sub>OTD</sub> is at 50°C <sup>(1)</sup>                | 36.18%  | 36.82% | 38.47% | VTB  |

|                         | Undertemperature in                                                                          | Threshold for –20°C <sup>(1)</sup>                                                        | 86.41%  | 87.14% | 89.72% | VTB  |

| $V_{UTD}$               | discharge programmable threshold (ratio of V <sub>TB</sub> )                                 | Threshold for -10°C <sup>(1)</sup>                                                        | 80.04%  | 80.94% | 83.10% | VTB  |

| V <sub>UTD(REC)</sub>   | Undertemperature in discharge recovery (ratio of                                             | Recovery threshold at $-10^{\circ}$ C when $V_{UTD}$ is at $-20^{\circ}$ C <sup>(1)</sup> | 80.04%  | 80.94% | 83.10% | VTB  |

| VOTD(REC)               | V <sub>TB</sub> )                                                                            | Recovery threshold at 0°C when V <sub>UTD</sub> is at –10°C <sup>(1)</sup>                | 71.70%  | 73.18% | 74.86% | VTB  |

|                         | Undertemperature in charge                                                                   | Threshold for -5°C <sup>(1)</sup>                                                         | 75.06%  | 77.22% | 78.32% | VTB  |

| V <sub>UTC</sub>        | programmable threshold (ratio of V <sub>TB</sub> )                                           | Threshold for 0°C <sup>(1)</sup>                                                          | 71.70%  | 73.18% | 74.86% | VTB  |

| V <sub>UTC(REC)</sub>   | Undertemperature in Charge                                                                   | Recovery threshold at 5°C when V <sub>UTC</sub> is at –5°C <sup>(1)</sup>                 | 68.80%  | 69.73% | 71.71% | VTB  |

| VUIC(REC)               | Recovery (ratio of V <sub>TB</sub> )                                                         | Recovery threshold at 10°C when V <sub>UTC</sub> is at 0°C <sup>(1)</sup>                 | 64.67%  | 65.52% | 67.46% | VTB  |

| V <sub>OCD1</sub>       | Overcurrent discharge 1 programmable threshold range, (V <sub>SRP</sub> – V <sub>SRN</sub> ) |                                                                                           | -85     |        | -10    | mV   |

| V <sub>OCD2</sub>       | Overcurrent discharge 2 programmable threshold range, (V <sub>SRP</sub> – V <sub>SRN</sub> ) |                                                                                           | -20     |        | -170   | mV   |

| V <sub>SCD</sub>        | Short circuit discharge progra<br>V <sub>SRN</sub> )                                         | mmable threshold range, (V <sub>SRP</sub> –                                               | -40     |        | -340   | mV   |

| V <sub>CCAL</sub>       | OCD1 detection accuracy at lower thresholds                                                  | V <sub>OCD1</sub> > -20 mV                                                                | -30%    |        | 30%    |      |

| V <sub>CCAH</sub>       | OCD1, OCD2, SCD detection accuracy                                                           | V <sub>OCD1</sub> ≤ −20 mV; all OCD2 and SCD threshold ranges                             | -20%    |        | 20%    |      |

| V <sub>OW</sub>         | Open-wire fault voltage threshold at VCx per cell with respect to VC <sub>x-1</sub>          | Voltage falling on VCx, 3.6 V to 0 V                                                      | 450     | 500    | 550    | mV   |

| V <sub>OW(HYS)</sub>    | Hysteresis for open wire fault                                                               | Voltage rising on VCx, 0 V to 3.6 V                                                       |         | 100    |        | mV   |

| CHARGE AND D            | ISCHARGE FET DRIVERS                                                                         |                                                                                           |         |        |        |      |

| V <sub>(FETON)</sub>    | CHG/CHGU/DSG on                                                                              | VDD ≥ 12 V, CL = 10 nF                                                                    | 11      | 12     | 14     | V    |

| (FEIUN)                 | 5.15,51100/D00 0II                                                                           | VDD < 12 V, CL = 10 nF                                                                    | VDD – 1 |        | VDD    | V    |

| V <sub>(FETOFF)</sub>   | CHG/CHGU/DSG off                                                                             | No load when CHG/CHGU/DSG is off.                                                         |         |        | 0.5    | V    |

| R <sub>(CHGOFF)</sub>   | CHG off resistance                                                                           | CHG off for > t <sub>CHGPDN</sub> and pin held at 2 V                                     |         | 0.5    |        | kΩ   |

| R <sub>(DSGOFF)</sub>   | CHGU/DSG off resistance                                                                      | CHGU/DSG off and pin held at 2 V                                                          |         | 10     | 16     | Ω    |

| I <sub>CHG(CLAMP)</sub> | CHG clamp current                                                                            | CHG off and pin held at 18 V                                                              |         |        | 450    | μA   |

www.ti.com

Typical values stated at  $T_A$  = 25°C and VDD = 16 V (bq77904) or 20 V (bq77905). MIN and MAX values stated with  $T_A$  = -40°C to +85°C and VDD = 3 to 20 V (bq77904) or VDD = 3 to 25 V (bq77905) unless otherwise noted.

| F                       | PARAMETER                                                                     | TEST CONDITIONS                                        | MIN       | TYP     | MAX       | UNIT |

|-------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------|-----------|---------|-----------|------|

| V <sub>CHG(CLAMP)</sub> | CHG clamp voltage                                                             | I <sub>CHG(CLAMP)</sub> = 300 μA                       | 16        | 18      | 20.5      | V    |

| CHGON                   | CHG on rise time                                                              | CL = 10 nF, 10% to 90%                                 |           | 50      | 150       | μs   |

| DSGON                   | CHGU/DSG on rise time                                                         | CL = 10 nF, 10% to 90%                                 |           | 2       | 75        | μs   |

| CHGOFF                  | CHG off fall time                                                             | CL = 10 nF, 90% to 10%                                 |           | 15      | 30        | μs   |

| DSGOFF                  | CHGU/DSG off fall time                                                        | CL = 10 nF, 90% to 10%                                 |           | 5       | 15        | μs   |

| CTRC AND CTRD C         | CONTROL                                                                       |                                                        |           |         |           | •    |

| V <sub>CTR1</sub>       | Enable FET driver (VSS)                                                       | With respect to VSS. Enabled < MAX                     |           |         | 0.6       | V    |

| V <sub>CTR2</sub>       | Enable FET driver (Stacked)                                                   | Enabled > MIN                                          | VDD + 2.2 |         |           | V    |

| V <sub>CTR(DIS)</sub>   | Disable FET driver                                                            | Disabled between MIN and MAX                           | 2.04      |         | VDD + 0.7 | V    |

| V <sub>CTR(MAXV)</sub>  | CTRC and CTRD clamp voltage                                                   | I <sub>CTR</sub> = 600 nA                              | VDD + 2.8 | VDD + 4 | VDD + 5   | V    |

| CTRDEG_ON) (2)          | CTRC and CTRD deglitch for ON signal                                          |                                                        |           | 7       |           | ms   |

| CTRDEG_OFF (2)          | CTRC and CTRD deglitch for OFF signal                                         |                                                        |           | 7       |           | ms   |

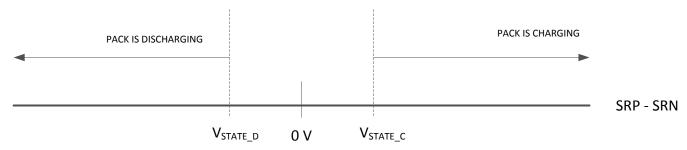

| CURRENT STATE C         | OMPARATOR                                                                     |                                                        |           |         |           |      |

| V <sub>(STATE_D1)</sub> | Discharge qualification threshold1                                            | Measured at SRP-SRN                                    | -3        | -2      | -1        | mV   |

| V <sub>(STATE_C1)</sub> | Charge qualification threshold1                                               | Measured at SRP-SRN                                    | 1         | 2       | 3         | mV   |

| STATE (2)               | State detection qualification time                                            |                                                        |           |         | 1.2       | ms   |

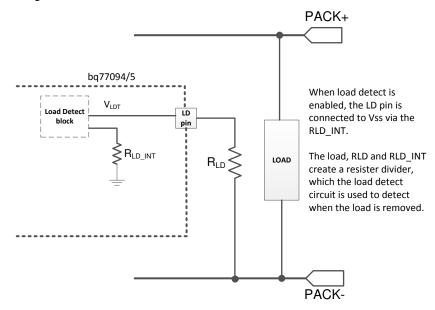

| LOAD REMOVAL D          | ETECTION                                                                      |                                                        |           |         |           |      |

| J <sub>LD(CLAMP)</sub>  | LD clamp voltage                                                              | I <sub>(LDCLAMP)</sub> = 300 μA                        | 16        | 18      | 20.5      | V    |

| LD(CLAMP)               | LD clamp current                                                              | V <sub>(LDCLAMP)</sub> = 18 V                          |           |         | 450       | μA   |

| $V_{LDT}$               | LD threshold                                                                  | Load removed < when V <sub>LDT</sub>                   | 1.25      | 1.3     | 1.35      | V    |

| R <sub>LD(INT)</sub>    | LD input resistance when enabled                                              | Measured to VSS                                        | 160       | 250     | 375       | kΩ   |

| t <sub>LD_DEG</sub>     | LD detection deglitch                                                         |                                                        | 1         | 1.5     | 2.3       | ms   |

| CCFG PIN                |                                                                               |                                                        |           |         | I         |      |

| V <sub>(CCFGL)</sub>    | CCFG threshold low (ratio of V <sub>AVDD</sub> )                              | 3-cell configuration                                   |           |         | 10%       | V    |

| V <sub>(CCFGH)</sub>    | CCFG threshold high (ratio of $V_{\text{AVDD}}$ )                             | 4-cell configuration                                   | 65%       |         | 100%      | V    |

| V <sub>(CCFGHZ)</sub>   | CFG threshold high-Z (ratio of V <sub>AVDD</sub> )                            | 5-cell configuration, CCFG floating, internally biased | 25%       | 33%     | 45%       | V    |

| CCFG_DEG (2)            | CCFG deglitch                                                                 |                                                        |           | 6       |           | ms   |

| CUSTOMER TEST I         | MODE (CTM)                                                                    |                                                        |           |         |           |      |

| V <sub>(CTM)</sub>      | Customer test mode entry voltage at VDD                                       | VDD > VC5 + V <sub>(CTM)</sub> , T <sub>A</sub> = 25°C | 8.5       |         | 10        | V    |

| CTM_ENTRY (3)           | Delay time to enter and exit<br>Customer Test Mode                            | VDD > VC5 + V <sub>(CTM)</sub> , T <sub>A</sub> = 25°C | 50        |         |           | ms   |

| CTM_DELAY (3)           | Delay time of faults while in<br>Customer Test Mode                           | T <sub>A</sub> = 25°C                                  |           |         | 200       | ms   |

| CTM_OC_REC (3)          | Fault recovery time of OCD1, OCD2, and SCD faults while in Customer Test Mode | 1 s and 8 s options, T <sub>A</sub> = 25°C             |           |         | 100       | ms   |

(1) Based on a 10-K $\Omega$  pull-up and 103AT thermistor

- (2) Not production tested parameters. Specified by design

(3) The device is in a no fault state prior to entering Customer Test Mode.

# 7.6 Timing Requirements

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      | MIN  | TYP  | MAX  | UNIT |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|------|------|------|

| PROTECTION             | DELAYS (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |      |      | •    |      |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0.5-s delay option   | 0.4  | 0.5  | 0.8  |      |

|                        | Overvoltage detection delevitime                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1-s delay option     | 0.8  | 1    | 1.4  |      |

| <sup>t</sup> OVn_DELAY | Overvoltage detection delay time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-s delay option     | 1.8  | 2    | 2.7  | S    |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4.5-s delay option   | 4    | 4.5  | 5.2  |      |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1-s delay option     | 0.8  | 1    | 1.5  |      |

| t <sub>UVn_DELAY</sub> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-s delay option     | 1.8  | 2    | 2.7  |      |

| UVn_DELAY              | Undervoltage detection delay time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4.5-s delay option   | 4    | 4.5  | 5.5  | S    |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9-s delay option     | 8    | 9    | 10.2 |      |

| t <sub>OWn_DELAY</sub> | Open-wire detection delay time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      | 3.6  | 4.5  | 5.3  | s    |

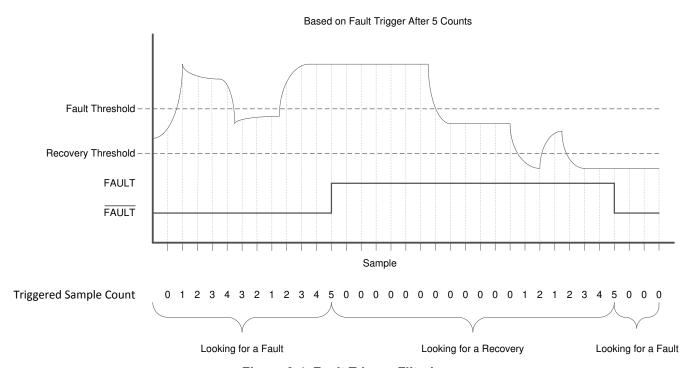

| t <sub>OTC_DELAY</sub> | Overtemperature charge detection delay time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      | 3.6  | 4.5  | 5.3  | s    |