BQ76922 ZHCSVT2A - APRIL 2022 - REVISED APRIL 2024

BQ76922 适用于锂离子、锂聚合物和磷酸铁锂电池包的 3 节至 5 节串联高精度电池临初 3 节至 5 节串联高精度电池监测器和保护器

# 1 特性

Ŧ

**TEXAS**

INSTRUMENTS

- 适用于3节至5节串联电池的电池监控功能

- 用于高侧 NFET 保护的集成电荷泵,可选择自主恢 复

- 广泛的保护套件,包括电压、温度、电流和内部诊断

- 两个独立的 ADC

- 支持电流和电压同步采样

- 高精度库伦计数器,输入失调电压误差 < 1µV</li>

(典型值)

- 高精度电池电压测量 < 10mV ( 典型值 )

- 宽量程的电流应用(检测电阻上的测量范围为 ±200mV)

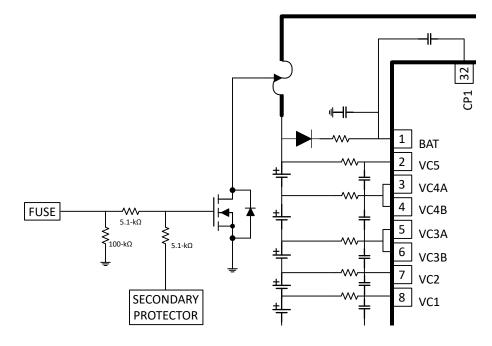

- 集成式化学保险丝驱动二级保护

- 自主式或主机控制型电芯均衡

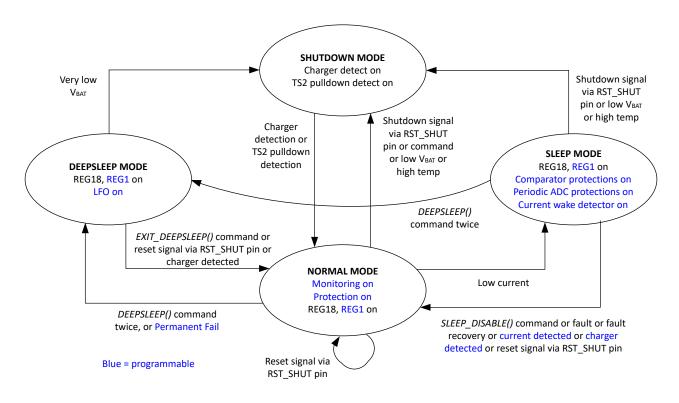

- 多种功耗模式(电池包典型运行范围条件)

- NORMAL 模式: 286µA

- 多个 SLEEP 模式选项: 24µA 至 41µA

- 多个 DEEPSLEEP 模式选项: 9µA 至 10µA

- SHUTDOWN 模式:1µA

- 电池连接和部分其他引脚上的高电压容差为 60V

- 在量产线支持随机的电芯连接序列

- 支持使用内部传感器和多达5个外部热敏电阻进行 温度检测

- 集成的一次性可编程 (OTP) 存储器可由客户在生产 线上进行编程

- 通信选项包含 400kHz I<sup>2</sup>C 和 HDQ 单线接口

- 供外部系统使用的可编程 LDO

- 32 引脚 QFN 封装 (RSN)

# 2 应用

- 无线电动工具和园艺工具

- 真空吸尘器

- 扫地机器人

- 非军用无人机

- 其他工业电池包(3节至5节串联)

### 3 说明

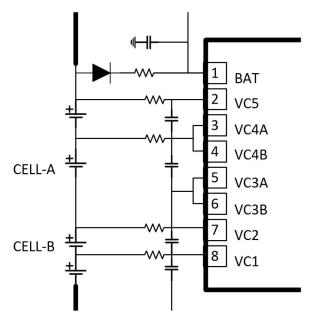

德州仪器 (TI)的 BQ76922 器件是一款高度集成的高精 度电池监控器和保护器,适用于 3 节至 5 节串联锂离 子、锂聚合物和磷酸铁锂电池包。该器件包括一个高精 度监控系统和一个高度可配置的保护子系统,并支持自 主式或主机控制型电芯均衡。它集成了高侧电荷泵 NFET 驱动器、供外部系统使用的可编程 LDO 以及一 个支持 400kHz I<sup>2</sup>C 和 HDQ 单线标准的主机通信外 设。BQ76922 器件可提供 32 引脚 4mm × 4mm QFN 封装。

器件信息

| 11111111111111111111111111111111111111 |            |           |  |  |  |  |

|----------------------------------------|------------|-----------|--|--|--|--|

| 器件型号 <sup>(1)</sup>                    | 封装         | 本体尺寸(标称值) |  |  |  |  |

| BQ76922                                | RSN(32 引脚) | 4mm × 4mm |  |  |  |  |

(1) 请参阅器件比较表以了解该器件系列。如需了解所有可用器件,请参阅数据表末尾的可订购产品附录。

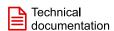

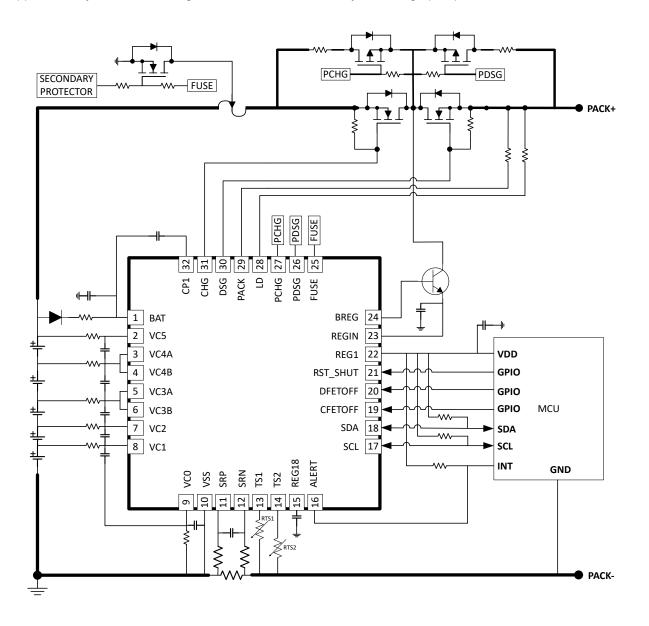

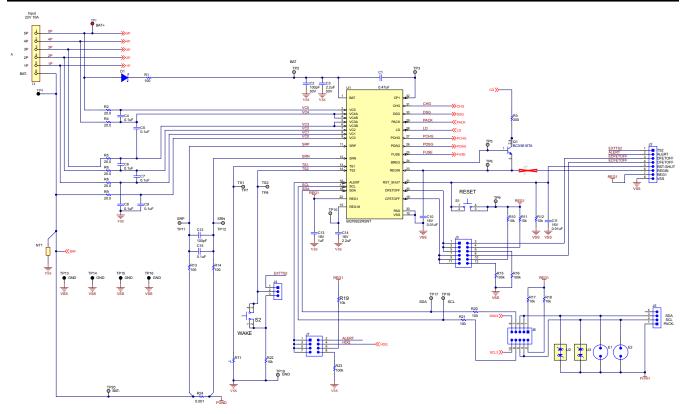

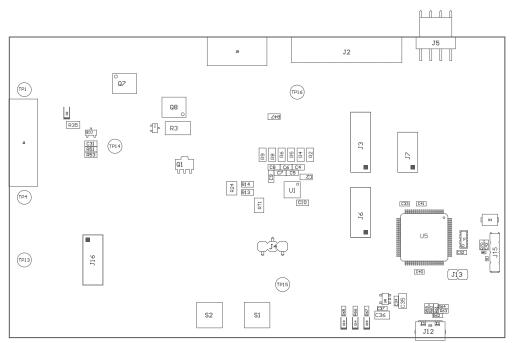

简化原理图

# **Table of Contents**

| 1 特性                                                          | 1              |

|---------------------------------------------------------------|----------------|

| 2 应用                                                          | 1              |

| 3 说明                                                          | 1              |

| 4 Device Comparison Table                                     |                |

| 5 Pin Configuration and Functions                             |                |

| 6 Specifications                                              |                |

| 6.1 Absolute Maximum Ratings                                  |                |

| 6.2 ESD Ratings                                               |                |

| 6.3 Recommended Operating Conditions                          |                |

| 6.4 Thermal Information BQ76922                               |                |

| 6.5 Supply Current                                            | <mark>8</mark> |

| 6.6 Digital I/O                                               |                |

| 6.7 LD Pin                                                    | 9              |

| 6.8 Precharge (PCHG) and Predischarge (PDSG)                  |                |

| FET Drive                                                     |                |

| 6.9 FUSE Pin Functionality                                    |                |

| 6.10 REG18 LDO                                                |                |

| 6.11 REG0 Pre-regulator                                       |                |

| 6.12 REG1 LDO                                                 |                |

| 6.13 Voltage References<br>6.14 Coulomb Counter               |                |

| 6.15 Coulomb Counter Digital Filter (CC1)                     |                |

| 6.16 Current Measurement Digital Filter (CC2)                 |                |

| 6.17 Current Wake Detector                                    |                |

| 6.18 Analog-to-Digital Converter                              |                |

| 6.19 Cell Balancing                                           |                |

| 6.20 Cell Open Wire Detector                                  |                |

| 6.21 Internal Temperature Sensor                              |                |

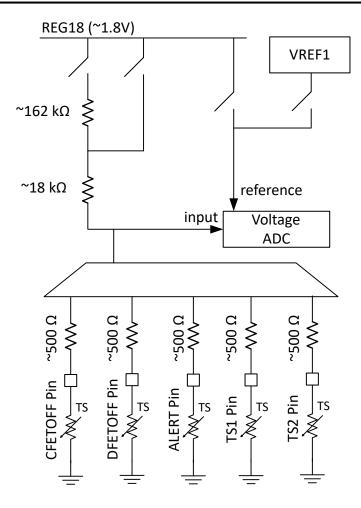

| 6.22 Thermistor Measurement                                   |                |

| 6.23 Internal Oscillators                                     |                |

| 6.24 High-side NFET Drivers                                   |                |

| 6.25 Comparator-Based Protection Subsystem                    | .17            |

| 6.26 Timing Requirements – I <sup>2</sup> C Interface, 100kHz |                |

| Mode                                                          | 19             |

| 6.27 Timing Requirements – I <sup>2</sup> C Interface, 400kHz |                |

| Mode                                                          | 19             |

|                                                               |                |

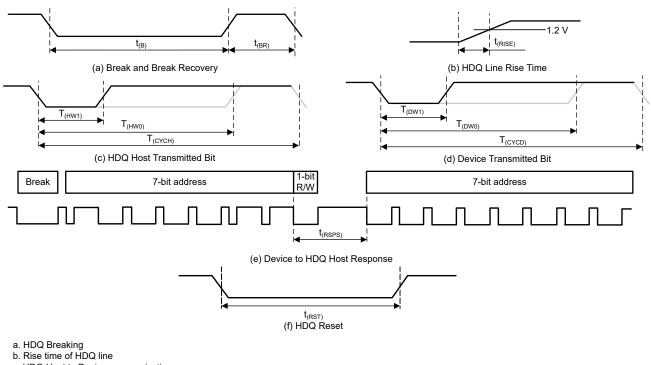

| 6.28 Timing Requirements - HDQ Interface        | 20              |

|-------------------------------------------------|-----------------|

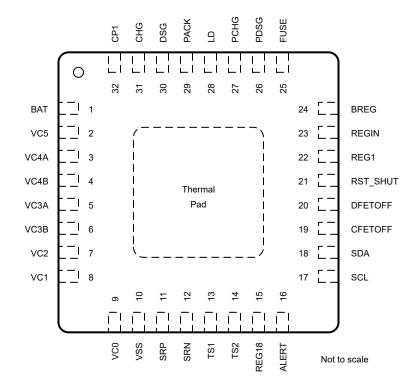

| 6.29 Interface Timing Diagrams                  | 20              |

| 6.30 Typical Characteristics                    |                 |

| 7 Detailed Description                          | 27              |

| 7.1 Overview                                    |                 |

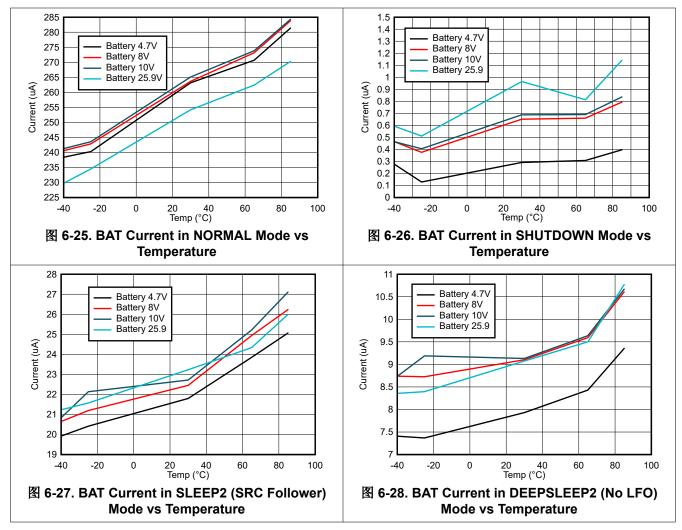

| 7.2 Functional Block Diagram                    | 27              |

| 7.3 Diagnostics                                 | 28              |

| 7.4 Device Configuration                        | <mark>28</mark> |

| 7.5 Measurement Subsystem                       |                 |

| 7.6 Primary and Secondary Protection Subsystems |                 |

| 7.7 Device Hardware Features                    |                 |

| 7.8 Device Functional Modes                     |                 |

| 7.9 Serial Communications Interface             |                 |

| 7.10 Cell Balancing                             |                 |

| 8 Application and Implementation                |                 |

| 8.1 Application Information                     |                 |

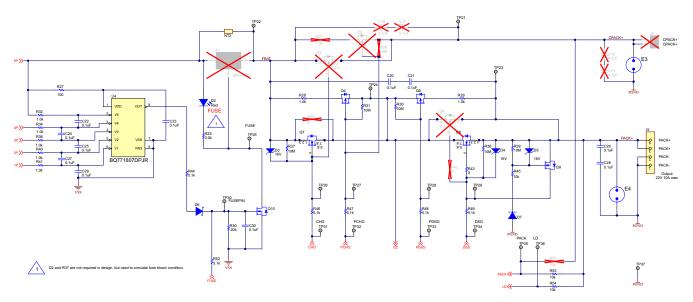

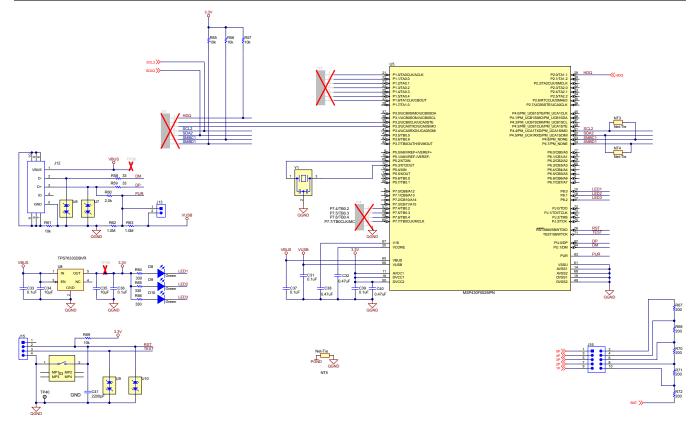

| 8.2 Typical Applications                        |                 |

| 8.3 Random Cell Connection Support              |                 |

| 8.4 Startup Timing                              |                 |

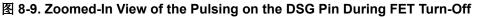

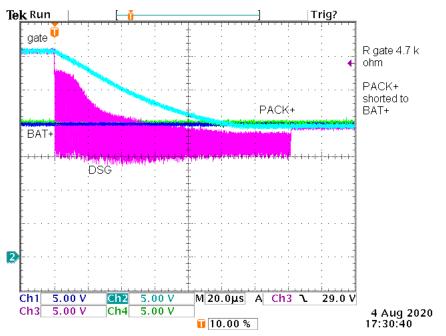

| 8.5 FET Driver Turn-Off                         |                 |

| 8.6 Unused Pins                                 | 62              |

| 9 Power Supply Requirements                     |                 |

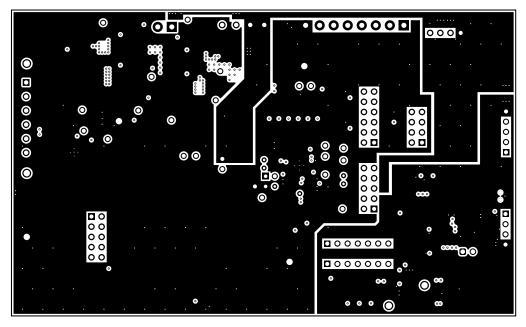

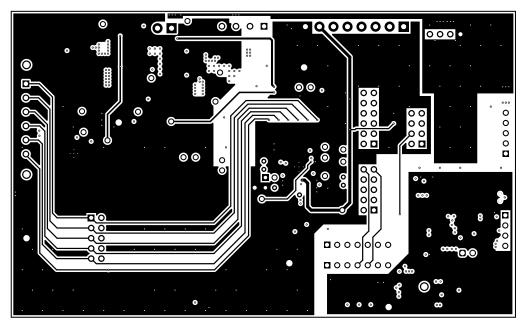

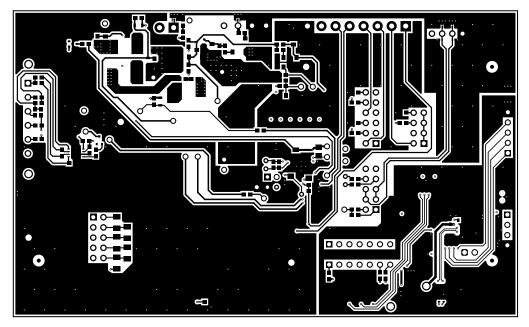

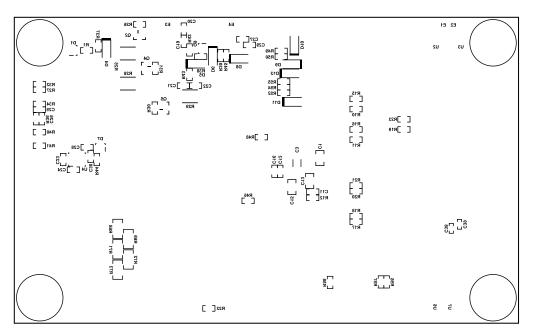

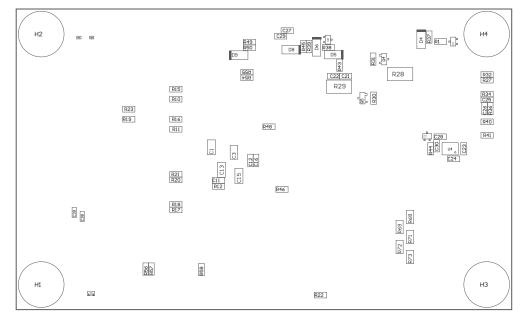

| 10 Layout                                       |                 |

| 10.1 Layout Guidelines                          |                 |

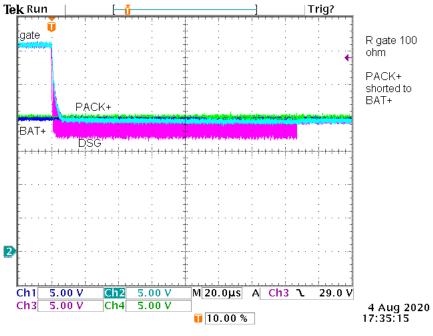

| 10.2 Layout Example                             |                 |

| 11 Device and Documentation Support             |                 |

| 11.1 第三方产品免责声明                                  |                 |

| 11.2 Documentation Support                      |                 |

| 11.3 Trademarks                                 |                 |

| 11.4 静电放电警告                                     |                 |

| 11.5 术语表                                        |                 |

| 12 Revision History                             |                 |

| 13 Mechanical, Packaging, Orderable Information | <mark>68</mark> |

### **4 Device Comparison Table**

| BQ76922 Device Family                                             |                  |   |                      |  |  |  |

|-------------------------------------------------------------------|------------------|---|----------------------|--|--|--|

| PART NUMBER Communications Interface CRC Enabled REG1 LDO Default |                  |   |                      |  |  |  |

| BQ76922                                                           | l <sup>2</sup> C | Ν | Enabled, set to 3.3V |  |  |  |

# **5** Pin Configuration and Functions

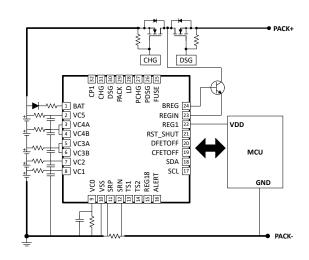

### 图 5-1. Pinout Diagram (top)

#### 表 5-1. Pin Functions

|     | PIN  | - I/O | ТҮРЕ | DESCRIPTION                                                                                                                                                                                                                            |  |

|-----|------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO. | NAME |       | 1175 | DESCRIPTION                                                                                                                                                                                                                            |  |

| 1   | BAT  | I     | Р    | Primary power supply input pin                                                                                                                                                                                                         |  |

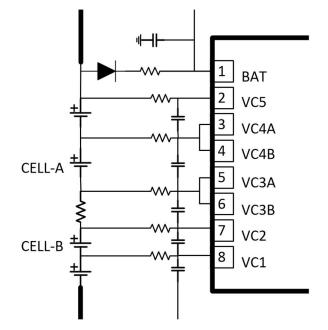

| 2   | VC5  | I     | IA   | Sense voltage input pin for the fifth cell from bottom of stack, balance current input for fifth cell from bottom of stack, and top-of-stack measurement point                                                                         |  |

| 3   | VC4A | I     | IA   | Sense voltage input pin for the fourth cell from bottom of stack, balance current input for fourth cell from bottom of stack, and return balance current for fifth cell from bottom of stack. Pins 3 and 4 must be shorted on the PCB. |  |

| 4   | VC4B | I     | IA   | Sense voltage input pin for the fourth cell from bottom of stack, balance current input for fourth cell from bottom of stack, and return balance current for fifth cell from bottom of stack. Pins 3 and 4 must be shorted on the PCB. |  |

| 5   | VC3A | I     | IA   | Sense voltage input pin for the third cell from bottom of stack, balance current input for third cell from bottom of stack, and return balance current for fourth cell from bottom of stack. Pins 5 and 6 must be shorted on the PCB.  |  |

# 表 5-1. Pin Functions(续)

|     |          | TYPE | DESCRIPTION |                                                                                                                                                                                                                                                   |

|-----|----------|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME     |      | ITPE        | DESCRIPTION                                                                                                                                                                                                                                       |

| 6   | VC3B     | I    | IA          | Sense voltage input pin for the third cell from bottom of stack, balance current input for third cell from bottom of stack, and return balance current for fourth cell from bottom of stack. Pins 5 and 6 must be shorted on the PCB.             |

| 7   | VC2      | I    | IA          | Sense voltage input pin for the second cell from bottom of stack, balance current input for second cell from bottom of stack, and return balance current for third cell from bottom of stack                                                      |

| 8   | VC1      | I    | IA          | Sense voltage input pin for the first cell from bottom of stack, balance current input for first cell from bottom of stack, and return balance current for second cell from bottom of stack                                                       |

| 9   | VC0      | I    | IA          | Sense voltage input pin for the negative terminal of the first cell from bottom of stack, and return balance current for first cell from bottom of stack                                                                                          |

| 10  | VSS      | —    | Р           | Device ground                                                                                                                                                                                                                                     |

| 11  | SRP      | I    | IA          | Analog input pin connected to the internal coulomb counter peripheral for integrating a small voltage between SRP and SRN, where SRP is the top of the sense resistor. A charging current generates a positive voltage at SRP relative to SRN.    |

| 12  | SRN      | I    | IA          | Analog input pin connected to the internal coulomb counter peripheral for integrating a small voltage between SRP and SRN, where SRN is the bottom of the sense resistor. A charging current generates a positive voltage at SRP relative to SRN. |

| 13  | TS1      | I/O  | OD, I/OA    | Thermistor input, or general-purpose ADC input                                                                                                                                                                                                    |

| 14  | TS2      | I/O  | OD, I/OA    | Thermistor input and functions as wakeup from SHUTDOWN, or general-purpose ADC input                                                                                                                                                              |

| 15  | REG18    | 0    | Р           | Internal 1.8-V LDO output (only for internal use)                                                                                                                                                                                                 |

| 16  | ALERT    | I    | I/OD, I/OA  | Multifunction pin, can be ALERT output, HDQ I/O, thermistor input, general-purpose ADC input, or general-purpose digital output                                                                                                                   |

| 17  | SCL      | I/O  | I/OD        | I <sup>2</sup> C clock                                                                                                                                                                                                                            |

| 18  | SDA      | I/O  | I/OD        | I <sup>2</sup> C data                                                                                                                                                                                                                             |

| 19  | CFETOFF  | I/O  | I/OD, I/OA  | Multifunction pin, can be CFETOFF, thermistor input, general-purpose ADC input, or general-purpose digital output                                                                                                                                 |

| 20  | DFETOFF  | I/O  | I/OD, I/OA  | Multifunction pin, can be DFETOFF or BOTHOFF, thermistor input, general-purpose ADC input, or general-purpose digital output                                                                                                                      |

| 21  | RST_SHUT | I    | ID          | Digital input pin for reset or shutdown                                                                                                                                                                                                           |

| 22  | REG1     | 0    | Р           | LDO (REG1) output, which can be programmed for 1.8 V, 2.5 V, 3.0 V, 3.3 V, or 5.0 V                                                                                                                                                               |

| 23  | REGIN    | 1    | IA          | Input pin for REG1 LDO                                                                                                                                                                                                                            |

| 24  | BREG     | 0    | OA          | Base control pin for external preregulator transistor                                                                                                                                                                                             |

| 25  | FUSE     | I/O  | I/OA        | Fuse drive                                                                                                                                                                                                                                        |

| 26  | PDSG     | 0    | OA          | Predischarge PFET control                                                                                                                                                                                                                         |

| 27  | PCHG     | 0    | OA          | Precharge PFET control                                                                                                                                                                                                                            |

| 28  | LD       | I/O  | I/OA        | Load detect pin                                                                                                                                                                                                                                   |

| 29  | PACK     | I    | IA          | Pack sense input pin                                                                                                                                                                                                                              |

| 30  | DSG      | 0    | OA          | NMOS Discharge FET drive output pin                                                                                                                                                                                                               |

| 31  | CHG      | 0    | OA          | NMOS Charge FET drive output pin                                                                                                                                                                                                                  |

| 32  | CP1      | I/O  | I/OA        | Charge pump capacitor                                                                                                                                                                                                                             |

# **6** Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

| DESCRIPTION                          | PINS                                                                                      | MIN                                                                             | MAX                                                                              | UNIT |

|--------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------|

| Supply voltage range                 | BAT                                                                                       | VSS - 0.3                                                                       | VSS+60                                                                           | V    |

| nput voltage range, V <sub>IN</sub>  | PACK, LD                                                                                  | VSS - 0.3                                                                       | VSS+60                                                                           | V    |

| Input voltage range, V <sub>IN</sub> | PACK, PCHG, PDSG, LD                                                                      | the maximum of $V_{BAT}$ <sup>-</sup> 10 or $V_{LD}$ <sup>-</sup> 10            | VSS+60                                                                           | V    |

| Input voltage range, V <sub>IN</sub> | REGIN                                                                                     | the maximum<br>of VSS <sup>–</sup> 0.3<br>or V <sub>BREG</sub> <sup>–</sup> 5.5 | the minimum<br>of VSS+6 or<br>V <sub>BAT</sub> +0.3 or<br>V <sub>BREG</sub> +0.3 | V    |

| input voltage range, V <sub>IN</sub> | FUSE <sup>(2)</sup>                                                                       | VSS - 0.3                                                                       | the minimum<br>of VSS+20 or<br>V <sub>BAT</sub> +0.3                             | V    |

| Input voltage range, V <sub>IN</sub> | BREG                                                                                      | the maximum<br>of VSS - 0.3<br>or V <sub>REGIN</sub> -<br>0.3                   | V <sub>REGIN</sub> +5.5                                                          | V    |

| Input voltage range, V <sub>IN</sub> | REG1                                                                                      | VSS - 0.3                                                                       | minimum of<br>VSS+6<br>or V <sub>REGIN</sub> +0.3                                | V    |

| Input voltage range, V <sub>IN</sub> | ALERT, SCL, SDA, CFETOFF, DFETOFF, RST_SHUT                                               | VSS - 0.3                                                                       | VSS+6                                                                            | V    |

| nput voltage range, V <sub>IN</sub>  | TS1, TS2, ALERT, CFETOFF, DFETOFF, (when used as thermistor or general purpose ADC input) | VSS - 0.3                                                                       | V <sub>REG18</sub> + 0.3                                                         | V    |

| nput voltage range, V <sub>IN</sub>  | SRP, SRN                                                                                  | VSS - 0.3                                                                       | V <sub>REG18</sub> + 0.3                                                         | V    |

| nput voltage range, V <sub>IN</sub>  | VC5                                                                                       | maximum of<br>VSS - 0.3 and<br>VC4A - 0.3                                       | VSS+60                                                                           | V    |

| Input voltage range, V <sub>IN</sub> | VC4A                                                                                      | maximum of<br>VSS - 0.3 and<br>VC4B - 0.3                                       | VSS+60                                                                           | V    |

| Input voltage range, V <sub>IN</sub> | VC4B                                                                                      | maximum of<br>VSS - 0.3 and<br>VC3A - 0.3                                       | VSS+60                                                                           | V    |

| Input voltage range, V <sub>IN</sub> | VC3A                                                                                      | maximum of<br>VSS - 0.3 and<br>VC3B - 0.3                                       | VSS+60                                                                           | V    |

| Input voltage range, V <sub>IN</sub> | VC3B                                                                                      | maximum of<br>VSS - 0.3 and<br>VC2 - 0.3                                        | VSS+60                                                                           | V    |

| Input voltage range, V <sub>IN</sub> | VC2                                                                                       | maximum of<br>VSS - 0.3 and<br>VC1 - 0.3                                        | VSS+60                                                                           | V    |

| Input voltage range, V <sub>IN</sub> | VC1                                                                                       | maximum of<br>VSS - 0.3 and<br>VC0 - 0.3                                        | VSS+60                                                                           | V    |

| nput voltage range, V <sub>IN</sub>  | VC0                                                                                       | VSS - 0.3                                                                       | VSS+6                                                                            | V    |

| Dutput voltage range, V <sub>O</sub> | CP1                                                                                       | V <sub>BAT</sub> - 0.3                                                          | the minimum<br>of VSS+60 or<br>V <sub>BAT</sub> +15                              | V    |

| Output voltage range, V <sub>O</sub> | СНС                                                                                       | VSS - 0.3                                                                       | VSS+60                                                                           | V    |

## 6.1 Absolute Maximum Ratings (续)

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

| DESCRIPTION                                          | PINS                                                                                                | MIN       | MAX    | UNIT |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------|--------|------|

| Output voltage range, V <sub>O</sub>                 | DSG                                                                                                 | VSS - 0.3 | VSS+60 | V    |

| Output voltage range, V <sub>O</sub>                 | REG1, TS2 (for wakeup function), ALERT, CFETOFF, DFETOFF, when configured to drive a digital output | VSS - 0.3 | VSS+6  | V    |

| Output voltage range, V <sub>O</sub>                 | REG18                                                                                               | VSS - 0.3 | VSS+2  | V    |

| Maximum cell balancing current through a single cell | VC0 - VC5                                                                                           |           | 100    | mA   |

| Maximum VSS current, I <sub>SS</sub>                 |                                                                                                     |           | 75     | mA   |

| Functional temperature, T <sub>FUNC</sub>            |                                                                                                     | - 40      | 85     | °C   |

| Junction temperature, T <sub>J</sub>                 |                                                                                                     | - 55      | 150    | °C   |

| Storage temperature, T <sub>STG</sub>                |                                                                                                     | - 55      | 150    | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) The current allowed to flow into the FUSE pin must be limited (such as by using external series resistance) to 2 mA or less.

(3) When the ALERT, CFETOFF, or DFETOFF pins are selected for thermistor input or general purpose ADC – input, their voltage is limited to V<sub>REG18</sub> + 0.3 V. These pins can accept up to 6 V when configured for other uses, such as a digital input.

## 6.2 ESD Ratings

|                    |                         |                                                                                          | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>          | ±1000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±250  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

Typical values stated where  $T_A = 25^{\circ}C$  and  $V_{BAT} = 18.5$  V, min/max values stated where  $T_A = -40^{\circ}C$  to  $85^{\circ}C$  and  $V_{BAT} = 4.7$  V to 27.5 V (unless otherwise noted)

|                        | PARAMETER                                  | TEST CONDITIONS                                                                                                            | MIN  | TYP  | MAX  | UNIT |

|------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>BAT</sub>       | Supply voltage                             | Voltage on BAT pin (normal operation)                                                                                      | 4.7  |      | 27.5 | V    |

| V <sub>BAT</sub>       | Supply voltage <sup>(3)</sup>              | Voltage on BAT pin (OTP programming)                                                                                       | 10   |      | 12   | V    |

| T <sub>OTP</sub>       | OTP programming temperature <sup>(3)</sup> |                                                                                                                            | - 40 |      | 45   | °C   |

| V <sub>PORA</sub>      | Power-on reset                             | Rising threshold on BAT                                                                                                    | 3    |      | 4    | V    |

| V <sub>PORA_HYS</sub>  | Power-on reset hysteresis                  | Device shuts down when BAT <<br>V <sub>PORA</sub> - V <sub>PORA_HYS</sub>                                                  |      | 225  |      | mV   |

| V <sub>WAKEONLD</sub>  | Wake on LD voltage                         | Rising edge on LD, with BAT already in valid range                                                                         | 0.8  | 1.45 | 2.25 | V    |

| V <sub>WAKEONTS2</sub> | Wake on TS2 voltage                        | Falling edge on TS2, with BAT<br>already in valid range. TS2 will be<br>weakly driven with a 5 V level during<br>shutdown. | 0.7  |      | 1.1  | V    |

| V <sub>IN</sub>        | Input voltage range <sup>(3)</sup>         | PACK, LD                                                                                                                   | 0    |      | 27.5 | V    |

## 6.3 Recommended Operating Conditions (续)

Typical values stated where  $T_A = 25^{\circ}C$  and  $V_{BAT} = 18.5$  V, min/max values stated where  $T_A = -40^{\circ}C$  to  $85^{\circ}C$  and  $V_{BAT} = 4.7$  V to 27.5 V (unless otherwise noted)

|                         | PARAMETER                                                        | TEST CONDITIONS                                                                                                                                           | MIN                                                                                                             | TYP MAX                                                                | UNIT |

|-------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------|

| V <sub>IN</sub>         | Input voltage range <sup>(3)</sup>                               | PCHG, PDSG                                                                                                                                                | the<br>maximum<br>of V <sub>BAT</sub> <sup>–</sup> 9<br>or V <sub>LD</sub> <sup>–</sup> 9                       | 27.5                                                                   | V    |

| V <sub>IN</sub>         | Input voltage range <sup>(3)</sup>                               | REG1, RST_SHUT, ALERT, SCL,<br>SDA, CFETOFF, DFETOFF, except<br>when the pin is being used for<br>general purpose ADC input or<br>thermistor measurement. | 0                                                                                                               | 5.5                                                                    | V    |

| V <sub>IN</sub>         | Input voltage range <sup>(3)</sup>                               | TS1, TS2, CFETOFF, DFETOFF,<br>ALERT, when the pin is configured<br>for general purpose ADC input or<br>thermistor measurement.                           | 0                                                                                                               | V <sub>REG18</sub>                                                     | V    |

| V <sub>IN</sub>         | Input voltage range <sup>(5)</sup>                               | SRP, SRN, SRP-SRN (while measuring current)                                                                                                               | - 0.2                                                                                                           | 0.2                                                                    | V    |

| V <sub>IN</sub>         | Input voltage range <sup>(3)</sup>                               | SRP, SRN (without measuring current)                                                                                                                      | - 0.2                                                                                                           | 0.75                                                                   | V    |

| V <sub>IN</sub>         | Input voltage range <sup>(3) (4)</sup>                           | V <sub>VC(0)</sub>                                                                                                                                        | - 0.2                                                                                                           | 0.5                                                                    | V    |

| V <sub>IN</sub>         | Input voltage range <sup>(5)</sup>                               | $V_{VC(x),} 1 \leqslant x \leqslant 3$                                                                                                                    | maximum<br>of V <sub>VC(x - 1)</sub><br>- 0.2 or<br>VSS - 0.2                                                   | minimum<br>of V <sub>VC(x -</sub><br><sub>1)</sub> +5.5 or<br>VSS+27.5 | V    |

| V <sub>IN</sub>         | Input voltage range                                              | $V_{VC(x), x} \ge 4$                                                                                                                                      | $\begin{array}{c} \mbox{maximum} \\ \mbox{of } V_{VC(x - 1)} \\ \ - \ 0.2 \ \mbox{or} \\ VSS + 2.0 \end{array}$ | minimum<br>of V <sub>VC(x - 1)</sub><br>+ 5.5 or<br>VSS + 27.5         | V    |

| R <sub>C</sub>          | External cell input resistance <sup>(3)</sup> (6)                |                                                                                                                                                           | 20                                                                                                              | 100                                                                    | Ω    |

| R <sub>C</sub>          | External cell input<br>capacitance <sup>(3)</sup> <sup>(6)</sup> |                                                                                                                                                           | 0.1                                                                                                             | 0.22 1                                                                 | μF   |

| Vo                      | Output voltage range                                             | LD                                                                                                                                                        |                                                                                                                 | 27.5                                                                   | V    |

| Vo                      | Output voltage range <sup>(5)</sup>                              | CHG, DSG, CP1                                                                                                                                             |                                                                                                                 | 40                                                                     | V    |

| T <sub>OPR</sub>        | Operating temperature <sup>(5)</sup>                             |                                                                                                                                                           | - 40                                                                                                            | 85                                                                     | °C   |

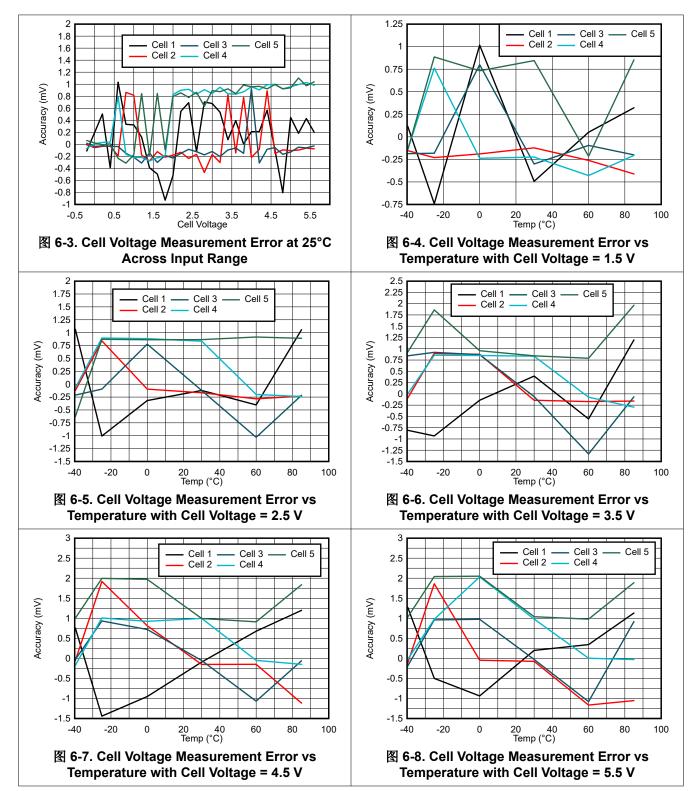

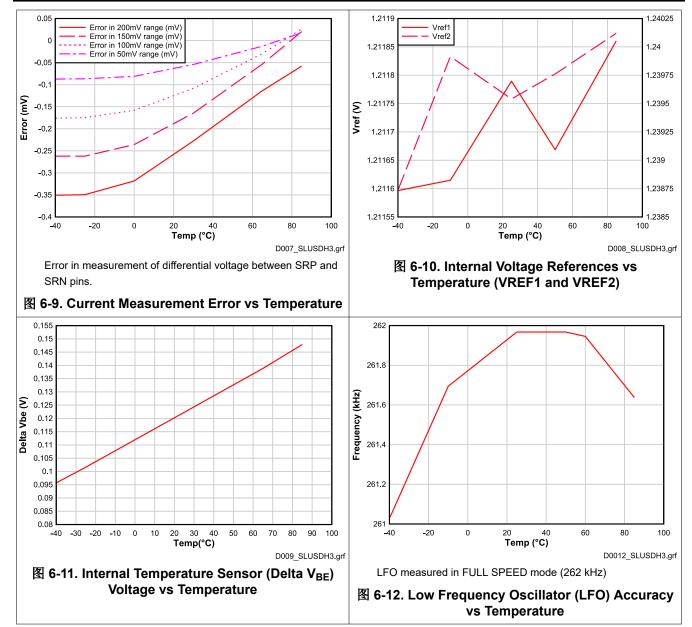

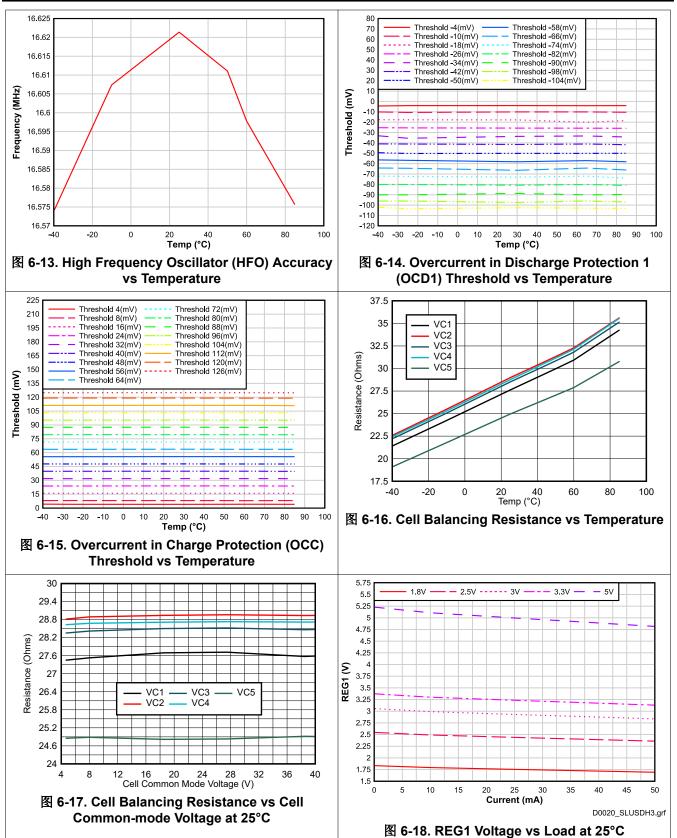

| V <sub>CELL(ACC)</sub>  | Cell voltage measurement accuracy                                | 2 V < V <sub>VC(x)</sub> - V <sub>VC(x-1)</sub> < 5 V, T <sub>A</sub> = 25°C, 1 $\leq$ x $\leq$ 5 <sup>(1)</sup> (2)                                      | - 5                                                                                                             | 5                                                                      | mV   |

| V <sub>CELL(ACC)</sub>  | Cell voltage measurement accuracy <sup>(5)</sup>                 | 2 V < V <sub>VC(x)</sub> - V <sub>VC(x-1)</sub> < 5 V, T <sub>A</sub> = 0°C to 60°C, 1 $\leq$ x $\leq$ 5 <sup>(1)</sup> (2)                               | - 10                                                                                                            | 10                                                                     | mV   |

| V <sub>CELL(ACC)</sub>  | Cell voltage measurement accuracy <sup>(5)</sup>                 | $^-$ 0.2 V < V_{VC(x)} - V_{VC(x-1)} < 5.5 V, T_A = -40°C to 85°C, 1 $\leqslant$ x $\leqslant$ 5 $^{(1)}$ $^{(2)}$                                        | - 15                                                                                                            | 15                                                                     | mV   |

| V <sub>STACK(ACC)</sub> | Stack voltage (VC5 - VSS) measurement accuracy <sup>(5)</sup>    | 0 V < V_{VC5} - V_{VSS} \leqslant 27.5 V, T_A = -40°C to 85°C^{(1)}                                                                                       | - 0.5                                                                                                           | 0.5                                                                    | V    |

| V <sub>PACK(ACC)</sub>  | PACK pin voltage measurement accuracy <sup>(5)</sup>             | 0 V < V <sub>PACK</sub> - V <sub>VSS</sub> $\leqslant$ 27.5 V, T <sub>A</sub> = -40°C to 85°C <sup>(1)</sup>                                              | - 0.5                                                                                                           | 0.5                                                                    | V    |

| V <sub>LD(ACC)</sub>    | LD pin voltage measurement accuracy <sup>(5)</sup>               | 0 V < V <sub>LD</sub> - V <sub>VSS</sub> $\leqslant$ 27.5 V, T <sub>A</sub> = -40°C to 85°C <sup>(1)</sup>                                                | - 0.5                                                                                                           | 0.5                                                                    | V    |

(1) Cell voltage accuracy is specified after completion of board offset calibration

(2) While in SLEEP mode, it is important that the cell 1 voltage measurement be validated before being considered valid. For further information and details, see Cell 1 Voltage Validation during SLEEP Mode.

(3) Specified by design

(4) Voltage on VC0 can extend higher (limited by absolute maximum specification) during cell balancing.

(5) Specified by characterization

(6) Values may need to be optimized during system design and evaluation for best performance

### 6.4 Thermal Information BQ76922

|                        |                                              | BQ76922   |      |

|------------------------|----------------------------------------------|-----------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RSN (QFN) | UNIT |

|                        |                                              | 32 PINS   |      |

| R <sub>0 JA</sub>      | Junction-to-ambient thermal resistance       | 33.2      | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 25.1      | °C/W |

| R <sub>0</sub> JB      | Junction-to-board thermal resistance         | 12.4      | °C/W |

| Ψ <sub>JT</sub>        | Junction-to-top characterization parameter   | 0.2       | °C/W |

| Ψ <sub>JB</sub>        | Junction-to-board characterization parameter | 12.4      | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 4         | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.5 Supply Current

Typical values stated where  $T_A = 25^{\circ}C$  and  $V_{BAT} = 18.5$  V, min/max values stated where  $T_A = -40^{\circ}C$  to  $85^{\circ}C$  and  $V_{BAT} = 4.7$  V to 27.5 V (unless otherwise noted)

|                          | PARAMETER      | TEST CONDITIONS                                                                                                                                                                                                                        | MIN | TYP  | MAX | UNIT |

|--------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| INORMAL                  | Normal Mode    | Regular measurements and protections active,<br>REG1 = 3.3 V with no load, CHG = ON in 11 V<br>overdrive mode, DSG = ON in 11 V overdrive<br>mode, <b>Settings:Configuration:Power</b><br><b>Config[FASTADC]</b> = 0, no communication |     | 252  |     | μA   |

| ISLEEP_1                 | SLEEP Mode     | Periodic protections and monitoring, no pack<br>current, REG1 = OFF, CHG = OFF, DSG = ON in<br>11 V overdrive mode, no communication,<br><b>Power:Sleep:Voltage Time</b> = 5 s                                                         |     | 38   |     | μA   |

| I <sub>SLEEP_2</sub>     | SLEEP Mode     | Periodic protections and monitoring, no pack<br>current, REG1 = OFF, CHG = OFF, DSG =<br>source follower mode, no communication,<br><b>Power:Sleep:Voltage Time</b> = 5 s                                                              |     | 23   |     | μA   |

| IDEEPSLEEP_1             | DEEPSLEEP Mode | No monitoring or protections, REG1 = 3.3 V with no load, LFO = ON, no communication                                                                                                                                                    |     | 10.6 |     | μA   |

| I <sub>DEEPSLEEP_2</sub> | DEEPSLEEP Mode | No monitoring or protections, REG1 = 3.3 V with<br>no load, LFO = OFF, no communication                                                                                                                                                |     | 9.1  |     | μΑ   |

| I <sub>SHUTDOWN</sub>    | SHUTDOWN Mode  | All blocks powered down, with the exception of<br>the TS2 wakeup circuit, no monitoring or<br>protections, no communication                                                                                                            |     | 1    | 3.1 | μA   |

### 6.6 Digital I/O

Typical values stated where  $T_A = 25^{\circ}C$  and  $V_{BAT} = 18.5$  V, min/max values stated where  $T_A = -40^{\circ}C$  to  $85^{\circ}C$  and  $V_{BAT} = 4.7$  V to 27.5 V (unless otherwise noted)

|                 | PARAMETER                            | TEST CONDITIONS                                                    | MIN                          | TYP MAX                      | UNIT |

|-----------------|--------------------------------------|--------------------------------------------------------------------|------------------------------|------------------------------|------|

| V <sub>IH</sub> | High-level input                     | ALERT (configured as HDQ), SCL, SDA,<br>CFETOFF, DFETOFF, RST_SHUT | 0.67 x<br>V <sub>REG18</sub> | 5.5                          | V    |

| V <sub>IL</sub> | Low-level input                      | ALERT (configured as HDQ), SCL, SDA,<br>CFETOFF, DFETOFF, RST_SHUT |                              | 0.33 x<br>V <sub>REG18</sub> | V    |

| V <sub>OH</sub> | Output voltage high, TS2             | TS2 during SHUTDOWN mode, V <sub>BAT</sub> > 6<br>V                | 4.5                          | 6                            | V    |

| V <sub>OH</sub> | Output voltage high, TS2 low voltage | TS2 during SHUTDOWN mode, 4.7 V $\leqslant$ V_BAT $\leqslant$ 6 V  | 3                            | 6                            | V    |

Copyright © 2024 Texas Instruments Incorporated

# 6.6 Digital I/O(续)

Typical values stated where  $T_A = 25^{\circ}C$  and  $V_{BAT} = 18.5$  V, min/max values stated where  $T_A = -40^{\circ}C$  to  $85^{\circ}C$  and  $V_{BAT} = 4.7$  V to 27.5 V (unless otherwise noted)

| PARAMETER                        | TEST CONDITIONS                                                                                                                                                                                     | MIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ТҮР                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | UNIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output voltage high, 5 V case    | ALERT, CFETOFF (configured as GPO),<br>DFETOFF (configured as GPO), pins<br>driving from REG1, $V_{REG1}$ set to 5 V<br>nominal setting, $V_{BAT}$ > 8 V, $I_{OH}$ = 5.0 mA,<br>10 pF load          | 0.9 x<br>V <sub>REG1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V <sub>REG1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Output voltage low, 5 V case     | ALERT, SCL, SDA, CFETOFF<br>(configured as GPO), DFETOFF<br>(configured as GPO), pins driving from<br>REG1, $V_{REG1}$ set to 5 V nominal setting,<br>$V_{BAT} > 8$ V, $I_{OL} = -5$ mA, 10 pF load |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

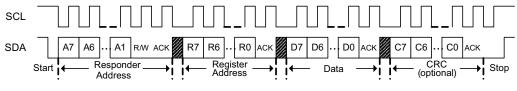

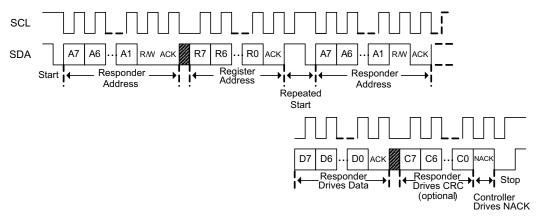

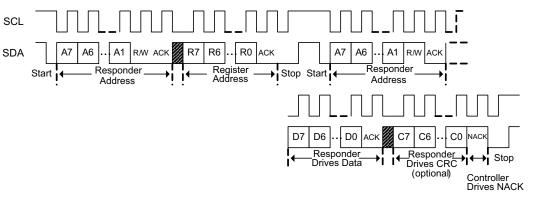

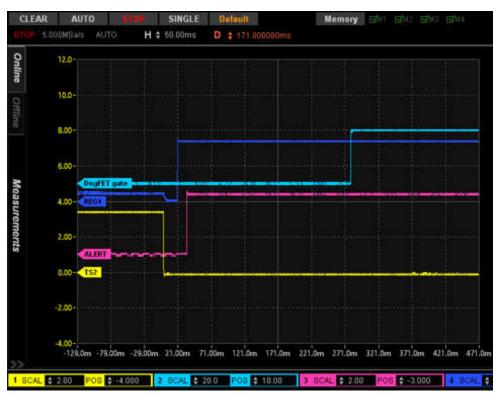

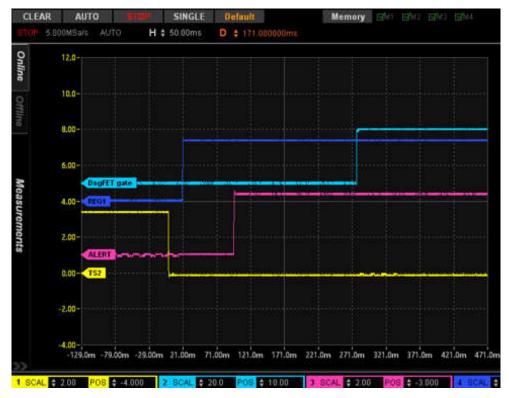

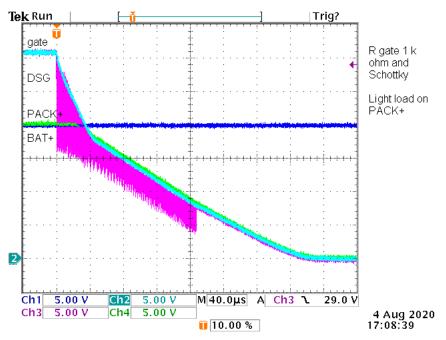

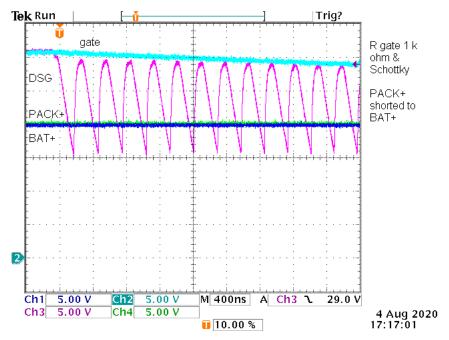

| Output weak high resistance      | TS2 during SHUTDOWN mode                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | kΩ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |