bq500211A

ZHCSAO7B - DECEMBER 2012-REVISED JUNE 2016

# bq500211A 符合 WPC1.1 标准的 5V 无线电源发射器管理器

Not Recommended for New Designs

## 1 特性

- 无线电源传输的智能控制

- 符合无线电源联盟 (WPC) 类型 A5 和类型 A11 发送器规范的 5V 运行

- WPC1.1 兼容,包括外来物体检测 (FOD)

- 增强型寄生金属检测 (PMOD) 确保了安全性

- 针对 USB 和受限源运行的 Dynamic Power Limiting™

- 数字解调减少了组件

- 充电状态和故障状态的发光二极管 (LED) 指示

## 2 应用范围

- 与 WPC 1.1 兼容的无线充电器用于:

- 经 Qi 认证的智能手机和其它手持设备

- 密封封装器件和工具

- 汽车和其它车辆

- 桌面充电接口

- TI 无线充电解决方案的更多信息,请见 www.ti.com.cn/wirelesspower

## 3 说明

bq500211A 是第二代数字无线电源控制器,此控制器集成了控制到一个单 WPC 兼容接收器的无线电源传输所需的全部功能。它与 WPC1.1 标准兼容并设计用于5V 系统,被用作一个 WPC 类型 A5 发送器(具有一个磁定位导向装置)或者作为一个 WPC 类型 A11 发送器(无磁导向装置)。bq500211A询问周围环境以寻找将被供电的 WPC 兼容器件,安全使用器件,接收来自被供电器件的数据包通信并管理电源传输。

bq500211A 特有的 Dynamic Power Limiting<sup>TM</sup>(DPL) 功能可最大限度地提升无线电源应用的灵活性。通过无缝优化受限输入电源上可用功率的使用,DPL 提高了用户体验。通过持续监测已建立的电源传输的效率,bq500211A 支持外来物体检测 (FOD) 和寄生金属检测 (PMOD),从而防止由于在无线电源传输路径上错误放置金属物体而导致的电源丢失。如果在电源传输期间发生任何异常情况,bq500211A 对其进行处理并提供指示器输出。综合状态和故障监视 特性 可实现一款稳健耐用的设计方案。

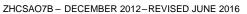

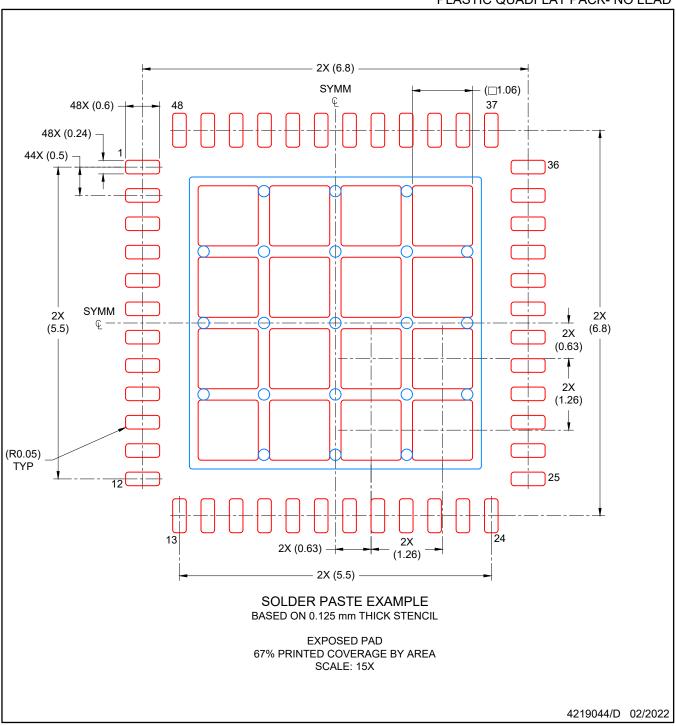

bq500211A 采用 48 引脚, 7mm x 7mm 四方扁平无引线 (QFN) 封装,运行温度范围介于 -40℃ 至 110℃ 之间。

器件信息(1)

| 器件型号      | 封装        | 封装尺寸 (标称值)      |  |  |

|-----------|-----------|-----------------|--|--|

| bq500211A | VQFN (48) | 7.00mm x 7.00mm |  |  |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

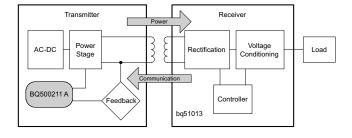

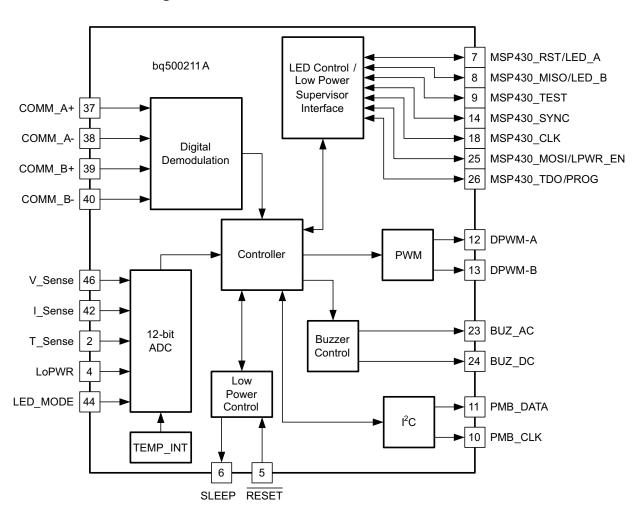

#### 功能图

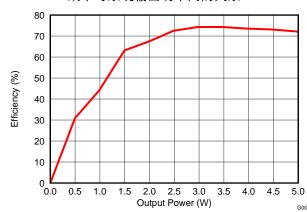

### 效率与系统输出功率间的关系

A

## bq500211A

Changes from Original (December 2012) to Revision A

www.ti.com.cn

Page

|                            |                                                                                                            | 目表     | 录            |                                                      |  |

|----------------------------|------------------------------------------------------------------------------------------------------------|--------|--------------|------------------------------------------------------|--|

| 1<br>2<br>3<br>4<br>5<br>6 | 特性                                                                                                         |        | 8<br>9<br>10 | 7.2 Functional Block Diagram 7.3 Feature Description |  |

| ha<br>i                    | 修订历史记录 nges from Revision A (September 2013) to F 己添加 <i>ESD</i> 额定值表,特性 描述部分,器件功<br>铛支持部分以及机械、封装和可订购信息部分… | 能模式,应用 |              |                                                      |  |

器件状态目前为 NRND。......1

## 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN      |    | 1/0 | DESCRIPTION                                                                                                                          |  |  |  |

|----------|----|-----|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME NO. |    | 1/0 | DESCRIPTION                                                                                                                          |  |  |  |

| AIN3     | 3  | I   | This pin can be either connected to GND or left open. Connecting to GND can improve layout grounding.                                |  |  |  |

| AIN5     | 1  | 1   | This pin can be either connected to GND or left open. Connecting to GND can improve layout grounding.                                |  |  |  |

| AIN7     | 45 | I   | This pin can be either connected to GND or left open. Connecting to GND can improve layout grounding.                                |  |  |  |

| BPCAP    | 35 | _   | Bypass capacitor for internal 1.8-V core regulator. Connect bypass capacitor to GND.                                                 |  |  |  |

| BUZ_AC   | 23 | 0   | AC Buzzer Output. Outputs a 400-ms, 4-kHz AC pulse when charging begins.                                                             |  |  |  |

| BUZ_DC   | 24 | 0   | DC Buzzer Output. Outputs a 400-ms DC pulse when charging begins. This could also be connected to an LED via 470- $\Omega$ resistor. |  |  |  |

| COMM_A+  | 37 | I   | Digital demodulation non-inverting input A, connect parallel to input B+.                                                            |  |  |  |

| COMM_A-  | 38 | I   | Digital demodulation inverting input A, connect parallel to input B                                                                  |  |  |  |

| COMM_B+  | 39 | I   | Digital demodulation non-inverting input B, connect parallel to input A+.                                                            |  |  |  |

| COMM_B-  | 40 | I   | Digital demodulation inverting input B, connect parallel to input A                                                                  |  |  |  |

| DOUT_RX  | 22 | I   | Leave this pin open.                                                                                                                 |  |  |  |

| DOUT_TX  | 21 | I   | Leave this pin open.                                                                                                                 |  |  |  |

| DOUT_2B  | 15 | 0   | Optional Logic Output 2B. Leave this pin open.                                                                                       |  |  |  |

| DPWM_A   | 12 | 0   | PWM Output A, controls one half of the full bridge in a phase-shifted full bridge. Switching deadtimes must be externally generated. |  |  |  |

# Pin Functions (continued)

| PIN              |     | 1/0 | DESCRIPTION                                                                                                                                     |  |  |  |  |

|------------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME             | NO. | I/O | DESCRIPTION                                                                                                                                     |  |  |  |  |

| DPWM_B           | 13  | 0   | PWM Output B, controls other half of the full bridge in a phase-shifted full bridge. Switching deadtimes must be externally generated.          |  |  |  |  |

| EPAD             | 49  | -   | Flood with copper GND plane and stitch vias to PCB internal GND plane.                                                                          |  |  |  |  |

| FOD              | 17  | 0   | FOD read pin. Leave open unless PMOD and FOD thresholds need to be different. It controls the FOD threshold resistor read at startup.           |  |  |  |  |

| GND              | 32  | _   | GND.                                                                                                                                            |  |  |  |  |

| GND              | 36  | _   | GND.                                                                                                                                            |  |  |  |  |

| GND              | 47  | _   | GND.                                                                                                                                            |  |  |  |  |

| I_SENSE          | 42  | I   | Transmitter input current, used for efficiency calculations. Use 20-m $\Omega$ sense resistor and A=50 gain current sense amplifier.            |  |  |  |  |

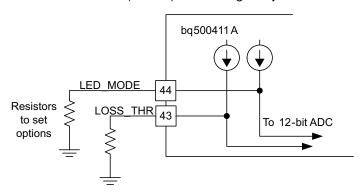

| LED_MODE         | 44  | I   | Input to select from 4 LED modes.                                                                                                               |  |  |  |  |

| LoPWR            | 4   | 1   | Dynamic Power Limiting <sup>™</sup> (DPL) control pin. To set power mode to 500 mA, pull to GND. For full-power operation pull to 3.3-V supply. |  |  |  |  |

| LOSS_THR         | 43  | I   | Input to program foreign and parasitic metal object detection threshold                                                                         |  |  |  |  |

| MSP_CLK          | 18  | I/O | Used for boot loading the MSP430 low power supervisor. If MSP430 is not used, leave t pin floating.                                             |  |  |  |  |

| MSP_MISO/LED_B   | 8   | I   | MSP – TMS, SPI-MISO, LED-B If external MSP430 is not used, connect to an LED via $470-\Omega$ resistor for status indication.                   |  |  |  |  |

| MSP_RST/LED_A    | 7   | 1   | MSP – Reset, LED-A If external MSP430 is not used, connect to an LED via 470- $\Omega$ resistor for status indication.                          |  |  |  |  |

| MSP_SYNC         | 14  | 0   | MSP SPI_SYNC, if external MSP430 is not used, leave this pin open.                                                                              |  |  |  |  |

| MSP_TDO/PROG     | 26  | I/O | MSP-TDO, MSP430 programmed indication.                                                                                                          |  |  |  |  |

| MSP_TEST         | 9   | I   | MSP – Test, If external MSP430 is not used, leave this pin open.                                                                                |  |  |  |  |

| MSP_MOSI/LPWR_EN | 25  | I/O | Low standby power supervisor enable. If low power is not needed, connect this to GND.                                                           |  |  |  |  |

| PMOD             | 16  | 0   | PMOD read pin. Leave open unless PMOD and FOD thresholds need to be different. It controls the PMOD threshold resistor read at startup.         |  |  |  |  |

| PMB_CLK          | 10  | I/O | 10-kΩ pull-up resistor to 3.3-V supply.                                                                                                         |  |  |  |  |

| PMB_DATA         | 11  | I/O | 10-kΩ pull-up resistor to 3.3-V supply.                                                                                                         |  |  |  |  |

| RESERVED         | 19  | 0   | Reserved, leave this pin open.                                                                                                                  |  |  |  |  |

| RESERVED         | 20  | I   | Reserved, connect to GND.                                                                                                                       |  |  |  |  |

| RESERVED         | 48  | I   | External Reference Voltage Input. Connect this input to GND.                                                                                    |  |  |  |  |

| RESERVED         | 27  | I/O | Reserved, leave this pin open.                                                                                                                  |  |  |  |  |

| RESERVED         | 28  | I/O | Reserved, leave this pin open.                                                                                                                  |  |  |  |  |

| RESERVED         | 29  | I/O | Reserved, leave this pin open.                                                                                                                  |  |  |  |  |

| RESERVED         | 30  | I/O | Reserved, leave this pin open.                                                                                                                  |  |  |  |  |

| RESERVED         | 31  | I/O | Reserved, connect 10-kΩ pull-down resistor to GND.                                                                                              |  |  |  |  |

| RESERVED         | 41  | 0   | Reserved, leave this pin open.                                                                                                                  |  |  |  |  |

| RESET            | 5   | I   | Device reset. Use a 10-k $\Omega$ to 100-k $\Omega$ pull-up resistor to the 3.3-V supply.                                                       |  |  |  |  |

| SLEEP            | 6   | 0   | Low-power mode output. Starts low-power ping cycle.                                                                                             |  |  |  |  |

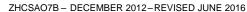

| T_SENSE          | 2   | 1   | Sensor Input. Device shuts down when below 1 V. If not used, keep above 1 V by connecting to the 3.3-V supply.                                  |  |  |  |  |

| V_SENSE          | 46  | I   | Transmitter input voltage, used for efficiency calculations. Use 76.8-k $\Omega$ to 10-k $\Omega$ divider to minimize quiescent current.        |  |  |  |  |

| V33A             | 34  | _   | Analog 3.3-V Supply. This pin can be derived from V33D supply, decouple with 10- $\Omega$ resistor and additional bypass capacitors             |  |  |  |  |

| V33D             | 33  | _   | Digital core 3.3-V supply. Be sure to decouple with bypass capacitors as close to the part as possible.                                         |  |  |  |  |

## 6 Specifications

# 6.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                      | MIN  | MAX | UNIT |

|--------------------------------------|------|-----|------|

| Voltage applied at V33D to GND       | -0.3 | 3.6 |      |

| Voltage applied at V33A to GND       | -0.3 | 3.6 | V    |

| Voltage applied to any pin (2)       | -0.3 | 3.6 |      |

| Storage temperature,T <sub>STG</sub> | -40  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages referenced to GND.

## 6.2 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                             | MIN | NOM | MAX | UNIT |

|----------------|---------------------------------------------|-----|-----|-----|------|

| V              | Supply voltage during operation, V33D, V33A | 3.0 | 3.3 | 3.6 | V    |

| T <sub>A</sub> | Operating free-air temperature range        | -40 |     | 110 | °C   |

| $T_{J}$        | Junction temperature                        |     |     | 110 | C    |

### 6.3 Thermal Information

|                       |                                              | bq500211A  |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RGZ (VQFN) | UNIT |

|                       |                                              | 48 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 28.4       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 14.2       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 5.4        | °C/W |

| ₽ <sub>ЈТ</sub>       | Junction-to-top characterization parameter   | 0.2        | °C/W |

| ₽ <sub>ЈВ</sub>       | Junction-to-board characterization parameter | 5.3        | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.4        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 6.4 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                         | PARAMETER                                          | TEST CONDITIONS                                    | MIN            | TYP | MAX             | UNIT  |

|-------------------------|----------------------------------------------------|----------------------------------------------------|----------------|-----|-----------------|-------|

| SUPPLY CURF             | RENT                                               |                                                    |                |     |                 |       |

| I <sub>V33A</sub>       | _                                                  | V33A = 3.3 V                                       |                | 8   | 15              |       |

| I <sub>V33D</sub>       | Supply current                                     | V33D = 3.3 V                                       |                | 44  | 55              | mA    |

| I <sub>TOTAL</sub>      |                                                    | V33D = V33A = 3.3 V                                |                | 52  | 60              |       |

| INTERNAL RE             | GULATOR CONTROLLER INPUTS/OUTPUTS                  |                                                    |                |     |                 |       |

| V33                     | 3.3-V linear regulator                             | Emitter of NPN transistor                          | 3.25           | 3.3 | 3.6             | V     |

| V33FB                   | 3.3-V linear regulator feedback                    |                                                    |                | 4   | 4.6             | · ·   |

| I <sub>V33FB</sub>      | Series pass base drive                             | V <sub>IN</sub> = 12 V; current into V33FB pin     |                | 10  |                 | mA    |

| Beta                    | Series NPN pass device                             |                                                    | 40             |     |                 |       |

| EXTERNALLY              | SUPPLIED 3.3 V POWER                               |                                                    |                |     |                 |       |

| V33D                    | Digital 3.3-V power                                | T <sub>A</sub> = 25°C                              | 3              |     | 3.6             | V     |

| V33A                    | Analog 3.3-V power                                 | T <sub>A</sub> = 25°C                              | 3              |     | 3.6             | v     |

| V33Slew                 | V33 slew rate                                      | V33 slew rate between 2.3 V and 2.9 V, V33A = V33D | 0.25           |     |                 | V/ms  |

| DIGITAL DEMO            | ODULATION INPUTS COMM_A+, COMM_A-, CO              | DMM_B+, COMM_B-                                    |                |     |                 |       |

| V <sub>CM</sub>         | Common mode voltage each pin                       |                                                    | -0.15          |     | 1.631           | V     |

| COMM+,<br>COMM-         | Modulation voltage digital resolution              |                                                    |                | 1   |                 | mV    |

| R <sub>EA</sub>         | Input impedance                                    | Ground reference                                   | 0.5            | 1.5 | 3               | ΜΩ    |

| I <sub>OFFSET</sub>     | Input offset current                               | 1-kΩ source impedance                              | -5             |     | 5               | μA    |

| ANALOG INPU             | JTS V_SENSE, I_SENSE, T_SENSE, LED_MODE            |                                                    |                |     | '               |       |

| V <sub>ADDR_OPEN</sub>  | Voltage indicating open pin                        | LED_MODE open                                      | 2.37           |     |                 |       |

| V <sub>ADDR_SHORT</sub> | Voltage indicating pin shorted to GND              | LED_MODE shorted to ground                         |                |     | 0.36            | V     |

| V <sub>ADC_RANGE</sub>  | Measurement range for voltage monitoring           | ALL ANALOG INPUTS                                  | 0              |     | 2.5             |       |

| INL                     | ADC integral nonlinearity                          |                                                    | -2.5           |     | 2.5             | mV    |

| I <sub>lkg</sub>        | Input leakage current                              | 3 V applied to pin                                 |                |     | 100             | nA    |

| R <sub>IN</sub>         | Input impedance                                    | Ground reference                                   | 8              |     |                 | ΜΩ    |

| C <sub>IN</sub>         | Input capacitance                                  |                                                    |                |     | 10              | pF    |

| DIGITAL INPU            | TS/OUTPUTS                                         |                                                    |                |     |                 |       |

| V <sub>OL</sub>         | Low-level output voltage                           | I <sub>OL</sub> = 6 mA , V33D = 3 V                |                |     | DGND1<br>+ 0.25 |       |

| V <sub>OH</sub>         | High-level output voltage                          | I <sub>OH</sub> = -6 mA , V33D = 3 V               | V33D<br>- 0.6V |     |                 | V     |

| V <sub>IH</sub>         | High-level input voltage                           | V33D = 3V                                          | 2.1            |     | 3.6             |       |

| V <sub>IL</sub>         | Low-level input voltage                            | V33D = 3.5 V                                       |                |     | 1.4             |       |

| I <sub>OH</sub> (MAX)   | Output high source current                         |                                                    |                |     | 4               | A     |

| I <sub>OL</sub> (MAX)   | Output low sink current                            |                                                    |                |     | 4               | mA    |

| SYSTEM PERF             | FORMANCE                                           |                                                    | •              |     | '               |       |

| V <sub>RESET</sub>      | Voltage where device comes out of reset            | V33D Pin                                           | 2.3            |     | 2.4             | V     |

| t <sub>RESET</sub>      | Pulse width needed for reset                       | RESET pin                                          | 2              |     |                 | μs    |

| f <sub>SW</sub>         | Switching Frequency                                |                                                    | 112            |     | 205             | kHz   |

| t <sub>detect</sub>     | Time to detect presence of device requesting power |                                                    |                |     | 0.5             | s     |

| t <sub>retention</sub>  | Retention of configuration parameters              | T <sub>J</sub> = 25°C                              | 100            |     |                 | Years |

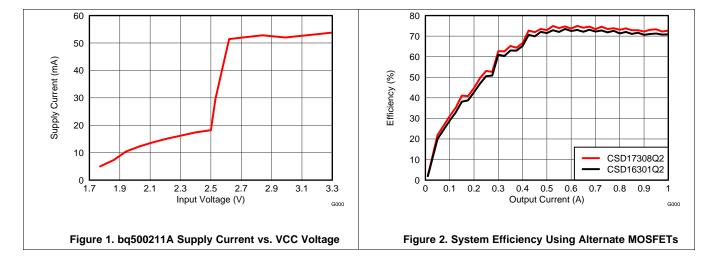

# 6.5 Typical Characteristics Curves

## 7 Detailed Description

#### 7.1 Overview

#### 7.1.1 Fundamentals

The principle of wireless power transfer is simply an open cored transformer consisting of primary and secondary coils and associated electronics. The primary coil and electronics are also referred to as the transmitter, and the secondary side the receiver. The transmitter coil and electronics are typically built into a charger pad. The receiver coil and electronics are typically built into a portable device, such as a cell-phone.

When the receiver coil is positioned on the transmitter coil, magnetic coupling occurs when the transmitter coil is driven. The flux is coupled into the secondary coil which induces a voltage, current flows, it is rectified and power can be transferred quite effectively to a load - wirelessly. Power transfer can be managed via any of various familiar closed-loop control schemes.

## 7.1.2 Wireless Power Consortium (WPC)

The Wireless Power Consortium (WPC) is an international group of companies from diverse industries. The WPC standard was developed to facilitate cross compatibility of compliant transmitters and receivers. The standard defines the physical parameters and the communication protocol to be used in wireless power. For more information, go to www.wirelesspowerconsortium.com.

#### 7.1.3 Power Transfer

Power transfer depends on coil coupling. Coupling is dependant on the distance between coils, alignment, coil dimensions, coil materials, number of turns, magnetic shielding, impedance matching, frequency and duty cycle.

Most importantly, the receiver and transmitter coils must be aligned for best coupling and efficient power transfer. The closer the space between the coils, the better the coupling, but the practical distance is set to be less than 5 mm (as defined within the WPC Specification) to account for housing and interface surfaces.

Shielding is added as a backing to both the transmitter and receiver coils to direct the magnetic field to the coupled zone. Magnetic fields outside the coupled zone do not transfer power. Thus, shielding also serves to contain the fields to avoid coupling to other adjacent system components.

Regulation can be achieved by controlling any one of the coil coupling parameters. For WPC compatibility, the transmitter coils and capacitance are specified and the resonant frequency point is fixed at 100 kHz. Power transfer is regulated by changing the operating frequency between 112 kHz to 205 kHz. The higher the frequency, the further from resonance and the lower the power. Duty cycle remains constant at 50% throughout the power band and is reduced only once 205 kHz is reached.

The WPC standard describes the dimension and materials of the coils. It also has information on tuning the coils to resonance. The value of the inductor and resonant capacitor are critical to proper operation and system efficiency.

#### 7.1.4 Communication

Communication within the WPC is from the receiver to the transmitter, where the receiver tells the transmitter to send power and how much. In order to regulate, the receiver must communicate with the transmitter whether to increase or decrease frequency. The receiver monitors the rectifier output and using Amplitude Modulation (AM), sends packets of information to the transmitter. A packet is comprised of a preamble, a header, the actual message and a checksum, as defined by the WPC standard.

The receiver sends a packet by modulating an impedance network. This AM signal reflects back as a change in the voltage amplitude on the transmitter coil. The signal is demodulated and decoded by the transmitter side electronics and the frequency of its coil drive output is adjusted to close the regulation loop. The bq500211A features internal digital demodulation circuitry.

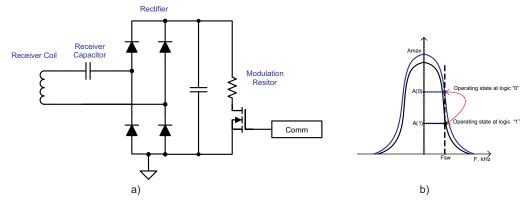

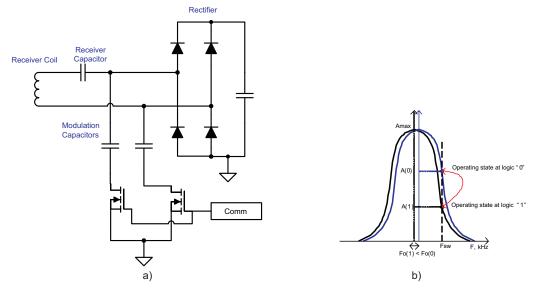

The modulated impedance network on the receiver can either be resistive or capacitive. Figure 3 shows the resistive modulation approach, where a resistor is periodically added to the load and also shows the resulting change in resonant curve which causes the amplitude change in the transmitter voltage indicated by the two operating points at the same frequency. Figure 4 shows the capacitive modulation approach, where a capacitor is periodically added to the load and also shows the resulting amplitude change in the transmitter voltage.

# **Overview (continued)**

Figure 3. Receiver Resistive Modulation Circuit

Figure 4. Receiver Capacitive Modulation Circuit

### 7.2 Functional Block Diagram

### 7.3 Feature Description

### 7.3.1 Dynamic Power Limiting™

Dynamic Power Limiting<sup>™</sup> (DPL) allows operation from a 5-V supply with limited current capability (such as a USB port). There are two modes of operation selected via an input pin. In the dynamic mode, when the input voltage is observed drooping, the output power is limited to reduce the load and provides margin relative to the supply's capability. The second mode, or constant current mode, is designed specifically for operation from a 500-mA capable USB port, it restricts the output such that the input current remains below the 500-mA limit.

#### NOTE

Pin 4 must always be terminated, else erratic behavior may result.

Anytime the DPL control loop is regulating the operating point of the transmitter, the LED will indicate that DPL is active. The LED color and flashing pattern are determined by the LED Table. If the receiver sends a Control Error Packet (CEP) with a negative value, (for example, to reduce power to the load), the WPTX in DPL mode will respond to this CEP via the normal WPC control loop.

#### NOTE

Depending on LED\_MODE selected, the power limit indication may be either solid amber (green + red) or solid red.

## **Feature Description (continued)**

### 7.3.2 Option Select Pin

Two pins (pin 43 and pin 44) on the bq500211A are allocated to program the Loss Threshold and the LED mode of the device. At power up, a bias current is applied to pins LED\_MODE and LOSS\_THR and the resulting voltage measured in order to identify the value of the attached programming resistor. The values of the operating parameters set by these pins are determined using Table 2. For LED\_MODE, the selected bin determines the LED behavior based on Table 1; for the LOSS\_THR, the selected bin sets a threshold used for parasitic metal object detection (see Parasitic Metal Detection (PMOD) and Foreign Object Detection (FOD) section). Table 1.

Figure 5. Option Select Pin Programming

#### 7.3.3 LED Indication Modes

The bq500211A can directly drive two LED outputs (pin 7 and pin 8) through a simple current limit resistor (typically 470  $\Omega$ ), based on the mode selected. The two current limit resistors can be individually adjusted to tune or match the brightness of the two LEDs. Do not exceed the maximum output current rating of the device.

The resistor in Figure 5 connected to pin 44 and GND selects the desired LED indication scheme in Table 1.

| LED               | LED                   |                       |             | Operational States |                   |                    |            |                               |  |

|-------------------|-----------------------|-----------------------|-------------|--------------------|-------------------|--------------------|------------|-------------------------------|--|

| CONTROL<br>OPTION | SELECTION<br>RESISTOR | DESCRIPTION           | LED         | STANDBY            | POWER<br>TRANSFER | CHARGE<br>COMPLETE | FAULT      | DYNAMIC<br>POWER<br>LIMITING™ |  |

| Х                 | < 36.5 kΩ             | Becaused do not use   | LED1, green |                    |                   |                    |            |                               |  |

| ^                 | < 30.5 K12            | Reserved, do not use  | LED2, red   | -                  | -                 | -                  | -          | -                             |  |

| 4                 | 42.2 kΩ               | Choice number 1       | LED1, green | Off                | Blink slow        | On                 | Off        | Blink slow                    |  |

| '                 | 42.2 KΩ               | Choice number 1       | LED2, red   | Off                | Off               | Off                | On         | Blink slow                    |  |

| 2                 | 48.7 kO               | Choice number 2       | LED1, green | On                 | Blink slow        | On                 | Off        | Blink slow                    |  |

| 2                 | 40.7 K12              | Choice number 2       | LED2, red   | On                 | Off               | Off                | On         | Blink slow                    |  |

| 3                 | FC 2 kO               | Choice number 3       | LED1, green | Off                | Off               | On                 | Off        | Off                           |  |

| 3                 | 56.2 kΩ               | Choice number 3       | LED2, red   | Off                | On                | Off                | Blink slow | On                            |  |

| 4                 | 64.0 1:0              | .9 kΩ Choice number 4 | LED1, green | Off                | On                | Off                | Off        | Off                           |  |

| 4                 | 64.9 KΩ               |                       | LED2, red   | Off                | Off               | Off                | On         | Blink slow                    |  |

|                   | > 75 kΩ               | Reserved, all LED off | -           | -                  | -                 | -                  | -          | -                             |  |

Table 1. LED Modes

### 7.3.4 Parasitic Metal Object Detect (PMOD) and Foreign Object Detection (FOD)

The bq500211A is WPC1.1 compliant and supports both enhanced PMOD and the new FOD features by continuously monitoring the input voltage and current to calculate input power. Combining input power, known losses, and the value of power reported by the RX device being charged, the bq500211A can estimate how much power is unaccounted for and presumed lost due to metal objects placed in the wireless power transfer path. If this unexpected loss exceeds the threshold set by the LOSS\_THR resistor, a fault is indicated and power transfer is halted. Whether the PMOD or the FOD algorithm is used is determined by the ID packet of the receiver being charged.

## **Feature Description (continued)**

PMOD has certain inherent weaknesses as rectified power is not ensured to be accurate per WPC1.0 Specification. The user has the flexibility to adjust the LOSS\_THR resistor to suit the application. Should issues with compliance or interoperability arise, the PMOD feature can be selectively disabled as explained below.

The FOD algorithm uses information from an in-system characterized and WPC1.1 certified RX and it is therefore more accurate. Where the WPC1.0 specification merely requires the Rectified Power packet, the WPC1.1 specification additionally uses the Received Power packet which more accurately tracks power used by the receiver.

As the default, PMOD and FOD share the same LOSS\_THR setting resistor for which the recommended starting point is 400 mW (selected by a 56.2-k $\Omega$  resistor on the LOSS\_THR option pin 43). That value has been empirically determined using standard WPC disc, ring and foil FOD test objects. Some tuning might be required in the final system as every system will be different. This tuning is best done by trial and error, use the set resistor values given in the table to increase or decrease the loss threshold and retry the system with the standard test objects. The ultimate goal of the FOD feature is safety, to protect misplaced metal objects from becoming hot. Reducing the loss threshold and making the system too sensitive will lead to false trips and a bad user experience. Find the balance which best suits the application.

If the application requires disabling one or the other or setting separate PMOD and FOD thresholds, a setting resistor of appropriate value can be connected directly from the LOSS\_THR (pin43) to the FOD (pin16) or PMOD (pin17) pins, as needed. These pins are then read at power up and the correct respective values are set. To selectively disable PMOD, for example, only the chosen FOD resistor value would be connected between LOSS\_THR (pin43) and FOD (pin 16) and PMOD (pin17) would left open.

Resistors of 1% tolerance must be used for proper detection of the desired bin.

| BIN NUMBER | RESISTANCE (kΩ) | LOSS THRESHOLD (mW) |  |

|------------|-----------------|---------------------|--|

| 0          | <36.5           | 250                 |  |

| 1          | 42.2            | 300                 |  |

| 2          | 48.7            | 350                 |  |

| 3          | 56.2            | 400                 |  |

| 4          | 64.9            | 450                 |  |

| 5          | 75.0            | 500                 |  |

| 6          | 86.6            | 550                 |  |

| 7          | 100             | 600                 |  |

| 8          | 115             | 650                 |  |

| 9          | 133             | 700                 |  |

| 10         | 154             | 750                 |  |

| 11         | 178             | 800                 |  |

| 12         | 205             | 850                 |  |

| 13         | >237            | Feature Disabled    |  |

**Table 2. Option Select Bins**

### 7.3.5 Shut Down via External Thermal Sensor or Trigger

Typical applications of the bq500211A will not require additional thermal protection. This shutdown feature is provided for enhanced applications and is not only limited to thermal shutdown. The key parameter is the 1.0 V threshold on pin 2. Voltage below 1.0 V on pin 2 causes the device to shutdown.

The application of thermal monitoring via a Negative Temperature Coefficient (NTC) sensor, for example, is straightforward. The NTC forms the lower leg of a temperature dependant voltage divider. The NTC leads are connected to the bq500211A device, pin 2 and GND. The threshold on pin 2 is set to 1.0 V, below which the system shuts down and a fault is indicated (depending on LED mode chosen).

To implement this feature follow these steps:

1) Consult the NTC datasheet and find the resistence vs temperature curve.

**ISTRUMENTS**

2) Determine the actual temperature where the NTC will be placed by using a thermal probe.

- 3) Read the NTC resistance at that temperature in the NTC datasheet, that is R\_NTC.

- 4) Use the following formula to determine the upper leg resistor (R\_Setpoint):

$$R_Setpoint = 2.3 \times R_NTC$$

(1)

The system will restore normal operation after approximately five minutes or if the receiver is removed. If the feature is not used, this pin must be pulled high.

#### **NOTE**

Pin 2 must always be terminated, else erratic behavior may result.

Figure 6. Negative Temperature Coefficient (NTC) Application

#### 7.3.6 Fault Handling and Indication

The following is a table of End Power Transfer (EPT) packet responses, fault conditions, the duration how long the condition lasts until a retry in attempted. The LED mode selected determines how the LED indicates the condition or fault.

Table 3. Fault Handling and Indication

| CONDITION             | DURATION<br>(before retry) | HANDLING                                          |  |

|-----------------------|----------------------------|---------------------------------------------------|--|

| EPT-00                | Immediate                  | Unknown                                           |  |

| EPT-01                | 5 seconds                  | Charge complete                                   |  |

| EPT-02                | Infinite                   | Internal fault                                    |  |

| EPT-03                | 5 minutes                  | Over temperature                                  |  |

| EPT-04                | Immediate                  | Over voltage                                      |  |

| EPT-05                | Immediate                  | Over current                                      |  |

| EPT-06                | Infinite                   | Battery failure                                   |  |

| EPT-07                | Not applicable             | Reconfiguration                                   |  |

| EPT-08                | Immediate                  | No response                                       |  |

| OVP (over voltage)    | Immediate                  |                                                   |  |

| OC (over current)     | 1 minute                   |                                                   |  |

| NTC (external sensor) | 5 minutes                  |                                                   |  |

| PMOD/FOD warning      | 12 seconds                 | 10 seconds LED only,<br>2 seconds LED +<br>buzzer |  |

| PMOD/FOD              | 5 minutes                  |                                                   |  |

## 7.3.7 Power Transfer Start Signal

The bq500211A features two signal outputs to indicate that power transfer has begun. Pin 23 outputs a 400-ms duration, 4-kHz square wave for driving low cost AC type ceramic buzzers. Pin 24 outputs logic high, also for 400 ms, which is suitable for DC type buzzers with built-in tone generators, or as a trigger for any type of customized indication scheme. If not used, these pins can be left open.

#### 7.3.8 Power-On Reset

The bq500211A has an integrated Power-On Reset (POR) circuit which monitors the supply voltage and handles the correct device startup sequence. Additional supply voltage supervisor or reset circuits are not needed.

#### 7.3.9 External Reset, RESET Pin

The bq500211A can be forced into a reset state by an external circuit connected to the  $\overline{\text{RESET}}$  pin. A logic low voltage on this pin holds the device in reset. For normal operation, this pin is pulled up to 3.3 V<sub>CC</sub> with a 10-k $\Omega$  pull-up resistor.

### 7.3.10 Trickle Charge and CS100

The WPC specification provides an End-of-Power Transfer message (EPT-01) to indicate charge complete. Upon receipt of the charge complete message, the bq500211A will change the LED indication to solid green LED output and halt power transfer for 5 seconds.

In some battery charging applications there is a benefit to continue the charging process in trickle-charge mode to top off the battery. There are several information packets in the WPC specification related to the levels of battery charge (Charge Status). The bq500211A uses these commands to enable top-off charging. The bq500211A changes the LED indication to reflect charge complete when a Charge Status message is 100% received, but unlike the response to an EPT, it will not halt power transfer while the LED is solid green. The mobile device can use a CS100 packet to enable trickle charge mode.

If the reported charge status drops below 90% normal, charging indication will be resumed.

### 7.3.11 Current Monitoring Requirements

The bq500211A is WPC1.1 ready. In order to enable the PMOD or FOD features, current monitoring must be provided in the design.

Current monitoring is optional however, it is used for the foreign metal protection features and over current protection. The system designer can choose not to include the current monitor and remain WPC1.0 compliant. Alternately, the additional current monitoring circuitry can be added to the hardware design but not loaded. This would enable a forward migration path to future WPC1.1 compatibility.

For proper scaling of the current monitor signal, the current sense resistor should be 20 mΩ and the current shunt amplifier should have a gain of 50, such as the INA199A1. The current sense resistor has a temperature stability of ±200 PPM. Proper current sensing techniques in the application hardware should also be observed.

### 7.3.12 Overcurrent Protection

The bq500211A has an integrated current protection feature which monitors the input current reported by the current sense resistor and amplifier. If the input current exceeds a safety threshold, a fault is indicated and power transfer is halted for one minute.

If this feature is desired, the sense resistor and amplifier are required. If this feature is not desired, the I\_SENSE input pin to the bq500410A (pin 42) should be grounded.

#### **NOTE**

Always terminate the I\_SENSE pin (pin 42), either with the output of a current monitor circuit or by connecting to ground.

## 7.3.13 MSP430G2001 Low Power Supervisor

This is an optional low-power feature. By adding the MSP430G2001, the entire bq500211A is periodically shut down to conserve power, yet all relevant states are recalled and all running LED status indicators remain on.

#### 7.3.13.1 MSP430 Low Power Supervisor Details

Since the bq500211A needs an external low-power mode to significantly reduce power consumption, one way of positively achieving that goal is to remove its supply and completely shut it down. In doing so, however, the bq500211A goes through a reset and any data in memory would be lost. Important information regarding charge state, fault condition and operating mode would be cleared. The MSP430G2001 maintains the LED indication and stores previous charge state during the bq500211A reset period.

The LEDs indicators are now driven by the MSP430G2001, do not exceed the pin output current drive limit.

Using the suggested circuitry, a standby power reduction from 300 mW to less than 90 mW can be expected making it possible to achieve Energy Star rating.

The user does not need to program the MSP430G2001, an off-the-shelf part and any of the available packages can be used as long as the connections are correct. The required MSP430G2001 firmware is embedded in the bq500211A and is boot loaded at first power up, similar to a field update. The MSP430G2001 code cannot be modified by the user.

#### **NOTE**

The user cannot program the MSP430G2001 in this system.

#### 7.3.14 All Unused Pins

All unused pins can be left open unless otherwise indicated. Pins 1, 3, 45 can be tied to GND and flooded with copper to improve ground shielding. Please refer to the pin definition table for further explanations.

## 8 Application and Implementation

#### **NOTE**

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

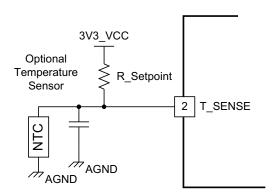

## 8.1 Typical Application

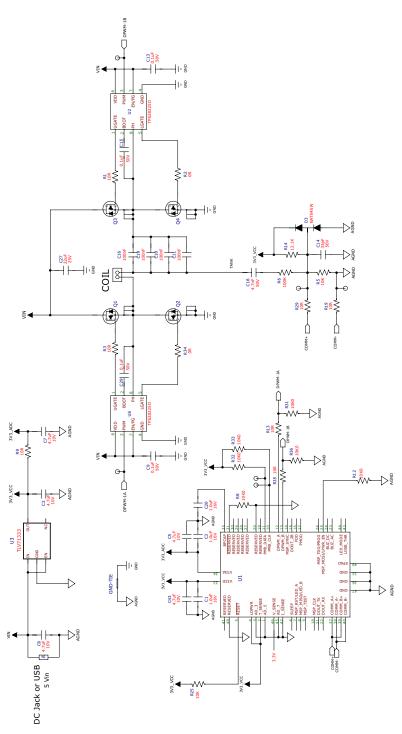

The application schematic for the transmitter with reduced standby power is shown in Figure 7.

### **CAUTION**

Please check the bq500211A product page for the most up-to-date application schematic and list of materials package before starting a new design.

# **Typical Application (continued)**

Figure 7. bq500211A Typical Low-Standby Power Application Diagram

## **Typical Application (continued)**

### 8.1.1 Detailed Design Procedure

#### 8.1.1.1 Coils and Matching Capacitors

The coil and matching capacitor selection for the transmitter has been established by WPC standard. This is fixed and cannot be changed on the transmitter side.

An up to date list of available and compatible A5 and A11 transmitter coils can be found here (SLUA649):

Capacitor selection is critical to proper system operation. A total capacitance value of 400 nF is required in the resonant tank. This is the WPC system compatibility requirement, not a guideline, and must be followed.

#### **NOTE**

A total capacitance value of 400 nF/50 V (C0G dielectric type or equivalent) is required in the resonant tank to achieve a 100-kHz resonance frequency.

The capacitors chosen must be rated for at least 50 V and must be of high quality C0G dielectric or equivalent. These are typically available in a 5% tolerance. The use of X7R types or below is not recommended if WPC compliance is required because critical WPC certification testing, such as the minimum modulation requirement, might fail.

A 400-nF capacitor is not a standard value and therefore several must be combined in parallel. The designer can combine a (4 nF x 100 nF) or a (180 nF + 220 nF) along with other combinations depending on market availability. All capacitors must be of high quality C0G type or equivalent and not mixed with lesser dielectric types.

## 8.1.1.2 Input Regulator

The bq500211A requires 3.3 VDC to operate. A buck regulator or a linear regulator can be used to step down from the 5-V system input. Either choice is fully WPC compatible, the decision lies in the user's requirements with respect to cost or efficiency.

For highest efficiency use a low-cost buck regulator, TPS62237, which on account of a 3-MHz switching frequency, can use a 0805 size chip inductor. This results in a very attractive combination, high performance, small size, ease of use and low cost.

#### 8.1.1.3 Power Train

The bq500211A drives a phase-shifted full bridge. This is essentially twin half bridges and the choice of driver devices is quite simple, a pair of TPS28225 synchronous MOSFET drivers are used with four CSD17308Q2 NexFETs. Other combinations work and system performance with regards to efficiency and EMI emissions vary. Any alternate MOSFETs chosen must be fully saturated at 5-V gate drive and be sure to pay attention whether or not to use gate resistors; some tuning might be required.

#### 8.1.1.4 Low Power Supervisor

Power reduction is achieved by periodically disabling the bq500211A while LED and housekeeping control functions are continued by U4 – the low-cost, low quiescent current microcontroller MSP430G2001. When U4 is present in the circuit (which is set by a pull-up resistor on bq500211A pin 25), the bq500211A at first power-up boots the MSP430G2001 with the necessary firmware and the two chips operate in tandem. During standby operation, the bq500211A periodically issues a SLEEP command, Q12 pulls the RESET pin low, therefore reducing its power consumption. Meanwhile, the MSP430G2001 maintains the LED indication and stores previous charge state during this bq500211A reset period. This bq500211A reset period is set by the RC time constant network of R26, C22 (see Figure 7). WPC compliance mandates receive detection within 500 ms, the power transmitter controller, bq500211A, awakes every 400 ms to produce an analog ping and check if a valid device is present. Increasing this time constant, therefore is not advised; shortening could result in faster detection time with some decrease in efficiency.

bq500211A

ZHCSAO7B - DECEMBER 2012-REVISED JUNE 2016

www.ti.com.cn

## **Typical Application (continued)**

## 8.1.1.5 Disabling Low Power Supervisor Mode

For lowest cost or if the low-power supervisor is not needed, please refer to Figure 8 for the application schematic.

#### NOTE

Current sense shunt and amplifier circuitry are optional. The circuitry is needed to enable Foreign Object Detection (FOD) and a forward migration path to WPC1.1 compliance.

# **Typical Application (continued)**

Figure 8. bq500211A Typical Low-Cost Application Diagram

bq500211A

ZHCSAO7B - DECEMBER 2012-REVISED JUNE 2016

## www.ti.com.cn

## 9 Layout

## 9.1 Layout Guidelines

A good PCB layout is critical to proper system operation and due care should be taken. There are many references on proper PCB layout techniques.

Generally speaking, the system layout will require a 4-layer PCB layout, although a 2-layer PCB layout can be achieved. A proven and recommended approach to the layer stack-up has been:

- Layer 1, component placement and as much ground plane as possible.

- · Layer 2, clean ground.

- · Layer 3, finish routing.

- · Layer 4, clean ground.

Thus, the circuitry is virtually sandwiched between grounds. This minimizes EMI noise emissions and also provides a noise free voltage reference plane for device operation.

Keep as much copper as possible. Make sure the bq500211A GND pins and the power pad have a continuous flood connection to the ground plane. The power pad should also be stitched to the ground plane, which also acts as a heat sink for the bq500211A. A good GND reference is necessary for proper bq500211A operation, such as analog-digital conversion, clock stability and best overall EMI performance.

Separate the analog ground plane from the power ground plane and use only one tie point to connect grounds. Having several tie points defeats the purpose of separating the grounds.

The COMM return signal from the resonant tank should be routed as a differential pair. This is intended to reduce stray noise induction. The frequencies of concern warrant low-noise analog signaling techniques, such as differential routing and shielding, but the COMM signal lines do not need to be impedance matched.

Typically a single chip controller solution with integrated power FET and synchronous rectifier will be used. To create a tight loop, pull in the buck inductor and power loop as close as possible. Likewise, the power-train, full-bridge components should be pulled together as tight as possible. See the *bq500211AEVM-045*, *bqTESLA* Wireless Power TX EVM User's Guide (SLVU536) for layout examples.

## 10 器件和文档支持

#### 10.1 文档支持

#### 10.1.1 相关文档

- 《构建一个无线电源发射器》, SLUA635

- 技术,无线电源联盟http://www.wirelesspowerconsortium.com/

- 《无线充电联盟标准和 TI 兼容解决方案介绍》, Bill-Johns。

- 《BQ500210 数据表》,SLUSAL8

- 《BQ51013 数据表》,SLVSAT9

### 10.2 社区资源

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

### 10.3 商标

Dynamic Power Limiting, E2E are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

## 10.4 静电放电警告

这些装置包含有限的内置 ESD 保护。 存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

### 10.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

### 11 机械、封装和可订购信息

以下页中包括机械、封装和可订购信息。这些信息是针对指定器件可提供的最新数据。这些数据会在无通知且不对本文档进行修订的情况下发生改变。欲获得该数据表的浏览器版本,请查阅左侧的导航栏。

www.ti.com 7-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|-----------------|-----------------------|------|-------------------------------|----------------------------|--------------|--------------|

|                       | (1)    | (2)           |                 |                       | (3)  | (4)                           | (5)                        |              | (6)          |

| BQ500211ARGZR         | NRND   | Production    | VQFN (RGZ)   48 | 2500   LARGE T&R      | Yes  | FULL NIPDAU                   | Level-3-260C-168 HR        | -40 to 110   | BQ500211A    |

| BQ500211ARGZR.A       | NRND   | Production    | VQFN (RGZ)   48 | 2500   LARGE T&R      | Yes  | FULL NIPDAU                   | Level-3-260C-168 HR        | -40 to 110   | BQ500211A    |

| BQ500211ARGZR.B       | NRND   | Production    | VQFN (RGZ)   48 | 2500   LARGE T&R      | Yes  | FULL NIPDAU                   | Level-3-260C-168 HR        | -40 to 110   | BQ500211A    |

| BQ500211ARGZT         | NRND   | Production    | VQFN (RGZ)   48 | 250   SMALL T&R       | Yes  | FULL NIPDAU                   | Level-3-260C-168 HR        | -40 to 110   | BQ500211A    |

| BQ500211ARGZT.A       | NRND   | Production    | VQFN (RGZ)   48 | 250   SMALL T&R       | Yes  | FULL NIPDAU                   | Level-3-260C-168 HR        | -40 to 110   | BQ500211A    |

| BQ500211ARGZT.B       | NRND   | Production    | VQFN (RGZ)   48 | 250   SMALL T&R       | Yes  | FULL NIPDAU                   | Level-3-260C-168 HR        | -40 to 110   | BQ500211A    |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 7-Nov-2025

PACKAGE MATERIALS INFORMATION

www.ti.com 29-Sep-2019

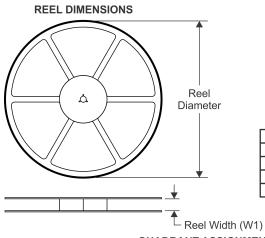

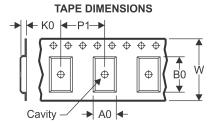

## TAPE AND REEL INFORMATION

| Α0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| BQ500211ARGZR | VQFN            | RGZ                | 48 | 2500 | 330.0                    | 16.4                     | 7.3        | 7.3        | 1.1        | 12.0       | 16.0      | Q2               |

| BQ500211ARGZT | VQFN            | RGZ                | 48 | 250  | 180.0                    | 16.4                     | 7.3        | 7.3        | 1.1        | 12.0       | 16.0      | Q2               |

www.ti.com 29-Sep-2019

#### \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins SPQ |      | Length (mm) | Width (mm) | Height (mm) |  |

|---------------|--------------|-----------------|----------|------|-------------|------------|-------------|--|

| BQ500211ARGZR | VQFN         | RGZ             | 48       | 2500 | 367.0       | 367.0      | 38.0        |  |

| BQ500211ARGZT | VQFN         | RGZ             | 48       | 250  | 210.0       | 185.0      | 35.0        |  |

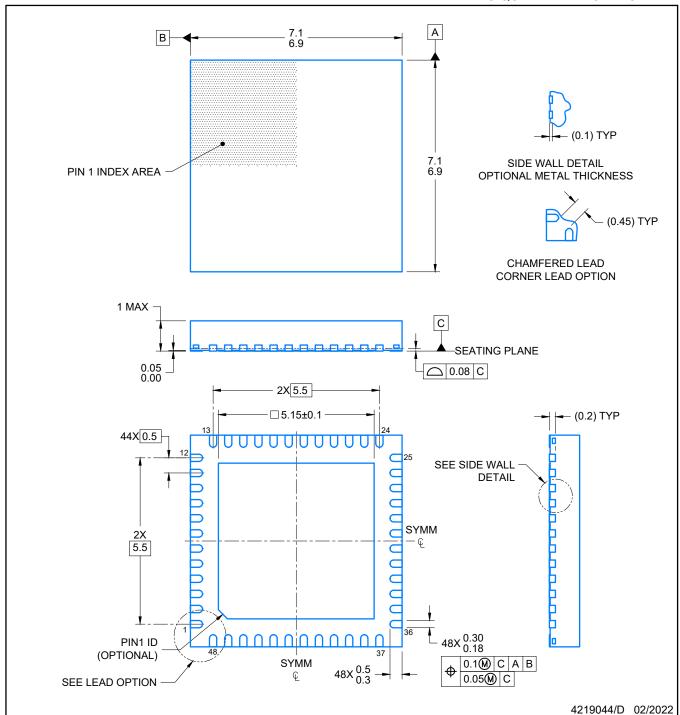

7 x 7, 0.5 mm pitch

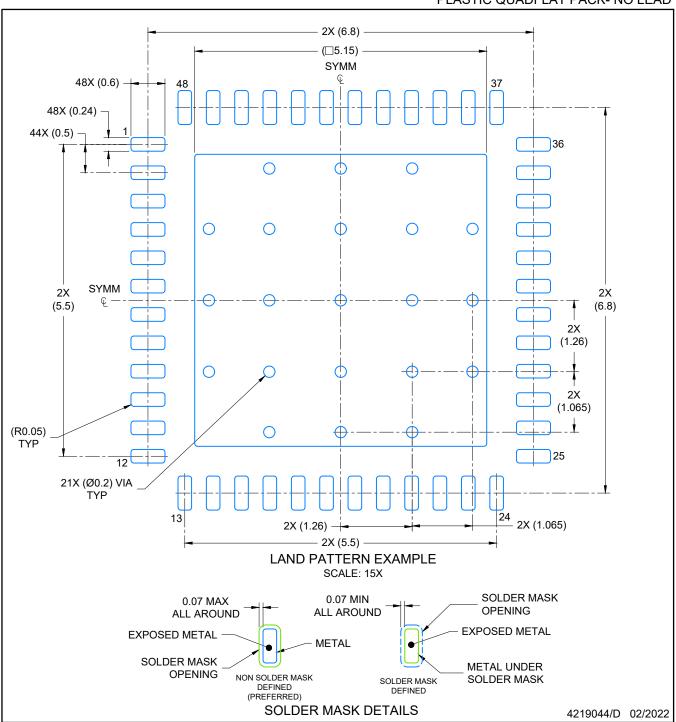

PLASTIC QUADFLAT PACK- NO LEAD

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4224671/A

PLASTIC QUADFLAT PACK- NO LEAD

#### NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

PLASTIC QUADFLAT PACK- NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC QUADFLAT PACK- NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月