Sample &

Buy

ZHCSEX1A - MARCH 2016-REVISED APRIL 2016

# **bq27220** 单节 CEDV 电量监测计

Technical

Documents

## 1 特性

- 单节串联锂离子电池电量监测计

- 驻留在电池组或系统主板上

- 支持嵌入式或可拆除电池

- 由集成低压降稳压器 (LDO) 的电池直接供电

- 支持低值 (10mΩ) 外部感测电阻

- 超低功耗:正常模式下为 50µA,休眠模式下为 9µA

- 基于补偿放电结束电压 (CEDV) 技术的电池电量监测

- 用平滑滤波器报告剩余电量和充电状态 (SOC)

- 针对电池老化、自放电以及温度和速率变化进行 自动调节

- 提供电池健康(老化)状况的估计

- 微控制器外设支持:

- 400kHz I<sup>2</sup>C™串行接口

- 可配置的 SOC 中断或 电池低电量数字输出警告

- 内部温度传感器、 主机报告的温度或 外部热敏电阻

## 2 应用

- 智能手机和功能手机

- 平板电脑

- 可穿戴产品

- 楼宇自动化

- 便携式医疗/工业手持终端

- 便携式音频设备

- 游戏机

## 3 说明

Tools &

Software

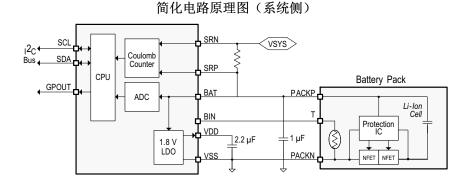

德州仪器 (TI) bq27220 电池电量监测计是一款单节电 池电量监测计,只需进行少量用户配置和系统微控制器 固件开发工作即可快速实现系统调通。 bq27220 器件 采用补偿放电结束电压 (CEDV) 算法进行电量检测, 可提供诸如剩余电量 (mAh)、充电状态 (%)、续航时间 (分钟)、电池电压 (mV)、温度 (℃) 和健康状况 (%) 等信息。

Support &

Community

**...**

bq27220 电池电量监测计在正常模式 (50μA) 和休眠模式 (9μA) 下均具有超低功耗,有助于延长电池运行时间。可配置中断有助于节省系统功耗,释放主机使其停止继续轮询。外部热敏电阻为精确温度感测提供支持。

客户可以使用 ROM 中预载的 CEDV 参数,或者使用 通过 TI 网络工具 GAUGEPARCAL 生成的定制化学参 数。生成的定制参数可在系统上电时通过主机编程到器 件 RAM 中,客户也可以将该参数编程到板载一次性可 编程 (OTP) 存储器中。

通过 bq27220 器件进行电池电量监测时,只需将 PACK+ (P+) 与 PACK- (P-) 连接至可拆卸电池组或嵌 入式电池电路即可。微型 9 焊球、1.62mm × 1.58mm、间距为 0.5mm 的 NanoFree™芯片级封装 (DSBGA),是空间受限类应用的 理想选择。

|         | 器件信息 <sup>(1)</sup> |                 |

|---------|---------------------|-----------------|

| 器件型号    | 封装                  | 封装尺寸(标称值)       |

| bq27220 | YZF (9)             | 1.62mm x 1.58mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

## 目录

| 1 | 特性   |                                                                               |   |

|---|------|-------------------------------------------------------------------------------|---|

| 2 | 应用   | 1                                                                             |   |

| 3 | 说明   |                                                                               |   |

| 4 | 修订   | 历史记录                                                                          |   |

| 5 | Pin  | Configuration and Functions 3                                                 |   |

| 6 | Spe  | cifications4                                                                  |   |

|   | 6.1  | Absolute Maximum Ratings 4                                                    |   |

|   | 6.2  | ESD Ratings 4                                                                 |   |

|   | 6.3  | Recommended Operating Conditions 5                                            |   |

|   | 6.4  | Thermal Information 5                                                         |   |

|   | 6.5  | Supply Current 5                                                              |   |

|   | 6.6  | Digital Input and Output DC Characteristics 5                                 |   |

|   | 6.7  | LDO Regulator, Wake-up, and Auto-Shutdown DC<br>Characteristics               | ; |

|   | 6.8  | LDO Regulator, Wake-up, and Auto-shutdown AC Characteristics                  | 5 |

|   | 6.9  | ADC (Temperature and Cell Measurement)<br>Characteristics                     |   |

|   | 6.10 | Integrating ADC (Coulomb Counter) Characteristics                             |   |

|   | 6.11 | I <sup>2</sup> C-Compatible Interface Communication Timing<br>Characteristics |   |

|   | 6.12 | SHUTDOWN and WAKE-UP Timing 8                                                 |   |

|    | 6.13 | Typical Characteristics                              | 8  |

|----|------|------------------------------------------------------|----|

| 7  | Deta | iled Description                                     | 9  |

|    | 7.1  | Overview                                             | 9  |

|    | 7.2  | Functional Block Diagram (System-Side Configuration) | 9  |

|    | 7.3  | Feature Description                                  | 9  |

|    | 7.4  | Device Functional Modes                              | 11 |

| 8  | Арр  | lication and Implementation                          | 12 |

|    | 8.1  | Application Information                              | 12 |

|    | 8.2  | Typical Applications                                 | 12 |

| 9  | Pow  | er Supply Recommendation                             | 15 |

|    | 9.1  | Power Supply Decoupling                              | 15 |

| 10 | Lay  | out                                                  | 15 |

|    | 10.1 | Layout Guidelines                                    | 15 |

|    | 10.2 | Layout Example                                       | 16 |

| 11 | 器件   | 和文档支持                                                | 17 |

|    | 11.1 | 文档支持                                                 | 17 |

|    | 11.2 | 社区资源                                                 | 17 |

|    | 11.3 | 商标                                                   | 17 |

|    | 11.4 | 静电放电警告                                               | 17 |

|    | 11.5 | Glossary                                             | 17 |

| 12 | 机械   | 、封装和可订购信息                                            | 17 |

## 4 修订历史记录

| 日期         | 修订版本 | 注释            |

|------------|------|---------------|

| 2016 年 4 月 | A    | "产品预览"至"量产数据" |

www.ti.com.cn

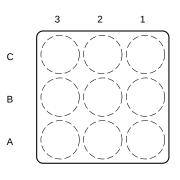

## 5 Pin Configuration and Functions

#### **Bottom View**

### **Pin Functions**

| Р           | IN | ТҮРЕ                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|-------------|----|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NUMBER |    | TIFE                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| BAT         | СЗ | PI, AI <sup>(1)</sup> | LDO regulator input and battery voltage measurement input. Kelvin sense connect to the positive battery terminal (PACKP). Connect a capacitor (1 $\mu F$ ) between BAT and V <sub>SS</sub> . Place the capacitor close to the gauge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| BIN         | B1 | DI                    | Battery insertion detection input. If <b>OpConfig [BI_PU_EN]</b> = 1 (default), a logic low on the pin is detected as battery insertion. For a removable pack, the BIN pin can be connected to $V_{SS}$ through a pulldown resistor on the pack, typically the 10-k $\Omega$ thermistor; the system board should use a 1.8-M $\Omega$ pullup resistor to $V_{DD}$ to ensure the BIN pin is high when a battery is removed. If the battery is embedded in the system or in the pack, it is recommended to leave <b>[BI_PU_EN]</b> = 1 and use a 10-k $\Omega$ pulldown resistor from BIN to $V_{SS}$ . If <b>[BI_PU_EN]</b> = 0, then the host must inform the gauge of battery insertion and removal with the <i>BAT_INSERT</i> and <i>BAT_REMOVE</i> subcommands. A 10-k $\Omega$ pulldown resistor should be placed between BIN and $V_{SS}$ , even if this pin is unused.<br><b>NOTE:</b> The BIN pin must not be shorted directly to $V_{CC}$ or $V_{SS}$ and any pullup resistor on the BIN pin must be connected only to $V_{DD}$ and not an external voltage rail. If an external thermistor is used for temperature input, the thermistor should be connected between this pin and $V_{SS}$ . |  |  |

(1) IO = Digital input-output, AI = Analog input, P = Power connection

**bq27220** ZHCSEX1A – MARCH 2016– REVISED APRIL 2016 STRUMENTS

XAS

#### **Pin Functions (continued)**

| PIN             |        | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|-----------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME            | NUMBER | ITPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| GPOUT           | A1     | DO   | This open-drain output can be configured to indicate BAT_LOW when the <b>OpConfig</b><br>[ <b>BATLOWEN</b> ] bit is set. By default [ <b>BATLOWEN</b> ] is cleared and this pin performs an interrupt<br>function (SOC_INT) by pulsing for specific events, such as a change in state-of-charge. Signal<br>polarity for these functions is controlled by the [ <b>GPIOPOL</b> ] configuration bit. This pin should not<br>be left floating, even if unused; therefore, a 10-k $\Omega$ pullup resistor is recommended. If the device<br>is in SHUTDOWN mode, toggling GPOUT makes the gauge exit SHUTDOWN. It is<br>recommended to connect GPOUT to a GPIO of the host MCU so that in case of any inadvertent<br>shutdown condition, the gauge can be commanded to come out of SHUTDOWN. |  |  |

| SCL             | A3     | DIO  | Slave I <sup>2</sup> C serial bus for communication with system (Master). Open-drain pins. Use with external                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| SDA             | A2     | DIO  | 10-k $\Omega$ pullup resistors (typical) for each pin. If the external pullup resistors will be disconnected from these pins during normal operation, recommend using external 1-M $\Omega$ pulldown resistors to V <sub>SS</sub> at each pin to avoid floating inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| SRN             | C2     | AI   | Coulomb counter differential inputs expecting an external 10-mΩ, 1% sense resistor. For system-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| SRP             | C1     | AI   | side configurations, Kelvin sense connect SRP to the positive battery terminal (PACKP) side of the external sense resistor. Kelvin sense connect SRN to the other side of the external sense resistor with the positive connection to the system (VSYS). For pack-side configurations with low-side sensing, connect SRP to PACK– and SRN to Cell–. See the <i>Simplified Schematic</i> . No calibration is required. The fuel gauge is pre-calibrated for a standard 10-m $\Omega$ , 1% sense resistor.                                                                                                                                                                                                                                                                                 |  |  |

| V <sub>DD</sub> | В3     | PO   | 1.8-V regulator output. Decouple with a 2.2- $\mu$ F ceramic capacitor to V <sub>SS</sub> . This pin is not intended to provide power for other devices in the system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| V <sub>SS</sub> | B2     | PI   | Ground pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                   |                                                         | MIN  | MAX                    | UNIT |

|-------------------|---------------------------------------------------------|------|------------------------|------|

| V <sub>BAT</sub>  | BAT pin input voltage range                             | -0.3 | 6                      | V    |

| V                 | SRP and SRN pins input voltage range                    | -0.3 | V <sub>BAT</sub> + 0.3 | V    |

| V <sub>SR</sub>   | Differential voltage across SRP and SRN. ABS(SRP - SRN) |      | 2                      | V    |

| V <sub>DD</sub>   | V <sub>DD</sub> pin supply voltage range (LDO output)   | -0.3 | 2                      | V    |

| V <sub>IOD</sub>  | Open-drain IO pins (SDA, SCL)                           | -0.3 | 6                      | V    |

| V <sub>IOPP</sub> | Push-pull IO pins (BIN)                                 | -0.3 | V <sub>DD</sub> + 0.3  | V    |

| T <sub>A</sub>    | Operating free-air temperature range                    | -40  | 85                     | °C   |

| Storage t         | temperature, T <sub>stg</sub>                           | -65  | 150                    | °C   |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                    |               |                                                                                | VALUE | UNIT |

|--------------------|---------------|--------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±1500 | V    |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±250  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

|                                   |                                                                                        |                                                                        | MIN  | NOM | MAX | UNIT |

|-----------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------|------|-----|-----|------|

| $C_{BAT}^{(1)}$                   | External input capacitor for internal LDO between BAT and $V_{SS}$                     | Nominal capacitor values specified.                                    |      | 0.1 |     | μF   |

| C <sub>LDO18</sub> <sup>(1)</sup> | External output capacitor for internal LDO between $V_{\text{DD}}$ and $V_{\text{SS}}$ | Recommend a 5% ceramic X5R-type capacitor located close to the device. |      | 2.2 |     | μF   |

| $V_{PU}^{(1)}$                    | External pullup voltage for open-drain<br>pins (SDA, SCL, GPOUT)                       |                                                                        | 1.62 |     | 3.6 | V    |

(1) Specified by design. Not production tested.

#### 6.4 Thermal Information

|                     |                                              | bq27220     |      |

|---------------------|----------------------------------------------|-------------|------|

|                     | THERMAL METRIC <sup>(1)</sup>                | YZF (DSBGA) | UNIT |

|                     |                                              | 9 PINS      |      |

| $R_{\theta JA}$     | Junction-to-ambient thermal resistance       | 64.1        | °C/W |

| R <sub>0JCtop</sub> | Junction-to-case (top) thermal resistance    | 59.8        | °C/W |

| $R_{\theta JB}$     | Junction-to-board thermal resistance         | 52.7        | °C/W |

| ΨJT                 | Junction-to-top characterization parameter   | 0.3         | °C/W |

| $\Psi_{JB}$         | Junction-to-board characterization parameter | 28.3        | °C/W |

| $R_{\theta JCbot}$  | Junction-to-case (bottom) thermal resistance | 2.4         | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953

### 6.5 Supply Current

$T_A = 30^{\circ}C$  and  $V_{BAT} = 3.6 V$  (unless otherwise noted)

|                 | PARAMETER             | TEST CONDITIONS                                                                   | MIN | TYP | MAX | UNIT |

|-----------------|-----------------------|-----------------------------------------------------------------------------------|-----|-----|-----|------|

| $I_{CC}^{(1)}$  | NORMAL mode current   | I <sub>LOAD</sub> > Sleep Current <sup>(2)</sup>                                  |     | 50  |     | μA   |

| $I_{SLP}^{(1)}$ | SLEEP mode current    | I <sub>LOAD</sub> < Sleep Current <sup>(2)</sup>                                  |     | 9   |     | μA   |

| $I_{SD}^{(1)}$  | SHUTDOWN mode current | Fuel gauge in host commanded<br>SHUTDOWN mode.<br>(LDO regulator output disabled) |     | 0.6 |     | μΑ   |

(1) Specified by design. Not production tested.

(2) Wake Comparator Disabled.

## 6.6 Digital Input and Output DC Characteristics

$T_A = -40^{\circ}$ C to 85°C, typical values at  $T_A = 30^{\circ}$ C and  $V_{BAT} = 3.6$  V (unless otherwise noted)

|                                | PARAMETER                                       | TEST CONDITIONS                      | MIN                   | TYP | MAX | UNIT |

|--------------------------------|-------------------------------------------------|--------------------------------------|-----------------------|-----|-----|------|

| V <sub>IH(OD)</sub>            | Input voltage, high <sup>(2)</sup>              | External pullup resistor to $V_{PU}$ | V <sub>PU</sub> × 0.7 |     |     | V    |

| V <sub>IH(PP)</sub>            | Input voltage, high <sup>(3)</sup>              |                                      | 1.4                   |     |     | V    |

| V <sub>IL</sub>                | Input voltage, low <sup>(2) (3)</sup>           |                                      |                       |     | 0.6 | V    |

| V <sub>OL</sub>                | Output voltage, low <sup>(2)</sup>              |                                      |                       |     | 0.6 | V    |

| I <sub>OH</sub>                | Output source current, high <sup>(2)</sup>      |                                      |                       |     | 0.5 | mA   |

| I <sub>OL(OD)</sub>            | Output sink current, low <sup>(2)</sup>         |                                      |                       |     | -3  | mA   |

| C <sub>IN</sub> <sup>(1)</sup> | Input capacitance <sup>(2)(3)</sup>             |                                      |                       |     | 5   | pF   |

| l <sub>lkg</sub>               | Input leakage current<br>(SCL, SDA, BIN, GPOUT) |                                      |                       |     | 1   | μA   |

Specified by design. Not production tested.

Open Drain pins: (SCL, SDA, GPOUT)

(3) Push-Pull pin: (BIN)

RUMENTS

## 6.7 LDO Regulator, Wake-up, and Auto-Shutdown DC Characteristics

$T_A = -40^{\circ}$ C to 85°C, typical values at  $T_A = 30^{\circ}$ C and  $V_{BAT} = 3.6$  V (unless otherwise noted)

| ~                               | , <b>, , ,</b> , , , , , , , , , , , , , , ,                                  | DAT                            | ,    |      |     |      |

|---------------------------------|-------------------------------------------------------------------------------|--------------------------------|------|------|-----|------|

|                                 | PARAMETER                                                                     | TEST CONDITIONS                | MIN  | TYP  | MAX | UNIT |

| V <sub>BAT</sub>                | BAT pin regulator input                                                       |                                | 2.45 |      | 4.5 | V    |

| V <sub>DD</sub>                 | Regulator output voltage                                                      |                                |      | 1.85 |     | V    |

| UVLO <sub>IT+</sub>             | V <sub>BAT</sub> undervoltage lock-out<br>LDO wake-up rising threshold        |                                |      | 2    |     | V    |

| UVLO <sub>IT-</sub>             | V <sub>BAT</sub> undervoltage lock-out<br>LDO auto-shutdown falling threshold |                                |      | 1.95 |     | V    |

| V <sub>WU+</sub> <sup>(1)</sup> | GPOUT (input) LDO Wake-up rising edge threshold <sup>(2)</sup>                | LDO Wake-up from SHUTDOWN mode | 1.2  |      |     | V    |

(1) Specified by design. Not production tested.

(2) If the device is commanded to SHUTDOWN via I<sup>2</sup>C with V<sub>BAT</sub> > UVLO<sub>IT+</sub>, a wake-up rising edge trigger is required on GPOUT.

#### 6.8 LDO Regulator, Wake-up, and Auto-shutdown AC Characteristics

#### $T_A = -40^{\circ}$ C to 85°C, typical values at $T_A = 30^{\circ}$ C and $V_{BAT} = 3.6$ V (unless otherwise noted)

|                                   | PARAMETER                            | TEST CONDITIONS                                                                                | MIN | TYP | MAX | UNIT |

|-----------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------|-----|-----|-----|------|

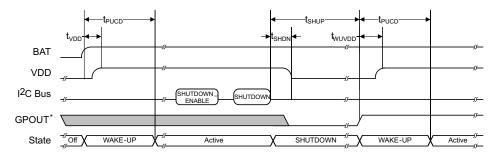

| t <sub>SHDN</sub> <sup>(1)</sup>  | SHUTDOWN entry time                  | Time delay from SHUTDOWN command to LDO output disable.                                        |     |     | 250 | ms   |

| t <sub>SHUP</sub> <sup>(1)</sup>  | SHUTDOWN GPOUT low time              | Minimum low time of GPOUT (input) in SHUTDOWN before WAKEUP                                    | 10  |     |     | μs   |

| $t_{VDD}^{(1)}$                   | Initial $V_{DD}$ output delay        |                                                                                                |     | 13  |     | ms   |

| t <sub>WUVDD</sub> <sup>(1)</sup> | Wake-up $V_{\text{DD}}$ output delay | Time delay from rising edge of GPOUT (input) to nominal V <sub>DD</sub> output.                |     | 8   |     | ms   |

| t <sub>PUCD</sub>                 | Power-up communication delay         | Time delay from rising edge of BAT to the Active state. Includes firmware initialization time. |     | 250 |     | ms   |

(1) Specified by design. Not production tested.

## 6.9 ADC (Temperature and Cell Measurement) Characteristics

$T_A = -40^{\circ}$ C to 85°C; typical values at  $T_A = 30^{\circ}$ C and  $V_{BAT} = 3.6$  V (unless otherwise noted)

|                       |                                      | Bitti                   |      |     |     |      |

|-----------------------|--------------------------------------|-------------------------|------|-----|-----|------|

|                       | PARAMETER                            | TEST CONDITIONS         | MIN  | TYP | MAX | UNIT |

| V <sub>IN(BAT)</sub>  | BAT pin voltage measurement<br>range | Voltage divider enabled | 2.45 |     | 4.5 | V    |

| t <sub>ADC_CONV</sub> | Conversion time                      |                         |      | 125 |     | ms   |

|                       | Effective resolution                 |                         |      | 15  |     | bits |

(1) Specified by design. Not tested in production.

#### 6.10 Integrating ADC (Coulomb Counter) Characteristics

$T_A = -40^{\circ}$ C to 85°C; typical values at  $T_A = 30^{\circ}$ C and  $V_{BAT} = 3.6$  V (unless otherwise noted)

|                      | PARAMETER                                        | TEST CONDITIONS   | MIN | TYP  | MAX              | UNIT |

|----------------------|--------------------------------------------------|-------------------|-----|------|------------------|------|

| V <sub>SRCM</sub>    | Input voltage range of SRN, SRP pins             |                   | VSS |      | V <sub>BAT</sub> | V    |

| V <sub>SRDM</sub>    | Input differential voltage range of<br>VSRP–VSRN |                   |     | ± 80 |                  | mV   |

| t <sub>SR_CONV</sub> | Conversion time                                  | Single conversion |     | 1    |                  | S    |

|                      | Effective Resolution                             | Single conversion |     | 16   |                  | bits |

(1) Specified by design. Not tested in production.

TEXAS INSTRUMENTS

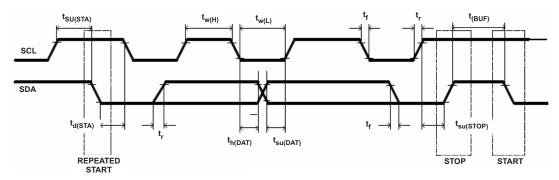

## 6.11 I<sup>2</sup>C-Compatible Interface Communication Timing Characteristics

$T_A = -40^{\circ}$ C to 85°C; typical values at  $T_A = 30^{\circ}$ C and  $V_{BAT} = 3.6$  V (unless otherwise noted)

|                       |                                      |                               | MIN  | NOM MAX | UNIT |

|-----------------------|--------------------------------------|-------------------------------|------|---------|------|

| Standard              | Mode (100 kHz)                       |                               |      |         |      |

| t <sub>d(STA)</sub>   | Start to first falling edge of SCL   |                               | 4    |         | μs   |

| t <sub>w(L)</sub>     | SCL pulse duration (low)             |                               | 4.7  |         | μs   |

| t <sub>w(H)</sub>     | SCL pulse duration (high)            |                               | 4    |         | μs   |

| t <sub>su(STA)</sub>  | Setup for repeated start             |                               | 4.7  |         | μs   |

| t <sub>su(DAT)</sub>  | Data setup time                      | Host drives SDA               | 250  |         | ns   |

| t <sub>h(DAT)</sub>   | Data hold time                       | Host drives SDA               | 0    |         | ns   |

| t <sub>su(STOP)</sub> | Setup time for stop                  |                               | 4    |         | μs   |

| t <sub>(BUF)</sub>    | Bus free time between stop and start | Includes Command Waiting Time | 66   |         | μs   |

| t <sub>f</sub>        | SCL or SDA fall time <sup>(1)</sup>  |                               |      | 300     | ns   |

| t <sub>r</sub>        | SCL or SDA rise time <sup>(1)</sup>  |                               |      | 300     | ns   |

| f <sub>SCL</sub>      | Clock frequency <sup>(2)</sup>       |                               |      | 100     | kHz  |

| Fast Mode             | e (400 kHz)                          |                               |      |         |      |

| t <sub>d(STA)</sub>   | Start to first falling edge of SCL   |                               | 600  |         | ns   |

| t <sub>w(L)</sub>     | SCL pulse duration (low)             |                               | 1300 |         | ns   |

| t <sub>w(H)</sub>     | SCL pulse duration (high)            |                               | 600  |         | ns   |

| t <sub>su(STA)</sub>  | Setup for repeated start             |                               | 600  |         | ns   |

| t <sub>su(DAT)</sub>  | Data setup time                      | Host drives SDA               | 100  |         | ns   |

| t <sub>h(DAT)</sub>   | Data hold time                       | Host drives SDA               | 0    |         | ns   |

| t <sub>su(STOP)</sub> | Setup time for stop                  |                               | 600  |         | ns   |

| t <sub>(BUF)</sub>    | Bus free time between stop and start | Includes Command Waiting Time | 66   |         | μs   |

| t <sub>f</sub>        | SCL or SDA fall time <sup>(1)</sup>  |                               |      | 300     | ns   |

| t <sub>r</sub>        | SCL or SDA rise time <sup>(1)</sup>  |                               |      | 300     | ns   |

| f <sub>SCL</sub>      | Clock frequency <sup>(2)</sup>       |                               |      | 400     | kHz  |

| f <sub>SCL</sub>      | Clock frequency <sup>(2)</sup>       |                               |      | 400     |      |

(1) Specified by design. Not production tested.

(2) If the clock frequency ( $f_{SCL}$ ) is > 100 kHz, use 1-byte write commands for proper operation. All other transactions types are supported at 400 kHz. (See  $\frac{PC}{C}$  Interface and  $\frac{PC}{C}$  Command Waiting Time.)

Figure 1. I<sup>2</sup>C-Compatible Interface Timing Diagram

## 6.12 SHUTDOWN and WAKE-UP Timing

\* GPOUT is configured as an input for wakeup signaling.

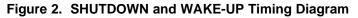

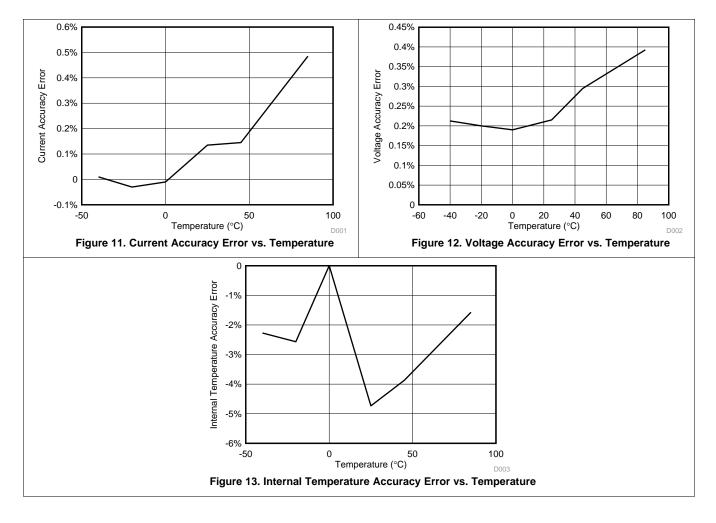

## 6.13 Typical Characteristics

## 7 Detailed Description

## 7.1 Overview

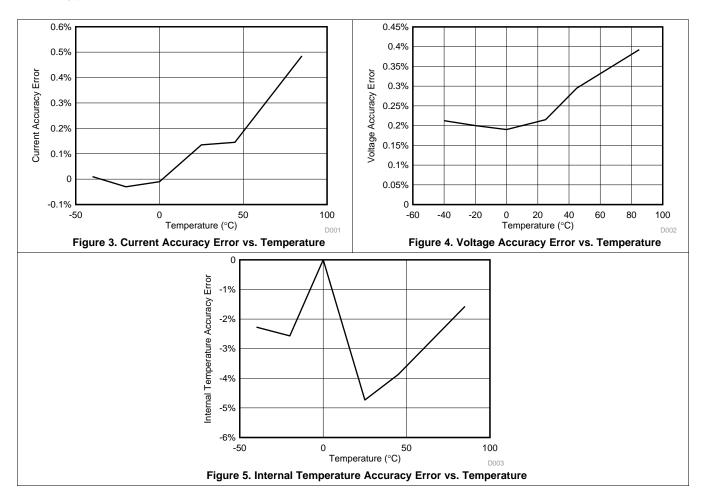

The bq27220 fuel gauge accurately predicts the battery capacity and other operational characteristics of a single Li-based rechargeable cell. It can be interrogated by a system processor to provide cell information such as state-of-charge (SoC). The bq27220 monitors charge and discharge activity by sensing the voltage across a small value resistor (10 m $\Omega$  typical) between the SRP and SRN pins and in series with the battery. By integrating charge passing through the battery, the battery's SOC is adjusted during battery charge or discharge.

The fuel gauging is derived from the Compensated End of Discharge Voltage (CEDV) method, which uses a mathematical model to correlate remaining state of charge (RSOC) and voltage near to the end of discharge state. This requires a full discharge cycle for a single point FCC update. The implementation models cell voltage (OCV) as a function of battery state of charge (SOC), temperature, and current. The impedance is also a function of SOC and temperature, all of which can be satisfied by using seven parameters: EMF, C0, R0, T0, R1, TC, C1.

## NOTE

The following formatting conventions are used in this document:

Commands: italics with parentheses() and no breaking spaces, for example, Control().

Data Flash: italics, bold, and breaking spaces, for example, Design Capacity.

Register bits and flags: italics with brackets [], for example, [TDA]

Data flash bits: italics, bold, and brackets [], for example, [LED1]

Modes and states: ALL CAPITALS, for example, UNSEALED mode.

## 7.2 Functional Block Diagram (System-Side Configuration)

## 7.3 Feature Description

Information is accessed through a series of commands called *Standard Commands*. Further capabilities are provided by the additional *Extended Commands* set. Both sets of commands, indicated by the general format *Command*), are used to read and write information within the control and status registers, as well as its data locations. Commands are sent from the system to the gauge using the I<sup>2</sup>C serial communications engine, and can be executed during application development, system manufacture, or end-equipment operation.

The fuel gauge measures the charging and discharging of the battery by monitoring the voltage across a small-value sense resistor. When a cell is attached to the fuel gauge, cell impedance is computed based on cell current, cell open-circuit voltage (OCV), and cell voltage under loading conditions.

The fuel gauge uses an integrated temperature sensor for estimating cell temperature. Alternatively, the host processor can provide temperature data for the fuel gauge.

Copyright © 2016, Texas Instruments Incorporated

#### Feature Description (continued)

For more details, see the bq27220 Technical Reference Manual (SLUUBD4).

The external temperature sensing is optimized with the use of a high accuracy negative temperature coefficient (NTC) thermistor with R25 =  $10.0 \text{ k}\Omega \pm 1\%$ . B25/85 =  $3435\text{K} \pm 1\%$  (such as Semitec NTC 103AT) on the BIN pin. Alternatively, the bq27220 can also be configured to use its internal temperature sensor or receive temperature data from the host processor. The bq27220 uses temperature to monitor the battery-pack environment, which is used for fuel gauging and cell protection functionality.

#### 7.3.1 Communications

#### 7.3.1.1 <sup>P</sup>C Interface

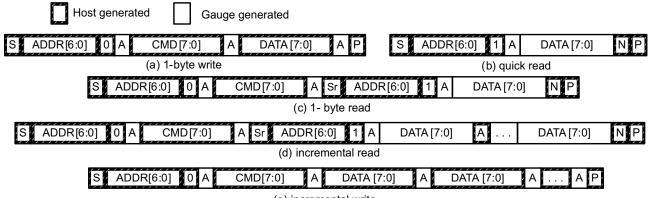

The fuel gauge supports the standard I<sup>2</sup>C read, incremental read, quick read, one-byte write, and incremental write functions. The 7-bit device address (ADDR) is the most significant 7 bits of the hex address and is fixed as 1010101. The first 8 bits of the I<sup>2</sup>C protocol are, therefore, 0xAA or 0xAB for write or read, respectively.

(e) incremental write

(S = Start, Sr = Repeated Start, A = Acknowledge, N = No Acknowledge, and P = Stop).

#### Figure 6. I<sup>2</sup>C Interface Read and Write Functions

The quick read returns data at the address indicated by the address pointer. The address pointer, a register internal to the I<sup>2</sup>C communication engine, increments whenever data is acknowledged by the fuel gauge or the I<sup>2</sup>C master. "Quick writes" function in the same manner and are a convenient means of sending multiple bytes to consecutive command locations (such as two-byte commands that require two bytes of data).

The following command sequences are not supported:

|             | r <i></i> . |   | ·····     |   | 2   |

|-------------|-------------|---|-----------|---|-----|

| S ADDR[6:0] | CMD[7:0]    | A | DATA[7:0] | Ν | P   |

|             |             | 1 | r         |   | 5-1 |

Figure 7. Attempt to Write a Read-Only Address (NACK After Data Sent By Master)

| R - K       |          |       |   |

|-------------|----------|-------|---|

| S ADDR[6:0] | CMD[7:0] | 1 N I | Ρ |

|             |          | u r-  | _ |

#### Figure 8. Attempt to Read an Address Above 0x6B (NACK Command)

#### 7.3.1.2 *P*C Time Out

The I<sup>2</sup>C engine releases both SDA and SCL if the I<sup>2</sup>C bus is held low for 2 seconds. If the fuel gauge is holding the lines, releasing them frees them for the master to drive the lines. If an external condition is holding either of the lines low, the I<sup>2</sup>C engine enters the low-power SLEEP mode.

#### Feature Description (continued)

#### 7.3.1.3 PC Command Waiting Time

To ensure proper operation at 400 kHz, a  $t_{(BUF)} \ge 66 \ \mu s$  bus-free waiting time must be inserted between all packets addressed to the fuel gauge. In addition, if the SCL clock frequency ( $f_{SCL}$ ) is > 100 kHz, use individual 1-byte write commands for proper data flow control. Figure 9 shows the standard waiting time required between issuing the control subcommand the reading the status result. For read-write standard commands, a minimum of 2 seconds is required to get the result updated. For read-only standard commands, there is no waiting time required, but the host must not issue any standard command more than two times per second. Otherwise, the gauge could result in a reset issue due to the expiration of the watchdog timer.

| S ADDR [6:0] 0 A | CMD [7:0]                                                                                   | A DATA [7 | :0] A P     | 66μs       |   |            |    |      |  |  |  |

|------------------|---------------------------------------------------------------------------------------------|-----------|-------------|------------|---|------------|----|------|--|--|--|

| S ADDR [6:0] 0 A | CMD [7:0]                                                                                   | A DATA [7 | :0] A P     | 66μs       |   |            |    |      |  |  |  |

| S ADDR [6:0] 0 A | CMD [7:0]                                                                                   | A Sr ADDF | R [6:0] 1 A | DATA [7:0] | A | DATA [7:0] | ΝP | 66µs |  |  |  |

| Waiting ti       | Waiting time inserted between two 1-byte write packets for a subcommand and reading results |           |             |            |   |            |    |      |  |  |  |

(required for 100 kHz <  $f_{scl} \le 400$  kHz)

| S ADDR [6:0] 0 A | CMD [7:0] |      | DATA [7:0] | A | DATA [7:0]   | AP | 66µs       |     |      |

|------------------|-----------|------|------------|---|--------------|----|------------|-----|------|

| S ADDR [6:0] 0 A | CMD [7:0] | A Sr | ADDR [6:0] | 1 | A DATA [7:0] | A  | DATA [7:0] | N P | 66µs |

Waiting time inserted between incremental 2-byte write packet for a subcommand and reading results

(acceptable for  $f_{SCL} \leq 100 \text{ kHz}$ )

| S ADDR [6:0 |   | A CMD [7:0] | A  | Sr ADDR | [6:0] <b>1</b> A | DATA [7:0] | A | DATA [7:0] | A |

|-------------|---|-------------|----|---------|------------------|------------|---|------------|---|

| DATA [7:0]  | A | DATA [7:0]  | NP | 66µs    |                  |            |   |            |   |

Waiting time inserted after incremental read

#### Figure 9. Standard Waiting Time

#### 7.3.1.4 $m \ell^2 C$ Clock Stretching

A clock stretch can occur during all modes of fuel gauge operation. In SLEEP mode, a short  $\leq$  100-µs clock stretch occurs on all I<sup>2</sup>C traffic as the device must wake-up to process the packet. In the other modes (INITIALIZATION, NORMAL), a  $\leq$  4-ms clock stretching period may occur within packets addressed for the fuel gauge as the I<sup>2</sup>C interface performs normal data flow control.

#### 7.4 Device Functional Modes

To minimize power consumption, the fuel gauge has several power modes: INITIALIZATION, NORMAL, and SLEEP. The fuel gauge passes automatically between these modes, depending upon the occurrence of specific events, though a system processor can initiate some of these modes directly. For more details, see the *bq27220 Technical Reference Manual* (SLUUBD4).

TEXAS INSTRUMENTS

www.ti.com.cn

## 8 Application and Implementation

#### NOTE

Information in the following application section is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1 Application Information

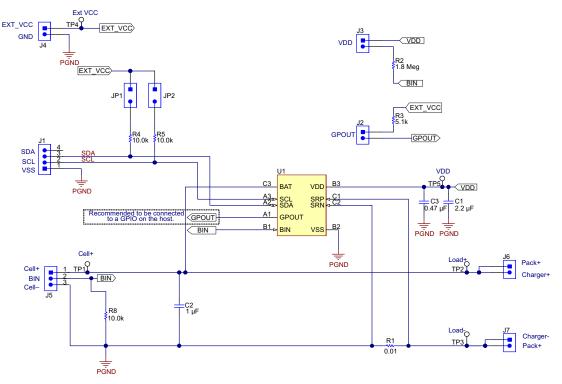

The bq27220 fuel gauge is a microcontroller peripheral that provides system-side or pack-side fuel gauging for single-cell Li-Ion batteries. The device requires minimal configuration and uses One-Time Programmable (OTP) Non-Volatile Memory (NVM). Battery fuel gauging with the fuel gauge requires connections only to PACK+ and PACK– for a removable battery pack or embedded battery circuit. To allow for optimal performance in the end application, special considerations must be taken to ensure minimization of measurement error through proper printed circuit board (PCB) board layout. Such requirements are detailed in *Design Requirements*.

### 8.2 Typical Applications

Figure 10. Typical Application for Pack-Side Using Low-Side Sensing

#### 8.2.1 Design Requirements

As shipped from the Texas Instruments factory, many bq27220 parameters in OTP NVM are left in the unprogrammed state (zero). This partially programmed configuration facilitates customization for each end application. Upon device reset, the contents of OTP are copied to associated volatile RAM-based data memory blocks. For proper operation, all parameters in RAM-based data memory require initialization — either by updating data memory parameters in a lab/evaluation situation or by programming the OTP for customer production. The *bq27220 Technical Reference Manual* (SLUUBD4) shows the default value and a typically expected value appropriate for most of applications.

### **Typical Applications (continued)**

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 BAT Voltage Sense Input

A ceramic capacitor at the input to the BAT pin is used to bypass AC voltage ripple to ground, greatly reducing its influence on battery voltage measurements. It proves most effective in applications with load profiles that exhibit high-frequency current pulses (that is, cell phones) but is recommended for use in all applications to reduce noise on this sensitive high-impedance measurement node.

#### 8.2.2.2 Integrated LDO Capacitor

The fuel gauge has an integrated LDO with an output on the  $V_{DD}$  pin of approximately 1.8 V. A capacitor with a value of at least 2.2  $\mu$ F should be connected between the  $V_{DD}$  pin and  $V_{SS}$ . The capacitor must be placed close to the gauge IC and have short traces to both the  $V_{DD}$  pin and  $V_{SS}$ . This regulator must not be used to provide power for other devices in the system.

#### 8.2.2.3 Sense Resistor Selection

Any variation encountered in the resistance present between the SRP and SRN pins of the fuel gauge will affect the resulting differential voltage, and derived current, that it senses. As such, it is recommended to select a sense resistor with minimal tolerance and temperature coefficient of resistance (TCR) characteristics. The standard recommendation based on the best compromise between performance and price is a 1% tolerance, 50-ppm drift sense resistor with a 1-W power rating.

#### 8.2.3 External Thermistor Support

The fuel gauge temperature sensing circuitry is designed to work with a negative temperature coefficient-type (NTC) thermistor with a characteristic 10-k $\Omega$  resistance at room temperature (25°C). The default curve-fitting coefficients configured in the fuel gauge specifically assume a Semitec 103AT type thermistor profile and so that is the default recommendation for thermistor selection purposes. Moving to a separate thermistor resistance profile (for example, JT-2 or others) requires an update to the default thermistor coefficients, which can be modified in RAM to ensure highest accuracy temperature measurement performance.

**bq27220** ZHCSEX1A – MARCH 2016–REVISED APRIL 2016

www.ti.com.cn

## **Typical Applications (continued)**

## 8.2.4 Application Curves

## 9 Power Supply Recommendation

### 9.1 Power Supply Decoupling

The battery connection on the BAT pin is used for two purposes:

- To supply power to the fuel gauge, and

- To provide an input for voltage measurement of the battery.

A capacitor of value of at least 1  $\mu$ F should be connected between BAT and V<sub>SS</sub>. The capacitor must be placed close to the gauge IC and have short traces to both the BAT pin and V<sub>SS</sub>.

The fuel gauge has an integrated LDO with an output on the V<sub>DD</sub> pin of approximately 1.8 V. A capacitor of value of at least 2.2  $\mu$ F should be connected between the V<sub>DD</sub> pin and V<sub>SS</sub>. The capacitor must be placed close to the gauge IC and have short traces to both the V<sub>DD</sub> pin and V<sub>SS</sub>. This regulator must not be used to provide power for other devices in the system.

## 10 Layout

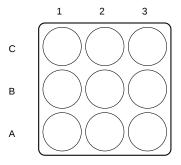

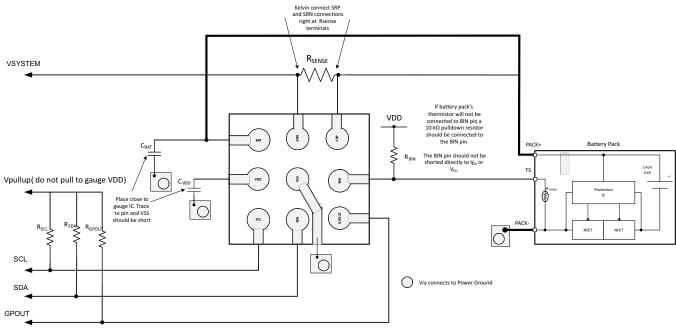

#### 10.1 Layout Guidelines

- A capacitor of value of at least 2.2 µF is connected between the V<sub>DD</sub> pin and V<sub>SS</sub>. The capacitor must be placed close to the gauge IC and have short traces to both the V<sub>DD</sub> pin and V<sub>SS</sub>. This regulator must not be used to provide power for other devices in the system.

- It is required to have a capacitor of at least 1.0 µF connect between the BAT pin and V<sub>SS</sub> if the connection between the battery pack and the gauge BAT pin has the potential to pick up noise. The capacitor should be placed close to the gauge IC and have short traces to both the BAT pin and V<sub>SS</sub>.

- If the external pullup resistors on the SCL and SDA lines will be disconnected from the host during low-power operation, it is recommended to use external 1-MΩ pulldown resistors to V<sub>SS</sub> to avoid floating inputs to the I<sup>2</sup>C engine.

- The value of the SCL and SDA pullup resistors should take into consideration the pullup voltage and the bus capacitance. Some recommended values, assuming a bus capacitance of 10 pF, can be seen in Table 1.

| VPU             | 1.8 V                                          |         | 3.3 V                             |         |  |  |

|-----------------|------------------------------------------------|---------|-----------------------------------|---------|--|--|

| D               | Range                                          | Typical | Range                             | Typical |  |  |

| R <sub>PU</sub> | $400 \ \Omega \leq R_{PU} \leq 37.6 \ k\Omega$ | 10 kΩ   | 900 Ω ≤ R <sub>PU</sub> ≤ 29.2 kΩ | 5.1 kΩ  |  |  |

#### Table 1. Recommended Values for SCL and SDA Pullup Resistors

- If the host is not using the GPOUT functionality, then it is recommended that GPOUT be connected to a GPIO of the host so that in the cases where the device is in SHUTDOWN, toggling GPOUT can wake the gauge from the SHUTDOWN state.

- If the battery pack thermistor is not connected to the BIN pin, the BIN pin should be pulled down to  $V_{SS}$  with a 10-k $\Omega$  resistor.

- The BIN pin should not be shorted directly to V<sub>DD</sub> or V<sub>SS</sub>.

- The actual device ground is pin B2 (V<sub>SS</sub>).

- The SRP and SRN pins should be Kelvin connected to the R<sub>SENSE</sub> terminals. SRP to the battery pack side of R<sub>SENSE</sub> and SRN to the system side of the R<sub>SENSE</sub>.

- Kelvin connect the BAT pin to the battery PACKP terminal.

**bq27220** ZHCSEX1A – MARCH 2016– REVISED APRIL 2016

www.ti.com.cn

## 10.2 Layout Example

### 11 器件和文档支持

### 11.1 文档支持

## 11.1.1 相关文档

- 《bq27220 技术参考》手册(文献编号: SLUUBD4)

- 《bg27220 快速入门指南》(文献编号: SLUUAP7)

- 《单节电池电量监测计电路设计》(SLUA456)

- 《bq27500 和 bq27501 主要设计注意事项》(SLUA439)

- 《手持式电池电子产品中的 ESD 和 RF 迁移》(SLUA460)

#### 11.2 社区资源

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support TI's Design Support** Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 11.3 商标

NanoFree, E2E are trademarks of Texas Instruments. I<sup>2</sup>C is a trademark of NXP Semiconductors, N.V. All other trademarks are the property of their respective owners.

#### 11.4 静电放电警告

ESD 可能会损坏该集成电路。德州仪器 (TI) 建议通过适当的预防措施处理所有集成电路。如果不遵守正确的处理措施和安装程序,可能会损坏集成电路。

**ESD** 的损坏小至导致微小的性能降级,大至整个器件故障。精密的集成电路可能更容易受到损坏,这是因为非常细微的参数更改都可能会导致器件与其发布的规格不相符。

#### 11.5 Glossary

#### SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

#### 12 机械、封装和可订购信息

以下页中包括机械、封装和可订购信息。这些信息是针对指定器件可提供的最新数据。这些数据会在无通知且不对 本文档进行修订的情况下发生改变。欲获得该数据表的浏览器版本,请查阅左侧的导航栏。

10-Dec-2020

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| BQ27220YZFR      | ACTIVE        | DSBGA        | YZF                | 9    | 3000           | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 85    | BQ27220                 | Samples |

| BQ27220YZFT      | ACTIVE        | DSBGA        | YZF                | 9    | 250            | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 85    | BQ27220                 | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <= 1000ppm threshold. Antimony trioxide based flame retardants must also meet the <= 1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com

## PACKAGE OPTION ADDENDUM

10-Dec-2020

Texas

STRUMENTS

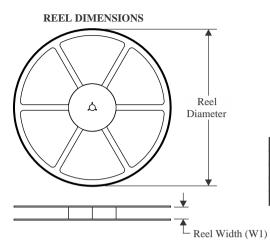

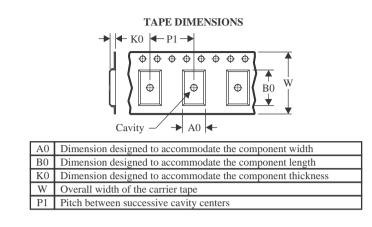

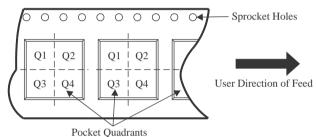

## TAPE AND REEL INFORMATION

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |       |                    |   |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | •     | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| BQ27220YZFR                 | DSBGA | YZF                | 9 | 3000 | 180.0                    | 8.4                      | 1.78       | 1.78       | 0.69       | 4.0        | 8.0       | Q1               |

| BQ27220YZFT                 | DSBGA | YZF                | 9 | 250  | 180.0                    | 8.4                      | 1.78       | 1.78       | 0.69       | 4.0        | 8.0       | Q1               |

www.ti.com

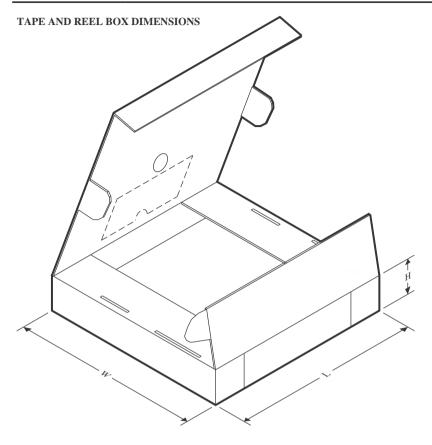

# PACKAGE MATERIALS INFORMATION

31-Jul-2023

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| BQ27220YZFR | DSBGA        | YZF             | 9    | 3000 | 182.0       | 182.0      | 20.0        |

| BQ27220YZFT | DSBGA        | YZF             | 9    | 250  | 182.0       | 182.0      | 20.0        |

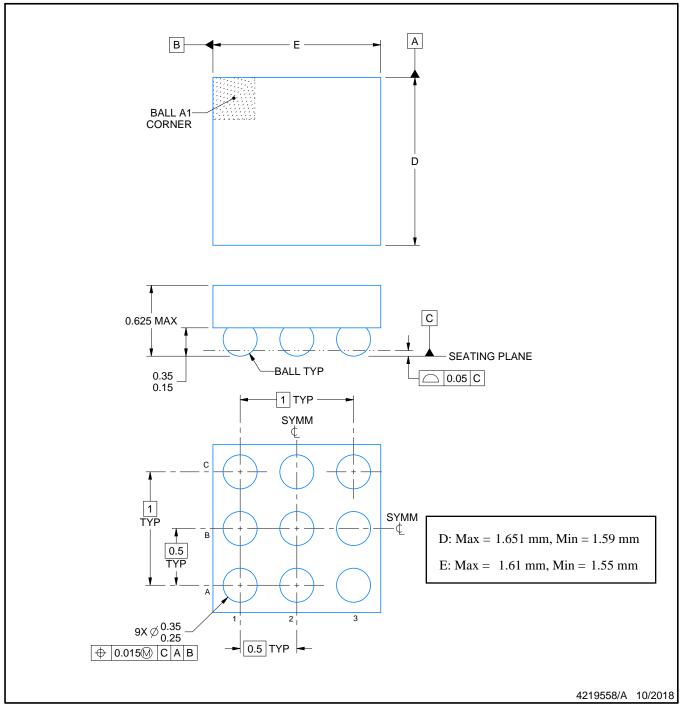

# **YZF0009**

# **PACKAGE OUTLINE**

## DSBGA - 0.625 mm max height

DIE SIZE BALL GRID ARRAY

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice.

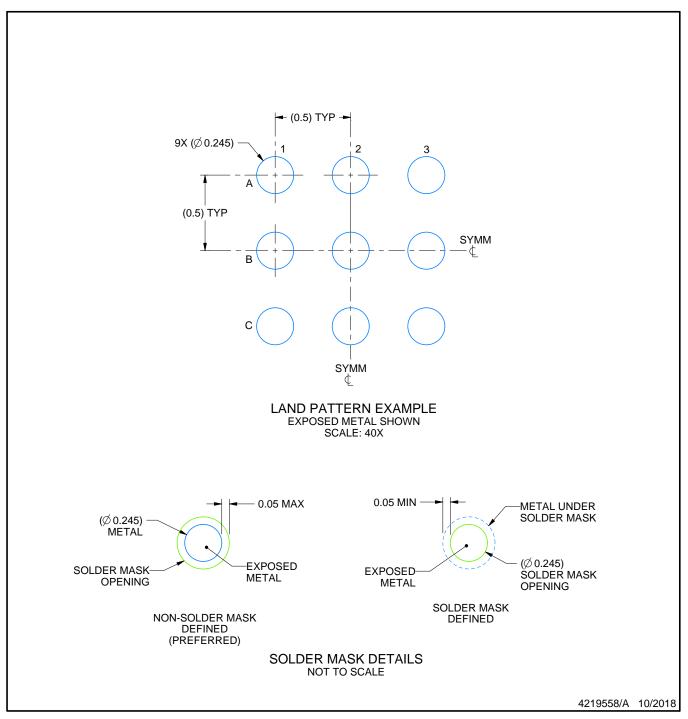

# YZF0009

# **EXAMPLE BOARD LAYOUT**

## DSBGA - 0.625 mm max height

DIE SIZE BALL GRID ARRAY

NOTES: (continued)

Final dimensions may vary due to manufacturing tolerance considerations and also routing constraints. See Texas Instruments Literature No. SNVA009 (www.ti.com/lit/snva009).

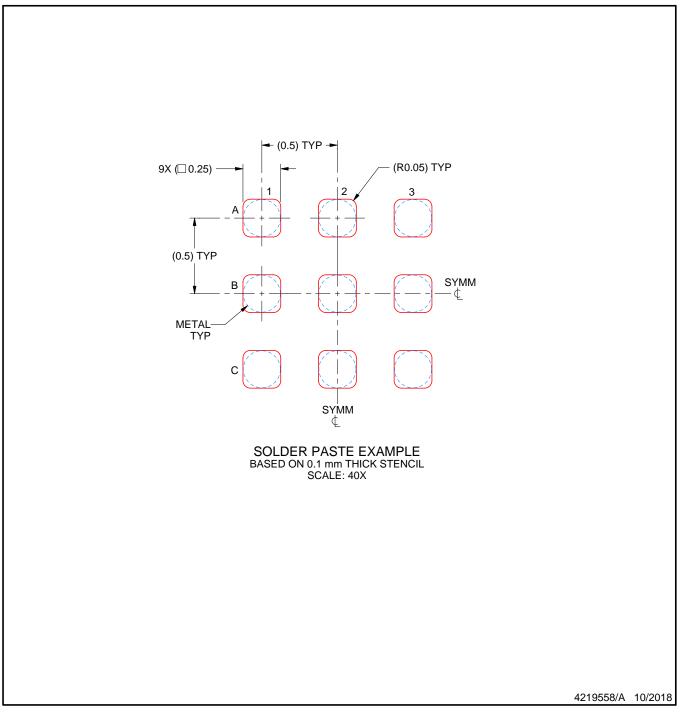

# YZF0009

# **EXAMPLE STENCIL DESIGN**

## DSBGA - 0.625 mm max height

DIE SIZE BALL GRID ARRAY

NOTES: (continued)

4. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release.

#### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源, 不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担 保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。 您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成 本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023,德州仪器 (TI) 公司