**BQ25756**

ZHCSOK3 - AUGUST 2023

# BQ25756:独立/I<sup>2</sup>C 控制型、1 至 14 节电池双向降压/升压电池充电控制器

# 1 特性

- 宽输入电压工作范围:4.2V 至 70V

- 宽电池电压工作范围:高达 70V,支持多化合物电

- 1 节至 14 节锂离子电池充电曲线

- 1 节至 16 节磷酸铁锂电池充电曲线

- 具有 NFET 驱动器的同步降压/升压充电控制器

- 可调节开关频率范围:200kHz 至 600kHz

- 一 可选择与外部时钟同步

- 带有软启动的集成环路补偿

- 可选栅极驱动器电源输入,可提高效率

- 用于太阳能充电的自动最大功率点跟踪 (MPPT)

- 仅降压模式

- 双向转换器运行(反向模式),支持 USB-PD 扩展 功率范围 (EPR)

- 可调输入电压 (VAC) 调节范围为 3.3V 至 65V, 步长为 20mV

- 使用 5mΩ 电阻器实现可调输入电流调节 (R<sub>AC SNS</sub>), 范围为 400mA 至 20A, 步长为 50mĀ

#### 高精度

- ±0.5% 充电 电压调节

- +3% 充电电流调节

- 输入电流调节范围为 ±3%

- 通过 I<sup>2</sup>C 控制,用于通过电池可编程选项实现出色 的系统性能

- 硬件可调输入和输出电流限制

- 用于电压、电流和温度监控的集成 16 位 ADC

- 高安全集成

- 可调输入过压和欠压保护

- 电池过压和过流保护

- 充电安全计时器

- 电池短路保护

- 热关断

- 状态输出

- 适配器存在状态 (PG)

- 充电器运行状态(STAT1、STAT2)

- 封装

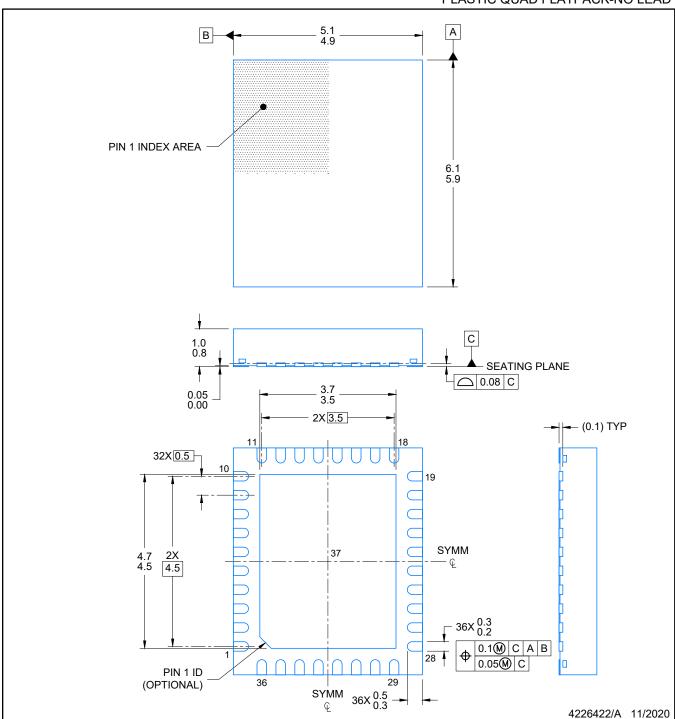

- 36 引脚 5mm × 6mm QFN 封装

### 2 应用

- 脚踢电动踏板车、电动自行车

- 无线电动工具、园艺工具

- 割草机器人

- 移动式发电站

- 无线真空吸尘器、扫地机器人

- 太阳能充电器

- USB-PD EPR(扩展功率范围)

# 3 说明

BQ25756 是一款具有双向功率流支持的宽输入电压、 开关模式降压/升压锂离子、锂聚合物或磷酸铁锂电池 充电控制器。该器件不仅能提供精确的充电电流和充电 电压调节,还能提供自动充电预调节、充电终止和充电 状态指示,可在宽电压范围内实现电池高效充电。该器 件集成了降压/升压转换器的所有环路补偿功能,因此 可提供易于使用的高密度解决方案。在反向模式下,该 器件从电池获取电力并通过添加的恒定电流环路调节输 入端子电压来实现保护,从而支持 USB-PD EPR 功率 配置。

#### 器件信息

| 器件型号(1) | 封装        | 封装尺寸 ( 标称值 )               |

|---------|-----------|----------------------------|

| BQ25756 | VQFN (36) | 5.0mm x 6.0mm <sup>2</sup> |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

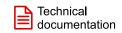

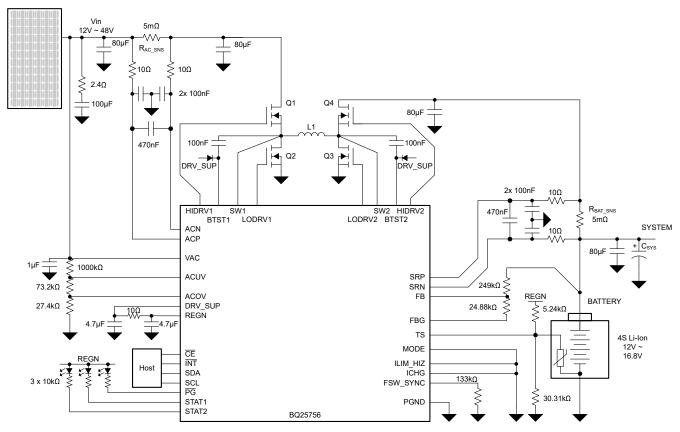

简化原理图

English Data Sheet: SLUSEN5

# **Table of Contents**

| <b>1 特性</b> 1                         | 8.4 Device Functional Modes             | 38              |

|---------------------------------------|-----------------------------------------|-----------------|

| 2 应用 1                                | 8.5 BQ25756 Registers                   | 40              |

| 3 说明 1                                | 9 Application and Implementation        |                 |

| 4 Revision History2                   | 9.1 Application Information             |                 |

| 5 说明(续)3                              | 9.2 Typical Applications                |                 |

| 6 Pin Configuration and Functions4    | 10 Power Supply Recommendations         |                 |

| 7 Specifications 7                    | 11 Layout                               | 74              |

| 7.1 Absolute Maximum Ratings7         | 11.1 Layout Guidelines                  | 74              |

| 7.2 ESD Ratings7                      | 11.2 Layout Example                     |                 |

| 7.3 Recommended Operating Conditions7 | 12 Device and Documentation Support     | <mark>77</mark> |

| 7.4 Thermal Information8              | 12.1 Device Support                     | <mark>77</mark> |

| 7.5 Electrical Characteristics9       | 12.2 接收文档更新通知                           | <mark>77</mark> |

| 7.6 Timing Requirements15             | 12.3 支持资源                               | <mark>77</mark> |

| 7.7 Typical Characteristics16         | 12.4 Trademarks                         | <mark>77</mark> |

| 8 Detailed Description19              | 12.5 静电放电警告                             | <mark>77</mark> |

| 8.1 Overview19                        | 12.6 术语表                                | <mark>77</mark> |

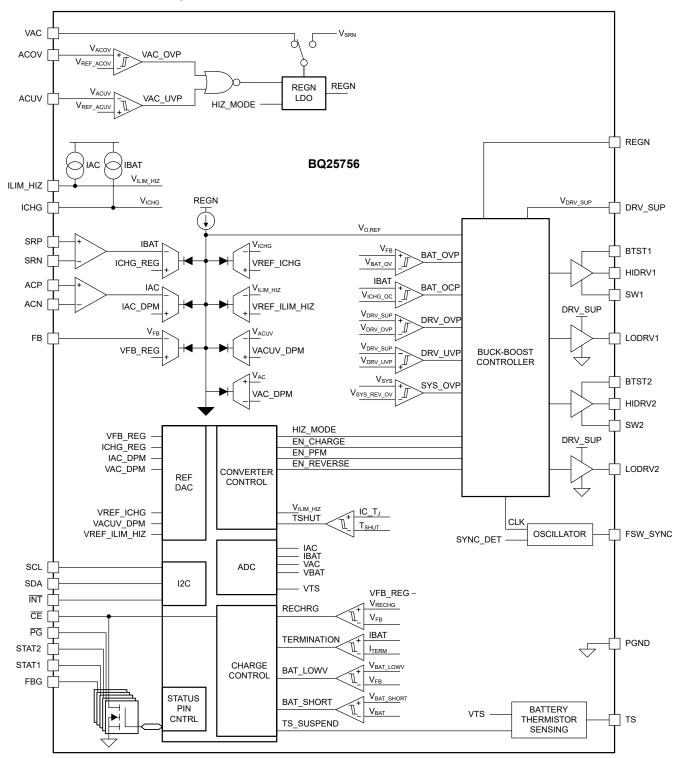

| 8.2 Functional Block Diagram20        | 13 Mechanical, Packaging, and Orderable |                 |

| 8.3 Feature Description21             | Information                             | <mark>78</mark> |

|                                       |                                         |                 |

4 Revision History 注:以前版本的页码可能与当前版本的页码不同

| DATE        |   |                 |

|-------------|---|-----------------|

| August 2023 | * | Initial Release |

# 5 说明(续)

除了  $I^2C$  主机控制的充电模式,该器件还通过电阻器可编程限制支持独立充电模式。输入电流、充电电流和充电电压调节目标可分别通过  $ILIM\_HIZ$ 、ICHG 和 FB 引脚进行设置。

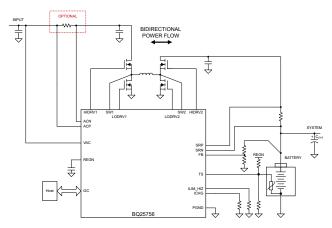

# **6 Pin Configuration and Functions**

图 6-1. BQ25756, RRV Package 36-pin VQFN Top View

表 6-1. Pin Functions

| PIN      |   | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|----------|---|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO. |   | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| SCL      | 1 | 1   | I²C Interface Clock – Connect SCL to the logic rail through a 10-kΩ resistor.                                                                                                                                                                                                                                                                                                                      |  |  |

| SDA      | 2 | Ю   | <sup>2</sup> C Interface Data – Connect SDA to the logic rail through a 10-kΩ resistor.                                                                                                                                                                                                                                                                                                            |  |  |

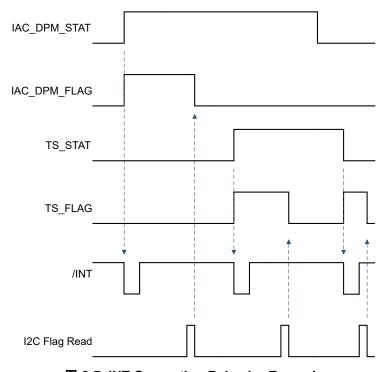

| INT      | 3 | 0   | <b>Open Drain Interrupt Output –</b> Connect the $\overline{\text{INT}}$ pin to a logic rail via 10-kΩ resistor. The $\overline{\text{INT}}$ pin sends an active low, 256-μs pulse to host to report the charger device status and faults.                                                                                                                                                         |  |  |

| STAT1    | 4 | 0   | <b>Open Drain Charge Status 1 Output –</b> STAT1 and STAT2 indicate various charger operations, see 表 8-6. Connect to the pull up rail via 10-k $\Omega$ resistor. The STAT1, STAT2 pin functions can be disabled when DIS_STAT_PINS bit is set to 1. When disabled, this pin can be used as a general purpose indicator via the FORCE_STAT1_ON bit.                                               |  |  |

| STAT2    | 5 | 0   | Open Drain Charge Status 2 Output – STAT1 and STAT2 indicate various charger operations, see 表 8-6. Connect to the pull up rail via 10-k $\Omega$ resistor. The STAT1, STAT2 pin functions can be disabled when DIS_STAT_PINS bit is set to 1. When disabled, this pin can be used as a general purpose indicator via the FORCE_STAT2_ON bit.                                                      |  |  |

| PG       | 6 | 0   | Open Drain Active Low Power Good Indicator – Connect to the pull up rail via 10-kΩ resistor. LOW indicates a good input source if VAC is within the programmed ACUV / ACOV operating window. The PG pin function can be disabled when DIS_PG_PIN bit is set to 1. When disabled, this pin can be used as a general purpose indicator via the FORCE_STAT3_ON bit.                                   |  |  |

| CE 7     |   | Ю   | Active Low Charge Enable Pin – Battery charging is enabled when EN_CHG bit is 1 and $\overline{\mathbb{CE}}$ pin is LOW. $\overline{\mathbb{CE}}$ pin must be pulled HIGH or LOW, do not leave floating. The $\overline{\mathbb{CE}}$ pin function can be disabled when DIS_CE_PIN bit is set to 1. When disabled, this pin can be used as a general purpose indicator via the FORCE_STAT4_ON bit. |  |  |

# 表 6-1. Pin Functions (continued)

| PIN      |     | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | 1,0 | DEGGAIF HOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

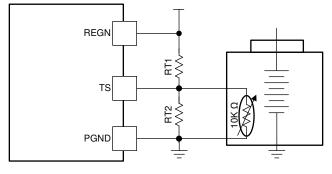

| TS       | 8   | I   | Temperature Qualification Voltage Input – Connect a negative temperature coefficient thermistor. Program temperature window with a resistor divider from REGN to TS to PGND. Charge suspends when TS pin voltage is out of range. Recommend 103AT-2 10-kΩ thermistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ICHG     | 9   | I   | Charge Current Limit Setting – ICHG pin sets the maximum charge current, and can be used to monitor the charge current. A programming resistor to PGND is used to set the charge current limit as $I_{CHG} = K_{ICHG}$ . When the device is under charge current regulation, the voltage at ICHG pin is $V_{REF\_ICHG}$ . When ICHG pin voltage is less than $V_{REF\_ICHG}$ , the actual charge current can be calculated as: IBAT = $K_{ICHG}$ x $V_{ICHG}$ / ( $K_{ICHG}$ x $V_{REF\_ICHG}$ ). The actual charge current limit is the lower of the limits set by ICHG pin or the ICHG_REG register bits. This pin function can be disabled when EN_ICHG_PIN bit is 0. If ICHG pin is not used, this pin should be pulled to PGND, do not leave floating.                                                                                                                                                                             |

| ILIM_HIZ | 10  | I   | Input Current Limit Setting and HIZ Mode Control Pin – ILIM_HIZ pin sets the maximum input current limit, can be used to monitor the input current and can be pulled HIGH to force device into HIZ mode. A programming resistor to PGND is used to set the input current limit as $I_{\text{LIM}} = K_{\text{ILIM}} / R_{\text{ILIM}}$ . When the device is under input current regulation, the voltage at ILIM_HIZ pin is $V_{\text{REF\_ILIM}}$ . When ILIM_HIZ pin voltage is less than $V_{\text{REF\_ILIM}}$ , the actual input current can be calculated as: IAC = $K_{\text{ILIM}} \times V_{\text{ILIM}} / (R_{\text{ILIM}} \times V_{\text{REF\_ILIM}})$ . The actual input current limit is the lower of the limits set by ILIM_HIZ pin or the IAC_DPM register bits. This pin function can be disabled when EN_ILIM_HIZ_PIN bit is 0. If ILIM_HIZ pin is not used, this pin should be pulled to PGND, do not leave floating. |

| FBG      | 11  | I   | Voltage Feedback Divider Return – Connect to the bottom of battery feedback resistor. When charging, this pin is driven to PGND internally. When input voltage is outside of the ACUV / ACOV operating window, this pin is high-impedance, minimizing battery leakage current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FB       | 12  | I   | Charge Voltage Analog Feedback Adjustment – Connect the output of a resistive voltage divider from the battery terminals to this node to adjust the output battery regulation voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SRN      | 13  | ı   | Charge Current-Sense Resistor, Negative Input – A 0.47-μF ceramic capacitor is placed from SRN to SRP to provide differential-mode filtering. An optional 0.1-μF ceramic capacitor is placed from the SRN pin to PGND for common-mode filtering.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SRP      | 14  | 1   | Charge Current-Sense Resistor, Positive Input – A 0.47-μF ceramic capacitor is placed from SRN to SRP to provide differential-mode filtering. A 0.1-μF ceramic capacitor is placed from the SRP pin to PGND for common-mode filtering.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| NC       | 15  | -   | No Connect - Leave this pin floating, do not tie to PGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| NC       | 16  | -   | No Connect - Leave this pin floating, do not tie to PGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PGND     | 17  | -   | Tie this pin directly to PGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SW2      | 18  | Р   | Boost Side Half Bridge Switching Node – Connect to the source of boost HS FET and the drain of boost LS FET. Connect the inductor between SW1 and SW2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| HIDRV2   | 19  | 0   | Boost Side High-Side Gate Driver – Connect to the boost high-side N-channel MOSFET gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BTST2    | 20  | Р   | Boost Side High-Side Power MOSFET Gate Driver Power Supply – Connect a capacitor between BTST2 and SW2 to provide bias to the high-side MOSFET gate driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| LODRV2   | 21  | 0   | Boost Side Low-Side Gate Driver - Connect to the boost low-side N-channel MOSFET gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PGND     | 22  | Р   | Power Ground Return – The high current ground connection for the low-side gate drivers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DRV_SUP  | 23  | Р   | Charger Gate Drive Supply Input – Voltage on this pin is used to drive the gates of buck-boost converter switching FET. Connect a 4.7-µF ceramic capacitor from DRV_SUP to power ground. REGN LDO voltage can be used as the gate driver supply for all switching FETs by connecting REGN to DRV_SUP pin. In high-voltage applications, it is possible to directly provide the DRV_SUP voltage with an external supply up to 12 V to achieve higher switching efficiency. See 节 8.3.3.2 for more details.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| REGN     | 24  | Р   | Charger Internal Linear Regulator Output – Connect a 4.7-µF ceramic capacitor from REGN to power ground. REGN LDO voltage can be used as the gate driver supply for all switching FETs by connecting REGN to DRV_SUP pin. In high-voltage applications, it is possible to directly provide the DRV_SUP voltage with an external supply up to 12 V to achieve higher switching efficiency. See 节8.3.3.2 for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LODRV1   | 25  | 0   | Buck Side Low-Side Gate Driver – Connect to the buck low-side N-channel MOSFET gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BTST1    | 26  | Р   | Buck Side High-Side Power MOSFET Gate Driver Power Supply – Connect a capacitor between BTST1 and SW1 to provide bias to the high-side MOSFET gate driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| HIDRV1   | 27  | 0   | Buck Side High-Side Gate Driver – Connect to the buck high-side N-channel MOSFET gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SW1      | 28  | Р   | Buck Side Half Bridge Switching Node – Connect to the source of buck HS FET and the drain of buck LS FET. Connect the inductor between SW1 and SW2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# 表 6-1. Pin Functions (continued)

| PIN                                    |     | I/O    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|----------------------------------------|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                                   | NO. | 1/0    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| ACN                                    | 29  | I      | Adapter Current-Sense Resistor, Negative Input – A 0.47-µF ceramic capacitor is placed from ACN to ACP to provide differential-mode filtering. An optional 0.1-µF ceramic capacitor is placed from the ACN pin to PGND for common-mode filtering.                                                                                                                                                                                                                                                                                                     |  |  |  |

| ACP                                    | 30  | I      | Adapter Current-Sense Resistor, Positive Input – A 0.47-μF ceramic capacitor is placed from ACN to ACP to provide differential-mode filtering. A 0.1-μF ceramic capacitor is placed from the ACP pin to PGND for common-mode filtering                                                                                                                                                                                                                                                                                                                |  |  |  |

| NC                                     | 31  | -      | No Connect - Leave this pin floating, do not tie to PGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

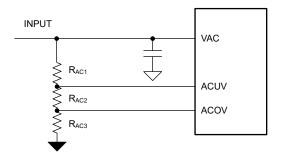

| \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | 32  |        | Input Voltage Detection and Power – Connect a 1-µF capacitor from pin to PGND. Pin 33 is the input                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| VAC                                    | 33  | P      | bias to power the IC, and ACOV/ACUV resistor divider should be connected relative to pin 33. When Reverse Mode is enabled, pin 32 is regulated to VAC_REV.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

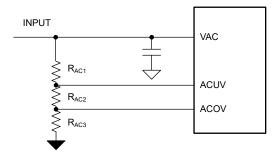

| ACUV                                   | 34  | I      | AC Undervoltage Comparator Input – Connect a resistor divider from VAC to PGND to program the undervoltage protection. When this pin falls below V <sub>REF_ACUV</sub> , the device stops charging. The hardware limit for input voltage regulation reference is V <sub>ACUV_DPM</sub> . The actual input voltage regulation is the higher of the pin-programmed value and the VAC_DPM register value. If ACUV programming is not used, pull this pin to VAC, do not leave floating.                                                                  |  |  |  |

| ACOV                                   | 35  | I      | <b>AC Overvoltage Comparator Input –</b> Connect a resistor divider from VAC to PGND to program the overvoltage protection. When this pin rises above V <sub>REF_ACOV</sub> , the device stops charging. If ACOV programming is not used, pull this pin to PGND, do not leave floating.                                                                                                                                                                                                                                                               |  |  |  |

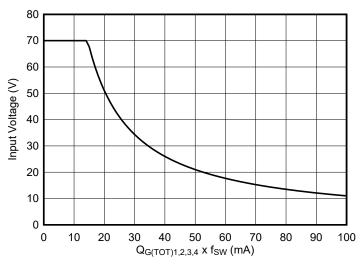

| FSW_SYNC                               | 36  | I      | Switching Frequency and Synchronization Input – An external resistor is connected to the FSW_SYNC pin and PGND to set the nominal switching frequency. This pin can also be used to synchronize the PWM controller to an external clock with 200-kHz to 600-kHz frequency.                                                                                                                                                                                                                                                                            |  |  |  |

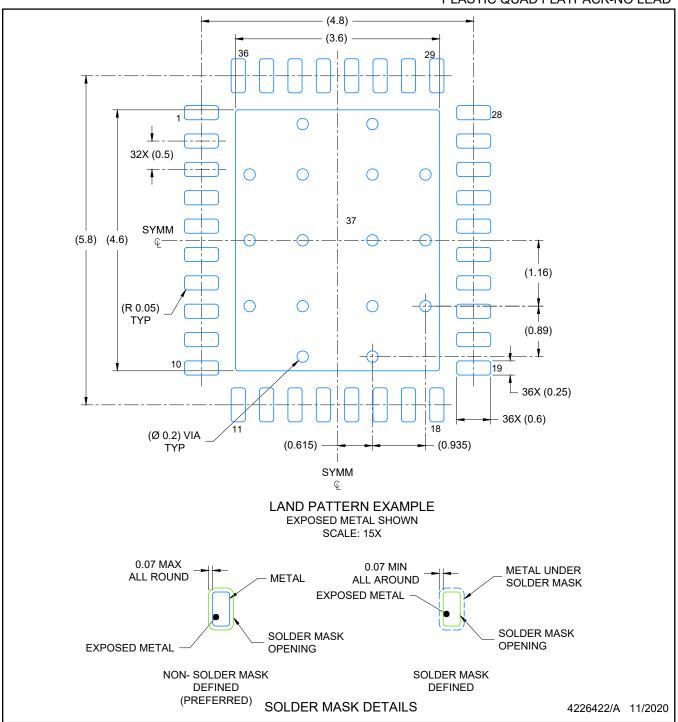

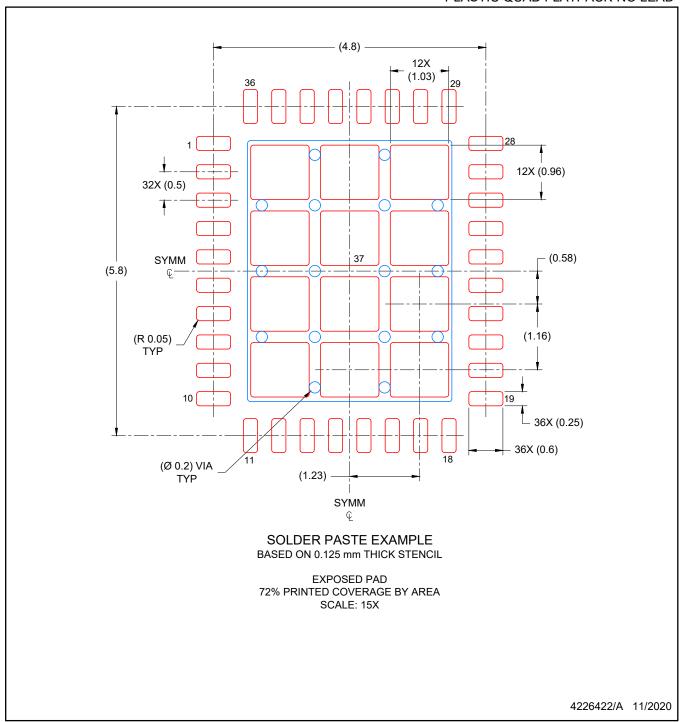

| Thermal Pad                            | 37  | Р      | <b>Exposed pad beneath the IC –</b> Always solder the thermal pad to the board, and have vias on the thermal pad plane star-connecting to PGND and ground plane for high-current power converter. It also serves as a thermal pad to dissipate the heat.                                                                                                                                                                                                                                                                                              |  |  |  |

|                                        |     | l<br>P | programming is not used, pull this pin to PGND, do not leave floating.  Switching Frequency and Synchronization Input – An external resistor is connected to the FSW_SYNC pin and PGND to set the nominal switching frequency. This pin can also be used to synchronize the PWM controller to an external clock with 200-kHz to 600-kHz frequency.  Exposed pad beneath the IC – Always solder the thermal pad to the board, and have vias on the thermal pad plane star-connecting to PGND and ground plane for high-current power converter. It all |  |  |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                        |                                                                           | MIN  | MAX | UNIT |

|------------------------|---------------------------------------------------------------------------|------|-----|------|

| Voltage                | VAC, ACUV, ACOV, ACP, ACN, SRP, SRN, FB, FBG                              | -0.3 | 85  | V    |

| Voltage                | SW1, SW2                                                                  | -2   | 85  | V    |

| Voltage                | SW1, SW2 (40ns transient)                                                 | -4   | 85  | V    |

| Voltage                | PG                                                                        | -0.3 | 40  | V    |

| Voltage                | BTST1, HIDRV1 with respect to SW1                                         | -0.3 | 14  | V    |

| Voltage                | BTST2, HIDRV2 with respect to SW2                                         | -0.3 | 14  | V    |

| Voltage                | DRV_SUP, LODRV1, LODRV2                                                   | -0.3 | 14  | V    |

| Voltage                | ACP with respect to ACN, SRP with respect to SRN                          | -0.3 | 0.3 | V    |

| Voltage                | CE, FSW_SYNC, ICHG, ILIM_HIZ, INT, REGN, SCL, SDA, MODE, STAT1, STAT2, TS | -0.3 | 6   | V    |

| Output Sink<br>Current | CE, PG, STAT1, STAT2                                                      |      | 5   | mA   |

| TJ                     | Junction temperature                                                      | -40  | 150 | °C   |

| T <sub>stg</sub>       | Storage temperature                                                       | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |                         |                                                                                     | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>     |       | \/   |

| V <sub>(ESD)</sub> |                         | Charged device model (CDM), per ANSI/ESDA/<br>JEDEC JS-002, all pins <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                      |                                                              | MIN  | NOM MAX | UNIT |

|----------------------|--------------------------------------------------------------|------|---------|------|

| V <sub>AC</sub>      | Input voltage                                                | 4.2  | 70      | V    |

| V <sub>BAT</sub>     | Battery voltage                                              | 0    | 70      | V    |

| V <sub>DRV_SUP</sub> | DRV_SUP pin direct drive voltage range                       | 4.0  | 12      | V    |

| F <sub>SW</sub>      | Switching Frequency                                          | 200  | 600     | kHz  |

| TJ                   | Junction temperature                                         | -40  | 125     | °C   |

| T <sub>A</sub>       | Ambient temperature                                          | -40  | 105     | °C   |

| C <sub>VAC</sub>     | VAC capacitor                                                | 1    |         | μF   |

| C <sub>IN</sub>      | Buck-boost input capacitance (minimum value after derating)  | 160  |         | μF   |

| C <sub>OUT</sub>     | Buck-boost output capacitance (minimum value after derating) | 160  |         | μF   |

| C <sub>REGN</sub>    | REGN capacitor (nominal value before derating)               | 4.7  |         | μF   |

| C <sub>DRV_SUP</sub> | DRV_SUP capacitor (nominal value before derating)            | 4.7  |         | μF   |

| L                    | Switched Inductor                                            | 2.2  | 15      | μH   |

| R <sub>DCR</sub>     | Inductor DC resistance                                       | 1.75 | 60      | mΩ   |

# 7.3 Recommended Operating Conditions (continued)

over operating free-air temperature range (unless otherwise noted)

|                       |                                        | MIN    | NOM | MAX | UNIT |

|-----------------------|----------------------------------------|--------|-----|-----|------|

| R <sub>AC_SNS</sub>   | Input current sense resistor           | 0(1)   | 5   | 10  | mΩ   |

| R <sub>BAT_SNS</sub>  | Battery current sense resistor         |        | 5   |     | mΩ   |

| R <sub>ICHG</sub>     | ICHG programming pulldown resistor     | 0.0(2) |     | 100 | kΩ   |

| R <sub>ILIM_HIZ</sub> | ILIM_HIZ programming pulldown resistor | 0.0(3) |     | 50  | kΩ   |

- (1) When  $R_{AC\_SNS}$  is  $0m\Omega$ , input current limit function is disabled

- (2) When R<sub>ICHG</sub> is pulled to GND, the hardware charge current limit is disabled, actual charge current is controlled by the ICHG\_REG register setting

- (3) When R<sub>ILIM\_HIZ</sub> is pulled to GND, the hardware input current limit is disabled, actual input current is controlled by the IAC\_DPM register setting

### 7.4 Thermal Information

|                                                                                 |                                              | BQ25756 |      |

|---------------------------------------------------------------------------------|----------------------------------------------|---------|------|

|                                                                                 | THERMAL METRIC(1)                            | RRV     | UNIT |

|                                                                                 |                                              | 36 PINS |      |

| R <sub>θJA</sub> Junction-to-ambient thermal resistance (JEDEC <sup>(1)</sup> ) |                                              | 29.4    | °C/W |

| R <sub>0JC(top)</sub>                                                           | Junction-to-case (top) thermal resistance    | 18.8    | °C/W |

| $R_{\theta JB}$                                                                 | Junction-to-board thermal resistance         | 9.9     | °C/W |

| $\Psi_{JT}$                                                                     | Junction-to-top characterization parameter   | 0.2     | °C/W |

| $\Psi_{JB}$                                                                     | Junction-to-board characterization parameter | 9.8     | °C/W |

| $R_{\theta JC(bot)}$                                                            | Junction-to-case (bottom) thermal resistance | 2.5     | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics

VAC = ACP = ACN = SYS = SRP = SRN = 28V,  $T_J$  = -40°C to +125°C, and  $T_J$  = 25°C for typical values (unless otherwise noted)

|                            | PARAMETER                                                                                      | TEST CONDITIONS                                                       | MIN        | TYP   | MAX   | UNIT      |

|----------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------|-------|-------|-----------|

| QUIESCENT CUR              | RRENTS                                                                                         |                                                                       |            |       |       |           |

| 1                          | Quiescent battery current with                                                                 | V <sub>BAT</sub> = 28V, VAC = 0V, ADC_EN = 0, T <sub>J</sub> < 105 °C |            | 17    |       | μA        |

| I <sub>Q_BAT</sub>         | BATFET on (I <sub>SRN</sub> + I <sub>SRP</sub> )                                               | V <sub>BAT</sub> = 28V, VAC = 0V, ADC_EN = 1, T <sub>J</sub> < 105 °C |            | 500   | 700   | μA        |

| I <sub>Q_VAC</sub>         | Quiescent input current (I <sub>VAC</sub> )                                                    | Not switching                                                         |            | 0.75  | 1     | mA        |

| I <sub>Q_REV</sub>         | Quiescent battery current in Reverse mode (I <sub>SRN</sub> + I <sub>SRP</sub> )               | Not switching                                                         |            | 0.75  | 1     | mA        |

| VAC / BAT POWE             | R UP                                                                                           |                                                                       |            |       |       |           |

| V <sub>VAC_OP</sub>        | VAC operating range                                                                            |                                                                       | 4.2        |       | 70    | V         |

| V <sub>VAC_OK</sub>        | VAC converter enable threshold                                                                 | VAC rising, no battery                                                | 4.2        |       |       | V         |

| V <sub>VAC_OKZ</sub>       | VAC converter disable threshold                                                                | VAC falling, no battery                                               |            |       | 3.5   | V         |

| V <sub>REF_ACUV</sub>      | ACUV comparator threshold to enter VAC_UVP                                                     | V <sub>ACUV</sub> falling                                             | 1.095      | 1.1   | 1.106 | ٧         |

| V <sub>REF_ACUV_HYS</sub>  | ACUV comparator threshold hysteresis                                                           | V <sub>ACUV</sub> rising                                              |            | 50    |       | mV        |

| V <sub>VAC_INT_OV</sub>    | VAC internal threshold to enter VAC_OVP                                                        | IN rising                                                             | 72         | 74    | 76    | V         |

| V <sub>VAC_INT_OVZ</sub>   | VAC internal thresholds to exit VAC_OVP                                                        | IN falling                                                            | 69         | 71    | 73    | V         |

| V <sub>REF_ACOV</sub>      | ACOV comparator threshold to enter VAC_OVP                                                     | V <sub>ACOV</sub> rising                                              | 1.184      | 1.2   | 1.206 | V         |

| V <sub>REF_ACOV_HYS</sub>  | ACOV comparator threshold hysteresis                                                           | V <sub>ACOV</sub> falling                                             |            | 50    |       | mV        |

| CHARGE VOLTA               | GE REGULATION                                                                                  |                                                                       |            |       |       |           |

| V <sub>VFB_RANGE</sub>     | Feedback voltage range                                                                         |                                                                       | 1.504      |       | 1.566 | V         |

| $V_{VFB\_NOM}$             | Nominal feedback voltage                                                                       | VFB_REG = 0x10                                                        |            | 1.536 |       | V         |

| V <sub>VFB_ACC</sub>       | Feedback voltage regulation accuracy                                                           | $T_J = 0$ °C to 85°C                                                  | -0.5       |       | 0.5   | %         |

| VFB_ACC                    | 1 coasaok voltage regulation accuracy                                                          | $T_J = -40$ °C to 125°C                                               | -0.7       |       | 0.7   | %         |

| $R_{FBG}$                  | FBG resistance to PGND                                                                         | I <sub>FBG</sub> = 1mA                                                |            | 33    | 55    | Ω         |

| FAST CHARGEC               | URRENT REGULATION                                                                              | -                                                                     |            |       |       |           |

| I <sub>CHG_REG_RANGE</sub> | Charge current regulation range                                                                |                                                                       | 0.4        |       | 20    | Α         |

|                            |                                                                                                | $R_{BAT\_SNS} = 5m\Omega$ , VBAT = 12V, 36V, 55V.                     |            | 15    |       | Α         |

|                            |                                                                                                | ICHG_REG = 0x012C                                                     | -3         |       | 3     | %         |

| I                          | I <sup>2</sup> C setting charge current regulation                                             | $R_{BAT SNS} = 5m\Omega$ , VBAT = 12V, 36V, 55V.                      |            | 5     |       | Α         |

| CHG_REG_ACC                | accuracy                                                                                       | ICHG_REG = 0x0064                                                     | -3         |       | 3     | %         |

|                            |                                                                                                | $R_{BAT SNS} = 5m\Omega$ , VBAT = 12V, 36V, 55V.                      |            | 2     |       | Α         |

|                            |                                                                                                | ICHG_REG = 0x0028                                                     | <b>–</b> 5 |       | 5     | %         |

| K <sub>ICHG</sub>          | Hardware charge current limit set factor (Amperes of charge current per $k\Omega$ on ICHG pin) | $R_{BAT\_SNS}$ = 5mΩ, $R_{ICHG}$ = 10kΩ, 5kΩ, and 3.33kΩ              | 48         | 50    | 52    | A x<br>kΩ |

| V <sub>REF_ICHG</sub>      | ICHG pin voltage when ICHG pin is in regulation                                                |                                                                       |            | 2.0   |       | ٧         |

| PRE-CHARGE CU              | URRENT REGULATION                                                                              |                                                                       |            |       |       |           |

| I <sub>PRECHG</sub> RANGE  | Precharge current regulation range                                                             | V <sub>FB</sub> < V <sub>BAT_LOWV</sub> * V <sub>VFB_REG</sub>        | 0.25       |       | 10    | Α         |

VAC = ACP = ACN = SYS = SRP = SRN = 28V,  $T_J$  = -40°C to +125°C, and  $T_J$  = 25°C for typical values (unless otherwise noted)

| noted)                    | PARAMETER                                                                                        | TEST CONDITIONS                                                                      | MIN  | TYP   | MAX  | UNIT      |

|---------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------|-------|------|-----------|

|                           |                                                                                                  | $R_{BAT~SNS} = 5m\Omega$ , $V_{FB} < V_{BAT~LOWV}$ *                                 |      | 3.0   |      | Α         |

|                           | I <sup>2</sup> C setting precharge current                                                       | V <sub>VFB_REG</sub> . IPRECHG = 0x003C                                              | -4   |       | 4    | %         |

| I <sub>PRECHG_ACC</sub>   |                                                                                                  | $R_{BAT~SNS} = 5m\Omega, V_{FB} < V_{BAT~LOWV}$ *                                    |      | 1.0   |      | Α         |

|                           | accuracy                                                                                         | $V_{VFB\_REG}$ . IPRECHG[1:0] = $0\bar{x}$ 0014                                      | -10  |       | 10   | %         |

|                           |                                                                                                  | $R_{BAT\_SNS} = 5m\Omega, V_{FB} < V_{BAT\_LOWV} *$                                  |      | 0.50  |      | Α         |

|                           |                                                                                                  | $V_{VFB\_REG}$ . IPRECHG[1:0] = 0x000A                                               | -30  |       | 30   | %         |

| CHARGE TERMI              | NATION                                                                                           |                                                                                      |      |       |      |           |

| I <sub>TERM_RANGE</sub>   | Termination current range                                                                        | $V_{FB} = V_{VFB\_REG}$                                                              | 0.25 |       | 10   | Α         |

|                           |                                                                                                  | $R_{BAT\_SNS} = 5m\Omega$ , VBAT = 12V, 36V,                                         |      | 1.5   |      | Α         |

|                           |                                                                                                  | 55V_ITERM = 0x001E                                                                   | -7   |       | 7    | %         |

| I <sub>TERM ACC</sub>     | Termination current accuracy                                                                     | $R_{BAT\_SNS} = 5m\Omega$ , VBAT = 12V, 36V, 55V.                                    |      | 0.50  |      | Α         |

| 1214M_7100                |                                                                                                  | ITERM = 0x000A                                                                       | -20  |       | 20   | %         |

|                           |                                                                                                  | $R_{BAT\_SNS} = 5m\Omega$ , VBAT = 12V, 36V, 55V.                                    |      | 0.250 | _    | Α         |

|                           |                                                                                                  | ITERM = 0x0005                                                                       | -50  |       | 50   | %         |

| BATTERY VOLTA             | AGE COMPARATORS                                                                                  | lv                                                                                   | 0.0  |       | 0.0  |           |

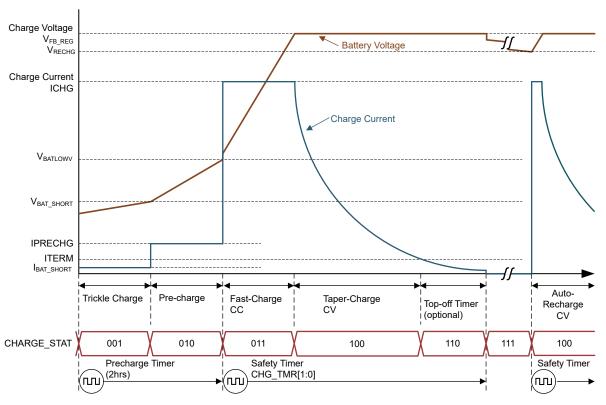

| V <sub>BAT_SHORT</sub>    | Trickle charge to pre-charge transition                                                          | V <sub>SRN</sub> rising                                                              | 2.8  | 3     | 3.2  | V         |

|                           | Pre-charge to trickle charge transition                                                          | V <sub>SRN</sub> falling                                                             | 2.2  | 2.4   | 2.6  | V         |

| $V_{BAT\_LOWV}$           | Pre-charge to fast-charge transition                                                             | V <sub>FB</sub> rising, as percentage of V <sub>FB_REG</sub> ,<br>VBAT_LOWV[2:0] = 3 | 69.0 | 71.7  | 73.8 | %         |

|                           |                                                                                                  | $V_{FB}$ rising, as percentage of $V_{FB\_REG}$ , VBAT_LOWV[2:0] = 2                 | 64.3 | 66.7  | 69.0 | %         |

|                           |                                                                                                  | $V_{FB}$ rising, as percentage of $V_{FB\_REG}$ , VBAT_LOWV[2:0] = 1                 | 52   | 55    | 58   | %         |

|                           |                                                                                                  | V <sub>FB</sub> rising, as percentage of V <sub>FB_REG</sub> ,<br>VBAT_LOWV[2:0] = 0 | 27   | 30    | 33   | %         |

| V <sub>BAT_LOWV_HYS</sub> | BAT_LOWV hysteresis                                                                              |                                                                                      |      | 5     |      | %         |

|                           |                                                                                                  | V <sub>FB</sub> falling, as percentage of V <sub>FB_REG</sub> ,<br>VRECHG[1:0] = 3   |      | 97.6  |      | %         |

|                           | Battery recharge threshold for Li-lon and LiFePO <sub>4</sub>                                    | V <sub>FB</sub> falling, as percentage of V <sub>FB_REG</sub> ,<br>VRECHG[1:0] = 2   |      | 95.2  |      | %         |

| V <sub>RECHG</sub>        |                                                                                                  | V <sub>FB</sub> falling, as percentage of V <sub>FB_REG</sub> , VRECHG[1:0] = 1      |      | 94.3  |      | %         |

|                           |                                                                                                  | V <sub>FB</sub> falling, as percentage of V <sub>FB_REG</sub> , VRECHG[1:0] = 0      |      | 93.0  |      | %         |

| INPUT CURRENT             | REGULATION                                                                                       |                                                                                      |      |       |      |           |

|                           |                                                                                                  | P 2mO IAC DDM - 0v00AC                                                               |      | 20    |      | Α         |

| I <sub>IREG_DPM_ACC</sub> |                                                                                                  | $R_{AC\_SNS} = 2m\Omega$ , IAC_DPM = 0x00A0                                          | -3   |       | 3    | %         |

|                           | I <sup>2</sup> C setting input current regulation                                                | $R_{AC~SNS} = 2m\Omega$ , IAC_DPM = 0x0050                                           |      | 10    |      | Α         |

|                           | accuracy in forward mode                                                                         | TVAC_SNS = 21112, 1740_D1 101 = 0x0000                                               | -4   |       | 4    | %         |

|                           |                                                                                                  | $R_{AC~SNS} = 2m\Omega$ , IAC_DPM = 0x0028                                           |      | 5.0   |      | Α         |

|                           |                                                                                                  | TAC_SNS - ZIIIIZ, IAC_DPINI = UXUUZ8                                                 | -7   |       | 7    | %         |

| K <sub>ILIM</sub>         | Hardware input current limit set factor (Amperes of input current per $k\Omega$ on ILIM_HIZ pin) | $R_{AC\_SNS}$ = 2mΩ, $R_{ILIM}$ = 5kΩ, 2.5kΩ, and 1.67kΩ                             | 48   | 50    | 52   | A x<br>kΩ |

| V <sub>REF_ILIM_HIZ</sub> | ILIM_HIZ pin voltage when ILIM_HIZ pin is in regulation                                          |                                                                                      |      | 2.0   |      | V         |

English Data Sheet: SLUSEN5

VAC = ACP = ACN = SYS = SRP = SRN = 28V,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , and  $T_J = 25^{\circ}C$  for typical values (unless otherwise noted)

|                             | PARAMETER                                                                                               | TEST CONDITIONS                            | MIN    | TYP    | MAX    | UNIT |

|-----------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------|--------|--------|--------|------|

| V <sub>IH_ILIM_HIZ</sub>    | ILIM_HIZ input high threshold to enter HIZ mode                                                         | V <sub>ILIM_HIZ</sub> rising               | 3.7    |        |        | V    |

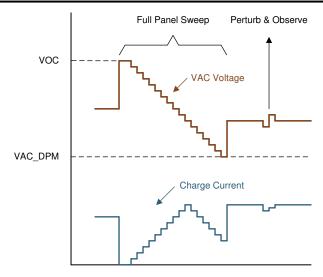

| INPUT VOLTAGE               | REGULATION                                                                                              |                                            |        |        |        |      |

| V <sub>VREG_DPM_RANGE</sub> | Input voltage DPM regulation range                                                                      |                                            | 4.2    |        | 65     | V    |

|                             | I <sup>2</sup> C setting input voltage regulation                                                       |                                            |        | 38     |        | V    |

| V <sub>VREG_DPM_ACC</sub>   | accuracy                                                                                                | VAC_DPM = 0x076C                           | -2     |        | 2      | %    |

|                             |                                                                                                         | VAC DPM = 0x04E2                           |        | 25     |        | V    |

| V                           | I <sup>2</sup> C setting input voltage regulation                                                       | VAC_DPIN = 0x04E2                          | -2     |        | 2      | %    |

| V <sub>VREG_DPM_ACC</sub>   | accuracy in forward mode                                                                                | VAC DPM = 0x03B6                           |        | 19     |        | V    |

|                             |                                                                                                         | VAC_BI IVI = 0X00B0                        | -2     |        | 2      | %    |

| V <sub>ACUV_DPM</sub>       | ACUV pin voltage when in VDPM regulation                                                                |                                            | 1.198  | 1.210  | 1.222  | V    |

| REVERSE MODE                | VOLTAGE REGULATION                                                                                      |                                            |        |        |        |      |

| V <sub>REV_RANGE</sub>      | VAC Voltage regulation range in Reverse mode                                                            |                                            | 3.3    |        | 65     | V    |

| V                           | Voltage regulation accuracy in                                                                          | VAC BEV - 0×0000                           |        | 48     |        | V    |

| V <sub>REV_ACC</sub>        | Reverse mode                                                                                            | VAC_REV = 0x0960                           | -2     |        | 2      | %    |

|                             |                                                                                                         | VAC REV = 0x0578                           |        | 28     |        | V    |

|                             |                                                                                                         | VAC_NEV = 0x0370                           | -2     |        | 2      | %    |

| V <sub>REV_ACC</sub>        | VAC Voltage regulation accuracy in                                                                      | VAC REV = 0x02EE                           |        | 15     |        | V    |

| *REV_ACC                    | Reverse mode                                                                                            | W.O (E.V. OXOZZZ                           | -2     |        | 2      | %    |

|                             |                                                                                                         | VAC_REV = 0x00FA                           |        | 5      |        | V    |

|                             |                                                                                                         |                                            | -2     |        | 2      | %    |

| REVERSE MODE                | CURRENT REGULATION                                                                                      |                                            |        |        |        |      |

|                             |                                                                                                         | $R_{AC SNS} = 2m\Omega$ , IAC_REV = 0x00A0 |        | 20     |        | Α    |

| I <sub>IREV ACC</sub>       | Input current regulation accuracy in                                                                    |                                            | -3.5   |        | 3.5    | %    |

| -INEV_ACC                   | Reverse mode                                                                                            | $R_{AC SNS} = 2m\Omega$ , IAC_REV = 0x0028 |        | 5.0    |        | Α    |

|                             |                                                                                                         | Ac_one ,                                   | -5.5   |        | 5.5    | %    |

| CHARGE MODE                 | BATTERY-PACK NTC MONITOR                                                                                |                                            |        |        |        |      |

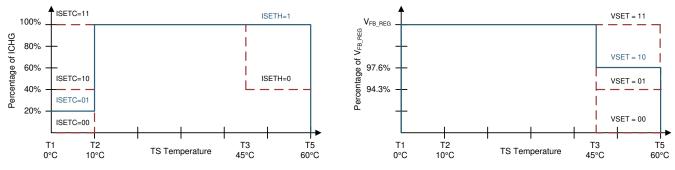

| V <sub>T1_RISE</sub>        | TS pin voltage rising T1 threshold, charge suspended above this voltage.                                | As Percentage to REGN, TS_T1=0°C w/ 103AT  | 72.75  | 73.25  | 73.85  | %    |

| V <sub>T1_FALL</sub>        | TS pin voltage falling T1 threshold, charge re-enabled below this voltage.                              | As Percentage to REGN, TS_T1=0°C w/ 103AT  | 71.5   | 72     | 72.5   | %    |

| V <sub>T2_RISE</sub>        | TS pin voltage rising T2 threshold, charge back to reduced ICHG above this voltage                      | As Percentage to REGN, TS_T2=10°C w/ 103AT | 67.75  | 68.25  | 68.75  | %    |

| V <sub>T2_FALL</sub>        | TS pin voltage falling T2 threshold.<br>Charge back to normal below this<br>voltage                     | As Percentage to REGN, TS_T2=10°C w/ 103AT | 66.45  | 66.95  | 67.45  | %    |

| V <sub>T3_FALL</sub>        | TS pin voltage falling T3 threshold, charge to ICHG and reduced V <sub>FB_REG</sub> below this voltage. | As Percentage to REGN, TS_T3=45°C w/ 103AT | 44.25  | 44.75  | 45.25  | %    |

| V <sub>T3_RISE</sub>        | TS pin voltage rising T3 threshold. Charge back to normal above this voltage.                           | As Percentage to REGN, TS_T3=45°C w/ 103AT | 45.55  | 46.05  | 46.55  | %    |

| V <sub>T5_FALL</sub>        | TS pin voltage falling T5 threshold, charge suspended below this voltage                                | As Percentage to REGN, TS_T5=60°C w/ 103AT | 33.875 | 34.375 | 34.875 | %    |

|                             |                                                                                                         |                                            |        |        |        |      |

VAC = ACP = ACN = SYS = SRP = SRN = 28V,  $T_J$  = -40°C to +125°C, and  $T_J$  = 25°C for typical values (unless otherwise noted)

|                         | PARAMETER                                                                                                   | TEST CONDITIONS                                               | MIN    | TYP    | MAX    | UNIT |

|-------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------|--------|--------|------|

| V <sub>T5_RISE</sub>    | TS pin voltage rising T5 threshold. Charge back to ICHG and reduced V <sub>FB_REG</sub> above this voltage. | As Percentage to REGN, TS_T5=60°C w/ 103AT                    | 35     | 35.5   | 36     | %    |

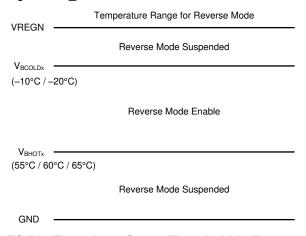

| REVERSE MOD             | E BATTERY-PACK NTC MONITOR                                                                                  |                                                               |        |        |        |      |

| V <sub>BCOLD_RISE</sub> | TS pin voltage rising TCOLD threshold. Reverse mode suspended above this voltage                            | As Percentage to REGN (BCOLD = -20°C w/ 103AT)                | 79.45  | 80.0   | 80.55  | %    |

| V <sub>BCOLD_RISE</sub> | TS pin voltage rising TCOLD threshold. Reverse mode suspended above this voltage                            | As Percentage to REGN (BCOLD = -10°C w/ 103AT)                | 76.65  | 77.15  | 77.65  | %    |

| V <sub>BCOLD_FALL</sub> | TCOLD comparator falling threshold.                                                                         | As Percentage to REGN (–20°C w/ 103AT)                        | 78.2   | 78.7   | 79.2   | %    |

| V <sub>BCOLD_FALL</sub> | TCOLD comparator falling threshold.                                                                         | As Percentage to REGN (-10°C w/ 103AT)                        | 75.5   | 75.6   | 76.5   | %    |

| V <sub>BHOT_FALL</sub>  | TS pin voltage falling THOT threshold. Reverse mode suspends below this voltage                             | As Percentage to REGN, (BHOT = 55°C w/ 103AT)                 | 37.2   | 37.7   | 38.2   | %    |

| V <sub>BHOT_FALL</sub>  | TS pin voltage falling THOT threshold. Reverse mode suspends below this voltage                             | As Percentage to REGN, (BHOT = 60°C w/ 103AT)                 | 33.875 | 34.375 | 34.875 | %    |

| V <sub>BHOT_FALL</sub>  | TS pin voltage falling THOT threshold. Reverse mode suspends below this voltage                             | As Percentage to REGN, (BHOT 65°C w/ 103AT)                   | 30.75  | 31.25  | 31.75  | %    |

| V <sub>BHOT_RISE</sub>  | TS pin voltage rising THOT threshold.<br>Reverse mode allowed above this<br>voltage                         | As Percentage to REGN, (BHOT = 55°C w/ 103AT)                 | 38.5   | 39.0   | 39.95  | %    |

| V <sub>BHOT_RISE</sub>  | TS pin voltage rising THOT threshold.<br>Reverse mode allowed above this<br>voltage                         | As Percentage to REGN, (BHOT = 60°C w/ 103AT)                 | 35     | 35.5   | 36     | %    |

| V <sub>BHOT_RISE</sub>  | TS pin voltage rising THOT threshold.<br>Reverse mode allowed above this<br>voltage                         | As Percentage to REGN, (BHOT 65°C w/ 103AT)                   | 32.0   | 32.5   | 33.0   | %    |

| BATTERY CHAI            | RGER PROTECTION                                                                                             |                                                               |        |        |        |      |

| V <sub>BAT_OV</sub>     | Battery overvoltage threshold                                                                               | V <sub>FB</sub> rising, as percentage of V <sub>FB_REG</sub>  | 102.5  | 104    | 105.5  | %    |

| V <sub>BAT_OVZ</sub>    | Battery overvoltage falling threshold                                                                       | V <sub>FB</sub> falling, as percentage of V <sub>FB_REG</sub> | 100.5  | 102    | 103.5  | %    |

| V <sub>ICHG_OC</sub>    | Battery charge over-current threshold                                                                       | V <sub>SRP</sub> - V <sub>SRN</sub> rising                    | 120    |        | 170    | mV   |

| THERMAL SHU             | TDOWN                                                                                                       |                                                               |        |        |        |      |

| т                       | Thermal shutdown rising threshold                                                                           | Temperature increasing                                        |        | 150    |        | °C   |

| T <sub>SHUT</sub>       | Thermal shutdown falling threshold                                                                          | Temperature decreasing                                        |        | 135    |        | °C   |

| REGN REGULA             | TOR AND GATE DRIVE SUPPLY (DRV_S                                                                            | SUP)                                                          |        |        |        |      |

| \/                      | REGN LDO output voltage                                                                                     | IREGN = 20mA                                                  | 4.8    | 5      | 5.2    | V    |

| $V_{REGN}$              | REGIN EDO output voltage                                                                                    | VAC = 5V, IREGN = 20mA                                        | 4.35   | 4.6    |        | V    |

| I <sub>REGN</sub>       | REGN LDO current limit                                                                                      | VREGN = 4.5V                                                  | 70     |        |        | mA   |

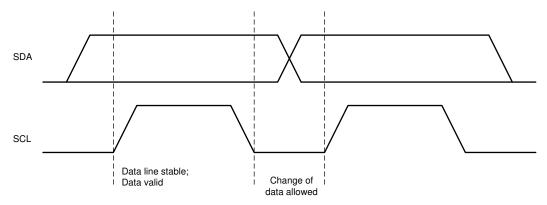

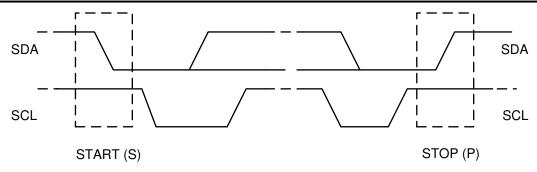

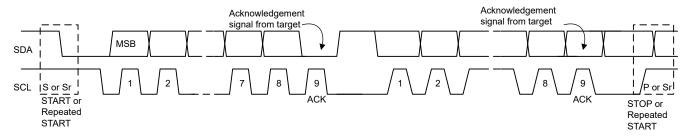

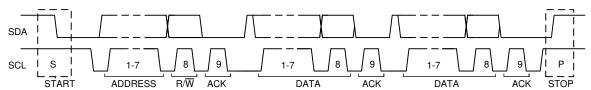

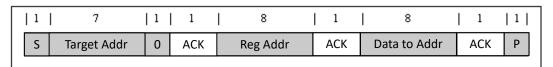

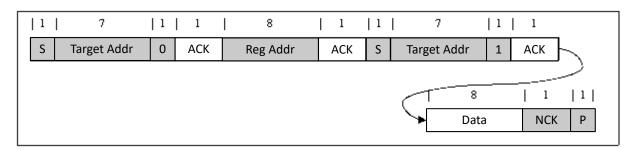

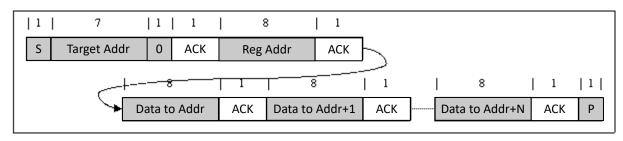

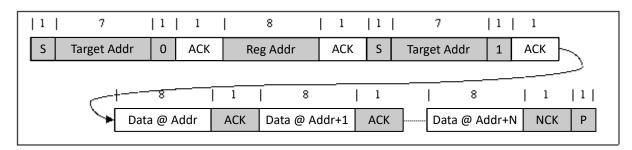

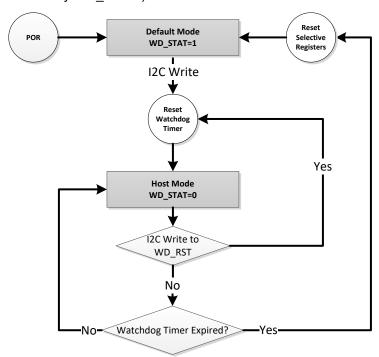

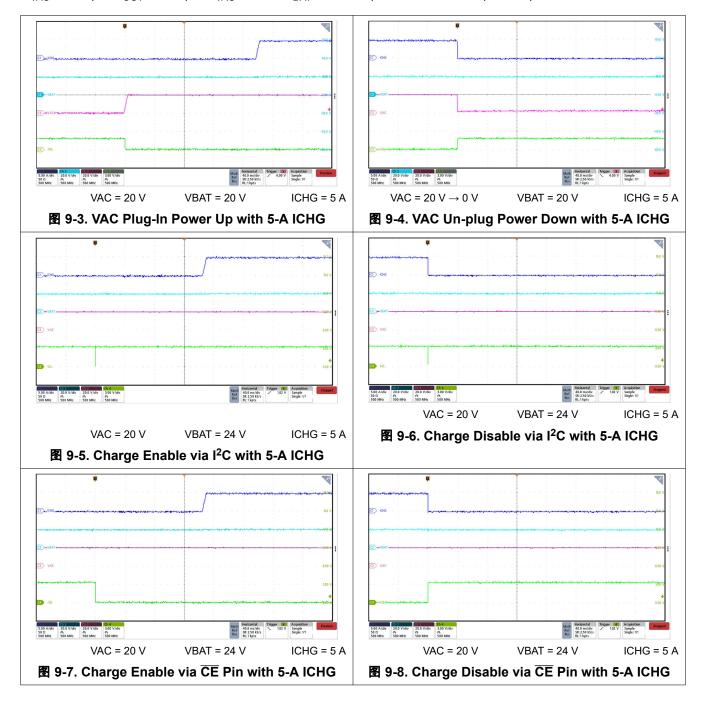

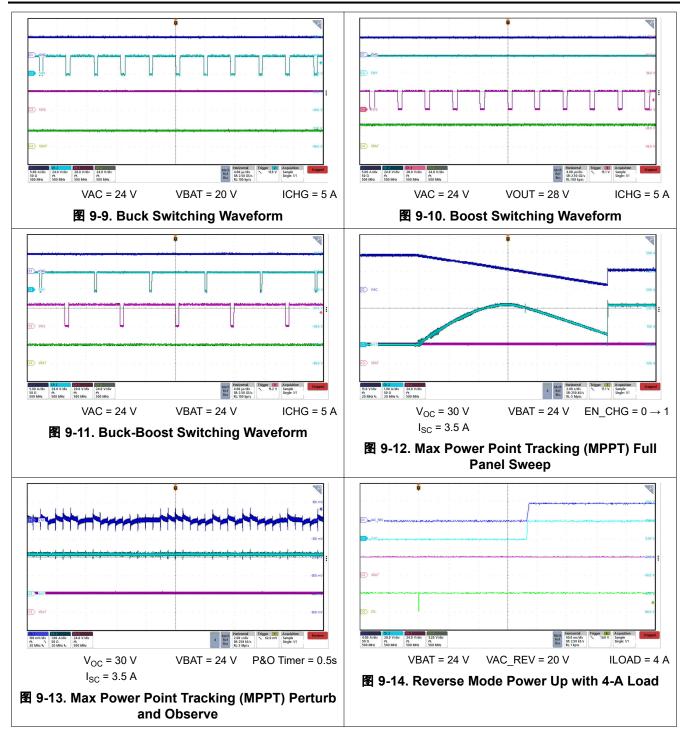

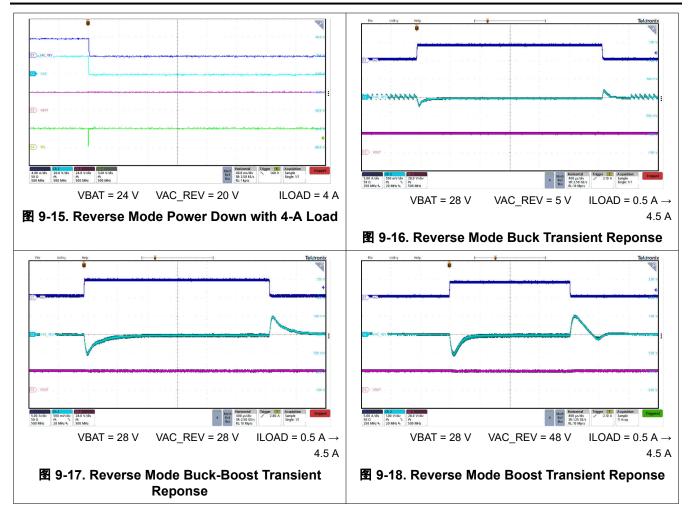

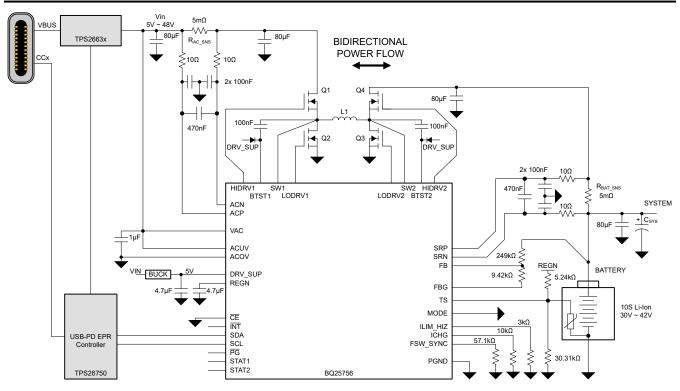

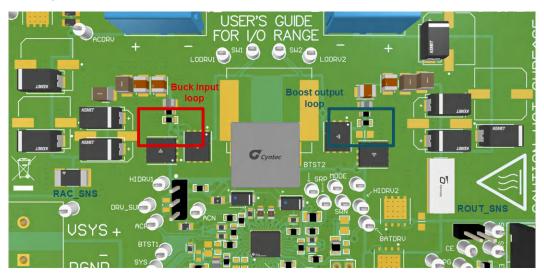

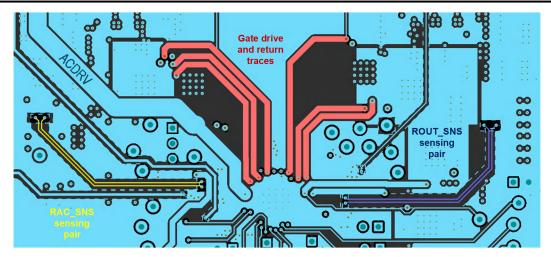

| V <sub>REGN_OK</sub>    | REGN OK threshold to allow switching                                                                        | REGN rising                                                   |        | 3.55   |        | V    |