bq2026 ZHCS608A - DECEMBER 2011 - REVISED OCTOBER 2014

# 具有 SDQ 接口的 1.5K 位串行 EPROM

# 特性

- 1536 位的一次性可编程 (OTP) EPROM, 用于存 储用户可编程的配置数据

- 厂家设定的唯一64位识别号

- 单线制接口以减少电路板布线

- 同步通信减少主机中断开销

- 在数据引脚上的 6KV IEC 61000-4-2 静电放电 (ESD)兼容性

- 无需待机电源

- 采用 3 引脚 SOT-23 和 TO-92 封装

# 2 应用

- 安全编码

- 库存跟踪

- 产品修正维护

- 电池组识别

# 3 说明

bg2026 是一款 1.5K 位串行 EPROM, 此器件包含一 个厂家设定, 唯一 48 位识别号, 8 位产品编码, 和一 个 64 位状态寄存器。

bq2026 SDQ™ 接口只要求一个单一连接和一个接地 返回。 SDQ 引脚也是 bq2026 的唯一电源。

该器件提供小型表面贴装选项, 可节省在印刷电路板上 的占用空间,同时拥有低成本优势,非常适合电池组配 置参数、记录保存、资产跟踪、产品版本状态以及代码 访问安全性等应用。

### 器件信息(1)

| 器件型号   | 封装         | 封装尺寸(标称值)       |

|--------|------------|-----------------|

| h~2026 | SOT-23 (3) | 4.30mm × 4.30mm |

| bq2026 | TO-92 (3)  | 2.92mm × 1.30mm |

(1) 要了解所有可用封装,请见数据表末尾的封装选项附录。

注: 可将 LP 封装的引脚 3 接地或保持悬空。

# 目录

| 1 | 特性                                 | 7 | Detailed Description                   | 5 |

|---|------------------------------------|---|----------------------------------------|---|

| 2 | 应用1                                |   | 7.1 Overview                           | 5 |

|   | 说明                                 |   | 7.2 Functional Block Diagram           | 5 |

|   | Pin Configuration and Functions    | 8 | 7.4 Device Functional Modes<br>器件和文档支持 |   |

| • | 6.1 Absolute Maximum Ratings       |   | 8.1 商标<br>8.2 静电放电警告                   |   |

|   | 6.3 Electrical Characteristics: DC | 9 | 8.3 术语表                                |   |

# 4 修订历史记录

| C | hanges from Original (April 2013) to Revision A | Page |

|---|-------------------------------------------------|------|

| • | 己更改文档格式以符合最新数据表标准                               | 1    |

| • | 已添加处理额定值表,特性描述,器件功能模式,器件和文档支持以及机械、封装和可订购信息部分    | 1    |

| • | 已添加注释至首页图                                       | 1    |

| • | Changed pin 3 (VSS) description for LP package  | 3    |

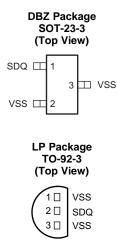

# 5 Pin Configuration and Functions

### **Pin Functions**

|      | PIN  |    | 1/0 | DESCRIPTION                       |  |  |

|------|------|----|-----|-----------------------------------|--|--|

| NAME | DBZ  | LP | I/O | DESCRIPTION                       |  |  |

| SDQ  | 1    | 2  | I/O | Data                              |  |  |

| VSS  | 2, 3 | 1  | _   | Ground                            |  |  |

| VSS  | _    | 3  | _   | Can be ground or left unconnected |  |  |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                                      |                                                 | MIN  | MAX | UNIT |

|------------------------------------------------------|-------------------------------------------------|------|-----|------|

| DC voltage applied to V <sub>PU</sub> See Figure 1   | -0.3                                            | 12.5 | V   |      |

| Low-level output current, I <sub>OL</sub>            |                                                 | 5    | mA  |      |

| ESD IEC 61000-4-2 Air discharge                      | SDQ to V <sub>SS</sub> , V <sub>SS</sub> to SDQ |      | 6   | kV   |

| Operating free-air temperature range, T <sub>A</sub> |                                                 | -20  | 70  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 Handling Ratings

|                  |                           | MIN | MAX | UNIT |

|------------------|---------------------------|-----|-----|------|

| T <sub>stg</sub> | Storage temperature range | -55 | 125 | °C   |

# 6.3 Electrical Characteristics: DC

At  $T_A = -20$ °C to 70°C;  $V_{PU(min)} = 2.65 \ V_{DC}$  to 5.5  $V_{DC}$ , all voltages relative to VSS.

|                  | PARAMETER                       | TEST CONDITION                                            | MIN  | TYP             | MAX | UNIT |

|------------------|---------------------------------|-----------------------------------------------------------|------|-----------------|-----|------|

| I <sub>SDQ</sub> | Supply current                  | V <sub>PU</sub> = 5.5 V                                   |      |                 | 20  | μΑ   |

| Loc              |                                 | Logic 0, $V_{PU}$ = 5.5 V, $I_{OL}$ = 4 mA, SDQ pin       |      |                 | 0.4 | V    |

| V <sub>OL</sub>  | Low-level output voltage        | Logic 0, V <sub>PU</sub> = 2.65 V, I <sub>OL</sub> = 2 mA |      |                 | 0.4 | V    |

| V <sub>OH</sub>  | High-level output voltage       | Logic 1                                                   |      | V <sub>PU</sub> | 5.5 | V    |

| I <sub>OL</sub>  | Low-level output current (sink) | V <sub>OL</sub> = 0.4 V, SDQ pin                          |      |                 | 4   | mA   |

| $V_{IL}$         | Low-level input voltage         | Logic 0                                                   |      |                 | 8.0 | V    |

| V <sub>IH</sub>  | High-level input voltage        | Logic 1                                                   | 2.2  |                 |     | V    |

| $V_{PP}$         | Programming voltage             |                                                           | 11.5 |                 | 12  | V    |

| I <sub>lkg</sub> | Input leakage                   |                                                           |      | 1.4             |     | μA   |

| C <sub>I</sub>   | Input capacitance               |                                                           |      | 1.2             |     | nF   |

# 6.4 Switching Characteristcs: AC

$T_A = -20$ °C to 70°C;  $V_{PU(min)} = 2.65 V_{DC}$  to 5.5  $V_{DC}$ , all voltages relative to VSS

|                     | PARAMETER                 | TEST CONDITION | MIN                | TYP | MAX            | UNIT |

|---------------------|---------------------------|----------------|--------------------|-----|----------------|------|

| t <sub>c</sub>      | Bit cycle time (1)        |                | 60                 |     | 120            | μs   |

| t <sub>WSTRB</sub>  | Write start cycle (1)     |                | 1                  |     | 15             | μs   |

| t <sub>WDSU</sub>   | Write data setup (1)      |                | t <sub>WSTRB</sub> |     | 15             | μs   |

| t <sub>WDH</sub>    | Write data hold (1) (2)   |                | 60                 |     | t <sub>c</sub> | μs   |

| t <sub>rec</sub>    | Recovery time (1)         |                | 1                  |     |                | μs   |

| t <sub>RSTRB</sub>  | Read start cycle (1)      |                | 1                  |     | 13             | μs   |

| t <sub>ODD</sub>    | Output data delay (1)     |                | t <sub>RSTRB</sub> |     | 13             | μs   |

| t <sub>ODHO</sub>   | Output data hold (1)      |                | 17                 |     | 60             | μs   |

| t <sub>RST</sub>    | Reset time (1)            |                | 480                |     |                | μs   |

| t <sub>PPD</sub>    | Presence pulse delay (1)  |                | 15                 |     | 64             | μs   |

| t <sub>PP</sub>     | Presence pulse (1)        |                | 60                 |     | 240            | μs   |

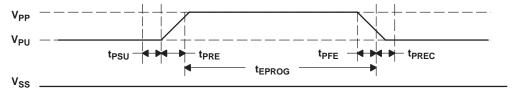

| t <sub>EPROG</sub>  | EPROM programming time    |                | 480                |     |                | μs   |

| t <sub>PSU</sub>    | Program setup time        |                | 5                  |     |                | μs   |

| t <sub>PREC</sub>   | Program recovery time     |                | 5                  |     |                | μs   |

| t <sub>PRE</sub>    | Program rising-edge time  |                |                    |     | 5              | μs   |

| t <sub>PFE</sub>    | Program falling-edge time |                |                    |     | 5              | μs   |

| t <sub>RSTREC</sub> |                           |                | 480                |     |                | μs   |

$<sup>\</sup>begin{array}{ll} \mbox{(1)} & \mbox{5-k}\Omega \mbox{ series resistor between SDQ pin and $V_{PU}$. (See Figure 1)} \\ \mbox{(2)} & \mbox{$t_{WDH}$ must be less than $t_{c}$ to account for recovery.} \end{array}$

## 7 Detailed Description

#### 7.1 Overview

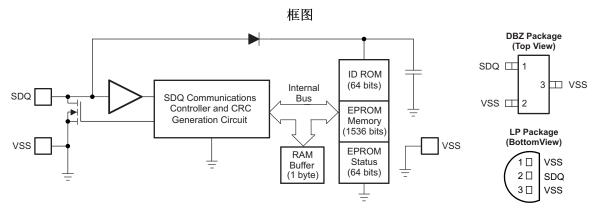

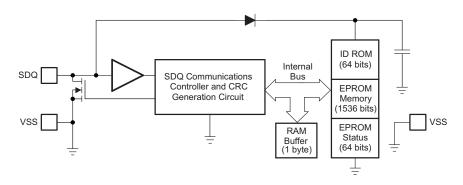

The block diagram shows the relationships among the major control and memory sections of the bq2026. The bq2026 has three main data components: a 64-bit factory-programmed ROM, including 8-bit family code, 48-bit identification number and 8-bit CRC value, 1536-bit EPROM, and EPROM Status bytes. Power for read and write operations is derived from the SDQ pin. An internal capacitor stores energy while the signal line is high, and releases energy during the low times of the SDQ pin until the pin returns high to replenish the charge on the capacitor.

# 7.2 Functional Block Diagram

## 7.3 Feature Description

#### 7.3.1 EPROM

Table 1 is a memory map of the 1536-bit EPROM section of the bq2026, configured as six pages of 32 bytes each. The 1-byte RAM buffer is an additional register used when programming the memory. Data are first written to the RAM buffer and then verified by reading a 16-bit CRC from the bq2026 that confirms proper receipt of the data. If the buffer contents are correct, a programming pulse is issued and a 1-byte segment of data is written into the selected address in memory. This process ensures data integrity when programming the memory. The details for reading and programming the 1536-bit EPROM portion of the bq2026 are in the *Memory and Status Function Commands* section of this data sheet.

ADDRESS (HEX)

00A0-00BF

0080-009F

0060-007F

Page 3

0040-005F

Page 2

0020-003F

Page 1

0000-001F

Page 0

Table 1. 1536-Bit EPROM Data Memory Map

# 7.3.2 EPROM Status Memory

In addition to the programmable 1536-bits of memory are eight bytes of status information, the first seven bytes are available to the user, contained in the EPROM status memory. The status memory is accessible with separate commands. The status bytes are EPROM and are read or programmed to indicate various conditions to the software interrogating the bq2026. These general-purpose bytes can be used by the customer to store various information.

**Table 2. EPROM Status Bytes**

| ADDRESS (HEX) | PAGE                              |  |

|---------------|-----------------------------------|--|

| 100h-107h     | General-purpose OTP status memory |  |

### 7.3.3 Error Checking

Implement error checking by comparing the 16-bit CRC values transmitted by the bq2026. If the two CRC values match, the transmission is error-free. Details are found in the CRC Generation section.

### 7.4 Device Functional Modes

### 7.4.1 Customizing the bq2026

The 64-bit ID identifies each bq2026 device. The 48-bit serial number is unique and programmed by Texas Instruments. The default 8-bit family code is 09h; however, a different value can be reserved on an individual customer basis. Contact your Texas Instruments sales representative for more information.

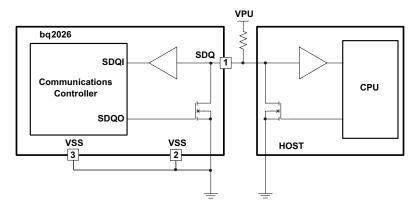

#### 7.4.2 Bus Termination

Because the drive output of the bq2026 is an open-drain, N-channel MOSFET, the host must provide a source current or a  $5-k\Omega$  external pullup, as shown in the typical application circuit in Figure 1.

Figure 1. Bus Termination Example for SOT-23 Package

### 7.4.3 Serial Communication

A host reads, programs, or checks the status of the bq2026 through the hierarchical command structure of the SDQ interface. Figure 2 shows that the host must first issue a ROM command before the EPROM memory or status can be read or modified.

Figure 2. General Command Sequence

#### 7.4.4 Initialization

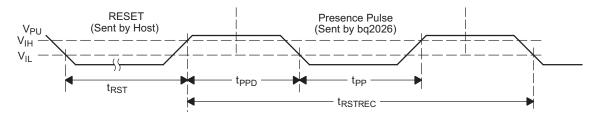

Initialization consists of two pulses, the reset and the presence pulses. The host generates the reset pulse, while the bq2026 responds with the presence pulse. The host resets the bq2026 by driving the DATA bus low for at least 480 µs. For more details, see the *Reset and Presence Pulse* section.

#### 7.4.5 ROM Commands

#### 7.4.5.1 Read ROM

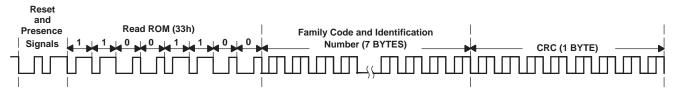

The Read ROM command sequence is the fastest sequence that allows the host to read the 8-bit family code and 48-bit identification number. The Read ROM sequence starts with the host generating the reset pulse of at least 480 µs. The bq2026 responds with a presence pulse. Next, the host continues by issuing the Read ROM command, 33h, and then reads the ROM and CRC byte using the read signaling (see the *Write* and *Read* sections) during the data frame.

Figure 3. Read ROM Sequence

#### 7.4.5.2 Match ROM

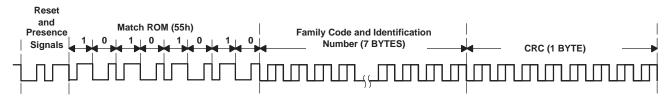

The Match ROM command, 55h, is used by the host to select a specific SDQ device when the family code and identification number is known. The host issues the Match ROM command followed by the family code, ROM number, and the CRC byte. The device that matches the 64-bit ROM sequence is selected and available to perform subsequent memory and status function commands.

Figure 4. Match ROM Sequence

### 7.4.5.3 Skip ROM

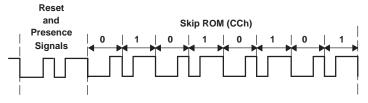

This Skip ROM command, CCh, allows the host to access the memory and status functions without issuing the 64-bit ROM code sequence. The Skip ROM command is directly followed by a memory or status functions command.

Figure 5. Skip ROM Sequence

### 7.4.6 Memory and Status Function Commands

Four memory and status function commands allow read and modification of the 1536-bit EPROM data memory or the 7-byte EPROM status memory. There is a Read Memory and Field CRC command, plus the Write Memory, Read Status, and Write Status commands. The bq2026 responds to memory and status function commands only after a device is selected by a ROM command.

### 7.4.7 Read Memory and Field CRC

To read the memory, the ROM command is followed by the Read Memory command, F0h, followed by the address low byte and then the address high byte.

The host then issues read time slots and receives data from the bq2026, starting at the initial address and continuing until the end of the 1536-bit data field is reached, or until a reset pulse is issued. If reading occurs through the end of memory space, the host may issue sixteen additional read time slots and the bq2026 responds with a 16-bit CRC of all data bytes read from the initial starting byte through the last byte of memory. After the CRC is received by the host, any subsequent read time slots appears as logical 1s until a reset pulse is issued. Any reads ended by a reset pulse prior to reaching the end of memory do not have the 16-bit CRC available.

| <br>on and ROM<br>nd Sequence | Read Memory Command<br>F0h | Add | Address Low<br>Byte |    |     |  | dress High<br>Byte | Read EPROM Memory Until<br>End of EPROM Memory | Read and<br>Verify 16-bit<br>CRC |

|-------------------------------|----------------------------|-----|---------------------|----|-----|--|--------------------|------------------------------------------------|----------------------------------|

|                               |                            | A0  | A7                  | A8 | A15 |  |                    |                                                |                                  |

<sup>(1)</sup> Individual bytes of address and data are transmitted LSB first.

Figure 6. Read Memory and Field CRC

#### 7.4.8 Read Status

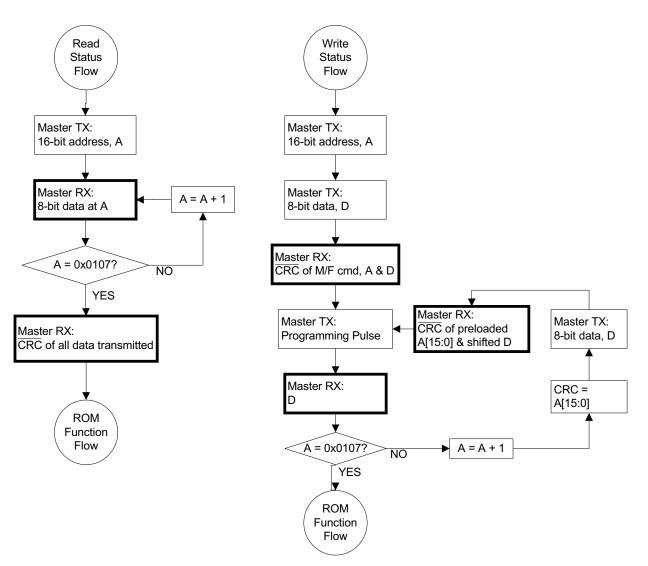

The Read Status command is used to read data from the EPROM status data field. After issuing a ROM command, the host issues the Read Status command, AAh, followed by the address low byte and then the address high byte.

#### **NOTE**

An 16-bit CRC of the command byte and address bytes is computed by the bq2026 and read back by the host to confirm that the correct command word and starting address were received.

If the CRC read by the host is incorrect, a reset pulse must be issued and the entire sequence must be repeated. If the CRC received by the host is correct, the host issues read time slots and receives data from the bq2026 starting at the supplied address and continuing until the end of the EPROM Status data field is reached. At that point, the host receives a 16-bit CRC that is the result of shifting into the CRC generator all of the data bytes from the initial starting byte through the final byte.

This feature is provided because the EPROM status information may change over time making it impossible to program the data once and include an accompanying CRC that is always valid. Therefore, the Read Status command supplies a 16-bit CRC that is based on (and always is consistent with) the current data stored in the EPROM status data field.

After the 16-bit CRC is read, the host receives logical 1s from the bq2026 until a reset pulse is issued. The Read Status command sequence can be ended at any point by issuing a reset pulse.

| Initialization and ROM<br>CommandSequence | Read Memory Command<br>AAh | Address Low<br>Byte | Address High<br>Byte | Read Status Memory Until<br>End of Page | Read and<br>Verify 16-bit<br>CRC   |

|-------------------------------------------|----------------------------|---------------------|----------------------|-----------------------------------------|------------------------------------|

|                                           |                            | A0 A7               | A8 A15               |                                         | of command,<br>address and<br>data |

Figure 7. READ STATUS Command

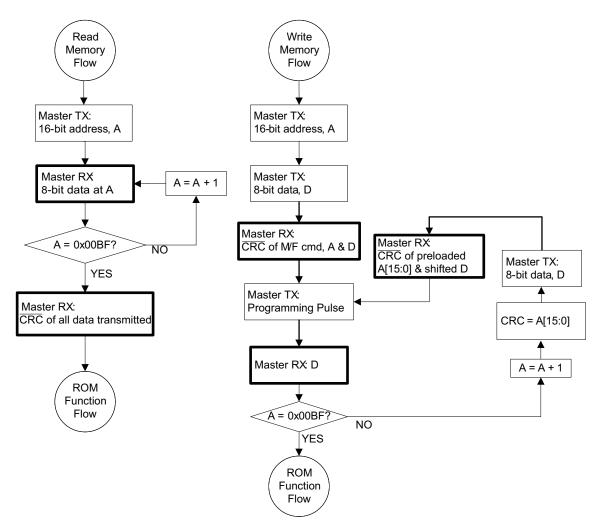

Figure 8. Status Memory Read and Write Flowchart

# 7.4.9 Write Memory

The Write Memory command is used to program the 1536-bit EPROM memory field. The 1536-bit memory field is programmed in 1-byte segments. Data is first written into an 1-byte RAM buffer. The contents of the RAM buffer is then ANDed with the contents of the EPROM memory field when the programming command is issued.

Figure 9 illustrates the sequence of events for programming the EPROM memory field. After issuing a ROM command, the host issues the Write Memory command, 0Fh, followed by the low byte and then the high byte of the starting address. The host then transmits 1 byte of data to the bq2026.

a 16-bit CRC is calculated and transmitted based on the command, address and data. If this CRC agrees with the CRC calculated by the host, the host applies the programming voltage for at least 480  $\mu$ s or t<sub>EPROG</sub>.

If at any time during the Write Memory process, the CRC read by the host is incorrect, a reset pulse must be issued, and the entire sequence must be repeated.

The Write Data Memory command sequence can be terminated at any point by issuing a reset pulse except during the program pulse period t<sub>PROG</sub>.

#### NOTE

The bq2026 responds with the data from the selected EPROM address sent least significant-bit first. This response should be checked to verify the programmed byte. If the programmed byte is incorrect, then the host must reset the part and begin the write sequence again.

For both of these cases, the decision to continue programming is made entirely by the host, because the bq2026 is not able to determine if the 16-bit CRC calculated by the host agrees with the 16-bit CRC calculated by the bq2026.

Prior to programming, bits in the 1536-bit EPROM data field appear as logical 1s.

Figure 9. General Use OTP Memory Read and Write Flowchart

### 7.4.10 Write Status

The Write Status command is used to program the EPROM Status data field after the bq2026 has been selected by a ROM command

The flow chart in Figure 9 illustrates that the host issues the Write Status command, 55h, followed by the address low byte and then the address high byte followed by the byte of data to be programmed.

### NOTE

Individual bytes of address and data are transmitted LSB first. a 16-bit CRC of the command byte, address bytes, and data byte is computed by the bq2026 and read back by the host to confirm that the correct command word, starting address, and data byte were received.

If the CRC read by the host is incorrect, a reset pulse must be issued and the entire sequence must be repeated. If the CRC received by the host is correct, the programming voltage,  $V_{PP}$  is applied to the SDQ pin for period  $t_{PROG}$ . Prior to programming, the first 7 bytes of the EPROM STATUS data field appear as logical 1s. For each bit in the data byte provided by the host that is set to a logical 0, the corresponding bit in the selected byte of the EPROM STATUS data field is programmed to a logical 0 after the programming pulse has been applied at the byte location.

After the programming pulse is applied and the data line returns to  $V_{PU}$ , the host issues eight read time slots to verify that the appropriate bits have been programmed. The bq2026 responds with the data from the selected EPROM STATUS address sent least significant bit first. This response should be checked to verify the programmed byte. If the programmed byte is incorrect, then the host must reset the device and begin the write sequence again. If the bq2026 EPROM data byte programming was successful, the bq2026 automatically increments its address counter to select the next byte in the STATUS MEMORY data field. The least significant byte of the new two-byte address is also loaded into the 16-bit CRC generator as a starting value. The host issues the next byte of data using eight write time slots.

As the bq2026 receives this byte of data into the RAM buffer, it also shifts the data into the CRC generator that has been preloaded with the LSB of the current address and the result is a 16-bit CRC of the new data byte and the new address. After supplying the data byte, the host reads this 16-bit CRC from the bq2026 with eight read time slots to confirm that the address incremented properly and the data byte was received correctly. If the CRC is incorrect, a Reset Pulse must be issued and the Write Status command sequence must be restarted. If the CRC is correct, the host issues a programming pulse and the selected byte in memory is programmed.

#### NOTE

The initial write of the Write Status command, generates a 16-bit CRC value that is the result of shifting the command byte into the CRC generator, followed by the two-address bytes, and finally the data byte. Subsequent writes within this Write Status command due to the bq2026 automatically incrementing its address counter generates a 16-bit CRC that is the result of loading (not shifting) the LSB of the new (incremented) address into the CRC generator and then shifting in the new data byte.

For both of these cases, the decision to continue programming the EPROM Status registers is made entirely by the host, because the bq2026 is not able to determine if the 16-bit CRC calculated by the host agrees with the 16-bit CRC calculated by the bq2026. If an incorrect CRC is ignored and a program pulse is applied by the host, incorrect programming could occur within the bq2026. Also note that the bq2026 always increments its internal address counter after the receipt of the eight read time slots used to confirm the programming of the selected EPROM byte. The decision to continue is again made entirely by the host, therefore if the EPROM data byte does not match the supplied data byte but the master continues with the Write Status command, incorrect programming could occur within the bq2026. The Write Status command sequence can be ended at any point by issuing a reset pulse.

COMMAND **DESCRIPTION CATEGORY** (HEX) 33h Read serialization ROM and CRC 55h Match serialization ROM ROM Commands Available in Command Level I CCh Skip serialization ROM F0h Read memory and field CRC AAh Read EPROM status **Memory Function Commands** Available in Command Level II 0Fh Write memory 55h Write EPROM status

**Table 3. Command Code Summary**

### 7.4.11 SDQ Signaling

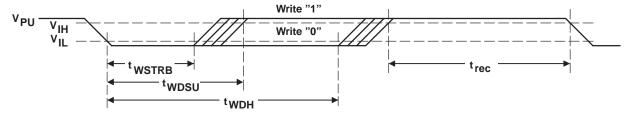

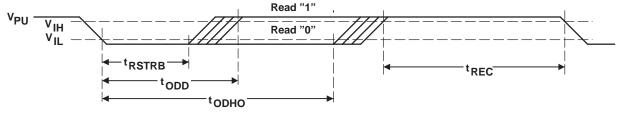

All SDQ signaling begins with initializing the device, followed by the host driving the bus low to write a 1 or 0, or to begin the start frame for a bit read. Figure 10 shows the initialization timing, whereas Figure 11 and Figure 12 show that the host initiates each bit by driving the data bus low for the start period,  $t_{WSTRB}$  /  $t_{RSTRB}$ . After the bit is initiated, either the host continues controlling the bus during a write, or the bq2026 responds during a read.

#### 7.4.12 Reset and Presence Pulse

If the data bus is driven low for more than 120  $\mu$ s, the bq2026 may be reset. Figure 10 shows that if the data bus is driven low for more than 480  $\mu$ s, the bq2026 resets and indicates that it is ready by responding with a presence pulse.

Figure 10. Reset Timing Diagram

#### 7.4.13 Write

The Write bit timing diagram in Figure 11 shows that the host initiates the transmission by issuing the t<sub>WSTRB</sub> portion of the bit and then either driving the data bus low for a write 0, or releasing the data bus for a write 1.

Figure 11. Write Bit Timing Diagram

### 7.4.14 Read

The Read bit timing diagram in Figure 12 shows that the host initiates the transmission of the bit by issuing the  $t_{RSTRB}$  portion of the bit. The bq2026 then responds by either driving the data bus low to transmit a read 0, or releasing the data bus to transmit a read 1.

Figure 12. Read Bit Timing Diagram

## 7.4.15 Program Pulse

Figure 13 shows the program pulse timing.

Figure 13. Program Pulse Timing Diagram

#### 7.4.16 Idle

If the bus is high, the bus is in the idle state. Bus transactions can be suspended by leaving the data bus in idle. Bus transactions can resume at any time from the idle state.

### 7.4.17 CRC Generation

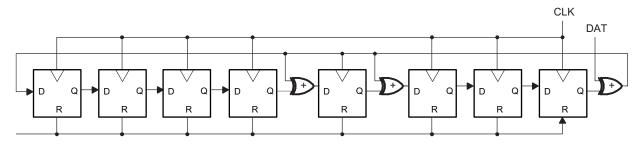

The bq2026 has a 8-bit CRC stored in the most significant byte of the 64-bit ROM. The bus master computes a CRC value from the first 56 bits of the 64-bit ROM and compares it to the value stored within the bq2026 to determine if the ROM data has been received error-free by the bus master. The equivalent polynomial function of this CRC is shown in Figure 14.

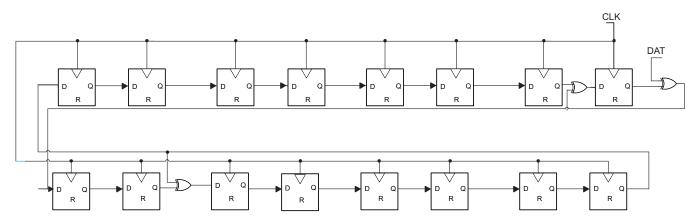

Under certain conditions, the bq2026 also generates a 16-bit CRC value using the polynomial function is shown in Figure 15 and provides this value to the bus master which validates the transfer of command, address, and data bytes from the bus master to the bq2026. The bq2026 computes a 16-bit CRC for the command, address, and data bytes received for the Write Memory and the Write Status commands, and then outputs this value to the bus master which confirms proper transfer. Similarly, the bq2026 computes a 16-bit CRC for the command and address bytes received from the bus master for the Read Memory, and Read Status commands to confirm that these bytes have been received correctly.

In each case, where a CRC is used for data transfer validation, the bus master must calculate a CRC value using the polynomial function in Figure 14 or Figure 15 and compares the calculated value to either the 8-bit CRC value stored in the 64-bit ROM portion of the bq2026 (for ROM reads) or the 16-bit CRC value computed within the bq2026. The comparison of CRC values and the decision to continue with an operation are determined entirely by the bus master. No circuitry on the bq2026 prevents a command sequence from proceeding if the CRC stored in or calculated by the bq2026 does not match the value generated by the bus master. Proper use of the CRC can result in a communication channel with a high level of integrity.

Figure 14. 8-bit CRC Generator Circuit (X8 + X5 + X4 + 1) for Serial Number Read

Figure 15. 16-bit CRC Generator Circuit ( $X^{16} + X^{15} + X^2 + 1$ ) for Memory Interface

# 8 器件和文档支持

# 8.1 商标

SDQ is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

## 8.2 静电放电警告

ESD 可能会损坏该集成电路。德州仪器 (TI) 建议通过适当的预防措施处理所有集成电路。如果不遵守正确的处理措施和安装程序,可能会损坏集成电路。

**ESD** 的损坏小至导致微小的性能降级,大至整个器件故障。 精密的集成电路可能更容易受到损坏,这是因为非常细微的参数更改都可能会导致器件与其发布的规格不相符。

## 8.3 术语表

SLYZ022 — TI 术语表。

这份术语表列出并解释术语、首字母缩略词和定义。

# 9 机械、封装和可订购信息

以下页中包括机械、封装和可订购信息。 这些信息是针对指定器件可提供的最新数据。 这些数据会在无通知且不 对本文档进行修订的情况下发生改变。 欲获得该数据表的浏览器版本,请查阅左侧的导航栏。 www.ti.com 10-Nov-2025

### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins   | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/        | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|------------------|-----------------------|------|---------------|--------------------|--------------|--------------|

|                       | (1)    | (2)           |                  |                       | (3)  | Ball material | Peak reflow        |              | (6)          |

|                       |        |               |                  |                       |      | (4)           | (5)                |              |              |

| BQ2026DBZR            | Active | Production    | SOT-23 (DBZ)   3 | 3000   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -20 to 70    | WAIS         |

| BQ2026DBZR.B          | Active | Production    | SOT-23 (DBZ)   3 | 3000   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -20 to 70    | WAIS         |

| BQ2026LPR             | Active | Production    | TO-92 (LP)   3   | 2000   LARGE T&R      | Yes  | SN            | N/A for Pkg Type   | -20 to 70    | BQ2026       |

| BQ2026LPR.B           | Active | Production    | TO-92 (LP)   3   | 2000   LARGE T&R      | Yes  | SN            | N/A for Pkg Type   | -20 to 70    | BQ2026       |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

**PACKAGE MATERIALS INFORMATION**

www.ti.com 5-Jan-2021

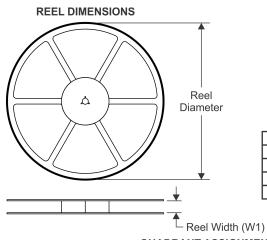

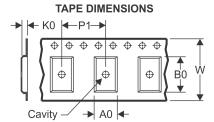

# TAPE AND REEL INFORMATION

|   |    | Dimension designed to accommodate the component width     |

|---|----|-----------------------------------------------------------|

| E | 30 | Dimension designed to accommodate the component length    |

| K | (0 | Dimension designed to accommodate the component thickness |

|   | N  | Overall width of the carrier tape                         |

| F | 21 | Pitch between successive cavity centers                   |

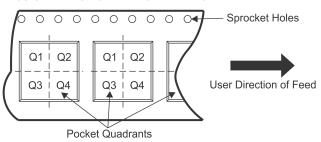

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

## \*All dimensions are nominal

| Device     | Package<br>Type | Package<br>Drawing |   |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| BQ2026DBZR | SOT-23          | DBZ                | 3 | 3000 | 179.0                    | 8.4                      | 3.15       | 2.95       | 1.22       | 4.0        | 8.0       | Q3               |

www.ti.com 5-Jan-2021

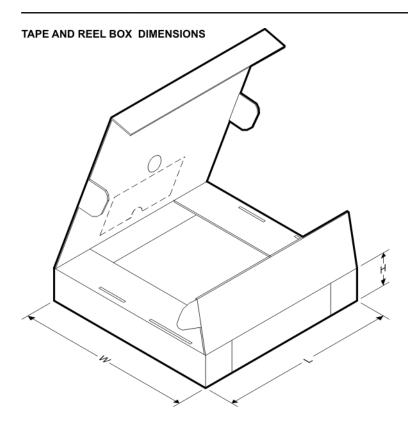

### \*All dimensions are nominal

| Device Package Type |        | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---------------------|--------|-----------------|------|------|-------------|------------|-------------|--|

| BQ2026DBZR          | SOT-23 | DBZ             | 3    | 3000 | 200.0       | 183.0      | 25.0        |  |

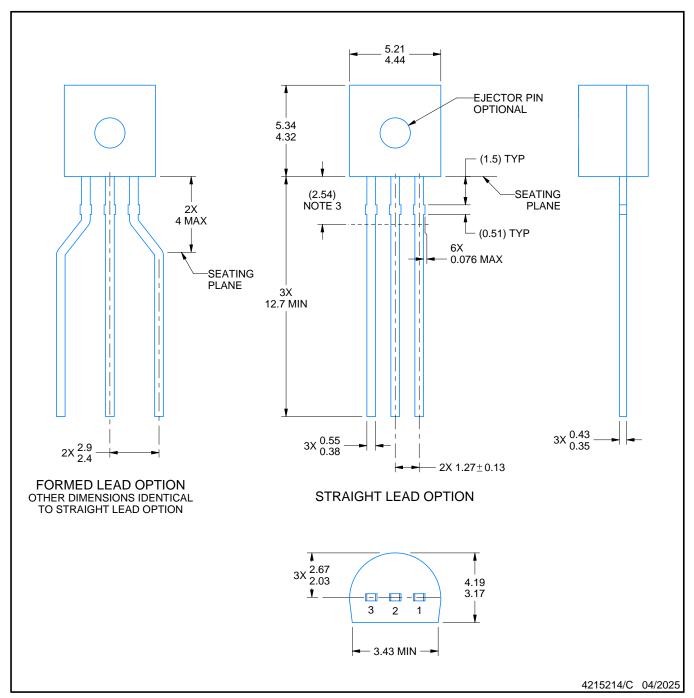

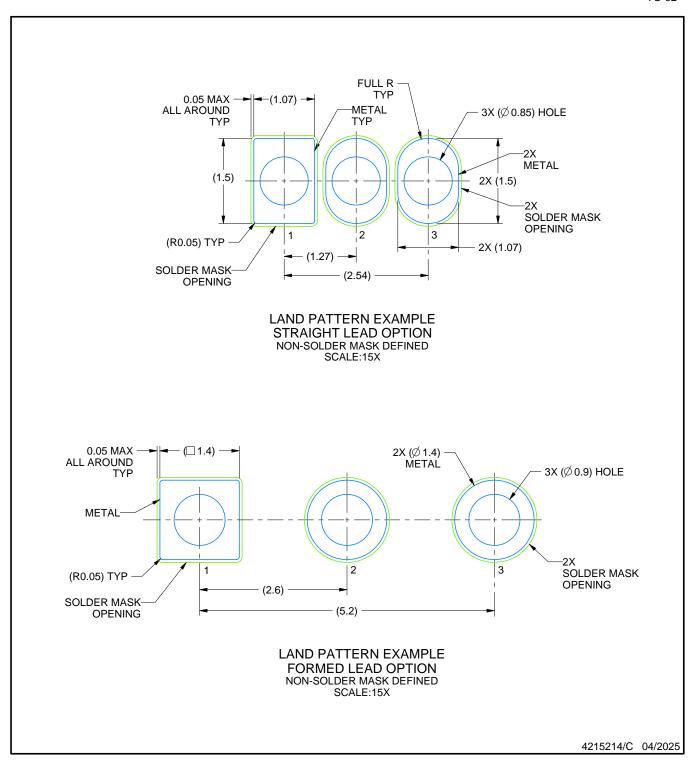

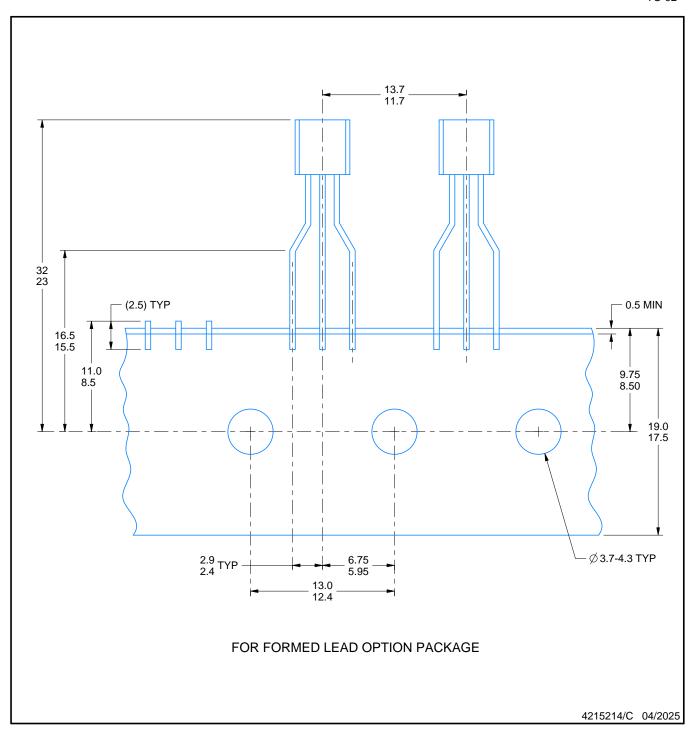

TO-92 - 5.34 mm max height

TO-92

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. Lead dimensions are not controlled within this area. 4. Reference JEDEC TO-226, variation AA.

- 5. Shipping method:

- a. Straight lead option available in bulk pack only.

b. Formed lead option available in tape and reel or ammo pack.

- c. Specific products can be offered in limited combinations of shipping medium and lead options.

- d. Consult product folder for more information on available options.

TO-92

TO-92

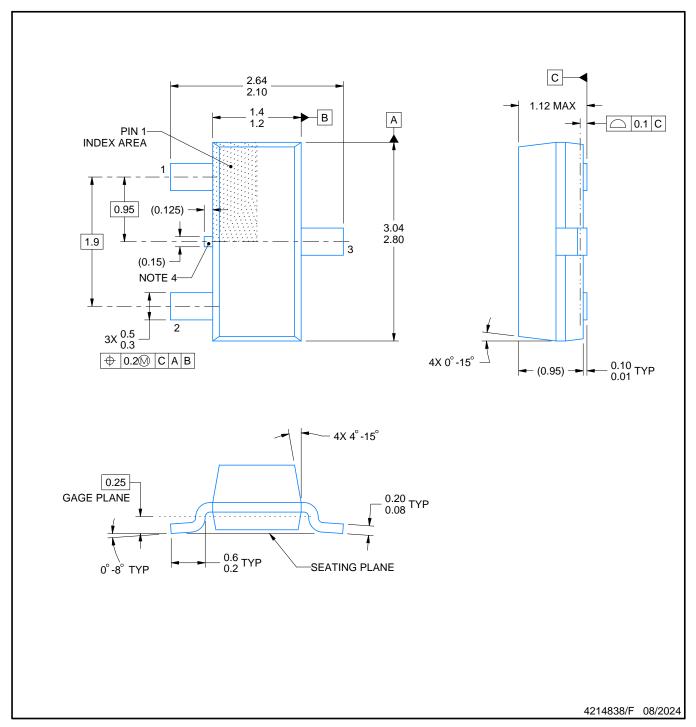

SMALL OUTLINE TRANSISTOR

# NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

This drawing is subject to change without notice.

Reference JEDEC registration TO-236, except minimum foot length.

- 4. Support pin may differ or may not be present.

- 5. Body dimensions do not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.25mm per side

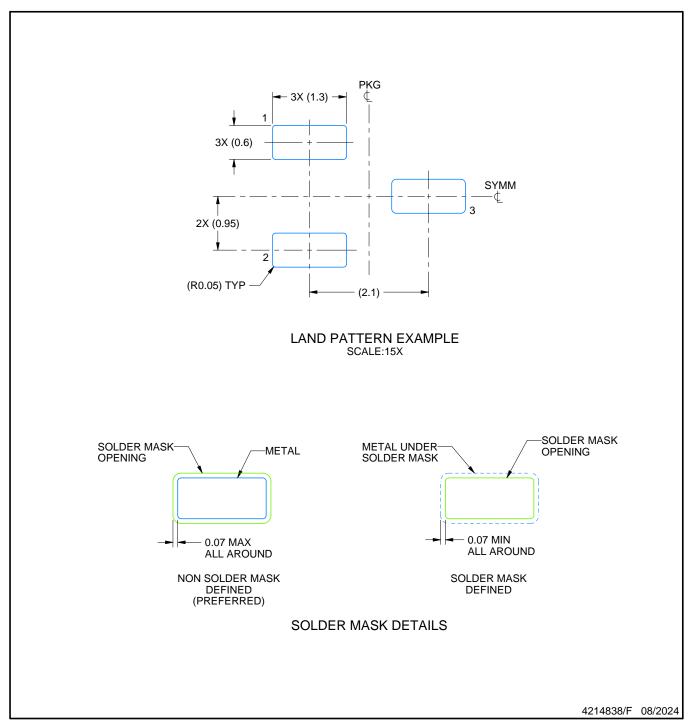

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

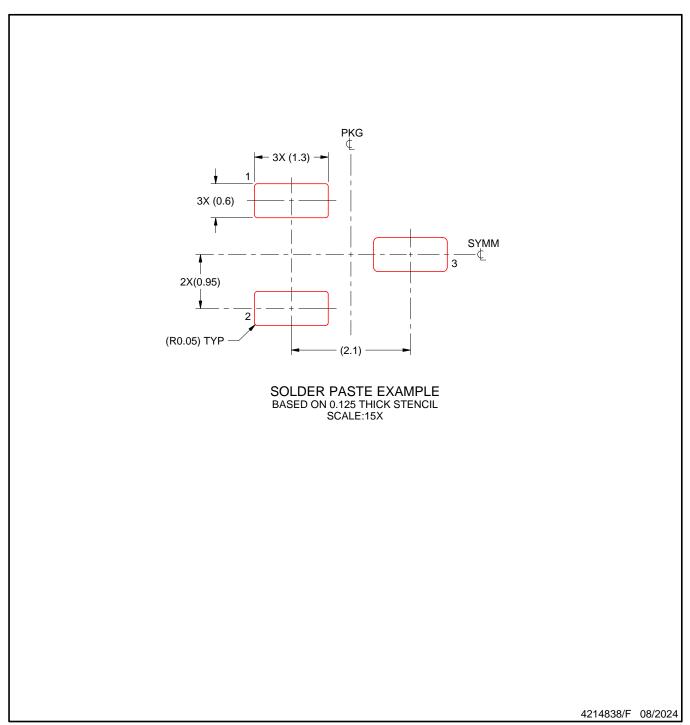

- 5. Publication IPC-7351 may have alternate designs.6. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

- 7. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 8. Board assembly site may have different recommendations for stencil design.

# 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月