# 带有集成模拟正交调制器的双路 14 位 65 百万次采样/秒 (MSPS) 数模转换

## 器

查询样品: AFE7070

#### 特性

- 最大采样率: 65MSPS

- 低功耗:

- 325mW 低压差分信令 (LVDS) 输出模式

- 334mW 模拟输出模式

- 交叉 CMOS 输入, 1.8-3.3V IOVDD

- 针对独立数据和数模转换器 (DAC) 时钟的输入 FIFO

- 用于寄存器编程的3或4个引脚SPI接口

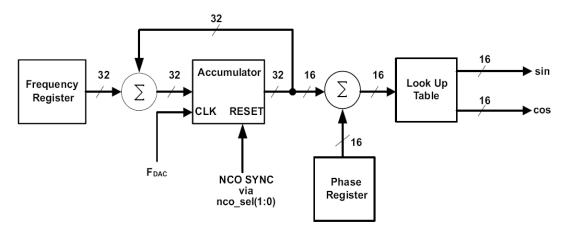

- 复杂数控振荡器 (NCO) (DDS): 32 位频率, 16 位相位

- 正交调制器校正:针对边带和本地振荡 (LO) 抑制 的增益、相位、偏移

- 支持可编程带宽的模拟基带滤波器: 20MHz 最大射频 (RF) 带宽

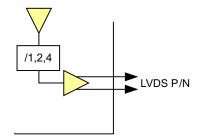

- RF 输出:模拟(线性)或 LVDS(时钟)

- RF 频率范围: 100MHz 至 2.7GHz

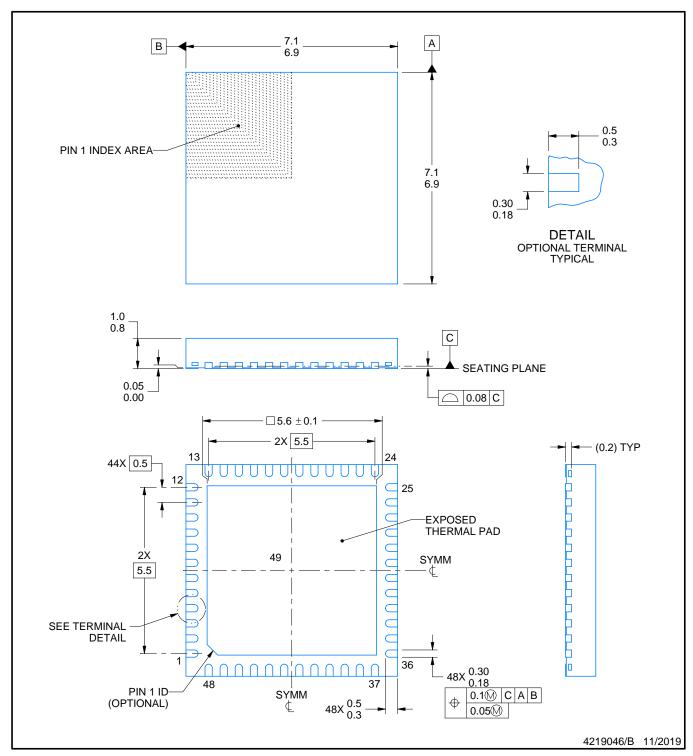

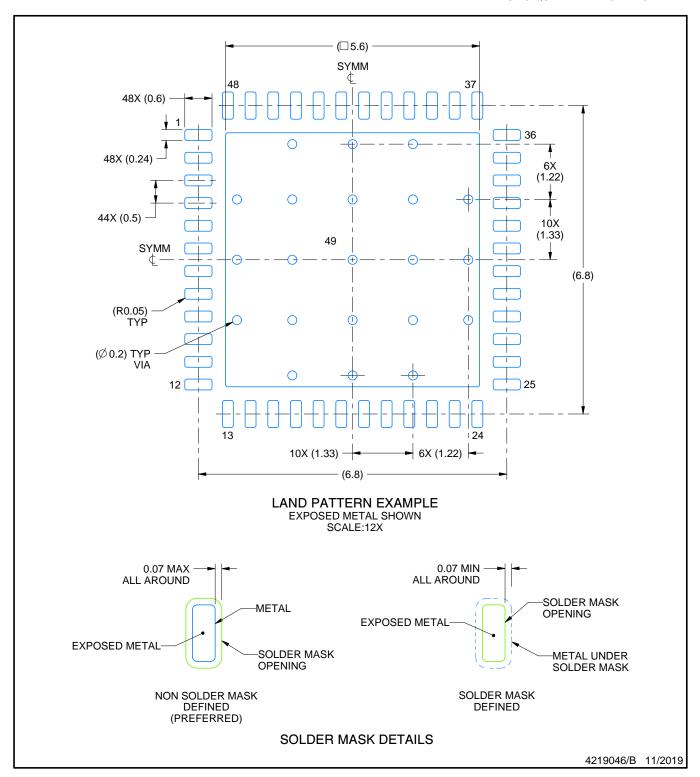

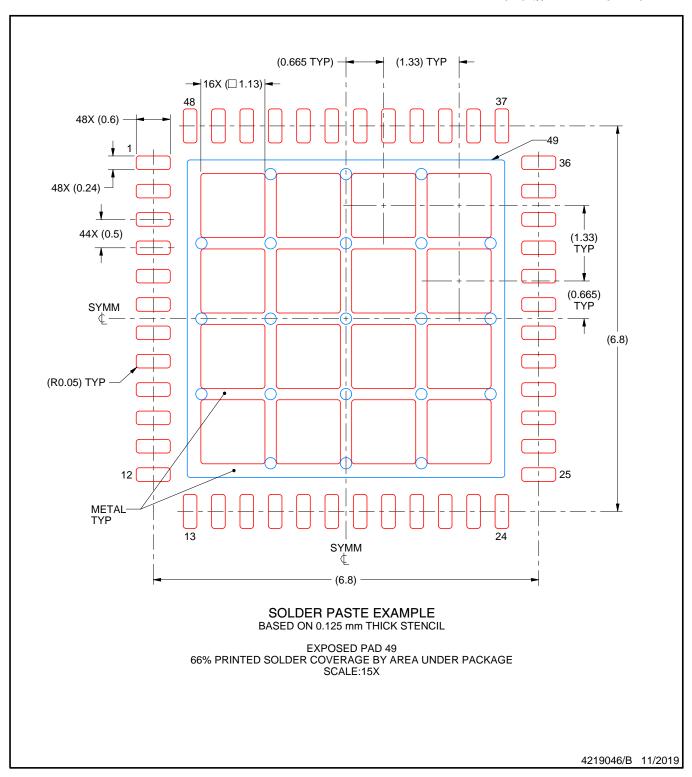

- 封装: 48 引脚四方扁平无引线 (QFN) 封装 (7mm x 7mm)

#### 应用范围

- 低功耗、紧凑型软件无线电

- 飞蜂窝和微蜂窝基站 (BTS)

- 时钟频率变换

#### 说明

AFE7070 是一款双路 14 位 65MSPS 数模转换器 (DAC),此转换器具有集成的、可编程四阶基带滤波器 和模拟正交调制器。 AFE7070 包括用于频率生成/转换的数控振荡器和用于提供 LO 和边带抑制功能的正交调制器校正电路等附加数字信号处理特性。 AFE7070 有一个交叉的 14 位 1.8V 至 3.3V CMOS 输入。 AFE7070 提供 RF 输出频率范围介于 100MHz 至 2.7GHz 之间的 20MHz RF 信号带宽。 一个可选 LVDS 输出可被用于将正交调制器输出转换为一个高达 800MHz 的时钟信号。 使用 LVDS 输出时,总功耗小于 350mW; 使用模拟 RF 输出时,总功耗小于 350mW; 使用模拟 RF 输出时,总功耗小于 334mW。

AFE7070 采用 7mm x 7mm 48 引脚 QFN 封装。 AFE7070 可在整个工业温度范围 (-40°C 至 85°C) 内 工作。

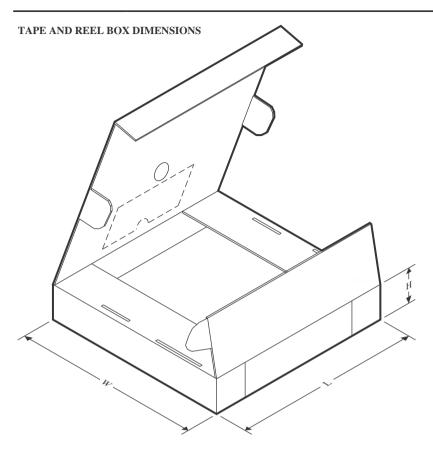

#### **AVAILABLE OPTIONS**

| T <sub>A</sub> | ORDER CODE    | PACKAGE DRAWING/TYPE              | TRANSPORT MEDIA | QUANTITY |

|----------------|---------------|-----------------------------------|-----------------|----------|

|                | AFE7070IRGZ25 |                                   |                 | 25       |

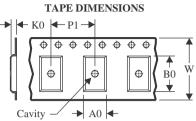

| -40°C to 85°C  | AFE7070IRGZT  | RGZ / 48QFN quad flatpack no-lead | Tape and reel   | 250      |

|                | AFE7070IRGZR  |                                   |                 | 2500     |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

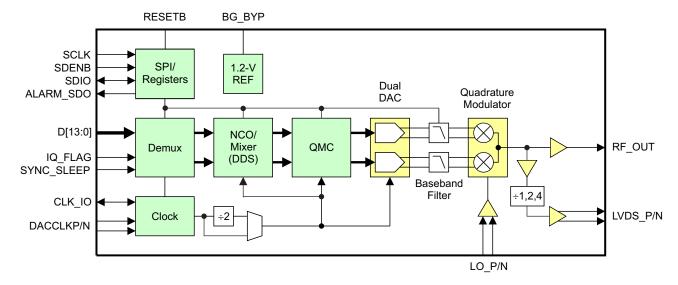

#### **BLOCK DIAGRAM**

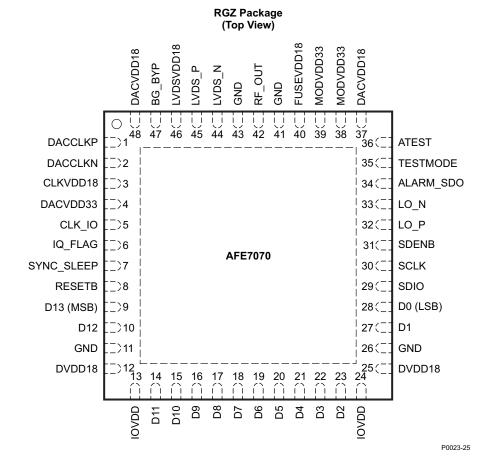

#### **PIN CONFIGURATION**

#### **PIN FUNCTIONS**

| DIN                 |                            |     | PIN FUNCTIONS                                                                                                                                                                                                                                                                                                 |

|---------------------|----------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN                 | NO                         | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                   |

| NAME                | NO.                        |     |                                                                                                                                                                                                                                                                                                               |

| MISC/SERIAL         |                            |     | T                                                                                                                                                                                                                                                                                                             |

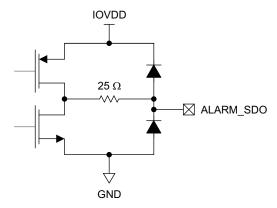

| ALARM_SDO           | _SDO 34 O                  |     | CMOS output for ALARM condition, active-low. The ALARM output functionality is defined through the CONFIG7 registers.                                                                                                                                                                                         |

| 7.E7 II (IVI_0D 0   | 0.                         | J   | Optionally, it can be used as the unidirectional data output in 4-pin serial interface mode (CONFIG3 sif_4pin = 1). 1.8-V to 3.3-V CMOS, set by IOVDD.                                                                                                                                                        |

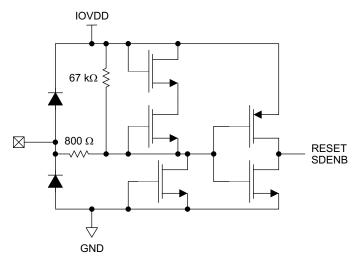

| RESETB              | 8                          | I   | Resets the chip when low. 1.8-V to 3.3-V CMOS, set by IOVDD. Internal pullup                                                                                                                                                                                                                                  |

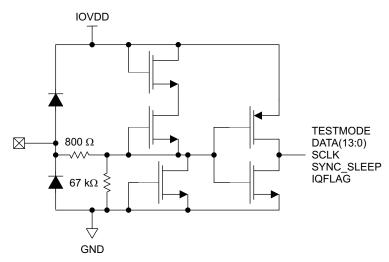

| SCLK                | 30                         | I   | Serial interface clock. 1.8-V to 3.3-V CMOS, set by IOVDD. Internal pulldown                                                                                                                                                                                                                                  |

| SDENB               | 31                         | I   | Active-low serial data enable, always an input. 1.8-V to 3.3-V CMOS, set by IOVDD. Internal pullup                                                                                                                                                                                                            |

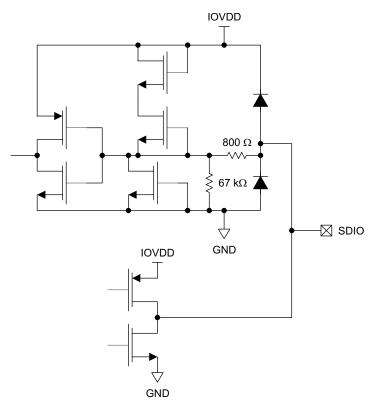

| SDIO                | 29                         | I/O | Bidirectional serial data in 3-pin mode (default). In 4-pin interface mode (CONFIG3 sif_4pin), the SDIO pin is an input only. 1.8-V to 3.3-V CMOS, set by IOVDD. Internal pulldown                                                                                                                            |

| DATA/CLOCK I        | NTERFA                     | CE  |                                                                                                                                                                                                                                                                                                               |

| CLK_IO              | 5                          | I/O | Single-ended input or output CMOS level clock for latching input data. 1.8-V to 3.3-V CMOS, set by IOVDD.                                                                                                                                                                                                     |

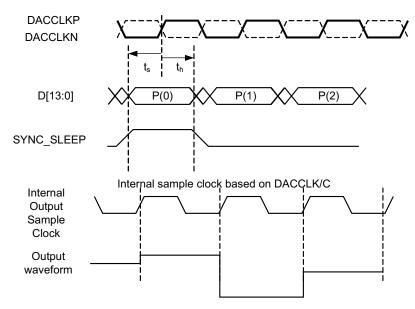

| D[13:0]             | 9, 10,<br>14–23,<br>27, 28 | I   | Data bits 0 through 13. D13 is the MSB, D0 is the LSB. For complex data, channel I and channel Q are multiplexed. For NCO phase data, either 14 bits are transferred at the internal sample clock rate, or 8 MSBs and 8 LSBs are interleaved on D[13:6]. 1.8-V to 3.3-V CMOS, set by IOVDD. Internal pulldown |

| DACCLKP,<br>DACCLKN | 1, 2                       | 1   | Differential input clock for DACs.                                                                                                                                                                                                                                                                            |

| IQ_FLAG             | 6                          | I   | When register CONFIG1 iqswap is 0, IQ-FLAG high identifies the DACA sample in dual-input or dual-output clock modes. 1.8-V or 3.3-V CMOS, set by IOVDD. Internal pulldown                                                                                                                                     |

| SYNC_SLEEP          | 7                          | 1   | Multi-function. Sync signal for signal processing blocks, TX ENABLE or SLEEP function. Selectable via SPI. 1.8-V to 3.3-V CMOS, set by IOVDD.                                                                                                                                                                 |

| RF                  |                            |     |                                                                                                                                                                                                                                                                                                               |

| LO_P, LO_N          | 32, 33                     | I   | Local oscillator input. Can be used differentially or single-ended by terminating the unused input through a capacitor and $50-\Omega$ resistor to GND.                                                                                                                                                       |

| LVDS_P,<br>LVDS_N   | 45, 44                     | 0   | Differential LVDS output                                                                                                                                                                                                                                                                                      |

| RF_OUT              | 42                         | 0   | Analog RF output                                                                                                                                                                                                                                                                                              |

| REFERENCE           |                            |     |                                                                                                                                                                                                                                                                                                               |

| ATEST               | 36                         | 0   | Factory use only. Do not connect.                                                                                                                                                                                                                                                                             |

| BG_BYP              | 47                         | I   | Reference voltage decoupling – connect 0.1 µF to GND.                                                                                                                                                                                                                                                         |

| TESTMODE            | 35                         | I   | Factory use only. Connect to GND.                                                                                                                                                                                                                                                                             |

| POWER               |                            |     |                                                                                                                                                                                                                                                                                                               |

| IOVDD               | 13, 24                     | Į   | 1.8-V to 3.3-V supply for CMOS I/Os                                                                                                                                                                                                                                                                           |

| CLKVDD18            | 3                          | I   | 1.8 V                                                                                                                                                                                                                                                                                                         |

| DVDD18              | 12, 25                     | I   | 1.8 V                                                                                                                                                                                                                                                                                                         |

| LVDSVDD18           | 46                         | I   | 1.8 V                                                                                                                                                                                                                                                                                                         |

| DACVDD18            | 37, 48                     | I   | 1.8 V                                                                                                                                                                                                                                                                                                         |

| DACVDD33            | 4                          | I   | 3.3 V                                                                                                                                                                                                                                                                                                         |

| MODVDD33            | 38, 39                     | I   | 3.3 V                                                                                                                                                                                                                                                                                                         |

| FUSEVDD18           | 40                         | I   | Connect to 1.8 V to 3.3 V supply (1.8 V is preferred to lower power dissipation).                                                                                                                                                                                                                             |

| GND                 | 11, 26,<br>41, 43          | 1   | Ground                                                                                                                                                                                                                                                                                                        |

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

|                                     |                                                                                      | VALUE                       |

|-------------------------------------|--------------------------------------------------------------------------------------|-----------------------------|

| Supply voltage                      | DACVDD33, MODVDD33, FUSEVDD18, IOVDD(2)                                              | −0.5 V to 4 V               |

| range                               | DVDD18, CLKVDD18, DACVDD18 <sup>(2)</sup>                                            | −0.5 V to 2.3 V             |

|                                     |                                                                                      | –0.5 V to 4 V               |

|                                     | D[130], IQ FLAG, SYNC_SLEEP, SCLK, SDENB, SDIO, ALARM_SDO, RESETB , CLK_IO, TESTMODE | -0.5 V to IOVDD + 0.5 V     |

| Supply voltage range <sup>(2)</sup> | DACCLKP, DACCLKN                                                                     | -0.5 V to CLKVDD18 + 0.5 V  |

| range (=/                           | LVDS_P, LVDS_N                                                                       | -0.5 V to LVDSVDD18 + 0.5 V |

|                                     | BG_BYP, ATEST                                                                        | -0.5 V to DACVDD33 + 0.5 V  |

|                                     | RFOUT, LO_P, LO_N                                                                    | -0.5 V to MODVDD33 + 0.5 V  |

| Operating free-air t                | emperature range, T <sub>A</sub>                                                     | -40°C to 85°C               |

| Storage temperatur                  | re range                                                                             | −65°C to 150°C              |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

Typical values at  $T_A = 25^{\circ}$ C, full temperature range is  $T_{MIN} = -40^{\circ}$ C to  $T_{MAX} = 85^{\circ}$ C, DAC sampling rate = 65 MSPS, DVDD18 = 1.8 V, CLKVDD18 = 1.8 V, DACVDD18 = 1.8 V, IOVDD = 3.3 V, DACVDD33 = 3.3 V, MODVDD33 = 3.3 V, analog output (unless otherwise noted)

|                        | PARAMETER                                                        | TEST CONDITIONS                                                       | MIN  | TYP | MAX  | UNIT |

|------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------|------|-----|------|------|

| DC SPECIFICA           | ATIONS                                                           |                                                                       |      |     |      |      |

|                        | DAC resolution                                                   |                                                                       | 14   |     |      | Bits |

| REFERENCE (            | OUTPUT                                                           |                                                                       |      |     |      |      |

|                        | Reference voltage                                                |                                                                       | 1.14 | 1.2 | 1.26 | V    |

| POWER SUPP             | PLY                                                              |                                                                       |      |     |      |      |

| IOVDD                  | I/O supply voltage                                               |                                                                       | 1.71 |     | 3.6  | V    |

| DVDD18                 | Digital supply voltage                                           |                                                                       | 1.71 | 1.8 | 1.89 | V    |

| CLKVDD18               | Clock supply voltage                                             |                                                                       | 1.71 | 1.8 | 1.89 | V    |

| DACVDD18               | DAC 1.8-V analog supply voltage                                  |                                                                       | 1.71 | 1.8 | 1.89 | V    |

| LVDSVDD18              | LVDS analog supply voltage                                       |                                                                       | 1.71 | 1.8 | 1.89 | V    |

| FUSEVDD18              | FUSE analog supply voltage                                       | Connect to 1.8-V supply for lower power                               | 1.71 | 1.8 | 3.6  | V    |

| DACVDD33               | DAC 3.3-V analog supply voltage                                  |                                                                       | 3.15 | 3.3 | 3.45 | V    |

| MODVDD33               | Modulator analog supply voltage                                  |                                                                       | 3.15 | 3.3 | 3.45 | V    |

| I <sub>IOVDD</sub>     | I/O supply current                                               |                                                                       |      |     |      | mA   |

| I <sub>DVDD18</sub>    | Digital supply current                                           |                                                                       |      | 18  |      | mA   |

| I <sub>CLKVDD18</sub>  | Clock supply current                                             |                                                                       |      |     |      | mA   |

| I <sub>DACVDD18</sub>  | DAC 1.8-V supply current                                         |                                                                       |      |     |      | mA   |

| I <sub>LVDSVDD18</sub> | LVDS output supply current                                       |                                                                       |      |     |      | mA   |

| I <sub>FUSEVDD18</sub> | FUSE supply current                                              |                                                                       |      | 21  |      | mA   |

| I <sub>DACVDD33</sub>  | DAC 3.3-V supply current                                         |                                                                       |      |     |      | mA   |

| I <sub>MODVDD33</sub>  | Modulator supply current                                         |                                                                       |      | 68  |      | mA   |

|                        |                                                                  | LVDS output: NCO, QMC active, $\rm f_{DAC} = 40~MHz,  IOVDD = 2.5~V$  |      | 337 | 380  | mW   |

|                        | Power dissipation                                                | Analog output: NCO off, QMC active, $f_{DAC}$ = 65 MHz, IOVDD = 2.5 V |      | 335 | 380  | mW   |

|                        |                                                                  | Sleep mode with clock, internal reference on, IOVDD = 2.5 V           |      | 80  |      | mW   |

|                        |                                                                  | Sleep mode without clock, internal reference off, IOVDD = 2.5 V       |      | 5   | 25   | mW   |

| POWER SUPP             | PLY vs MODE                                                      |                                                                       |      |     |      |      |

|                        | 3.3-V supplies (DACVDD33, MODVDD33, IOVDD)                       |                                                                       |      | 72  |      | mA   |

|                        | 1.8-V supplies (DVDD18, CLKVDD18, DACVDD18, FUSEVD18, LVDSVDD18) | NCO = 1 MHz, LVDS on, RF out off, no input data, 65 MSPS              |      | 47  |      | mA   |

|                        | Power dissipation                                                |                                                                       |      | 322 |      | mW   |

<sup>(2)</sup> Measured with respect to GND

## DC ELECTRICAL CHARACTERISTICS (continued)

Typical values at  $T_A = 25^{\circ}$ C, full temperature range is  $T_{MIN} = -40^{\circ}$ C to  $T_{MAX} = 85^{\circ}$ C, DAC sampling rate = 65 MSPS, DVDD18 = 1.8 V, CLKVDD18 = 1.8 V, DACVDD18 = 1.8 V, IOVDD = 3.3 V, DACVDD33 = 3.3 V, MODVDD33 = 3.3 V, analog output (unless otherwise noted)

| PARAMETER                                                         | TEST CONDITIONS                                                                   | MIN TYP | MAX | UNIT |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------|-----|------|

| 3.3-V supplies (DACVDD33, MODVDD33, IOVDD)                        |                                                                                   | 71      |     | mA   |

| 1.8-V supplies (DVDD18, CLKVDD18, DACVDD18, FUSEVDD18, LVDSVDD18) | NCO = 1 MHz, LVDS on, RF out off,<br>no input data, 40 MSPS                       | 32      |     | mA   |

| Power dissipation                                                 |                                                                                   | 337     |     | mW   |

| 3.3-V supplies (DACVDD33, MODVDD33, IOVDD)                        |                                                                                   | 102     |     | mA   |

| 1.8-V supplies (DVDD18, CLKVDD18, DACVDD18, FUSEVD18, LVDSVDD18)  | MHz full-scale input, RF out on, LVDS output off,     NCO off, QMC on, 65 MSPS    | 36      |     | mA   |

| Power dissipation                                                 |                                                                                   | 334     |     | mW   |

| 3.3-V supplies (DACVDD33, MODVDD33, IOVDD)                        |                                                                                   | 101     |     | mA   |

| 1.8-V supplies (DVDD18, CLKVDD18, DACVDD18, FUSEVD18, LVDSVDD18)  | MHz full-scale input, RF out on, LVDS output off,     NCO off, QMC off, 32.5 MSPS | 22      |     | mA   |

| Power dissipation                                                 |                                                                                   | 325     |     | mW   |

#### **ELECTRICAL CHARACTERISTICS**

Typical values at  $T_A = 25$ °C, full temperature range is  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, DAC sampling rate = 65 MSPS, DVDD18 = 1.8 V, CLKVDD18 = 1.8 V, DACVDD18 = 1.8 V, IOVDD = 3.3 V, DACVDD33 = 3.3 V, MODVDD33 = 3.3 V, analog output (unless otherwise noted)

|                       | PARAMETER                                        | TEST CONDITIONS                                               | MIN         | TYP  | MAX          | UNIT |

|-----------------------|--------------------------------------------------|---------------------------------------------------------------|-------------|------|--------------|------|

| DIGITAL               | INPUTS (D[13:0], IQ_FLAG, SDI, SCLK, SDENB, RE   | SETB, SYNC_SLEEP, ALARM_SDO, CLK_IO)                          |             |      |              |      |

|                       |                                                  | IOVDD = 3.3 V                                                 | 2.3         |      |              |      |

| $V_{\mathrm{IH}}$     | High-level input voltage                         | IOVDD = 2.5 V                                                 | 1.75        |      |              | V    |

|                       |                                                  | IOVDD = 1.8 V                                                 | 1.25        |      |              |      |

|                       |                                                  | IOVDD = 3.3 V                                                 |             |      | 1            |      |

| $V_{IL}$              | Low-level input voltage                          | IOVDD = 2.5 V                                                 |             |      | 0.75         | V    |

|                       |                                                  | IOVDD = 1.8 V                                                 |             |      | 0.54         |      |

| I <sub>IH</sub>       | High-level input current                         | IOVDD = 3.3 V                                                 | -80         |      | 80           | μΑ   |

| I <sub>IL</sub>       | Low-level input current                          | IOVDD = 3.3 V                                                 | -80         |      | 80           | μA   |

| C <sub>i</sub>        | Input capacitance                                |                                                               |             | 5    |              | pF   |

| f <sub>DAC</sub>      | DAC sample rate                                  | Interleaved data, f <sub>DAC</sub> = 1/2 × f <sub>INPUT</sub> | 0           |      | 65           | MSPS |

| f <sub>INPUT</sub>    | Input data rate                                  | Interleaved data, f <sub>INPUT</sub> = 2 × f <sub>DAC</sub>   | 0           |      | 130          | MSPS |

| DIGITAL               | OUTPUTS (ALARM_SDO, SDIO, CLK_IO)                |                                                               |             |      |              |      |

|                       | High land autout value                           | I <sub>LOAD</sub> = -100 μA                                   | IOVDD - 0.2 |      |              | V    |

| V <sub>OH</sub>       | High-level output voltage                        | I <sub>LOAD</sub> = -2 mA                                     | 0.8 × IOVDD |      |              | V    |

| .,                    |                                                  | I <sub>LOAD</sub> = 100 μA                                    |             |      | 0.2          | V    |

| V <sub>OL</sub>       | Low-level output voltage                         | I <sub>LOAD</sub> = 2 mA                                      |             |      | 0.22 × IOVDD | V    |

| CLOCK I               | NPUT (DACCLKP/DACCLKN)                           |                                                               |             |      |              |      |

|                       | DACCLKP/N duty cycle                             |                                                               | 40%         |      | 60%          |      |

|                       | DACCLKP/N differential voltage                   |                                                               | 0.4         |      | 1            | V    |

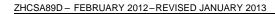

| Timing P              | arallel Data Input (D[13:0], IQ_FLAG, SYNC_SLEEP | ) – Dual Input Clock Mode                                     |             |      |              |      |

| t <sub>SU</sub>       | Input setup time                                 | Relative to CLK_IO rising edge                                |             | 1    |              | ns   |

| t <sub>H</sub>        | Input hold time                                  | Relative to CLK_IO rising edge                                |             | 1    |              | ns   |

| t <sub>LPH</sub>      | Input clock pulse high time                      |                                                               |             | 3    |              | ns   |

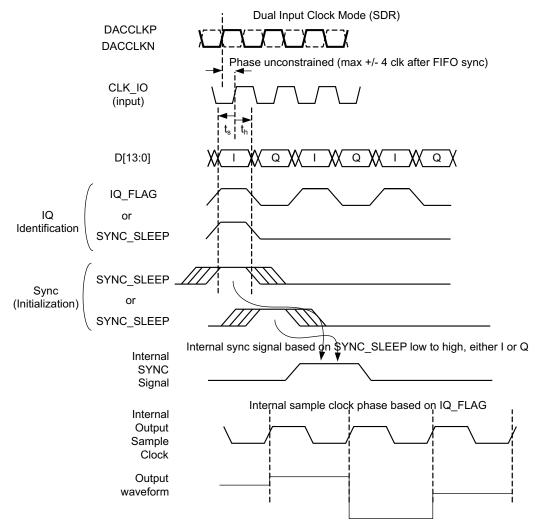

| Timing P              | arallel Data Input (D[13:0], IQ_FLAG, SYNC_SLEEP | ) – Dual Output Clock Mode                                    |             |      |              |      |

| t <sub>SU</sub>       | Input setup time                                 | Relative to CLK_IO rising edge                                | 1           | 0.2  |              | ns   |

| t <sub>H</sub>        | Input hold time                                  | Relative to CLK_IO rising edge                                | 1           | 0.2  |              | ns   |

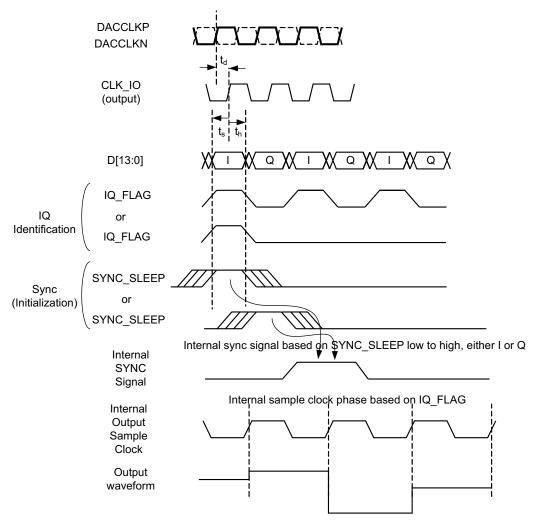

| Timing P              | arallel Data Input (D[13:0], IQ_FLAG, SYNC_SLEEP | ) – Single Differential DDR and SDR Clock Modes               |             |      |              |      |

| t <sub>SU</sub>       | Input setup time                                 | Relative to DACCLKP/N rising edge                             | 0           | -0.8 |              | ns   |

| t <sub>H</sub>        | Input hold time                                  | Relative to DACCLKP/N rising edge                             | 2           | 1    |              | ns   |

| Timing –              | Serial Data Interface                            |                                                               | ·           |      |              |      |

| t <sub>S(SDENB)</sub> | Setup time, SDENB to rising edge of SCLK         |                                                               |             | 20   |              | ns   |

| t <sub>S(SDIO)</sub>  | Setup time, SDIO valid to rising edge of SCLK    |                                                               |             | 10   |              | ns   |

| t <sub>H(SDIO)</sub>  | Hold time, SDIO valid to rising edge of SCLK     |                                                               |             | 5    |              | ns   |

| t <sub>SCLK</sub>     | Period of SCLK                                   |                                                               |             | 100  |              | ns   |

| t <sub>SCLKH</sub>    | High time of SCLK                                |                                                               |             | 40   |              | ns   |

| t <sub>SCLKL</sub>    | Low time of SCLK                                 |                                                               |             | 40   |              | ns   |

| t <sub>D(DATA)</sub>  | Data output delay after falling edge of SCLK     |                                                               |             | 10   |              | ns   |

| t <sub>RESET</sub>    | Minimum RESETB pulse duration                    |                                                               |             | 25   |              | ns   |

## **AC ELECTRICAL CHARACTERISTICS**

Typical values at  $T_A = 25$ °C, full temperature range is  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, DAC sampling rate = 65 MSPS, DVDD18 = 1.8 V, CLKVDD18 = 1.8 V, DACVDD18 = 1.8 V, IOVDD = 3.3 V, DACVDD33 = 3.3 V, MODVDD33 = 3.3 V, analog output (unless otherwise noted)

|                       | PARAMETER                                         | TEST CONDITIONS                                                                  | MIN | TYP | MAX | UNIT    |

|-----------------------|---------------------------------------------------|----------------------------------------------------------------------------------|-----|-----|-----|---------|

| LO INPU               | Т                                                 |                                                                                  |     |     |     |         |

| $f_{LO}$              | LO frequency range                                |                                                                                  | 0.1 |     | 2.7 | GHz     |

| P <sub>LO_IN</sub>    | LO input power                                    |                                                                                  | -5  |     | 5   | dBm     |

|                       | LO port return loss                               |                                                                                  |     | 15  |     |         |

| LVDS OL               | JTPUT                                             |                                                                                  |     |     |     |         |

| f <sub>LVDS_OUT</sub> | LVDS output frequency                             |                                                                                  | 100 |     | 800 | MHz     |

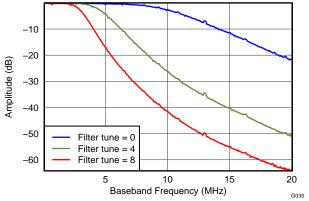

| INTEGRA               | ATED BASEBAND FILTER                              |                                                                                  |     |     |     |         |

|                       |                                                   | 2.5 MHz                                                                          |     | 1   |     |         |

|                       | Baseband attenuation at setting                   | 5 MHz                                                                            |     | 18  |     | -10     |

|                       | Filtertune = 8 relative to low-frequency signal   | 10 MHz                                                                           |     | 42  |     | dB      |

|                       | G                                                 | 20 MHz                                                                           |     | 65  |     |         |

|                       |                                                   | 10 MHz                                                                           |     | 1   |     |         |

|                       | Baseband attenuation at setting                   | 20 MHz                                                                           |     | 18  |     | ٩D      |

|                       | Filtertune = 0 relative to low-frequency signal   | 40 MHz                                                                           |     | 42  |     | dB      |

|                       | G .                                               | 55 MHz                                                                           |     | 58  |     |         |

|                       | Baseband filter phase linearity                   | RMS phase deviation from linear phase across minimum or maximum cutoff frequency |     | 2   |     | Degrees |

|                       | Baseband filter amplitude ripple                  | Frequency < 0.9 x nominal cutoff frequency                                       |     | 0.5 |     | dB      |

| RF Outpu              | ut Parameters – f <sub>LO</sub> = 100 MHz, Analog | Output                                                                           | ·   |     | ,   |         |

| P <sub>OUT_FS</sub>   | Full-scale RF output power                        | Full-scale 50-kHz digital sine wave                                              |     | -1  |     | dBm     |

| IP2                   | Output IP2                                        | Maximum LPF BW setting, f <sub>BB</sub> = 4.5, 5.5 MHz                           |     | 63  |     | dBm     |

| IP3                   | Output IP3                                        | Maximum LPF BW setting, f <sub>BB</sub> = 4.5, 5.5 MHz                           |     | 18  |     | dBm     |

|                       | Carrier feedthrough                               | Unadjusted, f <sub>BB</sub> = 50 kHz, full scale                                 |     | 45  |     | dBc     |

|                       | Sideband suppression                              | Unadjusted, f <sub>BB</sub> = 50 kHz, full scale                                 |     | 27  |     | dBc     |

|                       | Output noise floor                                | ≥ 30 MHz offset, f <sub>BB</sub> = 50 kHz, full scale                            |     | 137 |     | dBc/Hz  |

|                       | Output return loss                                |                                                                                  |     | 8.5 |     | dB      |

| RF Outpu              | ut Parameters – f <sub>LO</sub> = 450 MHz, Analog | Output                                                                           |     |     |     |         |

| P <sub>OUT_FS</sub>   | Full-scale RF output power                        | Full-scale 50-kHz digital sine wave                                              |     | 0.2 |     | dBm     |

| IP2                   | Output IP2                                        | Max LPF BW setting, f <sub>BB</sub> = 4.5, 5.5 MHz                               |     | 67  |     | dBm     |

| IP3                   | Output IP3                                        | Max LPF BW setting, f <sub>BB</sub> = 4.5, 5.5 MHz                               |     | 19  |     | dBm     |

|                       | Carrier feedthrough                               | Unadjusted, f <sub>BB</sub> = 50 kHz, full scale                                 |     | 45  |     | dBc     |

|                       | Sideband Suppression                              | Unadjusted, f <sub>BB</sub> = 50 kHz, full scale                                 |     | 38  |     | dBc     |

|                       | Output noise floor                                | ≥ 30 MHz offset, f <sub>BB</sub> = 50 kHz, full scale                            |     | 143 |     | dBc/Hz  |

|                       | Output return loss                                |                                                                                  |     | 8.5 |     | dB      |

| RF Outpu              | ut Parameters – f <sub>LO</sub> = 850 MHz, Analog | Output                                                                           |     |     |     |         |

| P <sub>OUT_FS</sub>   | Full-scale RF output power                        | Full-scale 50-kHz digital sine wave                                              |     | 0.3 |     | dBm     |

| IP2                   | Output IP2                                        | Max LPF BW setting, f <sub>BB</sub> = 4.5, 5.5 MHz                               |     | 64  |     | dBm     |

| IP3                   | Output IP3                                        | Max LPF BW setting, f <sub>BB</sub> = 4.5, 5.5 MHz                               |     | 19  |     | dBm     |

|                       | Carrier feedthrough                               | Unadjusted, f <sub>BB</sub> = 50 kHz, full scale                                 |     | 41  |     | dBc     |

|                       | Sideband suppression                              | Unadjusted, f <sub>BB</sub> = 50 kHz, full scale                                 |     | 37  |     | dBc     |

|                       | Output noise floor                                | ≥ 30 MHz offset, f <sub>BB</sub> = 50 kHz, full scale                            |     | 143 |     | dBc/Hz  |

|                       | Output return loss                                |                                                                                  |     | 8.5 |     | dB      |

| ACPR                  | Adjacent-channel power ratio                      | 1 WCDMA TM1 signal, PAR = 10 dB,<br>P <sub>OUT</sub> = -10 dBFS                  |     | 65  |     | dBc     |

| ACPR                  | ,                                                 |                                                                                  |     |     |     |         |

## **AC ELECTRICAL CHARACTERISTICS (continued)**

Typical values at  $T_A = 25^{\circ}$ C, full temperature range is  $T_{MIN} = -40^{\circ}$ C to  $T_{MAX} = 85^{\circ}$ C, DAC sampling rate = 65 MSPS, DVDD18 = 1.8 V, CLKVDD18 = 1.8 V, DACVDD18 = 1.8 V, FUSEVDD18 = 1.8 V, IOVDD = 3.3 V, DACVDD33 = 3.3 V, MODVDD33 = 3.3 V, analog output (unless otherwise noted)

|                     | PARAMETER                                       | TEST CONDITIONS                                                 | MIN T    | YP M    | ΑX  | UNIT   |

|---------------------|-------------------------------------------------|-----------------------------------------------------------------|----------|---------|-----|--------|

| ALT1                | Alternate-channel power ratio                   | 1 WCDMA TM1 signal, PAR = 10 dB,<br>P <sub>OUT</sub> = -10 dBFS |          | 66      |     | dBc    |

| RF Outp             | ut Parameters – f <sub>LO</sub> = 2.1 GHz, Anal | og Output                                                       |          |         |     |        |

| P <sub>OUT_FS</sub> | Fullscale RF output power                       |                                                                 | _        | 1.5     |     | dBm    |

| IP2                 | Output IP2                                      |                                                                 |          | 50      |     | dBm    |

| IP3                 | Output IP3                                      |                                                                 |          | 19      |     | dBm    |

|                     | Carrier feedthrough                             |                                                                 |          | 38      |     | dBc    |

|                     | Sideband suppression                            |                                                                 |          | 42      |     | dBc    |

|                     | Output noise floor                              | ≥ 30 MHz offset, f <sub>BB</sub> = 50 kHz, full scale           | 1        | 41      |     | dBc/Hz |

|                     | Output return loss                              |                                                                 | 8        | 3.5     |     | dB     |

| ACPR                | Adjacent-channel power ratio                    | 1 WCDMA TM1 signal, PAR = 10 dB,<br>P <sub>OUT</sub> = -10 dBFS |          | 65      |     | dBc    |

|                     |                                                 | 20 MHz LTE, PAR = 10 dB,<br>P <sub>OUT</sub> = - 10 dBFS        |          | 61      |     | dBc    |

| ALT1                | Alternate-channel power ratio                   | 1 WCDMA TM1 signal, PAR = 10 dB,<br>P <sub>OUT</sub> = -10 dBFS |          | 65      |     | dBc    |

| RF Outp             | ut Parameters – f <sub>LO</sub> = 2.7 GHz, Anal | og Output                                                       |          |         |     |        |

| P <sub>OUT_FS</sub> | Full-scale RF output power                      |                                                                 | -<       | 3.6     |     | dBm    |

| IP2                 | Output IP2                                      |                                                                 |          | 48      |     | dBm    |

| IP3                 | Output IP3                                      |                                                                 |          | 17      |     | dBm    |

|                     | Carrier feedthrough                             |                                                                 |          | 36      |     | dBc    |

|                     | Sideband suppression                            |                                                                 |          | 35      |     | dBc    |

|                     | Output noise floor                              | ≥ 30 MHz offset, f <sub>BB</sub> = 50 kHz, full scale           | 1        | 39      |     | dBc/Hz |

|                     | Output return loss                              |                                                                 | 3        | 3.5     |     | dB     |

| RF Outp             | ut Parameters – f <sub>LO</sub> = 622 MHz, LVD  | S Output, ÷4                                                    | ·        |         |     |        |

| $V_{OD}$            | Differential output voltage                     | Assumes a 100-Ω differential load                               | 247 3    | 50 4    | 54  | mV     |

| V <sub>OC</sub>     | Common-mode output voltage                      |                                                                 | 1.125 1. | .25 1.3 | 375 | V      |

|                     | Output noise floor                              | ≥ 13 MHz offset, f <sub>BB</sub> = 1 MHz                        |          |         |     |        |

|                     | Carrier feedthrough                             | Unadjusted, f <sub>BB</sub> = 50 kHz, full scale                |          | 40      |     | dBc    |

|                     | Sideband suppression                            | Unadjusted, f <sub>BB</sub> = 50 kHz, full cale                 |          | 40      |     | dBc    |

#### **TYPICAL PERFORMANCE PLOTS**

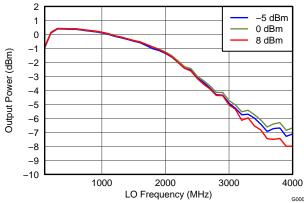

Figure 1. Output Power vs LO Frequency and LO Power

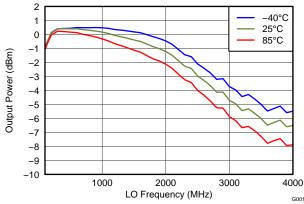

Figure 2. Output Power vs LO Frequency and Temperature

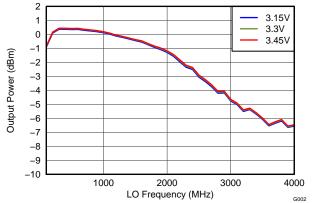

Figure 3. Output Power vs LO Frequency and Supply Voltage

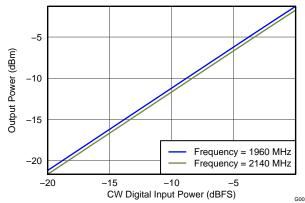

Figure 4. Output Power vs Input Power and LO Frequency

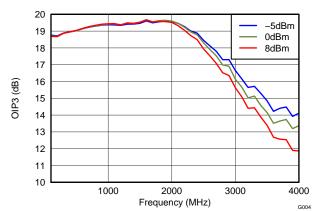

Figure 5. OIP3 vs LO Frequency and LO Power

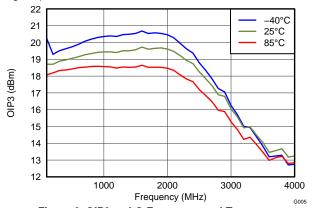

Figure 6. OIP3 vs LO Frequency and Temperature

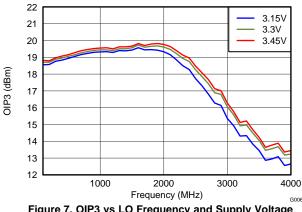

Figure 7. OIP3 vs LO Frequency and Supply Voltage

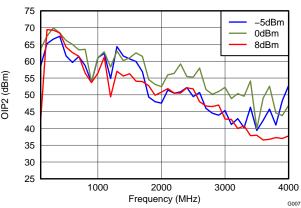

Figure 8. OIP2 vs LO Frequency and LO Power

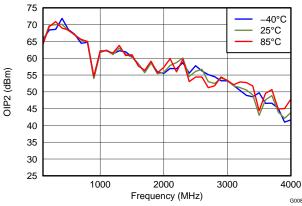

Figure 9. OIP2 vs LO Frequency and Temperature

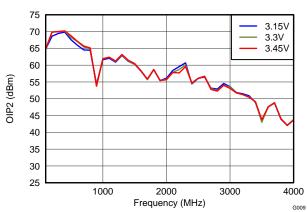

Figure 10. OIP2 vs LO Frequency and Supply Voltage

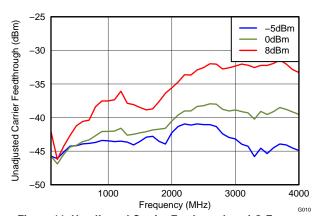

Figure 11. Unadjusted Carrier Feethrough vs LO Frequency and LO Power

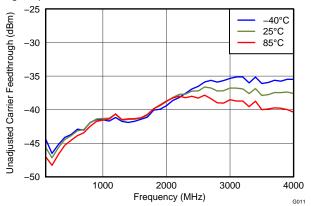

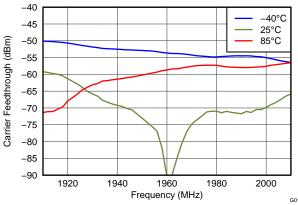

Figure 12. Unadjusted Carrier Feethrough vs LO Frequency and Temperature

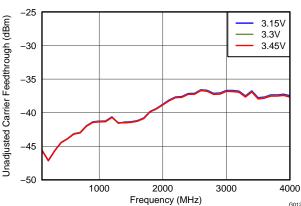

Figure 13. Unadjusted Carrier Feethrough vs LO Frequency and Supply Voltage

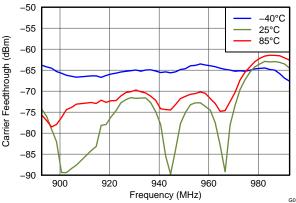

Figure 14. Adjusted Carrier Feethrough vs LO Frequency and Temperature at 940 MHz

Figure 15. Adjusted Carrier Feethrough vs LO Frequency and Temperature at 1960 MHz

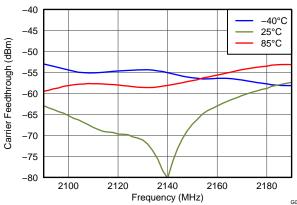

Figure 16. Adjusted Carrier Feethrough vs LO Frequency and Temperature at 2140 MHz

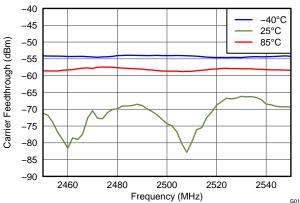

Figure 17. Adjusted Carrier Feethrough vs LO Frequency and Temperature at 2500 MHz

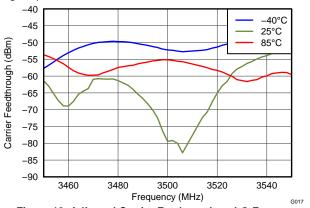

Figure 18. Adjusted Carrier Feethrough vs LO Frequency and Temperature at 3500 MHz

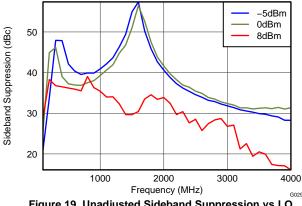

Figure 19. Unadjusted Sideband Suppression vs LO Frequency and LO Power

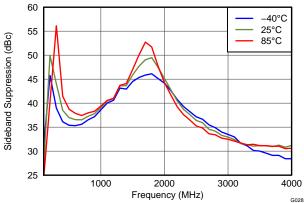

Figure 20. Unadjusted Sideband Suppression vs LO Frequency and Temperature

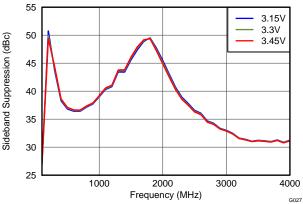

Figure 21. Unadjusted Sideband Suppression vs LO Frequency and Supply Voltage

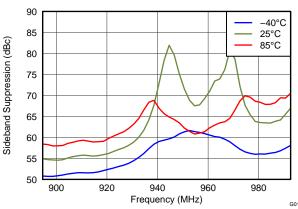

Figure 22. Adjusted Sideband Suppression vs LO Frequency and Temperature at 940 MHz

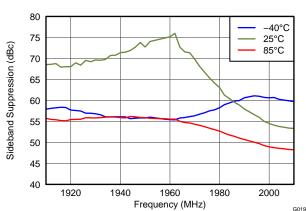

Figure 23. Adjusted Sideband Suppression vs LO Frequency and Temperature at 1960 MHz

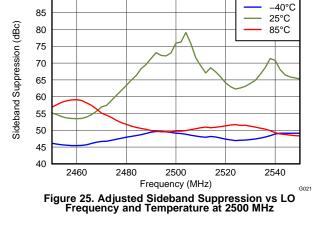

90

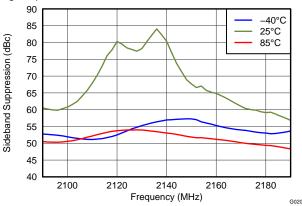

Figure 24. Adjusted Sideband Suppression vs LO Frequency and Temperature at 2140 MHz

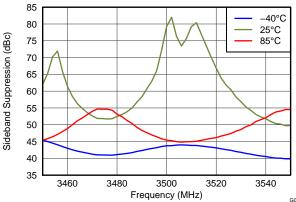

Figure 26. Adjusted Sideband Suppression vs LO Frequency and Temperature at 3500 MHz

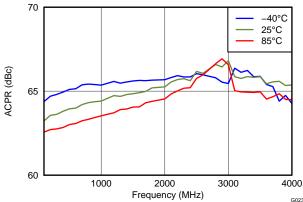

Figure 27. WCDMA Adjacent-Channel Power Ratio (ACPR) vs Temperature

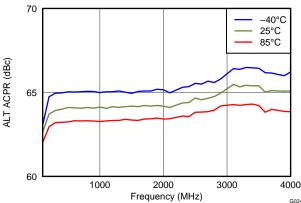

Figure 28. WCDMA Adjacent-Channel Power Ratio (Alt-ACPR) vs Temperature

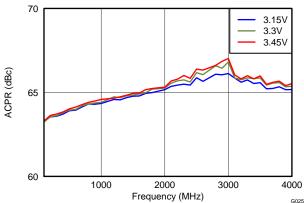

Figure 29. WCDMA Adjacent-Channel Power Ratio (ACPR) vs Supply Voltage

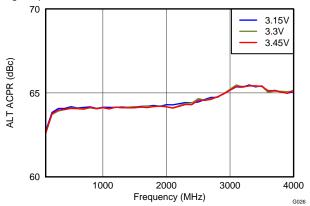

Figure 30. WCDMA Adjacent-Channel Power Ratio (Alt-ACPR) vs Supply Voltage

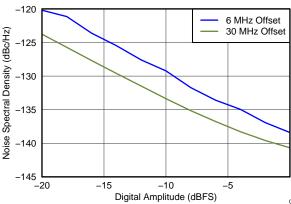

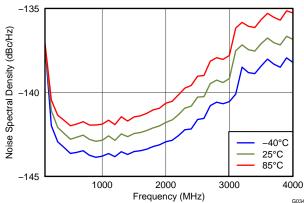

Figure 31. Noise Spectral Density (NSD) vs Input Power and LO Frequency

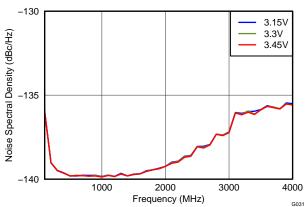

Figure 32. Noise Spectral Density (NSD) at 6-MHz Offset vs LO Frequency and Supply Voltage

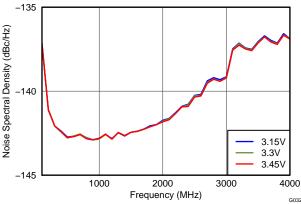

Figure 33. Noise Spectral Density (NSD) at 30-MHz Offset vs LO Frequency and Supply Voltage

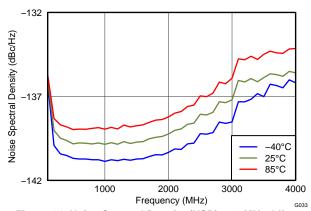

Figure 34. Noise Spectral Density (NSD) at 6-MHz Offset vs LO Frequency and Temperature

Figure 35. Noise Spectral Density (NSD) at 30-MHz Offset vs. LO Frequency and Temperature

Figure 36. Baseband Filter Response

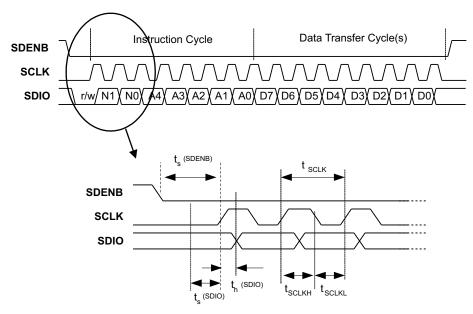

#### SERIAL INTERFACE

The serial port of the AFE7070 is a flexible serial interface which communicates with industry-standard microprocessors and microcontrollers. The interface provides read/write access to all registers used to define the operating modes of the AFE7070. The serial port is compatible with most synchronous transfer formats and can be configured as a 3- or 4-pin interface by **sif\_4pin** in **CONFIG3 (bit6)**. In both configurations, **SCLK** is the serial interface input clock and **SDENB** is serial interface enable. For the 3-pin configuration, **SDIO** is a bidirectional pin for both data in and data out. For the 4-pin configuration, **SDIO** is data-in only and **ALARM\_SDO** is data-out only. Data is input into the device with the rising edge of **SCLK**. Data is output from the device on the falling edge of **SCLK**.

Each read/write operation is framed by signal **SDENB** (serial data-enable bar) asserted low for 2 to 5 bytes, depending on the data length to be transferred (1–4 bytes). The first frame byte is the instruction cycle, which identifies the following data transfer cycle as read or write, how many bytes to transfer, and the address to which to transfer the data. Table 1 indicates the function of each bit in the instruction cycle and is followed by a detailed description of each bit. Frame bytes 2 through 5 comprise the data transfer cycle.

Table 1. Instruction Byte of the Serial Interface

|             | MSB |    |    |    |    |    |    | LSB |

|-------------|-----|----|----|----|----|----|----|-----|

| Bit         | 7   | 6  | 5  | 4  | 3  | 2  | 1  | 0   |

| Description | R/W | N1 | N0 | A4 | А3 | A2 | A1 | A0  |

R/W Identifies the following data transfer cycle as a read or write operation. A high indicates a read operation from the AFE7070, and a low indicates a write operation to the AFE7070.

[N1 : N0] Identifies the number of data bytes to be transferred, as listed in Table 2. Data is transferred MSB first.

Table 2. Number of Transferred Bytes Within One Communication Frame

| N1 | N0 | DESCRIPTION      |

|----|----|------------------|

| 0  | 0  | Transfer 1 byte  |

| 0  | 1  | Transfer 2 bytes |

| 1  | 0  | Transfer 3 bytes |

| 1  | 1  | Transfer 4 bytes |

[A4 : A0] Identifies the address of the register to be accessed during the read or write operation. For multibyte transfers, this address is the starting address. Note that the address is written to the AFE7070 MSB first and counts down for each byte.

Figure 37 shows the serial interface timing diagram for an AFE7070 write operation. **SCLK** is the serial interface clock input to AFE7070. Serial data enable **SDENB** is an active-low input to the AFE7070. **SDIO** is serial data in. Input data to the AFE7070 is clocked on the rising edges of **SCLK**.

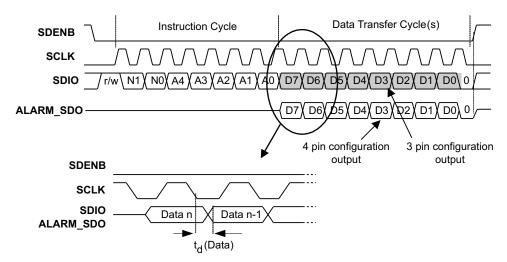

Figure 37. Serial Interface Write Timing Diagram

Figure 38 shows the serial interface timing diagram for an AFE7070 read operation. **SCLK** is the serial interface clock input to AFE7070. Serial data enable **SDENB** is an active-low input to the AFE7070. **SDIO** is serial data-in during the instruction cycle. In the 3-pin configuration, **SDIO** is data-out from the AFE7070 during the data transfer cycle(s), while **ALARM\_SDO** is in a high-impedance state. In the 4-pin configuration, **ALARM\_SDO** is data-out from the AFE7070 during the data transfer cycle(s). At the end of the data transfer, **ALARM\_SDO** outputs low on the final falling edge of **SCLK** until the rising edge of **SDENB**, when it enters the high-impedance state.

Figure 38. Serial Interface Read Timing Diagram

#### **REGISTER DESCRIPTIONS**

In the SIF interface there are three types of registers, *NORMAL*, *READ\_ONLY*, and *WRITE\_TO\_CLEAR*. The *NORMAL* register type allows data to be written and read from the register. All 8 bits of the data are registered at the same time, but there is no synchronizing with an internal clock. All register writes are asynchronous with respect to internal clocks. *READ\_ONLY* registers only allow reading of the registers—writing to them has no effect. *WRITE\_TO\_CLEAR* registers are just like *NORMAL* registers in that they can be written and read; however, when the internal signals set a bit high in these registers, that bit stays high until it is written to 0. This way, interrupts are captured and constant until dealt with and cleared.

#### **Register Map**

| Name     | Address | Default | (MSB)<br>bit 7       | bit 6             | bit 5            | bit 4               | bit 3               | bit 2               | bit 1                           | (LSB)<br>bit 0        |  |  |

|----------|---------|---------|----------------------|-------------------|------------------|---------------------|---------------------|---------------------|---------------------------------|-----------------------|--|--|

| CONFIG0  | 0x00    | 0x10    | div2_dacclk_ena      | div2_sync_ena     | clkio_sel        | clkio_out_ena_n     | data_clk_sel        | data_type           | fifo_ena                        | sync_lorQ             |  |  |

| CONFIG1  | 0x01    | 0x10    | twos                 | iqswap            | trim_cl          | k_rc_fltr           | daca_<br>complement | dacb_<br>complement | lyds clk div                    |                       |  |  |

| CONFIG2  | 0x02    | 0xXX    | Unused               | Unused            | Unused           | Unused              | Unused              | Unused              | Alarm_fifo_<br>2away            | Alarm_fifo_1away      |  |  |

| CONFIG3  | 0x03    | 0x10    | alarm_or_sdo_<br>ena | sif_4pin          | SLEEP            | TXENABLE            | SYNC                | sync_sleep          | sync_sleep_txenable_sel msb_out |                       |  |  |

| CONFIG4  | 0x04    | 0x0F    | fuse_pd              | mixer_gain        | pd_clkrcvr       | pd_clkrcvr_<br>mask |                     | coars               | se_dac(3:0)                     |                       |  |  |

| CONFIG5  | 0x05    | 0x00    | offset_ena           | qmc_corr_ena      | mixer_ena        |                     |                     | filter_tune(4:0     | )                               |                       |  |  |

| CONFIG6  | 0x06    | 0x00    | pd_lvds              | pd_rf_out         | pd_dac           | pd_analogout        | pd_lvds_mask        | pd_tf_out_<br>mask  | pd_dac_mask                     | pd_analogout_<br>mask |  |  |

| CONFIG7  | 0x07    | 0x13    | mask_2away           | mask_1away        | fifo_sync_mask   | fifo_offset         | alarm2away_<br>ena  |                     |                                 | alarm_1away_<br>ena   |  |  |

| CONFIG8  | 0x08    | 0x00    |                      |                   |                  | qmc_offseta         | (7:0)               |                     |                                 |                       |  |  |

| CONFIG9  | 0x09    | 0x7A    |                      |                   |                  | qmc_offsetb         | (7:0)               |                     |                                 |                       |  |  |

| CONFIG10 | 0x0A    | 0xB6    |                      | С                 | mc_offseta(12:8) |                     |                     | Unused              | Unused                          | Unused                |  |  |

| CONFIG11 | 0x0B    | 0xEA    |                      | qmc_offsetb(12:8) |                  |                     |                     |                     | Unused                          | Unused                |  |  |

| CONFIG12 | 0x0C    | 0x45    |                      |                   |                  | qmc_gaina           | (7:0)               |                     |                                 |                       |  |  |

| CONFIG13 | 0x0D    | 0x1A    |                      |                   |                  | qmc_gainb           | (7:0)               |                     |                                 |                       |  |  |

| CONFIG14 | 0x0E    | 0x16    |                      |                   |                  | qmc_phase           | (7:0)               |                     |                                 |                       |  |  |

| CONFIG15 | 0x0F    | 0xAA    | qmc_pl               | nase(9:8)         |                  | qmc_gaini(10:8)     |                     |                     | qmc_gainq(10                    | :8)                   |  |  |

| CONFIG16 | 0x10    | 0xC6    |                      |                   |                  | freq (7:0           | ))                  |                     |                                 |                       |  |  |

| CONFIG17 | 0x11    | 0x24    |                      |                   |                  | freq (15:           | 8)                  |                     |                                 |                       |  |  |

| CONFIG18 | 0x12    | 0x02    |                      |                   |                  | freq (23:1          | 6)                  |                     |                                 |                       |  |  |

| CONFIG19 | 0x13    | 0x00    |                      |                   |                  | freq (31:2          | 24)                 |                     |                                 |                       |  |  |

| CONFIG20 | 0x14    | 0x00    |                      |                   |                  | phase (7:           | (0)                 |                     |                                 |                       |  |  |

| CONFIG21 | 0x15    | 0x00    |                      |                   |                  | phase (15           | i:8)                |                     |                                 |                       |  |  |

| CONFIG22 | 0x16    | 0x00    |                      |                   |                  | Reserve             | d                   |                     |                                 |                       |  |  |

| CONFIG23 | 0x17    | 0xXX    |                      |                   |                  | Reserve             | d                   |                     |                                 |                       |  |  |

| CONFIG24 | 0x18    | 0xXX    |                      |                   |                  | Reserve             | d                   |                     |                                 |                       |  |  |

| CONFIG25 | 0x19    | 0xXX    |                      |                   |                  | Reserve             | d                   |                     |                                 |                       |  |  |

| CONFIG26 | 0x1A    | 0xXX    |                      |                   |                  | Reserve             | d                   |                     |                                 |                       |  |  |

| CONFIG27 | 0x1B    | 0xXX    |                      |                   |                  | Reserve             | d                   |                     |                                 |                       |  |  |

| CONFIG28 | 0x1C    | 0xXX    |                      |                   |                  | Reserve             | d                   |                     |                                 |                       |  |  |

| CONFIG29 | 0x1D    | 0xXX    |                      |                   |                  | Reserve             | d                   |                     |                                 |                       |  |  |

| CONFIG30 | 0x1E    | 0xXX    |                      |                   |                  | Reserve             | d                   |                     |                                 |                       |  |  |

| CONFIG31 | 0x1F    | 0x82    | titest_voh           | titest_vol        |                  |                     | Versio              | n(5:0)              |                                 |                       |  |  |

#### Register name: CONFIG0; Address: 0x00

BIT 7

| div2_dacclk_ena | div2_sync_ena | clkio_sel | clkio_out_ena_n | data_clk_sel | data_type | fifo_ena | sync_lorQ |

|-----------------|---------------|-----------|-----------------|--------------|-----------|----------|-----------|

| 0               | 0             | 0         | 1               | 0            | 0         | 0        | 0         |

#### **Table 3. Clock Mode Memory Programming**

| Mode                               | div2_dacclk_ena | div2_sync_ena | clkio_sel | clkio_out_ena_n | data_clk_sel |

|------------------------------------|-----------------|---------------|-----------|-----------------|--------------|

| Dual input clock(00)               | 1               | 0             | 1         | 1               | 0            |

| Dual output clock (01)             | 1               | 1             | 0         | 0               | 0            |

| Single differential DDR clock (10) | 0               | 0             | 0         | 1               | 1            |

| Single differential SDR clock (11) | 0               | 0             | 1         | 1               | 1            |

div2\_dacclk\_ena: When set to 1, this enables the divide-by-2 in the DAC clock path. This must be set to 1

when in dual-input clock mode or dual-output clock mode.

div2\_sync\_ena: When set to 1, the divide-by-2 is synchronized with the iq\_flag. It is only useful in the dual-

clock modes when the divide-by-2 is enabled. Care must be take to ensure the input data

and DAC clocks are correctly aligned.

clkio\_sel: This bit is used to determine which clock is used to latch the input data. This should be set

according to Table 3.

clkio out ena n: When set to 0, the clock CLK IO is an output. Depending on the mode, is should be set

according to Table 3.

data\_clk\_sel: This bit is used to determine which clock is used to latch the input data. This should be set

according to Table 3.

data type: When asserted, the phase data is presented at the data interface. The phase data is then

updated with each clock. The phase register then holds the value of the I and Q data to be

used with the mix operation.

fifo\_ena: When asserted, the FIFO is enabled. Used in dual-input clock mode only. In all other

modes, the FIFO is bypassed.

sync\_lorQ: When set to 0, sync is latched on the I phase of the input clock. When set to 1, sync is

detected on the Q phase of the clock and is sent to the rest of the chip when the next I

data is presented.

Register name: CONFIG1; Address: 0x01

BIT 7 BIT 0

| twos | iqswap | trim_clk_rc_fltr |  | daca_complement | dacb_complement | lvds_clk_div |   |

|------|--------|------------------|--|-----------------|-----------------|--------------|---|

| 0    | 0      | 0 1              |  | 0               | 0               | X            | X |

twos: When asserted, the input to the chip is 2s complement, otherwise offset binary.

igswap: When asserted, the DACA data is driven onto DACB and reverse.

trim\_clk\_rc\_fltr: 2 bits to trim the RC filter for LVDS out

daca\_complement: When asserted, the output to DACA is complemented. This allows the user of the chip

effectively to change the + and – designations of the PADs.

dacb\_complement: When asserted, the output to DACB is complemented. This allows the user of the chip

effectively to change the + and - designations of the PADs.

lvds\_clk\_div:

| lvds_clk_div | LVDS Clock Division |

|--------------|---------------------|

| 00           | 2                   |

| 01           | 4                   |

| 10           | 1                   |

| 11           | 1                   |

Register name: CONFIG2; Address: 0x02

Write-to-clear register bits remain asserted once set. Each bit must be written to 0 before another 1 can be captured.

BIT 7 BIT 0 unused unused unused unused unused unused Alarm\_fifo\_2away Alarm\_fifo\_1away 0 0 0 0 0 0

Alarm\_fifo\_2away: When asserted, the FIFO pointers are 2 away from collision. (WRITE\_TO\_CLEAR)

Alarm\_fifo\_1away: When asserted, the FIFO pointers are 1 away from collision. (WRITE\_TO\_CLEAR)

## Register name: CONFIG3; Address: 0x03 (INTERFACE SELECTION)

| BIT 7            |          |       |          |      |             |              | BIT 0   |

|------------------|----------|-------|----------|------|-------------|--------------|---------|

| alarm_or_sdo_ena | sif_4pin | SLEEP | TXenable | SYNC | sync_sleep_ | txenable_sel | msb_out |

| 0                | 0        | 0     | 1        | 0    | 0           | 0            | 0       |

alarm\_or\_sdo\_e When asserted, the output of the ALARM\_SDO pin is enabled.

na:

sif 4pin: When asserted, the part is in 4-pin SPI mode. The data-out is output on the ALARM SDO

pin. If this bit is not enabled, the alarm signal is output on the ALARM SDO pin.

sleep: When asserted, all blocks programmed to go to sleep in CONFIG4 and CONFIG6 registers

labeled pd\_\*\*\*\_mask are powered down.

TXenable: When 0, the data path is zeroed. When 1, the device transmits.

sync: When written with a 1, the part is synced. To be resynced using the sif register, it must be

reset to 0 by writing a 0 then write a 1 to the sif to sync.

sync\_sleep\_ This is used to define the function of the SYNC\_SLEEP pin. This pin can be used for multiple txenable\_sel: functions, but only one at a time. When it is set to control any one of the functions, all other

functions are controlled by writing their respective sif register bits.

| sync_sleep_txenable<br>_sel | Pin controls              |

|-----------------------------|---------------------------|

| 00                          | All controlled by sif bit |

| 01                          | TXENABLE                  |

| 10                          | SYNC                      |

| 11                          | SLEEP                     |

msb\_out: When set, and alarm\_sdo\_out\_ena is also set, the ALARM\_SDO pin outputs the value of

daca bit 13.

#### Register name: CONFIG4; Address: 0x04

BIT 7 BIT 0

| fuse_pd | mixer_gain | pd_clkrcvr | pd_clkrcvr_mask | coarse_dac(3:0) |   |   |   |

|---------|------------|------------|-----------------|-----------------|---|---|---|

| 0       | 0          | 0          | 0               | 1               | 1 | 1 | 1 |

fuse\_pd: When set to 1, the fuses are powered down. This saves approximately 50 µA at 1.8 V for

every intact fuse. The default value is 0.

mixer\_gain: When asserted, the complex mixer output is multiplied by 2. Only applied when the mixer is

enabled ( $mixer_ena = 1$ ).

pd\_clkrcvr: When asserted, the clock receiver is powered down.

pd\_clkrcvr\_mask: When asserted, allows the clock receiver to be powered down with the SYNC\_SLEEP pin or

sleep register bit.

coarse\_dac: DAC full-scale current control

#### Register name: CONFIG5; Address: 0x05

BIT 7 BIT 0

| offset_ena | qmc_corr_ena | mixer_ena | filter_tune(4:0) |   |   |   |   |

|------------|--------------|-----------|------------------|---|---|---|---|

| 0          | 0            | 0         | 0                | 0 | 0 | 0 | 0 |

When asserted, the gmc offset blk is enabled. offset ena: When asserted, the gmc correction is enabled. qmc corr ena:

When asserted, the complex mix is performed. Otherwise, the mixer is bypassed. mixer ena:

filter tune(4:0): Bits used to change the bandwidth of the analog filters

#### Register name: CONFIG6; Address: 0x06

BIT 0 BIT 7

| pd_lvds | pd_rf_out | pd_dac | pd_analogout | pd_lvds_mask | pd_tf_out_mask | pd_dac_mask | pd_analogout_<br>mask |

|---------|-----------|--------|--------------|--------------|----------------|-------------|-----------------------|

| 0       | 0         | 0      | 1            | 1            | 1              | 0           | 0                     |

pd lvds: When asserted, the LVDS output stage is powered down.

pd\_rf\_out: When asserted, the RF output stage is powered down.

pd dac: When asserted, DACs are powered down.

When asserted, the entire analog circuit after the DACs (filters, modulator, LO input, RF pd analog out:

output stage, LVDS output) is powered down.

The following are used to determine what blocks are powered down when the SYNC\_SLEEP pin is used or the sleep register bit is set.

pd\_lvds\_mask: When asserted, allows the LVDS to be powered down pd\_rf\_out\_mask: When asserted, allows the RF output to be powered down When asserted, allows the DACs to be powered down pd\_dac\_mask:

#### Register name: CONFIG7; Address: 0x07

BIT 7

| mask_2away | mask_1away | fifo_sync_mask | f | ifo_offse | t | alarm_2away_ena | alarm_1away_ena |

|------------|------------|----------------|---|-----------|---|-----------------|-----------------|

| 0          | 0          | 0              | 1 | 0         | 0 | 1               | 1               |

mask\_2away: When set to 1, the ALARM\_SDO pin is not asserted when the FIFO pointers are 2 away

from collision. The alarm still shows up in the CONFIG7 bits.

mask 1away: When set to 1, the ALARM SDO pin is not asserted when the FIFO pointers are 1 away

from collision. The alarm still shows up in the CONFIG7 bits.

fifo\_sync\_mask: When set to 1, the sync to the FIFO is masked off. Sync does not then reset the pointers.

If the value is 0, when the sync is toggled the FIFO pointers are reset to the offset values.

fifo\_offset: Used to set the offset pointers in the FIFO. Programs the starting location of the output

side of the FIFO, allows the output pointer to be shifted from -4 to +3 (2s complement) positions with respect to its default position when synced. The default position for the

output side pointer is 2. The input side pointer defaults to 0.

alarm\_2away\_ena: When asserted, alarms from the FIFO that represent the pointers being 2 away from

collision are enabled.

alarm\_1away\_ena: When asserted, alarms from the FIFO that represent the pointers being 1 away from

collision are enabled.

#### Register name: CONFIG8; Address: 0x08

| BIT 7 |   |   |          |            |   |   | BIT 0 |

|-------|---|---|----------|------------|---|---|-------|

|       |   |   | qmc_offs | seta (7:0) |   |   |       |

| 0     | 0 | 0 | 0        | 0          | 0 | 0 | 0     |

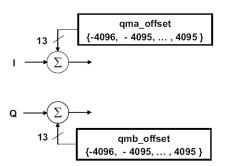

qmc\_offseta(7:0): Bits 7:0 of qmc\_offseta. The complete registers qmc\_offseta[12:0] and qmc\_offsetb[12:0]

are updated when CONFIG8 is written, so CONFIG9, CONFIG10, and CONFIG11 should

be written before CONFIG8.

## Register name: CONFIG9; Address: 0x09

| BIT 7 |                   |   |   |   |   |   | BIT 0 |  |  |

|-------|-------------------|---|---|---|---|---|-------|--|--|

|       | qmc_offsetb (7:0) |   |   |   |   |   |       |  |  |

| 0     | 1                 | 1 | 1 | 1 | 0 | 1 | 0     |  |  |

qmc\_offsetb(7:0): Bits 7:0 of qmc\_offsetb. The complete registers qmc\_offseta[12:0] and qmc\_offsetb[12:0]

are updated when CONFIG8 is written, so CONFIG9, CONFIG10, and CONFIG11 should

be written before CONFIG8.

#### Register name: CONFIG10; Address: 0x0A

| BIT 7 |   |                   |   |   |        |        | BIT 0  |

|-------|---|-------------------|---|---|--------|--------|--------|

|       |   | qmc_offseta(12:8) | ) |   | Unused | Unused | Unused |

| 1     | 0 | 1                 | 1 | 0 | 1      | 1      | 0      |

qmc\_offsetb(12:8): Bits 12:8 of qmc\_offseta. The complete registers qmc\_offseta[12:0] and qmc\_offsetb[12:0]

are updated when CONFIG8 is written, so CONFIG9, CONFIG10, and CONFIG11 should

be written before CONFIG8.

#### Register name: CONFIG11; Address: 0x0B

BIT 7

qmc\_offsetb(12:8)

Unused

Unused

Unused

Unused

1

1

1

0

1

0

1

0

qmc\_offsetb(12:8): Bits 12:8 of qmc\_offsetb. The complete registers qmc\_offseta[12:0] and

qmc\_offsetb[12:0] are updated when CONFIG8 is written, so CONFIG9, CONFIG10, and

CONFIG11 should be written before CONFIG8.

#### Register name: CONFIG12; Address: 0x0C

| BIT 7 |   |   |        |   |   |   | BIT 0 |

|-------|---|---|--------|---|---|---|-------|

|       |   |   | qmc_ga |   |   |   |       |

| 0     | 1 | 0 | 0      | 0 | 1 | 0 | 1     |

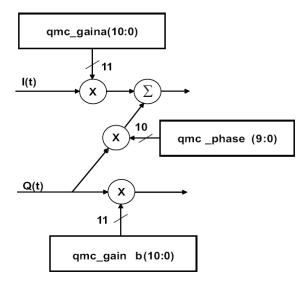

qmc\_gaina(7:0):

Bits 7:0 of qmc\_gaina. The complete registers qmc\_gaina[10:0], qmc\_gainb[10:0] and qmc\_phase[9:0] are updated when CONFIG12 is written, so CONFIG13, CONFIG14, and CONFIG15 should be written before CONFIG12.

#### Register name: CONFIG13; Address: 0x0D

| BIT 7 |   |   |        |           |   |   | BIT 0 |

|-------|---|---|--------|-----------|---|---|-------|

|       |   |   | qmc_ga | inb (7:0) |   |   |       |

| 0     | 0 | 0 | 1      | 1         | 0 | 0 | 0     |

qmc gainb(7:0):

Bits 7:0 of qmc\_gainb. The complete registers qmc\_gaina[10:0], qmc\_gainb[10:0] and qmc\_phase[9:0] are updated when CONFIG12 is written, so CONFIG13, CONFIG14, and CONFIG15 should be written before CONFIG12.

#### Register name: CONFIG14; Address: 0x0E

| BIT 7 |                 |   |   |   |   |   | BIT 0 |  |  |

|-------|-----------------|---|---|---|---|---|-------|--|--|

|       | qmc_phase (7:0) |   |   |   |   |   |       |  |  |

| 0     | 0               | 0 | 1 | 0 | 1 | 1 | 0     |  |  |

qmc\_phase(7:0)

Bits 7:0 of qmc\_phase. The complete registers qmc\_gaina[10:0], qmc\_gainb[10:0] and qmc\_phase[9:0] are updated when CONFIG12 is written, so CONFIG13, CONFIG14, and CONFIG15 should be written before CONFIG12.

#### Register name: CONFIG15; Address: 0x0F

| BIT 7 |            |   |                 |   |   |                 | BIT 0 |

|-------|------------|---|-----------------|---|---|-----------------|-------|

| qmc_r | ohase(9:8) |   | qmc_gaina(10:8) |   |   | qmc_gainb(10:8) |       |

| 1     | 0          | 1 | 0               | 1 | 0 | 1               | 0     |

qmc\_phase(9:8): Bits 9:8 of qmc\_phase value qmc\_gaina(10:8): Bits 9:8 of qmc\_gaina value qmc\_gainb(10:8): Bits 9:8 of qmc\_gainb value

The complete registers qmc\_gaina[10:0], qmc\_gainb[10:0] and qmc\_phase[9:0] are updated when CONFIG12 is written, so CONFIG13, CONFIG14, and CONFIG15 should be written before CONFIG12.

www.ti.com.cn

Register name: CONFIG16; Address: 0x10

| BIT 7 |   |   |      |       |   |   | BIT 0 |

|-------|---|---|------|-------|---|---|-------|

|       |   |   | freq | (7:0) |   |   |       |

| 1     | 1 | 0 | 0    | 0     | 1 | 1 | 0     |

freq(7:0): Bits 7:0 of frequency value

Register name: CONFIG17; Address: 0x11

| BIT 7 |             |   |   |   |   |   | BIT 0 |  |  |

|-------|-------------|---|---|---|---|---|-------|--|--|

|       | freq (15:8) |   |   |   |   |   |       |  |  |

| 0     | 0           | 1 | 0 | 0 | 1 | 0 | 0     |  |  |

freq (15:8): Bits 15:8 of frequency value

Register name: CONFIG18; Address: 0x12