**AFE4404**

ZHCSDV4C -JUNE 2015-REVISED MAY 2016

# AFE4404 用于可穿戴光学心率监测和生物传感的超小型集成 AFE

# 1 特性

- 发送器:

- 支持共阳极 LED 配置

- 动态范围: 100dB

- 6 位可编程 LED 电流最高达 50mA (可扩展至 100mA)

- 可编程 LED 接通时间

- 同时支持3个LED,适用于优化型血氧饱和度 (SpO2)测量、心率监测 (HRM)或多波长 HRM

- 接收器:

- 以 24 位二进制补码格式表示光电二极管的电流 输入

- TIA 输入端的独立直流偏移减法 DAC,用于每个 LED 和环境相位

- ADC 输出端的数字环境减法

- 可编程互阻抗增益:10kΩ 至 2MΩ

- 动态范围: 100dB

- 动态节能模式,可使电流降至 200µA 以下

- 脉冲频率: 10SPS 至 1000SPS

- 灵活的脉冲排序和定时控制

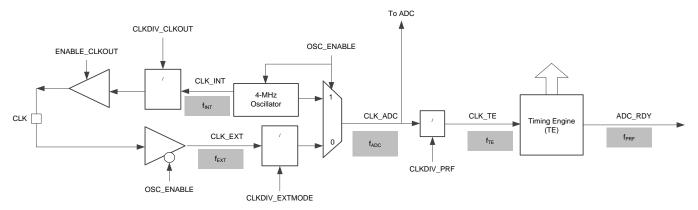

- 灵活的时钟选项:

- 外部时钟:4MHz 至 60MHz 输入时钟

- 内部时钟: 4MHz 振荡器

- I<sup>2</sup>C 接口

- 工作温度范围: -20°C 至 70°C

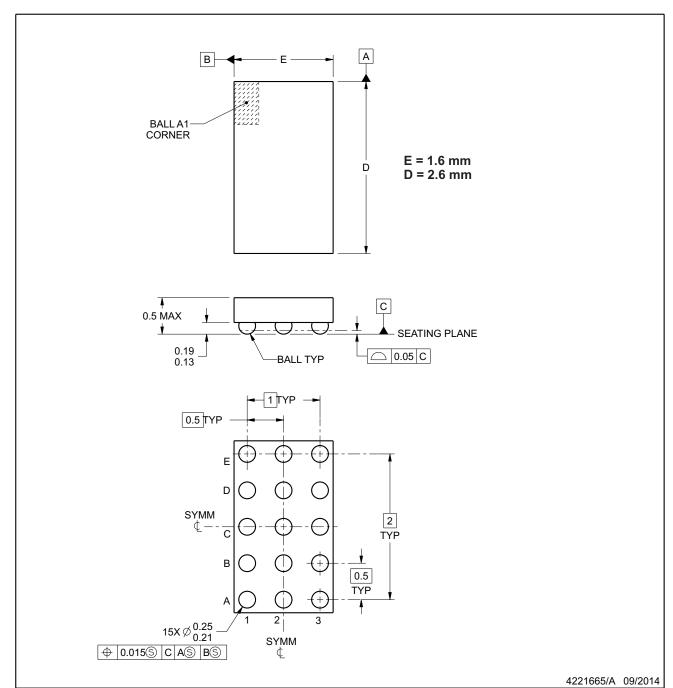

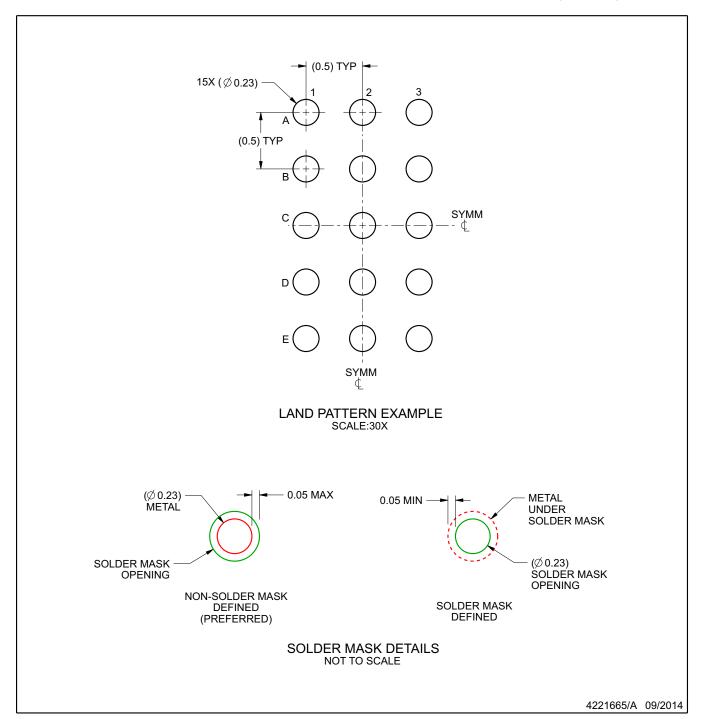

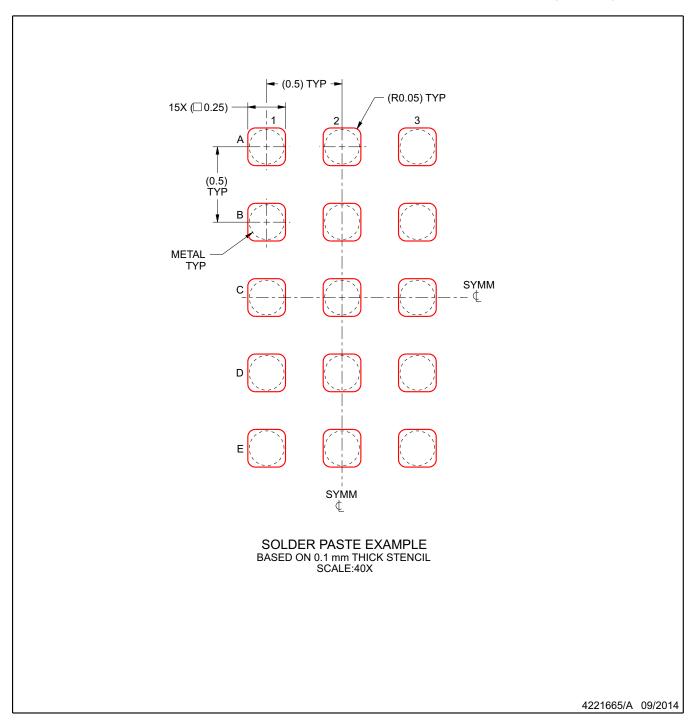

- 2.6mm x 1.6mm DSBGA 封装, 0.5mm 间距

- 电源: Rx: 2V 至 3.6V; Tx: 3V 至 5.25V; IO: 1.8V 至 3.6V

# 2 应用

- 光学心率监测 (HRM)

- 心率变异分析 (HRV)

- 血氧饱和仪(SpO2 测量)

- 最大摄氧量

- 卡路里消耗

# 3 说明

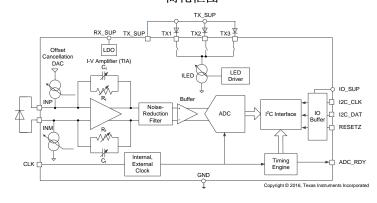

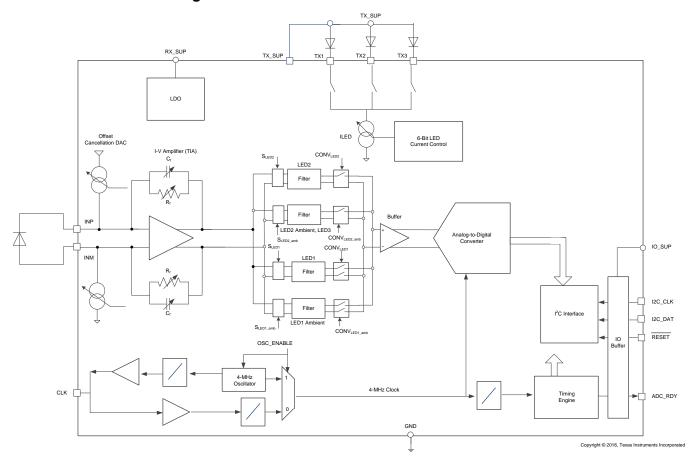

AFE4404 是一款面向光生物传感 应用的模拟前端 (AFE),例如心率监测 (HRM) 和血氧饱和度 (SpO2) 测量。该器件支持三个开关发光二极管 (LED) 和一个光电二极管。光电二极管的电流通过互阻抗放大器 (TIA) 转换为电压,并使用模数转换器 (ADC) 进行数字化。ADC 代码可使用 I<sup>2</sup>C 接口读出。AFE 还配有带 6 位电流控制的全集成 LED 驱动器。该器件具有宽动态范围的发送和接收电路,有助于感测超小信号电平。

#### 器件信息(1)

| 器件型号    | 封装         | 封装尺寸 (标称值)                     |

|---------|------------|--------------------------------|

| AFE4404 | DSBGA (15) | 2.60mm × 1.60mm <sup>(2)</sup> |

- (1) 如需了解所有可用封装,请见数据表末尾的可订购产品附录。

- (2) 请参见图 99 中的尺寸 D×E。

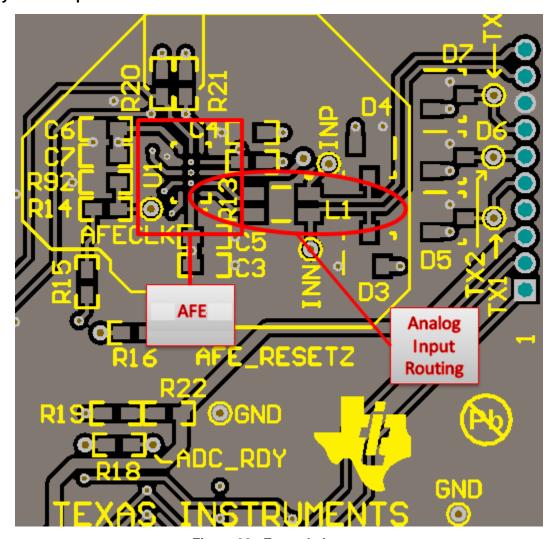

#### 简化框图

| 1<br>2<br>3<br>4 | 特性                                                                                                                  | 8.4 Device 8.5 Regis | ure Descriptione Functional Modes ster Map on and Implementation |        |

|------------------|---------------------------------------------------------------------------------------------------------------------|----------------------|------------------------------------------------------------------|--------|

| 5                | Device Comparison Table 3                                                                                           |                      | cation Information                                               |        |

| 6                | Pin Configuration and Functions                                                                                     | 9.2 Typic            | al Application                                                   | 6      |

| 7                | Specifications 5 7.1 Absolute Maximum Ratings 5                                                                     | 11 Layout            | upply Recommendations                                            | 70     |

|                  | 7.2 ESD Ratings                                                                                                     | 11.2 Layo            | out Guidelines<br>out Example<br>档支持                             | 70     |

|                  | 7.5 Electrical Characteristics 6 7.6 Timing Requirements 7 7.7 Typical Characteristics 8                            | 12.1 社区<br>12.2 商标   | 资源                                                               | 7<br>7 |

| 8                | Detailed Description         12           8.1 Overview         12           8.2 Functional Block Diagram         12 |                      | ssary<br>装和可订购信息                                                 |        |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| С | hanges from Revision B (October 2015) to Revision C                                                               | Page |

|---|-------------------------------------------------------------------------------------------------------------------|------|

| • | Changed specifications of t <sub>1</sub> and t <sub>4</sub> rows in Table 7 to improve rejection of ambient light | 23   |

| • | Changed Description column in Table 10                                                                            | 25   |

| • | Changed Table 11                                                                                                  | 26   |

| • | Changed Table 12                                                                                                  | 27   |

| • | Added Reducing Sensitivity to Ambient Light Modulation section                                                    | 69   |

| C | hanges from Revision A (August 2015) to Revision B                                          | Page |

|---|---------------------------------------------------------------------------------------------|------|

| • | Changed TX_SUP pin number to E3 in <i>Pin Functions</i> table                               | 4    |

| • | Added Figure 9                                                                              | 9    |

| • | Added Decimation Mode section                                                               | 31   |

| • | Added rows 3Dh, 3Fh, and 40h to Table 16                                                    | 34   |

| • | Added Register 3Dh description to Register Map section                                      | 65   |

| • | Added Register 3Fh and Register 40h descriptions to Register Map section                    | 66   |

| • | Added System-Level ESD Considerations section                                               | 68   |

| • | Added input-referred current paragraph associated to Figure 9 in Application Curves section | 71   |

| CI | hanges from Original (June 2015) to Revision A    | Page |

|----|---------------------------------------------------|------|

| •  | Deleted Diagnostics Mode section                  | 30   |

| •  | Changed bit 2 of address 00h to 0 in Table 16     | 32   |

| •  | Deleted row 30h from Table 16                     | 33   |

| •  | Changed bit 2 name and description in Register 0h | 35   |

| •  | Deleted Register 30h                              | 58   |

# 5 Device Comparison Table

| PRODUCT | PACKAGE-LEAD | LED DRIVE<br>CONFIGURATION | LED DRIVE<br>CURRENT<br>(mA, Max) | OPERATING<br>TEMPERATURE<br>RANGE | OPTIMIZED APPLICATION                      |

|---------|--------------|----------------------------|-----------------------------------|-----------------------------------|--------------------------------------------|

| AFE4400 | VQFN-40      | H-bridge,<br>common anode  | 50                                | 0°C to 70°C                       | Finger-clip pulse oximeters                |

| AFE4490 | VQFN-40      | H-bridge,<br>common anode  | 200                               | -40°C to 85°C                     | Clinical-grade pulse oximeters             |

| AFE4403 | DSBGA-36     | H-bridge,<br>common anode  | 100                               | –20°C to 70°C                     | Clinical pulse oximeter patches, wearables |

| AFE4404 | DSBGA-15     | Common anode               | 50 <sup>(1)</sup>                 | –20°C to 70°C                     | Wearable optical bio-sensing               |

<sup>(1)</sup> Mode that doubles the range to 100 mA with additional restrictions.

# **6 Pin Configuration and Functions**

YZP Package 15-Ball DSBGA Bottom View

| E | I2C_DAT | I2C_CLK | TX_SUP |

|---|---------|---------|--------|

| D | RESETZ  | TX2     | GND    |

| С | DNC     | CLK     | TX3    |

| В | INP     | ADC_RDY | TX1    |

| Α | INM     | RX_SUP  | IO_SUP |

|   | 1       | 2       | 3      |

#### **Pin Functions**

| PIN I/O |     | 1/0     | DESCRIPTION                                                                                                                                                                        |  |

|---------|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME    | NO. | 1/0     | DESCRIPTION                                                                                                                                                                        |  |

| ADC_RDY | B2  | Digital | ADC ready interrupt signal (output)                                                                                                                                                |  |

| CLK     | C2  | Digital | Clock input or output, selectable based on register. Default is input (external clock mode). Can be set via a register to output the clock when the oscillator is enabled. (1)(2)  |  |

| DNC     | C1  |         | Do not connect (leave floating)                                                                                                                                                    |  |

| GND     | D3  | Ground  | Common ground for transmitter and receiver                                                                                                                                         |  |

| I2C_CLK | E2  | Digital | $I^2C$ clock input, external pullup resistor to IO_SUP (for example, 10 k $\Omega$ )                                                                                               |  |

| I2C_DAT | E1  | Digital | $I^2C$ data, external pullup resistor to IO_SUP (for example, 10 k $\Omega$ )                                                                                                      |  |

| INM     | A1  | Analog  | Connect only to anode of photodiode <sup>(3)</sup>                                                                                                                                 |  |

| INP     | B1  | Analog  | Connect only to cathode of photodiode (3)                                                                                                                                          |  |

| IO_SUP  | А3  | Supply  | Separate supply for digital I/O. Must be less than or equal to RX_SUP. Can be tied to RX_SUP.                                                                                      |  |

| RESETZ  | D1  | Digital | RESETZ or PWDN: function based on (active low) duration of RESETZ pulse $^{(4)}$ . A 25- $\mu$ s to 50- $\mu$ s duration = RESETZ active. A > 200- $\mu$ s duration = PWDN active. |  |

| RX_SUP  | A2  | Supply  | Receiver supply; 1-µF decapacitor to GND                                                                                                                                           |  |

| TX1     | В3  | Analog  | Transmit output, LED1                                                                                                                                                              |  |

| TX2     | D2  | Analog  | Transmit output, LED2                                                                                                                                                              |  |

| TX3     | C3  | Analog  | Transmit output, LED3                                                                                                                                                              |  |

| TX_SUP  | E3  | Supply  | Transmitter supply; 1-µF decapacitor to GND                                                                                                                                        |  |

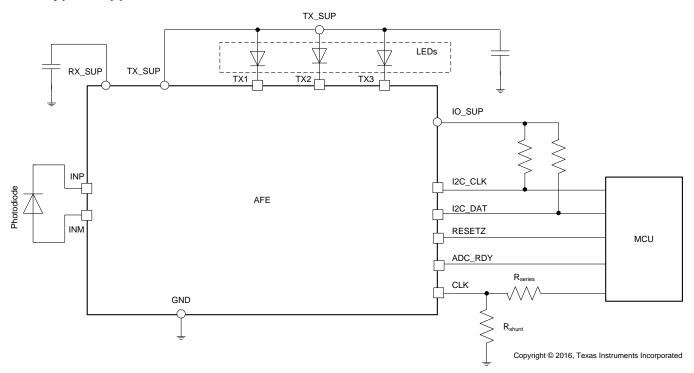

Depending on whether external clock mode or internal oscillator mode is used, extra series or shunt resistors are recommended on the CLK pin. For more details, see the *Typical Application* section.

In both hardware power-down (PWDN) and software power-down (PDNAFE) modes, the CLK pin is driven by the AFE to 0 V.

Therefore, if operating in external clock mode, take care to shut off the external clock to the AFE when in these power-down modes. Maintain the indicated polarity of photodiode connections to the AFE input pins.

A RESET pulse must be applied after power-up to ensure that the registers are all reset to their default values.

# 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                  |                                       | MIN                     | MAX                     | UNIT |  |

|------------------------------------------------------------------|---------------------------------------|-------------------------|-------------------------|------|--|

|                                                                  | RX_SUP to GND                         | -0.3                    | 4                       | V    |  |

| Cumply yeltogo rongo                                             | IO_SUP to GND                         | -0.3                    | 4                       |      |  |

| Supply voltage range                                             | RX_SUP-IO_SUP                         | -0.3                    |                         | V    |  |

|                                                                  | TX_SUP to GND                         | -0.3                    | 6                       |      |  |

| Voltage applied to analog inputs                                 |                                       | Max [-0.3, (GND - 0.3)] | Min [4, (RX_SUP + 0.3)] | V    |  |

| Voltage applied to digital inputs                                |                                       | Max [-0.3, (GND - 0.3)] | Min [4, (IO_SUP + 0.3)] | V    |  |

| Maximum duty cycle (cumulative):                                 | 50-mA LED current mode (ILED_2X = 0)  |                         | 10%                     |      |  |

| sum of all LED phase durations as a function of the total period | 100-mA LED current mode (ILED_2X = 1) |                         | 3%                      |      |  |

| Storage temperature, T <sub>stg</sub>                            |                                       | -60                     | 150                     | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |                                                        |                                                                     | VALUE | UNIT |

|--------------------|--------------------------------------------------------|---------------------------------------------------------------------|-------|------|

|                    | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1) | ±1000                                                               | 00    |      |

| V <sub>(ESD)</sub> | Electrostatic discharge                                | Charged device model (CDM), per JEDEC specification JESD22-C101 (2) | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|          |                     |                                       | MIN                                                                       | MAX               | UNIT |

|----------|---------------------|---------------------------------------|---------------------------------------------------------------------------|-------------------|------|

| RX_SUP   | Receiver supply     |                                       | 2                                                                         | 3.6               | V    |

| IO_SUP   | Input/output supply |                                       | 1.7                                                                       | Min (3.6, RX_SUP) | V    |

| TX_SUP T |                     | 50-mA LED current mode (ILED_2X = 0)  | 3.0 or (0.5 + V <sub>LED</sub> ) <sup>(1)</sup> , whichever is greater    | 5.25              | .,   |

|          | Transmitter supply  | 100-mA LED current mode (ILED_2X = 1) | 3.0 or (1.0 + V <sub>LED</sub> ) <sup>(1)</sup> ,<br>whichever is greater | 5.25              | V    |

|          | Digital inputs      |                                       | 0                                                                         | IO_SUP            | V    |

|          | Analog inputs       |                                       | 0                                                                         | RX_SUP            | V    |

|          | Operating temperatu | re range                              | -20                                                                       | 70                | °C   |

V<sub>LED</sub> refers to the maximum voltage drop across the external LED (at maximum LED current). This value is usually governed by the forward drop voltage (V<sub>FB</sub>) of the LED.

# 7.4 Thermal Information

|                        |                                              | AFE4404     |      |

|------------------------|----------------------------------------------|-------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | YZP (DSBGA) | UNIT |

|                        |                                              | 15 BALLS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 67.5        | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 0.5         | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 12.9        | °C/W |

| Ψ <sub>J</sub> T       | Junction-to-top characterization parameter   | 0.2         | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 12.9        | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | n/a         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 7.5 Electrical Characteristics

Minimum and maximum specifications are at  $T_A = -20$ °C to 70°C, typical specifications are at 25°C. TX\_SUP = 4 V, RX\_SUP = IO\_SUP = 3 V, 100-Hz PRF, 8-MHz external clock (with CLKDIV\_EXTMODE set to divide-by-2), detector  $C_{IN} = 50$  pF, and CLKDIV PRF set to 1, unless otherwise noted.

|                    | PARAMETER                             | TEST CONDITIONS                                                                                                                         | MIN               | TYP       | MAX      | UNIT                |

|--------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------|----------|---------------------|

| PULSE REP          | ETITION FREQUENCY                     |                                                                                                                                         |                   |           |          |                     |

| PRF <sup>(1)</sup> | Pulse repetition frequency            |                                                                                                                                         | 10 <sup>(2)</sup> |           | 1000     | SPS                 |

| RECEIVER           |                                       |                                                                                                                                         |                   |           | <u> </u> |                     |

|                    | Offset cancellation DAC current range |                                                                                                                                         |                   | –7 to 7   |          | μA                  |

|                    | Offset cancellation DAC current step  |                                                                                                                                         |                   | 0.47      |          | μA                  |

|                    | TIA gain setting                      |                                                                                                                                         |                   | 10k to 2M |          | Ω                   |

|                    | C <sub>f</sub> setting                |                                                                                                                                         |                   | 2.5 to 25 |          | pF                  |

|                    | Switched RC filter bandwidth          |                                                                                                                                         |                   | 2.5(3)    |          | kHz                 |

|                    | ADC averages                          |                                                                                                                                         | 1                 |           | 16       |                     |

|                    | Detector capacitance                  | Differential capacitance between INP, INN                                                                                               | 10                |           | 200      | pF                  |

| TRANSMIT           | ER                                    |                                                                                                                                         |                   |           |          |                     |

|                    | LED                                   | ILED_2X = 0                                                                                                                             |                   | 0 to 50   |          |                     |

|                    | LED current range                     | ILED_2X = 1                                                                                                                             |                   | 0 to 100  |          | mA                  |

|                    | LED current resolution                |                                                                                                                                         |                   | 6         |          | Bits                |

| CLOCKING           | (Internal Oscillator)                 |                                                                                                                                         |                   |           |          |                     |

|                    | Frequency                             |                                                                                                                                         |                   | 4         |          | MHz                 |

|                    | Accuracy                              | Room temperature                                                                                                                        |                   | ±1%       |          |                     |

|                    | Frequency drift with temperature      | Full temperature range                                                                                                                  |                   | ±0.5%     |          |                     |

|                    | Jitter (RMS)                          |                                                                                                                                         |                   | 100       |          | ps                  |

|                    | Output clock high level               |                                                                                                                                         |                   | IO_SUP    |          | V                   |

|                    | Output clock low level                |                                                                                                                                         |                   | 0         |          | V                   |

|                    | Output clock rise and fall times      | 10% to 90%, 15-pF load capacitance on CLK pin                                                                                           |                   | < 30      |          | ns                  |

| CLOCKING           | (External Clock)                      |                                                                                                                                         |                   |           | *        |                     |

|                    | Frequency range <sup>(4)</sup>        |                                                                                                                                         | 4                 |           | 60       | MHz                 |

|                    | Input clock high level                |                                                                                                                                         |                   | IO_SUP    |          | V                   |

|                    | Input clock low level                 |                                                                                                                                         |                   | 0         |          | V                   |

|                    | Input capacitance of CLK pin          | Capacitance to ground                                                                                                                   |                   | < 4       |          | pF                  |

| 12C INTERF         | ACE                                   |                                                                                                                                         |                   |           |          |                     |

|                    | Maximum clock speed                   |                                                                                                                                         |                   | 400       |          | kHz                 |

|                    | I <sup>2</sup> C slave address        |                                                                                                                                         |                   | 58        |          | Hex                 |

| PERFORMA           | NCE                                   | 1                                                                                                                                       |                   |           |          |                     |

|                    | Receiver SNR                          | SNR over a 20-Hz bandwidth for a 500-k $\Omega$ gain setting, 50% FS output, 2% LED and sampling pulse duration, ADC averages set to 16 |                   | 100       |          | dBFS <sup>(5</sup>  |

|                    | Transmitter SNR                       | SNR over a 20-Hz bandwidth for a 50-mA LED current setting                                                                              |                   | 100       |          | dBFS <sup>(5)</sup> |

PRF refers to the rate at which samples from each of the four phases are output from the AFE.

To extend the lower range of PRF down to 10 Hz, program the CLKDIV\_PRF setting.

The effective bandwidth of the switched RC filter scales as a function of the sampling duty cycle. For example, at 2% sampling width duty cycle, the effective bandwidth of the switched RC filter is approximately 50 Hz.

With appropriate setting of the clock divider ratio (CLKDIV\_EXTMODE).

dBFS refers to a full-scale voltage of 2 V.

# **Electrical Characteristics (continued)**

Minimum and maximum specifications are at  $T_A = -20^{\circ}\text{C}$  to 70°C, typical specifications are at 25°C. TX\_SUP = 4 V, RX\_SUP = IO\_SUP = 3 V, 100-Hz PRF, 8-MHz external clock (with CLKDIV\_EXTMODE set to divide-by-2), detector  $C_{IN} = 50$  pF, and CLKDIV\_PRF set to 1, unless otherwise noted.

|                      | PARAMETER                                                          | TEST CONDITIONS                                                      | MIN             | TYP    | MAX             | UNIT |

|----------------------|--------------------------------------------------------------------|----------------------------------------------------------------------|-----------------|--------|-----------------|------|

| CURRENT              | CONSUMPTION                                                        |                                                                      |                 |        |                 |      |

|                      |                                                                    | Normal operation, external clock mode 620                            |                 |        |                 |      |

|                      |                                                                    | Normal operation, internal oscillator mode                           | 670             |        |                 |      |

|                      | RX_SUP current                                                     | In dynamic power-down mode (6)                                       |                 | 300    |                 | μΑ   |

|                      |                                                                    | Hardware power-down (PWDN) mode (7)                                  |                 | 3      |                 |      |

|                      |                                                                    | Software power-down (PDNAFE) mode <sup>(7)</sup>                     |                 | 35     |                 |      |

|                      |                                                                    | Normal operation, external clock mode                                |                 | 20     |                 |      |

|                      |                                                                    | Normal operation, internal oscillator mode                           |                 | 5      |                 |      |

|                      | IO_SUP current                                                     | In dynamic power-down mode (6)                                       |                 | 20     |                 | μΑ   |

|                      | Hardware power-down (PWDN) mode <sup>(7)</sup>                     |                                                                      | 3               |        |                 |      |

|                      |                                                                    | Software power-down (PDNAFE) mode <sup>(7)</sup>                     |                 | 5      |                 |      |

|                      |                                                                    | Normal operation, external clock mode <sup>(8)</sup>                 |                 | 25     |                 |      |

|                      |                                                                    | Normal operation, internal oscillator mode <sup>(8)</sup>            |                 | 25     |                 |      |

| TX_SUP current       |                                                                    | In dynamic power-down mode (6)(8)                                    |                 | 5      |                 | μΑ   |

|                      |                                                                    | Hardware power-down (PWDN) mode (7)(8)                               |                 | 2      |                 |      |

|                      |                                                                    | Software power-down (PDNAFE) mode <sup>(7)(8)</sup>                  |                 | 2      |                 |      |

| TRANSIEN             | IT RECOVERY                                                        |                                                                      |                 |        |                 |      |

| t <sub>ACTIVE</sub>  | Recovery from PWDN mode                                            | Time for signal chain to be functional (9)                           |                 | 10     |                 | ms   |

| t <sub>CHANNEL</sub> | Recovery from any event causing a change in signal characteristics | PRF = 100 Hz, sampling duty cycle (each phase) of 2% <sup>(10)</sup> |                 | 200    |                 | ms   |

| DIGITAL IN           | IPUTS                                                              |                                                                      |                 |        |                 |      |

| V <sub>IH</sub>      | High-level input voltage                                           |                                                                      | 0.9 ×<br>IO_SUP | IO_SUP |                 | V    |

| V <sub>IL</sub>      | Low-level input voltage                                            |                                                                      |                 | 0      | 0.1 x<br>IO_SUP | V    |

| DIGITAL O            | UTPUTS                                                             |                                                                      |                 |        |                 |      |

| V <sub>OH</sub>      | High-level output voltage                                          |                                                                      |                 | IO_SUP |                 | V    |

| V <sub>OL</sub>      | Low-level output voltage                                           |                                                                      |                 | 0      |                 | V    |

- (6) In dynamic power-down mode for 90% and active mode for 10% of the period.

- (7) External clock mode with the external clock switched off.

- (8) LED currents set to 0 mA.

- (9) For full performance to be restored, a longer time as governed by t<sub>CHANNEL</sub> can be applicable.

- (10) t<sub>CHANNEL</sub>scales inversely with the sampling duty cycle.

# 7.6 Timing Requirements

|                           |                                                                                                                                            | MIN | TYP  | MAX | UNIT |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| t <sub>I2C_RISE</sub>     | $\mbox{I}^2\mbox{C}$ data rise time with a 10-k $\Omega$ pullup resistor with a 20-pF load from $\mbox{I}^2\mbox{C}$ data to GND           |     | 1200 |     | ns   |

| t <sub>I2C_FALL</sub>     | $\mbox{I}^2\mbox{C}$ data fall time (when the data line is pulled down by the AFE) with a 20-pF load from $\mbox{I}^2\mbox{C}$ data to GND |     | 28   |     | ns   |

| t <sub>ADC_RDY_RISE</sub> | ADC_RDY rise time (10% to 90%) with a 15-pF capacitive load to ground                                                                      |     | 21   |     | ns   |

| t <sub>ADC_RDY_FALL</sub> | ADC_RDY fall time (90% to 10%) with a 15-pF capacitive load to ground                                                                      | ·   | 21   |     | ns   |

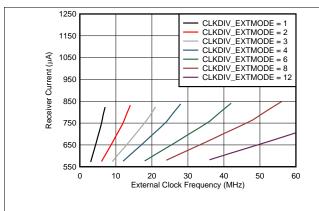

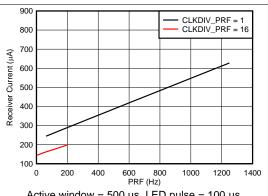

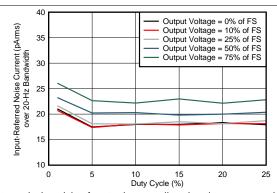

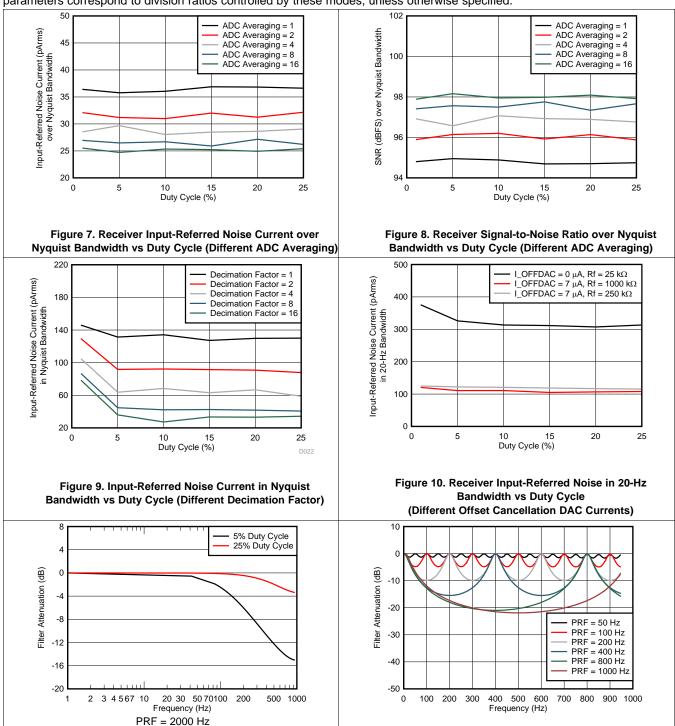

#### 7.7 Typical Characteristics

At 25°C, TX\_SUP = 4 V, RX\_SUP = IO\_SUP = 3.3 V, 100-Hz PRF, 25% duty cycle,  $R_f$  = 500 k $\Omega$ ,  $C_f$  is adjusted to keep the TIA time constant at 1/10th of the sampling duration, 8-MHz external clock (with CLKDIV\_EXTMODE set to divide-by-2), CLKDIV\_PRF = 1, detector  $C_{IN}$  = 50 pF, ADC averaging = max allowed, SNR (dBFS) = noise referred to full-scale range of 2 V, noise integrated from 1 Hz to Nyquist (= PRF / 2), and values assigned to CLKDIV\_EXTMODE and CLK\_DIV\_PRF parameters correspond to division ratios controlled by these modes, unless otherwise specified.

Figure 1. Receiver Current vs External Clock Frequency

Active window = 500  $\mu$ s, LED pulse = 100  $\mu$ s, all four DYNAMIC bits set to 1

Figure 2. Receiver Current vs PRF in Dynamic Power-Down Mode

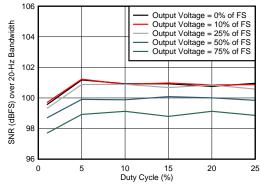

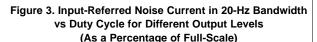

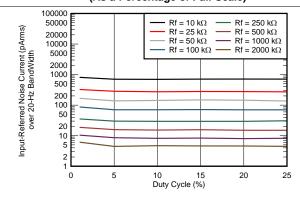

Duty cycle (x-axis) refers to the sampling duration expressed as a percentage of the pulse repetition period.

Duty cycle (x-axis) refers to the sampling duration expressed as a percentage of the pulse repetition period.

Figure 5. Receiver Input-Referred Noise Current in 20-Hz BW vs Duty Cycle (Different TIA Gain Settings)

Figure 4. Signal-to-Noise Ratio in 20-Hz Bandwidth vs Duty Cycle for Different Output Levels (As a Percentage of Full-Scale)

Figure 6. Receiver SNR in 20-Hz BW vs Duty Cycle (Different TIA Gain Settings)

# **Typical Characteristics (continued)**

At 25°C, TX\_SUP = 4 V, RX\_SUP = IO\_SUP = 3.3 V, 100-Hz PRF, 25% duty cycle,  $R_f$  = 500 k $\Omega$ ,  $C_f$  is adjusted to keep the TIA time constant at 1/10th of the sampling duration, 8-MHz external clock (with CLKDIV\_EXTMODE set to divide-by-2), CLKDIV\_PRF = 1, detector  $C_{IN}$  = 50 pF, ADC averaging = max allowed, SNR (dBFS) = noise referred to full-scale range of 2 V, noise integrated from 1 Hz to Nyquist (= PRF / 2), and values assigned to CLKDIV\_EXTMODE and CLK\_DIV\_PRF parameters correspond to division ratios controlled by these modes, unless otherwise specified.

Figure 11. Response of the Switched-RC Filter

at the AFE Output

Figure 12. Filter Response for Multiple PRFs at

1% Duty Cycle

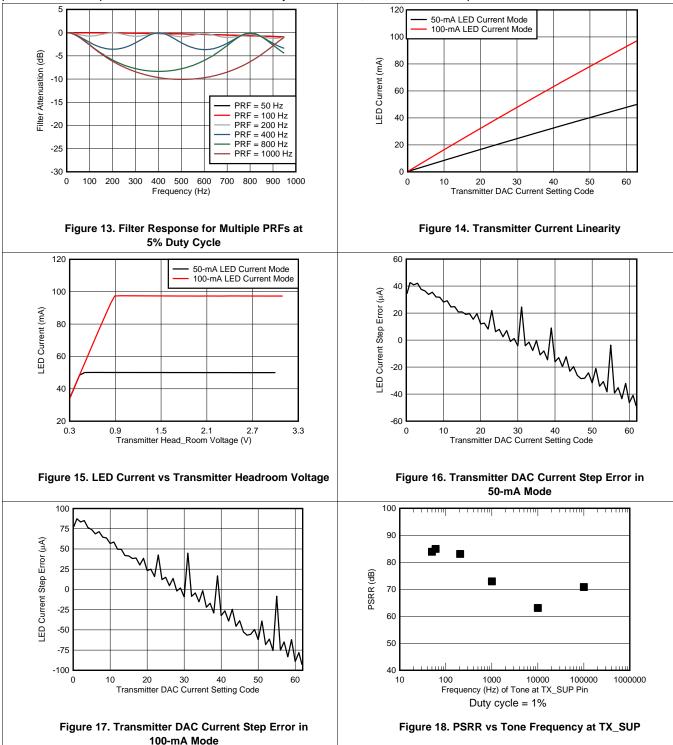

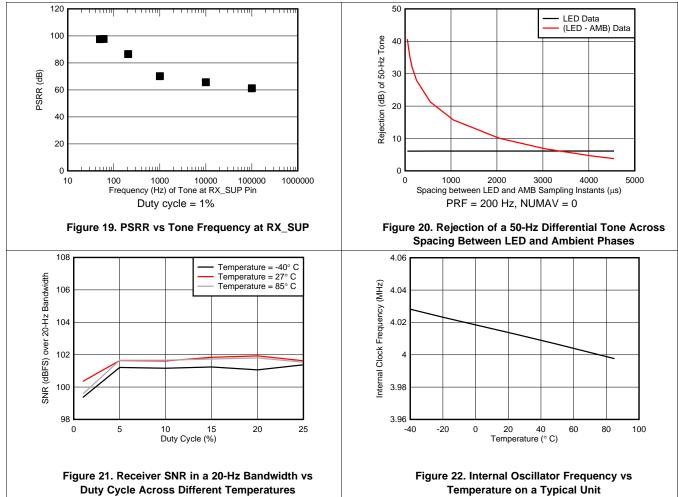

# **Typical Characteristics (continued)**

At 25°C, TX\_SUP = 4 V, RX\_SUP = IO\_SUP = 3.3 V, 100-Hz PRF, 25% duty cycle,  $R_f$  = 500 k $\Omega$ ,  $C_f$  is adjusted to keep the TIA time constant at 1/10th of the sampling duration, 8-MHz external clock (with CLKDIV\_EXTMODE set to divide-by-2), CLKDIV\_PRF = 1, detector  $C_{IN}$  = 50 pF, ADC averaging = max allowed, SNR (dBFS) = noise referred to full-scale range of 2 V, noise integrated from 1 Hz to Nyquist (= PRF / 2), and values assigned to CLKDIV\_EXTMODE and CLK\_DIV\_PRF parameters correspond to division ratios controlled by these modes, unless otherwise specified.

#### **Typical Characteristics (continued)**

At 25°C, TX\_SUP = 4 V, RX\_SUP = IO\_SUP = 3.3 V, 100-Hz PRF, 25% duty cycle,  $R_f$  = 500 k $\Omega$ ,  $C_f$  is adjusted to keep the TIA time constant at 1/10th of the sampling duration, 8-MHz external clock (with CLKDIV\_EXTMODE set to divide-by-2), CLKDIV\_PRF = 1, detector  $C_{IN}$  = 50 pF, ADC averaging = max allowed, SNR (dBFS) = noise referred to full-scale range of 2 V, noise integrated from 1 Hz to Nyquist (= PRF / 2), and values assigned to CLKDIV\_EXTMODE and CLK\_DIV\_PRF parameters correspond to division ratios controlled by these modes, unless otherwise specified.

# 8 Detailed Description

#### 8.1 Overview

The AFE has an integrated transmitter and receiver for optical heart-rate monitoring and pulse oximetry applications. The system is characterized by a parameter termed the *pulse repetition frequency (PRF)* that determines the repetition periodicity of a sequence of operations. Every cycle of a PRF results in four 24-bit digital samples at the output of the AFE, each of which is stored in a separate register.

# 8.2 Functional Block Diagram

#### 8.3 Feature Description

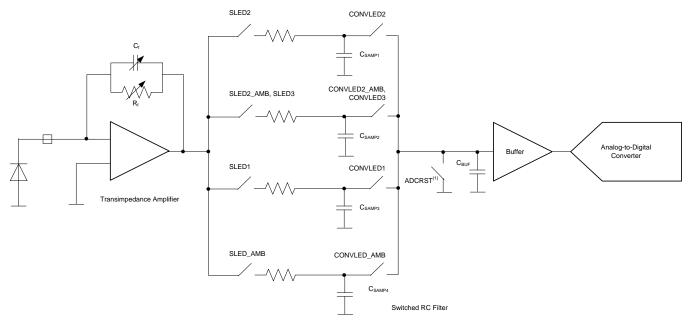

#### 8.3.1 TIA and Switched RC Filter

The receiver input pins (INP, INM) are meant to be connected differentially to a photodiode. The signal current from the photodiode is converted to a differential voltage using a transimpedance amplifier (TIA). The TIA gain is set by its feedback resistor ( $R_f$ ) and can be programmed from 10 k $\Omega$  to 2 M $\Omega$ . The transimpedance gain between the input current and output differential voltage of the TIA is equal to 2 ×  $R_f$ . At the output of the TIA is a switched RC filter. There are four parallel instances of the filter, each of which are connected to the TIA output signal during one of four sampling phases.

The signal chain is kept fully differential throughout the receiver channel in order to enable excellent rejection of common-mode noise as well as noise on power supplies. For simplicity, the scheme with the four parallel filters is shown in Figure 23 for a single-ended representation of the signal chain. The ADCRST signal corresponds to the collection of active phases of four ADCRST pulses: ADCRST0, ADCRST1, ADCRST2, and ADCRST3.

NOTE: For simplicity, this circuit is shown in single-ended format.

(1) ADCRST corresponds to ADCRST0, ADCRST1, ADCRST2, or ADCRST3.

Figure 23. Four Sampling and Conversion Phases Diagram

#### **Feature Description (continued)**

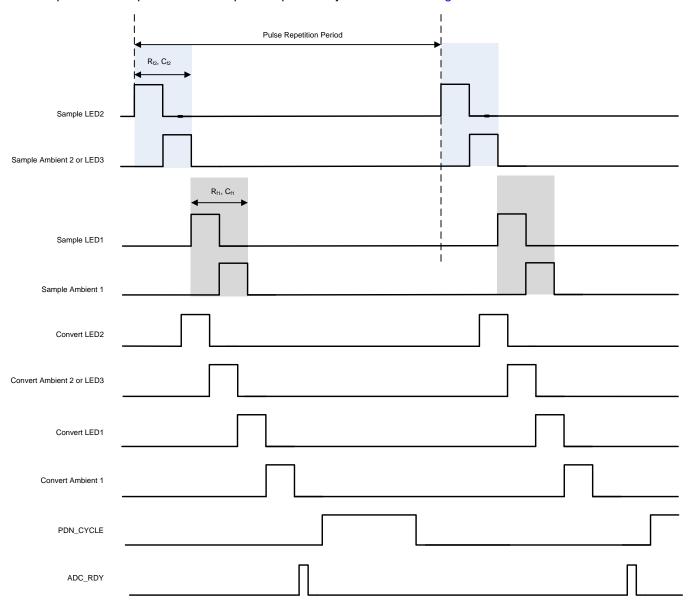

#### 8.3.1.1 Operation with Two and Three LEDs

The four sampling phases can correspond to either of the following signal state sequences received by the photodiode:

- 1. 2-LED mode: LED2 → ambient phase 2 → LED1 → ambient phase 1

- 2. 3-LED mode: LED2 → LED3 → LED1 → ambient

The sequence of the phases within a pulse repetition cycle is shown in Figure 24.

Figure 24. Sequence of Four Sampling and Conversion Phases

In the 2-LED mode, LED1 and LED2 are pulsed during the corresponding sampling instants. In the 3-LED mode, LED1, LED2, and LED3 are pulsed during the corresponding sampling instants. As mentioned in the *TIA Gain Settings* and *Operation with Two and Three LEDs* sections, the TIA gain (R<sub>f</sub>) and feedback capacitor (C<sub>f</sub>) can be programmed differently between two sets: R<sub>f1</sub> / C<sub>f1</sub> and R<sub>f2</sub> / C<sub>f2</sub>. The way these sets are applied to the four phases is shown in Figure 24.

#### Feature Description (continued)

#### 8.3.1.1.1 LED Current Setting

The default LED current range is from 0 mA to 50 mA. The individual currents of each of the three LEDs can be controlled independently, each with a separate 6-bit control.

Taken as a decimal number, the 6-bit setting provides 63 equal steps between 0 mA and 50 mA. Each increment of the ILED 6-bit code causes the LED current setting to increment by approximately 0.8 mA. For details, see register 22h.

The LED current range can be doubled by setting the ILED\_2X bit to 1. The accuracy of higher current settings close to 100 mA can be low because of current saturation of the driver. Each increment of the ILED 6-bit code causes the LED current to increment by approximately 1.6 mA when ILED\_2X is set to 1.

#### 8.3.1.2 TIA Gain Settings

The TIA gain is set by programming the value of R<sub>f</sub> (the feedback resistor of the TIA). The R<sub>f</sub> setting is controlled using the TIA\_GAIN register bit. For details see register 21h.

By default, the same TIA\_GAIN setting is applied for all four phases of the receiver. Separate gains can be set for two of the four phases by setting the EN\_SEP\_GAIN bit. When the EN\_SEP\_GAIN bit is enabled, the TIA\_GAIN register controls the  $R_{f2}$  settings.

Mapping of the  $R_{f1}$  /  $R_{f2}$  values to the two sets of 3-bit controls is described in Table 50.

#### 8.3.1.3 TIA Bandwidth Settings

TIA bandwidth settings are similar to TIA gain settings. The TIA bandwidth is set by programming the value of  $C_f$  (the feedback capacitance of the TIA). The product of  $R_f$  and  $C_f$  gives the time constant of the TIA and must be set approximately 1/5th (or less) of the LED or sampling pulse durations. This choice of time constant allows the TIA to pass the incoming pulses from the photodiode.

C<sub>f</sub> is controlled using the TIA\_CF register bit. For details, see register 21.

By default, the same TIA\_CF setting is applied for all four phases of the receiver. Similar to the TIA gain settings, a separate  $C_f$  can be set for two of the four phases by setting the EN\_SEP\_GAIN bit. When the EN\_SEP\_GAIN bit is enabled, the TIA\_CF register controls the  $C_{f1}$  settings and TIA\_CF\_SEP controls the  $C_{f2}$  settings. Mapping the  $C_{f1}$  /  $C_{f2}$  values to the two sets of 3-bit controls is the same as illustrated in Table 51.

#### 8.3.2 Power Management

The AFE has three independent supplies for the transmitter, receiver, and I/O.

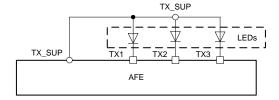

#### 8.3.2.1 Transmitter Supply (TX SUP)

The transmitter supply has a range of 3.0 V to 5.25 V. In the most common arrangement, this supply can be the same supply that the anodes of the LEDs are tied to, as shown in Figure 25.

Figure 25. LED to Pin Connections

When the LEDs must be tied to a different supply, care must be taken to ensure that the LED supply is within 0.3 V of TX\_SUP. This consideration of the LED supply voltage prevents the electrostatic discharge (ESD) diodes inside the AFE from turning on during the off state of the LEDs.

#### **Feature Description (continued)**

#### 8.3.2.2 Receiver Supply (RX\_SUP)

The receiver supply has a range of 2.0 V to 3.6 V. The AFE has internal low-dropout (LDO) regulators operating at 1.8 V that regulate both the analog and digital blocks inside the AFE. This rejection of supply noise from the internal LDOs, coupled with the differential nature of the architecture, enables excellent noise rejection on the supplies (for instance, 50-Hz noise).

#### 8.3.2.3 I/O Supply (IO\_SUP)

The I/O supply can either be tied to RX\_SUP or can be separately driven. The motivation for a separate I/O supply is to interface with certain microcontrollers (MCUs) that require a 1.8-V I/O current. In this case, IO\_SUP can be driven separately from RX\_SUP and can be tied to 1.8 V.

#### 8.3.2.4 Boost Converters Selection

If the supply voltage for TX\_SUP (and the LEDs) is unavailable in the system, a boost converter may be required to generate the supply voltage. TI has a portfolio of boost converters from which an appropriate device can be selected. Some choices are listed in Table 1.

Table 1. TI Boost Converter Details<sup>(1)</sup>

| TI PART NUMBER | SIZE<br>(mm, L × W × H) | INPUT SUPPLY<br>(V) | OUTPUT SUPPLY                                  | TYPICAL<br>QUIESCENT<br>CURRENT (μA) | EXTERNAL COMPONENTS                   |

|----------------|-------------------------|---------------------|------------------------------------------------|--------------------------------------|---------------------------------------|

| TPS61254       | 1.2 × 1.3 × 0.625       | 2.3 to 5.5          | Different parts with a fixed voltage up to 5 V | 36                                   | 2 capacitors, 1 inductor              |

| TPS61240       | 0.9 × 1.3 × 0.625       | 2.3 to 5.5          | 5 V (fixed)                                    | 30                                   | 2 capacitors, 1 inductor              |

| TPS61252       | 2 × 2 × 0.75            | 2.3 to 6            | Adjustable up to 6.5 V                         | 30                                   | 3 capacitors, 1 inductor, 4 resistors |

| TPS61220       | 2 × 2.2 × 1             | 0.7 to 5.5          | Adjustable from 1.8 V to 6 V                   | 5.5                                  | 2 capacitors, 1 inductor, 2 resistors |

<sup>(1)</sup> For the most current information, see the TI data sheets corresponding to each device (available for download from www.ti.com).

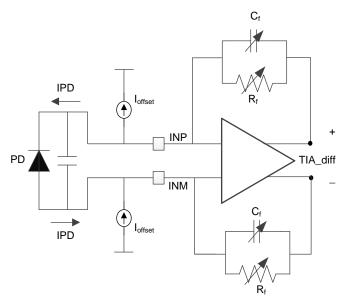

#### 8.3.3 Offset Cancellation DAC

A typical optical heart-rate signal has a dc component and an ac component. Although a higher TIA gain maximizes the ac signal at the AFE output, the magnitude of the dc component limits the maximum gain possible in the TIA. In order to decouple the affect of the dc level on the allowed ac signal gain, a current digital-to-analog converter (DAC) is placed at the input of the device. By setting a programmable cancellation current (based on the dc current signal level), the effective signal that is gained up by the TIA can be reduced. This reduction in the effective signal current into the TIA results in the ability to set a higher TIA gain than what is otherwise possible without enabling the offset correction. In each of the four phases of operation, a separate programmable current value can be set by programming four different sets of register bits. These cancellation currents are automatically presented to the input of the TIA in the appropriate phase. The ability to set a different cancellation current in each of the four phases can be used to cancel out the ambient current in the ambient phase. In the LED on phase, this ability can be used to cancel out the sum of the ambient current and dc current of the heart-rate signal. The polarities of the signal current and offset cancellation current is illustrated in Figure 26. The polarity of the offset cancellation current can be reversed by programming the POL\_OFFDAC bits.

With zero input current and zero current in the offset cancellation DAC, the output of the AFE will be close to zero. Based on the channel offset, the output voltage for zero input current could be a small positive or negative value, usually in the range of several mV. With the photodiode connected as shown in Figure 26 and a signal current coming from the photodiode, the output code of the device is expected to be positive with the offset cancellation DAC set to zero ( $I_{offset} = 0$ ). With  $I_{offset}$  set negative (POL\_OFFFAC = 1), a dc offset can be subtracted from the signal and the ac signal can be amplified with a higher gain than what is otherwise possible.

Figure 26. Offset Cancellation Current Polarity Diagram

A breakdown of the signal current and voltage levels is provided in Table 2 for a variety of signal levels. In Table 2, the current transfer ratio (CTR) is used to describe the relationship between the set LED current and the resulting photodiode current (IPD). CTR is the ratio of the photodiode current for a given LED current and is a function of the optical and mechanical parameters as well as human physiology.

| Table 2. Signal Current and Voltage Levels for a Hypothetical Use Case <sup>(1)</sup> | Table 2 | . Signal Current | and Voltage | Levels for a | <b>Hypothetical</b> | Use Case <sup>(1)</sup> |

|---------------------------------------------------------------------------------------|---------|------------------|-------------|--------------|---------------------|-------------------------|

|---------------------------------------------------------------------------------------|---------|------------------|-------------|--------------|---------------------|-------------------------|

| PHASE | ILED (mA) | CTR<br>(µA / mA) | I <sub>sig</sub> (μA) | I <sub>amb</sub> (μA) | IPD (μA) | I_OFFDAC<br>(µA) | I <sub>eff</sub> (μA) | R <sub>f</sub> (MΩ) | TIA_diff (V) |

|-------|-----------|------------------|-----------------------|-----------------------|----------|------------------|-----------------------|---------------------|--------------|

| LED2  | 25        | 0.025            | 0.625                 | 1                     | 1.625    | -1.4             | 0.225                 | 1                   | 0.45         |

| LED3  | 50        | 0.025            | 1.25                  | 1                     | 2.25     | -1.87            | 0.38                  | 0.5                 | 0.38         |

| LED1  | 12.5      | 0.025            | 0.3125                | 1                     | 1.3125   | -0.93            | 0.3825                | 0.5                 | 0.3825       |

| AMB1  | 0         | 0.025            | 0                     | 1                     | 1        | -0.93            | 0.07                  | 2                   | 0.28         |

<sup>(1)</sup> ILED is the set LED current; CTR is the current transfer ratio (in μA / mA); I<sub>sig</sub> is the photodiode signal current resulting from LED pulsing (I<sub>sig</sub> = ILED × CTR); I<sub>amb</sub> is the current in the photodiode resulting from ambient light (that is present in all phases and adds to I<sub>sig</sub>); IPD is the total input current (I<sub>sig</sub> + I<sub>amb</sub>); I\_OFFDAC is the current setting of the offset cancellation DAC; I<sub>eff</sub> is the effective current after offset cancellation (I<sub>sig</sub> + I\_OFFDAC); R<sub>f</sub> is the TIA gain setting; and TIA\_diff is the output differential signal of the TIA (note that this signal must be within the range of ±1 V).

#### 8.3.3.1 Offset Cancellation DAC Controls

The I\_OFFDAC bits control the magnitude of the current subtracted (or added) at the TIA input. The POL\_OFFDAC bits control the polarity of the current and determine whether the current is subtracted from or added to the input. For details, see register 3Ah.

#### 8.3.4 Analog-to-Digital Converter (ADC)

The AFE has an ADC that provides a 22-bit representation of the current from the photodiode. The ADC codes corresponding to the various sampling phases can be read out from 24-bit registers in twos complement format. The ADC full-scale input range is  $\pm 1.2$  V and spans bits 21 to 0. The mapping of the ADC input voltage to the ADC code is shown in Table 3.

Table 3. Mapping the ADC Input Voltage to the ADC Code

| DIFFERENTIAL INPUT VOLTAGE AT ADC INPUT | 24-BIT ADC OUTPUT CODE                  |

|-----------------------------------------|-----------------------------------------|

| –1.2 V                                  | 111000000000000000000000000000000000000 |

| (-1.2 / 2 <sup>21</sup> ) V             | 111111111111111111111111111111111111111 |

| 0                                       | 000000000000000000000000000000000000000 |

| (1.2 / 2 <sup>21</sup> ) V              | 000000000000000000000000000000000000000 |

| 1.2 V                                   | 000111111111111111111111111111111111111 |

The two MSBs of the 24-bit word serve as sign-extension bits to the 22-bit ADC code and are equal to the MSB of the 22-bit ADC code when the input to the ADC is within its full-scale range, as shown in Table 4.

Table 4. Using Sign-Extension Bits to Determine the Input Operating Voltage

| BITS 23-21 | INPUT STATUS                                                            |

|------------|-------------------------------------------------------------------------|

| 000        | Positive and lower than positive full-scale (within full-scale range)   |

| 111        | Negative and higher than negative full-scale (within full-scale range)  |

| 001        | Positive and higher than positive full-scale (outside full-scale range) |

| 110        | Negative and lower than negative full-scale (outside full-scale range)  |

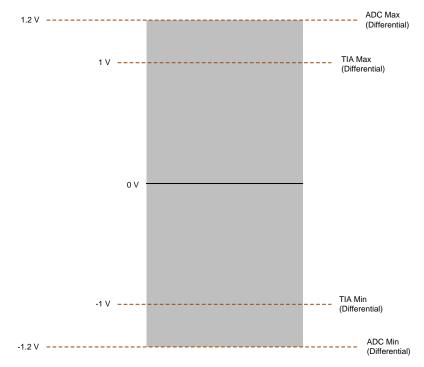

Noted that the TIA has an operating range of  $\pm 1$  V even though the ADC input full-scale range is  $\pm 1.2$  V, as shown in Figure 27. When setting the TIA gain, ensure that the signal at the TIA output does not exceed  $\pm 1$  V.

Figure 27. TIA and ADC Dynamic Ranges

#### 8.3.5 I<sup>2</sup>C Interface

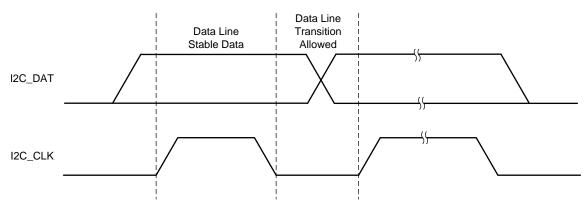

The AFE has an I<sup>2</sup>C interface for communication. The I2C\_CLK and I2C\_DAT lines require external pullup resistors to IO\_SUP. See the I<sup>2</sup>C protocol standards documents for details of the I<sup>2</sup>C interface. This section only describes certain key features of the interface. The data on I2C\_DAT must be stable during the high level of I2C\_CLK and may transition during the low level of I2C\_CLK, as shown in Figure 28.

Figure 28. Allowed Transition of I2C\_DAT while Transmission of Data Bits

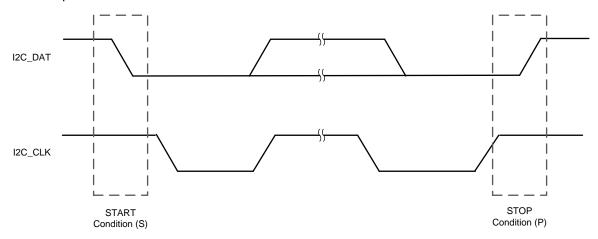

The start condition is indicated by a high-to-low transition of the I2C\_DAT line when the I2C\_CLK is high. A stop condition is indicated by a low-to-high transition of the I2C\_DAT line when the I2C\_CLK is high. Figure 29 shows the start and stop conditions.

Figure 29. Transition of I2C\_DAT during Start and Stop Conditions

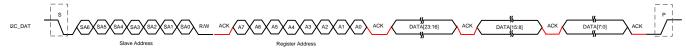

With the previously mentioned protocols for data, start, and stop conditions in place, the write and read operations are as shown in Figure 30 and Figure 31, respectively. In Figure 30 and Figure 31, the slave address for the AFE (indicated as SA6 to SA0) is a 7-bit representation of address 58h. The R/W bit is the read/write bit and is set to '1' for Read and '0' for Write. Only the ADC output registers (addressed from 2Ah to 2Fh) can be read out without the need for setting the REG\_READ bit. Prior to reading out any other register, the REG\_READ bit needs to be additionally set to '1'. In Figure 30 and Figure 31, the activity performed by the host is shown in black whereas activity from the AFE is shown in red. Thus, after the host sends the slave address during a write operation, the AFE pulls the I2C\_DAT line low (shown as ACK) if the slave address matches 58h. Similarly, the host pulls the I2C\_DAT line high (shown as NACK) as acknowledgment of a successfully completed read operation involving three bytes of data. Continuous read/write mode is not supported.

(1) Activity performed by the host is shown in black whereas activity from the AFE is shown in red. Continuous read/write mode is not supported.

Figure 30. I<sup>2</sup>C Write Option Timing

Figure 31. I<sup>2</sup>C Read Option Timing

#### 8.3.6 Timing Engine

The AFE has a fully-integrated timing engine that can be programmed to generate all clock phases for synchronized transmit drive, receive sampling, and data conversion. To enable the timing engine (after powering up the device), enable the TIMEREN bit.

#### 8.3.6.1 Timer and PRF Controls

The timing engine inside the AFE has a 16-bit counter. The duration of the count with respect to an internal clock (the timer clock) determines the pulse repetition period. The pulse repetition frequency (PRF) can be set using the PRPCT register bits that represent the high value of the counter (the low value of the counter is 0). The counter automatically counts until reaching PRPCT and then returns to 0 to start the next count. To suspend the count and keep the counter in reset state, enable the TM\_COUNT\_RST bit.

# 8.3.6.2 Timing Control Registers

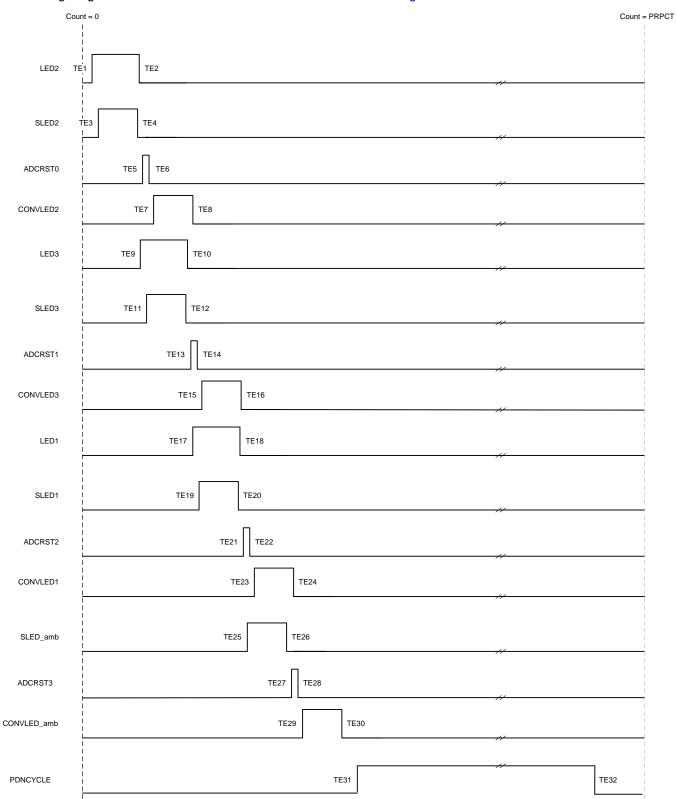

The start and stop counts for the various dynamic signals generated by the timing engine are shown in Table 5. The timing edge numbers are in reference to Figure 32.

**Table 5. Timing Register and Edge Details**

| TIMING SIGNAL            | DESCRIPTION                             | REGISTER<br>ADDRESS (Hex) | TIMING EDGE |

|--------------------------|-----------------------------------------|---------------------------|-------------|

| LED2STC                  | Sample LED2 start                       | 1h                        | TE3         |

| LED2ENDC                 | Sample LED2 end                         | 2h                        | TE4         |

| LED1LEDSTC               | LED1 start                              | 3h                        | TE17        |

| LED1LEDENDC              | LED1 end                                | 4h                        | TE18        |

| ALED2STC\LED3STC         | Sample ambient 2 (or sample LED3) start | 5h                        | TE11        |

| ALED2ENDC\LED3ENDC       | Sample ambient 2 (or sample LED3) end   | 6h                        | TE12        |

| LED1STC                  | Sample LED1 start                       | 7h                        | TE19        |

| LED1ENDC                 | Sample LED1 end                         | 8h                        | TE20        |

| LED2LEDSTC               | LED2 start                              | 9h                        | TE1         |

| LED2LEDENDC              | LED2 end                                | Ah                        | TE2         |

| ALED1STC                 | Sample ambient 1 start                  | Bh                        | TE25        |

| ALED1ENDC                | Sample ambient 1 end                    | Ch                        | TE26        |

| LED2CONVST               | LED2 convert phase start                | Dh                        | TE7         |

| LED2CONVEND              | LED2 convert phase end                  | Eh                        | TE8         |

| ALED2CONVST\LED3CONVST   | Ambient 2 (or LED3) convert phase start | Fh                        | TE15        |

| ALED2CONVEND\LED3CONVEND | Ambient 2 (or LED3) convert phase end   | 10h                       | TE16        |

| LED1CONVST               | LED1 convert phase start                | 11h                       | TE23        |

| LED1CONVEND              | LED1 convert phase end                  | 12h                       | TE24        |

| ALED1CONVST              | Ambient 1 convert phase start           | 13h                       | TE29        |

| ALED1CONVEND             | Ambient 1 convert phase end             | 14h                       | TE30        |

| ADCRSTSTCT0              | ADC reset phase 0 start                 | 15h                       | TE5         |

| ADCRSTENDCT0             | ADC reset phase 0 end                   | 16h                       | TE6         |

| ADCRSTSTCT1              | ADC reset phase 1 start                 | 17h                       | TE13        |

| ADCRSTENDCT1             | ADC reset phase 1 end                   | 18h                       | TE14        |

| ADCRSTSTCT2              | ADC reset phase 2 start                 | 19h                       | TE21        |

| ADCRSTENDCT2             | ADC reset phase 2 end                   | 1Ah                       | TE22        |

| ADCRSTSTCT3              | ADC reset phase 3 start                 | 1Bh                       | TE27        |

| ADCRSTENDCT3             | ADC reset phase 3 end                   | 1Ch                       | TE28        |

When three LEDs are used within a single period, the Ambient2 phase is replaced by the LED3 phase. The timing controls for driving the third LED are as shown in Table 6.

Table 6. Timing Controls for Driving the Third LED

| TIMING SIGNAL | DESCRIPTION | REGISTER ADDRESS (Hex) | TIMING EDGE |

|---------------|-------------|------------------------|-------------|

| LED3LEDSTC    | LED3 start  | 36h                    | TE9         |

| LED3LEDENDC   | LED3 end    | 37h                    | TE10        |

The timing diagram for when all three LEDs are active is shown in Figure 32.

Figure 32. Timing Diagram

# 8.3.6.3 Receiver Timing

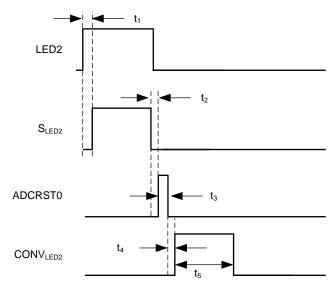

The timing engine can be programmed to set the different phases of the receiver. The relative timings of the LED phase, sampling phase, ADC reset phase, and ADC conversion phases are shown in Figure 33 and Table 7.

Figure 33. Receiver Timing Guidelines

**Table 7. Receiver Timing Details**

|                |                                                         | MIN MA                                                   | Х | UNIT                  |

|----------------|---------------------------------------------------------|----------------------------------------------------------|---|-----------------------|

| t <sub>1</sub> | Start of LED to start of sampling                       | Max [25, (0.2 × LED pulse duration)]                     |   | μs                    |

| $t_2$          | End of LED to start of ADC reset phase                  | 2                                                        |   | Counts <sup>(1)</sup> |

| t <sub>3</sub> | Duration of ADC reset phase                             | 6                                                        |   | Counts                |

| t <sub>4</sub> | End of ADC reset phase to start of ADC conversion phase | 2                                                        | 2 | Count                 |

| t <sub>5</sub> | Duration of ADC conversion phase (2)                    | (NUMAV + 2) × 200 × t <sub>ADC</sub> + 15 <sup>(3)</sup> |   | μs                    |

- (1) Refers to one clock period of CLK\_TE.

- (2) See Figure 36 for notations of the clocking domain.

- (3)  $t_{ADC} = 1 / f_{ADC}$ .

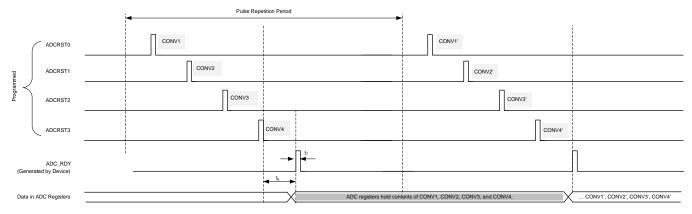

The fourth ADCRST signal (ADCRST3) in a period also defines the start of the ADC\_RDY pulse. The rising edge of the ADC\_RDY signal can be used as an interrupt by the MCU to readout the registers corresponding to the preceding four conversions in that period. If any of the four conversion phases are not needed, then their duration can be set to 0. However, the corresponding ADCRSTx pulse must still be defined. All four ADCRSTx pulses must be defined in order to generate the ADC\_RDY pulse. A scheme of the ADC\_RDY pulse generation is shown in Figure 34. The ADC\_RDY pulse timing is shown in Table 8.

Figure 34. ADC\_RDY Generation Scheme

# Table 8. ADC\_RDY Timing Details

|                |                                                         | ТҮР                                  | MAX                                       | UNIT |

|----------------|---------------------------------------------------------|--------------------------------------|-------------------------------------------|------|

| t <sub>6</sub> | End of fourth ADC reset phase to start of ADC_RDY pulse | (NUMAV + 1) × 200 × t <sub>ADC</sub> | (NUMAV + 2) × 200 × t <sub>ADC</sub> + 15 | μs   |

| t <sub>7</sub> | ADC_RDY pulse duration                                  | t <sub>ADC</sub> <sup>(1)</sup>      |                                           | μs   |

<sup>(1)</sup> If a larger pulse duration is needed for the ADC\_RDY interrupt, use PROG\_TG\_EN to enable a programmable timing signal to come out of the ADC\_RDY pin. The location of the signal can be set using the PROG\_TG\_STC and PROG\_TG\_ENDC counts.

#### 8.3.6.4 Dynamic Power-Down Timing

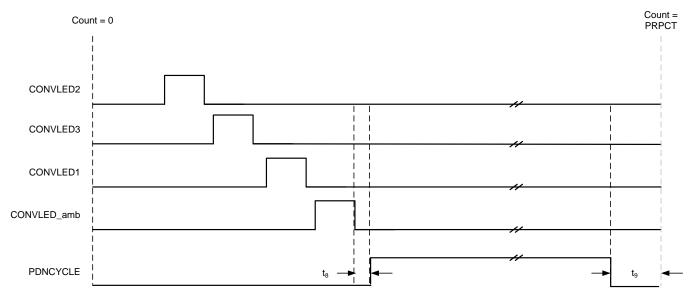

The dynamic power-down feature can be used to shut down the receiver inside every cycle to save power, as shown in Figure 35 and Table 9.

Figure 35. Dynamic Power-Down Timing Diagram

**Table 9. Dynamic Power-Down Timing Details**

|                |                                                      | MIN | UNIT |

|----------------|------------------------------------------------------|-----|------|

| t <sub>8</sub> | End of 4th conversion phase to the start of PDNCYCLE | 200 | μs   |

| t <sub>9</sub> | End of PDNCYCLE to start of next period              | 200 | μs   |

The timing controls for the PDNCYCLE pulse are shown in Table 10.

**Table 10. Timing Controls for Dynamic Power-Down**

| TIMING SIGNAL | DESCRIPTION              | REGISTER ADDRESS (Hex) | TIMING EDGE <sup>(1)</sup> |

|---------------|--------------------------|------------------------|----------------------------|

| PDNCYCLESTC   | Dynamic power-down start | 32h                    | TE31                       |

| PDNCYCLEENDC  | Dynamic power-down end   | 33h                    | TE32                       |

<sup>(1)</sup> See Figure 32.

#### 8.3.6.5 Sample Register Values

Table 11 lists a sample of the register settings for generating the different timing signals. These sample settings correspond to CLK\_INT = 4 MHz and a PRF of 100 Hz. Three LEDs are used in a cycle, each with a duty cycle of 1%, corresponding to a pulse duration of 100  $\mu$ s. The conversion durations are set in order to accommodate four averages (NUMAV = 3). Two cases are described in Table 11: one for CLKDIV\_PRF = 1 (CLK\_TE = 4 MHz) and the other for CLKDIV\_PRF = 16 (CLK\_TE = 250 kHz).

# **Table 11. Sample Register Settings**

| SIGNAL <sup>(1)</sup>   | REGISTER FIELD               | NO DIVISION OF C<br>ENGINE<br>(CLKDIV_ | CLOCK                              | ADC CLOCK TO TIMING ENGIN<br>CLOCK DIVIDED BY 16<br>(CLKDIV_PRF = 16) |                                    |  |  |  |  |

|-------------------------|------------------------------|----------------------------------------|------------------------------------|-----------------------------------------------------------------------|------------------------------------|--|--|--|--|

|                         |                              | TIME DURATION (µs)                     | REGISTER<br>SETTING <sup>(2)</sup> | TIME DURATION (µs)                                                    | REGISTER<br>SETTING <sup>(2)</sup> |  |  |  |  |

| PRF COUNTER             | PRPCT                        | 10000                                  | 39999 <sup>(3)</sup>               | 10000                                                                 | 2499 <sup>(3)</sup>                |  |  |  |  |

| LED2                    | LED2LEDSTC                   | 100                                    | 0                                  | 100                                                                   | 0                                  |  |  |  |  |

| LED2                    | LED2LEDENDC                  | 100                                    | 399                                | 100                                                                   | 24                                 |  |  |  |  |

|                         | LED2STC                      | 75                                     | 100                                | 70                                                                    | 7                                  |  |  |  |  |

| S <sub>LED2</sub>       | LED2ENDC                     | 75                                     | 399                                | 72                                                                    | 24                                 |  |  |  |  |

| ADCDCTO                 | ADCRSTSTCT0                  | 4.75                                   | 401                                | 4                                                                     | 26                                 |  |  |  |  |

| ADCRST0                 | ADCRSTENDCT0                 | 1.75                                   | 407                                | 4                                                                     | 26                                 |  |  |  |  |

| 20111/                  | LED2CONVST                   | 205                                    | 409                                | 000                                                                   | 28                                 |  |  |  |  |

| CONV <sub>LED2</sub>    | LED2CONVEND                  | 265                                    | 1468                               | 268                                                                   | 94                                 |  |  |  |  |

| LEDO                    | LED3LEDSTC                   | 400                                    | 401                                | 400                                                                   | 26                                 |  |  |  |  |

| LED3                    | LED3LEDENDC                  | 100                                    | 800                                | 100                                                                   | 50                                 |  |  |  |  |

|                         | ALED2STC\<br>LED3STC         | 75                                     | 501                                | 72                                                                    | 33                                 |  |  |  |  |

| S <sub>LED3</sub>       | ALED2ENDC\<br>LED3ENDC       | 75                                     | 800                                | 72                                                                    | 50                                 |  |  |  |  |

| ADCDCT4                 | ADCRSTSTCT1                  | 4.75                                   | 1470                               | 4                                                                     | 96                                 |  |  |  |  |

| ADCRST1                 | ADCRSTENDCT1                 | 1.75                                   | 1476                               | 4                                                                     | 96                                 |  |  |  |  |

| CONV                    | ALED2CONVST\<br>LED3CONVST   | 265                                    | 1478                               | 268                                                                   | 98                                 |  |  |  |  |

| CONV <sub>LED3</sub>    | ALED2CONVEND\<br>LED3CONVEND | 203                                    | 2537                               | 200                                                                   | 164                                |  |  |  |  |

| LED1                    | LED1LEDSTC                   | 100                                    | 802                                | 100                                                                   | 52                                 |  |  |  |  |

| LEDI                    | LED1LEDENDC                  | 100                                    | 1201                               | 100                                                                   | 76                                 |  |  |  |  |

| c                       | LED1STC                      | 75                                     | 902                                | 72                                                                    | 59                                 |  |  |  |  |

| S <sub>LED1</sub>       | LED1ENDC                     | 75                                     | 1201                               | 12                                                                    | 76                                 |  |  |  |  |

| ADCDST2                 | ADCRSTSTCT2                  | 1 75                                   | 2539                               | 4                                                                     | 166                                |  |  |  |  |

| ADCRST2                 | ADCRSTENDCT2                 | 1.75                                   | 2545                               | 4                                                                     | 166                                |  |  |  |  |

| CONIV                   | LED1CONVST                   | 2005                                   | 2547                               | 200                                                                   | 168                                |  |  |  |  |

| CONV <sub>LED1</sub>    | LED1CONVEND                  | 265                                    | 3606                               | 268                                                                   | 234                                |  |  |  |  |

| c                       | ALED1STC                     | 75                                     | 1303                               | 72                                                                    | 85                                 |  |  |  |  |

| S <sub>LED_AMB</sub>    | ALED1ENDC                    | /5                                     | 1602                               | 12                                                                    | 102                                |  |  |  |  |

| ADCDOTO                 | ADCRSTSTCT3                  | 4.75                                   | 3608                               |                                                                       | 236                                |  |  |  |  |

| ADCRST3                 | ADCRSTENDCT3                 | 1.75                                   | 3614                               | 4                                                                     | 236                                |  |  |  |  |

| CONV                    | ALED1CONVST                  | 265                                    | 3616                               | 269                                                                   | 238                                |  |  |  |  |

| CONV <sub>LED_AMB</sub> | ALED1CONVEND                 | 265                                    | 4675                               | 268                                                                   | 304                                |  |  |  |  |

| PDNCYCLE                | PDNCYCLESTC                  | 8431.25                                | 5475                               | 8384                                                                  | 354                                |  |  |  |  |

| IDINGIGLE               | PDNCYCLEENDC                 | 0431.23                                | 39199                              | 0304                                                                  | 2449                               |  |  |  |  |

<sup>(1)</sup> For signal names, see Figure 23.

(2) Time duration = (end count - start count + 1) / f<sub>TE</sub>.

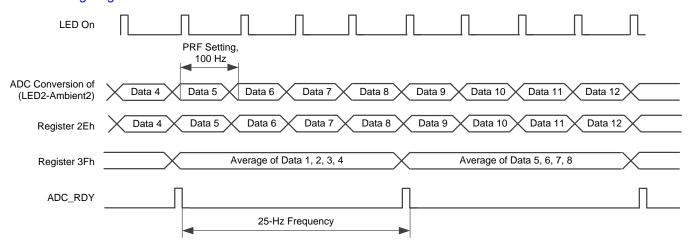

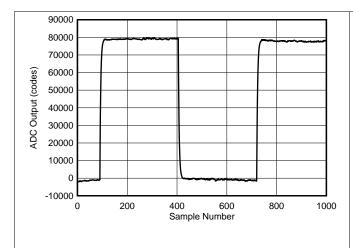

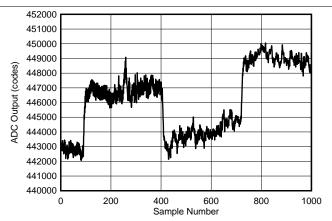

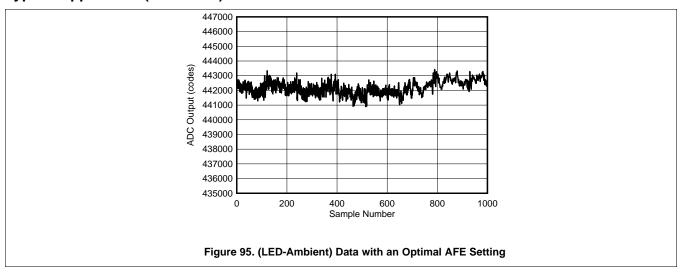

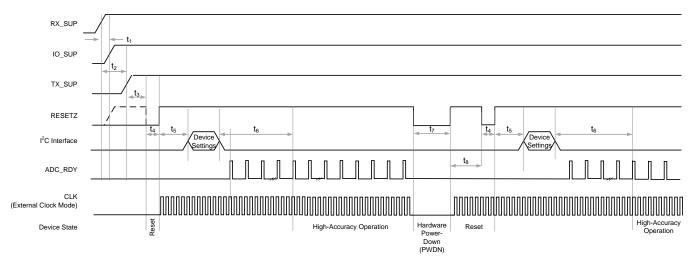

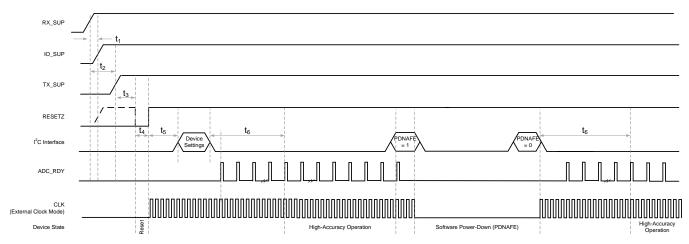

(3) For PRPCT, start count = 0.