# 10位,1每秒百万次采样(MSPS),8通道,单端,微功率,串口ADC

查询样品: ADS7955-Q1

### 特性

- 符合汽车应用要求

- 1MHz采样率串行器件

- 10位分辨率

- 零等待时间

- 20MHz串口

- 模拟电源范围: 2.7V至5.25V

- I/O电源范围: 1.7V至5.25V

- 2个SW可选单极,输入范围: 0至 2.5V 和 0至 5V

- 通道选择的自动和手动模式

- 8通道器件可共享16通道器件封装

- 每通道2个可编程警报级别

- 薄型小尺寸(TSSOP)封装器件的4个分别可配置通 用输入和输出接口(GPIO)

- 典型功率耗散值: 1MSPS下为14.5 mW (+VA = 5 V, +VBD = 3 V)

- 断电电流(1µA)

- 输入带宽(3db时为47MHz)

- · 30引脚TSSOP封装

#### 应用范围

- 可编程逻辑控制器(PLC)/进程间通信(IPC)

- 电池供电系统

- 医疗仪表

- 数字电源

- 触摸屏控制器

- 高速数据采集系统

- 高速闭合回路系统

#### 说明

ADS7955-Q1是一款10位多通道模数转换器。

此器件包括一个基于逐次逼近寄存器(SAR) A/D转换器的电容器,此转换器具有固有的采样和保持。

此器件接受宽范围的模拟电源电压(2.7V至5.25V)。 极低的功耗使得此器件适合于电池供电和独立电源供电 的应用。

1.7V至5.25V的宽电源电压范围使得无粘接接口与大多数广泛使用的CMOS数字主机间的连接更加便捷。

为了便于与微控制器和数字信号处理器(DSP)的连接, 此出口受CS和SCLK控制。

此输入信号在**CS**的下降边沿上进行采样。 它使用SCLK进行转换,串行数据输出,和读取串行数据。此器件可实现对预先选择的通道进行自动排序或者为下一个转换周期手工选择一个通道。

共有2个软件可选输入范围(0V - 2.5V 和 0V - 5V),4个独立配置的GPIO,和每个通道上的2个可编程警报阀值。 这些特性使得此器件适合于大多数数据采集应用。

此器件提供一个引人注意的断电特性。 当此器件运行 在较低转换速度时,此特性非常有助于节能。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

ZHCS622 – DECEMBER 2011 www.ti.com.cn

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

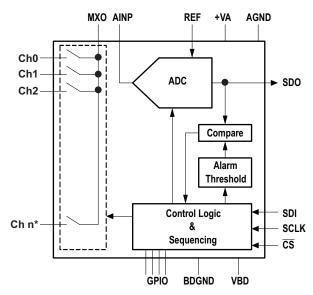

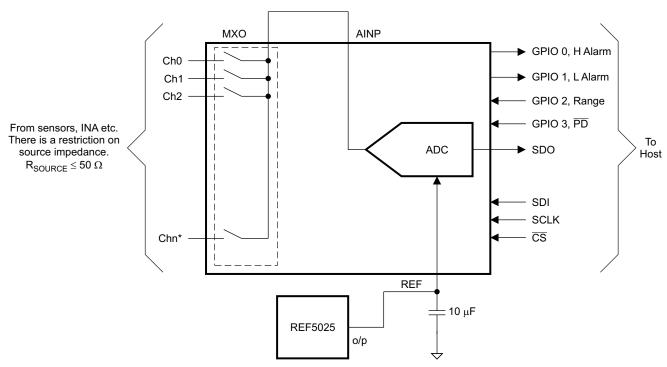

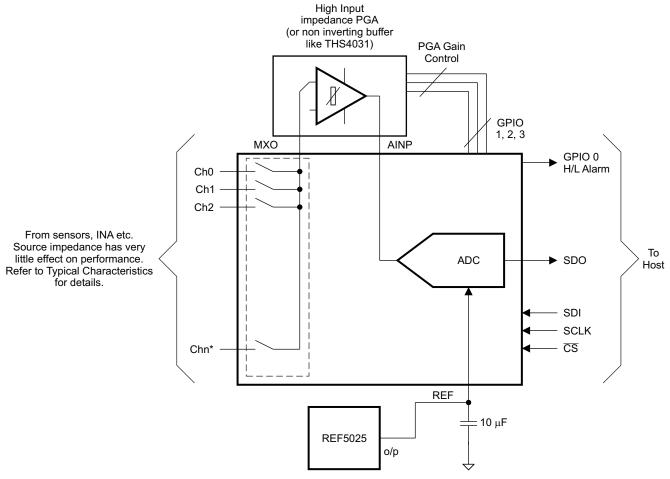

#### **ADS7955-Q1 BLOCK DIAGRAM**

NOTE: n\* is number of channels (16,12,8, or 4) depending on the device from the ADS79XX product family.

NOTE: 4 number of GPIO are available in TSSOP package device.

#### **ORDERING INFORMATION - 10-BIT**

| T <sub>A</sub> | LINEARITY (LSB) RESOLUTION (BIT) |      | NUMBER OF<br>CHANNELS | PACKAGE | ORDERABLE PART<br>NUMBER | TOP-SIDE MARKING |           |

|----------------|----------------------------------|------|-----------------------|---------|--------------------------|------------------|-----------|

| -40°C to 125°C | ±0.5                             | ±0.5 | 10                    | 8       | 30 pin TSSOP - DBT       | ADS7955QDBTRQ1   | ADS7955Q1 |

#### ABSOLUTE MAXIMUM RATINGS(1)

|                                                                       | VALUE                                                                | UNIT |

|-----------------------------------------------------------------------|----------------------------------------------------------------------|------|

| AINP or CHn to AGND                                                   | -0.3 to +VA +0.3                                                     | V    |

| +VA to AGND, +VBD to BDGND                                            | -0.3 to +7.0                                                         | V    |

| Digital input voltage to BDGND                                        | -0.3 to (7.0)                                                        | V    |

| Digital output to BDGND                                               | -0.3 to (+VA + 0.3)                                                  | V    |

| Operating temperature range                                           | -40 to 125                                                           | °C   |

| Storage temperature range                                             | -65 to 150                                                           | °C   |

| Junction temperature                                                  | 150                                                                  | °C   |

| Power dissipation                                                     | $(T_J Max-T_A)/\theta_{JA}$                                          |      |

| DBT packaged versions rated for MSL3 260C per JSTD-020 specifications |                                                                      |      |

| Human Body Model (HBM) ESD, Class H2 per Q100-002                     | 2                                                                    | kV   |

| Machine Model (MM) ESD, Class M2 per Q100-003                         | 200                                                                  | V    |

| Charged Device Model (CDM) ESD, Class C3B2 per Q100-011               | Maximum withstand voltage > 500 to ≤ to 750 V with corner pins > 750 | V    |

| Latch up (per JESD78)                                                 | Class I                                                              |      |

<sup>(1)</sup> Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

#### THERMAL INFORMATION

|                  |                                                             | ADS7955-Q1 |       |  |

|------------------|-------------------------------------------------------------|------------|-------|--|

|                  | THERMAL METRIC <sup>(1)</sup>                               | DBT        | UNITS |  |

|                  |                                                             | 30 PINS    |       |  |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 89.83      |       |  |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 22.94      |       |  |

| θ <sub>JB</sub>  | Junction-to-board thermal resistance (4)                    | 43.13      | 90.04 |  |

| ΨЈТ              | Junction-to-top characterization parameter <sup>(5)</sup>   | 0.77       | °C/W  |  |

| ΨЈВ              | Junction-to-board characterization parameter <sup>(6)</sup> | 42.52      |       |  |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | 22.94      |       |  |

- (1) 有关传统和新的热度量的更多信息,请参阅 IC 封装热度量 应用报告 SPRA953。

- (2) 在 JESD51-2a 描述的环境中,按照 JESD51-7 的指定在一个 JEDEC 标准 high-K 测试电路板上进行仿真,从而获得自然对流条件下的结 到外部热阻。

- (3) 通过在封装顶部进行冷板测试仿真来获得结到芯片外壳(顶部)热阻。 不存在特定的 JEDEC 标准测试,但可在 ANSI SEMI 标准 G30-88 中找到内容接近的说明。

- (4) 按照 JESD51-8 中的说明,通过在配有用于控制 PCB 温度的环形冷板夹具的环境中进行仿真,以获得结到电路板热阻。

- (5) 结到顶部的表征参数(Ψ<sub>JT</sub>)估算真实系统中器件的结温,并使用 JESD51-2a(第 6 章和第 7 章)中描述的程序从从得到 θ<sub>JA</sub>的仿真数据中 提取出该参数。

- (6) 结到电路板的表征参数 ( $ψ_{JB}$ ) 估算真实系统中器件的结温,并使用 JESD51-2a(第 6 章和第7 章)中描述的程序从从得到  $θ_{JA}$  的仿真数据中提取出该参数。

- (7) 通过在裸(电源)焊盘上进行冷板测试仿真来获得结到芯片外壳(底部)热阻。 不存在特定的 JEDEC 标准测试,但在 ANSI SEMI 标准 G30-88 中找到了内容接近的说明。

#### **ELECTRICAL CHARACTERISTICS**

+VA = 2.7 V to 5.25 V, +VBD = 1.7 V to 5.25 V,  $V_{ref}$  = 2.5 V  $\pm$  0.1 V,  $T_A$  = -40°C to 125°C,  $f_{sample}$  = 1 MHz (unless otherwise noted)

| PARAMETER                            | TEST CONDITIONS           | MIN   | TYP   | MAX           | UNIT               |

|--------------------------------------|---------------------------|-------|-------|---------------|--------------------|

| ANALOG INPUT                         |                           |       |       |               |                    |

| Full cools input appr (1)            | Range 1                   | 0     |       | Vref          | V                  |

| Full-scale input span <sup>(1)</sup> | Range 2 while 2Vref ≤ +VA | 0     |       | 2*Vref        | V                  |

| Aback to input range                 | Range 1                   | -0.20 |       | VREF<br>+0.20 | V                  |

| Absolute input range                 | Range 2 while 2Vref ≤ +VA | -0.20 | -0.20 |               | V                  |

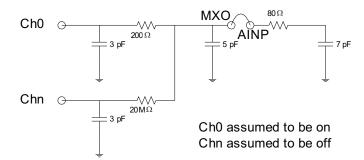

| Input capacitance                    |                           |       | 15    |               | ρF                 |

| Input leakage current                | $T_A = 125^{\circ}C$      |       | 61    |               | nA                 |

| SYSTEM PERFORMANCE                   |                           | •     |       | ,             |                    |

| Resolution                           |                           |       | 10    |               | Bits               |

| No missing codes                     |                           | 10    |       |               | Bits               |

| Integral linearity                   |                           | -0.5  | ±0.2  | 0.5           | LSB <sup>(2)</sup> |

| Differential linearity               |                           | -0.5  | ±0.2  | 0.5           | LSB                |

| Offset error <sup>(3)</sup>          |                           | -1.5  | ±0.5  | 1.5           | LSB                |

| Coin orror                           | Range 1                   | -1    | ±0.1  | 1             | LSB                |

| Gain error                           | Range 2                   |       | ±0.1  |               | LOD                |

| SAMPLING DYNAMICS                    |                           |       |       |               |                    |

| Conversion time                      | 20 MHz SCLK               |       |       | 800           | nSec               |

| Acquisition time                     |                           | 325   |       |               | nSec               |

| Maximum throughput rate              | 20 MHz SCLK               |       |       | 1.0           | MHz                |

| Aperture delay                       |                           |       | 5     |               | nsec               |

| Step response                        |                           |       | 150   |               | nsec               |

| Over voltage recovery                |                           |       | 150   |               | nsec               |

- (1) Ideal input span; does not include gain or offset error.

- (2) LSB means Least Significant Bit.

- (3) Measured relative to an ideal full-scale input

TEXAS INSTRUMENTS

ZHCS622 – DECEMBER 2011 www.ti.com.cn

## **ELECTRICAL CHARACTERISTICS (continued)**

+VA = 2.7 V to 5.25 V, +VBD = 1.7 V to 5.25 V,  $V_{ref}$  = 2.5 V  $\pm$  0.1 V,  $T_A$  = -40°C to 125°C,  $f_{sample}$  = 1 MHz (unless otherwise noted)

| PARA                                        | METER                 | TEST CONDITIONS                                                                                          | MIN        | TYP             | MAX  | UNIT    |

|---------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------|------------|-----------------|------|---------|

| DYNAMIC CHARA                               | CTERISTICS            |                                                                                                          |            |                 |      |         |

| Total harmonic dist                         | ortion <sup>(4)</sup> | 100 kHz                                                                                                  |            | -80             |      | dB      |

| Signal-to-noise ratio                       | )                     | 100 kHz                                                                                                  | 60         |                 |      | dB      |

| Signal-to-noise + di                        | stortion              | 100 kHz                                                                                                  | 60         |                 |      |         |

| Spurious free dynar                         | mic range             | 100 kHz                                                                                                  |            | 82              |      | dB      |

| Full power bandwid                          | lth                   | At –3 dB                                                                                                 |            | 47              |      | MHz     |

| Channel-to-channel crosstalk                |                       | Any off-channel with 100kHz, Full-scale input to channel being sampled with DC input.                    |            | <b>-</b> 95     |      |         |

|                                             |                       | From previously sampled to channel with 100kHz, Full-scale input to channel being sampled with DC input. |            | <del>-</del> 85 |      | dB      |

| EXTERNAL REFER                              | RENCE INPUT           |                                                                                                          |            |                 |      |         |

| V <sub>ref</sub> reference voltage at REFP  |                       |                                                                                                          | 2.0        | 2.5             | 3.0  | V       |

| Reference resistant                         | ce                    |                                                                                                          |            | 100             |      | kΩ      |

| ALARM SETTING                               |                       |                                                                                                          |            |                 |      |         |

| Higher threshold ra                         | nge                   |                                                                                                          | 000        |                 | FFC  | Hex     |

| Lower threshold range                       |                       |                                                                                                          | 000        |                 | FFC  | Hex     |

| DIGITAL INPUT/OU                            | UTPUT                 |                                                                                                          | *          |                 | ·    |         |

| Logic family                                |                       | CMOS                                                                                                     |            |                 |      |         |

|                                             | V <sub>IH</sub>       |                                                                                                          | 0.7*(+VBD) |                 |      |         |

|                                             | V <sub>IL</sub>       | +VBD = 5 V                                                                                               |            |                 | 0.8  |         |

| Logic level                                 | V <sub>IL</sub>       | +VBD = 3 V                                                                                               |            |                 | 0.4  | V       |

|                                             | V <sub>OH</sub>       | At I <sub>source</sub> = 200 μA                                                                          | Vdd-0.2    |                 |      |         |

|                                             | V <sub>OL</sub>       | At I <sub>sink</sub> = 200 μA                                                                            | 0.4        |                 |      |         |

| Data format MSB fi                          | rst                   |                                                                                                          | MSI        | B First         |      |         |

| POWER SUPPLY I                              | REQUIREMENTS          |                                                                                                          |            |                 | •    |         |

| +VA supply voltage                          | ı                     |                                                                                                          | 2.7        | 3.3             | 5.25 | V       |

| +VBD supply voltage                         | je                    |                                                                                                          | 1.7        | 3.3             | 5.25 | V       |

|                                             |                       | At +VA = 2.7 to 3.6 V and 1MHz throughput                                                                |            | 1.8             |      | mA      |

|                                             |                       | At +VA = 2.7 to 3.6 V static state                                                                       |            | 1.05            | 1    | mA      |

| Supply current (nor                         | mal mode)             | At +VA = 4.7 to 5.25 V and 1 MHz throughput                                                              |            | 2.3             | 3    | mA      |

|                                             |                       | At +VA = 4.7 to 5.25 V static state                                                                      |            | 1.1             | 1.5  | mA      |

| Power-down state supply current             |                       |                                                                                                          |            | 1               |      | μA      |

| +VBD supply current                         |                       | +VA = 5.25V, f <sub>s</sub> = 1MHz                                                                       |            | 1               |      | mA      |

| Power-up time                               |                       |                                                                                                          |            |                 | 1    | μSec    |

| Invalid conversions after power up or reset |                       |                                                                                                          |            |                 | 1    | Numbers |

| TEMPERATURE R                               | ANGE                  |                                                                                                          | •          |                 |      |         |

| Specified performar                         | nce                   |                                                                                                          | -40        |                 | 125  | °C      |

<sup>(4)</sup> Calculated on the first nine harmonics of the input frequency.

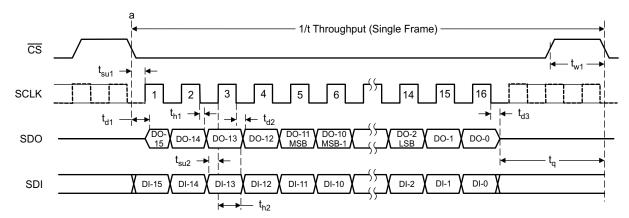

## TIMING REQUIREMENTS (see Figure 7 and Figure 8)

All specifications typical at -40°C to 125°C, +VA = 2.7 V to 5.25 V (unless otherwise specified)

|      | PARAMETER                                                                          | TEST CONDITIONS <sup>(1)</sup> (2) | MIN | TYP | MAX | UNIT       |  |  |  |  |  |

|------|------------------------------------------------------------------------------------|------------------------------------|-----|-----|-----|------------|--|--|--|--|--|

|      |                                                                                    | +VBD = 1.8 V                       |     |     | 16  |            |  |  |  |  |  |

| conv | Conversion time                                                                    | +VBD = 3 V                         |     |     | 16  | SCLK       |  |  |  |  |  |

|      |                                                                                    | +VBD = 5 V                         |     |     | 16  |            |  |  |  |  |  |

|      |                                                                                    | +VBD = 1.8 V                       | 40  |     |     |            |  |  |  |  |  |

| q    | Minimum quiet sampling time needed from bus<br>3-state to start of next conversion | +VBD = 3 V                         | 40  |     |     | ns         |  |  |  |  |  |

|      | o state to start of noxi conversion                                                | +VBD = 5 V                         | 40  |     |     |            |  |  |  |  |  |

|      |                                                                                    | +VBD = 1.8 V                       |     |     | 38  |            |  |  |  |  |  |

| d1   | Delay time, CS low to first data (DO-15) out                                       | +VBD = 3 V                         |     |     | 27  | ns         |  |  |  |  |  |

|      |                                                                                    | +VBD = 5 V                         |     |     | 17  |            |  |  |  |  |  |

|      |                                                                                    | +VBD = 1.8 V                       | 8   |     |     |            |  |  |  |  |  |

| su1  | Setup time, $\overline{\text{CS}}$ low to first rising edge of SCLK                | +VBD = 3 V                         | 6   |     |     | ns         |  |  |  |  |  |

|      |                                                                                    | +VBD = 5 V                         | 4   |     |     |            |  |  |  |  |  |

|      |                                                                                    | +VBD = 1.8 V                       |     |     | 35  |            |  |  |  |  |  |

| d2   | Delay time, SCLK falling to SDO next data bit valid                                | +VBD = 3 V                         |     |     | 27  | ns         |  |  |  |  |  |

|      |                                                                                    | +VBD = 5 V                         |     |     | 17  | +          |  |  |  |  |  |

|      |                                                                                    | +VBD = 1.8 V                       | 7   |     |     |            |  |  |  |  |  |

| h1   | Hold time, SCLK falling to SDO data bit valid                                      | +VBD = 3 V                         | 5   |     |     | ns         |  |  |  |  |  |

|      |                                                                                    | +VBD = 5 V                         | 3   |     |     |            |  |  |  |  |  |

|      |                                                                                    | +VBD = 1.8 V                       |     |     | 26  | <u>'</u> 6 |  |  |  |  |  |

| d3   | Delay time, 16 <sup>th</sup> SCLK falling edge to SDO 3-state                      | +VBD = 3 V                         |     |     | 22  | ns         |  |  |  |  |  |

|      |                                                                                    | +VBD = 5 V                         |     |     | 13  |            |  |  |  |  |  |

|      |                                                                                    | +VBD = 1.8 V                       | 2   |     |     | ns         |  |  |  |  |  |

| su2  | Setup time, SDI valid to rising edge of SCLK                                       | +VBD = 3 V                         | 3   |     |     |            |  |  |  |  |  |

|      |                                                                                    | +VBD = 5 V                         | 4   |     |     | 1          |  |  |  |  |  |

|      |                                                                                    | +VBD = 1.8 V                       | 12  |     |     |            |  |  |  |  |  |

| h2   | Hold time, rising edge of SCLK to SDI valid                                        | +VBD = 3 V                         | 10  |     |     | ns         |  |  |  |  |  |

|      |                                                                                    | +VBD = 5 V                         | 6   |     |     |            |  |  |  |  |  |

|      |                                                                                    | +VBD = 1.8 V                       | 20  |     |     |            |  |  |  |  |  |

| w1   | Pulse duration CS high                                                             | +VBD = 3 V                         | 20  |     |     | ns         |  |  |  |  |  |

|      | •                                                                                  | +VBD = 5 V                         |     |     |     |            |  |  |  |  |  |

|      |                                                                                    | +VBD = 1.8 V                       |     |     | 24  |            |  |  |  |  |  |

| d4   | Delay time CS high to SDO 3-state                                                  | +VBD = 3 V                         |     |     | 21  | ns         |  |  |  |  |  |

| ٠.   | , ,                                                                                | +VBD = 5 V                         |     |     | 12  |            |  |  |  |  |  |

|      |                                                                                    | +VBD = 1.8 V                       | 20  |     |     |            |  |  |  |  |  |

| wh   | Pulse duration SCLK high                                                           | +VBD = 3 V                         | 20  |     |     | ns         |  |  |  |  |  |

|      | Ç                                                                                  | +VBD = 5 V                         | 20  |     |     |            |  |  |  |  |  |

|      |                                                                                    | +VBD = 1.8 V                       | 20  |     |     |            |  |  |  |  |  |

| wl   | Pulse duration SCLK low                                                            | +VBD = 3 V                         | 20  |     |     | ns         |  |  |  |  |  |

| vv 1 |                                                                                    | +VBD = 5 V                         | 20  |     |     |            |  |  |  |  |  |

|      |                                                                                    | +VBD = 1.8 V                       |     |     | 20  |            |  |  |  |  |  |

|      | Frequency SCLK                                                                     | +VBD = 3 V                         |     |     | 20  | +          |  |  |  |  |  |

|      |                                                                                    | +VBD = 5 V                         |     | 20  |     |            |  |  |  |  |  |

<sup>(1) 1.8</sup>V specifications apply from 1.7V to 1.9V, 3V specifications apply from 2.7V to 3.6V, 5V specifications apply from 4.75V to 5.25V.(2) With 50-pF load

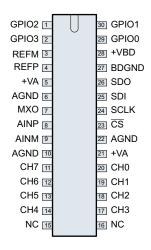

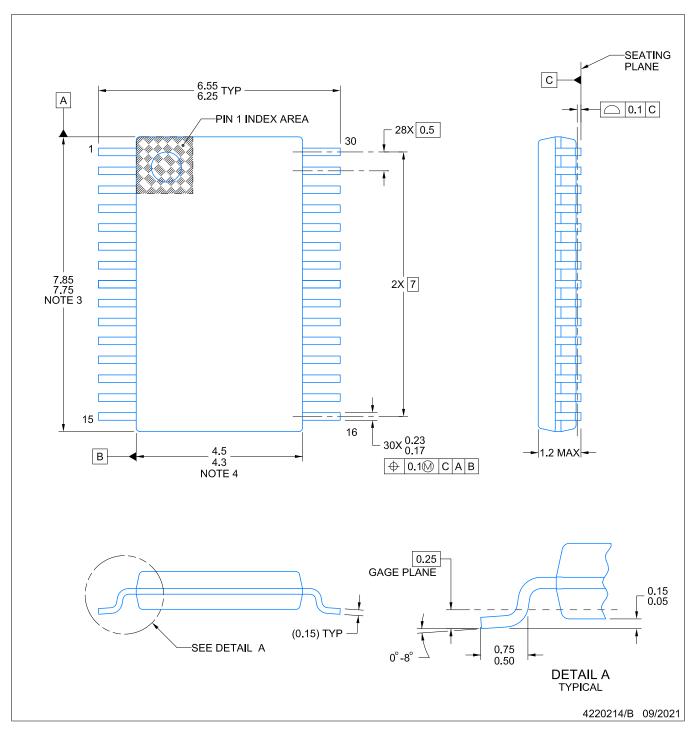

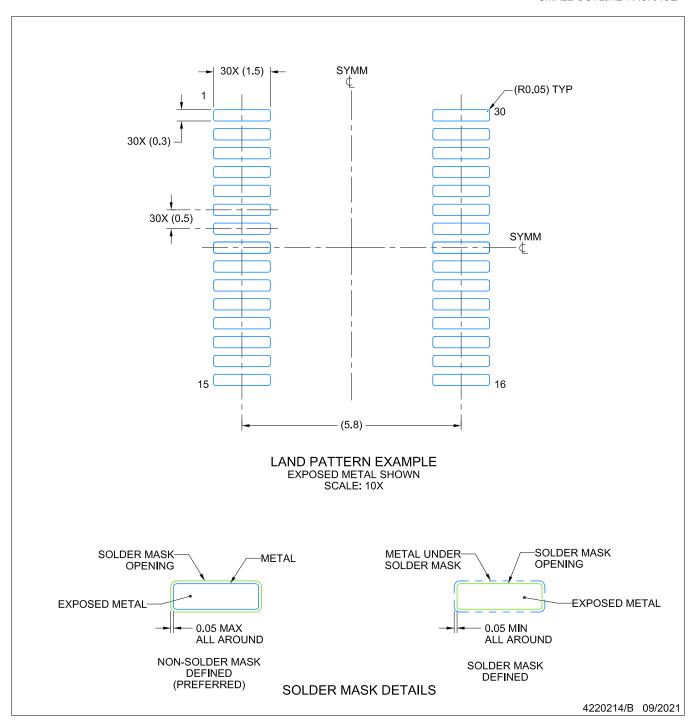

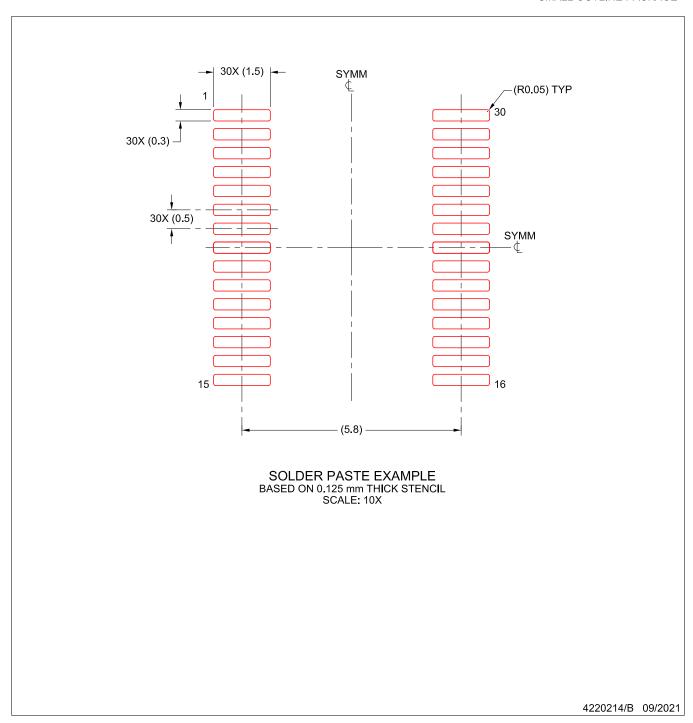

#### **DEVICE INFORMATION**

## **PIN CONFIGURATION (TOP VIEW)**

#### **TERMINAL FUNCTIONS - TSSOP PACKAGE**

|               |            |     | LI ONOTIONO - 10001 I AONAOL    |

|---------------|------------|-----|---------------------------------|

| DEVICE NAME   |            |     |                                 |

| ADS7955-Q1    | PIN NAME   | I/O | FUNCTION                        |

| PIN NO.       |            |     |                                 |

| REFERENCE     |            |     |                                 |

| 4             | REFP       | I   | Reference input                 |

| 3             | REFM       | 1   | Reference ground                |

| ADC ANALOG IN | IPUT       | ·   |                                 |

| 8             | AINP       | 1   | Signal input to ADC             |

| 9             | AINM       | I   | ADC input ground                |

| MULTIPLEXER   |            |     |                                 |

| 7             | MXO        | 0   | Multiplexer output              |

| 20            | Ch0        | 1   |                                 |

| 19            | Ch1        | 1   |                                 |

| 18            | Ch2        | I   |                                 |

| 17            | Ch3        | I   |                                 |

| 14            | Ch4        | I   |                                 |

| 13            | Ch5        | 1   |                                 |

| 12            | Ch6        | I   |                                 |

| 11            | Ch7        | I   | Analog channels for multiplayer |

| -             | Ch8        | I   | Analog channels for multiplexer |

| -             | Ch9        | 1   |                                 |

| -             | Ch10       | I   |                                 |

| -             | Ch11       | I   |                                 |

| -             | Ch12       | I   |                                 |

| -             | Ch13       | I   |                                 |

| -             | Ch14       | I   |                                 |

| -             | Ch15       | I   |                                 |

| DIGITAL CONTR | OL SIGNALS |     |                                 |

| 23            | <u>cs</u>  | I   | Chip select input               |

| 24            | SCLK       | I   | Serial clock input              |

| 25            | SDI        | I   | Serial data input               |

## **TERMINAL FUNCTIONS - TSSOP PACKAGE (continued)**

| DEVICE NAME              |                  |                  |                                                                                     |  |  |  |  |

|--------------------------|------------------|------------------|-------------------------------------------------------------------------------------|--|--|--|--|

| ADS7955-Q1               | PIN NAME         | I/O              | FUNCTION                                                                            |  |  |  |  |

| PIN NO.                  |                  |                  |                                                                                     |  |  |  |  |

| 26                       | SDO              | 0                | Serial data output                                                                  |  |  |  |  |

| GENERAL PURP programming | OSE INPUTS / OUT | PUTS: These pins | have programmable dual functionality. Refer to Table 8 for functionality            |  |  |  |  |

| 29                       | GPIO0            | I/O              | General purpose input or output                                                     |  |  |  |  |

|                          |                  | 0                | Active high output indicating high alarm or high/low alarm depending on programming |  |  |  |  |

| 30                       | GPIO1            | I/O              | General purpose input or output                                                     |  |  |  |  |

|                          | Low alarm        | 0                | Active high output indicating low alarm                                             |  |  |  |  |

| 1                        | GPIO2            | I/O              | General purpose input or output                                                     |  |  |  |  |

|                          | Range            | 1                | Selects range: High -> Range 2 / Low -> Range 1                                     |  |  |  |  |

| 2                        | GPIO3            | I/O              | General purpose input or output                                                     |  |  |  |  |

|                          | PD               | I                | Active low power down input                                                         |  |  |  |  |

| POWER SUPPLY             | AND GROUND       |                  |                                                                                     |  |  |  |  |

| 5, 21                    | +VA              | _                | Analog power supply                                                                 |  |  |  |  |

| 6, 10, 22                | AGND             |                  | Analog ground                                                                       |  |  |  |  |

| 28                       | +VBD             |                  | Digital I/O supply                                                                  |  |  |  |  |

| 27                       | BDGND            | _                | Digital ground                                                                      |  |  |  |  |

| NC PINS                  |                  |                  |                                                                                     |  |  |  |  |

| 15, 16                   | _                | _                | Pins internally not connected, do not float these pins                              |  |  |  |  |

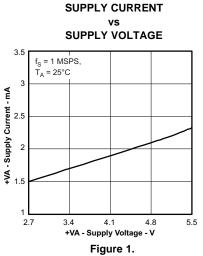

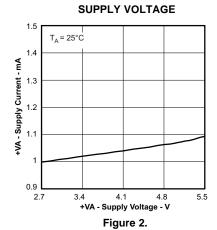

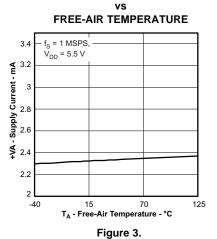

## TYPICAL CHARATERISTICS STATIC SUPPLY CURRENT

**SUPPLY CURRENT**

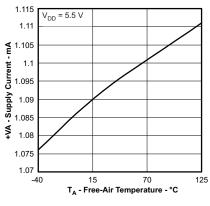

## STATIC SUPPLY CURRENT FREE-AIR TEMPERATURE

Figure 4.

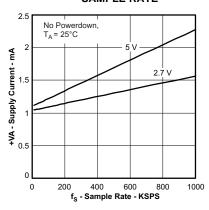

**SUPPLY CURRENT** SAMPLE RATE

Figure 5.

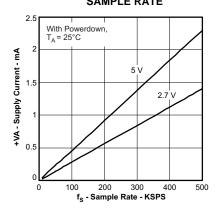

**SUPPLY CURRENT SAMPLE RATE**

Figure 6.

#### **DETAILED DESCRIPTION**

#### **DEVICE OPERATION**

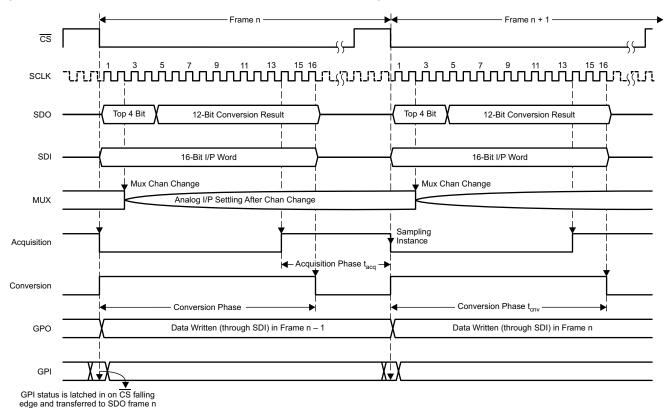

The ADS7955-Q1 is a 10-bit 8-channel device. Figure 7 and Figure 8 show device operation timing. Device operation is controlled with CS, SCLK, and SDI. The device outputs its data on SDO.

Figure 7. Device Operation Timing Diagram

Each frame begins with the falling edge of  $\overline{CS}$ . With the falling edge of  $\overline{CS}$ , the input signal from the selected channel is sampled, and the conversion process is initiated. The device outputs data while the conversion is in progress. The 16-bit data word contains a 4-bit channel address, followed by a 12-bit conversion result in MSB first format. There is an option to read the GPIO status instead of the channel address. (Refer to Table 1, Table 2, and Table 5 for more details.)

The device selects a new multiplexer channel on the second SCLK falling edge. The acquisition phase starts on the fourteenth SCLK rising edge. On the next  $\overline{\text{CS}}$  falling edge the acquisition phase will end, and the device starts a new frame.

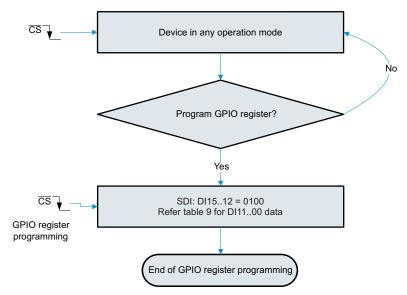

The TSSOP packaged device has four *General Purpose IO* (GPIO) pins, QFN versions have only one GPIO. These four pins can be individually programmed as GPO or GPI. It is also possible to use them for preassigned functions, refer to Table 10. GPO data can be written into the device through the SDI line. The device refreshes the GPO data on the CS falling edge as per the SDI data written in previous frame.

Similarly the device latches GPI status on the  $\overline{\text{CS}}$  falling edge and outputs the GPI data on the SDO line (if GPI read is enabled by writing DI04=1 in the previous frame) in the same frame starting with the  $\overline{\text{CS}}$  falling edge.

ZHCS622 – DECEMBER 2011 www.ti.com.cn

Figure 8. Serial Interface Timing Diagram for 10-Bit Devices

The falling edge of  $\overline{\text{CS}}$  clocks out DO-15 (first bit of the four bit channel address), and remaining address bits are clocked out on every falling edge of SCLK until the third falling edge. The conversion result MSB is clocked out on the 4th SCLK falling edge and LSB on the 15th/13th/11th falling edge respectively for the 10-bit device. On the 16th falling edge of SCLK, SDO goes to the 3-state condition. The conversion ends on the 16th falling edge of SCLK.

The device reads a sixteen bit word on the SDI pin while it outputs the data on the SDO pin. SDI data is latched on every rising edge of SCLK starting with the 1st clock as shown in Figure 8.

CS can be asserted (pulled high) only after 16 clocks have elapsed.

The device has two (high and low) programmable alarm thresholds per channel. If the input crosses these limits; the device flags out an alarm on GPIO0/GPIO1 depending on the GPIO program register settings (refer to Table 10). The alarm is asserted (under the alarm conditions) on the 12th falling edge of SCLK in the same frame when a data conversion is in progress. The alarm output is reset on the 10th falling edge of SCLK in the next frame.

The device offers a power-down feature to save power when not in use. There are two ways to powerdown the device. It can be powered down by writing DI05 = 1 in the mode control register (refer to Table 1, Table 2, and Table 5); in this case the device powers down on the 16th falling edge of SCLK in the next data frame. Another way to powerdown the device is through GPIO in the case of the TSSOP packaged device. GPIO3 can act as the  $\overline{PD}$  input (refer to Table 10, to assign this functionality to  $\overline{GPIO3}$ ). This is an asynchronous and active  $\overline{IOM}$  input. The device powers down instantaneously after  $\overline{GPIO3}$  ( $\overline{PD}$ ) = 0. The device will power up again on the  $\overline{CS}$  falling edge with DI05 = 0 in the mode control register and  $\overline{GPIO3}$  ( $\overline{PD}$ ) = 1.

#### **CHANNEL SEQUENCING MODES**

There are three modes for channel sequencing, namely *Manual mode*, *Auto-1 mode*, *Auto-2 mode*. Mode selection is done by writing into the *control register* (refer to Table 1, Table 2, and Table 5). A new multiplexer channel is selected on the second falling edge of SCLK (as shown in Figure 7) in all three modes.

**Manual mode:** When configured to operate in Manual mode, the next channel to be selected is programmed in each frame and the device selects the programmed channel in the next frame. On powerup or after reset the default channel is 'Channel-0' and the device is in Manual mode.

**Auto-1 mode:** In this mode the device scans pre-programmed channels in ascending order. A new multiplexer channel is selected every frame on the second falling edge of SCLK. There is a separate 'program register' for pre-programming the channel sequence. Table 3 and Table 4 show Auto-1 'program register' settings.

Once programmed the device retains 'program register' settings until the device is powered down, reset, or reprogrammed. It is allowed to exit and re-enter the Auto-1 mode any number of times without disturbing 'program register' settings.

The Auto-1 program register is reset to FFFF/FF/F hex for the 8 channel device upon device powerup or reset; implying the device scans all channels in ascending order.

**Auto-2 mode:** In this mode the user can configure the program register to select the last channel in the scan sequence. The device scans all channels from channel 0 up to and including the last channel in ascending order. The multiplexer channel is selected every frame on the second falling edge of SCLK. There is a separate 'program register' for pre-programming of the last channel in the sequence (multiplexer depth). Table 6 lists the 'Auto-2 prog' register settings for selection of the last channel in the sequence.

Once programmed the device retains program register settings until the device is powered down, reset, or reprogrammed. It is allowed to exit and re-enter Auto-2 mode any number of times, without disturbing the 'program register' settings.

On powerup or reset the bits D9-D6 of the Auto-2 program register are reset to 7 hex for the 8 channel device; implying the device scans all channels in ascending order.

#### **DEVICE PROGRAMMING AND MODE CONTROL**

The following section describes device programming and mode control. These devices feature two types of registers to configure and operate the devices in different modes. These registers are referred as 'Configuration Registers'. There are two types of 'Configuration Registers' namely 'Mode control registers' and 'Program registers'.

#### **Mode Control Register**

A 'Mode control register' is configured to operate the device in one of three channel sequencing modes, namely Manual mode, Auto-1 Mode, Auto-2 Mode. It is also used to control user programmable features like range selection, device power-down control, GPIO read control, and writing output data into the GPIO.

#### **Program Registers**

The 'Program registers' are used for device configuration settings and are typically programmed once on powerup or after device reset. There are different program registers such as 'Auto-1 mode programming' for pre-programming the channel sequence, 'Auto-2 mode programming' for selection of the last channel in the sequence, 'Alarm programming' for all 16 channels (8 channels) and GPIO for individual pin configuration as GPI or GPO or a pre-assigned function.

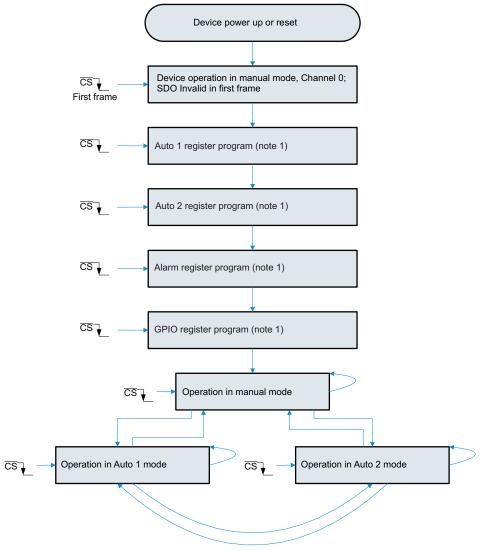

#### **DEVICE POWER-UP SEQUENCE**

The device power-up sequence is shown in Figure 9. Manual mode is the default power-up channel sequencing mode and Channel-0 is the first channel by default. As explained previously, these devices offer Program Registers to configure user programmable features like GPIO, Alarm, and to pre-program the channel sequence for Auto modes. At 'powerup or on reset' these registers are set to the default values listed in Table 1 to Table 10. It is recommended to program these registers on powerup or after reset. Once configured; the device is ready to use in any of the three channel sequencing modes namely Manual, Auto-1, and Auto-2.

- (1) The device continues its operation in Manual mode channel 0 through out the programming sequence and outputs valid conversion results. It is possible to change channel, range, GPIO by inserting extra frames in between two programming blocks. It is also possible to bypass any programming block if the user does not intent to use that feature.

- (2) It is possible to reprogram the device at any time during operation, regardless of what mode the device is in. During programming the device continues its operation in whatever mode it is in and outputs valid data.

Figure 9. Device Power-Up Sequence

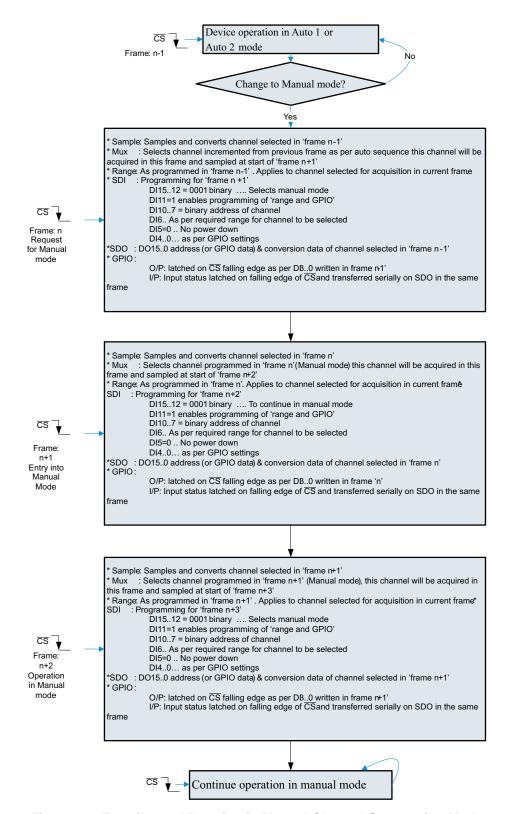

#### **OPERATING IN MANUAL MODE**

The details regarding entering and running in Manual channel sequencing mode are illustrated in Figure 10. Table 1 lists the Mode Control Register settings for Manual mode in detail. Note that there are no Program Registers for manual mode.

ZHCS622 - DECEMBER 2011

Figure 10. Entering and Running in Manual Channel Sequencing Mode

www.ti.com.cn

ZHCS622 - DECEMBER 2011

## Table 1. Mode Control Register Settings for Manual Mode

|         | DECET          |      |                                                 | DESCRIPTION                                                                                                                                                 |                      |                        |  |  |  |  |  |  |

|---------|----------------|------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------|--|--|--|--|--|--|

| BITS    | RESET<br>STATE | ON   |                                                 |                                                                                                                                                             |                      |                        |  |  |  |  |  |  |

| DI15-12 | 0001           | 0001 | Selects Manual Mode                             | cts Manual Mode                                                                                                                                             |                      |                        |  |  |  |  |  |  |

| DI11    | 0              | 1    | Enables programming of                          | ables programming of bits DI06-00.                                                                                                                          |                      |                        |  |  |  |  |  |  |

|         |                | 0    | Device retains values of                        | DI06-00 from the previous from                                                                                                                              | ame.                 |                        |  |  |  |  |  |  |

| DI10-07 | 0000           |      |                                                 | ata represents the address of the next channel to be selected in the next frame. DI10: MSB and . 0000 represents channel- 0, 0001 represents channel-1 etc. |                      |                        |  |  |  |  |  |  |

| DI06    | 0              | 0    | Selects 2.5V i/p range (F                       | Range 1)                                                                                                                                                    |                      |                        |  |  |  |  |  |  |

|         |                | 1    | Selects 5V i/p range (Ra                        | inge 2)                                                                                                                                                     |                      |                        |  |  |  |  |  |  |

| DI05    | 0              | 0    | Device normal operation                         |                                                                                                                                                             |                      |                        |  |  |  |  |  |  |

|         |                | 1    | Device powers down on                           | 16th SCLK falling edge                                                                                                                                      |                      |                        |  |  |  |  |  |  |

| DI04    | 0              | 0    | SDO outputs current charesult on DO1100.        | outputs current channel address of the channel on DO1512 followed by 12 bit conversion It on DO1100.                                                        |                      |                        |  |  |  |  |  |  |

|         |                | 1    | GPIO3-GPIO0 data (bot<br>Lower data bits DO11-D |                                                                                                                                                             |                      |                        |  |  |  |  |  |  |

|         |                |      | DOI5                                            | DOI4                                                                                                                                                        | DOI3                 | DOI2                   |  |  |  |  |  |  |

|         |                |      | GPIO3 <sup>(1)</sup>                            | GPIO2 <sup>(1)</sup>                                                                                                                                        | GPIO1 <sup>(1)</sup> | GPIO0 <sup>(1)</sup>   |  |  |  |  |  |  |

| DI03-00 | 0000           |      |                                                 | d as output. Device will ignor                                                                                                                              |                      | el which is configured |  |  |  |  |  |  |

|         |                |      | DI03                                            | DI02                                                                                                                                                        | DI01                 | DI00                   |  |  |  |  |  |  |

|         |                |      | GPIO3 <sup>(2)</sup>                            | GPIO2 <sup>(2)</sup>                                                                                                                                        | GPIO1 <sup>(2)</sup> | GPIO0 <sup>(2)</sup>   |  |  |  |  |  |  |

<sup>(1)</sup> GPIO 1 to 3 are available only in TSSOP packaged devices. QFN device offers GPIO 0 only.(2) GPIO 1 to 3 are available only in TSSOP packaged devices. QFN device offers GPIO 0 only.

#### **OPERATING IN AUTO-1 MODE**

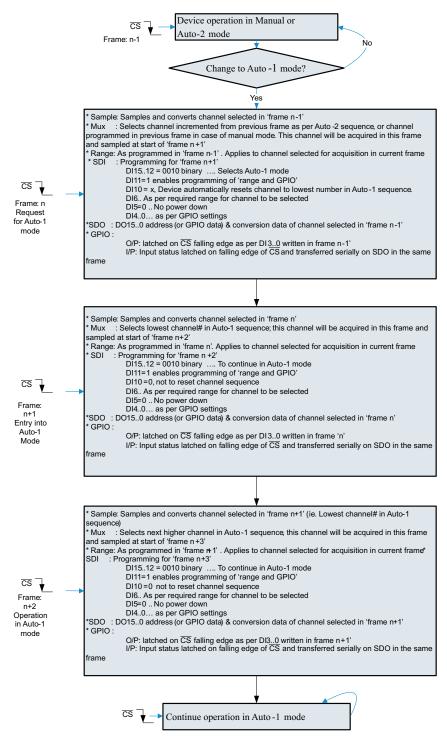

The details regarding entering and running in Auto-1 channel sequencing mode are illustrated in the flowchart in Figure 11. Table 2 lists the Mode Control Register settings for Auto-1 mode in detail.

Figure 11. Entering and Running in Auto-1 Channel Sequencing Mode

## Table 2. Mode Control Register Settings for Auto-1 Mode

|         | DEGET          |                |                                                                                                                                                                    | DESCRIPTION                                               |                           |                      |  |  |  |  |  |  |

|---------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------|----------------------|--|--|--|--|--|--|

| BITS    | RESET<br>STATE | LOGIC<br>STATE |                                                                                                                                                                    | FUNCTION                                                  |                           |                      |  |  |  |  |  |  |

| DI15-12 | 0001           | 0010           | Selects Auto-1 Mode                                                                                                                                                | Selects Auto-1 Mode                                       |                           |                      |  |  |  |  |  |  |

| DI11    | 0              | 1              | Enables programming of                                                                                                                                             | ables programming of bits DI10-00.                        |                           |                      |  |  |  |  |  |  |

|         |                | 0              | Device retains values of I                                                                                                                                         | DI10-00 from previous frame                               | е.                        |                      |  |  |  |  |  |  |

| DI10    | 0              | 1              | The channel counter is re                                                                                                                                          | eset to the lowest programm                               | ned channel in the Auto-1 | Program Register     |  |  |  |  |  |  |

|         |                | 0              | The channel counter incre                                                                                                                                          | ements every conversion (N                                | lo reset)                 |                      |  |  |  |  |  |  |

| DI09-07 | 000            | xxx            | Do not care                                                                                                                                                        |                                                           |                           |                      |  |  |  |  |  |  |

| DI06    | 0              | 0              | Selects 2.5V i/p range (R                                                                                                                                          | Selects 2.5V i/p range (Range 1)                          |                           |                      |  |  |  |  |  |  |

|         |                | 1              | Selects 5V i/p range (Ran                                                                                                                                          | nge 2)                                                    |                           |                      |  |  |  |  |  |  |

| DI05    | 0              | 0              | Device normal operation                                                                                                                                            | (no powerdown)                                            |                           |                      |  |  |  |  |  |  |

|         |                | 1              | Device powers down on t                                                                                                                                            | he 16th SCLK falling edge                                 |                           |                      |  |  |  |  |  |  |

| DI04    | 0              | 0              | SDO outputs current charresult on DO1100.                                                                                                                          | nnel address of the channel                               | on DO1512 followed by     | 12-bit conversion    |  |  |  |  |  |  |

|         |                | 1              |                                                                                                                                                                    | input and output) is mappe<br>000 represent 12-bit conver |                           |                      |  |  |  |  |  |  |

|         |                |                | DO15                                                                                                                                                               | DO14                                                      | DO13                      | DO12                 |  |  |  |  |  |  |

|         |                |                | GPIO3 <sup>(1)</sup>                                                                                                                                               | GPIO2 <sup>(1)</sup>                                      | GPIO1 <sup>(1)</sup>      | GPIO0 <sup>(1)</sup> |  |  |  |  |  |  |

| DI03-00 | 0000           |                | a for the channels configured as output. Device will ignore the data for the channel which is configured SDI bit and corresponding GPIO information is given below |                                                           |                           |                      |  |  |  |  |  |  |

|         |                |                | DI03                                                                                                                                                               | DI02                                                      | DI01                      | DI00                 |  |  |  |  |  |  |

|         |                |                | GPIO3 <sup>(2)</sup>                                                                                                                                               | GPIO2 <sup>(2)</sup>                                      | GPIO1 (2)                 | GPIO0 <sup>(2)</sup> |  |  |  |  |  |  |

<sup>(1)</sup> GPIO 1 to 3 are available only in TSSOP packaged devices. QFN device offers GPIO 0 only.

(2) GPIO 1 to 3 are available only in TSSOP packaged devices. QFN device offers GPIO 0 only.

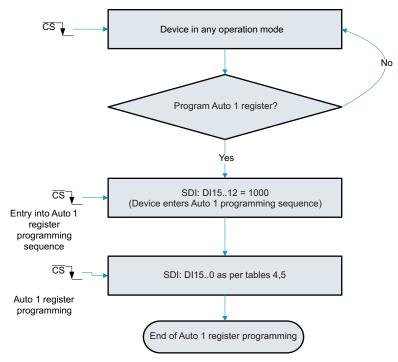

The Auto-1 Program Register is programmed (once on powerup or reset) to pre-select the channels for the Auto-1 sequence. Auto-1 Program Register programming requires two  $\overline{CS}$  frames for complete programming. In the first  $\overline{CS}$  frame the device enters the Auto-1 register programming sequence and in the second frame it programs the Auto-1 Program Register. Refer to Table 2, Table 3, and Table 4 for complete details.

NOTE: The device continues its operation in selected mode during programming. SDO is valid, however it is not possible to change the range or write GPIO data into the device during programming.

Figure 12. Auto-1 Register Programming Flowchart

Table 3. Program Register Settings for Auto-1 Mode

| DITC    | RESET  | DESCRIPTION        |                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

|---------|--------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| BITS    | STATE  | LOGIC STATE        | FUNCTION                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

| FRAME 1 | •      | •                  |                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| DI15-12 | NA     | 1000               | Device enters Auto-1 program sequence. Device programming is done in the next frame.                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| DI11-00 | NA     | Do not care        | not care                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

| FRAME 2 |        |                    |                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| DI15-00 | All 1s | 1 (individual bit) | A particular channel is programmed to be selected in the channel scanning sequence. The channel numbers are mapped one-to-one with respect to the SDI bits; e.g. DI15 $\rightarrow$ Ch15, DI14 $\rightarrow$ Ch14 DI00 $\rightarrow$ Ch00 |  |  |  |  |  |  |  |  |  |

|         |        | 0 (individual bit) | A particular channel is programmed to be skipped in the channel scanning sequence. The channel numbers are mapped one-to-one with respect to the SDI bits; e.g. DI15 $\rightarrow$ Ch15, DI14 $\rightarrow$ Ch14 DI00 $\rightarrow$ Ch00  |  |  |  |  |  |  |  |  |  |

**Table 4. Mapping of Channels to SDI Bits**

| Daviss (1)            |      |      |      |      |      |      |      | SD   | BITS |      |      |      |      |      |      |      |

|-----------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| Device <sup>(1)</sup> | DI15 | DI14 | DI13 | DI12 | DI11 | DI10 | DI09 | DI08 | DI07 | DI06 | DI05 | DI04 | DI03 | DI02 | DI01 | DI00 |

| 8 Chan                | Χ    | Х    | Χ    | Х    | Х    | Х    | Х    | Х    | 1/0  | 1/0  | 1/0  | 1/0  | 1/0  | 1/0  | 1/0  | 1/0  |

(1) When operating in Auto-1 mode, the device only scans the channels programmed to be selected.

ZHCS622 – DECEMBER 2011 www.ti.com.cn

#### **OPERATING IN AUTO-2 MODE**

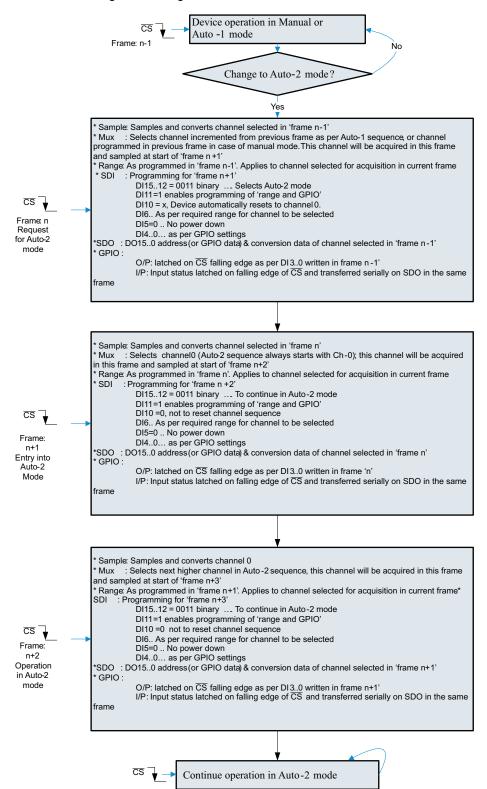

The details regarding entering and running in Auto-2 channel sequencing mode are illustrated in Figure 13. Table 5 lists the Mode Control Register settings for Auto-2 mode in detail.

Figure 13. Entering and Running in Auto-2 Channel Sequencing Mode

Table 5. Mode Control Register Settings for Auto-2 Mode

|         | DEGET          | DESCRIPTION    |                                                                                                                      |                                                            |                      |                                                          |      |                                                   |      |  |

|---------|----------------|----------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------|----------------------------------------------------------|------|---------------------------------------------------|------|--|

| BITS    | RESET<br>STATE | LOGIC<br>STATE | FUNCTION                                                                                                             |                                                            |                      |                                                          |      |                                                   |      |  |

| DI15-12 | 0001           | 0011           | Selects Auto-2 Mode                                                                                                  |                                                            |                      |                                                          |      |                                                   |      |  |

| DI11    | 0              | 1              | Enables programming                                                                                                  | Enables programming of bits DI10-00.                       |                      |                                                          |      |                                                   |      |  |

|         |                | 0              | Device retains values                                                                                                | of DI10-00 from the previou                                | us frame.            |                                                          |      |                                                   |      |  |

| DI10    | 0              | 1              | Channel number is res                                                                                                | set to Ch-00.                                              |                      |                                                          |      |                                                   |      |  |

|         |                | 0              | Channel counter incre                                                                                                | ments every conversion.(N                                  | o reset).            |                                                          |      |                                                   |      |  |

| DI09-07 | 000            | xxx            | Do not care                                                                                                          |                                                            |                      |                                                          |      |                                                   |      |  |

| DI06    | 0              | 0              | Selects 2.5V i/p range (Range 1)                                                                                     |                                                            |                      |                                                          |      |                                                   |      |  |

|         |                | 1              | Selects 5V i/p range (Range 2)                                                                                       |                                                            |                      |                                                          |      |                                                   |      |  |

| DI05    | 0              | 0              | Device normal operation (no powerdown)                                                                               |                                                            |                      |                                                          |      |                                                   |      |  |

|         |                | 1              | Device powers down of                                                                                                | lge                                                        |                      |                                                          |      |                                                   |      |  |

| DI04    | 0              | 0              | SDO outputs the current channel address of the channel on DO1512 followed by the 12-bit conversion result on DO1100. |                                                            |                      |                                                          |      |                                                   |      |  |

|         |                |                |                                                                                                                      | 1                                                          |                      | oth input and output) is ma<br>DO00 represent the 12-bit |      | 12 in the order shown below. the current channel. |      |  |

|         |                |                |                                                                                                                      |                                                            |                      | DO15                                                     | DO14 | DO13                                              | DO12 |  |

|         |                |                | GPIO3 <sup>(1)</sup>                                                                                                 | GPIO2 <sup>(1)</sup>                                       | GPIO1 <sup>(1)</sup> | GPIO0 <sup>(1)</sup>                                     |      |                                                   |      |  |

| DI03-00 | 0000           |                |                                                                                                                      | ired as output. Device igno<br>PIO information is given be |                      | nel which is configured as                               |      |                                                   |      |  |

|         |                |                | DI03                                                                                                                 | DI02                                                       | DI01                 | DI00                                                     |      |                                                   |      |  |

|         |                |                | GPIO3 <sup>(1)</sup>                                                                                                 | GPIO2 <sup>(1)</sup>                                       | GPIO1 <sup>(1)</sup> | GPIO0 <sup>(1)</sup>                                     |      |                                                   |      |  |

<sup>(1)</sup> GPIO 1 to 3 are available only in TSSOP packaged devices. QFN device offers GPIO 0 only.

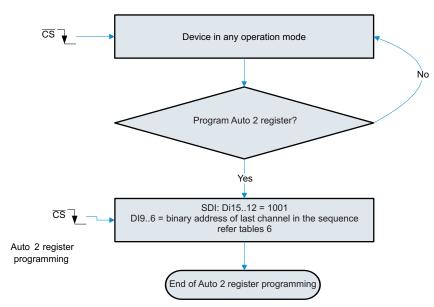

The Auto-2 Program Register is programmed (once on powerup or reset) to pre-select the last channel (or sequence depth) in the Auto-2 sequence. Unlike Auto-1 Program Register programming, Auto-2 Program Register programming requires only 1  $\overline{\text{CS}}$  frame for complete programming. See Figure 14 and Table 6 for complete details.

NOTE: The device continues its operation in the selected mode during programming. SDO is valid, however it is not possible to change the range or write GPIO data into the device during programming.

Figure 14. Auto-2 Register Programming Flowchart

#### Table 6. Program Register Settings for Auto-2 Mode

| BITS    | RESET<br>STATE | DESCRIPTION    |                                                                                                                                                                                                                                                                                |  |  |  |

|---------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|         |                | LOGIC<br>STATE | FUNCTION                                                                                                                                                                                                                                                                       |  |  |  |

| DI15-12 | NA             | 1001           | 1001 Auto-2 program register is selected for programming                                                                                                                                                                                                                       |  |  |  |

| DI11-10 | NA             | Do not care    |                                                                                                                                                                                                                                                                                |  |  |  |

| DI09-06 | NA             | aaaa           | This 4-bit data represents the address of the last channel in the scanning sequence. During device operation in Auto-2 mode, the channel counter starts at CH-00 and increments every frame until it equals "aaaa". The channel counter roles over to CH-00 in the next frame. |  |  |  |

| DI05-00 | NA             | Do not care    |                                                                                                                                                                                                                                                                                |  |  |  |

#### **CONTINUED OPERATION IN A SELECTED MODE**

Once a device is programmed to operate in one of the modes, the user may want to continue operating in the same mode. Mode Control Register settings to continue operating in a selected mode are detailed in Table 7.

Table 7. Continued Operation in a Selected Mode

|                                                                                                                                                                                                              | RESET<br>STATE | DESCRIPTION                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| BITS                                                                                                                                                                                                         |                | LOGIC<br>STATE                                                    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| DI15-12 0001 The device continues to operate in the selected counter increments normally, whereas in the Ma channel. The device ignores data on DI11-DI00 settings. This feature is provided so that SDI car |                | 0000                                                              | The device continues to operate in the selected mode. In Auto-1 and Auto-2 modes the channel counter increments normally, whereas in the Manual mode it continues with the last selected channel. The device ignores data on DI11-DI00 and continues operating as per the previous settings. This feature is provided so that SDI can be held low when no changes are required in the Mode Control Register settings. |  |  |  |

| DI11-00                                                                                                                                                                                                      | All '0'        | Device ignores these bits when DI15-12 is set to 0000 logic state |                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

#### PROGRAMMING ALARM THRESHOLDS

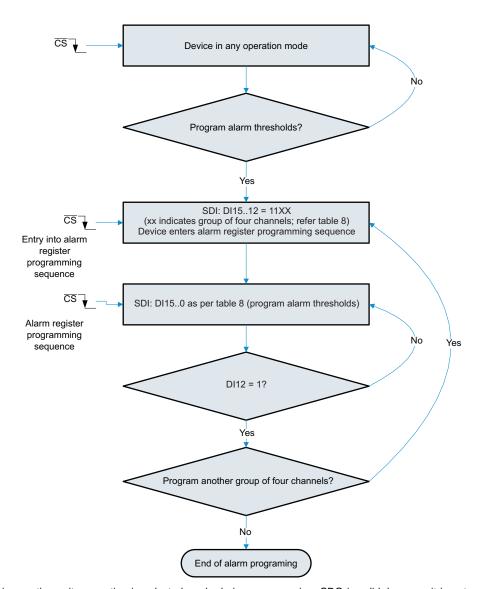

There are two Alarm Program Registers per channel, one for setting the high alarm threshold and the other for setting the low alarm threshold. For ease of programming, two alarm programming registers per channel, corresponding to four consecutive channels, are assembled into one group (a total eight registers). There are four such groups for 16 channel devices and 3/2/1 such groups for 12/8/4 channel devices respectively. The grouping of the various channels for each device in the ADS7955-Q1 is listed in Table 8. The details regarding programming the alarm thresholds are illustrated in the flowchart in Figure 15. Table 9 lists the details regarding the Alarm Program Register settings.

**Table 8. Grouping of Alarm Program Registers**

| GROUP NO. | REGISTERS                                     |

|-----------|-----------------------------------------------|

| 0         | High and low alarm for channel 0, 1, 2, and 3 |

| 1         | High and low alarm for channel 4, 5, 6, and 7 |

Each alarm group requires 9  $\overline{\text{CS}}$  frames for programming their respective alarm thresholds. In the first frame the device enters the programming sequence and in each subsequent frame it programs one of the registers from the group. The device offers a feature to program less than eight registers in one programming sequence. The device exits the alarm threshold programming sequence in the next frame after it encounters the first 'Exit Alarm Program' bit high.

NOTE: The device continues its operation in selected mode during programming. SDO is valid, however it is not possible to change the range or write GPIO data into the device during programming.

Figure 15. Alarm Program Register Programming Flowchart

**Table 9. Alarm Program Register Settings**

|                   |                      | DESCRIPTION    |                                                                                               |  |  |  |  |  |

|-------------------|----------------------|----------------|-----------------------------------------------------------------------------------------------|--|--|--|--|--|

| BITS              | RESET STATE          | LOGIC<br>STATE | FUNCTION                                                                                      |  |  |  |  |  |

| FRAME 1           |                      |                |                                                                                               |  |  |  |  |  |

| DI15-12           | NA                   | 1100           | Device enters 'alarm programming sequence' for group 0                                        |  |  |  |  |  |

|                   |                      | 1101           | Device enters 'alarm programming sequence' for group 1                                        |  |  |  |  |  |

|                   |                      | 1110           | Device enters 'alarm programming sequence' for group 2                                        |  |  |  |  |  |

|                   |                      | 1111           | Device enters 'alarm programming sequence' for group 3                                        |  |  |  |  |  |