**ADS7138**

ZHCSJS8-MAY 2019

# ADS7138 小型 8 通道 12 位 ADC, 具有 I<sup>2</sup>C 接口、GPIO 和 CRC

## 1 特性

- 小封装尺寸:

- 3mm × 3mm WQFN

- 8 通道,可配置为以下任意组合:

- 最多8个模拟输入、数字输入或数字输出

- 用于 I/O 扩展的 GPIO:

- 开漏、推挽数字输出

- 模拟监控:

- 每个通道的可编程阈值

- 用于瞬态抑制的事件计数器

- 宽工作范围:

- AVDD: 2.35V 至 5.5V

- DVDD: 1.65V 至 5.5V

- 温度范围: -40°C 至 +125°C

- 用于读取/写入操作的 CRC:

- 数据读取/写入 CRC

- 上电配置 CRC

- I<sup>2</sup>C 接口:

- 高达 3.4MHz (高速)

- 8 个可配置 I<sup>2</sup>C 地址

- 可编程均值滤波器:

- 用于求平均值的可编程样本大小

- 利用内部转换求平均值

#### 用于计算平均输出的 16 位分辨率

#### 2 应用

- 监控功能

- 便携式仪表

- 电信基础设施

- 电源监控

# 3 说明

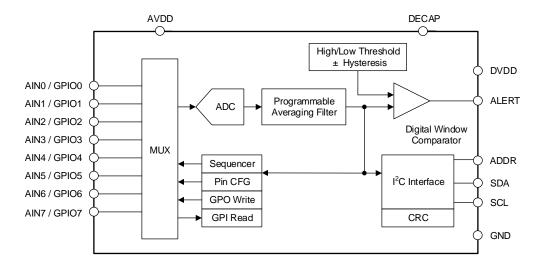

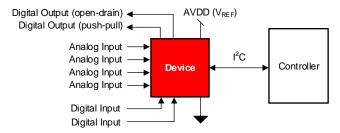

ADS7138 是一款易于使用的 8 通道多路复用 12 位逐次逼近寄存器模数转换器 (SAR ADC)。8 个通道可独立配置为模拟输入、数字输入或数字输出。该器件具有一个用于执行 ADC 转换过程的内部振荡器。

ADS7138 通过兼容 I<sup>2</sup>C 的接口进行通信,可以在自主或单冲转换模式下运行。ADS7138 使用具有可编程高低阈值、迟滞和事件计数器的数字窗口比较器,通过每通道事件触发的中断来实施模拟监控功能。ADS7138 具有用于数据读取/写入操作和上电配置的内置循环冗余校验 (CRC) 功能。

#### 器件信息<sup>(1)</sup>

| 部件名称    | 封装        | 封装尺寸 (标称值)      |

|---------|-----------|-----------------|

| ADS7138 | WQFN (16) | 3.00mm × 3.00mm |

<sup>(1)</sup> 如需了解所有可用封装,请见数据表末尾的可订购产品附录。

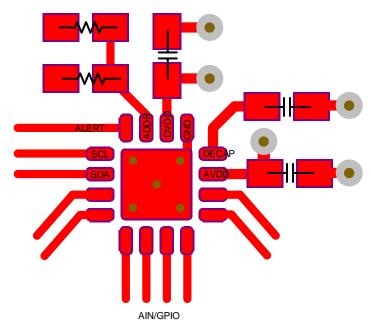

## ADS7138 方框图和 应用

#### **Device Block Diagram**

#### AVDD DECAP High/Low Threshold DVDD AIN0 / GPIO0 ALERT AIN1 / GPIO1 Programmable ADC Averaging Filter AIN2 / GPIO2 Digital Window AIN3 / GPIO3 Comparator MUX AIN4 / GPIO4 ADDR Sequencer AIN5 / GPIO5 I<sup>2</sup>C Interface Pin CFG SDA AIN6 / GPIO6 GPO Write SCL AIN7 / GPIO7 GPI Read CRC GND

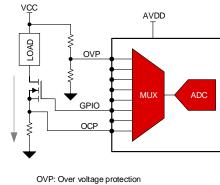

#### **Example System Architecture**

OCP: Over current protection

$\triangle$

# 目录

| 1 | 特性1                                            |       | 8.3 Feature Description                   |      |

|---|------------------------------------------------|-------|-------------------------------------------|------|

| 2 | 应用 1                                           |       | 8.4 Device Functional Modes               | . 18 |

| 3 | 说明1                                            |       | 8.5 Programming                           | 22   |

| 4 | 修订历史记录 2                                       |       | 8.6 ADS7138 Registers                     | 25   |

| 5 | Device Comparison Table                        | 9     | Application and Implementation            | 66   |

| - | Pin Configuration and Functions 4              |       | 9.1 Application Information               | 66   |

| 7 | _                                              |       | 9.2 Typical Applications                  | 66   |

| ′ | Specifications                                 | 10    | Power Supply Recommendations              | 68   |

|   | 7.1 Absolute Maximum Ratings                   |       | 10.1 AVDD and DVDD Supply Recommendations | 68   |

|   | 7.2 ESD Ratings                                | 11    | Layout                                    | 69   |

|   | 7.3 Recommended Operating Conditions 5         | • • • | -                                         |      |

|   | 7.4 Thermal Information 5                      |       | 11.1 Layout Guidelines                    |      |

|   | 7.5 Electrical Characteristics                 |       | 11.2 Layout Example                       | 69   |

|   | 7.6 I <sup>2</sup> C Timing Requirements       | 12    | 器件和文档支持                                   | 70   |

|   | 7.7 Timing Requirements                        |       | 12.1 接收文档更新通知                             | 70   |

|   | 7.8 I <sup>2</sup> C Switching Characteristics |       | 12.2 社区资源                                 | 70   |

|   |                                                |       | 12.3 商标                                   |      |

|   | 7.9 Switching Characteristics 8                |       | 12.4 静电放电警告                               |      |

| 8 | Detailed Description 9                         |       |                                           |      |

|   | 8.1 Overview                                   |       | 12.5 Glossary                             |      |

|   | 8.2 Functional Block Diagram9                  | 13    | 机械、封装和可订购信息                               | 70   |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| 日期         | 修订版本 | 说明     |

|------------|------|--------|

| 2019 年 5 月 | *    | 初始发行版。 |

# 5 Device Comparison Table

| PART NUMBER | DESCRIPTION                                                     | CRC MODULE | ZERO-CROSSING-DETECT (ZCD) MODULE | ROOT-MEAN-SQUARE<br>(RMS) MODULE |

|-------------|-----------------------------------------------------------------|------------|-----------------------------------|----------------------------------|

| ADS7128     | 8-channel, 12-bit ADC with I <sup>2</sup> C interface and GPIOs | Yes        | Yes                               | Yes                              |

| ADS7138     |                                                                 | Yes        | No                                | No                               |

| ADS7138-Q1  |                                                                 | Yes        | No                                | No                               |

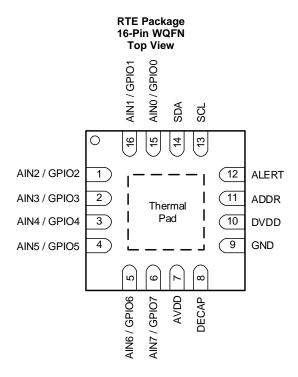

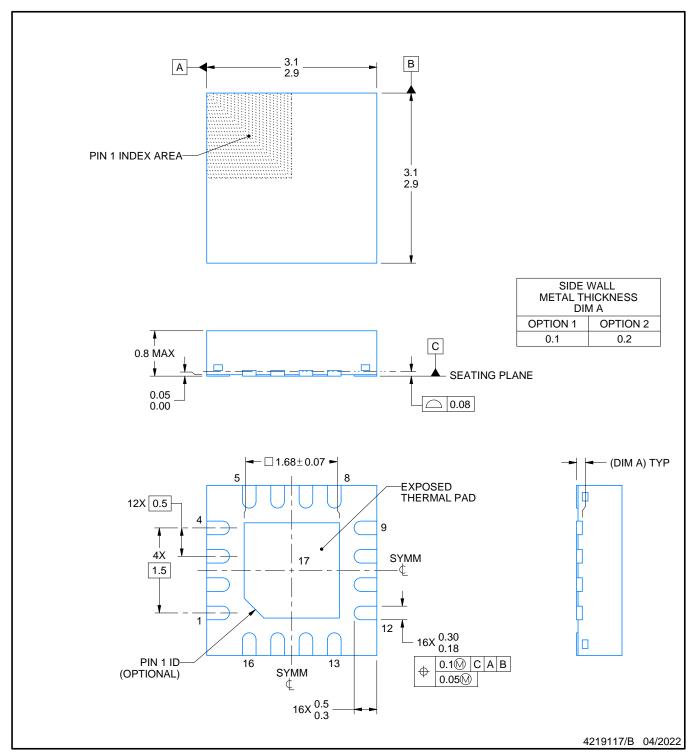

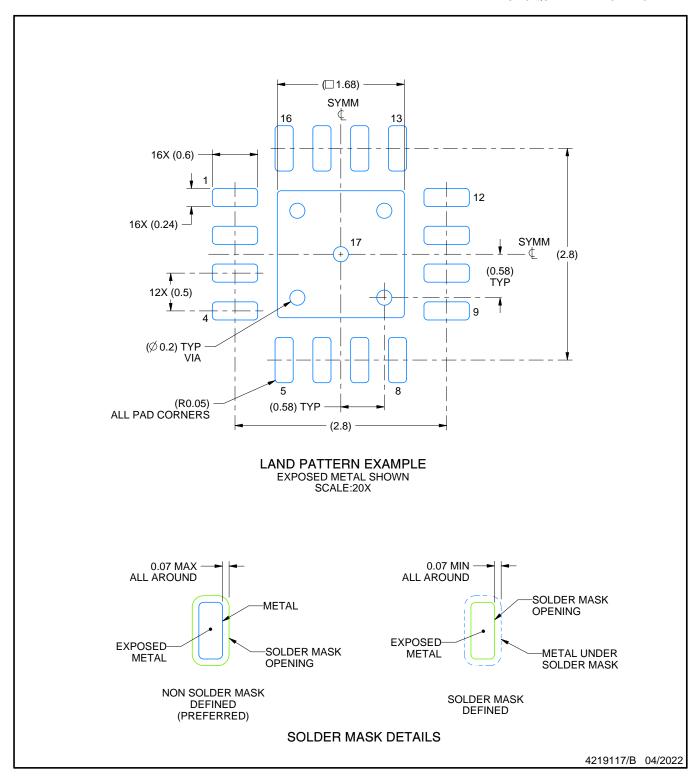

# 6 Pin Configuration and Functions

#### **Pin Functions**

| PIN        |     | FUNCTION <sup>(1)</sup> | DESCRIPTION                                                                                                                                          |  |

|------------|-----|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME       | NO. | FUNCTION                | DESCRIPTION                                                                                                                                          |  |

| AIN0/GPIO0 | 15  | AI, DI, DO              | Channel 0; configurable as either an analog input (default) or a general-purpose input/output (GPIO)                                                 |  |

| AIN1/GPIO1 | 16  | AI, DI, DO              | Channel 1; configurable as either an analog input (default) or a GPIO                                                                                |  |

| AIN2/GPIO2 | 1   | AI, DI, DO              | Channel 2; configurable as either an analog input (default) or a GPIO                                                                                |  |

| AIN3/GPIO3 | 2   | AI, DI, DO              | Channel 3; configurable as either an analog input (default) or a GPIO                                                                                |  |

| AIN4/GPIO4 | 3   | AI, DI, DO              | Channel 4; configurable as either an analog input (default) or a GPIO                                                                                |  |

| AIN5/GPIO5 | 4   | AI, DI, DO              | Channel 5; configurable as either an analog input (default) or a GPIO                                                                                |  |

| AIN6/GPIO6 | 5   | AI, DI, DO              | Channel 6; configurable as either an analog input (default) or a GPIO                                                                                |  |

| AIN7/GPIO7 | 6   | AI, DI, DO              | Channel 7; configurable as either an analog input (default) or a GPIO                                                                                |  |

| ADDR       | 11  | Al                      | Input for selecting the device I <sup>2</sup> C address.  Connect a resistor to this pin from DECAP pin or GND to select one of the eight addresses. |  |

| ALERT      | 12  | Digital output          | Open-drain (default) or push-pull output for the digital comparator                                                                                  |  |

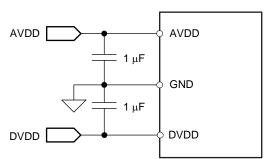

| AVDD       | 7   | Supply                  | Analog supply input, also used as the reference voltage to the ADC; connect a 1-µF decoupling capacitor to GND                                       |  |

| DECAP      | 8   | Supply                  | Connect a decoupling capacitor to this pin for the internal power supply                                                                             |  |

| DVDD       | 10  | Supply                  | Digital I/O supply voltage; connect a 1-µF decoupling capacitor to GND                                                                               |  |

| GND        | 9   | Supply                  | Ground for the power supply; all analog and digital signals are referred to this pin voltage                                                         |  |

| SDA        | 14  | DI, DO                  | Serial data input or output for the I <sup>2</sup> C interface                                                                                       |  |

| SCL        | 13  | DI                      | Serial clock for the I <sup>2</sup> C interface                                                                                                      |  |

<sup>(1)</sup> Al = analog input, DI = digital input, and DO = digital output.

# 7 Specifications

www.ti.com.cn

#### 7.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted)(1)

|                                                | MIN       | MAX        | UNIT |

|------------------------------------------------|-----------|------------|------|

| DVDD to GND                                    | -0.3      | 5.5        | V    |

| AVDD to GND                                    | -0.3      | 5.5        | V    |

| AINx/GPOx <sup>(2)</sup>                       | GND - 0.3 | AVDD + 0.3 | V    |

| ADDR                                           | GND - 0.3 | 2.1        | V    |

| Digital inputs                                 | GND - 0.3 | 5.5        | V    |

| Current through any pin except supply pins (3) | -10       | 10         | mA   |

| Junction temperature, T <sub>J</sub>           | -40       | 125        | °C   |

| Storage temperature, T <sub>stg</sub>          | -60       | 150        | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 7.2 ESD Ratings

|             |                         |                                                                               | VALUE | UNIT |

|-------------|-------------------------|-------------------------------------------------------------------------------|-------|------|

|             |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1)              | ±2000 |      |

| $V_{(ESD)}$ | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 | rating noo an temperature rang | , , ,                                 |      |     |            |      |

|-----------------|--------------------------------|---------------------------------------|------|-----|------------|------|

|                 | PARAMETER                      | TEST CONDITIONS                       | MIN  | TYP | MAX        | UNIT |

| POWER           | SUPPLY                         |                                       |      |     |            |      |

| AVDD            | Analog supply voltage          |                                       | 2.35 | 3.3 | 5.5        | V    |

| DVDD            | Digital supply voltage         |                                       | 1.65 | 3.3 | 5.5        | V    |

| ANALO           | GINPUTS                        |                                       |      |     | *          |      |

| FSR             | Full-scale input range         | AIN <sub>X</sub> <sup>(1)</sup> - GND | 0    |     | AVDD       | V    |

| V <sub>IN</sub> | Absolute input voltage         | AIN <sub>X</sub> - GND                | -0.1 | ·   | AVDD + 0.1 | V    |

| TEMPE           | RATURE RANGE                   |                                       |      | ·   |            |      |

| T <sub>A</sub>  | Ambient temperature            |                                       | -40  | 25  | 125        | °C   |

|                 |                                |                                       |      |     |            |      |

<sup>(1)</sup> AINx refers to AIN0, AIN1, AIN2, AIN3, AIN4, AIN5, AIN6, and AIN7.

#### 7.4 Thermal Information

|                      |                                              | ADS7138    |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RTE (WQFN) | UNIT |

|                      |                                              | 16 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 49.7       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 53.4       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 24.7       | °C/W |

| $\Psi_{JT}$          | Junction-to-top characterization parameter   | 1.3        | °C/W |

| $\Psi_{JB}$          | Junction-to-board characterization parameter | 24.7       | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 9.3        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> AlNx/GPIOx refers to pins 1, 2, 3, 4, 5, 6, 15, and 16.

<sup>(3)</sup> Pin current must be limited to 10mA or less.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.5 Electrical Characteristics

at AVDD = 5 V, DVDD = 1.65 V to 5.5 V, and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40^{\circ}$ C to +125°C; typical values at  $T_A = 25^{\circ}$ C.

|                   | PARAMETER                          | TEST CONDITIONS                                                          | MIN        | TYP   | MAX        | UNIT   |

|-------------------|------------------------------------|--------------------------------------------------------------------------|------------|-------|------------|--------|

| ANALO             | G INPUTS                           |                                                                          |            |       |            |        |

| C <sub>SH</sub>   | Sampling capacitance               |                                                                          |            | 12    |            | pF     |

| DC PEF            | RFORMANCE                          |                                                                          |            |       |            |        |

|                   | Resolution                         | No missing codes                                                         |            | 12    |            | bits   |

| DNL               | Differential nonlinearity          |                                                                          | -0.9       | ±0.2  | 0.9        | LSB    |

| INL               | Integral nonlinearity              |                                                                          | -2         | ±0.5  | 2          | LSB    |

| V <sub>(OS)</sub> | Input offset error                 | Post offset calibration                                                  | -2         | ±0.3  | 2          | LSB    |

|                   | Input offset thermal drift         | Post offset calibration                                                  |            | ±5    |            | ppm/°C |

|                   | Offset error match                 |                                                                          | -1         | ±0.5  | 1          | LSB    |

| G <sub>E</sub>    | Gain error                         |                                                                          | -0.1       | ±0.05 | 0.1        | %FSR   |

|                   | Gain error thermal drift           |                                                                          |            | ±5    |            | ppm/°C |

|                   | Gain error match                   |                                                                          | -0.05      | ±0.01 | 0.05       | %FSR   |

| AC PEF            | RFORMANCE                          |                                                                          |            |       |            |        |

| CINIAD            | Circulto poios i distortion ratio  | AVDD = 5 V, f <sub>IN</sub> = 2 kHz                                      | 68.5       | 71.5  |            | ٩D     |

| SINAD             | Signal-to-noise + distortion ratio | $AVDD = 3 V, f_{IN} = 2 kHz$                                             | 67.5       | 70.5  |            | dB     |

| CNID              | Circulto naino natio               | AVDD = 5 V, f <sub>IN</sub> = 2 kHz                                      | 69         | 72    |            | 4D     |

| SNR               | Signal-to-noise ratio              | AVDD = 3 V, f <sub>IN</sub> = 2 kHz                                      | 68         | 71    |            | dB     |

| THD               | Total harmonic distortion          | f <sub>IN</sub> = 2 kHz                                                  |            | -85   |            | dB     |

| SFDR              | Spurious-free dynamic range        | f <sub>IN</sub> = 2 kHz                                                  |            | 91    |            | dB     |

|                   | Crosstalk                          | 100-kHz signal applied on any OFF channel and measured on ON the channel |            | -100  |            | dB     |

| DECAP             | Pin                                |                                                                          | ļ.         |       |            |        |

|                   | Decoupling capacitor on DECAP pin  |                                                                          | 0.22       | 1     |            | μF     |

| DIGITA            | L INPUT/OUTPUT (SCL, SDA)          |                                                                          | I          |       |            |        |

| V <sub>IH</sub>   | Input high logic level             | All I <sup>2</sup> C modes                                               | 0.7 x DVDD |       | DVDD       | V      |

| V <sub>IL</sub>   | Input low logic level              | All I <sup>2</sup> C modes                                               | -0.3       |       | 0.3 x DVDD | V      |

|                   | 0                                  | Sink current = 2 mA, DVDD > 2 V                                          | 0          |       | 0.4        | .,     |

| $V_{OL}$          | Output low logic level             | Sink current = 2 mA, DVDD ≤ 2 V                                          | 0          |       | 0.2 x DVDD | V      |

|                   |                                    | V <sub>OL</sub> = 0.4 V, standard and fast Mode                          |            |       | 3          |        |

| l <sub>OL</sub>   | Low-level output current (sink)    | V <sub>OL</sub> = 0.6 V, fast mode                                       |            |       | 6          | mA     |

|                   |                                    | V <sub>OL</sub> = 0.4 V, fast mode plus                                  |            |       | 20         |        |

| GPIOs             |                                    |                                                                          |            |       |            |        |

| V <sub>IH</sub>   | Input high logic level             |                                                                          | 0.7 x AVDD |       | AVDD + 0.3 | V      |

| $V_{IL}$          | Input low logic level              |                                                                          | -0.3       |       | 0.3 x AVDD | V      |

|                   | Input leakge current               | GPIO configured as input                                                 |            | 10    | 100        | nA     |

| V <sub>OH</sub>   | Output high logic level            | GPO_DRIVE_CFG = push-pull,<br>I <sub>SOURCE</sub> = 2 mA                 | 0.8 x AVDD |       | AVDD       | ٧      |

| V <sub>OL</sub>   | Output low logic level             | I <sub>SINK</sub> = 2 mA                                                 | 0          |       | 0.2 x AVDD | V      |

| I <sub>OH</sub>   | Output high source current         | V <sub>OH</sub> > 0.7 x AVDD                                             |            |       | 5          | mA     |

| I <sub>OL</sub>   | Output low sink current            | V <sub>OL</sub> < 0.3 x AVDD                                             |            |       | 5          | mA     |

|                   | L OUTPUT (ALERT)                   |                                                                          |            |       |            |        |

| V <sub>OH</sub>   | Output high logic level            | GPO_DRIVE_CFG = push-pull,<br>I <sub>SOURCE</sub> = 2 mA                 | 0.8 x DVDD |       | DVDD       | V      |

| V <sub>OL</sub>   | Output low logic level             | I <sub>SINK</sub> = 2 mA                                                 | 0          |       | 0.2 x DVDD | V      |

## **Electrical Characteristics (continued)**

at AVDD = 5 V, DVDD = 1.65 V to 5.5 V, and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40$ °C to +125°C; typical values at  $T_A = 25$ °C.

|                   | PARAMETER                | TEST CONDITIONS                              | MIN | TYP | MAX | UNIT |

|-------------------|--------------------------|----------------------------------------------|-----|-----|-----|------|

| I <sub>OH</sub>   | Output high sink current | $V_{OH} > 0.7 \times DVDD$                   |     |     | 5   | mA   |

| I <sub>OL</sub>   | Output low sink current  | V <sub>OL</sub> < 0.3 x DVDD                 |     |     | 5   | mA   |

| POWER             | SUPPLY CURRENTS          |                                              |     |     |     |      |

|                   |                          | I <sup>2</sup> C high-speed mode, AVDD = 5 V |     | 260 | 430 |      |

|                   |                          | I <sup>2</sup> C fast mode plus, AVDD = 5 V  |     | 83  | 140 |      |

| I <sub>AVDD</sub> | Analog supply current    | I <sup>2</sup> C fast mode, AVDD = 5 V       |     | 35  | 57  | μΑ   |

|                   |                          | I <sup>2</sup> C standard mode, AVDD = 5 V   |     | 10  | 20  |      |

|                   |                          | No conversion, AVDD = 5 V                    |     | 5   | 15  |      |

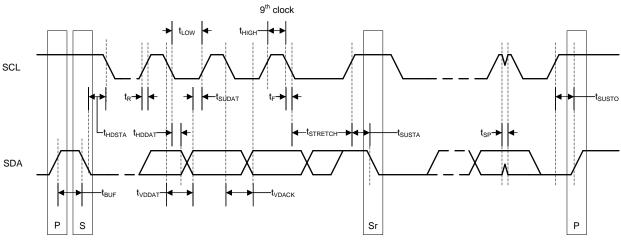

# 7.6 I<sup>2</sup>C Timing Requirements

|                    |                                               |        | МС          | DE        |      |      |

|--------------------|-----------------------------------------------|--------|-------------|-----------|------|------|

|                    |                                               | FAST N | <b>IODE</b> | HIGH-SPEE | MODE | UNIT |

|                    |                                               | MIN    | MAX         | MIN       | MAX  |      |

| f <sub>SCL</sub>   | SCL clock frequency <sup>(1)</sup>            |        | 1           |           | 3.4  | MHz  |

| t <sub>SUSTA</sub> | START condition setup time for repeated start | 260    |             | 160       |      | ns   |

| t <sub>HDSTA</sub> | Start condition hold time                     | 260    |             | 160       |      | ns   |

| t <sub>LOW</sub>   | Clock low period                              | 500    |             | 160       |      | ns   |

| t <sub>HIGH</sub>  | Clock high period                             | 260    |             | 60        |      | ns   |

| t <sub>SUDAT</sub> | Data in setup time                            | 50     |             | 10        |      | ns   |

| t <sub>HDDAT</sub> | Data in hold time                             | 0      |             | 0         |      | ns   |

| t <sub>R</sub>     | SCL rise time                                 |        | 120         |           | 80   | ns   |

| t <sub>F</sub>     | SCL fall time                                 |        | 120         |           | 80   | ns   |

| t <sub>SUSTO</sub> | STOP condition hold time                      | 260    |             | 60        |      | ns   |

| t <sub>BUF</sub>   | Bus free time before new transmission         | 500    |             | 300       |      | ns   |

<sup>(1)</sup> Bus load ( $C_B$ ) consideration;  $C_B \le 400$  pF for  $f_{SCL} \le 1$  MHz;  $C_B < 100$  pF for  $f_{SCL} = 3.4$  MHz.

## 7.7 Timing Requirements

at AVDD = 2.35 V to 5 V, DVDD = 1.65 V to 5.5 V, and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40$ °C to +125°C; typical values at  $T_A = 25$ °C.

|                  |                  | MIN MA | X UNIT |

|------------------|------------------|--------|--------|

| t <sub>ACQ</sub> | Acquisition time | 300    | ns     |

# 7.8 I<sup>2</sup>C Switching Characteristics

|                      |                                                                       |         | MODE                   |     |     |      |

|----------------------|-----------------------------------------------------------------------|---------|------------------------|-----|-----|------|

|                      |                                                                       | FAST MO | FAST MODE HIGH-SPEED I |     |     | UNIT |

|                      |                                                                       | MIN     | MAX                    | MIN | MAX |      |

| t <sub>VDDATA</sub>  | SCL low to SDA data out valid                                         |         | 450                    |     | 200 | ns   |

| t <sub>VDACK</sub>   | SCL low to SDA acknowledge time                                       |         | 450                    |     | 200 | ns   |

| t <sub>STRETCH</sub> | Clock stretch time in one-shot conversion mode; during ADC conversion |         | 1200                   |     | 950 | ns   |

| t <sub>SP</sub>      | Noise supression time constant on SDA and SCL                         |         | 50                     |     | 10  | ns   |

# 7.9 Switching Characteristics

at AVDD = 2.35 V to 5 V, DVDD = 1.65 V to 5.5 V, and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40$ °C to +125°C; typical values at  $T_A = 25$ °C.

|                       | PARAMETER                                             | TEST CONDITIONS                | MIN | MAX                  | UNIT |

|-----------------------|-------------------------------------------------------|--------------------------------|-----|----------------------|------|

| CONVERSI              | ON CYCLE                                              |                                |     |                      |      |

| t <sub>CONV</sub>     | ADC conversion time                                   | Manual and auto sequence modes |     | t <sub>STRETCH</sub> | ns   |

| 00144                 |                                                       | Autonomous mode                |     | 550                  | ns   |

| RESET AN              | DALERT                                                |                                |     |                      |      |

| t <sub>PU</sub>       | Power-up time for device                              | AVDD ≥ 2.35 V                  |     | 5                    | ms   |

| t <sub>RST</sub>      | Delay time: RST bit = 1b to device reset complete (1) |                                |     | 5                    | ms   |

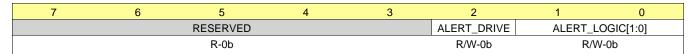

| t <sub>ALERT_HI</sub> | ALERT high period                                     | ALERT_LOGIC[1:0]<br>= 1x       | 85  | 105                  | ns   |

| t <sub>ALERT_LO</sub> | ALERT low period                                      | ALERT_LOGIC[1:0]<br>= 1x       | 85  | 105                  | ns   |

(1) RST bit is automatically reset to 0b after  $t_{RST}$ .

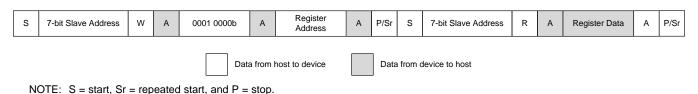

NOTE: S = start, Sr = repeated start, and P = stop.

图 1. I<sup>2</sup>C Timing Diagram

## 8 Detailed Description

INSTRUMENTS

#### 8.1 Overview

The ADS7138 is a small, eight-channel, multiplexed, 12-bit, analog-to-digital converter (ADC) with an I<sup>2</sup>C-compatible serial interface. The eight channels of the ADS7138 can be individually configured as either analog inputs, digital inputs, or digital outputs. The device includes a digital comparator with a dedicated alert pin that can be used to interrupt the host when a programmed high or low threshold is crossed on any input channel. The device uses an internal oscillator for conversion. The ADC can be used in the manual mode for reading ADC data over the I<sup>2</sup>C interface or in autonomous mode for monitoring the analog inputs without an active I<sup>2</sup>C interface.

The device features a programmable averaging filter that outputs a 16-bit result for enhanced resolution.

The I<sup>2</sup>C serial interface supports standard-mode, fast-mode plus, and high-speed mode. The device also features an 8-bit cyclic redundancy check (CRC) for the serial communication interface.

#### 8.2 Functional Block Diagram

ZHCSJS8-MAY 2019

#### 8.3 Feature Description

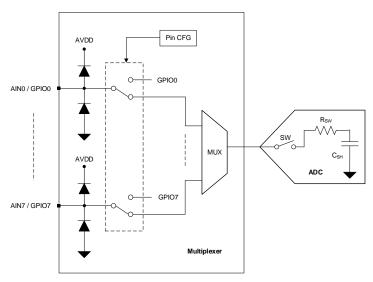

#### 8.3.1 Multiplexer and ADC

The eight channels of the multiplexer can be independently configured as ADC inputs or general-purpose inputs/outputs (GPIOs).

2 shows that each input pin has electrostatic discharge (ESD) protection diodes to AVDD and GND. On power-up or after device reset, all eight multiplexer channels are configured as analog inputs.

$\boxtimes$  2 shows an equivalent circuit for pins configured as analog inputs. The ADC sampling switch is represented by an ideal switch (SW) in series with the resistor, R<sub>SW</sub> (typically 150  $\Omega$ ), and the sampling capacitor, C<sub>SH</sub> (typically 12 pF).

图 2. Analog Inputs, GPIOs, and ADC Connections

During acquisition, the SW switch is closed to allow the signal on the selected analog input channel to charge the internal sampling capacitor. During conversion, the SW switch is opened to disconnect the analog input channel from the sampling capacitor.

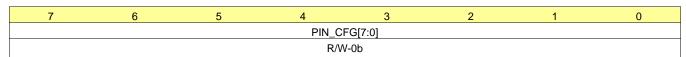

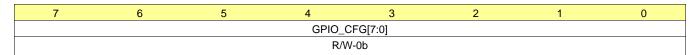

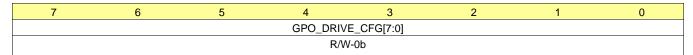

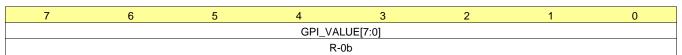

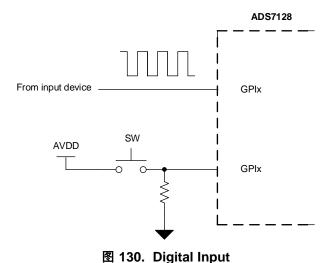

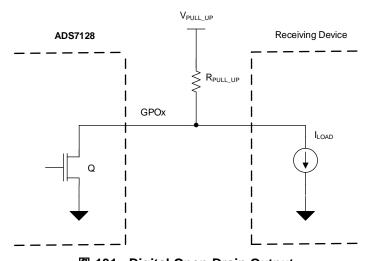

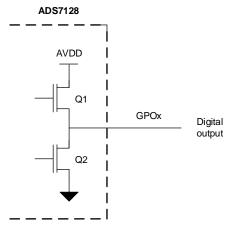

The multiplexer channels can be configured as GPIOs in the PIN\_CFG register. The direction of a GPIO (either as an input or an output) can be set in the GPIO\_CFG register. The logic level on the channels configured as digital inputs can be read from the GPI\_VALUE register. The digital outputs can be accessed by writing to the GPO\_OUTPUT\_VALUE register. The digital outputs can be configured as either open-drain or push-pull in the GPO\_DRIVE\_CFG register.

#### 8.3.2 Reference

The device uses the analog supply voltage (AVDD) as a reference for the analog-to-digital conversion process. TI recommends connecting a  $1-\mu F$ , low-equivalent series resistance (ESR) ceramic decoupling capacitor between the AVDD and GND pins.

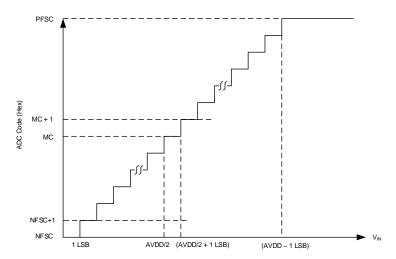

#### 8.3.3 ADC Transfer Function

The ADC output is in straight binary format. 公式 1 computes the ADC resolution:

$$1 LSB = V_{REF} / 2^{N}$$

where:

•  $V_{REF} = AVDD$

•

$$N = 12$$

(1)

图 3 and 表 1 detail the transfer characteristics for the device.

# Feature Description (接下页)

NSTRUMENTS

图 3. Ideal Transfer Characteristics

|       | _       |      | •     |        | 4.0   |

|-------|---------|------|-------|--------|-------|

| 表 1   | Iran    | ctar | Chara | ıctarı | etice |

| 4X I. | . IIaii | 31CI | Onara | CLCII  | SHUS  |

| INPUT VOLTAGE                            | CODE     | DESCRIPTION              | IDEAL OUTPUT CODE |

|------------------------------------------|----------|--------------------------|-------------------|

| ≤1 LSB                                   | NFSC     | Negative full-scale code | 000               |

| 1 LSB to 2 LSBs                          | NFSC + 1 | _                        | 001               |

| (AVDD / 2) to (AVDD / 2) + 1 LSB         | MC       | Mid code                 | 800               |

| (AVDD / 2) + 1 LSB to (AVDD / 2) + 2 LSB | MC + 1   | _                        | 801               |

| ≥ AVDD – 1 LSB                           | PFSC     | Positive full-scale code | FFF               |

#### 8.3.4 ADC Offset Calibration

The variation in ADC offset error resulting from changes in temperature or AVDD can be calibrated by setting the CAL bit in the GENERAL\_CFG register. The CAL bit is reset to 0 after calibration. The host can poll the CAL bit to check the ADC offset calibration completion status.

#### 8.3.5 I<sup>2</sup>C Address Selector

The I<sup>2</sup>C address for the device is determined by connecting external resistors on the ADDR pin. The device address is determined at power-up based on the resistor values. The device retains this address until the next power-up event, until the next device reset, or until the device receives a command to program its own address.

4 shows a connection diagram for the ADDR pin and 表 2 lists the resistor values for selecting different addresses of the device.

图 4. External Resistor Connection Diagram for the ADDR Pin

#### 表 2. I<sup>2</sup>C Address Selection

| RESIS              | TORS                       | ADDRESS         |  |  |  |

|--------------------|----------------------------|-----------------|--|--|--|

| R1 <sup>(1)</sup>  | R2 <sup>(1)</sup>          | ADDRESS         |  |  |  |

| 0 Ω                | DNP <sup>(2)</sup>         | 001 0111b (17h) |  |  |  |

| 11 kΩ              | DNP <sup>(2)</sup>         | 001 0110b (16h) |  |  |  |

| 33 kΩ              | DNP <sup>(2)</sup>         | 001 0101b (15h) |  |  |  |

| 100 kΩ             | DNP <sup>(2)</sup>         | 001 0100b (14h) |  |  |  |

| DNP <sup>(2)</sup> | $0~\Omega$ or DNP $^{(2)}$ | 001 0000b (10h) |  |  |  |

| DNP <sup>(2)</sup> | 11 kΩ                      | 001 0001b (11h) |  |  |  |

| DNP <sup>(2)</sup> | 33 kΩ                      | 001 0010b (12h) |  |  |  |

| DNP <sup>(2)</sup> | 100 kΩ                     | 001 0011b (13h) |  |  |  |

- Tolerance for R1, R2 ≤ ±5%.

- (2) DNP = Do not populate.

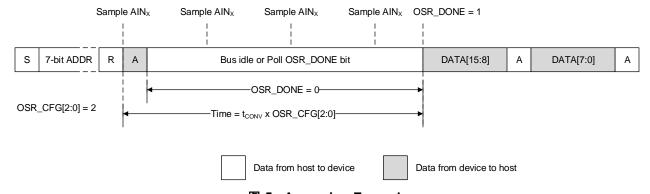

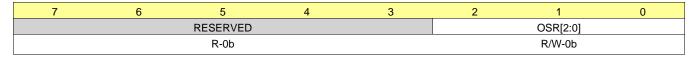

## 8.3.6 Programmable Averaging Filter

The ADS7138 features a built-in oversampling (OSR) function that can be used to average several samples. The averaging filter can be enabled by programming the OSR[2:0] bits in the OSR\_CFG register. The averaging filter configuration is common to all analog input channels. \$\overline{\mathbb{Z}}\$ 5 shows that the averaging filter module output is 16 bits long. In the manual conversion mode and auto-sequence mode, only the first conversion for the selected analog input channel must be initiated by the host; see the \*Manual Mode\* and \*Auto-Sequence Mode\* sections. As shown in \$\overline{\mathbb{Z}}\$ 5, any remaining conversions for the selected averaging factor are generated internally. The time required to complete the averaging operation is determined by the sampling speed and number of samples to be averaged. As shown in \$\overline{\mathbb{Z}}\$ 5, the 16-bit result can be read out after the averaging operation completes.

图 5. Averaging Example

In 图 5, SCL is stretched by the device after the start of conversions until the averaging operation is complete.

If SCL stretching is not required during averaging, enable the statistics registers by setting STATS\_EN to 1b and initiate conversions by writing 1b to the CNVST bit. The OSR\_DONE bit in the SYSTEM\_STATUS register can be polled to check the averaging completion status. When using the CNVST bit to initiate conversion, the result can be read in the RECENT\_CHx\_LSB and RECENT\_CHx\_MSB registers.

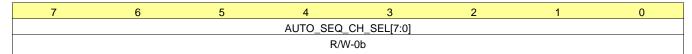

In the autonomous mode of operation, samples from the analog input channels that are enabled in the AUTO\_SEQ\_CH\_SEL register are averaged sequentially; see the *Autonomous Mode* section. The digital window comparator compares the top 12 bits of the 16-bit average result with the thresholds.

公式 2 provides the LSB value of the 16-bit average result.

$$1 LSB = \frac{AVDD}{2^{16}} \tag{2}$$

#### 8.3.7 CRC on Data Interface

The ADS7138 features a cyclic redundancy check (CRC) module for checking the integrity of the data bits exchanged over the  $I^2C$  interface. The CRC module is bidirectional and appends an 8-bit CRC to every byte read from the device while also evaluating the CRC of every incoming byte over the  $I^2C$  interface. The CRC module uses the CRC-8-CCITT polynomial ( $x^8 + x^2 + x + 1$ ) for CRC computation.

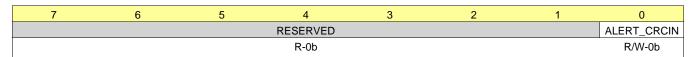

To enable the CRC module, set the CRC\_EN bit in the GENERAL\_CFG register. 表 3 shows how a CRC error can be detected when configuring the ADS7138.

| CRC ERROR NOTIFICATION | C ERROR NOTIFICATION CONFIGURATION DESCRIPTION                                       |                                                                                                         |  |  |  |  |  |

|------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ALERT pin              | ALERT pin ALERT_CRCIN = 1b ALERT pin is asserted if a CRC error is detected by the d |                                                                                                         |  |  |  |  |  |

| Status flags           | APPEND_STATUS = 10b                                                                  | 4-bit status flags are appended to the ADC data; see the <i>Output Data Format</i> section for details. |  |  |  |  |  |

| Register read          | <del>_</del>                                                                         | Read the CRC_ERR_IN bit to check if a CRC error is detected.                                            |  |  |  |  |  |

When the ADS7138 detects a CRC error, the erroneous data are ignored and the CRC\_ERR\_IN bit is set. 表 3 describes the additional notifications that can be enabled. Further register writes are disabled until the CRC\_ERR\_IN bit is cleared by writing 1b to it. When using autonomous mode, further conversions can be disabled on the CRC error by setting CONV\_ON\_ERR to 1b; see the *Autonomous Mode* section.

#### 8.3.8 General-Purpose I/Os (GPIOs)

The eight channels of the ADS7138 can be independently configured as analog inputs, digital inputs, or digital outputs. 表 4 describes how the PIN\_CFG and GPIO\_CFG registers can be used to configure the channels.

#### 表 4. Configuring Channels as Analog Inputs or GPIOs

| PIN_CFG[7:0] | GPIO_CFG[7:0] | GPO_DRIVE_CF<br>G[7:0] | CHANNEL CONFIGURATION             |

|--------------|---------------|------------------------|-----------------------------------|

| 0            | х             | х                      | Analog input (default)            |

| 1            | 0             | х                      | Digital input                     |

| 1            | 1             | 0                      | Digital output; open-drain driver |

| 1            | 1             | 1                      | Digital output; push-pull driver  |

The digital outputs can be configured to logic 1 or 0 by writing to the GPO\_OUTPUT\_VALUE register. Reading the GPI\_VALUE register returns the logic level for all channels configured as digital inputs.

#### 8.3.9 Oscillator and Timing Control

The device uses an internal oscillator for conversions. When using the averaging module, the host initiates the first conversion and all subsequent conversions are generated internally by the device. 表 5 shows that when the device generates the start of the conversion, the sampling rate is controlled by the OSC\_SEL and CLK\_DIV[3:0] register fields.

表 5. Configuring Sampling Rate for Internal Conversion Start Control

|              | OSC_SEL =                                     | 0                                      | OSC_SEL = 1                                   |                                     |  |  |  |

|--------------|-----------------------------------------------|----------------------------------------|-----------------------------------------------|-------------------------------------|--|--|--|

| CLK_DIV[3:0] | SAMPLING FREQUENCY, f <sub>CYCLE</sub> (kSPS) | CYCLE TIME,<br>t <sub>CYCLE</sub> (µs) | SAMPLING FREQUENCY, f <sub>CYCLE</sub> (kSPS) | CYCLE TIME, t <sub>CYCLE</sub> (µs) |  |  |  |

| 0000b        | 1000                                          | 1                                      | 31.25                                         | 32                                  |  |  |  |

| 0001b        | 666.7                                         | 1.5                                    | 20.83                                         | 48                                  |  |  |  |

| 0010b        | 500                                           | 2                                      | 15.63                                         | 64                                  |  |  |  |

| 0011b        | 333.3                                         | 3                                      | 10.42                                         | 96                                  |  |  |  |

| 0100b        | 250                                           | 4                                      | 7.81                                          | 128                                 |  |  |  |

| 0101b        | 166.7                                         | 6                                      | 5.21                                          | 192                                 |  |  |  |

| 0110b        | 125                                           | 8                                      | 3.91                                          | 256                                 |  |  |  |

| 0111b        | 83                                            | 12                                     | 2.60                                          | 384                                 |  |  |  |

| 1000b        | 62.5                                          | 16                                     | 1.95                                          | 512                                 |  |  |  |

| 1001b        | 41.7                                          | 24                                     | 1.3                                           | 768                                 |  |  |  |

| 1010b        | 31.3                                          | 32                                     | 0.98                                          | 1024                                |  |  |  |

| 1011b        | 20.8                                          | 48                                     | 0.65                                          | 1536                                |  |  |  |

| 1100b        | 15.6                                          | 64                                     | 0.49                                          | 2048                                |  |  |  |

| 1101b        | 10.4                                          | 96                                     | 0.33                                          | 3072                                |  |  |  |

The conversion time of the device (see t<sub>CONV</sub> in the *Switching Characteristics* table) is independent of the OSC\_SEL and CLK\_DIV[3:0] configuration.

#### 8.3.10 Output Data Format

6 illustrates various I<sup>2</sup>C frames for reading data.

- Read the ADC conversion result: Two 8-bit I<sup>2</sup>C packets are required (frame A).

- Read the averaged conversion result: Two 8-bit I<sup>2</sup>C packets are required (frame B).

- Read data with the channel ID appended: The 4-bit channel ID can be appended to the 12-bit ADC result by configuring the APPEND\_STATUS field in the GENERAL\_CFG register. When the channel ID appended to the 12-bit ADC data, two I<sup>2</sup>C packets are required (frame C). If the channel ID appended to the 16-bit average result, three I<sup>2</sup>C frames are required (frame D).

|       |                                                                                                                              | San | nple A              |     |       |                                        |        |       |        |         |         |         |        |                     |       |    |    |    | 5                  | Sample | A + 1 |

|-------|------------------------------------------------------------------------------------------------------------------------------|-----|---------------------|-----|-------|----------------------------------------|--------|-------|--------|---------|---------|---------|--------|---------------------|-------|----|----|----|--------------------|--------|-------|

| S     | 7-bit Slave Address                                                                                                          | R   | А                   | D11 | D10   | D9                                     | D8     | D7    | D6     | D5      | D4      | Α       | D3     | D2                  | D1    | D0 | 0  | 0  | 0                  | 0      | А     |

|       | Frame A : Reading ADC data                                                                                                   |     |                     |     |       |                                        |        |       |        |         |         |         |        |                     |       |    |    |    |                    |        |       |

| S     | 7-bit Slave Address                                                                                                          | R   | А                   | D15 | D14   | D13                                    | D12    | D11   | D10    | D9      | D8      | А       | D7     | D6                  | D5    | D4 | D3 | D2 | D1                 | D0     | А     |

|       | Frame B : Reading ADC data with averaging enabled                                                                            |     |                     |     |       |                                        |        |       |        |         |         |         |        |                     |       |    |    |    |                    |        |       |

| S     | 7-bit Slave Address                                                                                                          | R   | А                   | D11 | D10   | D9                                     | D8     | D7    | D6     | D5      | D4      | А       | D3     | D2                  | D1    | D0 |    |    | annel I<br>us Flag | _      | А     |

|       |                                                                                                                              |     | <br> <br> <br> <br> |     | Frame | C:Re                                   | eading | ADC d | ata wi | th stat | us flag | s or cl | nannel | ID app              | ended | l  |    |    |                    |        | <br>  |

| S     | 7-bit Slave Address                                                                                                          | R   | А                   | D15 | D14   | \(\(\)\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | 8      | A D   | )7 C   | 6       | D0      | Α       |        | -bit Ch<br>or Statu |       | _  | 0  | 0  | 0                  | 0      | А     |

| Clock | Clock stretching for conversion time Frame D : Reading ADC data with averaging enabled & status flags or channel ID appended |     |                     |     |       |                                        |        |       |        |         |         |         |        |                     |       |    |    |    |                    |        |       |

|       | Data from host to device Data from device to host                                                                            |     |                     |     |       |                                        |        |       |        |         |         |         |        |                     |       |    |    |    |                    |        |       |

图 6. Data Frames for Reading Data

When status flags are enabled, APPEND\_STATUS is set to 10b and four bits are appended to the ADC output. The device outputs status flags in this order: {1b, 0b, CRCERR\_IN, ALERT}. The level transitions on the digital interface, resulting from the fixed 1b and 0b in the status flags, can be used to detect if the digital outputs are shorted to a fixed voltage in the system. The CRCERR\_IN flag reflects the corresponding bit in the GENERAL\_CFG register. The ALERT flag is the output of the logical OR of the bits in the EVENT\_FLAG register.

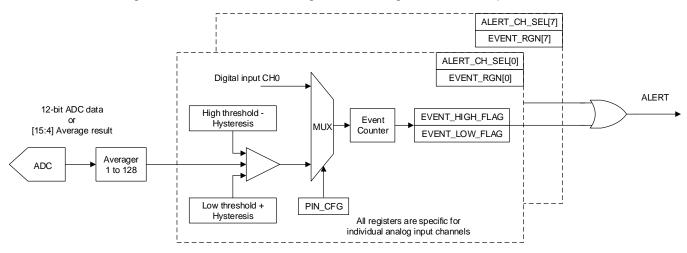

#### 8.3.11 Digital Window Comparator

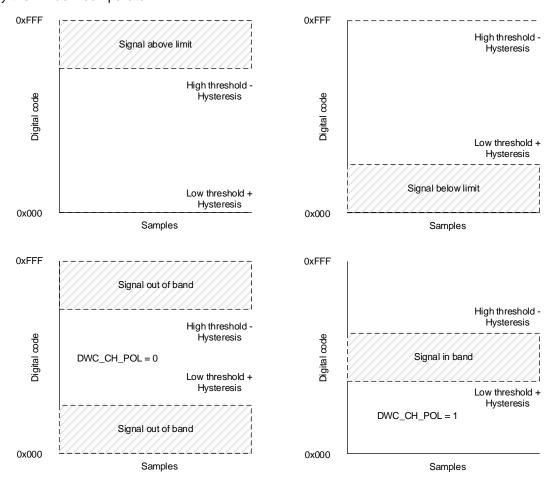

The internal digital window comparator (DWC) is available in all functional modes of the device (see the *Device Functional Modes* section for details). The digital window comparator controls output of the ALERT pin buffer. The ALERT pin can be configured as open-drain (default) or push-pull output using the ALERT\_DRIVE bit in the ALERT\_PIN\_CFG register. 图 7 shows a block diagram for the digital window comparator.

图 7. Digital Window Comparator Block Diagram

图 8. Event Monitoring With the Window Comparator

To enable the digital window comparator, set the DWC\_EN bit in the GENERAL\_CFG register. By default, hysteresis is 0, the high threshold is 0xFFF, and the low threshold is 0x000. A 12-bit straight binary code cannot be higher than 0xFFF or lower than 0x000, thus the thresholds have no effect unless set to different values. 图 8 shows the various types of event that can be detected by adjusting the thresholds. For detecting when a signal is in-band, the EVENT\_RGN register must be configured. In each of the cases shown in 图 8, either or both EVENT\_HIGH\_FLAG and EVENT\_LOW\_FLAG can be set.

The programmable event counter counts consecutive thresholds violations before alert flags can be set. The event count can be set to a higher value to avoid transients in the input signal setting the alert flags.

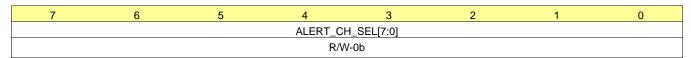

In order to assert the ALERT pin when the alert flag is set for a particular analog input channel, set the corresponding bit in the ALERT\_CH\_SEL register. Alert flags are set regardless of the ALERT\_CH\_SEL configuration if DWC\_EN is 1 and the high or low thresholds are exceeded.

#### 8.3.11.1 Interrupts From Digital Inputs

Logic 1 or logic 0 events can detected on channels configured as digital inputs, as shown in 表 6, by enabling the corresponding ALERT\_CH\_SEL bit.

| 表 6. C | onfiguring | Interrupts | From | <b>Digital</b> | <b>Inputs</b> |

|--------|------------|------------|------|----------------|---------------|

|        |            |            |      |                |               |

| PIN_CFG[7:0] | GPIO_CFG[7:0] | ALERT_CH_SEL[7: 0] | EVENT_RGN [7:0] | EVENT DESCRIPTION                                                |

|--------------|---------------|--------------------|-----------------|------------------------------------------------------------------|

| 1            | 0             | 1                  | 0               | EVENT_HIGH_FLAG is set when digital input channel is at logic 1. |

| 1            | 0             | 1                  | 1               | EVENT_LOW_FLAG is set when digital input channel is at logic 0.  |

#### 8.3.11.2 Changing Digital Outputs on Alert

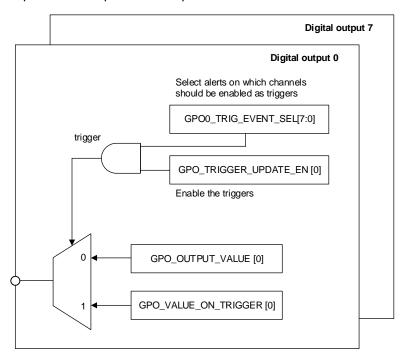

图 9 shows how digital outputs can be updated in response to alerts from individual channels.

图 9. Block Diagram for the Digital Output Logic

#### 8.3.11.2.1 Changing Digital Outputs on Alerts

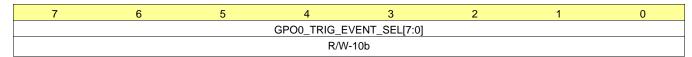

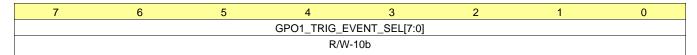

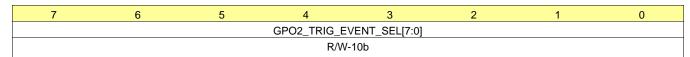

Any given digital output can be updated in response to an alert condition on one or more analog inputs and digital inputs. To update the digital output in response to alert conditions, the trigger must be configured and the value must be launched on the trigger.

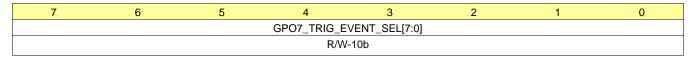

#### 8.3.11.2.1.1 Trigger

The following events can act as triggers for updating the value on the digital output:

- An alert occurs on one or more analog input channels. The digital window comparator must be enabled for these channels.

- An alert occurs on one or more digital input channels. The digital window comparator must be enabled for these channels.

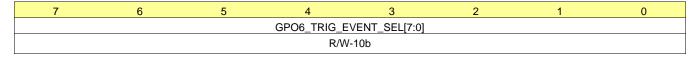

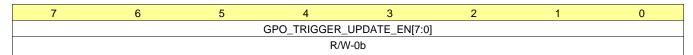

Configure the GPOx\_TRIG\_EVENT\_SEL register to select which channels, analog inputs, or digital inputs can trigger an update on the digital output pin. After configuring the triggers for updating a digital output, the logic can be enabled by configuring the corresponding bit in the GPO\_TRIGGER\_UPDATE\_EN register.

#### 8.3.11.2.1.2 Output Value

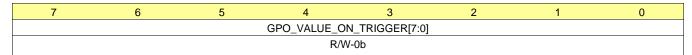

The digital outputs can be set to logic 1 or logic 0 in response to the triggers. The value to be updated on the digital output when a trigger event occurs can be configured in the GPO\_VALUE\_ON\_TRIGGER register.

#### 8.3.12 Minimum, Maximum, and Latest Data Registers

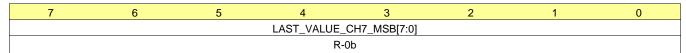

The ADS7138 can record the minimum, maximum, and latest code (statistics registers) for every analog input channel. To enable or re-enable recording statistics, set the STATS\_EN bit in the GENERAL\_CFG register. Writing 1 to the STATS\_EN bit reinitializes the statistics module, after which results from new conversions are recorded in the statistics registers. Until a new conversion result is available, previous values can be read from the statistics registers. Before reading the statistics registers, set STATS\_EN to 0 to prevent any updates to this register block.

#### 8.3.13 I<sup>2</sup>C Protocol Features

#### 8.3.13.1 General Call

On receiving a general call (00h), the device provides an acknowledge (ACK).

#### 8.3.13.2 General Call With Software Reset

On receiving a general call (00h) followed by a software reset (06h), the device resets itself.

#### 8.3.13.3 General Call With a Software Write to the Programmable Part of the Slave Address

On receiving a general call (00h) followed by 04h, the device reevaluates its own I<sup>2</sup>C address configured by the ADDR pin. During this operation, the device does not respond to other I<sup>2</sup>C commands except the general-call command.

#### 8.3.13.4 Configuring the Device for High-Speed I<sup>2</sup>C Mode

The device can be configured in high-speed  $I^2C$  mode by providing an  $I^2C$  frame with one of these codes: 0x09, 0x0B, 0x0D, or 0x0F.

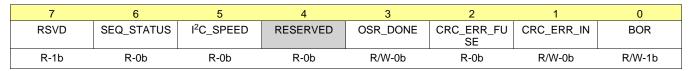

After receiving one of these codes, the device sets the I2C\_HIGH\_SPEED bit in the SYSTEM\_STATUS register and remains in high-speed I<sup>2</sup>C mode until a STOP condition is received in an I<sup>2</sup>C frame.

#### 8.4 Device Functional Modes

表 7 lists the functional modes supported by the ADS7138.

#### 表 7. Functional Modes

| FUNCTIONAL MODE | CONVERSION CONTROL            | MUX CONTROL                   | CONV_MODE[1:0] | SEQ_MODE[1:0] |

|-----------------|-------------------------------|-------------------------------|----------------|---------------|

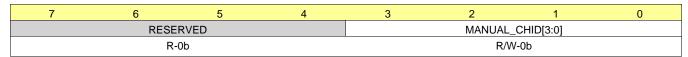

| Manual          | 9th falling edge of SCL (ACK) | Register write to MANUAL_CHID | 00b            | 00b           |

| Auto-sequence   | 9th falling edge of SCL (ACK) | Channel sequencer             | 00b            | 01b           |

| Autonomous      | Internal to the device        | Channel sequencer             | 01b            | 01b           |

The device powers up in manual mode (see the Manual Mode section) and can be configured into any mode listed in 表 7 by writing the configuration registers for the desired mode.

#### 8.4.1 Device Power-Up and Reset

On power-up, the device calculates the address from the resistors connected on the ADDR pin and the BOR bit is set, thus indicating a power-cycle or reset event.

The device can be reset by an I<sup>2</sup>C general call (00h) followed by a software reset (06h), by setting the RST bit, or by recycling the power on the AVDD pin.

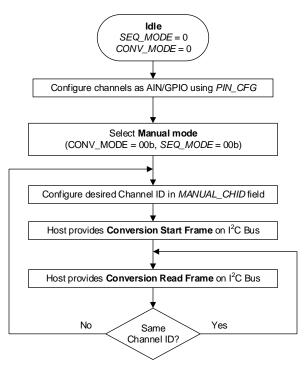

#### 8.4.2 Manual Mode

Manual mode allows the external host processor to directly select the analog input channel. 图 10 lists the steps for operating the device in manual mode.

Manual mode with channel selection using register write

图 10. Device Operation in Manual Mode

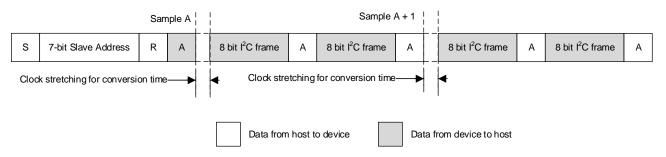

Provide an I<sup>2</sup>C start or restart frame to initiate a conversion, as shown in the conversion start frame of \bigseleft 11. after configuring the device registers. ADC data can be read in subsequent I<sup>2</sup>C frames. The number of I<sup>2</sup>C frames required to read conversion data depends on the output data frame size; see the Output Data Format section for more details. A new conversion is initiated on the ninth falling edge of SCL (ACK bit) when the last byte of output data is read.

图 11. Starting a Conversion and Reading Data in Manual Mode

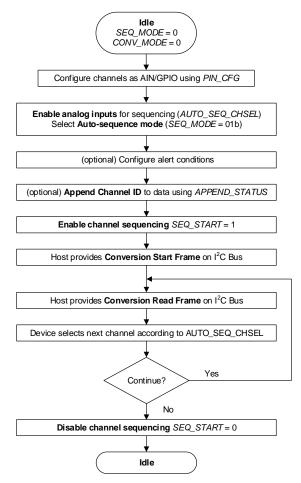

#### 8.4.3 Auto-Sequence Mode

In auto-sequence mode, the internal channel sequencer switches the multiplexer to the next analog input channel after every conversion. The desired analog input channels can be configured for sequencing in the AUTO\_SEQ\_CHSEL register. To enable the channel sequencer, set SEQ\_START to 1b. After every conversion, the channel sequencer switches the multiplexer to the next analog input in ascending order. To stop the channel sequencer from selecting channels, set SEQ\_START to 0b. 2 lists the conversion start and read frames for auto-sequence mode.

图 12. Device Operation in Auto-Sequence Mode

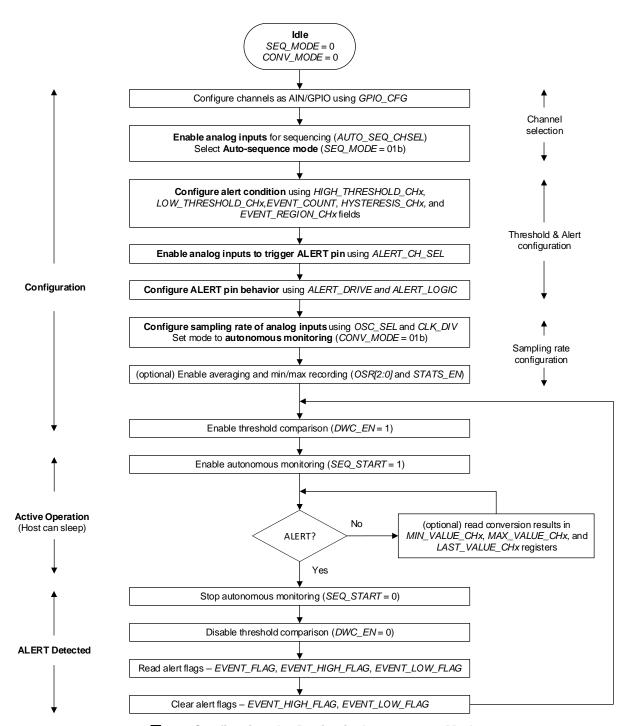

#### 8.4.4 Autonomous Mode

In autonomous mode, the device can be programmed to monitor the voltage applied on the analog input pins of the device and generate a signal on the ALERT pin when the programmable high or low threshold values are crossed. In this mode, the device generates the start of conversion using the internal oscillator. The first start of conversion must be provided by the host and the device then generates the subsequent start of conversions.

图 13. Configuring the Device in Autonomous Mode

#### 8.5 Programming

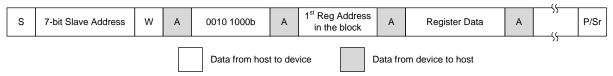

表 8 provides the acronyms for different conditions in an I<sup>2</sup>C frame. 表 9 lists the various command opcodes.

## 表 8. I<sup>2</sup>C Frame Acronyms

| SYMBOL | DESCRIPTION                                      |

|--------|--------------------------------------------------|

| S      | Start condition for the I <sup>2</sup> C frame   |

| Sr     | Restart condition for the I <sup>2</sup> C frame |

| Р      | Stop condition for the I <sup>2</sup> C frame    |

| A      | ACK (low)                                        |

| N      | NACK (high)                                      |

| R      | Read bit (high)                                  |

| W      | Write bit (low)                                  |

## 表 9. Opcodes for Commands

| OPCODE     | COMMAND DESCRIPTION                     |  |  |  |

|------------|-----------------------------------------|--|--|--|

| 0001 0000b | Single register read                    |  |  |  |

| 0000 1000b | Single register write                   |  |  |  |

| 0001 1000b | Set bit                                 |  |  |  |

| 0010 0000b | Clear bit                               |  |  |  |

| 0011 0000b | Reading a continuous block of registers |  |  |  |

| 0010 1000b | Writing a continuous block of registers |  |  |  |

#### 8.5.1 Reading Registers

The I<sup>2</sup>C master can either read a single register or a continuous block registers from the device, as described in the *Single Register Read* and *Reading a Continuous Block of Registers* sections.

#### 8.5.1.1 Single Register Read

To read a single register from the device, the  $I^2C$  master must provide an  $I^2C$  command with three frames to set the register address for reading data.  $\frac{1}{2}$  9 lists the opcodes for different commands. After this command is provided, the  $I^2C$  master must provide another  $I^2C$  frame (as shown in  $\frac{1}{2}$  14) containing the device address and the read bit. After this frame, the device provides the register data. The device provides the same register data even if the host provides more clocks. To end the register read command, the master must provide a STOP or a RESTART condition in the  $I^2C$  frame.

图 14. Reading Register Data

#### 8.5.1.2 Reading a Continuous Block of Registers

To read a continuous block of registers, the I<sup>2</sup>C master must provide an I<sup>2</sup>C command to set the register address. The register address is the address of the first register in the block that must be read. After this command is provided, the I<sup>2</sup>C master must provide another I<sup>2</sup>C frame, as shown in \$\mathbb{Z}\$ 15, containing the device address and the read bit. After this frame, the device provides the register data. The device provides data for the next register when more clocks are provided. When data are read from addresses that do not exist in the register map of the device, the device returns zeros. If the device does not have any further registers to provide data on, the device provide zeros. To end the register read command, the master must provide a STOP or a RESTART condition in the I<sup>2</sup>C frame.

NOTE: S = start, Sr = repeated start, and P = stop.

#### 图 15. Reading a Continuous Block of Registers

#### 8.5.2 Writing Registers

The I<sup>2</sup>C master can either write a single register or a continuous block of registers to the device, set a few bits in a register, or clear a few bits in a register.

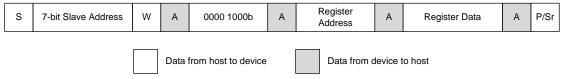

#### 8.5.2.1 Single Register Write

NOTE: S = start, Sr = repeated start, and P = stop.

图 16. Writing a Single Register

#### 8.5.2.2 Set Bit

The I<sup>2</sup>C master must provide an I<sup>2</sup>C command with four frames, as shown in  $\boxtimes$  16, to set bits in a register without changing the other bits. The register address is the address of the register that the bits must set and the register data is the value representing the bits that must be set. Bits with a value of 1 in the register data are set and bits with a value of 0 in the register data are not changed.  $\frac{1}{5}$  9 lists the opcodes for different commands. To end this command, the master must provide a STOP or RESTART condition in the I<sup>2</sup>C frame.

#### 8.5.2.3 Clear Bit

The I<sup>2</sup>C master must provide an I<sup>2</sup>C command with four frames, as shown in 图 16, to clear bits in a register without changing the other bits. The register address is the address of the register that the bits must clear and the register data is the value representing the bits that must be cleared. Bits with a value of 1 in the register data are cleared and bits with a value of 0 in the register data are not changed. 表 9 lists the opcodes for different commands. To end this command, the master must provide a STOP or a RESTART condition in the I<sup>2</sup>C frame.

#### 8.5.2.4 Writing a Continuous Block of Registers

The I<sup>2</sup>C master must provide an I<sup>2</sup>C command, as shown in 图 17, to write a continuous block of registers. The register address is the address of the first register in the block that must be written. The I<sup>2</sup>C master must provide data for registers in subsequent I<sup>2</sup>C frames in an ascending order of register addresses. Writing data to addresses that do not exist in the register map of the device have no effect. 表 9 lists the opcodes for different commands. If the data provided by the I<sup>2</sup>C master exceeds the address space of the device, the device ignores the data beyond the address space. To end the register write command, the master must provide a STOP or a RESTART condition in the I<sup>2</sup>C frame.

NOTE: S = start, Sr = repeated start, and P = stop.

图 17. Writing a Continuous Block of Registers

# 8.6 ADS7138 Registers

Table 10 lists the ADS7138 registers. All register offset addresses not listed in Table 10 should be considered as reserved locations and the register contents should not be modified.

Table 10. ADS7138 Registers

| Table 10. ADS/138 Registers |                  |                                                         |  |  |  |  |  |

|-----------------------------|------------------|---------------------------------------------------------|--|--|--|--|--|

| Address                     | Acronym          | Register Section<br>Name                                |  |  |  |  |  |

| 0x0                         | SYSTEM_STATUS    | SYSTEM_STATUS Register (Address = 0x0) [reset = 0x81]   |  |  |  |  |  |

| 0x1                         | GENERAL_CFG      | GENERAL_CFG Register (Address = 0x1) [reset = 0x0]      |  |  |  |  |  |

| 0x2                         | DATA_CFG         | DATA_CFG Register (Address = 0x2) [reset = 0x0]         |  |  |  |  |  |

| 0x3                         | OSR_CFG          | OSR_CFG Register (Address = 0x3) [reset = 0x0]          |  |  |  |  |  |

| 0x4                         | OPMODE_CFG       | OPMODE_CFG Register (Address = 0x4) [reset = 0x0]       |  |  |  |  |  |

| 0x5                         | PIN_CFG          | PIN_CFG Register (Address = 0x5) [reset = 0x0]          |  |  |  |  |  |

| 0x7                         | GPIO_CFG         | GPIO_CFG Register (Address = 0x7) [reset = 0x0]         |  |  |  |  |  |

| 0x9                         | GPO_DRIVE_CFG    | GPO_DRIVE_CFG Register (Address = 0x9) [reset = 0x0]    |  |  |  |  |  |

| 0xB                         | GPO_OUTPUT_VALUE | GPO_OUTPUT_VALUE Register (Address = 0xB) [reset = 0x0] |  |  |  |  |  |

| 0xD                         | GPI_VALUE        | GPI_VALUE Register (Address = 0xD) [reset = 0x0]        |  |  |  |  |  |

| 0xF                         | ZCD_BLANKING_CFG | ZCD_BLANKING_CFG Register (Address = 0xF) [reset = 0x0] |  |  |  |  |  |

| 0x10                        | SEQUENCE_CFG     | SEQUENCE_CFG Register (Address = 0x10) [reset = 0x0]    |  |  |  |  |  |

| 0x11                        | CHANNEL_SEL      | CHANNEL_SEL Register (Address = 0x11) [reset = 0x0]     |  |  |  |  |  |

| 0x12                        | AUTO_SEQ_CH_SEL  | AUTO_SEQ_CH_SEL Register (Address = 0x12) [reset = 0x0] |  |  |  |  |  |

| 0x14                        | ALERT_CH_SEL     | ALERT_CH_SEL Register (Address = 0x14) [reset = 0x0]    |  |  |  |  |  |

| 0x16                        | ALERT_MAP        | ALERT_MAP Register (Address = 0x16) [reset = 0x0]       |  |  |  |  |  |

| 0x17                        | ALERT_PIN_CFG    | ALERT_PIN_CFG Register (Address = 0x17) [reset = 0x0]   |  |  |  |  |  |

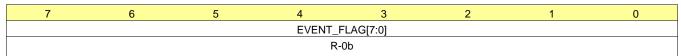

| 0x18                        | EVENT_FLAG       | EVENT_FLAG Register (Address = 0x18) [reset = 0x0]      |  |  |  |  |  |

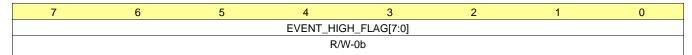

| 0x1A                        | EVENT_HIGH_FLAG  | EVENT_HIGH_FLAG Register (Address = 0x1A) [reset = 0x0] |  |  |  |  |  |

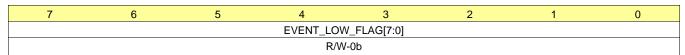

| 0x1C                        | EVENT_LOW_FLAG   | EVENT_LOW_FLAG Register (Address = 0x1C) [reset = 0x0]  |  |  |  |  |  |

| 0x1E                        | EVENT_RGN        | EVENT_RGN Register (Address = 0x1E) [reset = 0x0]       |  |  |  |  |  |

| 0x20                        | HYSTERESIS_CH0   | HYSTERESIS_CH0 Register (Address = 0x20) [reset = 0xF0] |  |  |  |  |  |

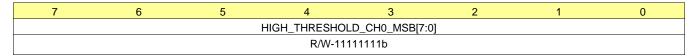

| 0x21                        | HIGH_TH_CH0      | HIGH_TH_CH0 Register (Address = 0x21) [reset = 0xFF]    |  |  |  |  |  |

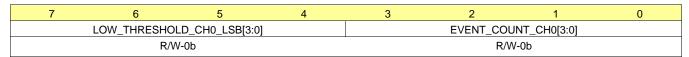

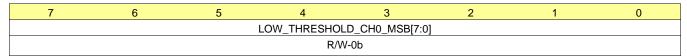

| 0x22                        | EVENT_COUNT_CH0  | EVENT_COUNT_CH0 Register (Address = 0x22) [reset = 0x0] |  |  |  |  |  |

| 0x23                        | LOW_TH_CH0       | LOW_TH_CH0 Register (Address = 0x23) [reset = 0x0]      |  |  |  |  |  |

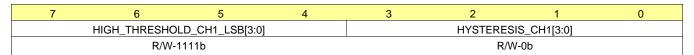

| 0x24                        | HYSTERESIS_CH1   | HYSTERESIS_CH1 Register (Address = 0x24) [reset = 0xF0] |  |  |  |  |  |

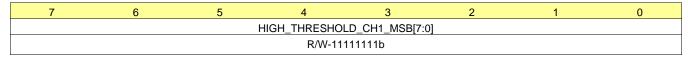

| 0x25                        | HIGH_TH_CH1      | HIGH_TH_CH1 Register (Address = 0x25) [reset = 0xFF]    |  |  |  |  |  |

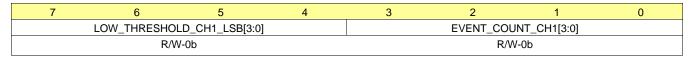

| 0x26                        | EVENT_COUNT_CH1  | EVENT_COUNT_CH1 Register (Address = 0x26) [reset = 0x0] |  |  |  |  |  |

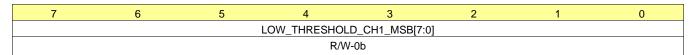

| 0x27                        | LOW_TH_CH1       | LOW_TH_CH1 Register (Address = 0x27) [reset = 0x0]      |  |  |  |  |  |

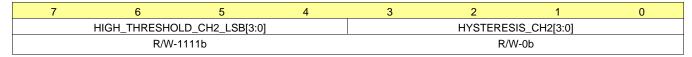

| 0x28                        | HYSTERESIS_CH2   | HYSTERESIS_CH2 Register (Address = 0x28) [reset = 0xF0] |  |  |  |  |  |

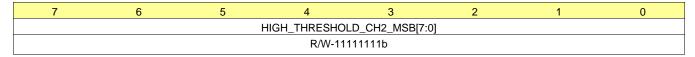

| 0x29                        | HIGH_TH_CH2      | HIGH_TH_CH2 Register (Address = 0x29) [reset = 0xFF]    |  |  |  |  |  |

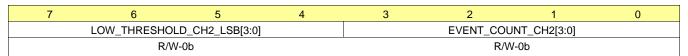

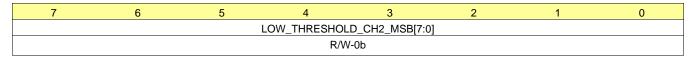

| 0x2A                        | EVENT_COUNT_CH2  | EVENT_COUNT_CH2 Register (Address = 0x2A) [reset = 0x0] |  |  |  |  |  |

| 0x2B                        | LOW_TH_CH2       | LOW_TH_CH2 Register (Address = 0x2B) [reset = 0x0]      |  |  |  |  |  |

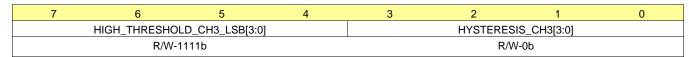

| 0x2C                        | HYSTERESIS_CH3   | HYSTERESIS_CH3 Register (Address = 0x2C) [reset = 0xF0] |  |  |  |  |  |

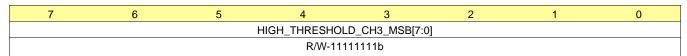

| 0x2D                        | HIGH_TH_CH3      | HIGH_TH_CH3 Register (Address = 0x2D) [reset = 0xFF]    |  |  |  |  |  |

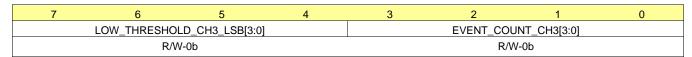

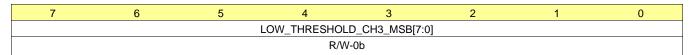

| 0x2E                        | EVENT_COUNT_CH3  | EVENT_COUNT_CH3 Register (Address = 0x2E) [reset = 0x0] |  |  |  |  |  |

| 0x2F                        | LOW_TH_CH3       | LOW_TH_CH3 Register (Address = 0x2F) [reset = 0x0]      |  |  |  |  |  |

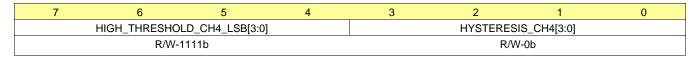

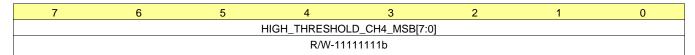

| 0x30                        | HYSTERESIS_CH4   | HYSTERESIS_CH4 Register (Address = 0x30) [reset = 0xF0] |  |  |  |  |  |

| 0x31                        | HIGH_TH_CH4      | HIGH_TH_CH4 Register (Address = 0x31) [reset = 0xFF]    |  |  |  |  |  |

| 0x32                        | EVENT_COUNT_CH4  | EVENT_COUNT_CH4 Register (Address = 0x32) [reset = 0x0] |  |  |  |  |  |

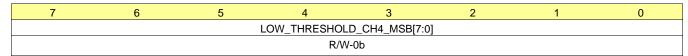

| 0x33                        | LOW_TH_CH4       | LOW_TH_CH4 Register (Address = 0x33) [reset = 0x0]      |  |  |  |  |  |

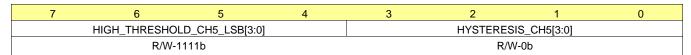

| 0x34                        | HYSTERESIS_CH5   | HYSTERESIS_CH5 Register (Address = 0x34) [reset = 0xF0] |  |  |  |  |  |

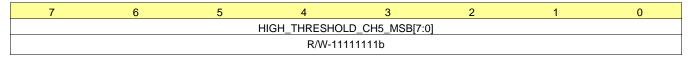

| 0x35                        | HIGH_TH_CH5      | HIGH_TH_CH5 Register (Address = 0x35) [reset = 0xFF]    |  |  |  |  |  |

| L                           | <u> </u>         | = = 0 0 0                                               |  |  |  |  |  |

# Table 10. ADS7138 Registers (continued)

| Address | Acronym         | Register Section<br>Name                                |

|---------|-----------------|---------------------------------------------------------|

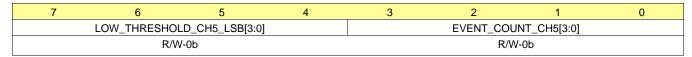

| 0x36    | EVENT_COUNT_CH5 | EVENT_COUNT_CH5 Register (Address = 0x36) [reset = 0x0] |

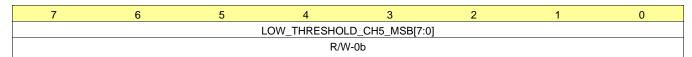

| 0x37    | LOW_TH_CH5      | LOW_TH_CH5 Register (Address = 0x37) [reset = 0x0]      |

| 0x38    | HYSTERESIS_CH6  | HYSTERESIS_CH6 Register (Address = 0x38) [reset = 0xF0] |

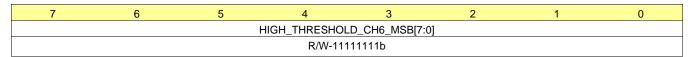

| 0x39    | HIGH_TH_CH6     | HIGH_TH_CH6 Register (Address = 0x39) [reset = 0xFF]    |

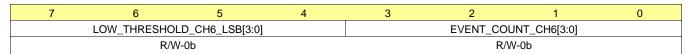

| 0x3A    | EVENT_COUNT_CH6 | EVENT_COUNT_CH6 Register (Address = 0x3A) [reset = 0x0] |

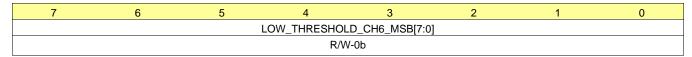

| 0x3B    | LOW_TH_CH6      | LOW_TH_CH6 Register (Address = 0x3B) [reset = 0x0]      |

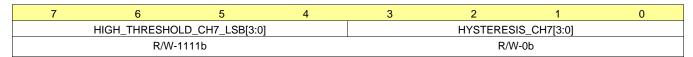

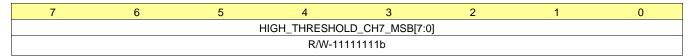

| 0x3C    | HYSTERESIS_CH7  | HYSTERESIS_CH7 Register (Address = 0x3C) [reset = 0xF0] |

| 0x3D    | HIGH_TH_CH7     | HIGH_TH_CH7 Register (Address = 0x3D) [reset = 0xFF]    |

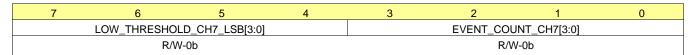

| 0x3E    | EVENT_COUNT_CH7 | EVENT_COUNT_CH7 Register (Address = 0x3E) [reset = 0x0] |

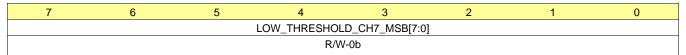

| 0x3F    | LOW_TH_CH7      | LOW_TH_CH7 Register (Address = 0x3F) [reset = 0x0]      |

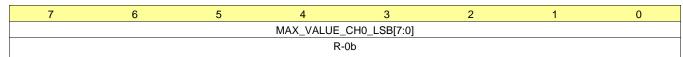

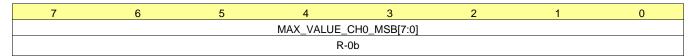

| 0x60    | MAX_CH0_LSB     | MAX_CH0_LSB Register (Address = 0x60) [reset = 0x0]     |

| 0x61    | MAX_CH0_MSB     | MAX_CH0_MSB Register (Address = 0x61) [reset = 0x0]     |

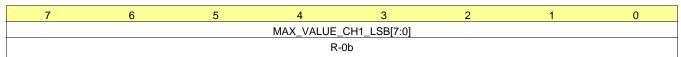

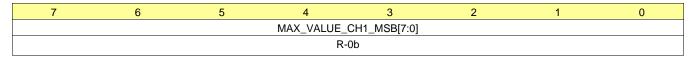

| 0x62    | MAX_CH1_LSB     | MAX_CH1_LSB Register (Address = 0x62) [reset = 0x0]     |

| 0x63    | MAX_CH1_MSB     | MAX_CH1_MSB Register (Address = 0x63) [reset = 0x0]     |

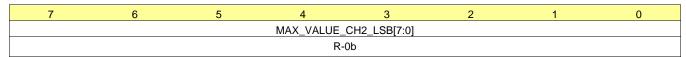

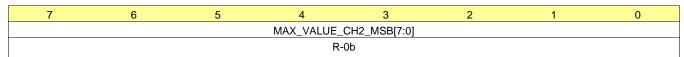

| 0x64    | MAX_CH2_LSB     | MAX_CH2_LSB Register (Address = 0x64) [reset = 0x0]     |

| 0x65    | MAX_CH2_MSB     | MAX_CH2_MSB Register (Address = 0x65) [reset = 0x0]     |

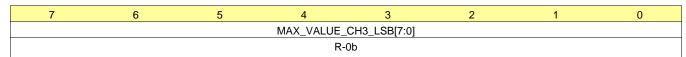

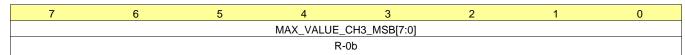

| 0x66    | MAX_CH3_LSB     | MAX_CH3_LSB Register (Address = 0x66) [reset = 0x0]     |

| 0x67    | MAX_CH3_MSB     | MAX_CH3_MSB Register (Address = 0x67) [reset = 0x0]     |

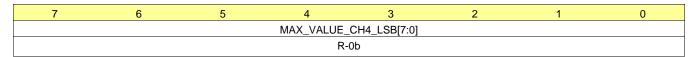

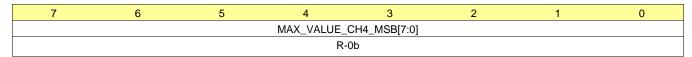

| 0x68    | MAX_CH4_LSB     | MAX_CH4_LSB Register (Address = 0x68) [reset = 0x0]     |

| 0x69    | MAX_CH4_MSB     | MAX_CH4_MSB Register (Address = 0x69) [reset = 0x0]     |

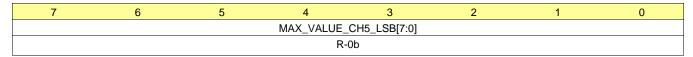

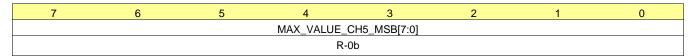

| 0x6A    | MAX_CH5_LSB     | MAX_CH5_LSB Register (Address = 0x6A) [reset = 0x0]     |

| 0x6B    | MAX_CH5_MSB     | MAX_CH5_MSB Register (Address = 0x6B) [reset = 0x0]     |

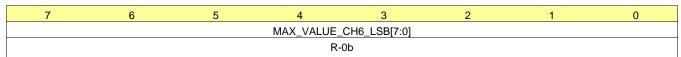

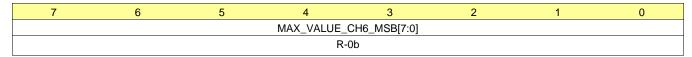

| 0x6C    | MAX_CH6_LSB     | MAX_CH6_LSB Register (Address = 0x6C) [reset = 0x0]     |

| 0x6D    | MAX_CH6_MSB     | MAX_CH6_MSB Register (Address = 0x6D) [reset = 0x0]     |

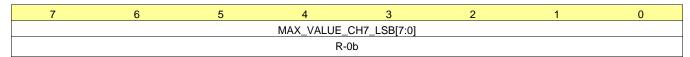

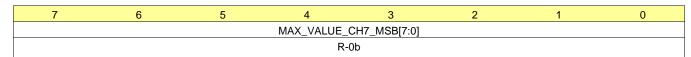

| 0x6E    | MAX_CH7_LSB     | MAX_CH7_LSB Register (Address = 0x6E) [reset = 0x0]     |

| 0x6F    | MAX_CH7_MSB     | MAX_CH7_MSB Register (Address = 0x6F) [reset = 0x0]     |

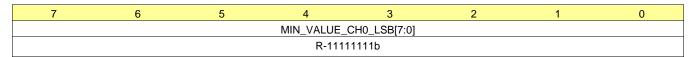

| 0x80    | MIN_CH0_LSB     | MIN_CH0_LSB Register (Address = 0x80) [reset = 0xFF]    |

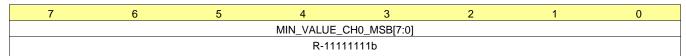

| 0x81    | MIN_CH0_MSB     | MIN_CH0_MSB Register (Address = 0x81) [reset = 0xFF]    |

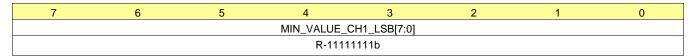

| 0x82    | MIN_CH1_LSB     | MIN_CH1_LSB Register (Address = 0x82) [reset = 0xFF]    |

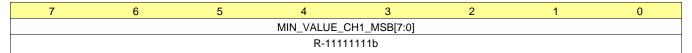

| 0x83    | MIN_CH1_MSB     | MIN_CH1_MSB Register (Address = 0x83) [reset = 0xFF]    |

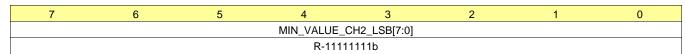

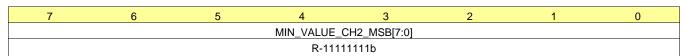

| 0x84    | MIN_CH2_LSB     | MIN_CH2_LSB Register (Address = 0x84) [reset = 0xFF]    |

| 0x85    | MIN_CH2_MSB     | MIN_CH2_MSB Register (Address = 0x85) [reset = 0xFF]    |

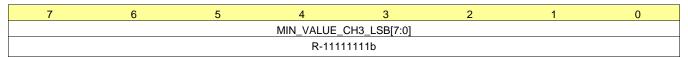

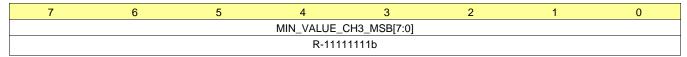

| 0x86    | MIN_CH3_LSB     | MIN_CH3_LSB Register (Address = 0x86) [reset = 0xFF]    |

| 0x87    | MIN_CH3_MSB     | MIN_CH3_MSB Register (Address = 0x87) [reset = 0xFF]    |

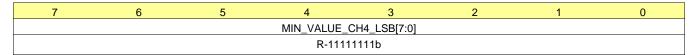

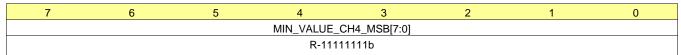

| 0x88    | MIN_CH4_LSB     | MIN_CH4_LSB Register (Address = 0x88) [reset = 0xFF]    |

| 0x89    | MIN_CH4_MSB     | MIN_CH4_MSB Register (Address = 0x89) [reset = 0xFF]    |

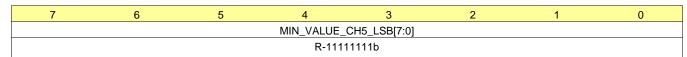

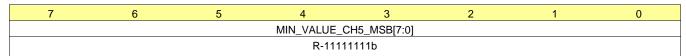

| A8x0    | MIN_CH5_LSB     | MIN_CH5_LSB Register (Address = 0x8A) [reset = 0xFF]    |

| 0x8B    | MIN_CH5_MSB     | MIN_CH5_MSB Register (Address = 0x8B) [reset = 0xFF]    |

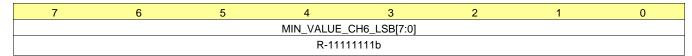

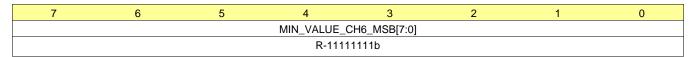

| 0x8C    | MIN_CH6_LSB     | MIN_CH6_LSB Register (Address = 0x8C) [reset = 0xFF]    |

| 0x8D    | MIN_CH6_MSB     | MIN_CH6_MSB Register (Address = 0x8D) [reset = 0xFF]    |

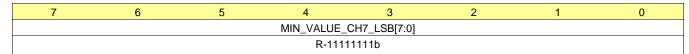

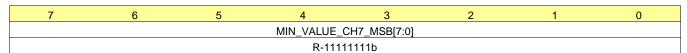

| 0x8E    | MIN_CH7_LSB     | MIN_CH7_LSB Register (Address = 0x8E) [reset = 0xFF]    |

| 0x8F    | MIN_CH7_MSB     | MIN_CH7_MSB Register (Address = 0x8F) [reset = 0xFF]    |

| 0xA0    | RECENT_CH0_LSB  | RECENT_CH0_LSB Register (Address = 0xA0) [reset = 0x0]  |

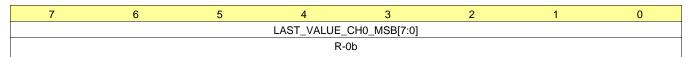

| 0xA1    | RECENT_CH0_MSB  | RECENT_CH0_MSB Register (Address = 0xA1) [reset = 0x0]  |

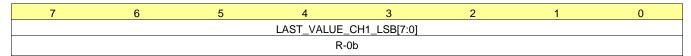

| 0xA2    | RECENT_CH1_LSB  | RECENT_CH1_LSB Register (Address = 0xA2) [reset = 0x0]  |

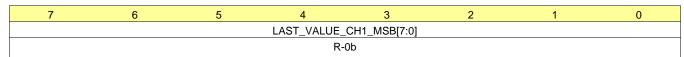

| 0xA3    | RECENT_CH1_MSB  | RECENT_CH1_MSB Register (Address = 0xA3) [reset = 0x0]  |

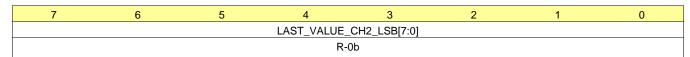

| 0xA4    | RECENT_CH2_LSB  | RECENT_CH2_LSB Register (Address = 0xA4) [reset = 0x0]  |

**ISTRUMENTS**

## Table 10. ADS7138 Registers (continued)

| Address | Acronym             | Register<br>Name | Section                                                     |

|---------|---------------------|------------------|-------------------------------------------------------------|

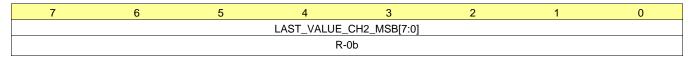

| 0xA5    | RECENT_CH2_MSB      |                  | RECENT_CH2_MSB Register (Address = 0xA5) [reset = 0x0]      |

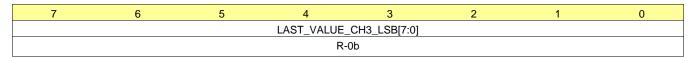

| 0xA6    | RECENT_CH3_LSB      |                  | RECENT_CH3_LSB Register (Address = 0xA6) [reset = 0x0]      |

| 0xA7    | RECENT_CH3_MSB      |                  | RECENT_CH3_MSB Register (Address = 0xA7) [reset = 0x0]      |

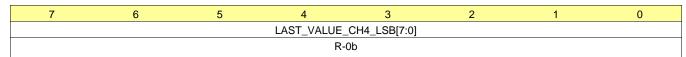

| 0xA8    | RECENT_CH4_LSB      |                  | RECENT_CH4_LSB Register (Address = 0xA8) [reset = 0x0]      |

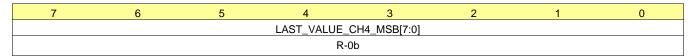

| 0xA9    | RECENT_CH4_MSB      |                  | RECENT_CH4_MSB Register (Address = 0xA9) [reset = 0x0]      |

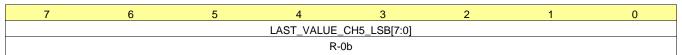

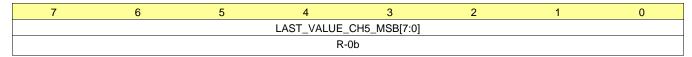

| 0xAA    | RECENT_CH5_LSB      |                  | RECENT_CH5_LSB Register (Address = 0xAA) [reset = 0x0]      |

| 0xAB    | RECENT_CH5_MSB      |                  | RECENT_CH5_MSB Register (Address = 0xAB) [reset = 0x0]      |

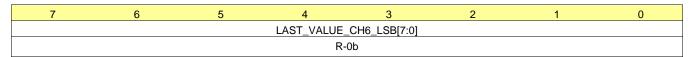

| 0xAC    | RECENT_CH6_LSB      |                  | RECENT_CH6_LSB Register (Address = 0xAC) [reset = 0x0]      |

| 0xAD    | RECENT_CH6_MSB      |                  | RECENT_CH6_MSB Register (Address = 0xAD) [reset = 0x0]      |

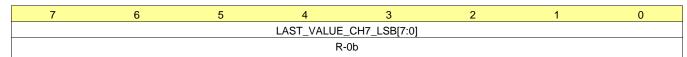

| 0xAE    | RECENT_CH7_LSB      |                  | RECENT_CH7_LSB Register (Address = 0xAE) [reset = 0x0]      |

| 0xAF    | RECENT_CH7_MSB      |                  | RECENT_CH7_MSB Register (Address = 0xAF) [reset = 0x0]      |

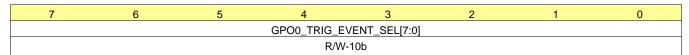

| 0xC3    | GPO0_TRIG_EVENT_SEL |                  | GPO0_TRIG_EVENT_SEL Register (Address = 0xC3) [reset = 0x2] |

| 0xC5    | GPO1_TRIG_EVENT_SEL |                  | GPO1_TRIG_EVENT_SEL Register (Address = 0xC5) [reset = 0x2] |

| 0xC7    | GPO2_TRIG_EVENT_SEL |                  | GPO2_TRIG_EVENT_SEL Register (Address = 0xC7) [reset = 0x2] |

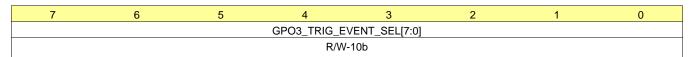

| 0xC9    | GPO3_TRIG_EVENT_SEL |                  | GPO3_TRIG_EVENT_SEL Register (Address = 0xC9) [reset = 0x2] |

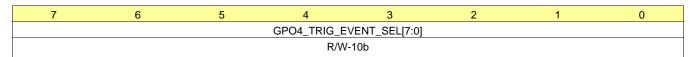

| 0xCB    | GPO4_TRIG_EVENT_SEL |                  | GPO4_TRIG_EVENT_SEL Register (Address = 0xCB) [reset = 0x2] |