Sample &

🖥 Buy

Reference

Design

ZHCS367E - JULY 2011 - REVISED JANUARY 2016

Support &

Community

2.2

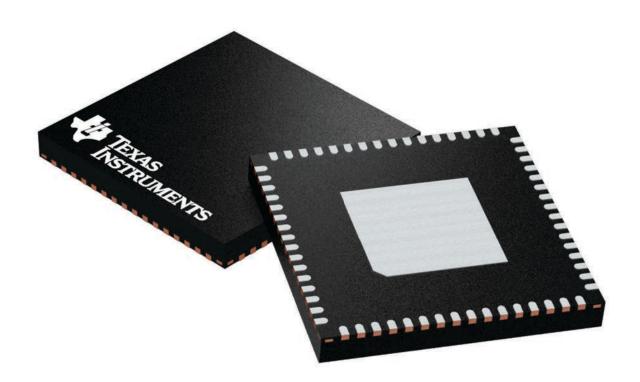

# ADS4249 双通道、14 位、250MSPS 超低功耗 ADC

Technical

Documents

#### 特性 1

- 最大采样率: 250MSPS

- 1.8V 单电源供电,具有超低功耗:

- 250MSPS 时的总功耗为 560mW

- 高动态性能:

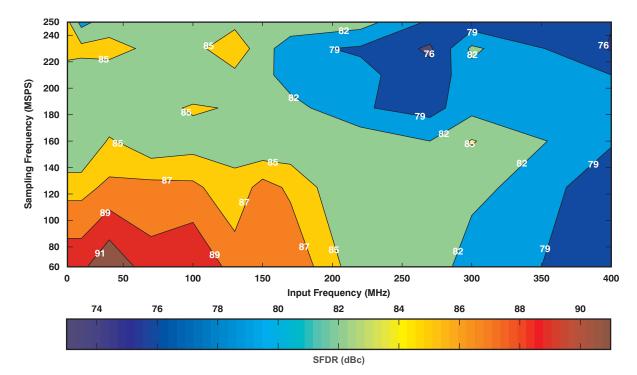

- 170MHz 时的无杂散动态范围 (SFDR) 为 80dBc

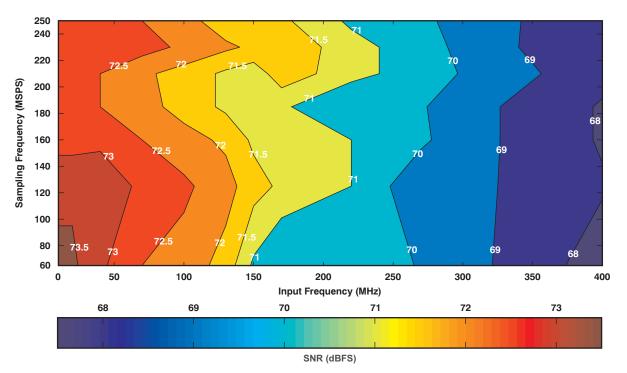

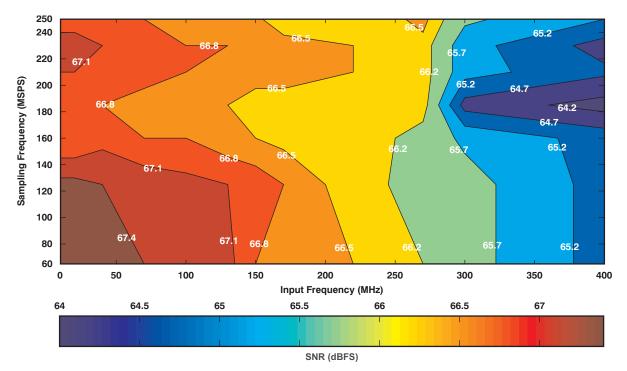

- 170MHz 时的信噪比 (SNR) 为 71.7dBFS

- 串扰: 185MHz 时大于 90dB

- 可编程增益最高达 6dB, 可权衡 SNR/SFDR 性能

- DC 偏移校正

- 输出接口选项:

- 1.8V 并行 CMOS 接口

- 支持可编程摆幅的双倍数据速率 (DDR) 低压动 态信令 (LVDS):

- 标准摆幅: 350mV

- 低摆幅: 200mV

- 支持低输入时钟振幅 低至 200mV<sub>PP</sub>

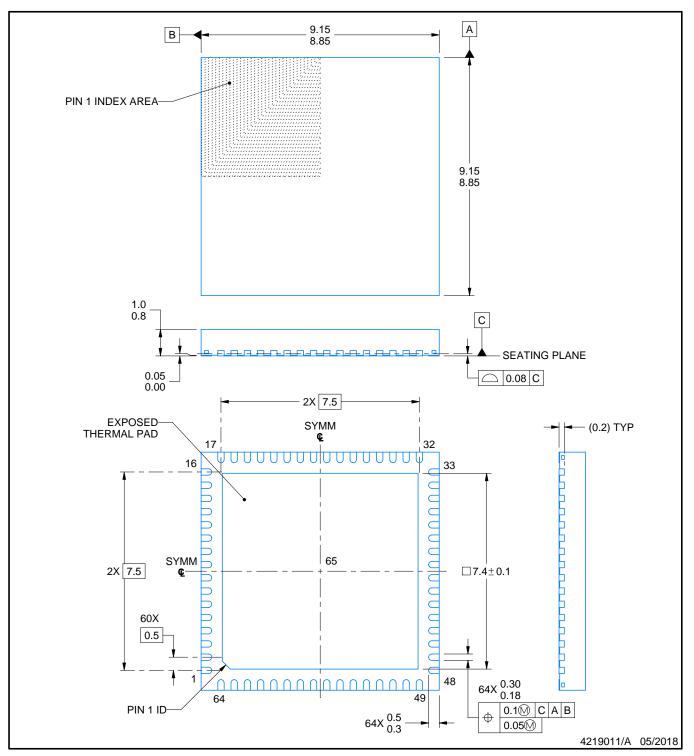

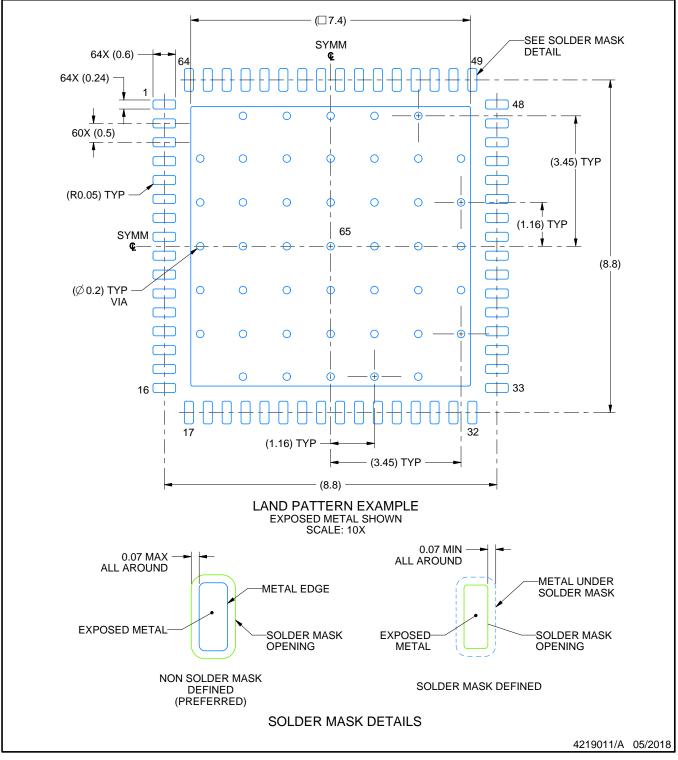

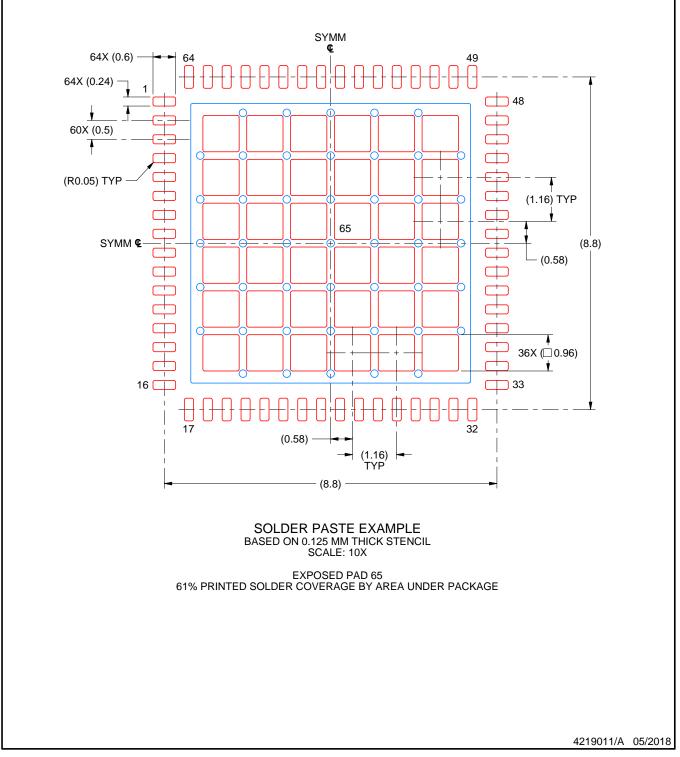

- 封装: 64 引脚 9mm × 9mm 超薄型四方扁平无引 线 (VQFN) 封装

- 2 应用

- 无线通信基础设施

Tools &

Software

- 软件定义的无线电 •

- 功率放大器线性化 •

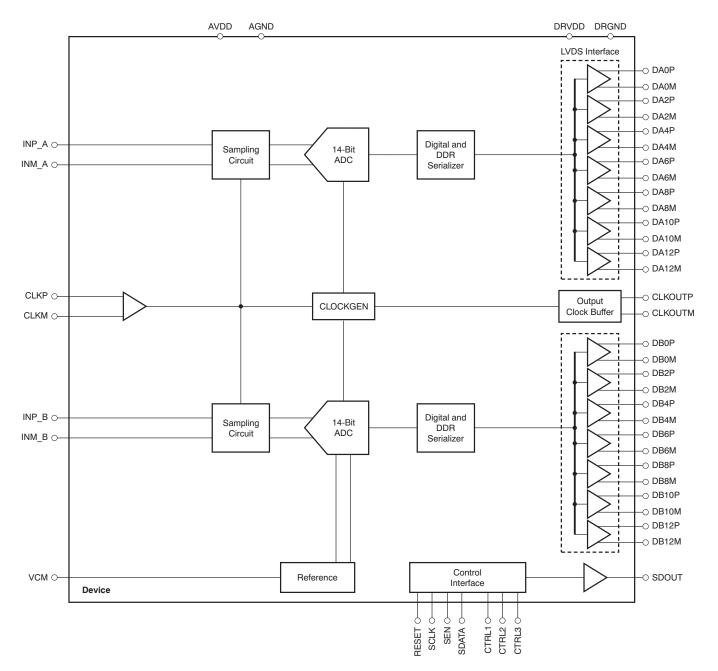

## 3 说明

ADS4249 属于 ADS42xx 双通道、12 位和 14 位模数 转换器 (ADC) 超低功耗系列产品。该器件凭借创新设 计技术实现了高动态性能,并且采用 1.8V 电源供电运 行,功耗极低。该拓扑使 ADS4249 非常适合多载波、 高带宽通信 应用。

ADS4249 具有增益选项,可用于提升在较小满量程输 入范围内的 SFDR 性能。这个器件还包括一个 DC 偏 移校正环路,可用于消除 ADC 偏移。DDR LVDS 与 并行 CMOS 数字输出接口都采用紧凑型 VQFN-64 封 装。PowerPAD™封装。

此器件包含内部基准,并消除了传统基准引脚与相关去 耦电容。ADS4249 的额定工业温度范围为 -40°C 至 85°C。

|         | 11月11日心   |                 |

|---------|-----------|-----------------|

| 器件型号    | 封装        | 封装尺寸(标称值)       |

| ADS4249 | VQFN (64) | 9.00mm x 9.00mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

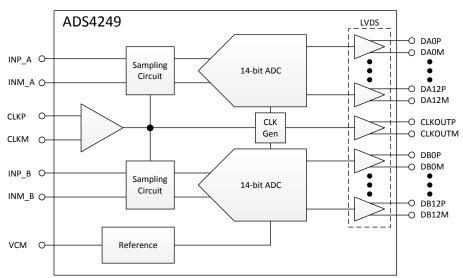

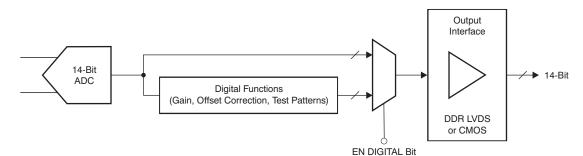

ADS4249 框图

#### ADS4249 ZHCS367E – JULY 2011 – REVISED JANUARY 2016

## 目录

| 特性1                                                   |    |

|-------------------------------------------------------|----|

| 应用1                                                   |    |

| 说明1                                                   |    |

| 修订历史记录 2                                              |    |

| ADS424x, ADS422x Family Comparison                    |    |

| Pin Configuration and Functions                       | 9  |

| Specifications                                        |    |

| 7.1 Absolute Maximum Ratings 10                       |    |

| 7.2 ESD Ratings                                       | 10 |

| 7.3 Recommended Operating Conditions 11               |    |

| 7.4 Thermal Information 11                            |    |

| 7.5 Electrical Characteristics: ADS4249 (250 MSPS) 12 |    |

| 7.6 Electrical Characteristics: General               | 11 |

| 7.7 Digital Characteristics 14                        |    |

| 7.8 LVDS and CMOS Modes Timing Requirements 15        |    |

| 7.9 LVDS Timings at Lower Sampling Frequencies 16     | 12 |

| 7.10 CMOS Timings at Lower Sampling Frequencies 16    |    |

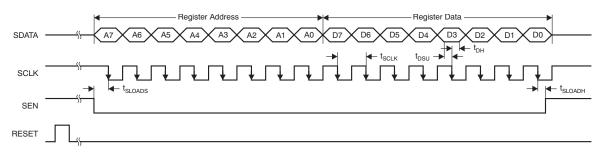

| 7.11 Serial Interface Timing Characteristics 16       |    |

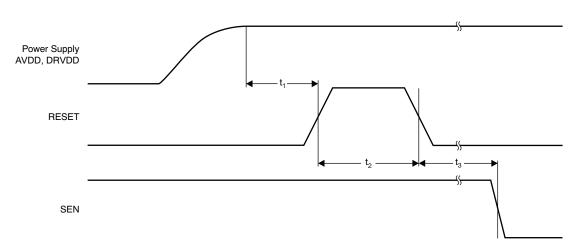

| 7.12 Reset Timing (Only when Serial Interface is      |    |

| Used)                                                 |    |

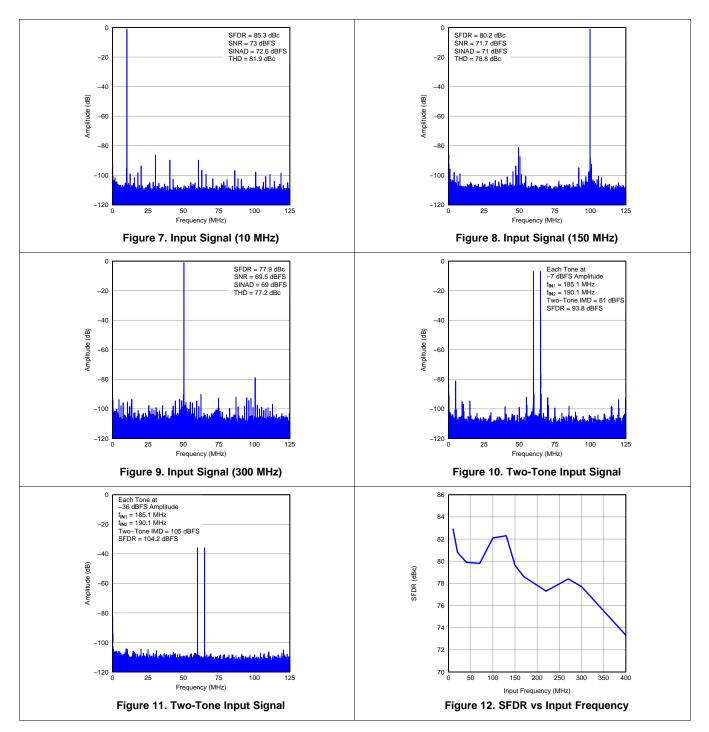

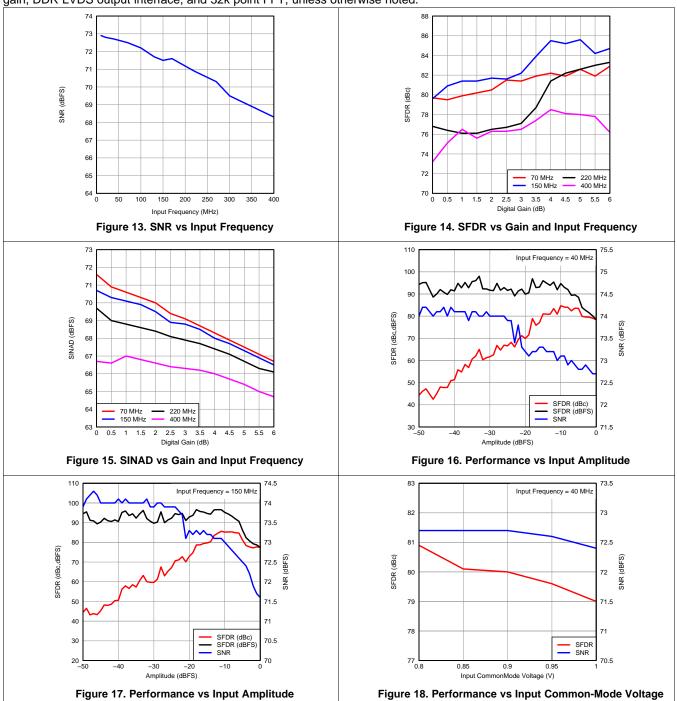

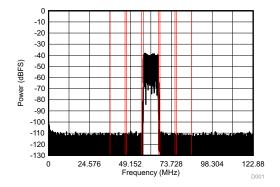

| 7.13 Typical Characteristics                          |    |

| Detailed Description                                  |    |

| 8.1 Overview 28                                       | 13 |

## 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| Ch | nanges from Revision D (May 2015) to Revision E                                                                                                       | Page |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Changed Pin Functions (LVDS Mode) table to comply with RGC Package (LVDS Mode) pin out diagram                                                        | 5    |

| •  | Changed Pin Functions (CMOS Mode) table to comply with RGC Package (CMOS Mode) pin out diagram                                                        | 8    |

| •  | Changed unit in last row of Clock Input, Input clock amplitude differential parameter to V <sub>PP</sub> in Recommended<br>Operating Conditions table | 11   |

| •  | Added text reference for Table 5                                                                                                                      |      |

### Changes from Revision C (July 2012) to Revision D

| • | 已添加 引脚配置和功能部分, | ESD 额定值表, | 特性 描述 部分, | 器件功能模式, | 应用和实施部分, | 电源相关建议部 |   |

|---|----------------|-----------|-----------|---------|----------|---------|---|

|   | 分,布局部分,器件和文档支  | 持部分以及机械   | 、封装和可订购信  | 息部分     |          |         | 1 |

### Changes from Revision B (September 2011) to Revision C

| • | Changed footnote 1 in CMOS Timings at Lower Sampling Frequencies      | 16 |

|---|-----------------------------------------------------------------------|----|

| • | Changed conditions for ADS4249 Typical Characteristics section        | 21 |

| • | Changed register D5h bit names of bits D7, D4, D3, and D0 in Table 10 | 41 |

| • | Changed register address D8 to DB in Table 10                         | 41 |

| • | Changed register address D5h to match change in Table 10              | 53 |

| • | Changed register address DB to match change in Table 10               | 53 |

| 8.3  | Feature Description              | 29               |

|------|----------------------------------|------------------|

| 8.4  | Device Functional Modes          | 31               |

| 8.5  | Programming                      | 37               |

| 8.6  | Register Maps                    | 41               |

| App  | lication and Implementation      | 54               |

| 9.1  | Application Information          | 54               |

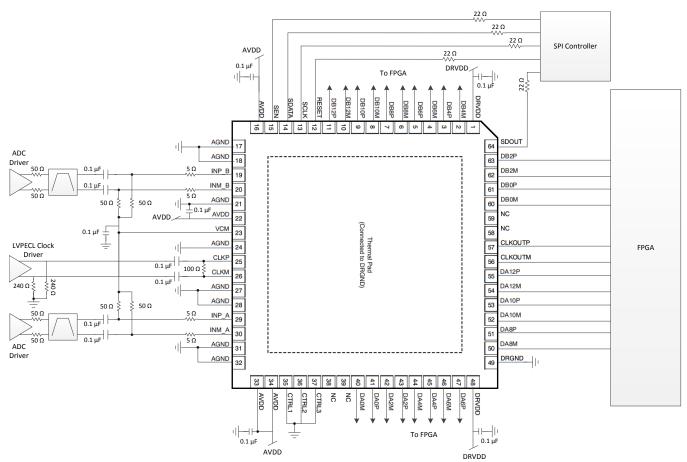

| 9.2  | Typical Application              | <mark>6</mark> 0 |

| Pow  | er Supply Recommendations        | 62               |

| 10.1 | Sharing DRVDD and AVDD Supplies. | 62               |

| 10.2 | Using DC-DC Power Supplies       | 62               |

| 10.3 | Power Supply Bypassing           | 62               |

| Lay  | out                              | 62               |

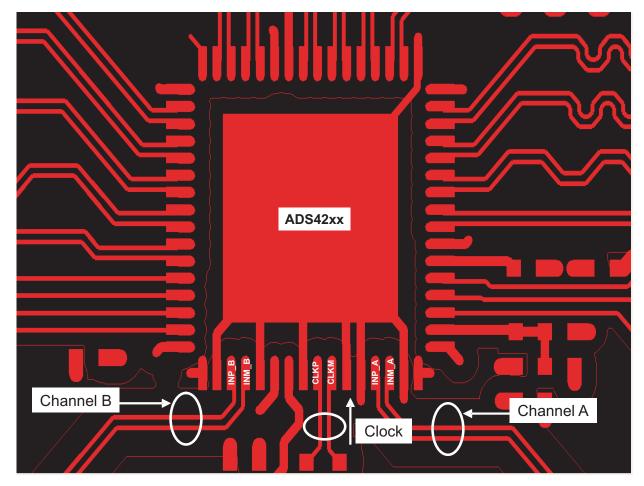

| 11.1 | Layout Guidelines                | 62               |

| 11.2 | Layout Example                   | 63               |

| 器件   | 和文档支持                            | 64               |

| 12.1 | 器件支持                             | 64               |

| 12.2 | 文档支持                             |                  |

| 12.3 | 社区资源                             | 65               |

| 12.4 | 商标                               | 65               |

| 12.5 | 静电放电警告                           | 66               |

8.2 Functional Block Diagram ...... 28

## Page

### Page

### www.ti.com.cn

| Cł | nanges from Revision A (September 2011) to Revision B                                                        | Page |

|----|--------------------------------------------------------------------------------------------------------------|------|

| •  | 己更改 文档状态至"量产数据"                                                                                              | 1    |

| •  | Changed AC power-supply rejection ratio parameter test condition in ADS4249 Electrical Characteristics table | 12   |

NSTRUMENTS

EXAS

## 5 ADS424x, ADS422x Family Comparison<sup>(1)</sup>

|                          | 65 MSPS | 125 MSPS | 160 MSPS | 250 MSPS |

|--------------------------|---------|----------|----------|----------|

| ADS422x<br>12-bit family | ADS4222 | ADS4225  | ADS4226  | ADS4229  |

| ADS424x<br>14-bit family | ADS4242 | ADS4245  | ADS4246  | ADS4249  |

(1) See Table 1 for details on migrating from the ADS62P49 family.

The ADS4249 is pin-compatible with the previous generation ADS62P49 data converter; this similar architecture enables easy migration. However, there are some important differences between the two device generations, summarized in Table 1.

### Table 1. Migrating from the ADS62P49

| ADS62P49                                                 | ADS4249                                                 |  |  |  |

|----------------------------------------------------------|---------------------------------------------------------|--|--|--|

| PINS                                                     |                                                         |  |  |  |

| Pin 22 is NC (not connected)                             | Pin 22 is AVDD                                          |  |  |  |

| Pins 38 and 58 are DRVDD                                 | Pins 38 and 58 are NC (do not connect, must be floated) |  |  |  |

| Pins 39 and 59 are DRGND                                 | Pins 39 and 59 are NC (do not connect, must be floated) |  |  |  |

| SUPPLY                                                   |                                                         |  |  |  |

| AVDD is 3.3 V                                            | AVDD is 1.8 V                                           |  |  |  |

| DRVDD is 1.8 V                                           | No change                                               |  |  |  |

| INPUT COMMON-MODE VOLTAGE                                |                                                         |  |  |  |

| VCM is 1.5 V                                             | VCM is 0.95 V                                           |  |  |  |

| SERIAL INTERFACE                                         |                                                         |  |  |  |

| Protocol: 8-bit register address and 8-bit register data | No change in protocol<br>New serial register map        |  |  |  |

| EXTERNAL REFERENCE                                       |                                                         |  |  |  |

| Supported                                                | Not supported                                           |  |  |  |

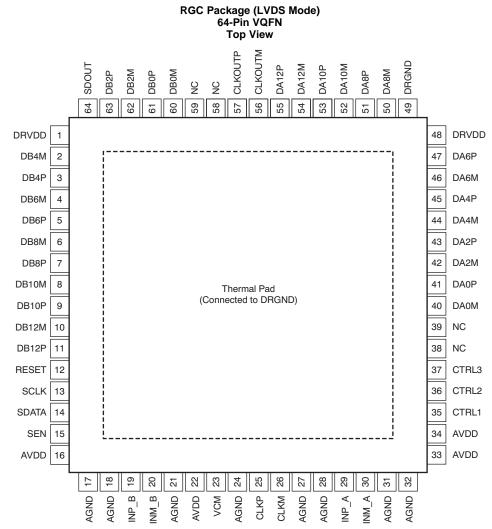

## 6 Pin Configuration and Functions

NOTE: The PowerPAD is connected to DRGND.

NC = do not connect; must float.

Pin Functions (LVDS Mode)

| PIN  |     | I/O | DESCRIPTION         |  |

|------|-----|-----|---------------------|--|

| NAME | NO. | 10  | DESCRIPTION         |  |

|      | 17  |     |                     |  |

|      | 18  |     |                     |  |

|      | 21  |     |                     |  |

| AGND | 24  | - I | Analog ground       |  |

| AGND | 27  |     |                     |  |

|      | 28  |     |                     |  |

|      | 31  |     |                     |  |

|      | 32  |     |                     |  |

|      | 16  |     |                     |  |

| AVDD | 22  |     |                     |  |

| AVDD | 33  | I   | Analog power supply |  |

|      | 34  |     |                     |  |

ADS4249 ZHCS367E – JULY 2011 – REVISED JANUARY 2016

www.ti.com.cn

NSTRUMENTS

**FEXAS**

## Pin Functions (LVDS Mode) (continued)

|         | PIN |     |                                                                                 |

|---------|-----|-----|---------------------------------------------------------------------------------|

| NAME    | NO. | I/O | DESCRIPTION                                                                     |

| CLKM    | 26  | 1   | Differential clock negative input                                               |

| CLKP    | 25  |     | Differential clock positive input                                               |

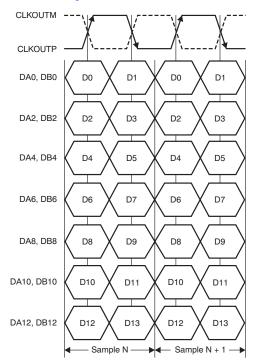

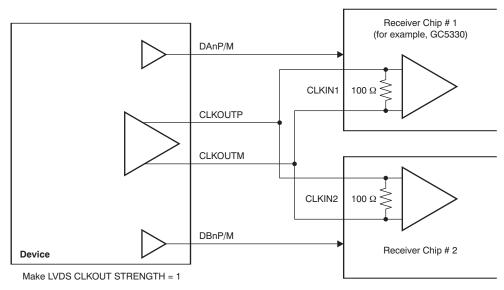

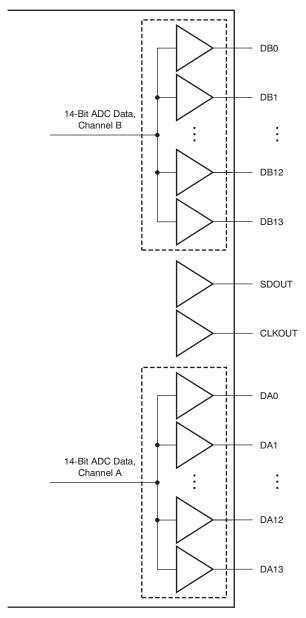

| CLKOUTP | 57  | 0   | Differential output clock, true                                                 |

| CLKOUTM | 56  | 0   | Differential output clock, complement                                           |

| CTRL1   | 35  |     |                                                                                 |

| CTRL2   | 36  | -   | Digital control input pins. Together, these pins control the various power-down |

| CTRL3   | 37  | _   | modes.                                                                          |

| DA0M    | 40  |     |                                                                                 |

| DA0P    | 41  | - O | Channel A differential output data pair, D0 and D1 multiplexed                  |

| DA2M    | 42  |     |                                                                                 |

| DA2P    | 43  | 0   | Channel A differential output data D2 and D3 multiplexed                        |

| DA4M    | 44  |     |                                                                                 |

| DA4P    | 45  | 0   | Channel A differential output data D4 and D5 multiplexed                        |

| DA6M    | 46  |     |                                                                                 |

| DA6P    | 47  | 0   | Channel A differential output data D6 and D7 multiplexed                        |

| DA8M    | 50  |     |                                                                                 |

| DA8P    | 51  | 0   | Channel A differential output data D8 and D9 multiplexed                        |

| DA10M   | 52  |     |                                                                                 |

| DA10P   | 53  | 0   | Channel A differential output data D10 and D11 multiplexed                      |

| DA12M   | 54  |     |                                                                                 |

| DA12P   | 55  | 0   | Channel A differential output data D12 and D13 multiplexed                      |

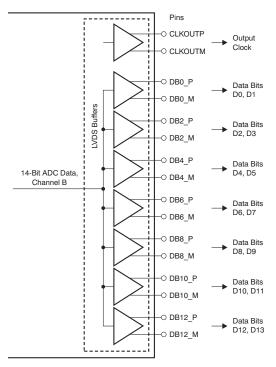

| DB0M    | 60  |     |                                                                                 |

| DB0P    | 61  | 0   | Channel B differential output data pair, D0 and D1 multiplexed                  |

| DB2M    | 62  |     |                                                                                 |

| DB2P    | 63  | 0   | Channel B differential output data D2 and D3 multiplexed                        |

| DB4M    | 2   | 0   | Channel D differential autout data D4 and D5 multiplayed                        |

| DB4P    | 3   | 0   | Channel B differential output data D4 and D5 multiplexed                        |

| DB6M    | 4   | 0   | Channel P differential output date D6 and D7 multiplexed                        |

| DB6P    | 5   | 0   | Channel B differential output data D6 and D7 multiplexed                        |

| DB8M    | 6   | 0   | Channel P differential output date DS and DO multiplexed                        |

| DB8P    | 7   | 0   | Channel B differential output data D8 and D9 multiplexed                        |

| DB10M   | 8   | - O | Channel B differential output data D10 and D11 multiplexed                      |

| DB10P   | 9   | 0   |                                                                                 |

| DB12M   | 10  | 0   | Channel B differential output data D12 and D13 multiplexed                      |

| DB12P   | 11  | 0   |                                                                                 |

| DRGND   | 49  |     | Output buffer ground                                                            |

| BIGHE   | PAD |     |                                                                                 |

| DRVDD   | 1   | - 1 | Output buffer supply                                                            |

|         | 48  |     |                                                                                 |

| INM_A   | 30  | I   | Differential analog negative input, channel A                                   |

| INP_A   | 29  | I   | Differential analog positive input, channel A                                   |

| INM_B   | 20  | 1   | Differential analog negative input, channel B                                   |

| INP_B   | 19  | I   | Differential analog positive input, channel B                                   |

## Pin Functions (LVDS Mode) (continued)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PIN | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 38  |     |                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39  |     | Do not connect must be flooted                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| INC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 58  |     | Do not connect, must be noated                                                                                                                                                                                                                                                                                                                                                                     |  |  |

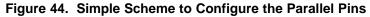

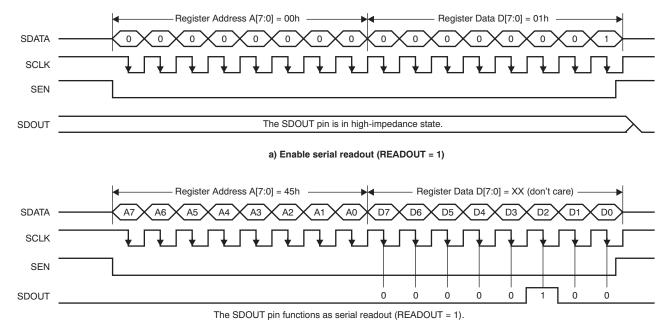

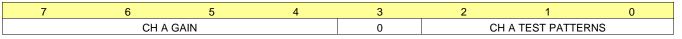

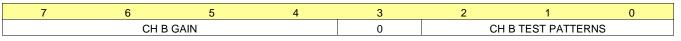

| NAME NO. Description   38 39 - Do not connect, must be floated   58 - Do not connect, must be floated   Figure 100 58 - Do not connect, must be floated   RESET 12 I Serial interface RESET input.<br>When using the serial interface mode, the internal registers must be through a hardware RESET by applying a high pulse on this pin or the software reset option; see the Serial Interface Configuration section.<br>In parallel interface mode, the RESET pin must be permanently tied SCLK and SEN are used as parallel control pins in this mode. This pintermal 150-kΩ pull-down resistor.   SCLK 13 I This pin functions as a serial interface clock input when RESET is lic controls the low-speed mode selection when RESET is tied high; se for detailed information. This pin has an internal 150-kΩ pull-down resistor.   SDATA 14 I Serial interface data input; this pin has an internal 150-kΩ pull-down resistor.   SDOUT 64 O This pin functions as a serial interface register readout when RESET is is enabled. When READUT = 0, this pin is put into a high-impedar   SEN 15 I This pin functions as a serial interface enable input when RESET is controls the output interface and data format selection when RESET is low when READUT = 0, this pin is put into |     |     |                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12  | I   | When using the serial interface mode, the internal registers must be initialized through a hardware RESET by applying a high pulse on this pin or by using the software reset option; see the <i>Serial Interface Configuration</i> section. In parallel interface mode, the RESET pin must be permanently tied high. SCLK and SEN are used as parallel control pins in this mode. This pin has an |  |  |

| SCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13  | I   | This pin functions as a serial interface clock input when RESET is low. SCLK controls the low-speed mode selection when RESET is tied high; see Table 7 for detailed information. This pin has an internal $150$ -k $\Omega$ pull-down resistor.                                                                                                                                                   |  |  |

| SDATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14  | I   | Serial interface data input; this pin has an internal 150-k $\Omega$ pull-down resistor.                                                                                                                                                                                                                                                                                                           |  |  |

| SDOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 64  | О   | This pin functions as a serial interface register readout when the READOUT bit is enabled. When READOUT = 0, this pin is put into a high-impedance state.                                                                                                                                                                                                                                          |  |  |

| SEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15  | I   | This pin functions as a serial interface enable input when RESET is low. SEN controls the output interface and data format selection when RESET is tied high; see Table 8 for detailed information. This pin has an internal 150-k $\Omega$ pullup resistor to AVDD.                                                                                                                               |  |  |

| VCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23  | Ο   | This pin outputs the common-mode voltage (0.95 V) that can be used externally to bias the analog input pins                                                                                                                                                                                                                                                                                        |  |  |

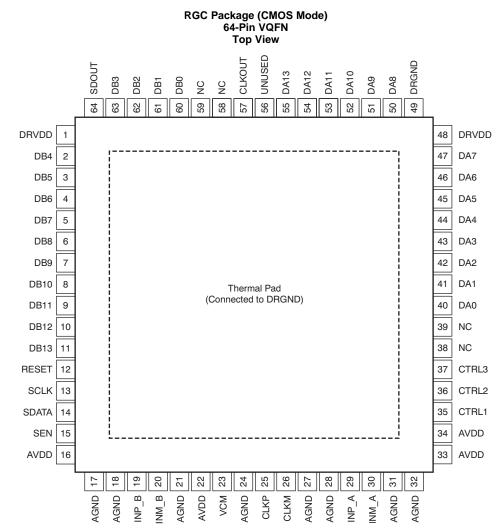

NOTE: The PowerPAD is connected to DRGND. NC = do not connect; must float.

### Pin Functions (CMOS Mode)

|      | PIN                                                                  | I/O | DESCRIPTION                       |  |  |

|------|----------------------------------------------------------------------|-----|-----------------------------------|--|--|

| NAME | NO.                                                                  | 1/0 | DESCRIPTION                       |  |  |

|      | NO.   17   18   21   24   27   28   31   32   16   22   33   34   26 |     |                                   |  |  |

|      | 18                                                                   |     |                                   |  |  |

|      | 21                                                                   |     |                                   |  |  |

| AGND | 24                                                                   |     | Analog ground                     |  |  |

|      | 27                                                                   |     |                                   |  |  |

|      | 28                                                                   |     |                                   |  |  |

|      | 31                                                                   |     |                                   |  |  |

|      | 32                                                                   |     |                                   |  |  |

|      | 16                                                                   |     |                                   |  |  |

| AVDD | 22                                                                   |     | Analog power supply               |  |  |

| AVDD | 33                                                                   | I   | Analog power supply               |  |  |

|      | 34                                                                   |     |                                   |  |  |

| CLKM | 26                                                                   | I   | Differential clock negative input |  |  |

| CLKP | 25                                                                   | I   | Differential clock positive input |  |  |

www.ti.com.cn

## Pin Functions (CMOS Mode) (continued)

|              | PIN |     |                                                                                    |

|--------------|-----|-----|------------------------------------------------------------------------------------|

| NAME         | NO. |     | DESCRIPTION                                                                        |

| CLKOUT       | 57  | 0   | CMOS output clock                                                                  |

| CTRL1        | 35  |     |                                                                                    |

| CTRL2        | 36  | I   | Digital control input pins. Together, these pins control various power-down modes. |

| CTRL3        | 37  |     |                                                                                    |

| DA0          | 40  |     |                                                                                    |

| DA1          | 41  |     |                                                                                    |

| DA2          | 42  |     |                                                                                    |

| DA3          | 43  |     |                                                                                    |

| DA4          | 44  |     |                                                                                    |

| DA5          | 45  |     |                                                                                    |

| DA6          | 46  | _   |                                                                                    |

| DA7          | 47  | 0   | Channel A ADC output data bits, CMOS levels                                        |

| DA8          | 50  | 1   |                                                                                    |

| DA9          | 51  | -   |                                                                                    |

| DA10         | 52  |     |                                                                                    |

| DA11         | 53  |     |                                                                                    |

| DA12         | 54  | _   |                                                                                    |

| DA13         | 55  |     |                                                                                    |

| DB0          | 60  |     |                                                                                    |

| DB1          | 61  |     |                                                                                    |

| DB2          | 62  |     |                                                                                    |

| DB3          | 63  |     |                                                                                    |

| DB4          | 2   |     |                                                                                    |

| DB5          | 3   |     |                                                                                    |

| DB6          | 4   |     |                                                                                    |

| DB7          | 5   | 0   | Channel B ADC output data bits, CMOS levels                                        |

| DB8          | 6   |     |                                                                                    |

| DB9          | 7   |     |                                                                                    |

| DB10         | 8   |     |                                                                                    |

| DB10<br>DB11 | 9   | -   |                                                                                    |

| DB12         | 10  | -   |                                                                                    |

| DB12<br>DB13 | 11  | _   |                                                                                    |

|              | 49  |     |                                                                                    |

| DRGND        | PAD | - I | Output buffer ground                                                               |

|              | 1   |     |                                                                                    |

| DRVDD        | 48  | - I | Output buffer supply                                                               |

| INM_A        | 30  | 1   | Differential analog negative input, channel A                                      |

| INP_A        | 29  |     | Differential analog positive input, channel A                                      |

| INF_A        | 29  |     | Differential analog positive input, channel B                                      |

| INP_B        | 19  | 1   | Differential analog positive input, channel B                                      |

| <u> </u>     | 38  |     |                                                                                    |

|              | 39  | -   |                                                                                    |

| NC           | 58  |     | Do not connect, must be floated                                                    |

|              | 58  | -   |                                                                                    |

|              | 59  |     |                                                                                    |

STRUMENTS

XAS

### Pin Functions (CMOS Mode) (continued)

| PIN    |     | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|--------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME   | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| RESET  | 12  | I   | Serial interface RESET input.<br>When using the serial interface mode, the internal registers must be initialized through a hardware RESET by applying a high pulse on this pin or by using the software reset option; see the <i>Serial Interface Configuration</i> section.<br>In parallel interface mode, the RESET pin must be permanently tied high. SDATA and SEN are used as parallel control pins in this mode. This pin has an internal 150-k $\Omega$ pull-down resistor. |  |  |

| SCLK   | 13  | I   | This pin functions as a serial interface clock input when RESET is low. SCLK controls the low-speed mode when RESET is tied high; see Table 7 for detailed information. This pin has an internal 150-kΩ pull-down resistor.                                                                                                                                                                                                                                                         |  |  |

| SDATA  | 14  | I   | Serial interface data input; this pin has an internal 150-k $\Omega$ pull-down resistor.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| SDOUT  | 64  | О   | This pin functions as a serial interface register readout when the READOUT bit is enabled. When READOUT = 0, this pin is put into a high-impedance state.                                                                                                                                                                                                                                                                                                                           |  |  |

| SEN    | 15  | I   | This pin functions as a serial interface enable input when RESET is low. SEN controls the output interface and data format selection when RESET is tied high; see Table 8 for detailed information. This pin has an internal 150-k $\Omega$ pull-up resistor to AVDD.                                                                                                                                                                                                               |  |  |

| UNUSED | 56  | —   | This pin is not used in the CMOS interface                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| VCM    | 23  | Ο   | This pin outputs the common-mode voltage (0.95 V) that can be used externally to bias the analog input pins                                                                                                                                                                                                                                                                                                                                                                         |  |  |

### 7 Specifications

## 7.1 Absolute Maximum Ratings<sup>(1)</sup>

|                                       |                                                       | MIN  | MAX                          | UNIT |

|---------------------------------------|-------------------------------------------------------|------|------------------------------|------|

| Supply voltage, AVDD                  |                                                       | -0.3 | 2.1                          | V    |

| Supply voltage, DRVDD                 | y voltage, DRVDD                                      |      | 2.1                          | V    |

| Voltage between AGND and DRGNI        | 0                                                     | -0.3 | -0.3 0.3                     |      |

| Voltage between AVDD to DRVDD (       | when AVDD leads DRVDD)                                | -2.4 | 2.4                          | V    |

| Voltage between DRVDD to AVDD (       | Voltage between DRVDD to AVDD (when DRVDD leads AVDD) |      | 2.4                          | V    |

|                                       | INP_A, INM_A, INP_B, INM_B                            | -0.3 | Minimum<br>(1.9, AVDD + 0.3) |      |

| Voltage applied to input pins         | CLKP, CLKM <sup>(2)</sup>                             | -0.3 | AVDD + 0.3                   | V    |

|                                       | RESET, SCLK, SDATA, SEN,<br>CTRL1, CTRL2, CTRL3       | -0.3 | 3.9                          |      |

| Operating free-air temperature, $T_A$ |                                                       | -40  | 85                           | °C   |

| Operating junction temperature, $T_J$ |                                                       |      | 125                          | °C   |

| Storage temperature, T <sub>stg</sub> |                                                       | -65  | 150                          | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) When AVDD is turned off, switching off the input clock (or ensuring the voltage on CLKP, CLKM is less than |0.3 V|) is recommended. This configuration prevents the ESD protection diodes at the clock input pins from turning on.

## 7.2 ESD Ratings

|                    |                         |                                                                   | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

Over operating free-air temperature range, unless otherwise noted.

|                                                |                                                                 | MIN        | NOM      | MAX | UNIT            |

|------------------------------------------------|-----------------------------------------------------------------|------------|----------|-----|-----------------|

| SUPPLIES                                       |                                                                 | ·          |          |     |                 |

| Analog supply voltage, AVDD                    | Analog supply voltage, AVDD                                     |            | 1.8      | 1.9 | V               |

| Digital supply voltage, DRVDD                  |                                                                 | 1.7        | 1.8      | 1.9 | V               |

| ANALOG INPUTS                                  |                                                                 |            |          |     |                 |

| Differential input voltage                     |                                                                 |            | 2        |     | V <sub>PP</sub> |

| Input common-mode                              |                                                                 | VCN        | 1 ± 0.05 |     | V               |

| Maximum analog input frequency w               | ith 2-V <sub>PP</sub> input amplitude <sup>(1)</sup>            |            | 400      |     | MHz             |

| Maximum analog input frequency w               | ith 1-V <sub>PP</sub> input amplitude <sup>(1)</sup>            |            | 600      |     | MHz             |

| CLOCK INPUT                                    |                                                                 |            |          |     |                 |

| Input clock comple rate                        | Low-speed mode enabled <sup>(2)</sup>                           | 1          |          | 80  | MSPS            |

| Input clock sample rate                        | Low-speed mode disabled <sup>(2)</sup> (by default after reset) | 80         |          | 250 |                 |

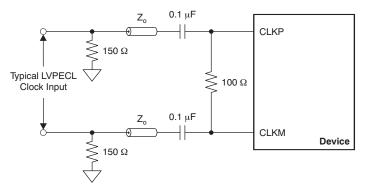

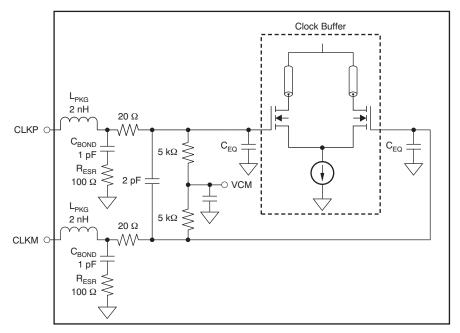

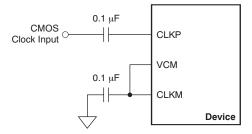

| Input clock sample rate                        | Sine wave, ac-coupled                                           | 0.2        | 1.5      |     |                 |

|                                                | LVPECL, ac-coupled                                              |            | 1.6      |     | M               |

| (V <sub>CLKP</sub> – V <sub>CLKM</sub> )       | LVDS, ac-coupled                                                |            | 0.7      |     | V <sub>PP</sub> |

|                                                | LVCMOS, single-ended, ac-coupled                                |            | 1.5      |     |                 |

| Input clock duty cycle                         | Low-speed mode disabled                                         | 35%        | 50%      | 80  |                 |

|                                                | Low-speed mode enabled                                          | 40%        | 50%      | 60% |                 |

| DIGITAL OUTPUTS                                |                                                                 | - <b>.</b> |          | I   |                 |

| Maximum external load capacitance              | e from each output pin to DRGND, C <sub>LOAD</sub>              |            | 5        |     | pF              |

| Differential load resistance between           | the LVDS output pairs (LVDS mode), R <sub>LOAD</sub>            |            | 100      |     | Ω               |

| Operating free-air temperature, T <sub>A</sub> |                                                                 | -40        |          | +85 | °C              |

(1)

See the *Theory of Operation* section. See the *Serial Interface Configuration* section for details on programming the low-speed mode. (2)

### 7.4 Thermal Information

|                       |                                              | ADS4249    |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RGC (VQFN) | UNIT |

|                       |                                              | 64 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 23.9       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 10.9       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 4.3        | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.1        | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 4.4        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.6        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application (1) report, SPRA953.

ZHCS367E – JULY 2011 – REVISED JANUARY 2016

## 7.5 Electrical Characteristics: ADS4249 (250 MSPS)

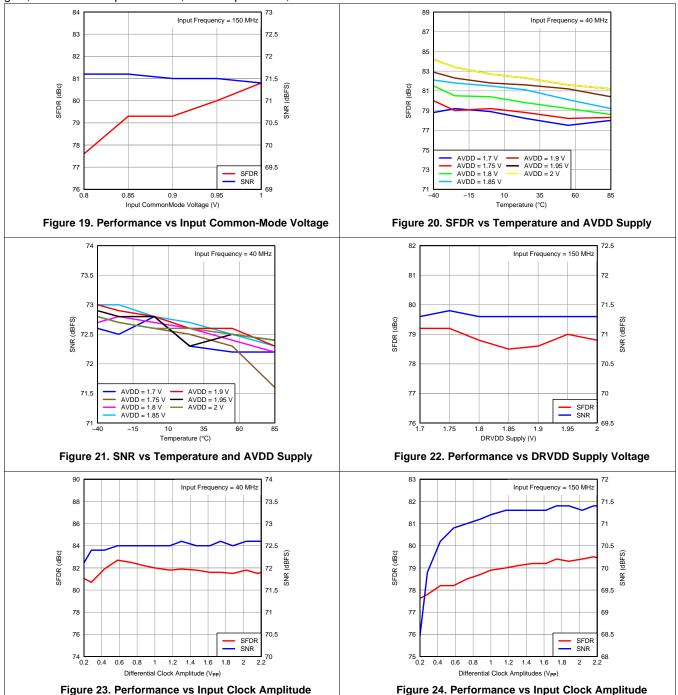

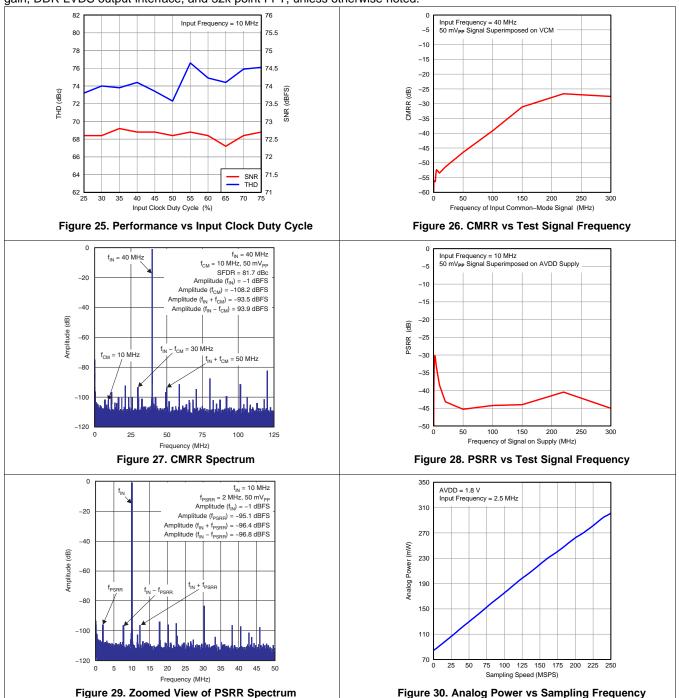

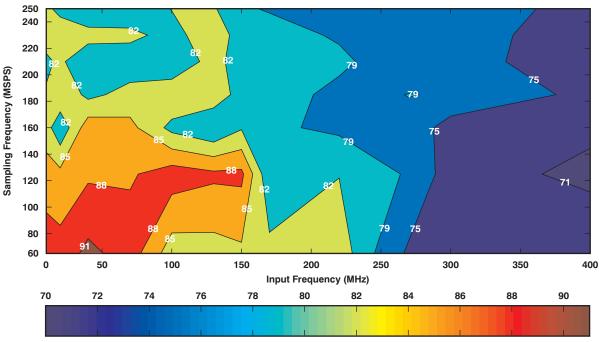

Typical values are at +25°C, AVDD = 1.8 V, DRVDD = 1.8 V, 50% clock duty cycle, -1 dBFS differential analog input, LVDS interface, and 0-dB gain, unless otherwise noted. Minimum and maximum values are across the full temperature range:  $T_{MIN} = -40$ °C to  $T_{MAX} = +85$ °C, AVDD = 1.8 V, and DRVDD = 1.8 V.

|       | PARAMETER                               | TEST CONDITIONS                                                                                      | MIN   | TYP   | MAX  | UNIT        |

|-------|-----------------------------------------|------------------------------------------------------------------------------------------------------|-------|-------|------|-------------|

|       | Resolution                              |                                                                                                      |       |       | 14   | Bits        |

|       |                                         | f <sub>IN</sub> = 20 MHz                                                                             |       | 72.8  |      |             |

|       |                                         | f <sub>IN</sub> = 70 MHz                                                                             |       | 72.5  |      |             |

| SNR   | Signal-to-noise ratio                   | f <sub>IN</sub> = 100 MHz                                                                            |       | 72.2  |      | dBFS        |

|       |                                         | f <sub>IN</sub> = 170 MHz                                                                            | 67.5  | 71.7  |      |             |

|       |                                         | f <sub>IN</sub> = 300 MHz                                                                            |       | 69.4  |      |             |

|       |                                         | f <sub>IN</sub> = 20 MHz                                                                             |       | 72    |      |             |

|       |                                         | f <sub>IN</sub> = 70 MHz                                                                             |       | 71.6  |      |             |

| SINAD | Signal-to-noise and<br>distortion ratio | f <sub>IN</sub> = 100 MHz                                                                            |       | 71.6  |      | dBFS        |

|       |                                         | f <sub>IN</sub> = 170 MHz                                                                            | 66.5  | 70.7  |      |             |

|       |                                         | f <sub>IN</sub> = 300 MHz                                                                            |       | 68.7  |      |             |

|       |                                         | f <sub>IN</sub> = 20 MHz                                                                             |       | 80    |      |             |

|       |                                         | f <sub>IN</sub> = 70 MHz                                                                             |       | 79    |      |             |

| SFDR  | Spurious-free dynamic                   | f <sub>IN</sub> = 100 MHz                                                                            |       | 82    |      | dBc         |

|       | range                                   | f <sub>IN</sub> = 170 MHz                                                                            | 71    | 80    |      |             |

|       |                                         | f <sub>IN</sub> = 300 MHz                                                                            |       | 76    |      |             |

|       |                                         | f <sub>IN</sub> = 20 MHz                                                                             |       | 78    |      |             |

|       |                                         | f <sub>IN</sub> = 70 MHz                                                                             |       | 77    |      |             |

| THD   | Total harmonic distortion               | f <sub>IN</sub> = 100 MHz                                                                            |       | 79    |      | dBc         |

|       |                                         | f <sub>IN</sub> = 170 MHz                                                                            | 69    | 76    |      |             |

|       |                                         | f <sub>IN</sub> = 300 MHz                                                                            |       | 75    |      |             |

|       |                                         | $f_{IN} = 20 \text{ MHz}$                                                                            |       | 80    |      |             |

|       | Second-order harmonic distortion        | f <sub>IN</sub> = 70 MHz                                                                             |       | 79    |      |             |

| HD2   |                                         | f <sub>IN</sub> = 100 MHz                                                                            |       | 81    |      | dBc         |

|       |                                         | f <sub>IN</sub> = 170 MHz                                                                            | 71    | 80    |      | 420         |

|       |                                         | f <sub>IN</sub> = 300 MHz                                                                            |       | 76    |      |             |

|       |                                         | f <sub>IN</sub> = 20 MHz                                                                             |       | 85    |      |             |

|       |                                         | f <sub>IN</sub> = 70 MHz                                                                             |       | 87    |      |             |

| HD3   | Third-order harmonic                    | f <sub>IN</sub> = 100 MHz                                                                            |       | 96    |      | dBc         |

| .20   | distortion                              | f <sub>IN</sub> = 170 MHz                                                                            | 71    | 80    |      | 420         |

|       |                                         | f <sub>IN</sub> = 300 MHz                                                                            |       | 84    |      |             |

|       |                                         | $f_{\rm IN} = 20 \rm MHz$                                                                            |       | 92    |      |             |

|       |                                         | f <sub>IN</sub> = 70 MHz                                                                             |       | 95    |      |             |

|       | Worst spur<br>(other than second and    | f <sub>IN</sub> = 100 MHz                                                                            |       | 94    |      | dBc         |

|       | third harmonics)                        | f <sub>IN</sub> = 170 MHz                                                                            | 77    | 88    |      | ubc         |

|       |                                         | f <sub>IN</sub> = 300 MHz                                                                            |       | 85    |      |             |

|       | Two-tone intermodulation                | $f_{1N} = 600$ km/z<br>$f_{1} = 46$ MHz, $f_{2} = 50$ MHz,<br>each tone at $-7$ dBFS                 |       | 95    |      |             |

| MD    | distortion                              | $f_1 = 185 \text{ MHz}, f_2 = 190 \text{ MHz},$<br>each tone at $-7 \text{ dBFS}$                    |       | 82    |      | dBFS        |

|       | Crosstalk                               | 20-MHz full-scale signal on channel under observation;<br>170-MHz full-scale signal on other channel |       | 95    |      | dB          |

|       | Input overload recovery                 | Recovery to within 1%<br>(of full-scale) for 6 dB overload with sine-wave input                      |       | 1     |      | Clock cycle |

| PSRR  | AC power-supply rejection ratio         | For 50-mV <sub>PP</sub> signal on AVDD supply, up to 10 MHz                                          |       | 30    |      | dB          |

| ENOB  | Effective number of bits                | f <sub>IN</sub> = 170 MHz                                                                            |       | 11.45 |      | LSBs        |

| DNL   | Differential nonlinearity               | f <sub>IN</sub> = 170 MHz                                                                            | -0.95 | ±0.5  | 1.7  | LSBs        |

| NL    | Integrated nonlinearity                 | f <sub>IN</sub> = 170 MHz                                                                            |       | ±2    | ±4.5 | LSBs        |

### 7.6 Electrical Characteristics: General

Typical values are at +25°C, AVDD = 1.8 V, DRVDD = 1.8 V, 50% clock duty cycle, and -1 dBFS differential analog input, unless otherwise noted. Minimum and maximum values are across the full temperature range:  $T_{MIN} = -40$ °C to  $T_{MAX} = +85$ °C, AVDD = 1.8 V, and DRVDD = 1.8 V.

|                    | PARAMETER                                                                                                                     | MIN | TYP                 | MAX | UNIT            |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------|-----|---------------------|-----|-----------------|

| ANALOG I           | NPUTS                                                                                                                         |     |                     |     |                 |

|                    | Differential input voltage range                                                                                              |     | 2                   |     | V <sub>PP</sub> |

|                    | Differential input resistance (at 200 MHz)                                                                                    |     | 0.75                |     | kΩ              |

|                    | Differential input capacitance (at 200 MHz)                                                                                   |     | 3.7                 |     | pF              |

|                    | Analog input bandwidth (with 50- $\Omega$ source impedance, and 50- $\Omega$ termination)                                     |     | 550                 |     | MHz             |

|                    | Analog input common-mode current<br>(per input pin of each channel)                                                           |     | 1.5                 |     | µA/MSPS         |

| VCM                | Common-mode output voltage                                                                                                    |     | 0.95 <sup>(1)</sup> |     | V               |

|                    | VCM output current capability                                                                                                 |     | 4                   |     | mA              |

| DC ACCUF           | ACY                                                                                                                           |     |                     |     |                 |

|                    | Offset error                                                                                                                  | -15 | 2.5                 | 15  | mV              |

|                    | Temperature coefficient of offset error                                                                                       |     | 0.003               |     | mV/°C           |

| E <sub>GREF</sub>  | Gain error as a result of internal reference inaccuracy alone                                                                 | -2  |                     | 2   | %FS             |

| E <sub>GCHAN</sub> | Gain error of channel alone                                                                                                   |     | ±0.1                | 1   | %FS             |

|                    | Temperature coefficient of E <sub>GCHAN</sub>                                                                                 |     | 0.002               |     | ∆%/°C           |

| POWER SI           | JPPLY                                                                                                                         |     |                     |     |                 |

| IAVDD              | Analog supply current                                                                                                         |     | 167                 | 190 | mA              |

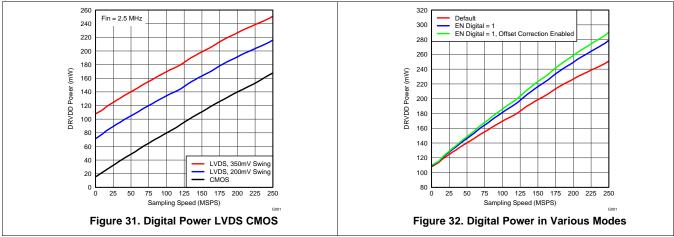

| IDRVDD             | Output buffer supply current, LVDS interface, 350-mV swing with 100- $\Omega$ external termination, $f_{\text{IN}}$ = 2.5 MHz |     | 144                 | 160 | mA              |

| IDRVDD             | Output buffer supply current, CMOS interface, no load capacitance, $f_{\rm IN}$ = 2.5 MHz <sup>(2)</sup>                      |     | 94                  |     | mA              |

|                    | Analog power                                                                                                                  |     | 301                 | 342 | mW              |

|                    | Digital power, LVDS interface, 350-mV swing with 100- $\Omega$ external termination, f <sub>IN</sub> = 2.5 MHz                |     | 259                 | 288 | mW              |

|                    | Digital power, CMOS interface, 8-pF external load capacitance <sup>(2)</sup> , $f_{IN} = 2.5 \text{ MHz}$                     |     | 169                 |     | mW              |

|                    | Global power-down                                                                                                             |     |                     | 25  | mW              |

(1) VCM changes to 0.87 V when serial register bits HIGH PERF MODE[7:2] are set.

(2) In CMOS mode, the DRVDD current scales with the sampling frequency, the load capacitance on output pins, input frequency, and the supply voltage (see the CMOS Interface Power Dissipation section).

### 7.7 Digital Characteristics

At AVDD = 1.8 V and DRVDD = 1.8 V, unless otherwise noted. DC specifications refer to the condition where the digital outputs do not switch, but are permanently at a valid logic level 0 or 1.

| PARA                                      | METER                      | TEST CONDITIONS                           | MIN         | TYP   | MAX  | UNIT |  |

|-------------------------------------------|----------------------------|-------------------------------------------|-------------|-------|------|------|--|

| DIGITAL INPUTS (RESET, SC                 | LK, SDATA, SEN, CTRL       | 1, CTRL2, CTRL3) <sup>(1)</sup>           |             |       |      |      |  |

| High-level input voltage                  |                            | All digital inputs support 1.8-V          | 1.3         |       |      | V    |  |

| ow-level input voltage                    |                            | and 3.3-V CMOS logic levels               |             |       | 0.4  | V    |  |

|                                           | SDATA, SCLK <sup>(2)</sup> | V <sub>HIGH</sub> = 1.8 V                 |             | 10    |      |      |  |

| High-level input current                  | SEN <sup>(3)</sup>         | V <sub>HIGH</sub> = 1.8 V                 |             | 0     | -    | μA   |  |

| Low-level input current                   | SDATA, SCLK                | $V_{LOW} = 0 V$                           |             | 0     |      |      |  |

| Low-level input current                   | SEN                        | $V_{LOW} = 0 V$                           |             | 10    |      | μA   |  |

| DIGITAL OUTPUTS, CMOS IN                  | ITERFACE (DA[13:0], DB     | [13:0], CLKOUT, SDOUT)                    |             |       |      |      |  |

| High-level output voltage                 |                            |                                           | DRVDD – 0.1 | DRVDD |      | V    |  |

| Low-level output voltage                  |                            |                                           |             | 0     | 0.1  | V    |  |

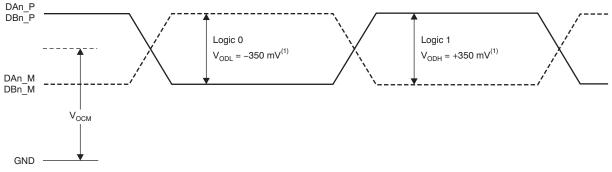

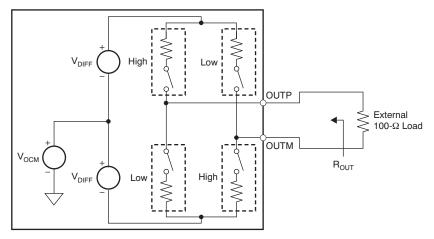

| DIGITAL OUTPUTS, LVDS IN                  | TERFACE                    |                                           |             |       |      |      |  |

| High-level output<br>differential voltage | V <sub>ODH</sub>           | With an external $100-\Omega$ termination | 270         | 350   | 430  | mV   |  |

| Low-level output<br>differential voltage  | V <sub>ODL</sub>           | With an external 100-Ω termination        | -430        | -350  | -270 | mV   |  |

| Output common-mode voltage                | V <sub>OCM</sub>           |                                           | 0.9         | 1.05  | 1.25 | V    |  |

(1) SCLK, SDATA, and SEN function as digital input pins in serial configuration mode.

(2)

SDATA, SCLK have internal 150-k $\Omega$  pull-down resistor. SEN has an internal 150-k $\Omega$  pull-up resistor to AVDD. Because the pull-up is weak, SEN can also be driven by 1.8 V or 3.3 V CMOS (3) buffers.

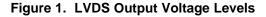

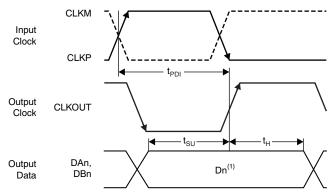

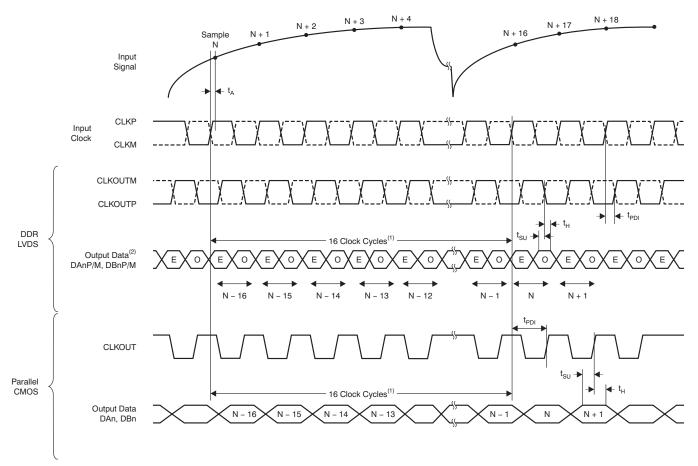

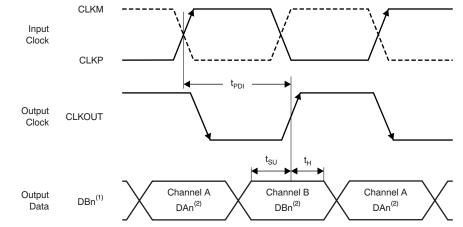

### 7.8 LVDS and CMOS Modes Timing Requirements

Typical values are at +25°C, AVDD = 1.8 V, DRVDD = 1.8 V, sampling frequency = 250 MSPS, sine wave input clock,  $C_{LOAD}$  = 5 pF, and  $R_{LOAD}$  = 100  $\Omega$ , unless otherwise noted. Minimum and maximum values are across the full temperature range:  $T_{MIN}$  = -40°C to  $T_{MAX}$  = +85°C, AVDD = 1.8 V, and DRVDD = 1.7 V to 1.9 V.<sup>(1)</sup>

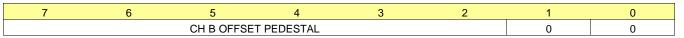

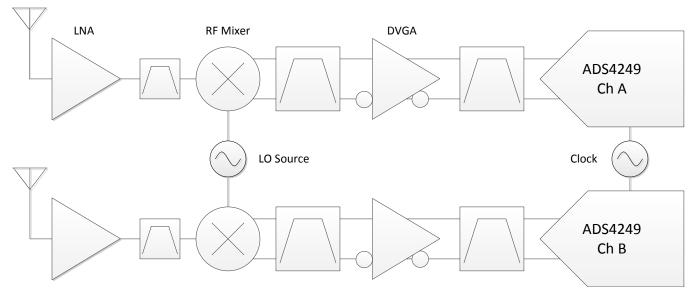

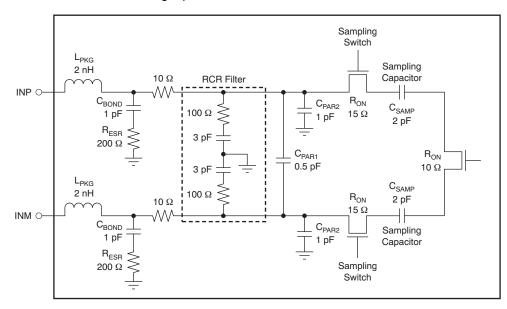

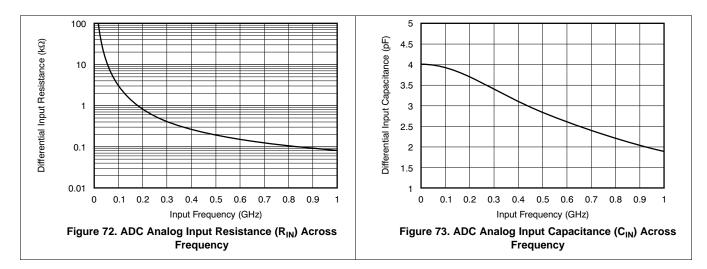

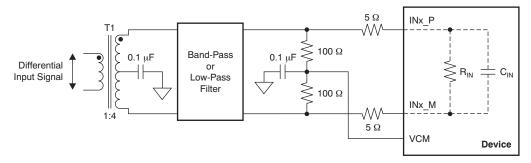

|                                                |                                                                                         |                                                                                                                        | MIN       | TYP  | MAX | UNIT               |