# 输入电压范围 12V 至 100V、输出电流 0.2A 开关转换器

查询样品: UCC25230

## 特性

- 运行为一个降压转换器、或者隔离型正-反 激,Flybuck™ 高度集成转换器

- 从 12V 至 100V 的宽运行输入电压范围, 105V 浪 涌电压。

- 高达 0.2A 的输出电流

- 具有高达 2mA 电流能力的 9V 常开 VDD 输出

- 耐热增强型 4mm x 4mm 小外形尺寸无引线 (SON)-8/S-塑料超薄型小外形尺寸无引线 (PVSON)-N8 (DRM) 封装

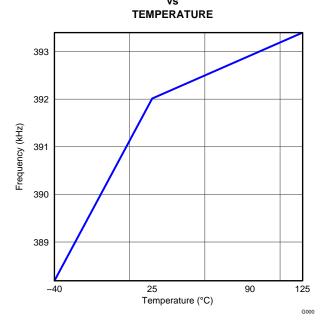

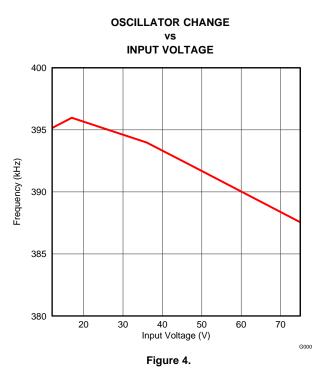

- 内部设定的 380kHz 固定开关频率

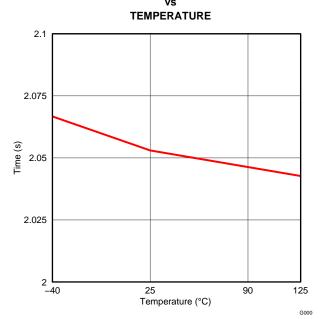

- 内部持续时间为 2ms 的软启动

- 带有输入前馈的电压模式控制可实现最佳输出滤波 器设计

- 2% 精度内部 2.5V 基准

- V<sub>DD</sub>欠压闭锁 (UVLO)

- 针对高电容负载下初次启动的带有频率折返功能的 逐周期电流限制

- 带有输入正常信号的输入 UVLO 和过压闭锁 (OVLO)

- 集成型 110V, 高侧和低侧开关

## 应用范围

- 高密度隔离待机偏置电源

- 直流 (DC) 到 DC 转换器

## 说明

UCC25230 是一款高度集成的脉宽调制 (PWM) 转换 器,此转换器可作为一个隔离式正反激控制器。 它具 有集成的高侧和低侧电源开关,以及包含所有关键转换 器功能的控制电路。 功率级仅需一个或者多个绕组耦 合电感器和输出电容器即可实现完整解决方案。 带有 外部补偿的电压模式前馈控制可在宽输入电压范围内实 现最佳输出滤波器选择。 UCC25230 具有内部设定的 380kHz 固定频率。 它还包括带有滞后的输入电压 UVLO 和 OVLO 比较器,以及可被用于启用 PWM 控 制器的输入正常、开路集电极输出信号。

UCC25230 采用耐热增强型 8 引脚小外形尺寸无引线 (SON) 封装,在此封装中 PowerPad™ 用作一个接地 引脚。

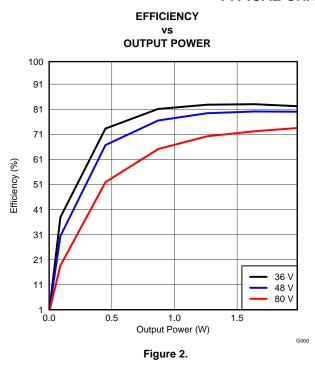

其它特性包括内部软启动和逐周期电流保护。 输入电 压和输出电流范围内隔离转换器的实测效率显示 在Figure 2中。

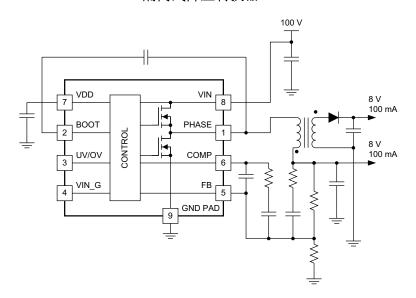

## 隔离式降压转换器。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. PowerPad. Flybuck are trademarks of Texas Instruments.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### **ORDERING INFORMATION**

| TEMPERATURE RANGE, $T_A = T_J$ | PACKAGE                | TAPE AND REEL QTY. | PART NUMBER  |

|--------------------------------|------------------------|--------------------|--------------|

| 40°C to 1425°C                 | CON 9/C DVCON NO (DDM) | 250                | UCC25230DRMT |

| -40°C to +125°C                | SON-8/S-PVSON-N8 (DRM) | 3000               | UCC25230DRMR |

## **ABSOLUTE MAXIMUM RATINGS**(1)(2)

over operating free-air temperature range (unless otherwise noted)

|                                                              |                            | MIN  | MAX                       | UNIT |

|--------------------------------------------------------------|----------------------------|------|---------------------------|------|

| Complements are present VIN                                  | DC                         | -0.3 | 100                       |      |

| Supply voltage range, VIN                                    | Repetitive surge < 200 ms  |      | 105                       |      |

| Outside all and a RIMOF                                      | DC                         | -0.3 | VIN + 0.5                 |      |

| Output voltage on PHASE                                      | Repetitive pulse < 100 ns  | -2   | VIN + 1                   | .,   |

| Voltage                                                      | BOOT with respect to PHASE | -0.3 | 10                        | V    |

| Voltage                                                      | VDD                        | -0.3 | 10                        |      |

| Voltage                                                      | FB, UV/OV, COMP            | -0.3 | VDD                       |      |

| Voltage                                                      | VIN_G                      | -0.3 | 5.5                       |      |

| 50D #                                                        | НВМ                        |      | 2                         | kV   |

| ESD rating                                                   | CDM                        |      | 500                       | V    |

| Sink current                                                 | PHASE (peak)               |      | 220 (internally limited)  | A    |

| Source current                                               | PHASE (peak)               |      | -220 (internally limited) | mA   |

| Operating virtual junction temperature range, T <sub>J</sub> |                            | -40  | 150                       |      |

| Operating ambient temperature range, T <sub>A</sub>          |                            | -40  | 125                       | °C   |

| Storage temperature, T <sub>STG</sub>                        |                            | -65  | 150                       | -0   |

| Lead temperature (soldering, 10 sec.)                        |                            |      | 300                       |      |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>(2)</sup> All voltages are with respect to GND. Currents are positive into, negative out of the specified terminal. Consult Packaging Section of the Databook for thermal limitations and considerations of packages.

## THERMAL INFORMATION

|                  |                                                             | UCC25230 |       |

|------------------|-------------------------------------------------------------|----------|-------|

|                  | THERMAL METRIC <sup>(1)</sup>                               | DRM      | UNITS |

|                  |                                                             | 8 PINS   |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 33.9     |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance (3)               | 33.2     |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance (4)                    | 11.4     | 9000  |

| Ψлт              | Junction-to-top characterization parameter <sup>(5)</sup>   | 0.4      | °C/W  |

| ΨЈВ              | Junction-to-board characterization parameter (6)            | 11.7     |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | 2.3      |       |

- (1) 有关传统和新的热度量的更多信息,请参阅 IC 封装热度量 应用报告 SPRA953。

- (2) 在 JESD51-2a 描述的环境中,按照 JESD51-7 的指定在一个 JEDEC 标准 high-K 测试电路板上进行仿真,从而获得自然对流条件下的结 到外部热阻。

- (3) 通过在封装顶部进行冷板测试仿真来获得结到芯片外壳(顶部)热阻。 不存在特定的 JEDEC 标准测试,但可在 ANSI SEMI 标准 G30-88 中找到内容接近的说明。

- (4) 按照 JESD51-8 中的说明,通过在配有用于控制 PCB 温度的环形冷板夹具的环境中进行仿真,以获得结到电路板热阻。

- (5) 结到顶部的表征参数(ψ<sub>JT</sub>)估算真实系统中器件的结温,并使用 JESD51-2a(第 6 章和第 7 章)中描述的程序从**从得到** θ<sub>JA</sub>的仿真数据中 提取出该参数。

- (6) 结到电路板的表征参数(Ψ<sub>JB</sub>) 估算真实系统中器件的结温,并使用 JESD51-2a(第 6 章和第7 章)中描述的程序从从得到 θ<sub>JA</sub> 的仿真数据 中提取出该参数。

- (7) 通过在裸(电源)焊盘上进行冷板测试仿真来获得结到芯片外壳(底部)热阻。 不存在特定的 JEDEC 标准测试,但在 ANSI SEMI 标准 G30-88 中找到了内容接近的说明。

#### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                                 | MIN | TYP | MAX                     | UNIT |

|-------------------------------------------|-----|-----|-------------------------|------|

| Supply voltage range, VIN                 | 12  | 48  | 75,<br>(100 V for 1 ms) | V    |

| Supply bypass capacitor, C <sub>VIN</sub> |     | 1.0 |                         |      |

| Supply bypass capacitor, C <sub>VDD</sub> | 0.1 | 1.0 | 2.2                     | μF   |

| Operating junction temperature range      | -40 |     | +125                    | °C   |

## **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 48 V, 1- $\mu$ F capacitor from VIN to GND, 1- $\mu$ F capacitor from VDD to GND,  $T_A$  =  $T_J$  = -40°C to 125°C, (unless otherwise noted)

| PARAMETER              |                                                  | TEST CONDITION                            | MIN      | TYP | MAX      | UNITS |

|------------------------|--------------------------------------------------|-------------------------------------------|----------|-----|----------|-------|

| Supply C               | urrents                                          | ·                                         | <u> </u> |     |          |       |

| I <sub>VIN</sub>       | Quiescent current                                | V <sub>IN</sub> = 5 V                     |          | 0.5 | 2        | ^     |

| I <sub>VINO</sub>      | V <sub>IN</sub> operating current                | FB = COMP                                 |          | 4.5 | 10       | mA    |

| VDD Reg                | ulator                                           |                                           | <u> </u> |     | <u>.</u> |       |

| $V_{DD}$               | VDD, output voltage                              |                                           | 8.46     | 9   | 9.54     | V     |

|                        | Line regulation                                  | 17 V < V <sub>IN</sub> < 75 V             |          | ±5  | ±40      | \/    |

|                        | Load regulation                                  | -2 mA < I <sub>VDD</sub> < 0 mA           |          | ±5  | ±40      | mV    |

|                        | VDD current limit (when V <sub>DD</sub> = 5.5 V) |                                           | -2       | -6  | -13      | mA    |

| Internal (             | Jndervoltage Lockout (V <sub>DD_UVLO</sub> )     |                                           |          |     |          |       |

| VDD <sub>rising</sub>  | VDD rising threshold                             |                                           | 7.0      | 7.5 | 8        |       |

| VDD <sub>hyst</sub>    | VDD threshold hysteresis                         |                                           | 0.4      | 0.7 | 1.1      | V     |

| VDD <sub>falling</sub> | VDD falling threshold                            |                                           | 6.3      | 6.8 | 7.3      |       |

| Undervol               | tage (external programmable)                     |                                           |          |     |          |       |

|                        | Falling threshold                                |                                           | 0.9      | 1.0 | 1.1      | V     |

|                        | Ihyst                                            |                                           | 7        | 11  | 18       | μΑ    |

| Overvolta              | age (external programmable)                      |                                           |          |     | •        |       |

|                        | OVLO Rising threshold                            |                                           | 4.5      | 5   | 5.5      | V     |

|                        | Ihyst                                            |                                           | -15      | -22 | -40      | μΑ    |

| VIN Powe               | er GOOD                                          | ·                                         | <u> </u> |     |          |       |

|                        | PG output sink resistance                        | $I_{PG} = 5 \text{ mA to } 10 \text{ mA}$ |          | 50  | 100      | Ω     |

| Oscillato              | r                                                |                                           |          |     | •        |       |

| f                      | Oscillator frequency fixed                       |                                           | 324      | 380 | 445      | kHz   |

| DC <sub>MIN</sub>      | Minimum duty cycle                               | FB = 3.0 V                                |          |     | 0%       |       |

| DC <sub>MAX</sub>      | Maximum duty cycle                               | FB = 2.0 V                                | 85%      |     |          |       |

|                        | Frequency variation                              | 12 V < V <sub>IN</sub> < 75 V             | -15%     |     | 15%      |       |

# **ELECTRICAL CHARACTERISTICS (continued)**

$V_{IN}$  = 48 V, 1- $\mu$ F capacitor from VIN to GND, 1- $\mu$ F capacitor from VDD to GND,  $T_A$  =  $T_J$  = -40°C to 125°C, (unless otherwise noted)

|                        | PARAMETER                                               | TEST CONDITION                   | MIN     | TYP     | MAX  | UNITS |

|------------------------|---------------------------------------------------------|----------------------------------|---------|---------|------|-------|

| Error Am               | plifier                                                 | ,                                | -       | 1       | •    |       |

|                        | FB = COMP, (T = 25°C)                                   |                                  | 2.42    | 2.50    | 2.58 |       |

|                        | REF voltage                                             | FB = COMP,<br>(T = -40 to 125°C) | 2.40    | 2.50    | 2.60 | V     |

| Avol                   | Avol open loop voltage gain                             |                                  | 40      | 80      |      | dB    |

|                        | Input leakage current, FB                               |                                  |         |         | ±2   | μΑ    |

| I <sub>COM(sink)</sub> | COMP sink current                                       | V <sub>COMP</sub> = 4.5 V        | 2       | 4.8     | 10   |       |

| I <sub>COM(sourc</sub> | COMP source current                                     | V <sub>COMP</sub> = 4.5 V        | -2      | -6.1    | -12  | mA    |

| V <sub>OL</sub>        | COMP voltage range                                      | I <sub>COMP</sub> = 100 μA       |         | .4      | 1.2  | V     |

| V <sub>OH</sub>        | COMP voltage range                                      | I <sub>COMP</sub> = -100 μA      | VDD-1.2 | VDD-0.7 | VDD  | V     |

| Soft Start             |                                                         | •                                | ·       |         |      |       |

|                        | Time for COMP to ramp                                   | FB = COMP                        | 1.75    | 2.05    | 2.35 | ms    |

| Output                 |                                                         |                                  |         |         |      |       |

|                        | R <sub>DS(on)</sub> high                                | V <sub>IN</sub> = 48 V           |         | 6       | 15   | Ω     |

|                        | R <sub>DS(on)</sub> low                                 | V <sub>IN</sub> = 48 V           |         | 5       | 10   | 12    |

|                        | Max average current                                     |                                  |         | 200     |      | mA    |

| ILIMIT <sup>(1)</sup>  |                                                         | •                                | ·       |         |      |       |

|                        | ILIMIT phase high                                       | V <sub>IN</sub> = 30 V           | -600    | -400    | -220 | mA    |

|                        | Propagation delay, blanking delay plus ILIMIT delay     |                                  | 60      | 100     | 140  | ns    |

|                        | ILIMIT phase low                                        | V <sub>IN</sub> = 30 V           | 220     | 400     | 600  | mA    |

|                        | Propagation delay, blanking delay plus ILIMIT delay (2) |                                  | 60      | 100     | 140  | ns    |

<sup>(1)</sup> Continued operation while in ILIM could exceed the maximum power dissipation for the device. For Non-Isolated applications additional external over current protection may be required.

<sup>(2)</sup> Specified by design, not production tested.

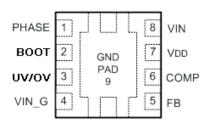

## **DEVICE INFORMATION**

Figure 1.

## **TERMINAL FUNCTIONS**

| TERM                | MINAL | DESCRIPTION |                                                                                                                                                                                  |

|---------------------|-------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                | NO.   | 1/0         | DESCRIPTION                                                                                                                                                                      |

| PHASE               | 1     | 0           | Phase output of high-side and low-side power FETs.                                                                                                                               |

| воот                | 2     | I           | 0.1-µF capacitor connected between BOOT and PHASE pins along with the internal diode between BOOT and VDD provides supply voltage to the drive circuit of the upper power FET.   |

| UV/OV               | 3     | I           | Input to internal comparators. Internal linear regulator remains functional. A bypass cap of at least 1000 pF is recommended.                                                    |

| VIN_G               | 4     | 0           | VIN power good. Open drain output, state determined by UV/OV pin.                                                                                                                |

| FB                  | 5     | I           | Error amplifier inverting input. Connect to output voltage divider with compensation circuit to this pin.                                                                        |

| COMP <sup>(1)</sup> | 6     | 0           | Output of error amplifier.                                                                                                                                                       |

| VDD                 | 7     | 0           | Output of internal linear regulator. Bypass VDD pin to GND pins close to device package with a high quality, low ESR 1-µF ceramic capacitor.                                     |

| VIN                 | 8     | I           | Input supply for the power MOSFET switches and internal bias regulator. Bypass VIN pins to GND pins close to device package with a high quality, low ESR 1-µF ceramic capacitor. |

| GND PAD             | 9     | -           | Thermal ground pad and electrical ground for the device.                                                                                                                         |

<sup>(1)</sup> Input feed forward control with RAMP magnitude  $V_{\text{IN}}$  x 6%.

## **Detailed Pin Description**

**PHASE (pin 1):** Output of the internal high and low sides of the internal synchronous FETS. This output drives the external power inductor, or primary side of a coupled inductor for multiple outputs.

**BOOT** (pin 2): Connect a 0.1-μF capacitor between the BOOT pin and the PHASE pin. This provides the necessary level shift voltage to drive the internal upper FET gate.

**UV/OV** (pin 3): Input to the internal window comparator with a 1-V and 5-V reference. The input to the UV/OV pin determines the state of the open drain output of VIN\_G. This does not determine the operating range of the UCC25230. A bypass cap at least 1000 pF is recommended for noise immunity.

VIN\_G (pin 4): Open drain output of The UCC25230's internal comparator. The output state is determined by the voltage on the UV/OV pin. The UCC25230 will continue to function regardless of the state of this pin. Used for controlling external circuitry. Maximum voltage to this pin is 5.5 V.

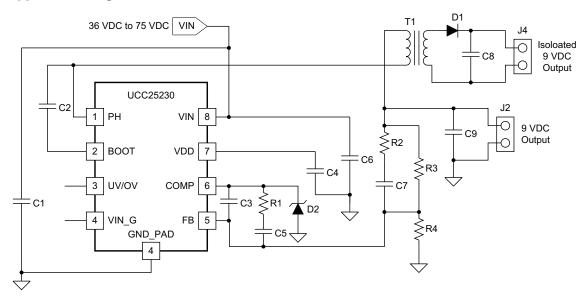

**FB** (pin 5): FB is the inverting input of the UCC25230's internal error amplifier. Connect the output voltage sensing divider to this pin. Internal reference is 2.5 V on the non inverting input.

$$R2 = \left(\left(\frac{V_{OUT}}{2.5}\right) - 1\right) \times R1 \tag{1}$$

**COMP (pin 6):** The COMP pin is the internal error amplifier's output. The voltage range of COMP is 0 V to 8.3 V. At steady state, a higher COMP pin voltage results in a larger duty cycle. Add compensation components between this pin and FB. The device has input feed forward control which makes PWM RAMP magnitude  $V_{IN}$  x 6%.

**VDD** (pin 7): This is the 9-V output of the UCC25230's internal voltage regulator. This output may be used for powering additional circuitry, up to a current of 2 mA, depending on the voltage on the VIN pin. Care must be taken not to exceed the devices total power dissipation.

VIN (pin 8): This is the voltage input pin for the UCC25230. It supplies the internal voltage regulator and output switches. Bypass this pin with at least 1-µF low ESR capacitor.

GND PAD (pin 9): GND PAD is the ground reference for the whole device. Tie all signal returns to this point.

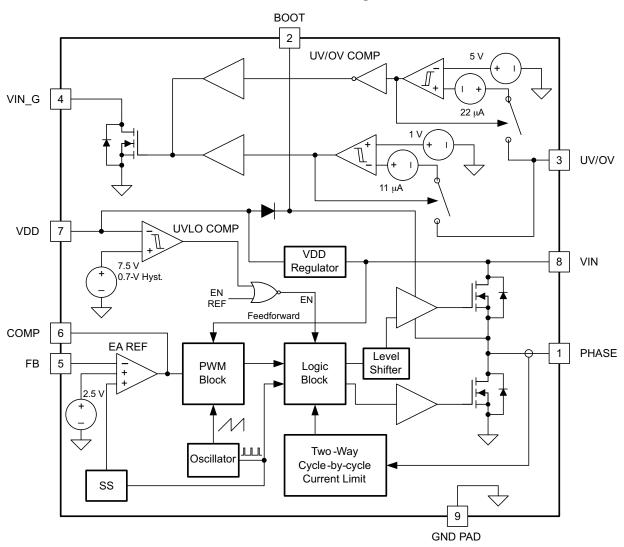

## **Functional Block Diagram**

**OSCILLATOR CHANGE**

## TYPICAL CHARACTERISTICS

Figure 3.

**SOFT-START TIME**

# **TYPICAL CHARACTERISTICS (continued)**

VDD CHANGE

vs **TEMPERATURE** 9.11 9.10 9.09 Voltage (V) 9.08 9.07 9.06 9.05 25 Temperature (°C)

Figure 6.

-40

90

125

G000

#### **APPLICATION INFORMATION**

## **Detailed Description**

The UCC25230 PWM converter integrates all necessary functions to operate as an isolated auxiliary bias supply. It is capable of operating from an input voltage range of 12 V to 100 V (up to 105-V surge), making it ideal for usage in 24-V or 48-V input telecom applications. High-side and low-side power switches are integrated and provide up to 200 mA of peak output current. The UCC25230 is an ideal, complementary solution to primary-side or secondary-side PWM control methodologies as it provides bias voltages necessary for PWM controllers and/or external peripheral circuitry. UCC25230 is capable of delivering a primary-side and/or secondary-side bias voltage for power supplies. As such, UCC25230 is optimized for Texas Instruments' family of UCD3k digital and analog PWM controllers as well as the C2000 family of microcontrollers.

UCC25230 operates using Texas Instruments' Flybuck™ Topology, which simplifies design versus a traditional flyback topology. Flybuck™ Topology allows a synchronous buck–like design methodology. It also enables a significant reduction in external parts count, and also allows usage of a small 2-winding transformer. The Flybuck™ Topology does not require a third transformer winding or opto-isolator for regulation. Circuits employing extra transformer windings compromise dynamic response, and add to the transformer's physical size and cost. The Flybuck™ is a portmanteau of flyback and buck since the transformer is connected as a flyback converter and the input to output voltage relationship is similar to a buck derived converter.

Typically, an auxiliary bias supply must be designed such that it is the first device in the system to power up, and be the very last device, in the system, to power down. It must be a robust supply, being able to ride through any fault conditions (OV, UV, OTP, etc) and it also must not prematurely shut down the entire power supply. The UCC25230 was designed with these goals in mind:

- A 2-ms soft start ensures a smooth, monotonic startup on both primary and secondary-side voltages.

- Voltage mode with input voltage feedforward allows optimal output filter design.

- Cycle-by-cycle current limit with frequency foldback permits startup under high-capacitive loading.

- Programmable UV/OV detection circuit.

- A VIN\_G fault output provides a fast propagation open drain signal to indicate when an overvoltage or undervoltage condition has been detected. The UCC25230 is specifically designed to remain operational when a fault is detected in order to allow for fast external shutdown.

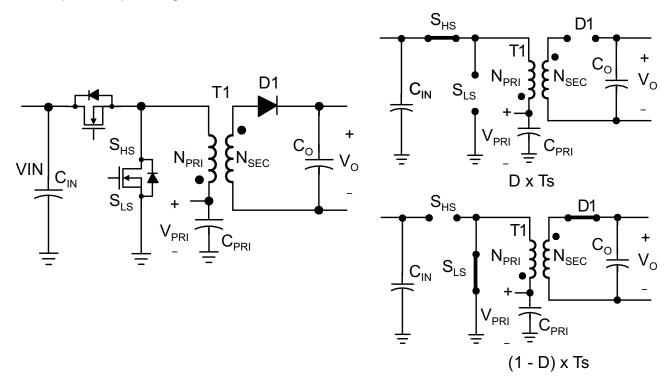

## Operation of the Flybuck™ Converter

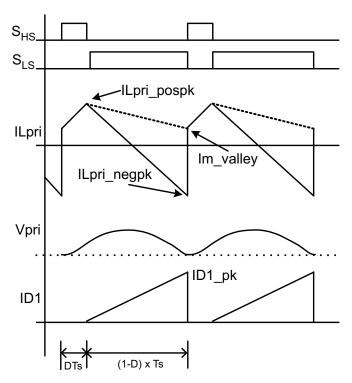

Figure 7 shows a simplified schematic and the two primary operational states of the Flybuck converter. The power supply is a variation of a Flyback converter and consists of a half bridge power stage  $S_{HS}$  and  $S_{LS}$ , transformer, primary side capacitor, diode and output capacitor. The output voltage is regulated indirectly by using the primary side capacitor voltage,  $V_{PRI}$ , as feedback. The Flybuck is a portmanteau of flyback and buck since the transformer is connected as a flyback converter and the input to output voltage relationship is similar to a buck derived converter, assuming the converter is operating in steady state and the transformer has negligible leakage inductance.

The  $C_{PRI}$  and  $L_{PRI}$  are charged by the input voltage source VIN during the time the high side switch  $S_{HS}$  is on. During this time, diode D1 is reversed biased and the load current is supplied by output capacitor  $C_O$ .

During the off time of  $S_{HS}$ ,  $S_{LS}$  conducts and the voltage on  $C_{PRI}$  continues to increase during a portion of the  $S_{LS}$  conduction time. The voltage increase is due to the energy transfer from  $L_{PRI}$  to  $C_{PRI}$ . For the remaining portion of the  $S_{LS}$  conduction time, the  $C_{PRI}$  voltage decreases because of current in  $L_{PRI}$  reverses; see the  $IL_{PRI}$  and  $V_{PRI}$  waveforms in Figure 8. By neglecting the diode voltage drop, conduction dead time and leakage inductance, the input to output voltage conversion ratio can be derived as shown in Equation 2 from the flux balance in  $L_{PRI}$ . It can be seen in Equation 2 that the input to output relationship is the same as a buck-derived converter with transformer isolation. The dc voltage  $V_{PRI}$  on the primary side capacitor in Equation 3 has the same linear relationship to the input voltage as a buck converter.

Figure 7. Simplified Schematic with Two Primary Operational States

The small signal model for the Flybuck is derived by changing the transformer to the inductor equivalent and reflecting the output filter to the primary side for the circuit shown in Figure 7. Assuming negligible leakage inductance and equivalent series resistance for the capacitors, the  $V_{PRI}$  transfer function is similar to the voltage mode control buck power stage transfer function with the exception that the  $C_O$  and load are in parallel with the  $C_{PRI}$  only for the 1-D time. The device has input feed forward control which makes PWM RAMP magnitude  $V_{IN}$  x 6%.

$$\frac{V_{O}}{V_{IN}} = \frac{N_{SEC}}{N_{PRI}} \times D \tag{2}$$

$$\frac{V_{PRI}}{V_{IN}} = D \tag{3}$$

Figure 8. Simplified Voltage and Current Waveforms

## **Typical Application Diagram**

Figure 9. Typical Application Diagram

修订历史记录

# Changes from Revision A (November, 2011) to Revision B Page ● Added 集成型 110V 高侧和低侧开关特性着重号 1 ● Added note, Input feed forward control with RAMP magnitude V<sub>IN</sub> x 6%. 6 ● Added COMP pin description, The device has input feed forward control which makes PWM RAMP magnitude V<sub>IN</sub> x 6%. 7 ● Deleted Averaging the secondary side components, an approximate transfer function is shown in and pole location in . R<sub>O</sub> is the secondary side load resistance and the R<sub>LM</sub> is the dc resistance of the primary. R<sub>i</sub> is the inverse of the Comp to PH gm. 13 ● Added The device has input feed forward control which makes PWM RAMP magnitude V<sub>IN</sub> x 6%. 13

www.ti.com 11-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|----------------|-----------------------|------|---------------|----------------------------|--------------|--------------|

|                       | (1)    | (2)           |                |                       | (3)  | Ball material | (5)                        |              | (6)          |

| UCC25230DRMR          | Active | Production    | VSON (DRM)   8 | 3000   LARGE T&R      | Yes  | NIPDAUAG      | Level-1-260C-UNLIM         | -40 to 125   | 25230        |

| UCC25230DRMR.A        | Active | Production    | VSON (DRM)   8 | 3000   LARGE T&R      | Yes  | NIPDAUAG      | Level-1-260C-UNLIM         | -40 to 125   | 25230        |

| UCC25230DRMT          | Active | Production    | VSON (DRM)   8 | 250   SMALL T&R       | Yes  | NIPDAUAG      | Level-1-260C-UNLIM         | -40 to 125   | 25230        |

| UCC25230DRMT.A        | Active | Production    | VSON (DRM)   8 | 250   SMALL T&R       | Yes  | NIPDAUAG      | Level-1-260C-UNLIM         | -40 to 125   | 25230        |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 25-Jul-2025

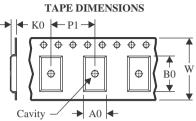

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

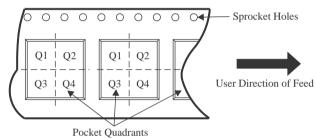

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| UCC25230DRMR | VSON            | DRM                | 8 | 3000 | 330.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

| UCC25230DRMT | VSON            | DRM                | 8 | 250  | 180.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

**PACKAGE MATERIALS INFORMATION**

www.ti.com 25-Jul-2025

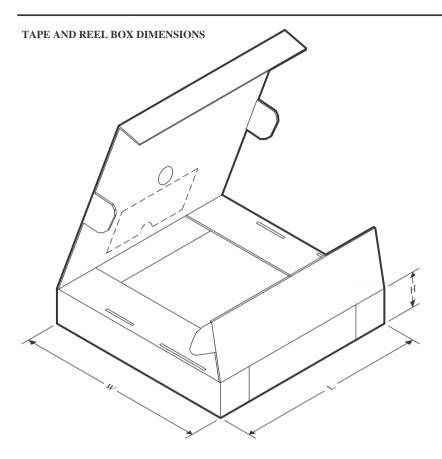

## \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UCC25230DRMR | VSON         | DRM             | 8    | 3000 | 353.0       | 353.0      | 32.0        |

| UCC25230DRMT | VSON         | DRM             | 8    | 250  | 213.0       | 191.0      | 35.0        |

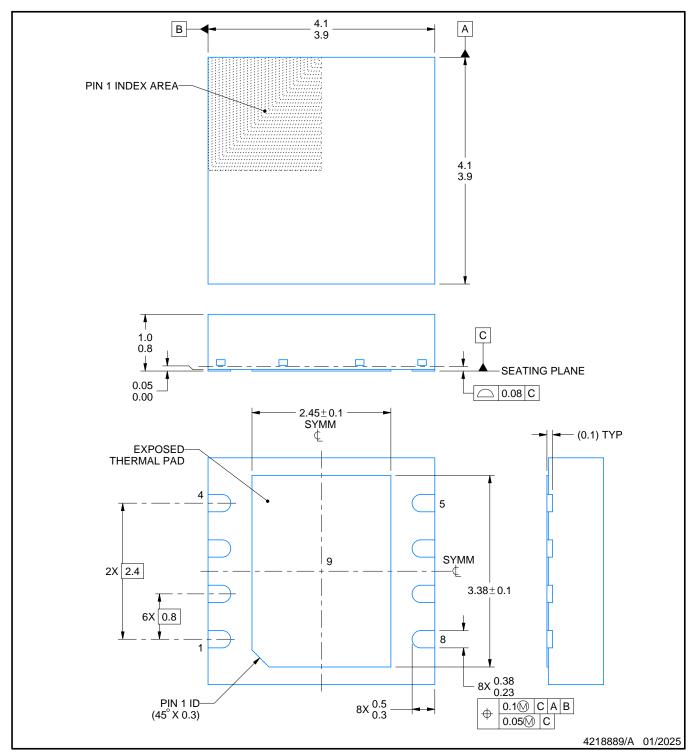

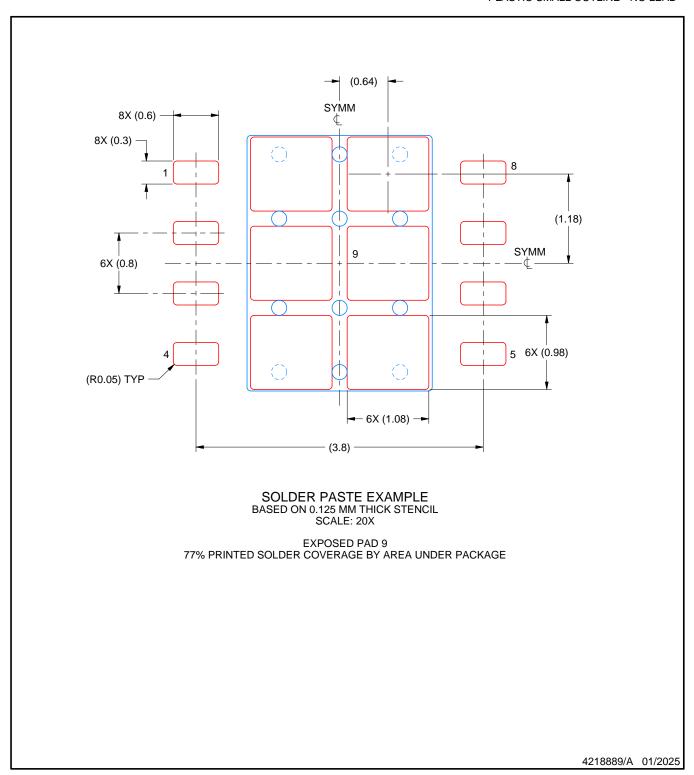

PLASTIC SMALL OUTLINE - NO LEAD

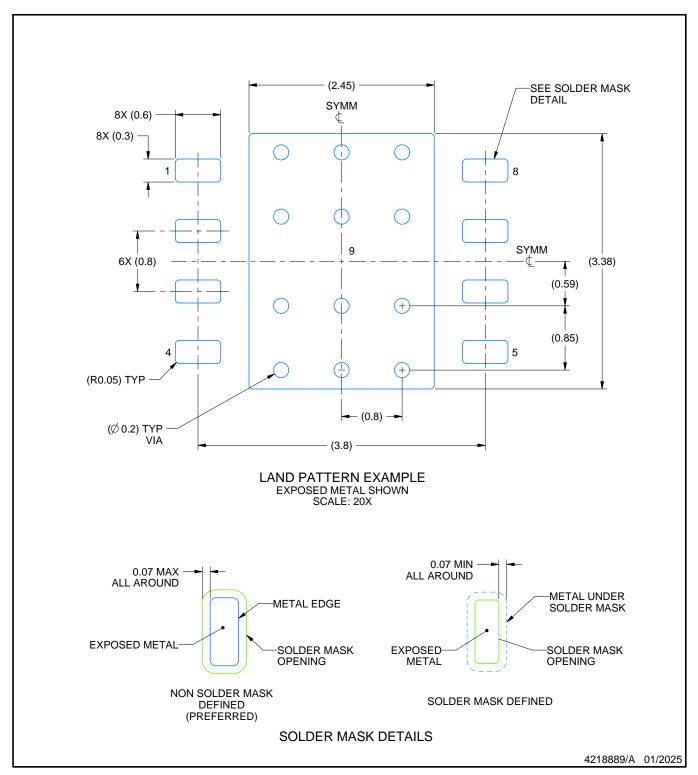

### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

# 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月