TPSI3050-Q1

ZHCSP85D - NOVEMBER 2021 - REVISED AUGUST 2023

## TPSI3050-Q1 具有集成 10-V 栅极电源的汽车类增强型隔离式开关驱动器

## 1 特性

- 无需隔离式次级电源

- 驱动外部功率晶体管或 SCR

- 5-kV<sub>RMS</sub> reinforced isolation

- 具有 1.5/3A 峰值拉电流和灌电流的 10-V 栅极驱动

- 适用于外部辅助电路的最高 50mW 电源

- 支持交流或直流开关

- 支持双线或三线模式

- 七电平功率传输,电阻可选

- 功能安全型

- 可提供用于功能安全系统设计的文档

- 符合面向汽车应用的 AEC Q-100 标准:

- 温度等级 1: –40 至 +125°C, T<sub>△</sub>

- 安全相关认证

- 符合 DIN EN IEC 60747-17 (VDE 0884-17) 标 准的 7071V<sub>PK</sub> 增强型隔离

- 符合 UL 1577 标准且长达 1 分钟的 5kV<sub>RMS</sub> 隔

## 2 应用

- 固态继电器 (SSR)

- 电池管理系统

- 车载充电器

- 混合动力、电动和动力总成系统

- 楼宇自动化

- 工厂自动化和控制

## 3 说明

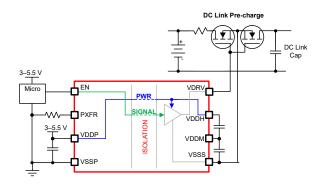

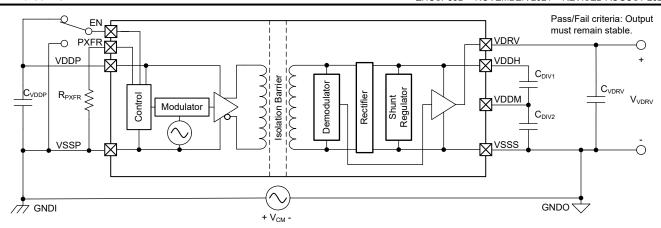

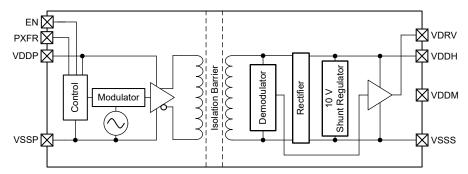

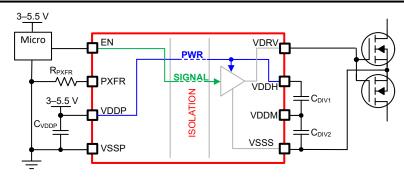

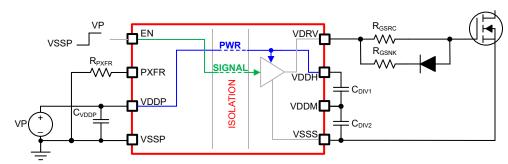

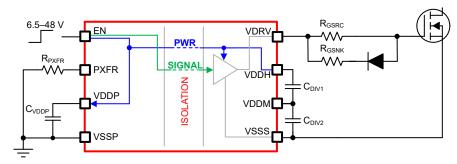

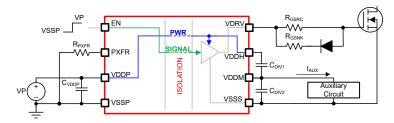

TPSI3050-Q1 是一款完全集成的隔离式开关驱动器 与外部电源开关结合使用时,可构成完整的隔离式固态 继电器 (SSR)。当标称栅极驱动电压为 10 V、峰值拉 电流和灌电流为 1.5/3.0A 时,可以选择多种外部电源 开关来满足各种应用需求。TPSI3050-Q1 可通过初级 侧电源自行产生次级偏置电源,因此无需隔离式次级电 源偏置。而且,TPSI3050-Q1 可以有选择性地向外部 配套电路供电,以满足不同的应用需求。

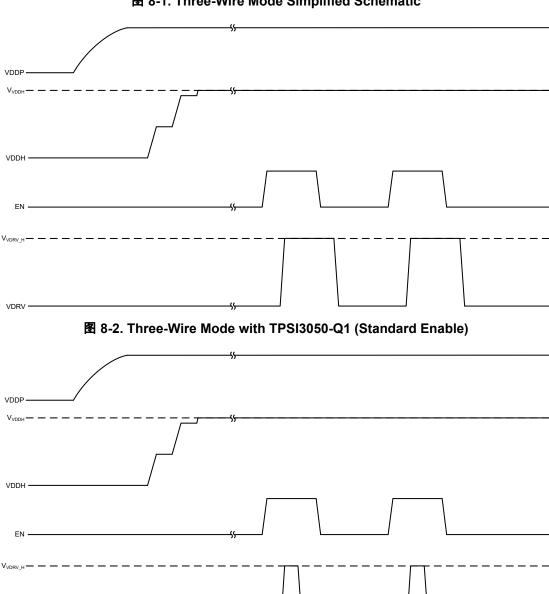

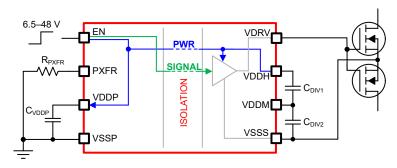

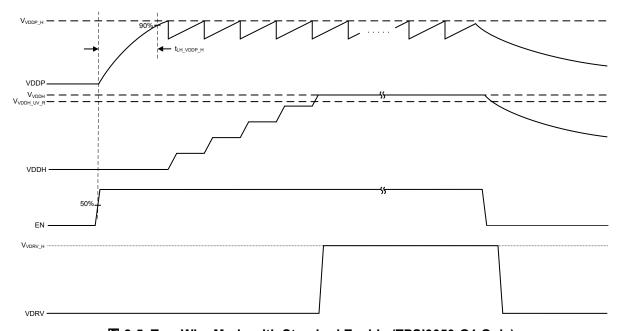

TPSI3050-Q1 根据所需的输入引脚数量,支持两种工 作模式。在双线模式(通常用于驱动机械继电器)中, 控制开关仅需两个引脚,并支持 6.5V 至 48V 的 宽工作电压范围。在三线模式中,由外部提供 3V 至 5.5V 的初级侧电源,并通过独立的使能引脚控制 开关。TPSI3050S-Q1 具有可实现开关控制的一次性 启用功能,且仅在三线模式下可用。此功能对于驱动 SCR 非常有用,通常只需要一个电流脉冲即可触发。

次级侧可为驱动多种电源开关提供 10 V 的浮动稳压 电源轨,无需次级偏置电源。具体用途包括为直流应用 驱动单个电源开关,或为交流应用驱动两个背靠背电源 开关,以及各种类型的 SCR。TPSI3050-Q1 集成式隔 离保护功能非常稳健,与传统机械继电器和光耦合器相 比,其可靠性更高、功耗更低,且温度范围更宽。

使用从 PXFR 引脚到 VSSP 的外部电阻器在七个功 率等级设置中选择一个,以调节 TPSI3050-Q1 的功率 传输。此操作可根据应用需求权衡功率损耗与次级侧功 耗。

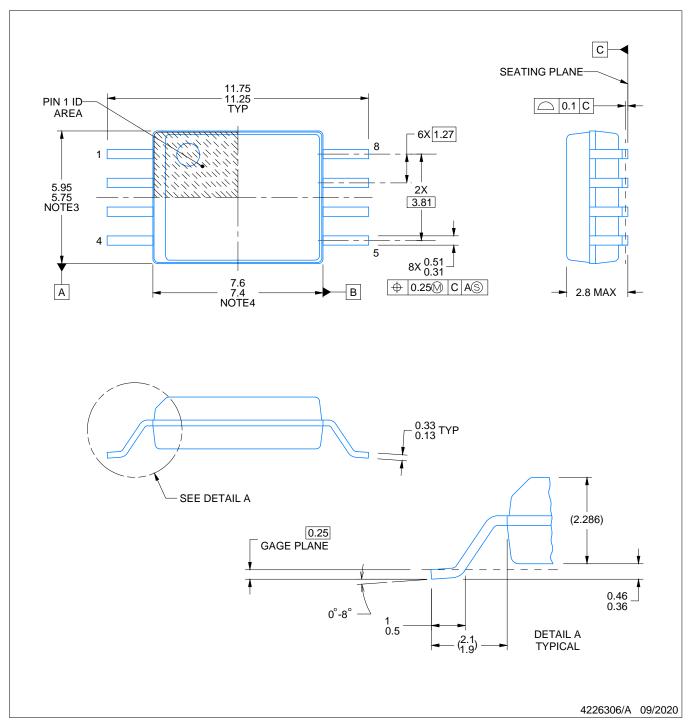

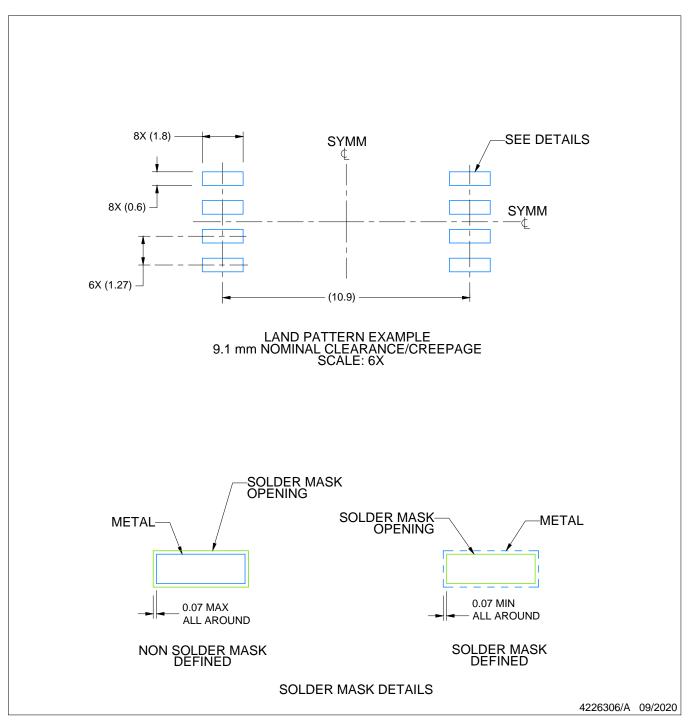

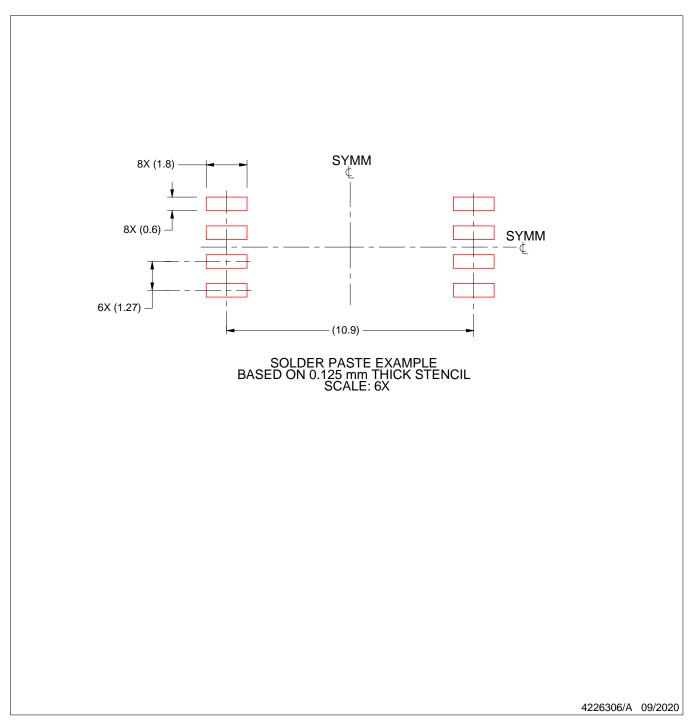

## 封装信息

| 器件型号         | 封装 <sup>(1)</sup>   | 封装尺寸 ( 标称值 )          |

|--------------|---------------------|-----------------------|

| TPSI3050-Q1  | SOIC 8 引脚 (DWZ)     | 7.50mm x 5.95mm       |

| TPSI3050S-Q1 | 3010 8 51114 (DVVZ) | 7.5011111 ^ 5.6511111 |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

TPSI3050-Q1 简化版原理图

## **Table of Contents**

| 1 特性                                  | . 1 8 Detailed Description                 | 18 |

|---------------------------------------|--------------------------------------------|----|

| 2 应用                                  |                                            |    |

| 3 说明                                  | . 1 8.2 Functional Block Diagram           | 18 |

| 4 Revision History                    |                                            |    |

| 5 Pin Configuration and Functions     |                                            |    |

| 6 Specifications                      |                                            | 26 |

| 6.1 Absolute Maximum Ratings          |                                            |    |

| 6.2 ESD Ratings                       |                                            |    |

| 6.3 Recommended Operating Conditions  |                                            |    |

| 6.4 Thermal Information               | 6 9.4 Layout                               | 34 |

| 6.5 Power Ratings                     | 6 10 Device and Documentation Support      | 37 |

| 6.6 Insulation Specifications         |                                            | 37 |

| 6.7 Safety-Related Certifications     | . 7   10.2 接收文档更新通知                        | 37 |

| 6.8 Safety Limiting Values            | 7   10.3 支持资源                              | 37 |

| 6.9 Electrical Characteristics        | 8 10.4 Trademarks                          | 37 |

| 6.10 Switching Characteristics        | 11 10.5 静电放电警告                             | 37 |

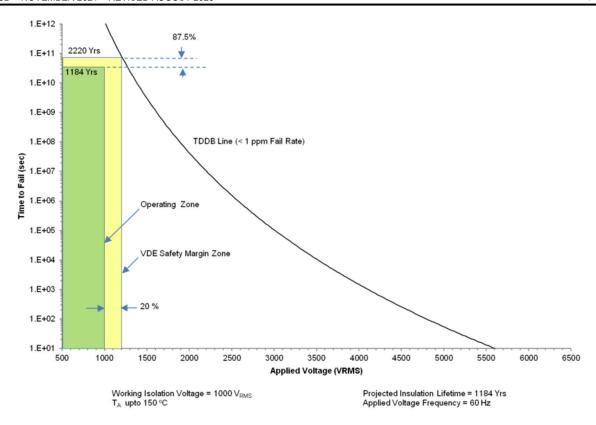

| 6.11 Insulation Characteristic Curves | 13 10.6 术语表                                | 37 |

| 6.12 Typical Characteristics          | 14 11 Mechanical, Packaging, and Orderable |    |

| 7 Parameter Measurement Information   | 16 Information                             | 37 |

|                                       |                                            |    |

|                                       |                                            |    |

|    | Revision History<br>:以前版本的页码可能与当前版本的页码不同                                                   |     |   |

|----|--------------------------------------------------------------------------------------------|-----|---|

| Cł | hanges from Revision C (April 2023) to Revision D (August 2023)                            | Pag | е |

| •  | Updated Safety-Related Certifications section with associated file and certificate numbers |     | 5 |

| Cł | hanges from Revision B (December 2022) to Revision C (April 2023)                          | Pag | e |

| •  | 删除了 TPSI3050S-Q1 的产品预发布                                                                    |     | 1 |

| •  | 更改了首页格式以与当前 TI 数据表标准保持一致                                                                   |     | 1 |

| •  | Added  ΔV <sub>EN</sub> /Δt  to Recommended Operating Conditions                           |     | 5 |

| •  | Added Power Supply and EN Sequencing section                                               |     |   |

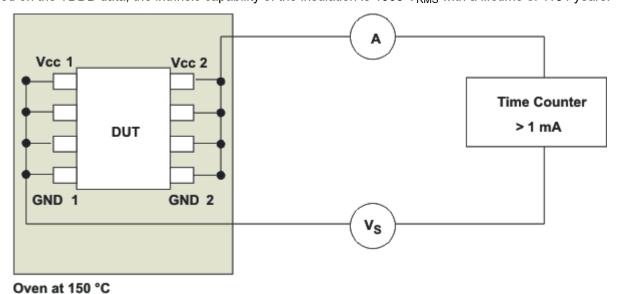

| •  | Added Insulation Lifetime section                                                          | 3   | 3 |

| Cł | hanges from Revision A (April 2022) to Revision B (December 2022)                          | Pag | e |

| •  | 将状态从"预告信息"更改为"量产数据"                                                                        |     | 1 |

| Cł | hanges from Revision * (November 2021) to Revision A (April 2022)                          | Pag |   |

| •  | 更新了"安全认证"和整个文档的参考资料                                                                        |     | 1 |

| •  | 更新了附带链接的 <i>应用</i> 部分                                                                      |     |   |

| •  | 更新了说明部分,表明一次性启用模式                                                                          |     |   |

|    | TPSI3050S-Q1 三线模式下可用                                                                       |     |   |

| •  | Changed name of DUTY pin to PXFR pin throughout the document                               |     |   |

| •  | Updated 图 6-10,图 6-11,图 6-8,图 6-9                                                          |     |   |

| •  | Removed two-wire mode timing, one-shot enable figure because one-shot enable is not sup    |     |   |

|    | two-wire mode                                                                              |     |   |

| •  | Changed C <sub>IN</sub> to C <sub>VDDP</sub>                                               |     |   |

| •  | Removed one-shot enable feature in two-wire mode for TPSI3050S-Q1                          |     |   |

| •  | Updated 表 8-3 to reflect one-shot enable mode is only available in three-wire r            |     |   |

| _  | TPSI3050S-Q1                                                                               |     |   |

| •  | Changed from equal to approximate 0.5-V drop of the VDDH supply                            |     |   |

|    | Changed C <sub>IN</sub> to C <sub>VDDP</sub>                                               |     |   |

| -  | Onanged OIN to OVDDP                                                                       | ∠   | J |

# www.ti.com.cn

| • | Updated I <sub>O+</sub> and I <sub>O-</sub> calculations and values | 29 |

|---|---------------------------------------------------------------------|----|

|   | Updated calculator tool results summary and descriptions            |    |

|   | Updated 图 9-14, 图 9-15, 图 9-16                                      |    |

## **5 Pin Configuration and Functions**

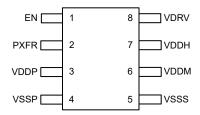

图 5-1. TPSI3050-Q1, TPSI3050S-Q1 8-Pin SOIC Top View

表 5-1. Pin Functions

| PIN NO. NAME |      |     |      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |      | 1/0 | ITPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1            | EN   | I   | _    | Active high driver enable                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2            | PXFR | I   | _    | Power transfer can be adjusted by selecting one of seven power level settings using an external resistor from the PXFR pin to VSSP. In three-wire mode, a given resistor setting sets the duty cycle of the power converter (see 表 8-1) and hence the amount of power transferred. In two-wire mode, a given resistor setting adjusts the current limit of the EN pin (see 表 8-2) and hence the amount of power transferred. |

| 3            | VDDP | _   | Р    | Power supply for primary side                                                                                                                                                                                                                                                                                                                                                                                                |

| 4            | VSSP | _   | GND  | Ground supply for primary side                                                                                                                                                                                                                                                                                                                                                                                               |

| 5            | VSSS | _   | GND  | Ground supply for secondary side                                                                                                                                                                                                                                                                                                                                                                                             |

| 6            | VDDM | _   | Р    | Generated mid supply                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7            | VDDH | _   | Р    | Generated high supply                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8            | VDRV | 0   | _    | Active high driver output                                                                                                                                                                                                                                                                                                                                                                                                    |

<sup>(1)</sup> P = power, GND = ground, NC = no connect

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

| PARAMETER <sup>(1)</sup>              |             | MIN  | MAX | UNIT |

|---------------------------------------|-------------|------|-----|------|

|                                       | VDDP        | -0.3 | 6   | V    |

| Primary Side Supply <sup>(2)</sup>    | EN          | -0.3 | 60  | V    |

|                                       | PXFR        | -0.3 | 60  | V    |

|                                       | VDRV        | -0.3 | 12  | V    |

| Secondary Side Supply <sup>(3)</sup>  | VDDH        | -0.3 | 12  | V    |

| Secondary Side Supply                 | VDDM        | -0.3 | 6   | V    |

|                                       | VDDH – VDDM | -0.3 | 6   | V    |

| Junction temperature, T <sub>J</sub>  |             | -40  | 150 | °C   |

| Storage temperature, T <sub>stg</sub> |             | -65  | 150 | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 6.2 ESD Ratings

|                    |  |                                                                     |                              | VALUE | UNIT |

|--------------------|--|---------------------------------------------------------------------|------------------------------|-------|------|

|                    |  | Human body model (HBM), per AEC Q100 HBM ESD classification level 2 | 0-002 <sup>(1)</sup>         | ±2000 |      |

| V <sub>(ESD)</sub> |  | Charged device model (CDM), per AEC                                 | Corner pins (1, 4, 5, and 8) | ±750  | V    |

|                    |  | Q100-011<br>CDM ESD classification level C4B                        | Other pins                   | ±500  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing must be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                            |                                                                         | MIN   | NOM MAX | UNIT |

|----------------------------|-------------------------------------------------------------------------|-------|---------|------|

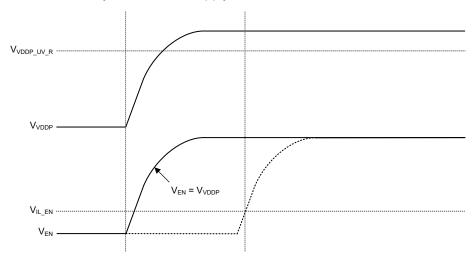

| VDDP                       | Primary side supply voltage three-wire mode <sup>(1)</sup>              | 3.0   | 5.5     | V    |

| EN                         | Enable in two-wire mode <sup>(1)</sup>                                  | 0     | 48.0    | V    |

| □IN                        | Enable in three-wire mode <sup>(1)</sup>                                | 0     | 5.5     | V    |

| PXFR                       | Power transfer control <sup>(1)</sup>                                   | 0     | 5.5     | V    |

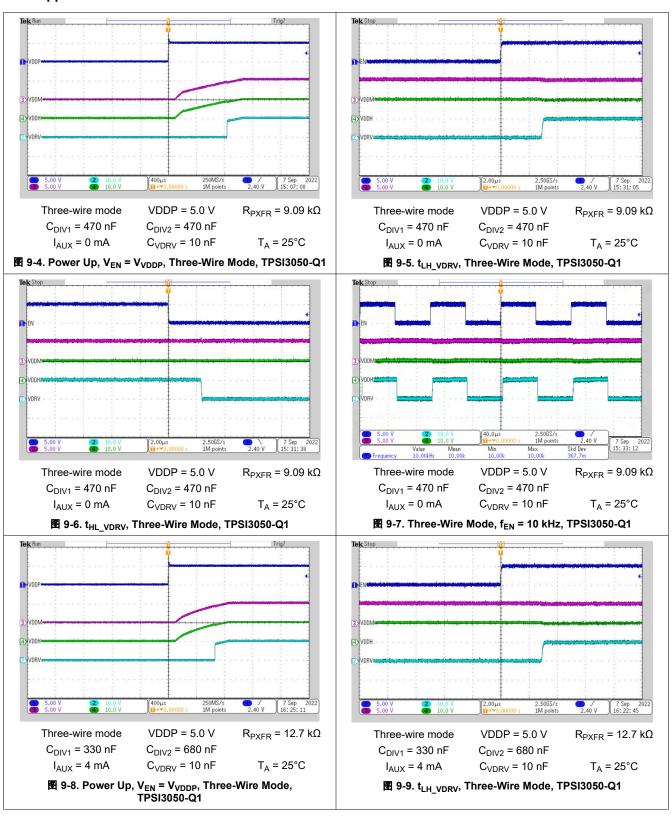

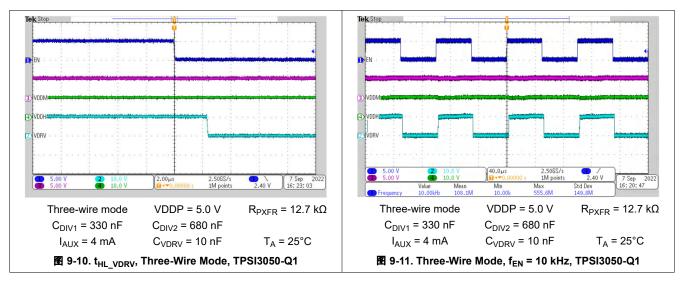

| C                          | Decoupling capacitance on VDDP and VSSP, two-wire mode <sup>(3)</sup>   | 220   | 330     | nF   |

| $C_{VDDP}$                 | Decoupling capacitance on VDDP and VSSP, three-wire mode <sup>(3)</sup> | 0.22  | 20      | μF   |

| C <sub>DIV1</sub> (2)      | Decoupling capacitance across VDDH and VDDM <sup>(3)</sup>              | 0.003 | 40      | μF   |

| C <sub>DIV2</sub> (2)      | Decoupling capacitance across VDDM and VSSS <sup>(3)</sup>              | 0.003 | 40      | μF   |

| T <sub>A</sub>             | Ambient operating temperature                                           | -40   | 125     | °C   |

| TJ                         | Operating junction temperature                                          | -40   | 150     | °C   |

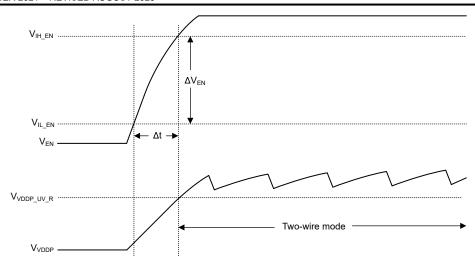

| $ \Delta V_{EN}/\Delta t $ | EN rise and fall rates, two-wire mode.                                  | 65    |         | V/ms |

<sup>(1)</sup> All voltage values are with respect to VSSP.

<sup>(2)</sup> All voltage values are with respect to VSSP.

<sup>(3)</sup> All voltage values are with respect to VSSS.

<sup>(2)</sup>  $C_{DIV2} \ge C_{DIV1}$ .  $C_{DIV1}$  and  $C_{DIV2}$  should be of same type and tolerance.

<sup>(3)</sup> All capacitance values are absolute. Derating should be applied where necessary.

## **6.4 Thermal Information**

|                       |                                              | DEVICE    |      |

|-----------------------|----------------------------------------------|-----------|------|

|                       | THERMAL METRIC(1)                            | DWZ(SOIC) | UNIT |

|                       |                                              | 8 PINS    |      |

| R <sub>OJA</sub>      | Junction-to-ambient thermal resistance       | 89.3      | °C/W |

| R <sub>OJC(top)</sub> | Junction-to-case (top) thermal resistance    | 40.3      | °C/W |

| R <sub>OJB</sub>      | Junction-to-board thermal resistance         | 45.2      | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 10.3      | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 44.4      | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## **6.5 Power Ratings**

| PARAMETER      |                                  | TEST CONDITIONS                                                                                                                                                                                                                                            | MIN | TYP | MAX | UNIT |

|----------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| P <sub>D</sub> | Maximum power dissipation, VDDP. | $\begin{split} &V_{VDDP}=5~V,\\ &R_{PXFR}=20~k\Omega,~three-wire~mode,\\ &C_{VDRV}=100~pF,\\ &C_{DIV1}=C_{DIV2}=100~nF,\\ &f_{EN}=1\text{-kHz}~square~wave,}~V_{EN}=5~V~peak\\ &to~peak. \end{split}$                                                      |     |     | 250 | mW   |

| l D            | Maximum power dissipation, EN.   | $\begin{split} R_{PXFR} &= 20 \text{ k}\Omega, \text{ two-wire mode,} \\ C_{VDRV} &= 100 \text{ pF,} \\ C_{DIV1} &= C_{DIV2} = 100 \text{ nF,} \\ f_{EN} &= 1\text{-kHz square wave,} \text{ $V_{EN}$} = 48 \text{ V} \\ \text{peak to peak.} \end{split}$ |     |     | 350 | mW   |

## 6.6 Insulation Specifications

|                   | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TEST CONDITIONS                                                           | SPECIFIC ATION | UNIT      |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------|-----------|

| GENERA            | AL .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                           |                |           |

| CLR               | External clearance <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Shortest terminal-to-terminal distance through air                        | ≥ 8.5          | mm        |

| CPG               | External Creepage <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Shortest terminal-to-terminal distance across the package surface         | ≥ 8.5          | mm        |

| DTI               | Distance through the insulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Minimum internal gap (internal clearance)                                 | ≥ 120          | μm        |

| СТІ               | Comparative tracking index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DIN EN 60112 (VDE 0303-11); IEC 60112                                     | ≥ 600          | V         |

|                   | Material Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | According to IEC 60664-1                                                  | I              |           |

|                   | Overvoltage category per IEC 60664-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Rated mains voltage ≤ 600 V <sub>RMS</sub>                                | I-IV           |           |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Rated mains voltage ≤ 1000 V <sub>RMS</sub>                               | 1-111          |           |

| DIN EN I          | EC 60747-17 (VDE 0884-17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                           |                |           |

| V <sub>IORM</sub> | Maximum repetitive peak isolation voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | AC voltage (bipolar)                                                      | 1414           | $V_{PK}$  |

| .,                | Manifestoria de la Manifestoria de la constanta de la constant | AC voltage (sine wave)                                                    | 1000           | $V_{RMS}$ |

| V <sub>IOWM</sub> | Maximum isolation working voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DC voltage                                                                | 1414           | $V_{DC}$  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>TEST</sub> = V <sub>IOTM</sub> ; t = 60 s (qualification test)     | 7070           | $V_{PK}$  |

| V <sub>IOTM</sub> | Maximum transient isolation voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $V_{TEST} = 1.2 \times V_{IOTM}$ ; t = 1 s (100% production test)         | 8484           | $V_{PK}$  |

| V <sub>IMP</sub>  | Maximum impulse voltage <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Tested in air;<br>1.2/50-µs waveform per IEC 62638-1                      | 9230           | $V_{PK}$  |

| V <sub>IOSM</sub> | Maximum surge isolation voltage <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Tested in oil (qualification test);<br>1.2/50-µs waveform per IEC 62638-1 | 12000          | $V_{PK}$  |

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

## 6.6 Insulation Specifications (continued)

|                  | PARAMETER                                             | TEST CONDITIONS                                                                                                                                                                                            | SPECIFIC ATION     | UNIT      |

|------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------|

|                  |                                                       | Method a: After input-output safety test subgroup 2/3, $V_{\text{ini}} = V_{\text{IOTM}},  t_{\text{ini}} = 60 \text{ s}; \\ V_{\text{pd(m)}} = 1.2 \times V_{\text{IORM}},  t_{\text{m}} = 10 \text{ s}.$ |                    |           |

| $q_{pd}$         | Apparent charge <sup>(4)</sup>                        | $\begin{aligned} & \text{Method a: After environmental tests subgroup 1,} \\ & V_{ini} = V_{IOTM},  t_{ini} = 60 \text{ s;} \\ & V_{pd(m)} = 1.6 \times V_{IORM},  t_m = 10 \text{ s.} \end{aligned}$      | ≤ 5                | pC        |

|                  |                                                       | Method b1: At routine test (100% production test) and preconditioning (type test), $V_{ini} = V_{IOTM}$ , $t_{ini} = 1$ s; $V_{pd(m)} = 1.875 \times V_{IORM}$ , $t_m = 1$ s.                              | ≤ 5                |           |

| C <sub>IO</sub>  | Barrier capacitance, input to output <sup>(5)</sup>   | $V_{IO} = 0.4 \times \sin(2\pi ft)$ , f = 1 MHz                                                                                                                                                            | 3                  | pF        |

|                  |                                                       | V <sub>IO</sub> = 500 V, T <sub>A</sub> = 25°C                                                                                                                                                             | > 10 <sup>12</sup> |           |

| R <sub>IO</sub>  | Insulation resistance, input to output <sup>(5)</sup> | V <sub>IO</sub> = 500 V, 100°C ≤ T <sub>A</sub> ≤ 125°C                                                                                                                                                    | > 10 <sup>11</sup> | Ω         |

|                  |                                                       | V <sub>IO</sub> = 500 V at T <sub>S</sub> = 150°C                                                                                                                                                          | > 10 <sup>9</sup>  |           |

|                  | Pollution degree                                      |                                                                                                                                                                                                            | 2                  |           |

|                  | Climatic category                                     |                                                                                                                                                                                                            | 40/125/21          |           |

| UL 1577          | 1                                                     | -                                                                                                                                                                                                          | '                  |           |

| V <sub>ISO</sub> | Withstand isolation voltage                           | $V_{TEST}$ = $V_{ISO}$ = 5000 $V_{RMS}$ , t = 60 s (qualification test), $V_{TEST}$ = 1.2 × $V_{ISO}$ = 6000 $V_{RMS}$ , t = 1 s (100% production test)                                                    | 5000               | $V_{RMS}$ |

- (1) Creepage and clearance requirements should be applied according to the specific equipment isolation standards of an application. Care should be taken to maintain the creepage and clearance distance of a board design to ensure that the mounting pads of the isolator on the printed-circuit board do not reduce this distance. Creepage and clearance on a printed-circuit board become equal in certain cases. Techniques such as inserting grooves, ribs, or both on a printed-circuit board are used to help increase these specifications.

- (2) Testing is carried out in air to determine the intrinsic surge immunity of the package.

- (3) Testing is carried out in oil to determine the intrinsic surge immunity of the isolation barrier.

- (4) Apparent charge is electrical discharge caused by a partial discharge (pd).

- (5) All pins on each side of the barrier tied together creating a two-pin device.

## 6.7 Safety-Related Certifications

| VDE                                                                                                                                                                                  | UL                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Certified according to DIN EN IEC 60747-17 (VDE 0884-17)                                                                                                                             | Recognized under UL 1577 Component Recognition Program |

| Reinforced insulation; Maximum transient isolation voltage, 7071 $V_{PK};$ Maximum repetitive peak isolation voltage, 1414 $V_{PK};$ Maximum surge isolation voltage, 12000 $V_{PK}$ | Single protection, 5000 V <sub>RMS</sub>               |

| Certificate number: 40040142                                                                                                                                                         | File number: UL-US-2300613-0                           |

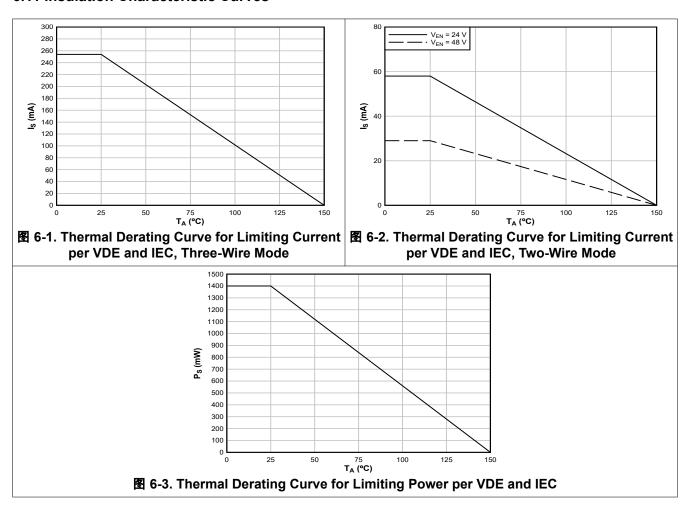

## 6.8 Safety Limiting Values

| PARAMETER <sup>(1)</sup> (2) |                                                                                                                        | TEST CONDITIONS                                                                                                     | MIN | TYP | MAX | UNIT |

|------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

|                              |                                                                                                                        | $R_{\theta JA}$ = 89.3°C/W, $V_{VDDP}$ = 5.5 V,<br>$T_{J}$ = 150°C, $T_{A}$ = 25°C,<br>three-wire mode.             |     |     | 254 |      |

| Is                           | I <sub>S</sub> Safety input, output, or supply current                                                                 | $R_{\theta JA} = 89.3^{\circ}C/W, V_{EN} = 24 V,$<br>$T_{J} = 150^{\circ}C, T_{A} = 25^{\circ}C,$<br>two-wire mode. |     |     | 58  | mA   |

|                              | $R_{\theta JA} = 89.3^{\circ} C/W, V_{EN} = 48 V,$<br>$T_{J} = 150^{\circ} C, T_{A} = 25^{\circ} C,$<br>two-wire mode. |                                                                                                                     |     | 29  |     |      |

### 6.8 Safety Limiting Values (continued)

|                | PARAMETER <sup>(1)</sup> (2) | TEST CONDITIONS                                                                 | MIN | TYP | MAX | UNIT |

|----------------|------------------------------|---------------------------------------------------------------------------------|-----|-----|-----|------|

| Ps             |                              | R <sub>θ,JA</sub> = 89.3°C/W,<br>T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C. |     |     | 1.4 | W    |

| T <sub>S</sub> | Maximum safety temperature   |                                                                                 |     |     | 150 | °C   |

- (1) Safety limiting intends to minimize potential damage to the isolation barrier upon failure of input or output circuitry. A failure of the I/O can allow low resistance to ground or the supply and, without current limiting, dissipate sufficient power to overheat the die and damage the isolation barrier, potentially leading to secondary system failures.

- (2) The safety-limiting constraint is the maximum junction temperature specified in the data sheet. The power dissipation and junction-to-air thermal impedance of the device installed in the application hardware determines the junction temperature. The assumed junction-to-air thermal resistance in the Thermal Information table is that of a device installed on a high-K test board for leaded surface-mount packages. The power is the recommended maximum input voltage times the current. The junction temperature is then the ambient temperature plus the power times the junction-to-air thermal resistance.

#### **6.9 Electrical Characteristics**

over operating free-air temperature range (unless otherwise noted). Typicals at  $T_A$  = 25°C.  $C_{VDDP}$  = 220 nF,  $C_{DIV1}$  =  $C_{DIV2}$  = 3.3 nF,  $C_{VDRV}$  = 100 pF,  $R_{PXFR}$  = 7.32 k $\Omega$  ± 1%

| PARAMETER                 |                                                                                                                    | TEST CONDITIONS                                                                                      | MIN  | TYP  | MAX  | UNIT |

|---------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------|------|------|------|

| COMMON                    |                                                                                                                    |                                                                                                      | •    |      |      |      |

| V <sub>VDDP_UV_R</sub>    | VDDP undervoltage threshold rising                                                                                 | VDDP rising                                                                                          | 2.50 | 2.70 | 2.90 | V    |

| $V_{VDDP\_UV\_F}$         | VDDP undervoltage threshold falling                                                                                | VDDP falling                                                                                         | 2.35 | 2.55 | 2.75 | V    |

| V <sub>VDDP_UV_HYS</sub>  | VDDP undervoltage threshold hysterisis                                                                             |                                                                                                      |      | 75   |      | mV   |

| TSD                       | Temperature shutdown                                                                                               |                                                                                                      |      | 173  |      | °C   |

| TSDH                      | Temperature shutdown hysteresis                                                                                    |                                                                                                      |      | 32   |      | °C   |

| V <sub>VDDH_UV_R</sub>    | VDDH undervoltage threshold rising                                                                                 | VDDH rising.                                                                                         | 8.3  | 8.6  | 9.0  | V    |

| V <sub>VDDH_UV_</sub> F   | VDDH undervoltage threshold falling TPSI3050-Q1 only.                                                              | VDDH falling.                                                                                        | 6.3  | 6.6  | 6.9  | V    |

| V <sub>VDDH_UV_</sub> f   | VDDH undervoltage threshold falling TPSI3050S-Q1 only. One-shot enable mode only available in threewire operation. | VDDH undervoltage threshold falling TPSI3050S-Q1 only. One-shot enable mode only available in three- |      | 7.5  | 7.8  | V    |

| V <sub>VDDH_UV_HY</sub> s | VDDH undervoltage threshold hysterisis TPSI3050-Q1 only.                                                           |                                                                                                      |      | 2    |      | V    |

| V <sub>VDDH_UV_HYS</sub>  | VDDH undervoltage threshold hysterisis TPSI3050S-Q1 only.                                                          |                                                                                                      |      | 1.1  |      | V    |

| I <sub>Q_VDDH</sub>       | Internal quiescent current of VDDH supply.                                                                         |                                                                                                      |      | 36   |      | μΑ   |

| D                         | Driver on resistance in low state                                                                                  | Force V <sub>VDDH</sub> = 10 V,<br>sink I <sub>VDRV</sub> = 50 mA.                                   |      | 1.7  |      | Ω    |

| R <sub>DSON_VDRV</sub>    | Driver on resistance in high state                                                                                 | Force V <sub>VDDH</sub> = 10 V,<br>source I <sub>VDRV</sub> = 50 mA.                                 |      | 2.5  |      | Ω    |

| 1                         | VDRV peak output current during rise                                                                               | V <sub>VDDH</sub> in steady state,<br>transition EN from low to high,<br>measure peak current.       |      | 1.5  |      | Α    |

| IVDRV_PEAK                | VDRV peak output current during fall                                                                               | V <sub>VDDH</sub> in steady state,<br>transition EN from high to low,<br>measure peak current.       |      | 3    |      | Α    |

| CMTI                      | Common-mode transient immunity                                                                                     | V <sub>CM</sub>   = 1000 V                                                                           | 100  |      |      | V/ns |

| TWO-WIRE MODE             | ·                                                                                                                  |                                                                                                      |      |      |      |      |

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

## **6.9 Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted). Typicals at  $T_A$  = 25°C.  $C_{VDDP}$  = 220 nF,  $C_{DIV1}$  =  $C_{DIV2}$  = 3.3 nF,  $C_{VDRV}$  = 100 pF,  $R_{PXFR}$  = 7.32 k $\Omega$  ± 1%

|                          | PARAMETER                                                                            | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MIN  | TYP  | MAX  | UNIT |

|--------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

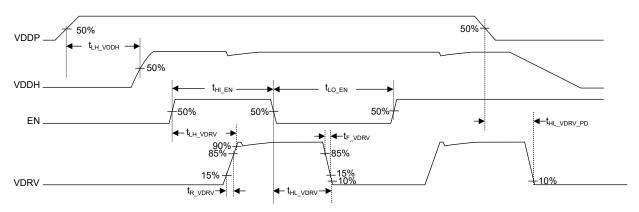

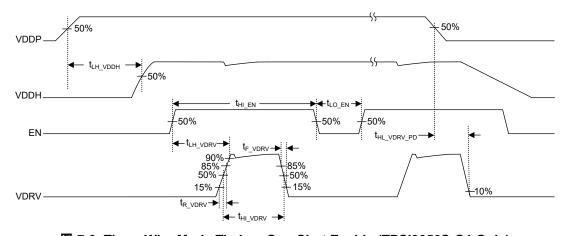

| V <sub>IH_EN</sub>       | Minimum voltage on EN to be detected as a valid logic high                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.5  |      |      | V    |