TPA3131D2, TPA3132D2

ZHCSBD2B - SEPTEMBER 2013-REVISED JANUARY 2015

# TPA313xD2 具有 AM 干扰抑制功能的 4W、25W 无滤波器 D 类立体声放大器

# 1 特性

- 支持多种输出配置

- 7.4V 电压、8Ω 桥接负载 (BTL) 负载条件下的 功率为 2 x 4W (TPA3130D2)

- 19V 电压、8Ω BTL 负载条件下的功率为 2 x 25W (TPA3132D2)

- 宽电压范围: 4.5V 至 26V

- 汽车抛负载兼容

- 高效 D 类运行

- 兼具 > 90% 的功率效率与低空闲损耗特性,无 需散热器即可稳定运行

- 高级调制系统配置

- 多重开关频率

- AM 抑制

- 主从模式同步

- 高达 1.2MHz 的切换频率

- 采用具有高 PSRR 的反馈功率级架构,降低了 PSU 需求

- 可编程功率限制

- 差分和单端输入

- 立体声模式和单声道模式(采用单滤波器单声道配置)

- 由单电源供电运行,减少了元件数量

- 集成了具有错误报告功能的自保护电路,其中包括过压、欠压、过热、直流检测和短路等保护

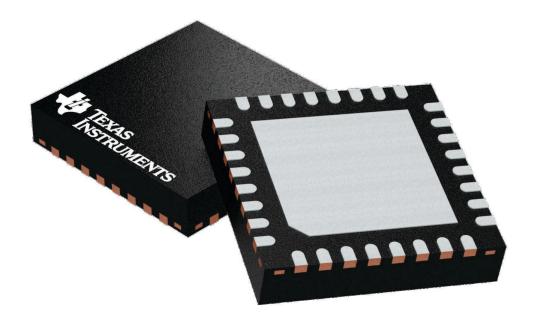

- 散热增强型封装

- 32 引脚超薄型四方扁平无引线 (VQFN) 封装 (焊盘朝下)

- -40°C 至 85°C 环境温度范围

#### 2 应用

- 笔记本计算机和超极本

- 平板电视

- 消费类音频应用

# 3 说明

TPA313xD2 是用于驱动扬声器的高效立体声数字放大器功率级,峰值驱动功率高达 2x42W/4Ω。

TPA3131/32D2 的印刷电路板 (PCB) 通过底部 PowerPAD™ 进行散热,无需使用散热器,同时可持续提供 2 × 4W/8Ω (TPA3131D2) 至 2 × 25W/8Ω (TPA3132D2) 范围内的输出功率。

TPA313xD2 高级振荡器/PLL 电路采用多开关频率选项来抑制 AM 干扰; 搭配使用主从模式同步选项时,还可使多个器件实现同步。

TPA313xD2 针对短路、过热、过压、欠压和直流等故障提供了全面保护。 在过载情况下,器件会将故障情况报告给处理器,从而避免自身遭到损坏。

特性兼容器件包括: 2×50W

TPA3116D2 (PowerPAD 朝上)、2×15W

TPA3130D2 (PowerPAD 朝下)和 2 x 30W

TPA3118D2(PowerPAD 朝下)。

# 器件信息<sup>(1)</sup>

| 器件型号      | 封装          | 封装尺寸(标称值)       |  |  |

|-----------|-------------|-----------------|--|--|

| TPA3131D2 | \(OEN (22\) | F 00mm v F 00mm |  |  |

| TPA3132D2 | VQFN (32)   | 5.00mm x 5.00mm |  |  |

(1) 如需了解所有可用封装,请见数据表末尾的可订购产品附录。

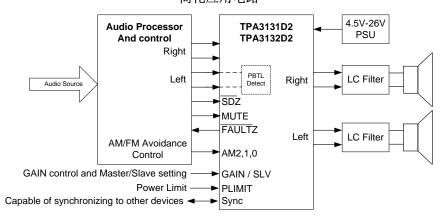

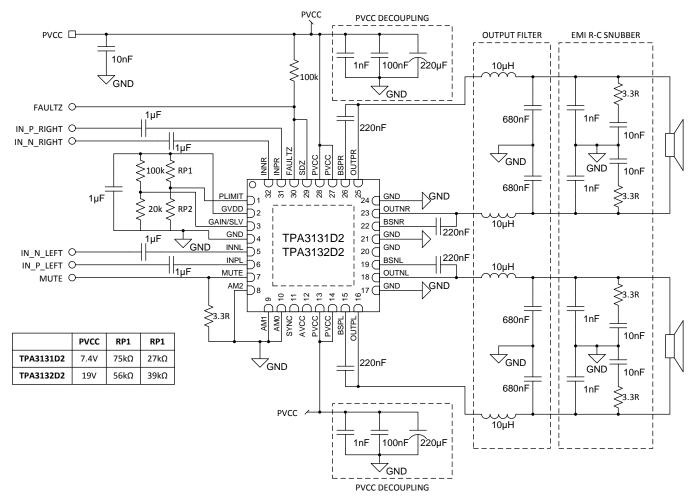

# 简化应用电路

# 目录

| 1 | 特性 1                                    |    | 7.3 Feature Description         | 11               |

|---|-----------------------------------------|----|---------------------------------|------------------|

| 2 | 应用 1                                    |    | 7.4 Device Functional Modes     | 20               |

| 3 |                                         | 8  | Applications and Implementation | 21               |

| 4 | 修订历史记录                                  |    | 8.1 Application Information     | 21               |

| 5 | Pin Configuration and Functions         |    | 8.2 Typical Application         | 21               |

| 6 | Specifications                          | 9  | Power Supply Recommendations    | 23               |

| • | 6.1 Absolute Maximum Ratings            | 10 | Layout                          | 23               |

|   | 6.2 ESD Ratings                         |    | 10.1 Layout Guidelines          |                  |

|   | 6.3 Recommended Operating Conditions    |    | 10.2 Layout Example             | <mark>2</mark> 4 |

|   | 6.4 Thermal Information                 |    | 10.3 Thermal Design             | 25               |

|   | 6.5 DC Electrical Characteristics       | 11 | 器件和文档支持                         | 27               |

|   | 6.6 AC Electrical Characteristics       |    | 11.1 相关链接                       | 27               |

|   | 6.7 Typical Characteristics             |    | 11.2 商标                         | 27               |

| 7 | Detailed Description 11                 |    | 11.3 静电放电警告                     | 27               |

| • | 7.1 Overview                            |    | 11.4 术语表                        |                  |

|   | 7.2 Functional Block Diagram            | 12 | 机械、封装和可订购信息                     | <mark>27</mark>  |

|   | · · = · · · · · · · · · · · · · · · · · |    |                                 |                  |

# 4 修订历史记录

#

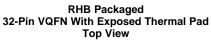

# 5 Pin Configuration and Functions

# **Pin Functions**

|     | PIN TYPE( |                     |                                                                                                                                                       |

|-----|-----------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME      | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                           |

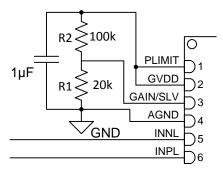

| 1   | PLIMIT    | I                   | Power limit level adjust. Connect a resistor divider from GVDD to GND to set power limit. Connect directly to GVDD for no power limit.                |

| 2   | GVDD      | РО                  | Internally generated gate voltage supply. Not to be used as a supply or connected to any component other than a 1uF X7R ceramic decoupling capacitor. |

| 3   | GAIN/SLV  | I                   | Sets Gain and selects between Master and Slave mode depending on pin voltage divider.                                                                 |

| 4   | GND       | G                   | Ground                                                                                                                                                |

| 5   | INNL      | 1                   | Negative audio input for left channel. Biased at 3V.                                                                                                  |

| 6   | INPL      | 1                   | Positive audio input for left channel. Biased at 3V.                                                                                                  |

| 7   | MUTE      | I                   | Mute signal for fast disable/enable of outputs: HIGH = outputs OFF (high-Z), LOW = outputs ON. TTL logic levels with compliance to AVCC.              |

| 8   | AM2       | I                   | AM Avoidance Frequency Selection                                                                                                                      |

| 9   | AM1       | I                   | AM Avoidance Frequency Selection                                                                                                                      |

| 10  | AM0       | ı                   | AM Avoidance Frequency Selection                                                                                                                      |

| 11  | SYNC      | DIO                 | Clock input/output for synchronizing multiple class-D devices. Direction determined by GAIN/SLV pin. Input signal not to exceed GVDD (7V)             |

| 12  | AVCC      | Р                   | Analog Supply                                                                                                                                         |

| 13  | PVCC      | Р                   | Power supply                                                                                                                                          |

| 14  | PVCC      | Р                   | Power supply                                                                                                                                          |

| 15  | BSPL      | BST                 | Boot strap for positive left channel output, connect to 220nF X7R ceramic cap to OUTPL                                                                |

| 16  | OUTPL     | PO                  | Positive left channel output                                                                                                                          |

| 17  | GND       | G                   | Ground                                                                                                                                                |

| 18  | OUTNL     | PO                  | Negative left channel output                                                                                                                          |

| 19  | BSNL      | BST                 | Boot strap for negative left channel output, connect to 220nF X7R ceramic cap to OUTNL                                                                |

| 20  | GND       | G                   | Ground                                                                                                                                                |

| 21  | GND       | G                   | Ground                                                                                                                                                |

| 22  | BSNR      | BST                 | Boot strap for negative right channel output, connect to 220nF X7R ceramic cap to OUTNR                                                               |

(1) **TYPE**: DO = Digital Output, I = Analog Input, G = General Ground, PO = Power Output, BST = Boot Strap.

# Pin Functions (continued)

|     | PIN         |      | PIN TYPE <sup>(1</sup>                                                                                                        |  | DESCRIPTION |

|-----|-------------|------|-------------------------------------------------------------------------------------------------------------------------------|--|-------------|

| NO. | NAME        | ITPE | DESCRIPTION                                                                                                                   |  |             |

| 23  | OUTNR       | PO   | Negative right channel output                                                                                                 |  |             |

| 24  | GND         | G    | Ground                                                                                                                        |  |             |

| 25  | OUTPR       | PO   | Positive right channel output                                                                                                 |  |             |

| 26  | BSPR        | BST  | Boot strap for positive right channel output, connect to 220nF X7R ceramic cap to OUTPR                                       |  |             |

| 27  | PVCC        | PI   | Power supply                                                                                                                  |  |             |

| 28  | PVCC        | PI   | Power supply                                                                                                                  |  |             |

| 29  | SDZ         | I    | Shutdown logic input for audio amp (LOW = outputs Hi-Z, HIGH = outputs enabled). TTL logic levels with compliance to AVCC.    |  |             |

| 30  | FAULTZ      | DO   | General fault reporting including Over-current_PVCC, OVP_DVDD FAULT1Z = High, normal operation FAULT1Z = Low, fault condition |  |             |

| 31  | INPR        | 1    | Positive audio input for right channel. Biased at 3V.                                                                         |  |             |

| 32  | INNR        | 1    | Negative audio input for right channel. Biased at 3V.                                                                         |  |             |

| 33  | Thermal pad | G    | Connect to GND for best system performance. If not connected to GND, leave floating.                                          |  |             |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)

|                                                |                          | MIN  | MAX      | UNIT |

|------------------------------------------------|--------------------------|------|----------|------|

| Supply voltage, V <sub>CC</sub>                | $PV_{CC}$ , $AV_{CC}$    | -0.3 | 30       | V    |

|                                                | INPL, INNL, INPR, INNR   | -0.3 | 6.3      | V    |

| Input voltage, V <sub>I</sub>                  | PLIMIT, GAIN / SLV, SYNC | -0.3 | GVDD+0.3 | V    |

|                                                | AM0, AM1, AM2, MUTE, SDZ | -0.3 | PVCC+0.3 | V    |

| Slew rate, maximum                             | AM0, AM1, AM2, MUTE, SDZ |      | 10       | V/ms |

| Operating free-air temper                      | erature, T <sub>A</sub>  | -40  | 85       | °C   |

| Operating junction temperature, T <sub>J</sub> |                          | -40  | 150      | °C   |

| Storage temperature, T <sub>s</sub>            | tg                       | -40  | 125      | °C   |

# 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                       |                          |                                                                         | MIN | NOM | MAX | UNIT |

|-----------------------|--------------------------|-------------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>CC</sub>       | Supply voltage           | PV <sub>CC</sub> , AV <sub>CC</sub>                                     | 4.5 |     | 26  | V    |

| V <sub>IH</sub>       | High-level input voltage | AM0, AM1, AM2, MUTE, SDZ, SYNC                                          | 2   |     |     | V    |

| V <sub>IL</sub>       | Low-level input voltage  | AM0, AM1, AM2, MUTE, SDZ, SYNC                                          |     |     | 0.8 | V    |

| V <sub>OL</sub>       | Low-level output voltage | FAULTZ, $R_{PULL-UP} = 100 \text{ k}\Omega$ , $PV_{CC} = 26 \text{ V}$  |     |     | 0.8 | V    |

| I <sub>IH</sub>       | High-level input current | AM0, AM1, AM2, MUTE, SDZ (V <sub>I</sub> = 2 V, V <sub>CC</sub> = 18 V) |     |     | 50  | μΑ   |

| R <sub>L</sub> (BTL)  | Minimum load             | Output filter: L = 10 µH, C = 680 nF                                    | 3.2 | 4   |     | ^    |

| R <sub>L</sub> (PBTL) | Impedance                | Output filter: L = 10 μH, C = 1 μF                                      | 1.6 |     |     | Ω    |

| Lo                    | Output-filter Inductance | Minimum output filter inductance under short-circuit condition          | 1   |     |     | μΗ   |

#### 6.4 Thermal Information

| <b>U.</b> .     | Thomas information                           |           |      |  |  |  |  |

|-----------------|----------------------------------------------|-----------|------|--|--|--|--|

|                 |                                              | TPA313xD2 |      |  |  |  |  |

|                 | THERMAL METRIC <sup>(1)(2)</sup>             | VQFN      | UNIT |  |  |  |  |

|                 |                                              | 32 PINS   |      |  |  |  |  |

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance       | 31.3      |      |  |  |  |  |

| ΨЈТ             | Junction-to-top characterization parameter   | 0.2       | °C/W |  |  |  |  |

| ΨЈВ             | Junction-to-board characterization parameter | 5.5       |      |  |  |  |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> The heat sink drawing used for the thermal model data are shown in the application section, size: 14mm wide, 50mm long, 25mm high.

# 6.5 DC Electrical Characteristics

$\rm T_A = 25^{\circ}C,~AV_{CC} = PV_{CC} = 7.4~V$  to 26 V,  $\rm R_L = 8~\Omega$  (unless otherwise noted)

|                     | PARAMETER                                               | TEST CONDITIONS                                                    | MIN  | TYP  | MAX  | UNIT     |  |

|---------------------|---------------------------------------------------------|--------------------------------------------------------------------|------|------|------|----------|--|

| Vos                 | Class-D output offset voltage (measured differentially) | V <sub>I</sub> = 0 V, Gain = 36 dB                                 |      | 1.5  | 15   | mV       |  |

|                     | Ovices and a supply assessed                            | SDZ = 2 V, No load or filter, PV <sub>CC</sub> = 7.4 V (TPA3131D2) | 16   |      |      |          |  |

| I <sub>CC</sub>     | Quiescent supply current                                | SDZ = 2 V, No load or filter, PV <sub>CC</sub> = 19 V (TPA3132D2)  |      | 27   |      | mA       |  |

| I <sub>CC(SD)</sub> | Quiescent supply current in shutdown mode               | SDZ = 0.8 V, No load or filter                                     |      | <50  |      | μΑ       |  |

| r <sub>DS(on)</sub> | Drain-source on-state resistance, measured pin to pin   | $PV_{CC} = 7.4V$ to 19V V, $I_{out} = 500$ mA, $T_J = 25$ °C       |      | 120  |      | mΩ       |  |

|                     | Gain (MSTR)                                             | R1 = 5.6 kΩ, R2 = Open                                             | 19   | 20   | 21   | 4D       |  |

| G                   |                                                         | R1 = 20 kΩ, $R2 = 100$ kΩ                                          | 25   | 26   | 27   | dB<br>dB |  |

| G                   |                                                         | R1 = 39 kΩ, R2 = 100 kΩ                                            | 31   | 32   | 33   |          |  |

|                     |                                                         | R1 = 47 kΩ, R2 = 75 kΩ                                             | 35   | 36   | 37   |          |  |

|                     |                                                         | R1 = 51 kΩ, R2 = 51 kΩ                                             | 19   | 20   | 21   | -ID      |  |

| 0                   | Caia (CLV)                                              | R1 = 75 kΩ, R2 = 47 kΩ                                             | 25   | 26   | 27   | dB       |  |

| G                   | Gain (SLV)                                              | R1 = 100 kΩ, R2 = 39 kΩ                                            | 31   | 32   | 33   | -ID      |  |

|                     |                                                         | R1 = 100 kΩ, R2 = 16 kΩ                                            | 35   | 36   | 37   | dB       |  |

| t <sub>on</sub>     | Turn-on time                                            | SDZ = 2 V                                                          |      | 10   |      | ms       |  |

| t <sub>OFF</sub>    | Turn-off time                                           | SDZ = 0.8 V                                                        |      | 2    |      | μs       |  |

| GVDD                | Gate drive supply                                       | IGVDD < 200 μA                                                     | 6.4  | 6.9  | 7.4  | ٧        |  |

| Vo                  | Output voltage maximum under PLIMIT control             | V(PLIMIT) = 2 V; V <sub>I</sub> = 1 V <sub>rms</sub>               | 6.75 | 7.90 | 8.75 | ٧        |  |

# 6.6 AC Electrical Characteristics

$\rm T_A = 25^{\circ}C,~AV_{CC} = PV_{CC} = 7.4~V$  to 24 V,  $\rm R_L = 8~\Omega$  (unless otherwise noted)

|       | PARAMETER                         | TEST CONDITIONS                                                                                                                                     | MIN TYP | MAX | UNIT |

|-------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|------|

| KSVR  | Power supply ripple rejection     | 200 mV <sub>PP</sub> ripple at 1 kHz, Gain = 20 dB, Inputs AC-coupled to GND                                                                        | -70     |     | dB   |

|       |                                   | $R_L$ = 8 Ω, THD+N = 10%, f = 1 kHz, $PV_{CC}$ = 7.4 V (TPA3131D2)                                                                                  | 4       |     |      |

| Б     | Continuous sutnut nouser          | $R_L$ = 4 $\Omega$ , THD+N = 10%, f = 1 kHz, $PV_{CC}$ = 7.4 V (TPA3131D2)                                                                          | 7.3     |     | W    |

| Po    | Continuous output power           | $R_L$ = 8 Ω, THD+N = 10%, f = 1 kHz, $PV_{CC}$ = 19V (TPA3132D2)                                                                                    | 25      |     | VV   |

|       |                                   | $R_L = 4 \Omega$ , THD+N = 10%, f = 1 kHz, $PV_{CC} = 19V$ (TPA3132D2)                                                                              |         |     |      |

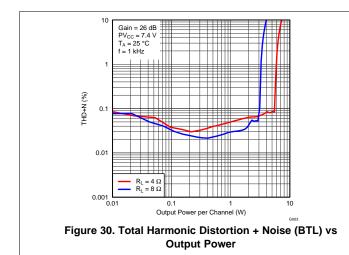

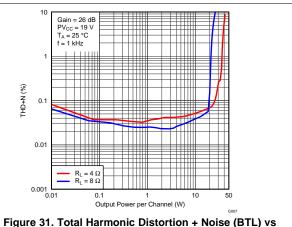

| THD+N | Total harmonic distortion + noise | $R_L = 8 \ \Omega, f = 1 \ kHz, P_O = 0.1W \ to \ 2 \ W \ (TPA3132D2)$<br>$R_L = 8 \ \Omega, f = 1 \ kHz, P_O = 0.1W \ to \ 12.5 \ W \ (TPA3131D2)$ | 0.1%    |     |      |

| Vn    | Output into metal ancies          |                                                                                                                                                     | 70      |     | μV   |

| VII   | Output integrated noise           | 20 Hz to 22 kHz, A-weighted filter, Gain = 20 dB                                                                                                    | -80     |     | dBV  |

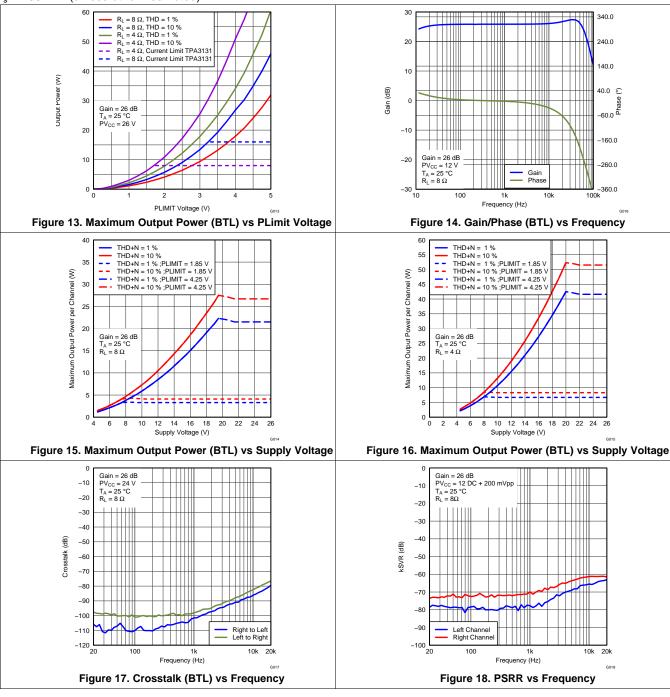

|       | Crosstalk                         | $V_0 = 1 V_{rms}$ , Gain = 20 dB, f = 1 kHz                                                                                                         | -100    |     | dB   |

| SNR   | Signal to naigo ratio             | Maximum output at THD+N < 1%, f = 1 kHz, Gain = 20 dB, A-weighted (TPA3131D2, $PV_{CC}$ = 7.4V)                                                     | 98      |     | dB   |

| SINK  | Signal-to-noise ratio             | Maximum output at THD+N < 1%, f = 1 kHz, Gain = 20 dB, A-weighted (TPA3131D2, $PV_{CC}$ = 19V)                                                      | 105     |     | uБ   |

# **AC Electrical Characteristics (continued)**

$T_{A}$  = 25°C,  $AV_{CC}$  =  $PV_{CC}$  = 7.4 V to 24 V,  $R_{L}$  = 8  $\Omega$  (unless otherwise noted)

|      | PARAMETER                  | TEST CONDITIONS                 | MIN      | TYP  | MAX  | UNIT  |

|------|----------------------------|---------------------------------|----------|------|------|-------|

|      |                            | AM2=0, AM1=0, AM0=0             | 376      | 400  | 424  |       |

|      |                            | AM2=0, AM1=0, AM0=1             | 470      | 500  | 530  |       |

|      |                            | AM2=0, AM1=1, AM0=0             | 564      | 600  | 636  |       |

|      | On sillaton fra successive | AM2=0, AM1=1, AM0=1             | 940      | 1000 | 1060 | 1.11= |

| fosc | Oscillator frequency       | AM2=1, AM1=0, AM0=0             | 1128     | 1200 | 1278 | kHz   |

|      |                            | AM2=1, AM1=0, AM0=1             |          |      |      |       |

|      |                            | AM2=1, AM1=1, AM0=0             | Reserved |      |      |       |

|      |                            | AM2=1, AM1=1, AM0=1             |          |      |      |       |

|      | Thermal trip point         |                                 |          | 150+ |      | °C    |

|      | Thermal hysteresis         |                                 | 15       |      |      | °C    |

|      | Over average their regist  | TPA3131D2                       | 3.4      |      |      | Α     |

|      | Over current trip point    | er current trip point TPA3132D2 |          | 7    |      |       |

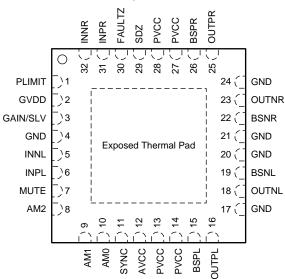

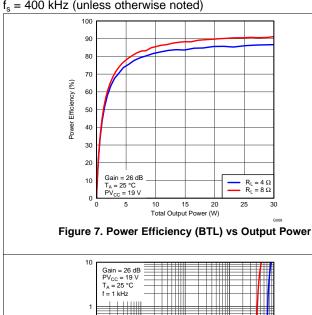

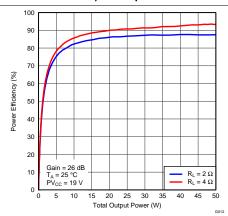

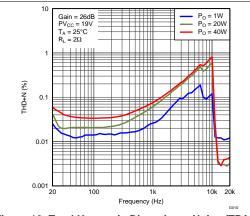

# 6.7 Typical Characteristics

$f_s = 400 \text{ kHz}$  (unless otherwise noted)

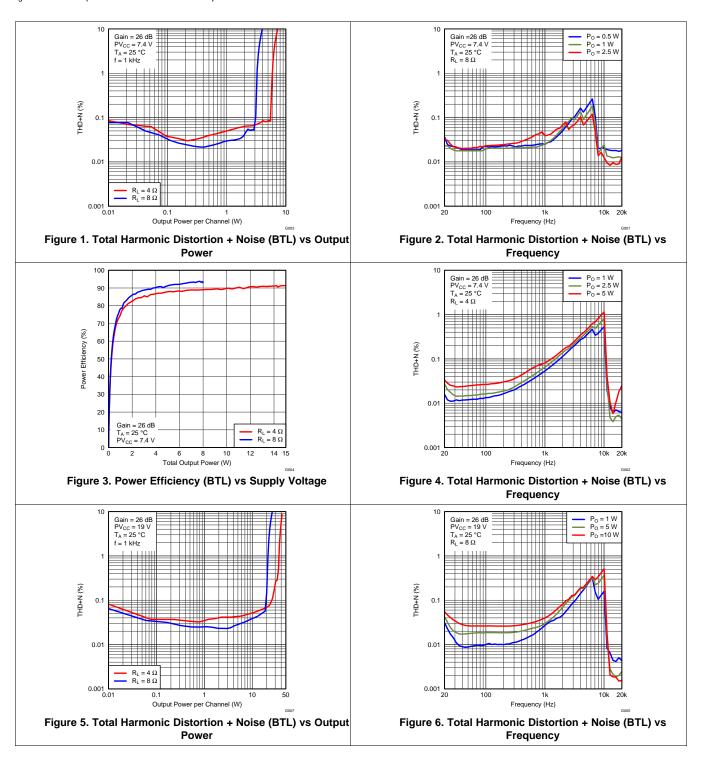

# **Typical Characteristics (continued)**

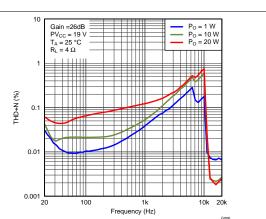

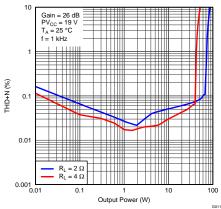

f<sub>s</sub> = 400 kHz (unless otherwise noted)

Figure 8. Total Harmonic Distortion + Noise (BTL) vs Frequency

Figure 9. Total Harmonic Distortion + Noise (TPA3132D2 **PBTL) vs Output Power**

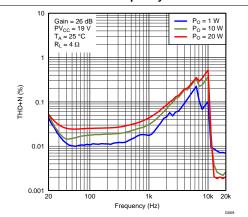

Figure 10. Total Harmonic Distortion + Noise (TPA3132D2 PBTL) vs Frequency

Figure 11. Power Efficiency (TPA3132D2 PBTL) vs Output Power

Figure 12. Total Harmonic Distortion + Noise (TPA3132D2 PBTL) vs Frequency

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

f<sub>s</sub> = 400 kHz (unless otherwise noted)

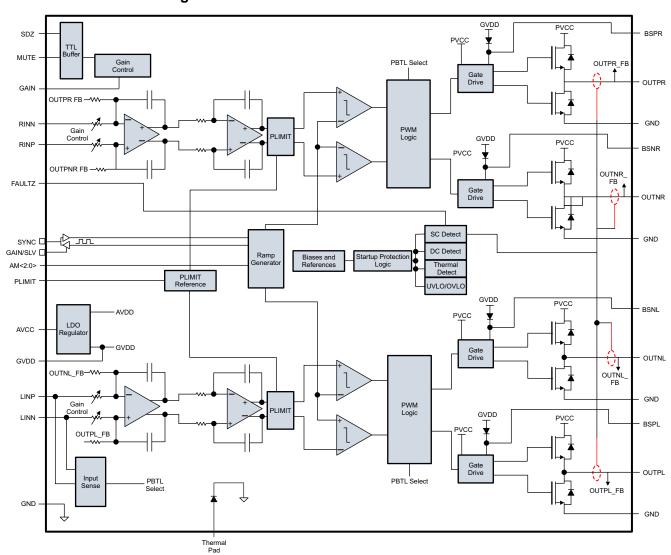

# 7 Detailed Description

#### 7.1 Overview

The TPA3132D2 device is a high-efficiency stereo Class-D audio power amplifier optimized for high-transient power capability to utilize the dynamic power headroom of small loudspeakers. It's capable of delivering high peak power into a  $4-\Omega$  speaker.

The device can be configured for either master or slave operation by using the SYNC pin. This helps to prevent audible beats noise.

# 7.2 Functional Block Diagram

# 7.3 Feature Description

#### 7.3.1 Gain Setting and Master and Slave

The gain of the TPA3131D2 is set by the voltage divider connected to the GAIN/SLV control pin. Master or Slave mode is also controlled by the same pin. An internal ADC is used to detect the 8 input states. The first four stages sets the GAIN in Master mode in gains of 20, 26, 32, 36 dB respectively, while the next four stages sets the GAIN in Slave mode in gains of 20, 26, 32, 36 dB respectively. The gain setting is latched during power-up and cannot be changed while device is powered. shows the recommended resistor values and the state and gain:

# **Feature Description (continued)**

#### Table 1. Gain and Master/Slave

| MASTER / SLAVE<br>MODE | GAIN  | R1 (to GND) | R2 (to GVDD) | INPUT IMPEDANCE |

|------------------------|-------|-------------|--------------|-----------------|

| Master                 | 20 dB | 5.6 kΩ      | OPEN         | 60 kΩ           |

| Master                 | 26 dB | 20 kΩ       | 100 kΩ       | 30 kΩ           |

| Master                 | 32 dB | 39 kΩ       | 100 kΩ       | 15 kΩ           |

| Master                 | 36 dB | 47 kΩ       | 75 kΩ        | 9 kΩ            |

| Slave                  | 20 dB | 51 kΩ       | 51 kΩ        | 60 kΩ           |

| Slave                  | 26 dB | 75 kΩ       | 47 kΩ        | 30 kΩ           |

| Slave                  | 32 dB | 100 kΩ      | 39 kΩ        | 15 kΩ           |

| Slave                  | 36 dB | 100 kΩ      | 16 kΩ        | 9 kΩ            |

Figure 19. Gain and Master/Slave Select Resistors

In Master mode, SYNC terminal is an output, in Slave mode, SYNC terminal is an input for a clock input. TTL logic levels with compliance to GVDD.

#### 7.3.2 Input Impedance

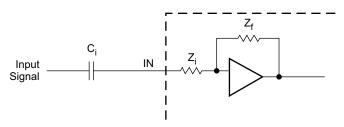

The TPA313xD2 input stage is a fully differential input stage and the input impedance changes with the gain setting from 9 k $\Omega$  at 36 dB gain to 60 k $\Omega$  at 20 dB gain. Table 1 lists the values from min to max gain. The tolerance of the input resistor value is ±20% so the minimum value will be higher than 7.2 k $\Omega$ . The inputs need to be AC-coupled to minimize the output dc-offset and ensure correct ramping of the output voltages during power-ON and power-OFF. The input ac-coupling capacitor together with the input impedance forms a high-pass filter with the following cut-off frequency:

$$f = \frac{1}{2\pi Z_i C_i} \tag{1}$$

If a flat bass response is required down to 20 Hz the recommended cut-off frequency is a tenth of that, 2 Hz. lists the recommended ac-couplings capacitors for each gain step. If a -3 dB is accepted at 20 Hz 10 times lower capacitors can used – for example, a 1  $\mu$ F can be used.

**Table 2. Recommended Input AC-Coupling Capacitors**

| GAIN  | INPUT IMPEDANCE | INPUT CAPACITANCE | HIGH-PASS FILTER |

|-------|-----------------|-------------------|------------------|

| 20 dB | 60 kΩ           | 1.5 µF            | 1.8 Hz           |

| 26 dB | 30 kΩ           | 3.3 µF            | 1.6 Hz           |

| 32 dB | 15 kΩ           | 5.6 μF            | 2.3 Hz           |

| 36 dB | 9 kΩ            | 10 μF             | 1.8 Hz           |

Figure 20. Input AC Coupling

The input capacitors used should be a type with low leakage, like quality electrolytic, tantalum or ceramic. If a polarized type is used the positive connection should face the input pins which are biased to 3 Vdc.

#### 7.3.3 Start-up/Shutdown Operation

The TPA313xD2 employs a shutdown mode of operation designed to reduce supply current (Icc) to the absolute minimum level during periods of nonuse for power conservation. The SDZ input terminal should be held high (see specification table for trip point) during normal operation when the amplifier is in use. Pulling SDZ low will put the outputs to mute and the amplifier to enter a low-current state. It is not recommended to leave SDZ unconnected, because amplifier operation would be unpredictable.

For the best power-off pop performance, place the amplifier in the shutdown mode prior to removing the power supply. The gain setting is selected at the end of the start-up cycle. At the end of the start-up cycle, the gain is selected and cannot be changed until the next power-up.

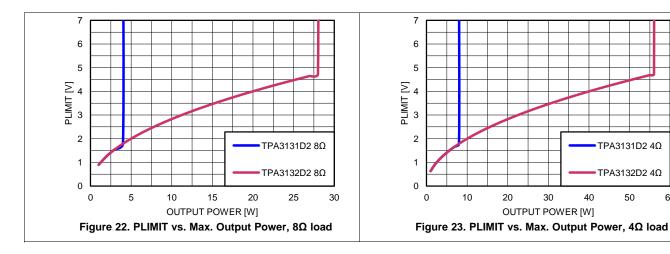

# 7.3.4 PLIMIT Operation

The TPA313xD2 has a built-in voltage limiter that can be used to limit the output voltage level below the supply rail, the amplifier simply operates as if it was powered by a lower supply voltage, and thereby limits the output power. Add a resistor divider from GVDD to ground to set the voltage at the PLIMIT pin. An external reference may also be used if tighter tolerance is required. Add a 1  $\mu$ F capacitor from pin PLIMIT to ground to ensure stability.

Figure 21. Power Limit Example

The PLIMIT circuit sets a limit on the output peak-to-peak voltage. The limiting is done by limiting the duty cycle to a fixed maximum value. This limit can be thought of as a "virtual" voltage rail which is lower than the supply connected to PVCC. This "virtual" rail is approximately 4 times the voltage at the PLIMIT pin. This output voltage can be used to calculate the maximum output power for a given maximum input voltage and speaker impedance.

TPA3131D2 40

TPA3132D2 4Ω

$$P_{OUT} = \frac{\left( \left( \frac{R_L}{R_L + 2 \times R_S} \right) \times V_P \right)^2}{2 \times R_I} \quad \text{for unclipped power}$$

where

- $P_{OUT}$  (10%THD) = 1.25 x  $P_{OUT}$  (unclipped)

- R<sub>I</sub> is the load resistance.

- R<sub>S</sub> is the total series resistance including R<sub>DS(on)</sub>, and output filter resistance.

- V<sub>P</sub> is the peak amplitude

- V<sub>P</sub> = 4 x PLIMIT voltage if PLIMIT < 4 x V<sub>P</sub>

(2)

Increasing the PLIMIT voltage from a given value increases the maximum output voltage swing until it equals PVCC. Adjusting PLIMIT to a higher value will disable the PLIMIT function and will offer highest available output power, however for TPA3131D2 and TPA3132D2 it is always advised to use the PLIMIT function if PVCC is higher than nominal value to prevent shutdown due to over current protection. If PLIMIT is disabled on TPA3131D2 and TPA3132D2 an over current shutdown can occur with minimum recommended load impedance when PVCC is higher than its nominal value. To disable the PLIMIT function, the PLIMIT pin is simply connected to GVDD.

**Table 3. Power Limit Example**

| MINIMUM<br>PV <sub>CC</sub> (V) | PART NUMBERS         | PART NUMBERS PLIMIT VOLTAGE (V) <sup>(1)</sup> |       | R to GVDD | OUTPUT POWER 8Ω (W) |

|---------------------------------|----------------------|------------------------------------------------|-------|-----------|---------------------|

| 7.4 V                           | TPA3131D2, TPA3132D2 | 1.85                                           | 27 kΩ | 75 kΩ     | 4                   |

| 12 V                            | TPA3132D2            | 2.87                                           | 39 kΩ | 56 kΩ     | 10                  |

| 19 V                            | TPA3132D2            | 4.26                                           | 56 kΩ | 36 kΩ     | 25                  |

(1) PLIMIT measurements taken with EVM gain set to 26dB and input level adjusted for 10% THD.

#### 7.3.5 GVDD Supply

The GVDD Supply is used to power the gates of the output full bridge transistors. It can also be used to supply the PLIMIT and GAIN/SLV voltage dividers. Decouple GVDD with a X5R ceramic 1 µF capacitor to GND. The GVDD supply is not intended to be used for external supply. It is recommended to limit the current consumption by using resistor voltage dividers for GAIN/SLV and PLIMIT of 100 k $\Omega$  or more.

### 7.3.6 BSPx and BSNx Capacitors

The full H-bridge output stages use only NMOS transistors. Therefore, they require bootstrap capacitors for the high side of each output to turn on correctly. A 220 nF ceramic capacitor of quality X5R or better, rated for at least 16 V, must be connected from each output to its corresponding bootstrap input. (See the application circuit diagram in Figure 29.) The bootstrap capacitors connected between the BSxx pins and corresponding output function as a floating power supply for the high-side N-channel power MOSFET gate drive circuitry. During each high-side switching cycle, the bootstrap capacitors hold the gate-to-source voltage high enough to keep the high-side MOSFETs turned on.

#### 7.3.7 Differential Inputs

The differential input stage of the amplifier cancels any noise that appears on both input lines of the channel. To use the TPA313xD2 with a differential source, connect the positive lead of the audio source to the RINP or LINP input and the negative lead from the audio source to the RINN or LINN input. To use the TPA313xD2 with a single-ended source, ac ground the negative input through a capacitor equal in value to the input capacitor on positive and apply the audio source to either input. In a single-ended input application, the unused input should be ac grounded at the audio source instead of at the device input for best noise performance. For good transient performance, the impedance seen at each of the two differential inputs should be the same.

The impedance seen at the inputs should be limited to an RC time constant of 1 ms or less if possible. This is to allow the input dc blocking capacitors to become completely charged during the 10 ms power-up time. If the input capacitors are not allowed to completely charge, there will be some additional sensitivity to component matching which can result in pop if the input components are not well matched.

#### 7.3.8 Device Protection System

The TPA313xD2 contains a complete set of protection circuits carefully designed to make system design efficient as well as to protect the device against any kind of permanent failures due to short circuits, overload, over temperature, and under-voltage. The FAULTZ pin will signal if an error is detected according to the fault table below:

|                                            |                                      | •      | _                     |                           |

|--------------------------------------------|--------------------------------------|--------|-----------------------|---------------------------|

| FAULT TRIGGERING CONDITION (typical value) |                                      | FAULTZ | ACTION                | LATCHED/SELF-<br>CLEARING |

| Over Current                               | Output short or short to PVCC or GND | Low    | Output high impedance | Latched                   |

| Over Temperature                           | T <sub>j</sub> > 150°C               | Low    | Output high impedance | Latched                   |

| Too High DC Offset                         | DC output voltage                    | Low    | Output high impedance | Latched                   |

| Under Voltage on PVCC                      | PVCC < 4.5V                          | ı      | Output high impedance | Self-clearing             |

| Over Voltage on PVCC                       | PVCC > 27V                           | -      | Output high impedance | Self-clearing             |

**Table 4. Fault Reporting**

#### 7.3.9 DC Detect Protection

The TPA313xD2 has circuitry which will protect the speakers from DC current which might occur due to defective capacitors on the input or shorts on the printed circuit board at the inputs. A DC detect fault will be reported on the FAULT pin as a low state. The DC Detect fault will also cause the amplifier to shutdown by changing the state of the outputs to Hi-Z.

If automatic recovery from the short circuit protection latch is desired, connect the FAULTZ pin directly to the SDZ pin. This allows the DC Protection function to automatically drive the SDZ pin low which clears the DC Detect protection latch.

A DC Detect Fault is issued when the output differential duty-cycle of either channel exceeds 60% for more than 420 msec at the same polarity. Table x below shows some examples of the typical DC Detect Protection threshold for several values of the supply voltage. This feature protects the speaker from large DC currents or AC currents less than 2Hz. To avoid nuisance faults due to the DC detect circuit, hold the SD pin low at power-up until the signals at the inputs are stable. Also, take care to match the impedance seen at the positive and negative inputs to avoid nuisance DC detect faults.

The minimum output offset voltages required to trigger the DC detect are show in Table 5. The outputs must remain at or above the voltage listed in the table for more than 420 msec to trigger the DC detect.

**Table 5. DC Detect Threshold**

| PV <sub>CC</sub> (V) | V <sub>OS</sub> - OUTPUT OFFSET VOLTAGE (V) |

|----------------------|---------------------------------------------|

| 4.5                  | 0.96                                        |

| 6                    | 1.3                                         |

| 12                   | 2.6                                         |

| 18                   | 3.9                                         |

# 7.3.10 Short-Circuit Protection and Automatic Recovery Feature

The TPA313xD2 has protection from over current conditions caused by a short circuit on the output stage. The short circuit protection fault is reported on the FAULTZ pin as a low state. The amplifier outputs are switched to a high impedance state when the short circuit protection latch is engaged. The latch can be cleared by cycling the SDZ pin through the low state.

If automatic recovery from the short circuit protection latch is desired, connect the FAULTZ pin directly to the SDZ pin. This allows the FAULTZ pin function to automatically drive the SDZ pin low which clears the short-circuit protection latch.

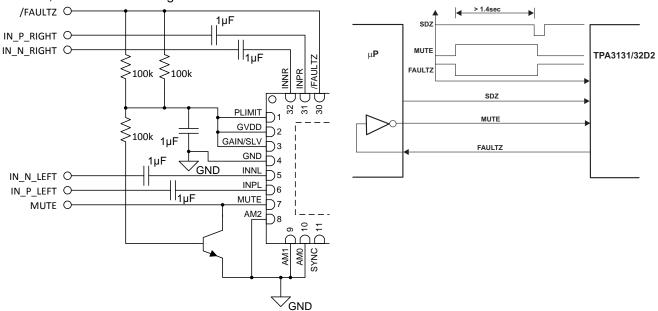

In systems where a possibility of a permanent short from the output to PVDD or to a high voltage battery like a car battery can occur, pull the MUTE pin low with the FAULTZ signal with a inverting transistor to ensure a high-Z restart, like shown in the figure below:

Figure 24. MUTE Driven by Inverted FAULTZ

Figure 25. Timing Requirement for SDZ

#### 7.3.11 Thermal Protection

Thermal protection on the TPA313xD2 prevents damage to the device when the internal die temperature exceeds 150°C. There is a ±15°C tolerance on this trip point from device to device. Once the die temperature exceeds the thermal trip point, the device enters into the shutdown state and the outputs are disabled. This is a latched fault.

Thermal protection faults are reported on the FAULTZ terminal as a low state.

If automatic recovery from the thermal protection latch is desired, connect the FAULTZ pin directly to the SDZ pin. This allows the FAULTZ pin function to automatically drive the SDZ pin low which clears the thermal protection latch.

### 7.3.12 Efficiency: LC Filter Required with the Traditional Class-D Modulation Scheme

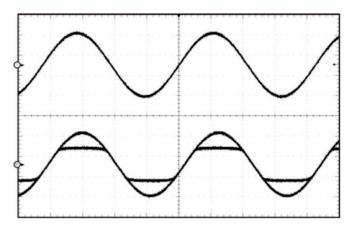

The main reason that the traditional class-D amplifier-based on AD modulation needs an output filter is that the switching waveform results in maximum current flow. This causes more loss in the load, which causes lower efficiency. The ripple current is large for the traditional modulation scheme, because the ripple current is proportional to voltage multiplied by the time at that voltage. The differential voltage swing is 2 × VCC, and the time at each voltage is half the period for the traditional modulation scheme. An ideal LC filter is needed to store the ripple current from each half cycle for the next half cycle, while any resistance causes power dissipation. The speaker is both resistive and reactive, whereas an LC filter is almost purely reactive.

The TPA313xD2 modulation scheme has little loss in the load without a filter because the pulses are short and the change in voltage is VCC instead of  $2 \times VCC$ . As the output power increases, the pulses widen, making the ripple current larger. Ripple current could be filtered with an LC filter for increased efficiency, but for most applications the filter is not needed.

An LC filter with a cutoff frequency less than the class-D switching frequency allows the switching current to flow through the filter instead of the load. The filter has less resistance but higher impedance at the switching frequency than the speaker, which results in less power dissipation, therefore increasing efficiency.

#### 7.3.13 Ferrite Bead Filter Considerations

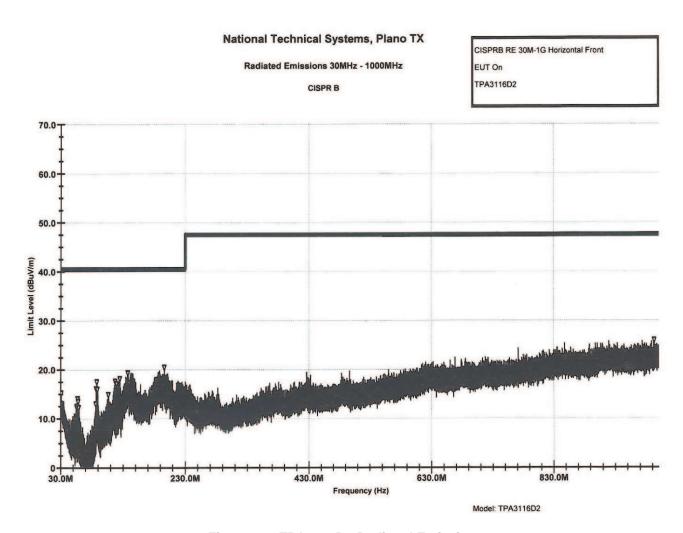

Using the Advanced Emissions Suppression Technology in the TPA313xD2 amplifier it is possible to design a high efficiency class-D audio amplifier while minimizing interference to surrounding circuits. It is also possible to accomplish this with only a low-cost ferrite bead filter. In this case it is necessary to carefully select the ferrite bead used in the filter. One important aspect of the ferrite bead selection is the type of material used in the ferrite bead. Not all ferrite material is alike, so it is important to select a material that is effective in the 10 to 100 MHz range which is key to the operation of the class-D amplifier. Many of the specifications regulating consumer electronics have emissions limits as low as 30 MHz. It is important to use the ferrite bead filter to block radiation in the 30 MHz and above range from appearing on the speaker wires and the power supply lines which are good antennas for these signals. The impedance of the ferrite bead can be used along with a small capacitor with a value in the range of 1000 pF to reduce the frequency spectrum of the signal to an acceptable level. For best performance, the resonant frequency of the ferrite bead/ capacitor filter should be less than 10 MHz.

Also, it is important that the ferrite bead is large enough to maintain its impedance at the peak currents expected for the amplifier. Some ferrite bead manufacturers specify the bead impedance at a variety of current levels. In this case it is possible to make sure the ferrite bead maintains an adequate amount of impedance at the peak current the amplifier will see. If these specifications are not available, it is also possible to estimate the bead current handling capability by measuring the resonant frequency of the filter output at low power and at maximum power. A change of resonant frequency of less than fifty percent under this condition is desirable. Examples of ferrite beads which have been tested and work well with the TPA3130D2 can be seen in the TPA3130D2EVM user guide SLOU341.

A high quality ceramic capacitor is also needed for the ferrite bead filter. A low ESR capacitor with good temperature and voltage characteristics will work best.

Additional EMC improvements may be obtained by adding snubber networks from each of the class-D outputs to ground. Suggested values for a simple RC series snubber network would be 18  $\Omega$  in series with a 330 pF capacitor although design of the snubber network is specific to every application and must be designed taking into account the parasitic reactance of the printed circuit board as well as the audio amp. Take care to evaluate the stress on the component in the snubber network especially if the amp is running at high PVCC. Also, make sure the layout of the snubber network is tight and returns directly to the GND pins on the IC.

Figure 26. TPA311xD2 Radiated Emissions

# 7.3.14 When to Use an Output Filter for EMI Suppression

The TPA313xD2 has been tested with a simple ferrite bead filter for a variety of applications including long speaker wires up to 125 cm and high power. The TPA313xD2 EVM passes FCC class-B specifications under these conditions using twisted speaker wires. The size and type of ferrite bead can be selected to meet application requirements. Also, the filter capacitor can be increased if necessary with some impact on efficiency.

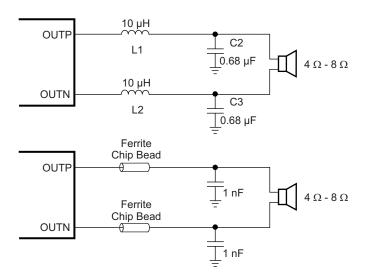

There may be a few circuit instances where it is necessary to add a complete LC reconstruction filter. These circumstances might occur if there are nearby circuits which are sensitive to noise. In these cases a classic second order Butterworth filter similar to those shown in the figures below can be used.

Some systems have little power supply decoupling from the AC line but are also subject to line conducted interference (LCI) regulations. These include systems powered by "wall warts" and "power bricks." In these cases, LC reconstruction filters can be the lowest cost means to pass LCI tests. Common mode chokes using low frequency ferrite material can also be effective at preventing line conducted interference.

Figure 27. Output Filter Configurations

# 7.3.15 AM Avoidance EMI Reduction

To reduce interference in the AM radio band, the TPA313xD2 has the ability to change the switching frequency via AM<2:0> pins. The recommended frequencies are listed in Table 6. The fundamental frequency and its second harmonic straddle the AM radio band listed. This eliminates the tones that can be present due to the switching frequency being demodulated by the AM radio.

**Table 6. AM Frequencies**

| US                 | EUROPEAN           |                           |     |     |     |

|--------------------|--------------------|---------------------------|-----|-----|-----|

| AM FREQUENCY (kHz) | AM FREQUENCY (kHz) | SWITCHING FREQUENCY (kHz) | AM2 | AM1 | AM0 |

|                    | 522-540            |                           |     |     |     |

| 540-917            | 540-914            | 500                       | 0   | 0   | 1   |

| 047.4425           | 914-1122           | 600 (or 400)              | 0   | 1   | 0   |

| 917-1125           | 914-1122           | 600 (or 400)              | 0   | 0   | 0   |

| 1125-1375          | 1122-1373          | 500                       | 0   | 0   | 1   |

| 1375-1547          | 1373-1548          | 600 (or 400)              | 0   | 1   | 0   |

| 1375-1547          | 1373-1546          | 600 (or 400)              | 0   | 0   | 0   |

| 4547 4700          | 4549.4704          | 600 (07 500)              | 0   | 1   | 0   |

| 1547-1700          | 1548-1701          | 600 (or 500)              | 0   | 0   | 1   |

#### 7.4 Device Functional Modes

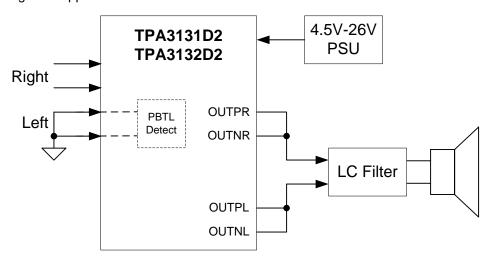

# 7.4.1 Mono Mode (PBTL)

The TPA313xD2 can be connected in MONO mode enabling up to 85W output power. This is done by:

- Connect INPL and INNL directly to Ground (without capacitors) this sets the device in Mono mode during power up.

- Connect OUTPR and OUTNR together for the positive speaker terminal and OUTNL and OUTPL together for the negative terminal.

- Analog input signal is applied to INPR and INNR.

Figure 28. Output Mode select

# 8 Applications and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# 8.1 Application Information

This section describes a typical stereo speaker application with differential inputs. The amplifier gain is set to 26 dB and the output PWM is set to 400 kHz.

# 8.2 Typical Application

Figure 29. Typical Application Schematic

# 8.2.1 Design Requirements

| DESIGN PARAMETERS        | EXAMPLE VALUE                               |

|--------------------------|---------------------------------------------|

| Input voltage range PVCC | 4.5 V to 26 V                               |

| PWM output frequencies   | 400 kHz, 500 kHz, 600 kHz, 1 MHz or 1.2 MHz |

| Maximum output power     | 25 Wx2 (TPA3132D2) or 4 Wx2 (TPA3131D2)     |

#### 8.2.2 Detailed Design Procedure

The TPA31xxD2 is a very flexible and easy to use Class D amplifier; therefore the design process is straightforward. Before beginning the design, gather the following information regarding the audio system.

- PVCC rail planned for the design

- Speaker or load impedance

- Maximum output power requirement

- Desired PWM frequency

# 8.2.2.1 Select the PWM Frequency

Set the PWM frequency by using AM0, AM1 and AM2 pins.

# 8.2.2.2 Select the Amplifier Gain and Master/Slave Mode

In order to select the amplifier gain setting, the designer must determine the maximum power target and the speaker impedance. Once these parameters have been determined, calculate the required output voltage swing which delivers the maximum output power.

Choose the lowest analog gain setting that corresponds to produce an output voltage swing greater than the required output swing for maximum power. The analog gain and master/slave mode can be set by selecting the voltage divider resistors (R1 and R2) on the Gain/SLV pin.

# 8.2.2.3 Select Input Capacitance

Select the bulk capacitors at the PVCC inputs for proper voltage margin and adequate capacitance to support the power requirements. In practice, with a well-designed power supply, two 100-µF, 50-V capacitors should be sufficient. One capacitor should be placed near the PVCC inputs at each side of the device. PVCC capacitors should be a low ESR type because they are being used in a high-speed switching application.

#### 8.2.2.4 Select Decoupling Capacitors

Good quality decoupling capacitors need to be added at each of the PVCC inputs to provide good reliability, good audio performance, and to meet regulatory requirements. X5R or better ratings should be used in this application. Consider temperature, ripple current, and voltage overshoots when selecting decoupling capacitors. Also, these decoupling capacitors should be located near the PVCC and GND connections to the device in order to minimize series inductances.

#### 8.2.2.5 Select Bootstrap Capacitors

Each of the outputs require bootstrap capacitors to provide gate drive for the high-side output FETs. For this design, use 0.22-µF, 25-V capacitors of X5R quality or better.

#### 8.2.3 Application Curves

Figure 31. Total Harmonic Distortion + Noise (BTL) vs

Output Power

# 9 Power Supply Recommendations

The power supply requirements for the TPA313xD2 device consist of one higher-voltage supply to power the output stage of the speaker amplifier. Several on-chip regulators are included on the TPA3116D2 device to generate the voltages necessary for the internal circuitry of the audio path. It is important to note that the voltage regulators which have been integrated are sized only to provide the current necessary to power the internal circuitry. The external pins are provided only as a connection point for off-chip bypass capacitors to filter the supply. Connecting external circuitry to these regulator outputs may result in reduced performance and damage to the device. The high voltage supply, between 4.5 V and 26 V, supplies the analog circuitry (AVCC) and the power stage (PVCC). The AVCC supply feeds internal LDO including GVDD. This LDO output are connected to external pins for filtering purposes, but should not be connected to external circuits. GVDD LDO output have been sized to provide current necessary for internal functions but not for external loading.

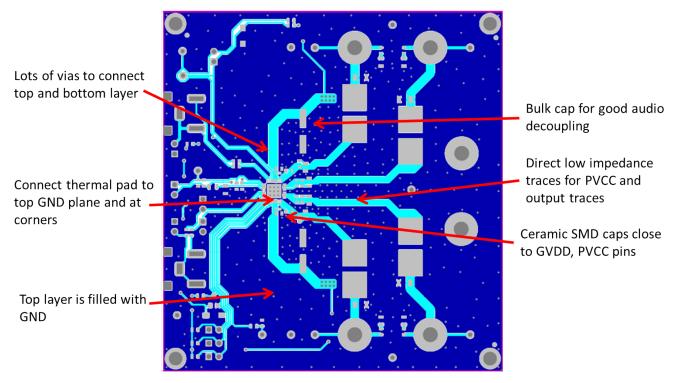

# 10 Layout

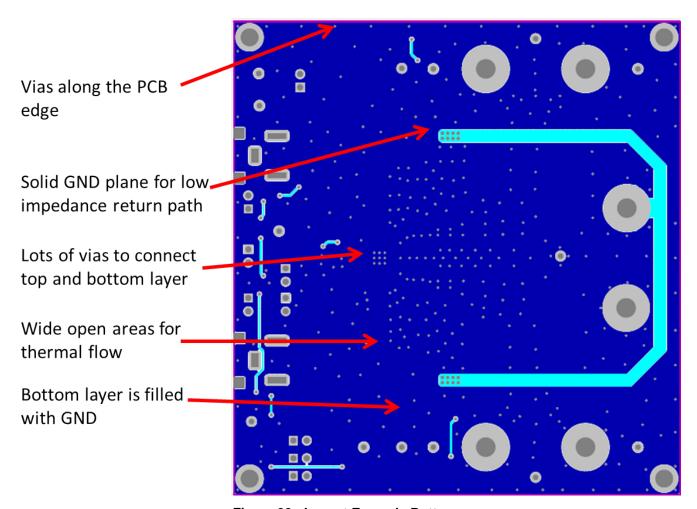

# 10.1 Layout Guidelines

The TPA313xD2 can be used with a small, inexpensive ferrite bead output filter for most applications. However, since the class-D switching edges are fast, it is necessary to take care when planning the layout of the printed circuit board. The following suggestions will help to meet EMC requirements.

- Decoupling capacitors The high-frequency decoupling capacitors should be placed as close to the PVCC and AVCC terminals as possible. Large (100 μF or greater) bulk power supply decoupling capacitors should be placed near the TPA313xD2 on the PVCC supplies. Local, high-frequency bypass capacitors should be placed as close to the PVCC pins as possible. These caps can be connected to the IC GND pad directly for an excellent ground connection. Consider adding a small, good quality low ESR ceramic capacitor between 220 pF and 1 nF and a larger mid-frequency cap of value between 100 nF and 1 μF also of good quality to the PVCC connections at each end of the chip.

- Keep the current loop from each of the outputs through the ferrite bead and the small filter cap and back to GND as small and tight as possible. The size of this current loop determines its effectiveness as an antenna.

- Grounding The PVCC decoupling capacitors should connect to GND. All ground should be connected at the IC GND, which should be used as a central ground connection or star ground for the TPA313xD2.

- Output filter The ferrite EMI filter (see Figure 27) should be placed as close to the output terminals as

possible for the best EMI performance. The LC filter should be placed close to the outputs. The capacitors

used in both the ferrite and LC filters should be grounded.

For an example layout, see the TPA313xD2 Evaluation Module (TPA313xD2EVM) User Manual. Both the EVM user manual and the thermal pad application report are available on the TI Web site at http://www.ti.com.

# 10.2 Layout Example

Figure 32. Layout Example Top

# **Layout Example (continued)**

Figure 33. Layout Example Bottom

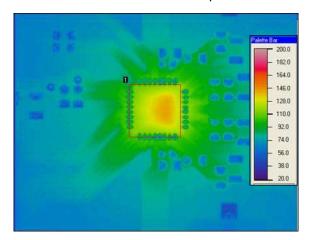

#### 10.3 Thermal Design

Main thermal path for cooling the device is from the bottom side PowerPAD through multiple via connections in the PCB to the bottom side ground plane. The high power efficiency allows TPA3131D2 to be operated continuously at rated output power into both 4- $\Omega$  and 8- $\Omega$  load, and TPA3132D2 into 8- $\Omega$  load using a PCB layout similar to what is used in the TPA3131D2/32D2 EVMs. The rated output power of TPA3132D2 into 4- $\Omega$  load will be available only for a limited duration of time when using a PCB layout similar to the EVM layout. Sustained power output into 4  $\Omega$  needs to be limited to prevent excess heating of the device. TPA3132D2 will be able to output full output power for a limited duration of time. The duration depends on the actual PCB layout. For the TPA3132D2 EVM layout the TPA3132D2 full output power with 4- $\Omega$  load can be illustrated with a burst test at room temp (25°C):

Table 7. TPA3132D2 EVM Burst Output Power

| BURST<br>RATIO | FULL POWER 1kHz     | REDUCED POWER 1kHz<br>(1/8 of full power) | MAXIMUM DEVICE<br>TEMPERATURE | PCB TEMPERATURE (Bottom Side, Under Device) |

|----------------|---------------------|-------------------------------------------|-------------------------------|---------------------------------------------|

| 1:3            | 1 Cycle 44 W / 4 Ω  | 2 Cycles 5.25 W / 4 Ω                     | 116°C                         | 85°C                                        |

| 2:5            | 2 Cycles 44 W / 4 Ω | 3 Cycles 5.25 W / 4 Ω                     | 143°C                         | 102°C                                       |

It is not recommended to operate the device with a maximum temperature above 150°C.

Figure 34. TPA3132D2 EVM Temperature with 2:5 (42W/5.25W/4Ω) Burst Power

It is advised to use the PLIMT function to avoid thermal shutdown in system designs not using signal processing to limit the average output power. Such systems can accidentally exceed the thermal limits of the amplifier and a OTE shutdown will occur.

# 11 器件和文档支持

# 11.1 相关链接

以下表格列出了快速访问链接。 范围包括技术文档、支持与社区资源、工具和软件,并且可以快速访问样片或购买链接。

表 8. 相关链接

| 器件        | 产品文件夹 | 样片与购买 | 技术文档  | 工具与软件 | 支持与社区 |

|-----------|-------|-------|-------|-------|-------|

| TPA3131D2 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |

| TPA3132D2 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |

# 11.2 商标

PowerPAD is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

# 11.3 静电放电警告

这些装置包含有限的内置 ESD 保护。 存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

# 11.4 术语表

SLYZ022 — TI 术语表。

这份术语表列出并解释术语、首字母缩略词和定义。

# 12 机械、封装和可订购信息

以下页中包括机械、封装和可订购信息。 这些信息是针对指定器件可提供的最新数据。 这些数据会在无通知且不对本文档进行修订的情况下发生改变。 欲获得该数据表的浏览器版本,请查阅左侧的导航栏。

www.ti.com 23-Mar-2024

#### PACKAGING INFORMATION

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| TPA3131D2RHBR    | ACTIVE     | VQFN         | RHB                | 32   | 3000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 85    | TPA3131                 | Samples |

| TPA3131D2RHBT    | ACTIVE     | VQFN         | RHB                | 32   | 250            | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | TPA3131                 | Samples |

| TPA3132D2RHBR    | ACTIVE     | VQFN         | RHB                | 32   | 3000           | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | TPA3132                 | Samples |

| TPA3132D2RHBT    | ACTIVE     | VQFN         | RHB                | 32   | 250            | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | TPA3132                 | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

# **PACKAGE OPTION ADDENDUM**

www.ti.com 23-Mar-2024

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

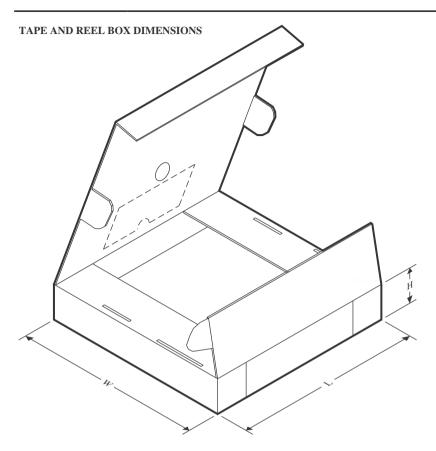

**PACKAGE MATERIALS INFORMATION**

www.ti.com 20-Apr-2023

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

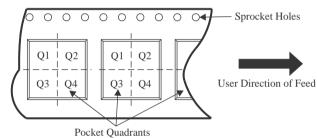

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPA3131D2RHBR | VQFN            | RHB                | 32 | 3000 | 330.0                    | 12.4                     | 5.3        | 5.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPA3131D2RHBT | VQFN            | RHB                | 32 | 250  | 180.0                    | 12.4                     | 5.3        | 5.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPA3132D2RHBR | VQFN            | RHB                | 32 | 3000 | 330.0                    | 12.4                     | 5.3        | 5.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPA3132D2RHBT | VQFN            | RHB                | 32 | 250  | 180.0                    | 12.4                     | 5.3        | 5.3        | 1.1        | 8.0        | 12.0      | Q2               |

www.ti.com 20-Apr-2023

# \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPA3131D2RHBR | VQFN         | RHB             | 32   | 3000 | 346.0       | 346.0      | 33.0        |

| TPA3131D2RHBT | VQFN         | RHB             | 32   | 250  | 210.0       | 185.0      | 35.0        |

| TPA3132D2RHBR | VQFN         | RHB             | 32   | 3000 | 346.0       | 346.0      | 33.0        |

| TPA3132D2RHBT | VQFN         | RHB             | 32   | 250  | 210.0       | 185.0      | 35.0        |

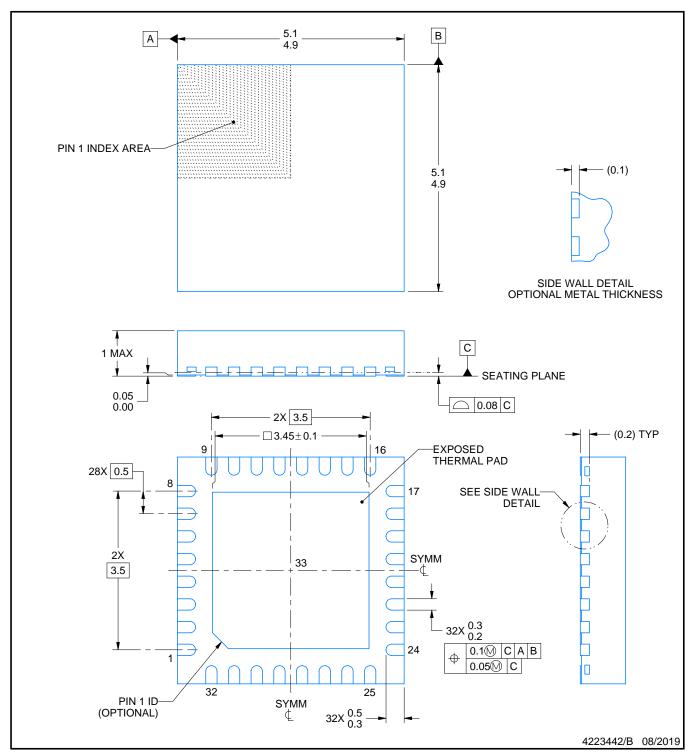

5 x 5, 0.5 mm pitch

PLASTIC QUAD FLATPACK - NO LEAD

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4224745/A

PLASTIC QUAD FLATPACK - NO LEAD

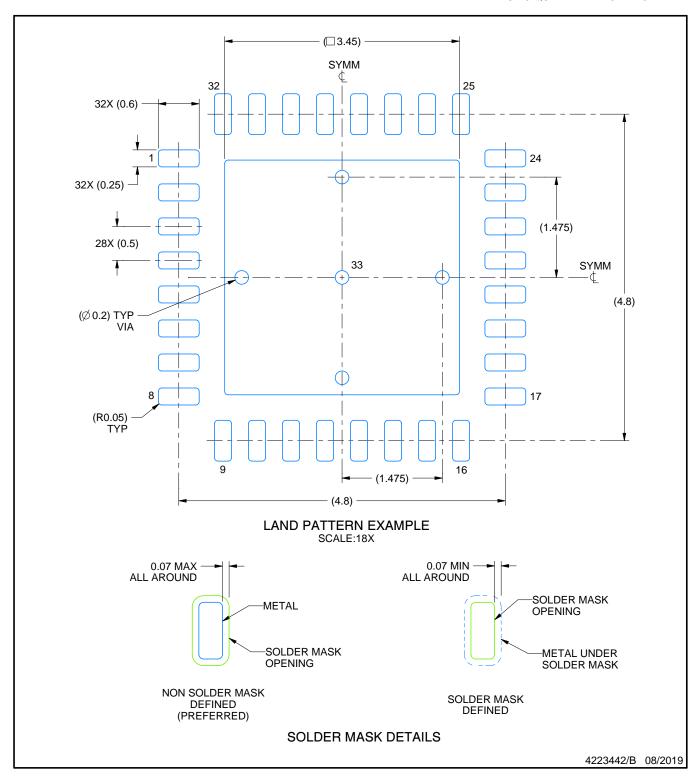

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

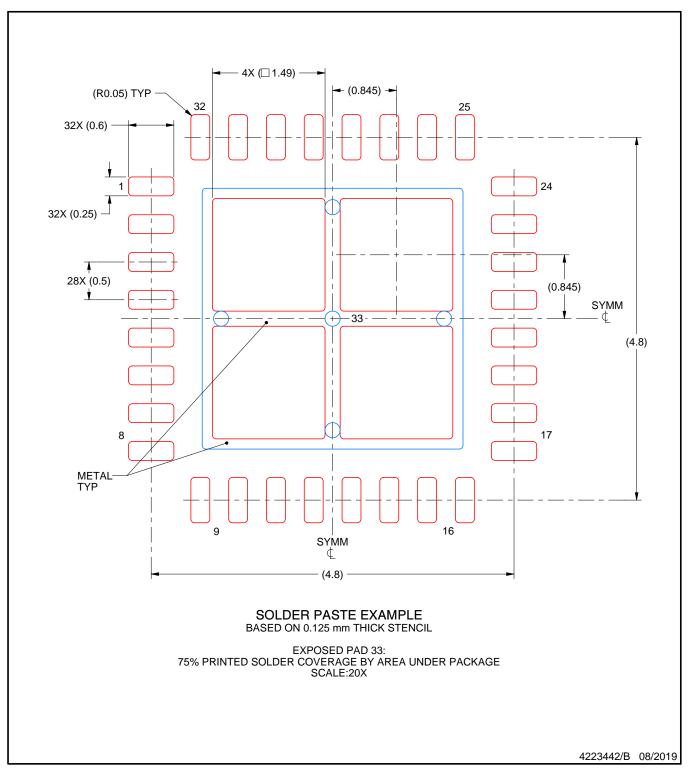

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

# 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024,德州仪器 (TI) 公司