THVD1500

ZHCSGF8A - JULY 2017-REVISED NOVEMBER 2018

# 具有 ±8kV IEC ESD 保护功能的 THVD1500 500kbps RS-485 收发器

## 1 特性

- 达到或超出 TIA/EIA-485A 标准和中国国家电网公司 (SGCC) 第 11 部分串行通信协议 RS-485 标准的要求

- 4.5V 至 5.5V 电源电压

- 半双工 RS-422/RS-485

- 总线 I/O 保护

- ±16kV HBM ESD

- ±8kV IEC 61000-4-2 接触放电

- ±10kV IEC 61000-4-2 空气间隙放电

- ±2kV IEC 61000-4-4 快速瞬变脉冲

- 扩展的工业温度范围: -40°C 至 125°C

- 用于噪声抑制的大接收器滞后

- 低功耗

- 低待机电源电流: 小于 1μA

- 运行静态电流: 小于 660μA

- 适用于热插拔功能的无干扰加电/断电

- 开路、短路和空闲总线失效防护

- 1/8 单位负载选项(多达 256 个总线节点)

- 低 EMI 500kbps

### 2 应用

- 电量计

- 逆变器

- HVAC 系统

- 视频监控系统

# 3 说明

THVD1500 是适用于工业应用的强大半双工 RS-485 收发器。这些总线引脚可耐受高级别的 IEC 接触放电 ESD 事件,从而无需使用其他系统级保护组件。

该器件由 5V 单电源供电。总线引脚具备宽共模电压范围和低输入泄漏,因此 THVD1500 适用于长电缆上的多点 应用。

THVD1500 采用可实现简易兼容性的工业标准 8 引脚 SOIC 封装。该器件的温度范围是 -40℃ 至 125℃。

## 器件信息<sup>(1)</sup>

| 器件编号     | 封装       | 封装尺寸 (标称值)      |

|----------|----------|-----------------|

| THVD1500 | SOIC (8) | 4.90mm × 3.91mm |

(1) 如需了解所有可用封装,请参阅产品说明书末尾的可订购产品 附录。

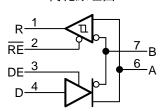

#### 简化原理图

13 机械、封装和可订购信息.......22

|   |                                      | 目录 |    |                                |    |

|---|--------------------------------------|----|----|--------------------------------|----|

| 1 | 特性                                   |    |    | 8.3 Feature Description        | 13 |

| 2 | 应用1                                  |    |    | 8.4 Device Functional Modes    | 13 |

| 3 | 说明                                   |    | 9  | Application and Implementation | 15 |

| 4 | 修订历史记录                               |    |    | 9.1 Application Information    | 15 |

| 5 | Pin Configuration and Functions 3    |    |    | 9.2 Typical Application        | 15 |

| 6 | Specifications                       |    | 10 | Power Supply Recommendations   | 19 |

| ٠ | 6.1 Absolute Maximum Ratings         |    | 11 | Layout                         | 20 |

|   | 6.2 ESD Ratings                      |    |    | 11.1 Layout Guidelines         | 20 |

|   | 6.3 Recommended Operating Conditions |    |    | 11.2 Layout Example            | 20 |

|   | 6.4 Thermal Information              |    | 12 | 器件和文档支持                        | 21 |

|   | 6.5 Power Dissipation                |    |    | 12.1 器件支持                      | 21 |

|   | 6.6 Electrical Characteristics 6     |    |    | 12.2 第三方产品免责声明                 | 21 |

|   | 6.7 Switching Characteristics        |    |    | 12.3 接收文档更新通知                  | 21 |

|   | 6.8 Typical Characteristics          |    |    | 12.4 社区资源                      | 21 |

| 7 | Parameter Measurement Information    |    |    | 12.5 商标                        | 21 |

| 8 | Detailed Description                 |    |    | 12.6 静电放电警告                    | 21 |

# 4 修订历史记录

| Cł | hanges from Original (July 2018) to Revision A                                                               | Page |

|----|--------------------------------------------------------------------------------------------------------------|------|

| •  | 将标题中的"300kbps RS-485"更改成了"500kbps RS-485"                                                                    | 1    |

| •  | 将特性中的"低 EMI 300kbps"更改成了"低 EMI 500kbps"                                                                      | 1    |

| •  | Changed Signaling rate From: 300 kbps To: 500 kbps in the Recommended Operating Condition                    | 5    |

| •  | Changed text From: "data transmission up to 300 kbps" To: "data transmission up to 500 kbps" in the Overview |      |

|    | section                                                                                                      | 13   |

# **5 Pin Configuration and Functions**

## **Pin Functions**

| PIN             |     | 1/0              | DECORIDATION                                         |  |  |

|-----------------|-----|------------------|------------------------------------------------------|--|--|

| NAME            | NO. | - I/O            | DESCRIPTION                                          |  |  |

| R               | 1   | Digital output   | Receive data output                                  |  |  |

| RE              | 2   | Digital input    | Receiver enable, active low (internal 2-MΩ pull-up)  |  |  |

| DE              | 3   | Digital input    | Driver enable, active high (internal 2-MΩ pull-down) |  |  |

| D               | 4   | Digital input    | Driver data input                                    |  |  |

| GND             | 5   | Ground           | Local device ground                                  |  |  |

| Α               | 6   | Bus input/output | Bus I/O port, A (complementary to B)                 |  |  |

| В               | 7   | Bus input/output | Bus I/O port, B (complementary to A)                 |  |  |

| V <sub>CC</sub> | 8   | Power            | 5-V supply                                           |  |  |

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                              |                                                                            | MIN  | MAX | UNIT |

|----------------------------------------------|----------------------------------------------------------------------------|------|-----|------|

| Supply voltage                               | V <sub>CC</sub>                                                            | -0.5 | 7   | V    |

| Bus voltage                                  | Range at any bus pin (A or B)                                              | -18  | 18  | V    |

|                                              | Range at any logic pin (D, DE, or RE)                                      | -0.3 | 5.7 |      |

| Input voltage                                | Transient pulse voltage range at any bus pin (A or B) through 100 $\Omega$ | -100 | 100 | V    |

| Receiver output current                      | Io                                                                         | -24  | 24  | mA   |

| Junction temperature                         |                                                                            |      | 170 | °C   |

| Absolute ambient temperature, T <sub>A</sub> |                                                                            |      | 125 | °C   |

| Storage temperature, T <sub>stg</sub>        |                                                                            |      | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                           |                                                                      |                                       | VALUE   | UNIT |  |

|--------------------|---------------------------|----------------------------------------------------------------------|---------------------------------------|---------|------|--|

|                    | Electrostatic discharge   | Contact Discharge, per IEC 61000-4-2                                 | Pins Bus terminals and GND            | ±8,000  |      |  |

|                    |                           | Air Gap Discharge, per IEC 61000-4-2                                 | Pins Bus terminals and GND            | ±10,000 |      |  |

| V <sub>(ESD)</sub> |                           | Human-body model (HBM), per                                          | Pins Bus terminals and GND            | ±16,000 | V    |  |

| (202)              |                           | Human-body model (HBM), per<br>ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | All pins except Bus terminals and GND | ±4,000  |      |  |

|                    |                           | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2)  |                                       | ±1,500  |      |  |

|                    |                           | Machine model (MM), per JEDEC JESD22-A115-A                          |                                       | ±400    |      |  |

| $V_{(EFT)}$        | Electrical fast transient | Per IEC 61000-4-4                                                    | Pins Bus terminals                    | ±2,000  | V    |  |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                                                                              | MIN | NOM MAX         | UNIT |

|-------------------|------------------------------------------------------------------------------|-----|-----------------|------|

| V <sub>CC</sub>   | Supply voltage                                                               | 4.5 | 5.5             | V    |

| VI                | Input voltage at any bus terminal <sup>(1)</sup>                             | -7  | 12              | V    |

| V <sub>IH</sub>   | High-level input voltage (Driver, driver enable, and receiver enable inputs) | 2   | V <sub>CC</sub> | V    |

| V <sub>IL</sub>   | Low-level input voltage (Driver, driver enable, and receiver enable inputs)  | 0   | 0.8             | V    |

| V <sub>ID</sub>   | Differential input voltage                                                   | -12 | 12              | V    |

| Io                | Output current, Driver                                                       | -60 | 60              | mA   |

| I <sub>OR</sub>   | Output current, Receiver                                                     | -8  | 8               | mA   |

| R <sub>L</sub>    | Differential load resistance                                                 | 54  |                 | Ω    |

| 1/t <sub>UI</sub> | Signaling rate                                                               |     | 500             | kbps |

| T <sub>A</sub>    | Operating ambient temperature                                                | -40 | 125             | °C   |

| TJ                | Junction temperature                                                         | -40 | 150             | °C   |

<sup>(1)</sup> The algebraic convention, in which the least positive (most negative) limit is designated as minimum is used in this data sheet.

### 6.4 Thermal Information

|                       |                                              | THVD1500 |      |

|-----------------------|----------------------------------------------|----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | D (SOIC) | UNIT |

|                       |                                              | 8 PINS   |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 130.1    | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 72.8     | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 73.6     | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 25.0     | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 72.9     | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | NA       | °C/W |

| $T_{J(TSD)}$          | Thermal shut-down temperature                | 170      | °C   |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Power Dissipation

over operating free-air temperature range (unless otherwise noted)

|        | PARAMETER                                                                        | TEST CONDITIONS                                                                |          | VALUE | UNIT |

|--------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------|-------|------|

| Driver | Driver and receiver enabled,                                                     | Unterminated $R_L = 300 \Omega$ , $C_L = 50 pF (driver)$                       | 300 kbps | 50    | mW   |

| PD     | $V_{CC}$ = 5.5 V, $T_{J}$ = 150 °C, 50% duty cycle square wave at signaling rate | RS-422 load R <sub>L</sub> = 100 $\Omega$ ,<br>C <sub>L</sub> = 50 pF (driver) | 300 kbps | 110   | mW   |

|        |                                                                                  | RS-485 load R <sub>L</sub> = 54 $\Omega$ ,<br>C <sub>L</sub> = 50 pF (driver)  | 300 kbps | 170   | mW   |

# 6.6 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                                 | PARAMETER                                    | TEST CONDITIONS                                                                                                                   |                                                                                                                 | MIN                | TYP                   | MAX                | UNIT |

|---------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|--------------------|------|

| Driver                          |                                              |                                                                                                                                   |                                                                                                                 |                    |                       |                    |      |

|                                 |                                              | $R_L$ = 60 Ω, -7 V ≤ $V_{test}$ ≤ 12 (See 🖁 8)                                                                                    |                                                                                                                 | 1.5                | 2                     |                    | V    |

| $ V_{OD} $                      | Driver differential output voltage magnitude | R <sub>L</sub> = 100 Ω (See 图 9)                                                                                                  |                                                                                                                 | 2                  | 2.5                   |                    | V    |

|                                 | ronago magimado                              | R <sub>L</sub> = 54 Ω (See 🖫 9)                                                                                                   |                                                                                                                 | 1.5                | 2                     |                    | V    |

| $\Delta  V_{OD} $               | Change in differential output voltage        | $R_L$ = 54 $\Omega$ or 100 $\Omega$ (See $\Xi$ 9)                                                                                 |                                                                                                                 | -50                |                       | 50                 | mV   |

| $V_{OC}$                        | Common-mode output voltage                   | $R_L$ = 54 $\Omega$ or 100 $\Omega$ (See $\Xi$ 9)                                                                                 |                                                                                                                 | 1                  | V <sub>CC</sub> /2    | 3                  | V    |

| $\Delta V_{OC(SS)}$             | Steady-state common-<br>mode output voltage  | $R_L$ = 54 $\Omega$ or 100 $\Omega$ (See $\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $                                                   |                                                                                                                 | -50                |                       | 50                 | mV   |

| $V_{OC(PP)}$                    | Peak-to-peak common-<br>mode output voltage  | $R_L$ = 54 $\Omega$ or 100 $\Omega$ (See $\Xi$ 9)                                                                                 |                                                                                                                 |                    | 450                   |                    | mV   |

| Ios                             | Short-circuit output current                 | DE = $V_{CC}$ , -7 V $\leq$ $V_{O}$ $\leq$ 12 V, or A pin shorted to B                                                            | oin                                                                                                             | -100               |                       | 100                | mA   |

| Receiver                        |                                              |                                                                                                                                   |                                                                                                                 | -                  |                       |                    |      |

| L                               | Bus input current                            | DE = 0 V,                                                                                                                         | V <sub>I</sub> = 12 V                                                                                           |                    | 75                    | 100                | μΑ   |

| I <sub>I1</sub>                 | bus input current                            | V <sub>CC</sub> = 0 V or 5.5 V                                                                                                    | V <sub>I</sub> = -7 V                                                                                           | -97                | -70                   |                    | μΑ   |

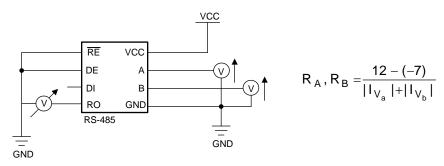

| R <sub>A</sub> , R <sub>B</sub> | Bus input impedance                          | $V_A = -7 \text{ V}, V_B = 12 \text{ V} \text{ and } V_A = 12 \text{ V}, V_B = -7 \text{ V} \text{ (See } \boxed{\$} \text{ 14)}$ | $V_A = -7 \text{ V}, V_B = 12 \text{ V} \text{ and } V_A = 12 \text{ V}, V_B = -7 \text{ V} \text{ (See § 14)}$ |                    |                       |                    | kΩ   |

| V <sub>TH+</sub>                | Positive-going input threshold voltage       |                                                                                                                                   |                                                                                                                 | See <sup>(1)</sup> | -70                   | -50                | mV   |

| $V_{TH-}$                       | Negative-going input threshold voltage       |                                                                                                                                   |                                                                                                                 | -200               | -150                  | See <sup>(1)</sup> | mV   |

| $V_{HYS}$                       | Input hysteresis                             |                                                                                                                                   |                                                                                                                 | 20                 | 50                    |                    | mV   |

| $V_{OH}$                        | Output high voltage                          | I <sub>OH</sub> = -8 mA                                                                                                           |                                                                                                                 | 4                  | V <sub>CC</sub> - 0.3 |                    | ٧    |

| V <sub>OL</sub>                 | Output low voltage                           | I <sub>OL</sub> = 8 mA                                                                                                            |                                                                                                                 |                    | 0.2                   | 0.4                | V    |

| I <sub>OZ</sub>                 | Output high-impedance current                | $V_{O} = 0 \text{ V or } V_{CC}, \overline{RE} = V_{CC}$                                                                          |                                                                                                                 | -1                 |                       | 1                  | μΑ   |

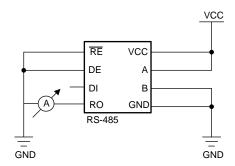

| I <sub>OSR</sub>                | Output short-circuit current                 | RE = 0, DE = 0, See 图 13                                                                                                          |                                                                                                                 |                    |                       | 95                 | mA   |

| Logic                           |                                              |                                                                                                                                   |                                                                                                                 |                    |                       |                    |      |

| I <sub>IN</sub>                 | Input current<br>(D, DE, RE)                 | 4.5 V ≤ V <sub>CC</sub> ≤ 5.5 V                                                                                                   |                                                                                                                 | <b>-</b> 5         | 0                     | 5                  | μΑ   |

| Supply                          |                                              |                                                                                                                                   |                                                                                                                 |                    |                       | '                  |      |

|                                 |                                              | Driver and receiver enabled                                                                                                       | $\overline{RE}$ = 0 V, DE = V <sub>CC</sub> , No load                                                           |                    | 440                   | 660                | μΑ   |

|                                 |                                              | Driver enabled, receiver disabled                                                                                                 | $\overline{RE} = V_{CC}$ , DE = $V_{CC}$ ,<br>No load                                                           |                    | 295                   | 420                | μΑ   |

| I <sub>CC</sub>                 | Supply current (quiescent)                   | Driver disabled, receiver enabled                                                                                                 | RE = 0 V, DE = 0 V, No load                                                                                     |                    | 275                   | 400                | μA   |

|                                 |                                              | Driver and receiver disabled                                                                                                      | RE = V <sub>CC</sub> , DE = 0 V, D<br>= open, No load                                                           |                    | 0.1                   | 1                  | μΑ   |

<sup>(1)</sup> Under any specific conditions,  $V_{\text{IT+}}$  is assured to be at least  $V_{\text{HYS}}$  higher than VIT-.

# 6.7 Switching Characteristics

over recommended operating conditions

|                                                                       | PARAMETER                                        | TEST CO                        | NDITIONS          | MIN | TYP | MAX | UNIT |

|-----------------------------------------------------------------------|--------------------------------------------------|--------------------------------|-------------------|-----|-----|-----|------|

| Driver                                                                |                                                  |                                |                   |     |     |     |      |

| t <sub>r</sub> , t <sub>f</sub>                                       | Differential output rise/fall time               |                                |                   | 180 | 250 | 450 | ns   |

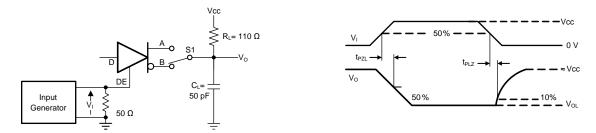

| t <sub>PHL</sub> , t <sub>PLH</sub>                                   | Propagation delay                                | $R_L = 54 \Omega, C_L = 50 pF$ | See 图 10          |     | 250 | 350 | ns   |

| t <sub>SK(P)</sub>                                                    | Pulse skew,  t <sub>PHL</sub> - t <sub>PLH</sub> |                                |                   |     | 25  | 40  | ns   |

| t <sub>PHZ</sub> , t <sub>PLZ</sub>                                   | Disable time                                     |                                |                   |     | 70  | 160 | ns   |

|                                                                       | Enable time                                      | RE = 0 V                       | See 图 11 and 图 12 |     | 220 | 400 | ns   |

| t <sub>PZH</sub> , t <sub>PZL</sub>                                   | Enable time                                      | $\overline{RE} = V_{CC}$       |                   |     | 1.5 | 3   | μs   |

| Receiver                                                              |                                                  |                                | ·                 |     |     |     |      |

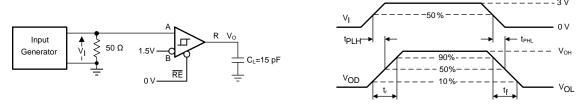

| t <sub>r</sub> , t <sub>f</sub>                                       | Differential output rise/fall time               |                                |                   |     | 15  | 25  | ns   |

| t <sub>PHL</sub> , t <sub>PLH</sub>                                   | Propagation delay                                | C <sub>L</sub> = 15 pF         | See 图 15          |     | 70  | 100 | ns   |

| t <sub>SK(P)</sub>                                                    | Pulse skew,  t <sub>PHL</sub> - t <sub>PLH</sub> |                                |                   |     | 3   | 7   | ns   |

| t <sub>PHZ</sub> , t <sub>PLZ</sub>                                   | Disable time                                     |                                |                   |     | 15  | 30  | ns   |

| t <sub>PZH(1)</sub> ,                                                 |                                                  | DE = V <sub>CC</sub>           | See 图 16          |     | 100 | 175 | ns   |

| t <sub>PZL(1)</sub> ,<br>t <sub>PZH(2)</sub> ,<br>t <sub>PZL(2)</sub> | Enable time                                      | DE = 0 V                       | See 图 17          |     | 1   | 4   | μS   |

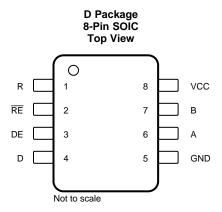

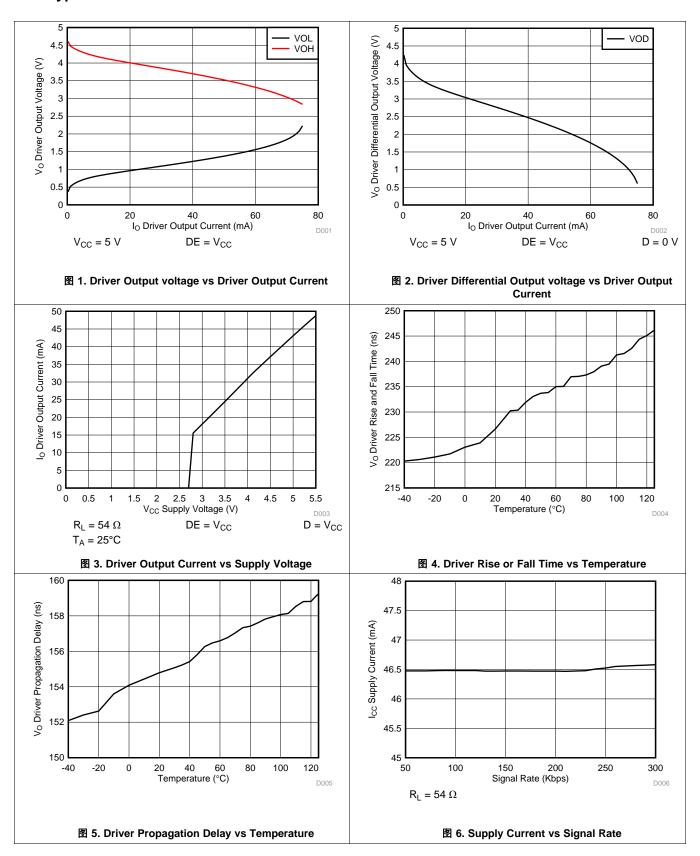

## 6.8 Typical Characteristics

# Typical Characteristics (接下页)

$\Delta V_{OC(SS)}$

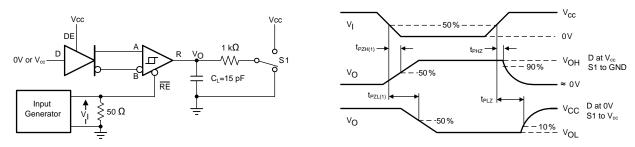

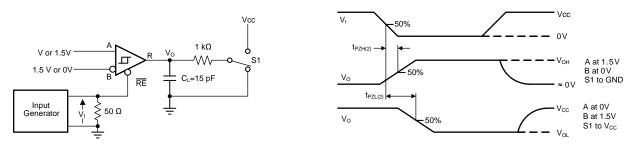

### 7 Parameter Measurement Information

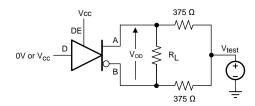

### 图 8. Measurement of Driver Differential Output Voltage With Common-Mode Load

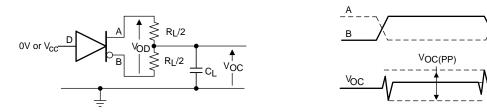

图 9. Measurement of Driver Differential and Common-Mode Output With RS-485 Load

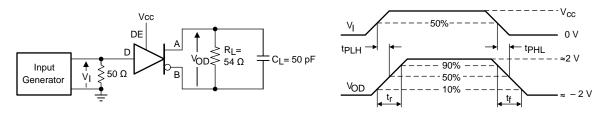

图 10. Measurement of Driver Differential Output Rise and Fall Times and Propagation Delays

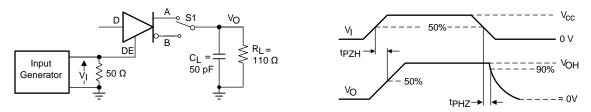

### 图 11. Measurement of Driver Enable and Disable Times With Active High Output and Pull-Down Load

图 12. Measurement of Driver Enable and Disable Times With Active Low Output and Pull-up Load

# Parameter Measurement Information (接下页)

图 13. Measurement of Receiver Output Short Circuit Current

图 14. Measurement of Bus Impedance

图 15. Measurement of Receiver Output Rise and Fall Times and Propagation Delays

图 16. Measurement of Receiver Enable/Disable Times With Driver Enabled

# Parameter Measurement Information (接下页)

图 17. Measurement of Receiver Enable Times With Driver Disabled

# 8 Detailed Description

#### 8.1 Overview

The THVD1500 is a low-power, half-duplex RS-485 transceiver suitable for data transmission up to 500 kbps.

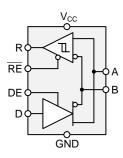

#### 8.2 Functional Block Diagrams

# 8.3 Feature Description

Internal ESD protection circuits protect the transceiver against Electrostatic Discharges (ESD) according to IEC 61000-4-2 of up to ±8 kV (Contact Discharge), ±10 kV (Air Gap Discharge) and against electrical fast transients (EFT) according to IEC 61000-4-4 of up to ±2 kV.

The THVD1500 provides internal biasing of the receiver input thresholds in combination with large input-threshold hysteresis. With a positive input threshold of  $V_{IT+} = -50$  mV and an input hysteresis of  $V_{HYS} = 50$  mV, the receiver output remains logic high under a bus-idle or bus-short conditions without the need for external failsafe biasing resistors. Device operation is specified over a wide temperature range from -40°C to 125°C.

#### 8.4 Device Functional Modes

When the driver enable pin, DE, is logic high, the differential outputs A and B follow the logic states at data input D. A logic high at D causes A to turn high and B to turn low. In this case, the differential output voltage defined as  $V_{OD} = V_A - V_B$  is positive. When D is low, the output states reverse, B turns high, A becomes low, and  $V_{OD}$  is negative.

When DE is low, both outputs turn high-impedance. In this condition the logic state at D is irrelevant. The DE pin has an internal pull-down resistor to ground, thus when left open the driver is disabled (high-impedance) by default. The D pin has an internal pull-up resistor to  $V_{CC}$ , thus, when left open while the driver is enabled, output A turns high and B turns low.

| INPUT | ENABLE | OUTPUTS |   |                                    |

|-------|--------|---------|---|------------------------------------|

| D     | DE     | Α       | В | FUNCTION                           |

| Н     | Н      | Н       | L | Actively drive bus high            |

| L     | Н      | L       | Н | Actively drive bus low             |

| Х     | L      | Z       | Z | Driver disabled                    |

| Х     | OPEN   | Z       | Z | Driver disabled by default         |

| OPEN  | Н      | Н       | L | Actively drive bus high by default |

表 1. Driver Function Table

When the receiver enable pin,  $\overline{RE}$ , is logic low, the receiver is enabled. When the differential input voltage defined as  $V_{ID} = V_A - V_B$  is positive and higher than the positive input threshold,  $V_{IT_-}$ , the receiver output, R, turns high. When  $V_{ID}$  is negative and lower than the negative input threshold,  $V_{IT_-}$ , the receiver output, R, turns low. If  $V_{ID}$  is between  $V_{IT_+}$  and  $V_{IT_-}$  the output is indeterminate.

When  $\overline{RE}$  is logic high or left open, the receiver output is high-impedance and the magnitude and polarity of  $V_{ID}$  are irrelevant. Internal biasing of the receiver inputs causes the output to go failsafe-high when the transceiver is disconnected from the bus (open-circuit), the bus lines are shorted (short-circuit), or the bus is not actively driven (idle bus).

# 表 2. Receiver Function Table

| DIFFERENTIAL INPUT                  | ENABLE | OUTPUT | FUNCTION                     |

|-------------------------------------|--------|--------|------------------------------|

| $V_{ID} = V_A - V_B$                | RE     | R      | FUNCTION                     |

| $V_{IT+} < V_{ID}$                  | L      | Н      | Receive valid bus high       |

| $V_{IT-} < V_{ID} < V_{IT+}$        | L      | ?      | Indeterminate bus state      |

| V <sub>ID</sub> < V <sub>IT</sub> - | L      | L      | Receive valid bus low        |

| X                                   | Н      | Z      | Receiver disabled            |

| X                                   | OPEN   | Z      | Receiver disabled by default |

| Open-circuit bus                    | L      | Н      | Fail-safe high output        |

| Short-circuit bus                   | L      | Н      | Fail-safe high output        |

| Idle (terminated) bus               | L      | Н      | Fail-safe high output        |

# 9 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 9.1 Application Information

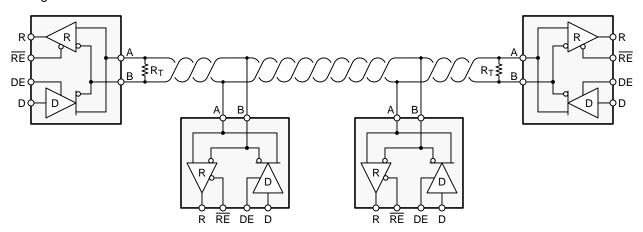

The THVD1500 is a half-duplex RS-485 transceiver commonly used for asynchronous data transmissions. The driver and receiver enable pins allow for the configuration of different operating modes.

## 9.2 Typical Application

An RS-485 bus consists of multiple transceivers connecting in parallel to a bus cable. To eliminate line reflections, each cable end is terminated with a termination resistor,  $R_T$ , whose value matches the characteristic impedance,  $Z_0$ , of the cable. This method, known as parallel termination, allows for higher data rates over longer cable length.

图 18. Typical RS-485 Network With Half-Duplex Transceivers

#### 9.2.1 Design Requirements

RS-485 is a robust electrical standard suitable for long-distance networking that may be used in a wide range of applications with varying requirements, such as distance, data rate, and number of nodes.

#### 9.2.1.1 Data Rate and Bus Length

There is an inverse relationship between data rate and cable length, which means the higher the data rate, the shorter the cable length; and conversely, the lower the data rate, the longer the cable length. While most RS-485 systems use data rates between 10 kbps and 100 kbps, some applications require data rates up to 300 kbps at distances of 4000 feet and longer. Longer distances are possible by allowing for small signal jitter of up to 5 or 10%.

(1)

# Typical Application (接下页)

#### 9.2.1.2 Stub Length

When connecting a node to the bus, the distance between the transceiver inputs and the cable trunk, known as the stub, should be as short as possible. Stubs present a non-terminated piece of bus line which can introduce reflections as the length of the stub increases. As a general guideline, the electrical length, or round-trip delay, of a stub should be less than one-tenth of the rise time of the driver, thus giving a maximum physical stub length as shown in 公式 1.

$L_{(STUB)} \le 0.1 \times t_r \times v \times c$

#### where

- t<sub>r</sub> is the 10/90 rise time of the driver

- c is the speed of light  $(3 \times 10^8 \text{ m/s})$

- v is the signal velocity of the cable or trace as a factor of c

#### 9.2.1.3 Bus Loading

The RS-485 standard specifies that a compliant driver must be able to driver 32 unit loads (UL), where 1 unit load represents a load impedance of approximately 12 k $\Omega$ . Because the THVD1500 consists of 1/8 UL transceivers, connecting up to 256 receivers to the bus is possible.

#### 9.2.1.4 Receiver Failsafe

The differential receivers of the THVD1500 are fails afe to invalid bus states caused by the following:

- Open bus conditions, such as a disconnected connector

- Shorted bus conditions, such as cable damage shorting the twisted-pair together

- Idle bus conditions that occur when no driver on the bus is actively driving

In any of these cases, the differential receiver will output a failsafe logic high state so that the output of the receiver is not indeterminate.

Receiver failsafe is accomplished by offsetting the receiver thresholds such that the *input indeterminate* range does not include zero volts differential. In order to comply with the RS-422 and RS-485 standards, the receiver output must output a high when the differential input  $V_{ID}$  is more positive than 200 mV, and must output a low when  $V_{ID}$  is more negative than -200 mV. The receiver parameters which determine the failsafe performance are  $V_{IT+}$ ,  $V_{IT-}$ , and  $V_{HYS}$  (the separation between  $V_{IT+}$  and  $V_{IT-}$ ). As shown in the *Electrical Characteristics* table, differential signals more negative than -200 mV will always cause a low receiver output, and differential signals more positive than 200 mV will always cause a high receiver output.

When the differential input signal is close to zero, it is still above the  $V_{IT_+}$  threshold, and the receiver output will be high. Only when the differential input is more than  $V_{HYS}$  below  $V_{IT_+}$  will the receiver output transition to a low state. Therefore, the noise immunity of the receiver inputs during a bus fault conditions includes the receiver hysteresis value,  $V_{HYS}$ , as well as the value of  $V_{IT_+}$ .

# Typical Application (接下页)

#### 9.2.1.5 Transient Protection

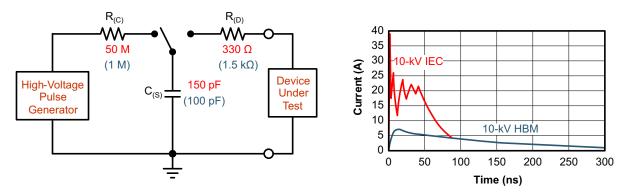

The bus pins of the THVD1500 transceiver family include on-chip ESD protection against  $\pm 16$ -kV HBM and  $\pm 8$ -kV IEC 61000-4-2 contact discharge. The International Electrotechnical Commission (IEC) ESD test is far more severe than the HBM ESD test. The 50% higher charge capacitance,  $C_{(S)}$ , and 78% lower discharge resistance,  $R_{(D)}$ , of the IEC model produce significantly higher discharge currents than the HBM model.

图 19. HBM and IEC ESD Models and Currents in Comparison (HBM Values in Parenthesis)

The on-chip implementation of IEC ESD protection significantly increases the robustness of equipment. Common discharge events occur because of human contact with connectors and cables. Designers may choose to implement protection against longer duration transients, typically referred to as surge transients.

EFTs are generally caused by relay-contact bounce or the interruption of inductive loads. Surge transients often result from lightning strikes (direct strike or an indirect strike which induce voltages and currents), or the switching of power systems, including load changes and short circuit switching. These transients are often encountered in industrial environments, such as factory automation and power-grid systems.

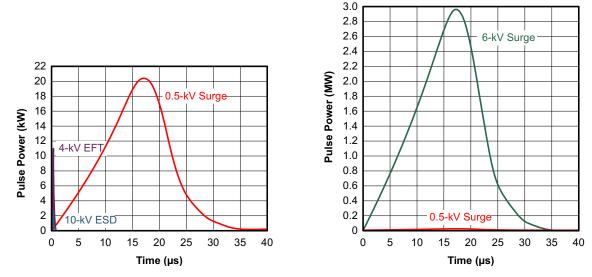

₹ 20 compares the pulse-power of the EFT and surge transients with the power caused by an IEC ESD transient. The left hand diagram shows the relative pulse-power for a 0.5-kV surge transient and 4-kV EFT transient, both of which dwarf the 10-kV ESD transient visible in the lower-left corner. 500-V surge transients are representative of events that may occur in factory environments in industrial and process automations.

The right hand diagram shows the pulse-power of a 6-kV surge transient, relative to the same 0.5-kV surge transient. 6-kV surge transients are most likely to occur in power generation and power-grid systems.

图 20. Power Comparison of ESD, EFT, and Surge Transients

# Typical Application (接下页)

In the event of surge transients, high-energy content is characterized by long pulse duration and slow decaying pulse power. The electrical energy of a transient that is dumped into the internal protection cells of a transceiver is converted into thermal energy, which heats and destroys the protection cells, thus destroying the transceiver.

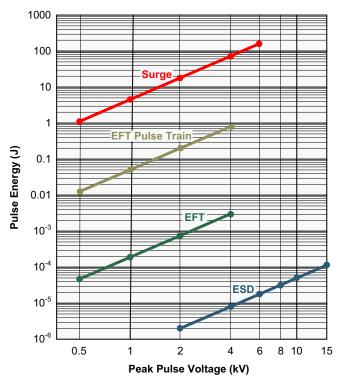

21 shows the large differences in transient energies for single ESD, EFT, surge transients, and an EFT pulse train that is commonly applied during compliance testing.

图 21. Comparison of Transient Energies

# Typical Application (接下页)

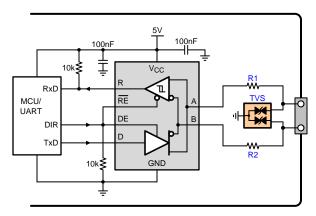

### 9.2.2 Detailed Design Procedure

In order to protect bus nodes against high-energy transients, the implementation of external transient protection devices is necessary. 图 22 suggest a protection circuit against 1 kV surge (IEC 61000-4-5) transients. 表 3 shows the associated Bill of Materials.

图 22. Transient Protection Against ESD, EFT, and Surge Transients for Half-Duplex Devices

表 3. Bill of Materials

| DEVICE | FUNCTION                                       | ORDER NUMBER          | MANUFACTURER |  |

|--------|------------------------------------------------|-----------------------|--------------|--|

| XCVR   | RS-485 transceiver                             | THVD1500              | TI           |  |

| R1     | 40.0 mulas musef thield files manietan         | CDCM/0000040D INFALID | Vielen       |  |

| R2     | 10- $\Omega$ , pulse-proof thick-film resistor | CRCW0603010RJNEAHP    | Vishay       |  |

| TVS    | Bidirectional 400-W transient suppressor       | CDSOT23-SM712         | Bourns       |  |

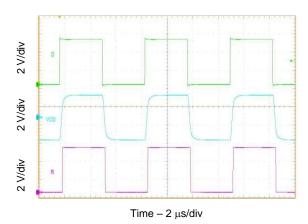

### 9.2.3 Application Curves

Data Rate = 300 Kbps

图 23. TBD

## 10 Power Supply Recommendations

To ensure reliable operation at all data rates and supply voltages, each supply should be decoupled with a 100 nF ceramic capacitor located as close to the supply pins as possible. This helps to reduce supply voltage ripple present on the outputs of switched-mode power supplies and also helps to compensate for the resistance and inductance of the PCB power planes.

# 11 Layout

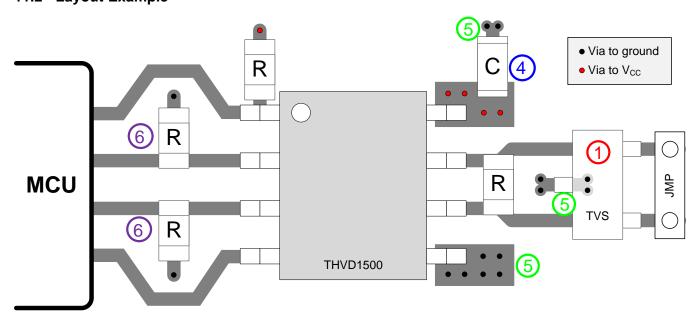

## 11.1 Layout Guidelines

Robust and reliable bus node design often requires the use of external transient protection devices in order to protect against surge transients that may occur in industrial environments. Since these transients have a wide frequency bandwidth (from approximately 3 MHz to 300 MHz), high-frequency layout techniques should be applied during PCB design.

- 1. Place the protection circuitry close to the bus connector to prevent noise transients from propagating across the board.

- 2. Use V<sub>CC</sub> and ground planes to provide low inductance. Note that high-frequency currents tend to follow the path of least impedance and not the path of least resistance.

- 3. Design the protection components into the direction of the signal path. Do not force the transient currents to divert from the signal path to reach the protection device.

- Apply 100-nF to 220-nF bypass capacitors as close as possible to the V<sub>CC</sub> pins of transceiver, UART and/or controller ICs on the board.

- 5. Use at least two vias for  $V_{CC}$  and ground connections of bypass capacitors and protection devices to minimize effective via inductance.

- Use 1-kΩ to 10-kΩ pullup and pulldown resistors for enable lines to limit noise currents in theses lines during transient events.

- 7. Insert pulse-proof resistors into the A and B bus lines if the TVS clamping voltage is higher than the specified maximum voltage of the transceiver bus pins. These resistors limit the residual clamping current into the transceiver and prevent it from latching up.

- 8. While pure TVS protection is sufficient for surge transients up to 1 kV, higher transients require metal-oxide varistors (MOVs) which reduce the transients to a few hundred volts of clamping voltage, and transient blocking units (TBUs) that limit transient current to less than 1 mA.

## 11.2 Layout Example

图 24. Layout Example

### 12 器件和文档支持

### 12.1 器件支持

#### 12.2 第三方产品免责声明

TI 发布的与第三方产品或服务有关的信息,不能构成与此类产品或服务或保修的适用性有关的认可,不能构成此类产品或服务单独或与任何 TI 产品或服务一起的表示或认可。

## 12.3 接收文档更新通知

要接收文档更新通知,请导航至 Tl.com.cn 上的器件产品文件夹。单击右上角的通知我进行注册,即可每周接收产品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。.

### 12.4 社区资源

下列链接提供到 TI 社区资源的连接。链接的内容由各个分销商"按照原样"提供。这些内容并不构成 TI 技术规范,并且不一定反映 TI 的观点;请参阅 TI 的 《使用条款》。

TI E2E™ 在线社区 TI 的工程师对工程师 (E2E) 社区。此社区的创建目的在于促进工程师之间的协作。在 e2e.ti.com 中,您可以咨询问题、分享知识、拓展思路并与同行工程师一道帮助解决问题。

设计支持 71 参考设计支持 可帮助您快速查找有帮助的 E2E 论坛、设计支持工具以及技术支持的联系信息。

#### 12.5 商标

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

### 12.6 静电放电警告

这些装置包含有限的内置 ESD 保护。 存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

### 12.7 术语表

SLYZ022 — TI 术语表。

这份术语表列出并解释术语、缩写和定义。

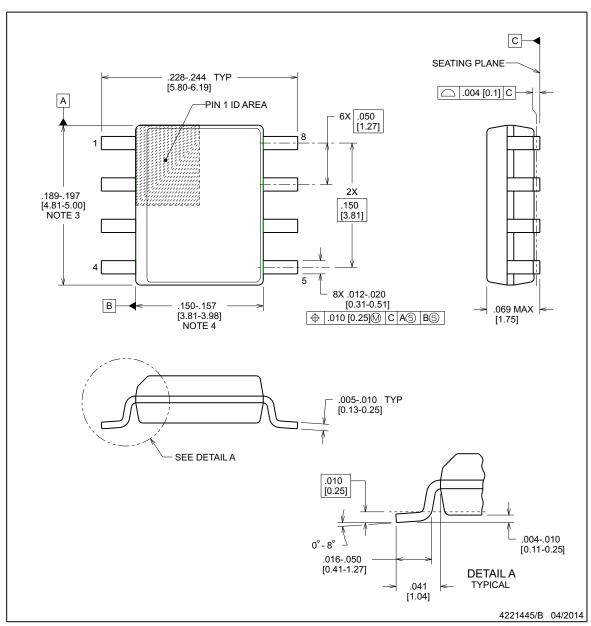

# 13 机械、封装和可订购信息

以下页面包含机械、封装和可订购信息。这些信息是指定器件的最新可用数据。数据如有变更,恕不另行通知,且 不会对此文档进行修订。如需获取此产品说明书的浏览器版本,请查阅左侧的导航栏。

**D0008B**

## PACKAGE OUTLINE

# SOIC - 1.75 mm max height

SOIC

#### NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15], per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

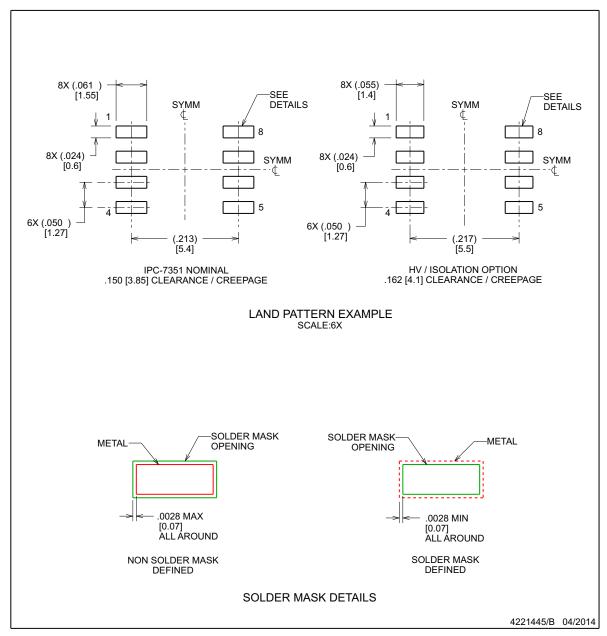

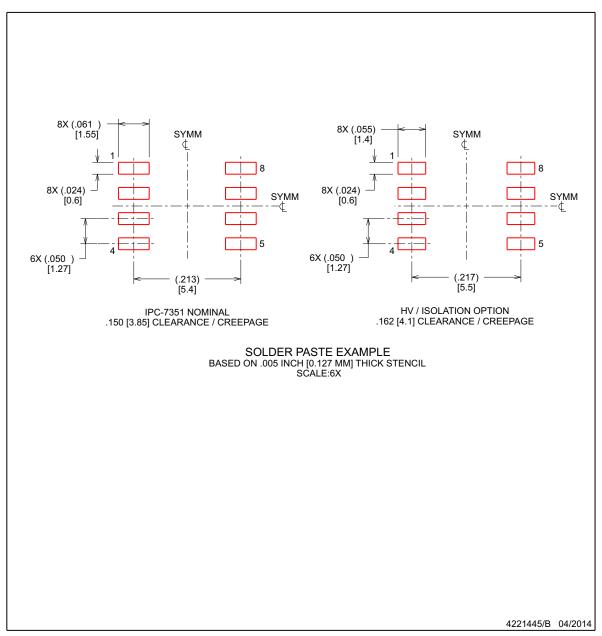

# **EXAMPLE BOARD LAYOUT**

# **D0008B**

SOIC - 1.75 mm max height

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

25

# **EXAMPLE STENCIL DESIGN**

# **D0008B**

# SOIC - 1.75 mm max height

SOIC

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

www.ti.com 10-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|----------------|-----------------------|------|-------------------------------|----------------------------|--------------|--------------|

|                       | (1)    | (2)           |                |                       | (3)  | (4)                           | (5)                        |              | (6)          |

| THVD1500D             | Active | Production    | SOIC (D)   8   | 75   TUBE             | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | VD1500       |

| THVD1500D.B           | Active | Production    | SOIC (D)   8   | 75   TUBE             | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | VD1500       |

| THVD1500DR            | Active | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | VD1500       |

| THVD1500DR.A          | Active | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | VD1500       |

| THVD1500DR.B          | Active | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | VD1500       |

| THVD1500DRG4          | Active | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | VD1500       |

| THVD1500DRG4.A        | Active | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | VD1500       |

| THVD1500DRG4.B        | Active | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | VD1500       |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 10-Nov-2025

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-Aug-2025

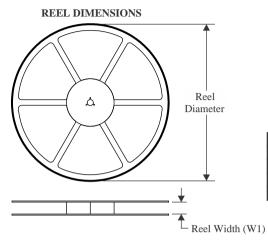

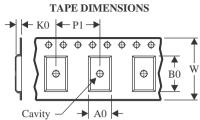

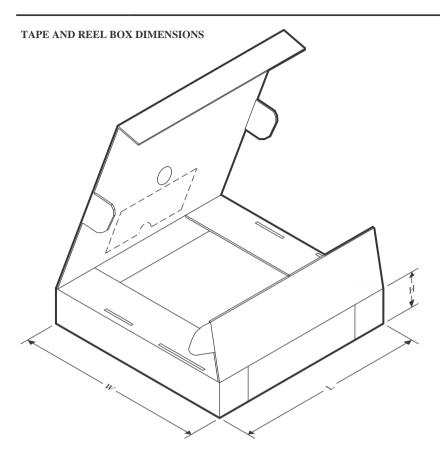

## **TAPE AND REEL INFORMATION**

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

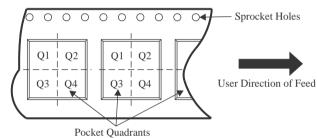

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       |      | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| THVD1500DR   | SOIC | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| THVD1500DRG4 | SOIC | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

www.ti.com 23-Aug-2025

### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| THVD1500DR   | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| THVD1500DRG4 | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-Aug-2025

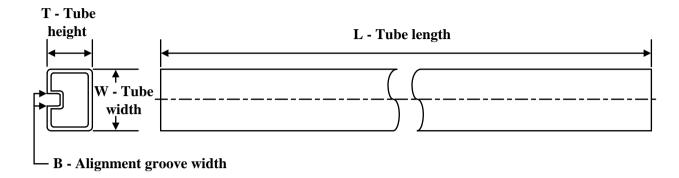

## **TUBE**

### \*All dimensions are nominal

| Device      | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|-------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| THVD1500D   | D            | SOIC         | 8    | 75  | 507    | 7.85   | 3750   | 2.24   |

| THVD1500D.B | D            | SOIC         | 8    | 75  | 507    | 7.85   | 3750   | 2.24   |

## 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月