TFP401A-Q1

ZHCSAH8B - NOVEMBER 2012 - REVISED MARCH 2022

# TFP401A-Q1 TI Panelbus™汽车类数字接收器

# 1 特性

- 符合汽车应用要求

- 具有符合 AEC-Q100 标准的下列特性:

- 器件温度等级 3:-40°C 至 85°C 环境工作温度 范围

- 器件 HBM ESD 分类等级 H2

- 器件 CDM ESD 分类等级 C3B

- 支持高达 165 MHz 的像素速率 (包括 60Hz 时的 1080p 和 WUXGA)

- 符合数字可视化接口 (DVI) 技术规范 <sup>1</sup>

- 真彩色,24位/像素,1670万种颜色(每时钟驱动 1或2个像素)

- 通过激光修整内部端接电阻器,实现出色的固定阻 抗兀配

- 高达 1 个像素时钟周期的偏移容限

- 4 倍过采样

- 降低功耗: 1.8V 内核运行, 3.3V I/O 和电源<sup>2</sup>

- 使用错时像素输出来减少接地反弹

- 使用 TI PowerPAD™ 封装实现低噪声和良好的功率 耗散

- 采用 TI 0.18µm EPIC-5™ CMOS 工艺的先进技术

- TFP401A-Q1 具有 HSYNC 抖动抗扰能力<sup>3</sup>

#### 2 应用

- 高清电视

- 高清 PC 显示器

- 数字视频

- 高清投影仪

- DVI/HDMI 接收器 4

### 3 说明

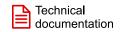

德州仪器 (TI) 的 TFP401A-Q1 器件是一款 TI Panelbus™ 平板显示产品,是全系列兼容端到端 DVI 1.0 解决方案的一部分。主要针对的是台式机 LCD 显 示器和数字投影仪,TFP401A-Q1器件可应用于任何 需要高速数字接口的设计中。

TFP401A-Q1 器件支持高达 1080p 的显示分辨率和 24 位真彩色像素格式的 WUXGA。它还具有设计灵活 性,可在每个时钟内驱动 1 个或 2 个像素,支持 TFT 或 DSTN 面板并提供用时间触发的像素输出来减少接 地反弹的选项。

PowerPAD 先进的封装技术可获得业界最佳的功率耗 散、封装尺寸和超低接地电感。

TFP401A-Q1 将创新的 Panelbus 电路与 TI 先进的 0.18 µm EPIC-5™ CMOS 工艺技术以及 TI 的 PowerPAD 封装技术组合在一起,用于实现可靠的低 功耗、低噪声、高速数字接口解决方案。

#### 器件信息(1)

| 器件型号       | 封装         | 封装尺寸(标称值)         |

|------------|------------|-------------------|

| TFP401A-Q1 | PQFP (100) | 14.00mm × 14.00mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

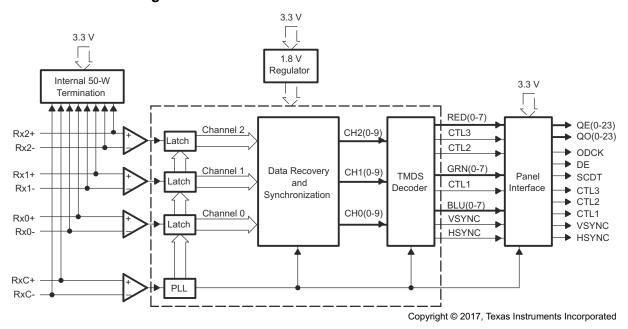

TFP401A-Q1 框图

<sup>1</sup> TFP401A-Q1 器件包含可以从 DVI 发送器创建稳定 HSYNC 的附加电路,这些发送器会在已发送的 HSYNC 信号上引入有害抖动。

<sup>&</sup>lt;sup>2</sup> TFP401A-Q1 器件具有一个内部稳压器,可通过外部 3.3V 电源提供 1.8V 内核电源。

<sup>3</sup> 数字可视化接口规范 (DVI) 是数字显示工作组 (DDWG) 为了与数字显示屏建立高速数字连接而开发的一个行业标准。TFP401A-Q1 与 DVI 技术规范修订版本 1.0 兼容。

<sup>&</sup>lt;sup>4</sup> 仅 HDMI 视频

# **Table of Contents**

| 1 特性 1                                        | 7.1 Overview                            | 12               |

|-----------------------------------------------|-----------------------------------------|------------------|

| <br>2 应用 1                                    | 7.2 Functional Block Diagram            | 12               |

| - <i>二</i> , 7<br>3 说明                        | 7.3 Feature Description                 | 12               |

| 4 Revision History2                           | 7.4 Device Functional Modes             | 15               |

| 5 Pin Configuration and Functions             | 8 Application and Implementation        | 17               |

| 6 Specifications                              | 8.1 Application Information             | 17               |

| 6.1 Absolute Maximum Ratings                  | 8.2 Power Supply Recommendations        | <mark>2</mark> 1 |

| 6.2 ESD Ratings                               | 8.3 Layout                              | <mark>2</mark> 1 |

| 6.3 Recommended Operating Conditions6         | 9 Device and Documentation Support      | <mark>2</mark> 7 |

| 6.4 Thermal Information                       | 9.1 接收文档更新通知                            | 27               |

| 6.5 DC Digital I/O Electrical Characteristics | 9.2 支持资源                                | <mark>2</mark> 7 |

| 6.6 DC Electrical Characteristics             |                                         |                  |

| 6.7 AC Electrical Characteristics             |                                         |                  |

| 6.8 Timing Requirements8                      | 9.5 术语表                                 |                  |

| 6.9 Switching Characteristics10               | 10 Mechanical, Packaging, and Orderable |                  |

| 6.10 Typical Characteristics11                | Information                             | 27               |

| 7 Detailed Description12                      |                                         |                  |

**4 Revision History** 注:以前版本的页码可能与当前版本的页码不同

| C | hanges from Revision A (January 2017) to Revision B (March 2022)                                                                       | Page        |

|---|----------------------------------------------------------------------------------------------------------------------------------------|-------------|

| • | 更新了整个文档中的表格、图和交叉参考的编号格式                                                                                                                | 1           |

| • | Added the Thermal Package information to the Pin Functions table                                                                       | 3           |

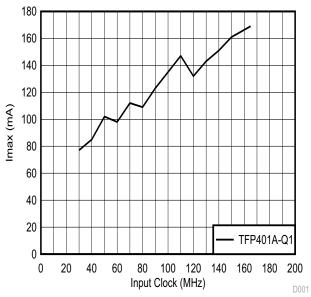

| • | Added TFP401A-Q1 to the Imax vs Input Frequency figure                                                                                 |             |

| • | Added sentence to end of first paragraph that recommends soldering package thermal pad to PCB is minimize stress on peripheral pins    | n order to  |

| C | hanges from Revision * (November 2012) to Revision A (January 2017)                                                                    | Page        |

| • | 添加了 <i>器件信息</i> 表、 <i>引脚配置和功能</i> 部分、 <i>ESD 等级</i> 表、 <i>应用和实施</i> 部分、 <i>电源相关建议</i> 部分、 <i>和                                    </i> | <i>有局</i> 部 |

Submit Document Feedback

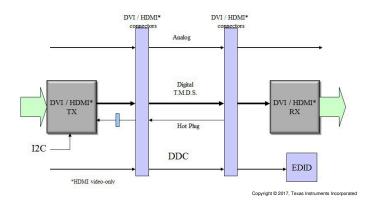

# **5 Pin Configuration and Functions**

图 5-1. PZP Package, 100-Pin PQFP PowerPAD Package (Top View)

表 5-1. Pin Functions

|          | PIN                   | TYPE(1)  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                               |  |

|----------|-----------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME     | NO.                   | ITPE     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                               |  |

| AGND     | 79, 83, 87, 89,<br>92 | GND      | Analog ground - Ground reference and current return for analog circuitry                                                                                                                                                                                                                                                                                  |  |

| AVDD     | 82, 84, 88, 95        | $V_{DD}$ | log VDD - Power supply for analog circuitry. Nominally 3.3 V                                                                                                                                                                                                                                                                                              |  |

| CTL[3:1] | 42, 41, 40            | DO       | eral-purpose control signals - Used for user-defined control. CTL1 is not powered down ugh PDO.                                                                                                                                                                                                                                                           |  |

| DE       | 46                    | DO       | Output data enable - Used to indicate time of active video display versus non-active display or blank time. During blank, the device transmits only HSYNC, VSYNC, and CTL[3:1]. During times of active display, or non-blank, the device transmits only pixel data, QE[23:0], and QO[23:0]. High: Active display time Low: Blank time                     |  |

| DFO      | 1                     | DI       | Output clock data format - Controls the output clock (ODCK) format for either TFT or DSTN panel support. For TFT support, the ODCK clock runs continuously. For DSTN support, ODCK only clocks when DE is high; otherwise, ODCK remains low when DE is low.  High: DSTN support - ODCK held low when DE = low  Low: TFT support - ODCK runs continuously. |  |

| GND      | 5, 39, 68             | GND      | Digital ground - Ground reference and current return for digital core                                                                                                                                                                                                                                                                                     |  |

| DVDD     | 6, 38, 67             | $V_{DD}$ | Digital VDD - Power supply for digital core. Nominally 3.3 V.                                                                                                                                                                                                                                                                                             |  |

| EXT_RES  | 96                    | Al       | Internal impedance matching – The TFP401A-Q1 device has internal optimization for impedance matching at 50 $^{\Omega}$ . An external resistor tied to this pin has no effect on device performance.                                                                                                                                                       |  |

| HSYNC    | 48                    | DO       | orizontal sync output                                                                                                                                                                                                                                                                                                                                     |  |

| RSVD     | 99                    | DI       | Reserved. Tie this pin high for normal operation.                                                                                                                                                                                                                                                                                                         |  |

# 表 5-1. Pin Functions (continued)

|           | PIN                   | <b>TYPE</b> (1)     | 2 3-1.1 III 1 unctions (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-----------|-----------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME      | NO.                   | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| OVDD      | 18, 29, 43, 57,<br>78 | V <sub>DD</sub>     | Output driver VDD - Power supply for output drivers. Nominally 3.3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| ODCK      | 44                    | DO                  | Output data clock - Pixel clock. The device synchronizes all pixel outputs QE[23:0] and QO[23:0] (if in 2-pixels-per-clock mode), along with DE, HSYNC, VSYNC and CTL[3:1], to this clock.                                                                                                                                                                                                                                                                                                                                                       |  |  |

| OGND      | 19, 28, 45, 58,<br>76 | GND                 | Output driver ground - Ground reference and current return for digital output drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| OCK_INV   | 100                   | DI                  | ODCK polarity - Selects ODCK edge to which pixel data (QE[23:0] and QO[23:0]) and control signals (HSYNC, VSYNC, DE, CTL[3:1]) latch. Normal mode: High: Latches output data on rising ODCK edge Low: Latches output data on falling ODCK edge                                                                                                                                                                                                                                                                                                   |  |  |

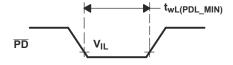

| PD        | 2                     | DI                  | Power down - An active-low signal that controls the TFP401A-Q1 power-down state. During power down, all output buffers switch to a high-impedance state. The device powers down all analog circuits and disables all inputs, except for PD.  If leaving PD unconnected, an internal pullup defaults the TFP401A-Q1 device to normal operation.  High: Normal operation Low: Power down                                                                                                                                                           |  |  |

| PDO       | 9                     | DI                  | Dutput drive power down - An active-low signal that controls the power-down state of the output drivers. During output drive power down, the output drivers (except SCDT and CTL1) are driven a high-impedance state. When PDO is left unconnected, an internal pullup defaults the TFP401, 21 device to normal operation.  High: Normal operation; output drivers on Low: Output drive powered down                                                                                                                                             |  |  |

| PGND      | 98                    | GND                 | PLL GND - Ground reference and current return for internal PLL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| PIXS      | 4                     | DI                  | Pixel select - Selects between 1- and 2-pixels-per-clock output modes. During the 2-pixels-per-clock mode, the device outputs both even pixels, QE[23:0], and odd pixels, QO[23:0], in tandem on a given clock cycle. During 1-pixel-per-clock mode, the device outputs even and odd pixels sequentially, one at a time, with the even pixel first, on the even-pixel bus, QE[23:0]. (The first pixel per line is pixel-0, the even pixel. The second pixel per line is pixel-1, the odd pixel). High: 2 pixels per clock Low: 1 pixel per clock |  |  |

| PVDD      | 97                    | V <sub>DD</sub>     | PLL VDD - Power supply for internal PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| QE[8:15]  | 20 - 27               | DO                  | Even green-pixel output - Output for even and odd green pixels when in 1-pixel-per-clock mode. Output for even-only green pixel when in 2-pixels-per-clock mode. Output data synchronizes to the output data clock, ODCK. LSB: QE8, pin 20 MSB: QE15, pin 27                                                                                                                                                                                                                                                                                     |  |  |

| QE[16:23] | 30 - 37               | DO                  | Even red-pixel output - Output for even and odd red pixels when in 1-pixel-per-clock mode. Output for even-only red pixel when in 2-pixels-per-clock mode. Output data synchronizes to the output data clock, ODCK. LSB: QE16, pin 30 MSB: QE23, pin 37                                                                                                                                                                                                                                                                                          |  |  |

| QO[0:7]   | 49 - 56               | DO                  | Odd blue-pixel output - Output for odd-only blue pixel when in 2-pixels-per-clock mode. Not used, and held low, when in 1-pixel-per-clock mode. Output data synchronizes to the output data clock, ODCK. LSB: Q00, pin 49 MSB: Q07, pin 56                                                                                                                                                                                                                                                                                                       |  |  |

| QO[8:15]  | 59 - 66               | DO                  | Odd green-pixel output - Output for odd-only green pixel when in 2-pixels-per-clock mode. Not used, and held low, when in 1-pixel-per-clock mode. Output data synchronizes to the output data clock, ODCK. LSB: QO8, pin 59 MSB: QO15, pin 66                                                                                                                                                                                                                                                                                                    |  |  |

### 表 5-1. Pin Functions (continued)

|                                                                                                                  | PIN         | TVD=(1)             | DEGODISTION                                                                                                                                                                                                                                                                                                                                              |  |

|------------------------------------------------------------------------------------------------------------------|-------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                                                                                                             | NO.         | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                              |  |

| QO[16:23]                                                                                                        | 69 - 75, 77 | DO                  | Odd red-pixel output - Output for odd-only red pixel when in 2-pixels-per-clock mode. Not used, and held low, when in 1-pixel-per-clock mode. Output data synchronizes to the output data clock, ODCK. LSB: QO16, pin 69 MSB: QO23, pin 77                                                                                                               |  |

| QE[0:7]                                                                                                          | 10 - 17     | DO                  | Even blue-pixel output - Output for even and odd blue pixels when in 1-pixel-per-clock mode. Output for even-only blue pixel when in 2-pixels-per-clock mode. Output data synchronizes to the output data clock, ODCK. LSB: QE0, pin 10 MSB: QE7, pin 17                                                                                                 |  |

| RxC+                                                                                                             | 93          | Al                  | Clock positive receiver input - Positive side of reference clock. TMDS low-voltage signal differential-input pair.                                                                                                                                                                                                                                       |  |

| RxC -                                                                                                            | 94          | Al                  | Clock negative receiver input - Negative side of reference clock. TMDS low-voltage signal differential-input pair.                                                                                                                                                                                                                                       |  |

| Channel-0 positive receiver input - Positive side of channel-0. TMDS low-voltage signal differential-input pair. |             |                     |                                                                                                                                                                                                                                                                                                                                                          |  |

| Rx0 -                                                                                                            | 91          | Al                  | Channel-0 negative receiver input - Negative side of channel-0. TMDS low-voltage signal differential-input pair.                                                                                                                                                                                                                                         |  |

| Rx1+                                                                                                             | 85          | Al                  | Channel-1 positive receiver input - Positive side of channel-1 TMDS low-voltage signal differential-input pair. Channel-1 receives green-pixel data in active display and CTL1 control signals in blank.                                                                                                                                                 |  |

| Rx1 -                                                                                                            | 86          | Al                  | Channel-1 negative receiver input - Negative side of channel-1 TMDS low-voltage signal differential-input pair.                                                                                                                                                                                                                                          |  |

| Rx2+                                                                                                             | 80          | Al                  | Channel-2 positive receiver input - Positive side of channel-2 TMDS low-voltage signal differential-input pair. Channel-2 receives red-pixel data in active display and CTL2, CTL3 control signals in blank.                                                                                                                                             |  |

| Rx2 -                                                                                                            | 81          | Al                  | Channel-2 negative receiver input - Negative side of channel-2 TMDS low-voltage signal differential-input pair                                                                                                                                                                                                                                           |  |

| SCDT                                                                                                             | 8           | DO                  | Sync detect - Output to signal when the link is active or inactive. The link is active when DE is actively switching. The TFP401A-Q1 device monitors the state of DE to determine link activity. SCDT can be tied externally to $\overline{\text{PDO}}$ to power down the output drivers when the link is inactive. High: Active link Low: Inactive link |  |

| ST                                                                                                               | 3           | DI                  | Output drive strength select $^-$ Selects output drive strength for high- or low-current drive. (See dc specifications for $I_{OH}$ and $I_{OL}$ versus the ST state). High: High drive strength Low: Low drive strength                                                                                                                                 |  |

| STAG                                                                                                             | 7           | DI                  | Staggered pixel select - An active-low signal used in the 2-pixels-per-clock pixel mode (PIXS = high). Time-staggers the even and odd pixel outputs to reduce ground bounce. Normal operation outputs the odd and even pixels simultaneously.  High: Normal simultaneous even-and-odd pixel output  Low: Time-staggered even-and-odd pixel output        |  |

| VSYNC                                                                                                            | 47          | DO                  | Vertical sync output                                                                                                                                                                                                                                                                                                                                     |  |

| Thermal Pac                                                                                                      | 1           | _                   | Thermal pad. Recommend soldering the package thermal pad to thermal pad on PCB. Soldering the thermal pad will help to release stress through the solder, otherwise the stress will be absorbed by the peripheral pins.                                                                                                                                  |  |

<sup>(1)</sup> DI = Digital Input; DO = Digital Output; AI = Analog Input; AO = Analog Output

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted) (1)

|                                                     | MIN   | MAX | UNIT |

|-----------------------------------------------------|-------|-----|------|

| Supply-voltage range DVDD, AVDD, OVDD, PVDD         | - 0.3 | 4   | V    |

| Input-voltage range, logic and analog signals       | - 0.3 | 4   | V    |

| Operating ambient temperature range, T <sub>A</sub> | - 40  | 85  | °C   |

| Storage temperature, T <sub>stg</sub>               | - 65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|                    |                         |                                              |                                                       | VALUE | UNIT |

|--------------------|-------------------------|----------------------------------------------|-------------------------------------------------------|-------|------|

|                    | Human-b                 | Human-body model (HBM), per AEC Q100-        | man-body model (HBM), per AEC Q100-002 <sup>(1)</sup> |       |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per AEC Q100-011 | All pins                                              | ±750  | V    |

| V (ESD)            | •                       |                                              | Corner pins (1, 25. 26. 50. 51, 75, 76, and 100)      | ±750  | ·    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# **6.3 Recommended Operating Conditions**

|                |                                                                  | MIN  | NOM | MAX | UNIT |

|----------------|------------------------------------------------------------------|------|-----|-----|------|

| $V_{DD}$       | Supply voltage ( $DV_{DD}$ , $AV_{DD}$ , $PV_{DD}$ , $OV_{DD}$ ) | 3    | 3.3 | 3.6 | V    |

| R <sub>t</sub> | Single-ended analog-input termination resistance                 | 45   | 50  | 55  | Ω    |

| T <sub>A</sub> | Operating free-air temperature                                   | - 40 | 25  | 85  | °C   |

#### **6.4 Thermal Information**

|                        |                                              | TFP401A-Q1 |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | PZP (PQFP) | UNIT |

|                        |                                              | 100 PINS   |      |

| R <sub>0</sub> JA      | Junction-to-ambient thermal resistance       | 24.9       | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 13.2       | °C/W |

| R <sub>0</sub> JB      | Junction-to-board thermal resistance         | 8.4        | °C/W |

| ΨJT                    | Junction-to-top characterization parameter   | 0.2        | °C/W |

| ψ ЈВ                   | Junction-to-board characterization parameter | 8.5        | °C/W |

| R <sub>θ JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.7        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semicondictor and IC Package Thermal Metrics application report.

Product Folder Links: TFP401A-Q1

# 6.5 DC Digital I/O Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                 | PARAMETER                         | TEST CONDITIONS                    | MIN | TYP | MAX     | UNIT |

|-----------------|-----------------------------------|------------------------------------|-----|-----|---------|------|

| V <sub>IH</sub> | High-level digital input voltage  |                                    | 2   |     | $DV_DD$ | V    |

| V <sub>IL</sub> | Low-level digital input voltage   |                                    | 0   |     | 0.8     | V    |

|                 | High-level output drive current   | ST = high, V <sub>OH</sub> = 2.4 V | 5   | 10  | 16.3    | mA   |

| I <sub>OH</sub> |                                   | ST = low, V <sub>OH</sub> = 2.4 V  | 3   | 6   | 10.3    |      |

| L               | Low-level output drive current    | ST = high, V <sub>OL</sub> = 0.8 V | 8   | 13  | 19      | mA   |

| I <sub>OL</sub> | or row-level oribut alive callett | ST = low, V <sub>OL</sub> = 0.8 V  | 4   | 7   | 11      | ША   |

| I <sub>OZ</sub> | Hi-Z output leakage current       | PD = low or PDO = low              | - 1 |     | 1       | μА   |

#### **6.6 DC Electrical Characteristics**

over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                                                     | TEST CONDITIONS                     | MIN                    | TYP MAX               | UNIT |

|-----------------------|---------------------------------------------------------------|-------------------------------------|------------------------|-----------------------|------|

| V <sub>ID</sub>       | Analog-input differential voltage <sup>(1)</sup>              |                                     | 75                     | 1200                  | mV   |

| V <sub>IC</sub>       | Analog-input common-mode voltage <sup>(1)</sup>               |                                     | AV <sub>DD</sub> - 300 | AV <sub>DD</sub> - 37 | mV   |

| V <sub>I(OC)</sub>    | Open-circuit analog input voltage                             |                                     | AV <sub>DD</sub> - 10  | AV <sub>DD</sub> + 10 | mV   |

| I <sub>DD(2PIX)</sub> | Normal 2-pixels-per-clock power-supply current <sup>(2)</sup> | ODCK = 82.5 MHz, 2 pixels per clock |                        | 370                   | mA   |

| I <sub>PD</sub>       | Power-down current <sup>(3)</sup>                             | PD = low                            |                        | 10                    | mA   |

| I <sub>PDO</sub>      | Output-drive power-down current <sup>(3)</sup>                | PDO = low                           |                        | 35                    | mA   |

- (1) Specified as dc characteristic with no overshoot or undershoot.

- Alternating 2-pixel black and 2-pixel white patterns. ST = high,  $\overline{STAG}$  = high, QE[23:0] and QO[23:0] C<sub>L</sub> = 10 pF.

- (3) Analog inputs are open-circuit (transmitter disconnected from the TFP401A-Q1 device).

### **6.7 AC Electrical Characteristics**

over recommended operating free-air temperature range (unless otherwise noted)

|                    | PARAMETER                                     | TEST CONDITIONS         | MIN  | TYP | MAX  | UNIT              |  |

|--------------------|-----------------------------------------------|-------------------------|------|-----|------|-------------------|--|

| V <sub>ID(2)</sub> | Differential input sensitivity <sup>(1)</sup> |                         | 150  |     | 1560 | mV <sub>p-p</sub> |  |

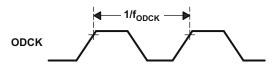

| f <sub>ODCK</sub>  | ODCK frequency                                | PIXS = low (1-PIX/CLK)  | 25   |     | 165  | MHz               |  |

|                    | ODCK frequency                                | PIXS = high (2-PIX/CLK) | 12.5 |     | 82.5 | IVIMZ             |  |

|                    | ODCK duty-cycle                               |                         | 45%  | 60% | 75%  |                   |  |

(1) Specified as ac parameter to include sensitivity to overshoot, undershoot, and reflection.

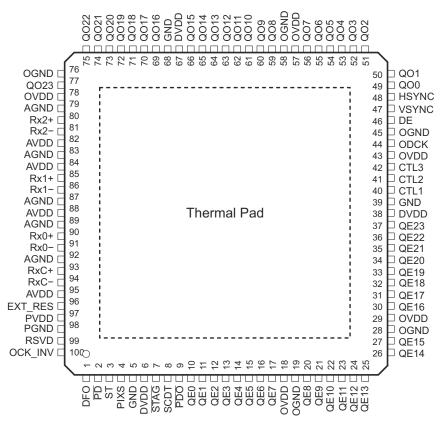

#### 6.8 Timing Requirements

|                   | PARAMETER                                                               | TEST CONDITIONS                                                 | MIN  | TYP MAX | UNIT                 |  |  |  |

|-------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------|------|---------|----------------------|--|--|--|

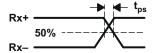

| t <sub>ps</sub>   | Analog input intra-pair (+ to - ) differential skew <sup>(2)</sup>      |                                                                 |      | 0.4     | t <sub>bit</sub> (1) |  |  |  |

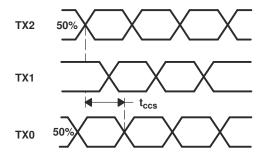

| t <sub>ccs</sub>  | Analog input inter-pair or channel-to-channel skew (2)                  |                                                                 |      | 1       | t <sub>pix</sub> (3) |  |  |  |

| t <sub>ijit</sub> | Worst-case differential input-clock jitter tolerance <sup>(2) (4)</sup> |                                                                 | 50   |         | ps                   |  |  |  |

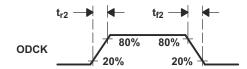

|                   | Fall time of data and control signals <sup>(5)</sup> (6)                | ST = low, C <sub>L</sub> = 5 pF                                 |      | 2.4     |                      |  |  |  |

| t <sub>f1</sub>   | Fail time of data and control signals of to                             | ST = high, C <sub>L</sub> = 10 pF                               |      | ns      |                      |  |  |  |

|                   | Rise time of data and control signals <sup>(5)</sup> (6)                | ST = low, C <sub>L</sub> = 5 pF                                 |      | 2.4     | no                   |  |  |  |

| t <sub>r1</sub>   | Trise time of data and control signals (7.47)                           | ST = high, C <sub>L</sub> = 10 pF                               |      | 1.9     | ns                   |  |  |  |

|                   | Rise time of ODCK clock <sup>(5)</sup>                                  | ST = low, C <sub>L</sub> = 5 pF                                 |      | 2.4     | no                   |  |  |  |

| t <sub>r2</sub>   | Rise time of ODCR Glock                                                 | ST = high, C <sub>L</sub> = 10 pF                               |      | 1.9     | ns                   |  |  |  |

| t <sub>f2</sub>   | Fall time of ODCK clock <sup>(5)</sup>                                  | ST = low, C <sub>L</sub> = 5 pF                                 |      | 2.4     | ne                   |  |  |  |

| կք <u>2</u>       | rail time of ODCR Gock                                                  | ST = high, C <sub>L</sub> = 10 pF                               |      | ns      |                      |  |  |  |

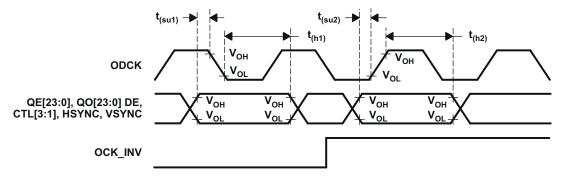

|                   |                                                                         | 1 pixel per clock, PIXS = low, OCK_INV = low                    | 1.8  |         |                      |  |  |  |

| t <sub>su1</sub>  | ODCK                                                                    | 2 pixels per clock, PIXS = high,<br>STAG = high, OCK_INV = low  | 3.8  |         | ns                   |  |  |  |

|                   |                                                                         | 2 pixels and STAG, PIXS = high,<br>STAG = low, OCK_INV = low    | 0.6  |         |                      |  |  |  |

|                   | Hold time, data and control signal to falling edge of ODCK              | 1 pixel per clock, PIXS = low, OCK_INV = low                    | 0.6  |         |                      |  |  |  |

| t <sub>h1</sub>   |                                                                         | 2 pixels and STAG, PIXS = high, STAG = low, OCK_INV = low       | 2.5  |         | ns                   |  |  |  |

|                   |                                                                         | 2 pixels per clock, PIXS = high,<br>STAG = high, OCK_INV = low  | 2.9  |         |                      |  |  |  |

|                   |                                                                         | 1 pixels per clock, PIXS = low, OCK_INV = high                  | 2.1  |         |                      |  |  |  |

| t <sub>su2</sub>  | Setup time, data and control signal to rising edge of ODCK              | 2 pixels per clock, PIXS = high,<br>STAG = high, OCK_INV = high | 4    |         | ns                   |  |  |  |

|                   |                                                                         | 2 pixels and STAG, PIXS = high,<br>STAG = low, OCK_INV = high   | 1.5  |         |                      |  |  |  |

|                   | Hold time, data and control signal to rising edge of                    | 1 pixel per clock, PIXS = low, OCK_INV = high                   | 0.3  |         |                      |  |  |  |

| t <sub>h2</sub>   |                                                                         | 2 pixels and STAG, PIXS = high,<br>STAG = low, OCK_INV = high   | 2.4  |         | ns                   |  |  |  |

|                   |                                                                         | 2 pixels per clock, PIXS = high,<br>STAG = high, OCK_INV = high | 2.1  |         |                      |  |  |  |

| t <sub>pix</sub>  | Pixel time <sup>(3)</sup>                                               |                                                                 | 6.06 | 40      | ns                   |  |  |  |

- $t_{\text{bit}}$  is 1/10 the pixel time,  $t_{\text{pix}}.$  Specified by characterization. (1)

- (2)

- t<sub>pix</sub> is the pixel time defined as the period of the RxC clock input. The period of the output clock, ODCK, is equal to t<sub>pix</sub> when in 1-pixel-(3) per-clock mode or 2 t<sub>pix</sub> when in 2-pixels-per-clock mode.

Measured differentially at 50% crossing using ODCK output clock as trigger.

- (4)

- (5) Rise and fall times measured as time between 20% and 80% of signal amplitude.

- Data and control signals are QE[23:0], QO[23:0], DE, HSYNC, VSYNC. and CTL[3:1].

- Amount of time detected between DE transitions determines whether link is active or inactive. SCDT indicates link activity.

图 6-1. Rise and Fall Times of Data and Control Signals

Submit Document Feedback

图 6-2. Rise and Fall Times of ODCK

图 6-3. ODCK Frequency

图 6-4. Data Setup and Hold Times to Rising and Falling Edges of ODCK

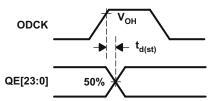

图 6-5. ODCK High to QE[23:0] Staggered Data Output

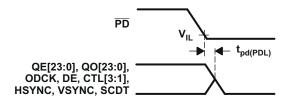

图 6-6. Delay From PD Low to Hi-Z Outputs

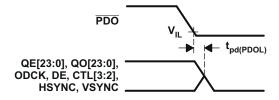

图 6-7. Delay From PDO Low to Hi-Z Outputs

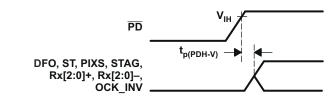

图 6-8. Delay From PD Low to High Until Inputs Are Active

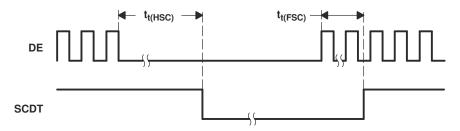

图 6-9. Time From DE Transitions to SCDT Low and SCDT High

# 6.9 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

| PARAMETER             |                                                           | PARAMETER TEST CONDITIONS |  |      |   | UNIT             |

|-----------------------|-----------------------------------------------------------|---------------------------|--|------|---|------------------|

| t <sub>pd(PDL)</sub>  | Propagation delay time from PD low to Hi-Z outputs        |                           |  |      | 9 | ns               |

| t <sub>pd(PDOL)</sub> | Propagation delay time from PDO low to Hi-Z outputs       |                           |  |      | 9 | ns               |

| $t_{t(HSC)}$          | Delay time from DE transition to SCDT low <sup>(7)</sup>  |                           |  | 1e6  |   | t <sub>pix</sub> |

| t <sub>t(FSC)</sub>   | Delay time from DE transition to SCDT high <sup>(7)</sup> |                           |  | 1600 |   | t <sub>pix</sub> |

| t <sub>d(st)</sub>    | Delay time, ODCK latching edge to QE[23:0] data output    | STAG = low, PIXS = high   |  | 0.25 |   | t <sub>pix</sub> |

图 6-10. Analog Input Intra-Pair Differential Skew

图 6-11. Minimum Time PD Low

图 6-12. Analog Input Channel-to-Channel Skew

Submit Document Feedback

图 6-13. Minimum DE Low and Maximum DE High

# **6.10 Typical Characteristics**

图 6-14. Imax vs Input Frequency

# 7 Detailed Description

#### 7.1 Overview

The TFP401A-Q1 device is a digital visual interface (DVI)-compliant TMDS digital receiver used in digital flat-panel display systems to receive and decode TMDS-encoded RGB pixel data streams. In a digital display system, a host (usually a PC or workstation) contains a TMDS-compatible transmitter that receives 24-bit pixel data along with appropriate control signals. The host encodes the data and control signals into a high-speed low-voltage differential serial bit stream (fit for transmission over a twisted-pair cable) to a display device. The display device (usually a flat-panel monitor) requires a TMDS-compatible receiver like the TI TFP401A-Q1 device to decode the serial bit stream back to the same 24-bit pixel data and control signals that originated at the host. This decoded data is then suitable for application directly to the flat-panel drive circuitry to produce an image on the display. Host and display separation distances can be up to 5 meters or more, making serial transmission of the pixel data preferable. Support of modern display resolutions up to UXGA requires a high-bandwidth receiver with good jitter and skew tolerance.

#### 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### 7.3.1 TMDS Pixel Data and Control Signal Encoding

The device transmits only one of two possible transition-minimized differential signaling (TMDS) characters for a given pixel at a given time. The transmitter keeps a running count of the number of ones and zeros previously sent, and transmits the character that minimizes the number of transitions to approximate a dc balance of the transmission line.

Reception of RGB pixel data during active display time uses three TMDS channels, DE = high. The same three channels also receive control signals, HSYNC, VSYNC, and user-defined control signals CTL[3:1]. Reception of these control signals occurs during inactive display or blanking-time. Blanking-time is when DE = low. The following table maps the received input data to the appropriate TMDS input channel in a DVI-compliant system.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

表 7-1. TMDS Pixel Data and Control Signal Encoding

| ,,                                           |                   |                                      |  |  |  |  |  |  |  |

|----------------------------------------------|-------------------|--------------------------------------|--|--|--|--|--|--|--|

| RECEIVED PIXEL DATA ACTIVE DISPLAY DE = HIGH | INPUT CHANNEL     | OUTPUT PINS<br>(VALID FOR DE = HIGH) |  |  |  |  |  |  |  |

| Red[7:0]                                     | Channel-2 (Rx2 ±) | QE[23:16] QO[23:16]                  |  |  |  |  |  |  |  |

| Green[7:0]                                   | Channel-1 (Rx1 ±) | QE[15:8] QO[15:8]                    |  |  |  |  |  |  |  |

| Blue[7:0]                                    | Channel-0 (Rx0 ±) | QE[7:0] QO[7:0]                      |  |  |  |  |  |  |  |

| RECEIVED CONTROL DATA BLANKING DE = LOW      | INPUT CHANNEL     | OUTPUT PINS<br>(VALID FOR DE = LOW)  |  |  |  |  |  |  |  |

| CTL[3:2]                                     | Channel-2 (Rx2 ±) | CTL[3:2]                             |  |  |  |  |  |  |  |

| CTL[1: 0] <sup>(1)</sup>                     | Channel-1 (Rx1 ±) | CTL1                                 |  |  |  |  |  |  |  |

| HSYNC, VSYNC                                 | Channel-0 (Rx0 ±) | HSYNC, VSYNC                         |  |  |  |  |  |  |  |

|                                              |                   |                                      |  |  |  |  |  |  |  |

<sup>(1)</sup> Some TMDS transmitters transmit a CTL0 signal. The TFP401A-Q1 device decodes and transfers CTL[3:1] and ignores CTL0 characters. CTL0 is not available as a TFP401A-Q1 output.

The TFP401A-Q1 device discriminates between valid pixel TMDS characters and control TMDS characters to determine the state of active display versus blanking, in effect, the state of DE.

#### 7.3.2 TFP401A-Q1 Clocking and Data Synchronization

The TFP401A-Q1 device receives a clock reference from the DVI transmitter that has a period equal to the pixel time,  $t_{pix}$ . Another name for the frequency of this clock is the pixel rate. Because the TMDS encoded data on Rx[2:0] contains 10 bits per 8-bit pixel, it follows that the Rx[2:0] serial bit rate is 10 times the pixel rate. For example, the required pixel rate to support a UXGA resolution with 60-Hz refresh rate is 165 MHz. The TMDS serial bit rate is  $10^{\times}$  the pixel rate, or 1.65 Gb/s. Due to the transmission of this high-speed digital bit stream, on three separate channels (or twisted-pair wires) of long distances (3 - 5 meters), there is no assurance of phase synchronization between the data steams and the input reference clock. In addition, skew between the three data channels is common. The TFP401A-Q1 device uses a 4× oversampling scheme of the input data streams to achieve reliable synchronization with up to 1- $t_{pix}$  channel-to-channel skew tolerance. Accumulated jitter on the clock and data lines due to reflections and external noise sources is also typical of high-speed serial data transmission; hence, the TFP401A-Q1 design for high jitter tolerance.

A phase-locked loop (PLL) conditions the input clock of the TFP401A-Q1 device to remove high-frequency jitter from the clock. The PLL provides four  $10\times$  clock outputs of different phase to locate and sync the TMDS data streams ( $4\times$  oversampling). During active display, the pixel data encoding is for transition minimization, whereas in blank, the control data encoding is for transition maximization. Transmitting in blank for a minimum period of time,  $128~t_{pix}$ , requires a DVI-compliant transmitter to ensure sufficient time for data synchronization when the receiver sees a transition-maximized code. Synchronization during blank, when the data is transition-maximized, ensures reliable data-bit boundary detection. Phase synchronization to the data streams, maintained as long as the link remains active, is unique for each of the three input channels.

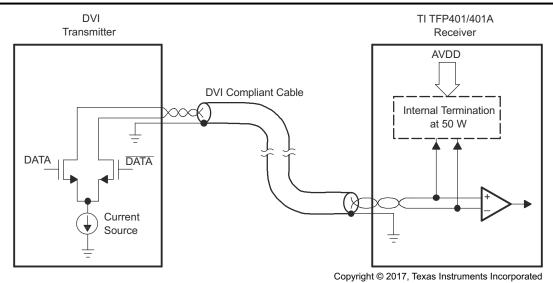

#### 7.3.3 TFP401A-Q1 TMDS Input Levels and Input Impedance Matching

The TMDS inputs to the TFP401A-Q1 receiver have a fixed single-ended termination to AV<sub>DD</sub>. A laser trim process internally optimizes the TFP401A-Q1 device to fix the impedance precisely at 50  $\,^{\Omega}$ . The device functions normally with or without a resistor on the EXT\_RES pin, so it remains drop-in compatible with current sockets. The fixed impedance eliminates the need for an external resistor while providing optimum impedance matching to standard 50- $^{\Omega}$  DVI cables.

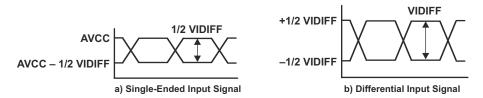

☑ 7-1 shows a conceptual schematic of a DVI transmitter and TFP401A-Q1 receiver connection. A transmitter drives the twisted-pair cable through a current source, usually using an open-drain type of output driver. The internal resistor, matched to the cable impedance at the TFP401A-Q1 input, provides a pullup to AV<sub>DD</sub>. Naturally, with the transmitter disconnected and the TFP401A-Q1 DVI inputs left unconnected, the TFP401A-Q1 receiver inputs pull up to AV<sub>DD</sub>. ☑ 7-2 shows the single-ended differential signal and full-differential signal. The design of the TFP401A-Q1 device is for response to differential signal swings ranging from 150 mV to 1.56 V, with common-mode voltages ranging from (AV<sub>DD</sub> - 300 mV) to (AV<sub>DD</sub> - 37 mV).

图 7-1. TMDS Differential Input and Transmitter Connection

图 7-2. TMDS Inputs

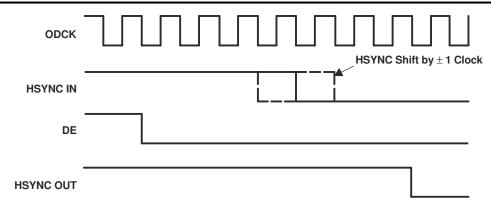

#### 7.3.4 TFP401A-Q1 Device Incorporates HSYNC Jitter Immunity

Several DVI transmitters available in the market introduce jitter on the transmitted HSYNC and VSYNC signals during the TMDS encryption process. The HSYNC signal can shift by one pixel position (one clock) from nominal in either direction, resulting in up to two cycles of HSYNC shift. This jitter carries through to the DVI receiver, and if the position of HSYNC shifts continuously, the receiver can lose track of the input timing, causing pixel noise to occur on the display. For this reason, one should use a DVI-compliant receiver with HSYNC jitter immunity in all displays that could be connected to host PCs with transmitters that have this HSYNC jitter problem.

The TFP401A-Q1 integrates HSYNC regeneration circuitry that provides a seamless interface to these noncompliant transmitters. The regeneration circuitry always fixes the position of the data enable (DE) signal in relation to data, irrespective of the location of HSYNC. The TFP401A-Q1 receiver uses the DE and clock signals to recreate stable vertical and horizontal sync signals. The circuit filters the HSYNC output of the receiver and shifts HSYNC to the nearest eighth bit boundary, producing a stable output with respect to the data, as shown in  $\mathbb{Z}$  7-3. This ensures accurate data synchronization at the input of the display timing controller.

This HSYNC regeneration circuit is transparent to the monitor, and removal is unnecessary even if the transmitted HSYNC is stable. For example, the *PanelBus* line of DVI 1.0-compliant transmitters, such as the TFP6422 and TFP420, do not have the HSYNC jitter problem. The TFP401A-Q1 device operates correctly with either compliant or noncompliant transmitters. In contrast, the TFP401A-Q1 device is ideal for customers who have control over the transmit portion of the design, such as bundled-system manufacturers and for internal monitor use (the DVI connection between monitor and panel modules).

图 7-3. HSYNC Regeneration Timing Diagram

#### 7.4 Device Functional Modes

### 7.4.1 TFP401A-Q1 Modes of Operation

The TFP401A-Q1 device provides system design flexibility and value by providing the system designer with configurable options or modes of operation to support varying system architectures. 表 7-2 outlines the various supportable panel modes, along with appropriate external control pin settings.

| ₹ 1-2. Oupported 1 differ modes |                               |                   |                 |   |      |         |  |  |  |  |

|---------------------------------|-------------------------------|-------------------|-----------------|---|------|---------|--|--|--|--|

| PANEL                           | PIXEL RATE                    | ODCK LATCH EDGE   | LATCH EDGE ODCK |   | PIXS | OCK_INV |  |  |  |  |

| TFT or 16-bit DSTN              | 1 pixel per clock             | Falling           | Free run        | 0 | 0    | 0       |  |  |  |  |

| TFT or 16-bit DSTN              | 16-bit DSTN 1 pixel per clock |                   | Rising Free run |   | 0    | 1       |  |  |  |  |

| TFT                             | FT 2 pixels per clock         |                   | Free run        | 0 | 1    | 0       |  |  |  |  |

| TFT                             | 2 pixels per clock            | Rising            | Free run        | 0 | 1    | 1       |  |  |  |  |

| 24-bit DSTN                     | 1 pixel per clock             | Falling           | Gated low       | 1 | 0    | 0       |  |  |  |  |

| None                            | 1 pixel per clock             | Rising            | Gated low       | 1 | 0    | 1       |  |  |  |  |

| 24-bit DSTN 2 pixels per clock  |                               | Falling Gated low |                 | 1 | 1    | 0       |  |  |  |  |

| 24-bit DSTN                     | 2 pixels per clock            | Rising Gated low  |                 | 1 | 1    | 1       |  |  |  |  |

表 7-2. Supported Panel Modes

#### 7.4.2 TFP401A-Q1 Output Driver Configurations

The TFP401A-Q1 device provides flexibility by offering various output driver features for use to optimize power consumption, ground bounce, and power-supply noise. The following sections outline the output driver features and their effects.

**Output Driver Power Down** ( $\overline{PDO}$  = low): Pulling  $\overline{PDO}$  low places all the output drivers, except CTL1 and SCDT, into a high-impedance state. One can tie the SCDT output, which indicates link-disabled or link-inactive, directly to the  $\overline{PDO}$  input to disable the output drivers when the link is inactive or when the cable is disconnected. An internal pullup on the  $\overline{PDO}$  pin defaults the TFP401A-Q1 device to the normal nonpower-down output-drive mode if left unconnected.

**Drive Strength** (ST = high for high drive strength, ST = low for low drive strength): The TFP401A-Q1 device allows for selectable output drive strength on the data, control, and ODCK outputs. See the *DC Electrical Characteristics* table for the values of  $I_{OH}$  and  $I_{OL}$  current drives for a given ST state. The high output-drive strength offers approximately two times the drive as the low output-drive strength.

**Time-Staggered Pixel Output:** This option works only in conjunction with the 2-pixels-per-clock mode (PIXS = high). Setting  $\overline{STAG}$  = low time-staggers the even- and odd-pixel outputs so as to reduce the amount of instantaneous current surge from the power supply. Depending on the PCB layout and design, this can help reduce the amount of system ground bounce and power-supply noise. The time stagger is such that in 2-pixels-per-clock mode, the even pixel is delayed from the latching edge of ODCK by 0.25  $t_{cip}$ . ( $t_{cip}$  is the period of ODCK. The ODCK period is 2  $t_{pix}$  when in 2-pixels-per-clock mode.)

Depending on system constraints of output load, pixel rate, panel input architecture, and board cost, the TFP401A-Q1 drive-strength and staggered-pixel options allow flexibility to reduce system power-supply noise, ground bounce, and EMI.

**Power Management:** The TFP401A-Q1 device offers several system power-management features.

The output-driver power down (PDO = low) is an intermediate mode which offers several uses. During this mode, all output drivers except SCDT and CTL1 go into a high-impedance state while the rest of the device circuitry remains active.

Power down ( $\overline{PD}$  = low) of the TFP401A-Q1 device is a complete power down in that it powers down the digital core, the analog circuitry, and output drivers. All output drivers go into a Hi-Z state. Of all the inputs, only  $\overline{PD}$  remains active. The TFP401A-Q1 device does not respond to any digital or analog inputs until  $\overline{PD}$  is pulled high.

Both  $\overline{PDO}$  and  $\overline{PD}$  have internal pullups, so if left unconnected they default the TFP401A-Q1 device to normal operating modes.

**Sync Detect:** The TFP401A-Q1 device offers an output, SCDT, to indicate link activity. The TFP401A-Q1 device monitors activity on DE to determine if the link is active. When 1 million (1e6) pixel clock periods pass without a transition on DE, the TFP401A-Q1 device considers the link inactive, and drives SCDT low. While SCDT is low, if two DE transitions are detected within 1600 pixel clock periods, the device considers the link active and pulls SCDT high.

A use of SCDT is to signal a system power management circuit to initiate a system power down when the device considers the link inactive. The SCDT can also be tied directly to the TFP401A-Q1 PDO input to power down the output drivers when the link is inactive. It is not recommended to use SCDT to drive the PD input, because once in complete power-down, the analog inputs are ignored and the SCDT state does not change. An external system power-management circuit to drive PD is preferred.

Product Folder Links: TFP401A-Q1

# 8 Application and Implementation

#### 备注

以下应用部分中的信息不属于 TI 器件规格的范围, TI 不担保其准确性和完整性。TI 的客 户应负责确定器件是否适用于其应用。客户应验证并测试其设计,以确保系统功能。

### 8.1 Application Information

The TFP401A-Q1 is a DVI (Digital Visual Interface) compliant digital receiver that is used in digital flat panel display systems to receive and decode T.M.D.S. encoded RGB pixel data streams. In a digital display system a host, usually a PC or workstation, contains a DVI compliant transmitter that receives 24 bit pixel data along with appropriate control signals and encodes them into a high speed low voltage differential serial bit stream fit for transmission over a twisted-pair cable to a display device. The display device, usually a flat-panel monitor, will require a DVI compliant receiver like the TI TFP401A-Q1 to decode the serial bit stream back to the same 24 bit pixel data and control signals that originated at the host. This decoded data can then be applied directly to the flat panel drive circuitry to produce an image on the display. Since the host and display can be separated by distances up to 5 meters or more, serial transmission of the pixel data is preferred. The TFP401A-Q1 will support resolutions up to UXGA.

#### 8.1.1 Typical Application

图 8-1. Typical Application

#### 8.1.1.1 Design Requirements

表 8-1. Design Parameters

| PARAMETER                   | VALUE             |  |  |

|-----------------------------|-------------------|--|--|

| Power supply                | 3.3 V-DC at 1 A   |  |  |

| Input clock                 | Single-ended      |  |  |

| Input clock frequency range | 25 MHz to 165 MHz |  |  |

| Output format               | 24 bits/pixel     |  |  |

| Input clock latching        | Rising edge       |  |  |

| I2C EEPROM support          | No                |  |  |

| De-skew                     | No                |  |  |

#### 8.1.1.2 Detailed Design Procedure

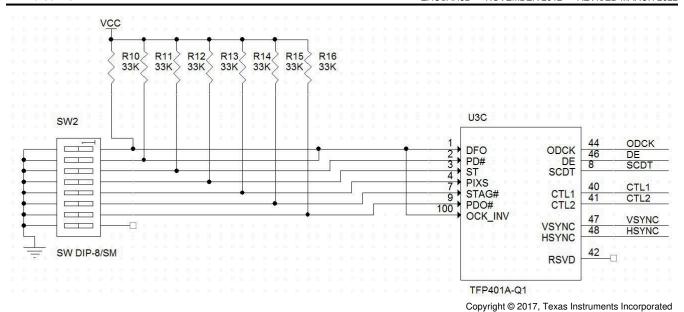

### 8.1.1.2.1 Data and Control Signals

The trace length of data and control signals out of the receiver should be kept as close to equal as possible. Trace separation should be  $\approx$ 5X Height. As a general rule, traces also should be less than 2.8 inches if possible (longer traces can be acceptable).

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

#### Calculation:

图 8-2. TFP401A-Q1 App Info Data and Control Signals

TFP401A-Q1

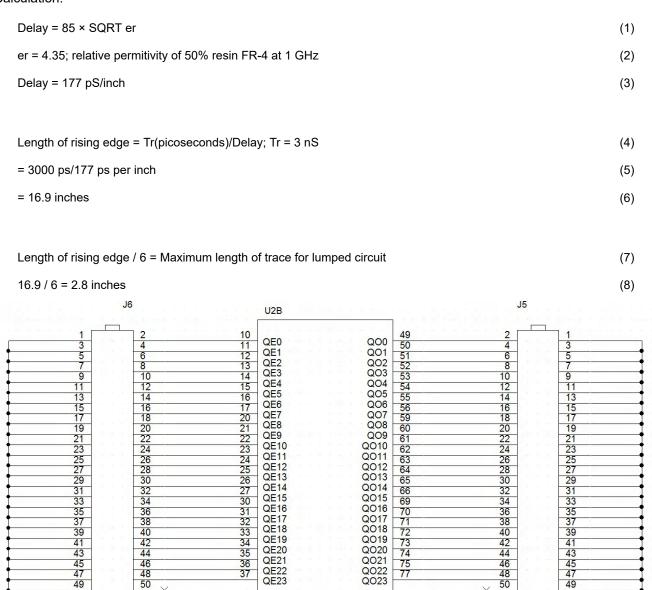

#### 8.1.1.2.2 Configuration Options

HEADER 30X2

The TFP401A-Q1 can be configured in several modes depending on the required output format, for example 1-byte/clock, 2-bytes/clock, falling/rising clock edge.

You can leave place holders for future configuration changes.

HEADER 30X2

图 8-3. TFP401A-Q1 App Info Config Options

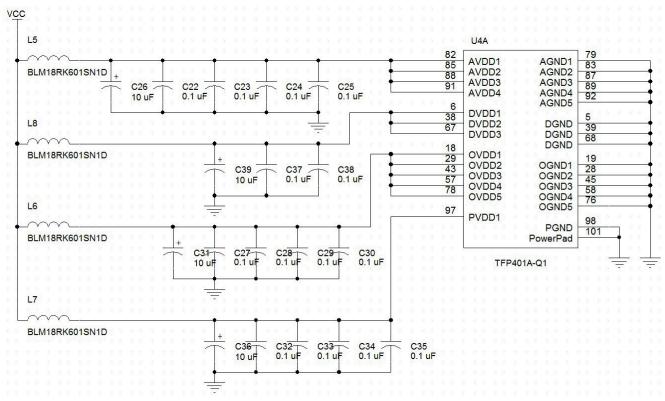

#### 8.1.1.2.3 Power Supplies Decoupling

Digital, analog and PLL supplies must be decoupled from each other to avoid electrical noise on the PLL and the core.

Copyright © 2017, Texas Instruments Incorporated

图 8-4. TFP401A-Q1 App Info Power Decoupling

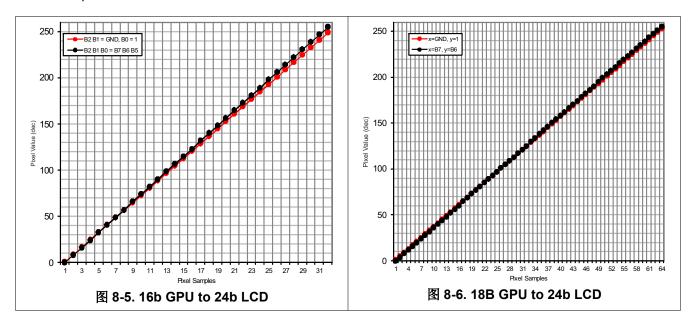

#### 8.1.1.3 Application Curves

Sometimes the panel does not support the same format as the GPU (graphics processor unit). In these cases the user must decide how to connect the unused bits.

The below plots show the mismatches between the 18-bit GPU and a 24-bit LCD where *x* and *y* represent the 2 LSB of the panel.

#### 8.1.1.4 DVDD

Place one 0.01- $\mu F$  capacitor as close as possible between each DVDD device pin (Pins 6, 38, and 67) and ground.

#### 8.1.1.5 OVDD

Place one 0.01-µF capacitor as close as possible between each OVDD device pin (Pins 18, 29, 43, 57, and 78) and ground.

A 22-µF tantalum capacitor should be placed between the supply and 0.01-µF capacitors.

A ferrite bead should be used between the source and the 22-µF capacitor.

#### 8.1.1.6 AVDD

Place one 0.01-µF capacitor as close as possible between each AVDD device pin (Pins 82, 84, 88, and 95) and ground.

A 22-µF tantalum capacitor should be placed between the supply and 0.01-µF capacitors.

A ferrite bead should be used between the source and the 22-µF capacitor.

### 8.1.1.7 PVDD

Place three 0.01- $\mu$ F capacitors in parallel as close as possible between the PVDD device pin (Pin 97) and ground. A 22- $\mu$ F tantalum capacitor should be placed between the supply and 0.01- $\mu$ F capacitors. A ferrite bead should be used between the source and the 22- $\mu$ F capacitor.

### 8.2 Power Supply Recommendations

Use solid ground planes, tie ground planes together with as many vias as is practical. This will provide a desirable return path for current. Each supply should be on separate split power planes, where each power plane should be as large an area as possible. Connect PanelBus receiver power and ground pins and all bypass caps to appropriate power or ground plane with via. Vias should be as fat and short as practical, the goal is to minimize the inductance.

#### 8.3 Layout

#### 8.3.1 Layout Guidelines

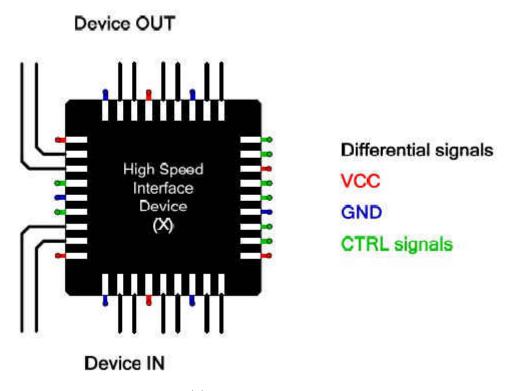

#### 8.3.1.1 Layer Stack

The pinout of Texas Instruments High Speed Interface (HSI) devices features differential signal pairs and the remaining signals comprise the supply rails, VCC and ground, and lower speed signals such as control pins. As an example, consider a device X which is a repeater/re-driver, so both its inputs and outputs are high-speed differential signals. These guidelines can be applied to other high-speed devices such as drivers, receivers, multiplexers, and so on.

A minimum of four layers is required to accomplish a low EMI PCB design. Layer stacking should be in the following order (top-to-bottom): high-speed differential signal layer, ground plane, power plane and control signal layer.

图 8-7. Layer Stack

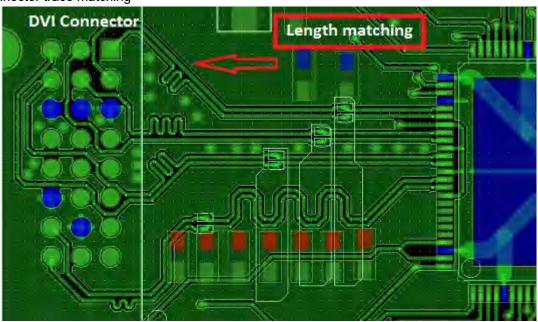

# 8.3.1.2 Routing High-Speed Differential Signal Traces (RxC-, RxC+, Rx0-, Rx0+, Rx1-, Rx1+, Rx2-, Rx2+)

Trace impedance should be controlled for optimal performance. Each differential pair should be equal in length and symmetrical and should have equal impedance to ground with a trace separation of 2X to 4X Height. A differential trace separation of 4X Height yields about 6% cross-talk (6% effect on impedance). TI recommends that differential trace routing should be side by side, though it is not important that the differential traces be tightly coupled together because tight coupling is not achievable on PCB traces. Typical ratios on PCB's are only 20-50%, 99.9% is the value of a well-balanced twisted pair cable. Each differential trace should be as short as

possible (< 2 inches preferably) with no 90° angles. These high-speed transmission traces hould be on layer 1 (top layer).

RxC-, RxC+, Rx0-, Rx0+, Rx1-, Rx1+, Rx2-, Rx2+ signals all route directly from the DVI connector pins to the device, no external components are needed.

# 8.3.2 Layout Example

· DVI connector trace matching

图 8-8. DVI Connector

· Keep data lines as far as possible from each other

图 8-9. Data Route

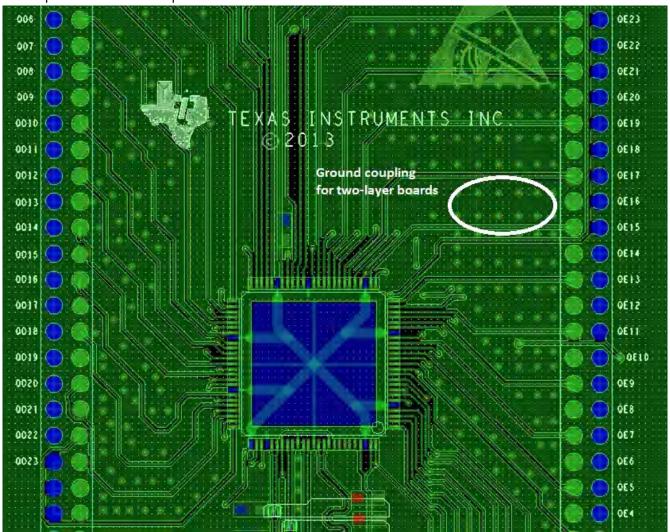

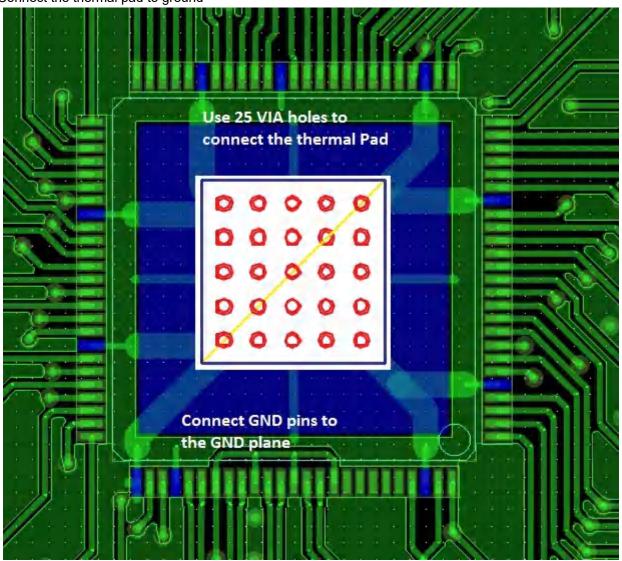

· Connect the thermal pad to ground

图 8-10. GND Route

#### 8.3.3 TI PowerPAD 100-TQFP Package

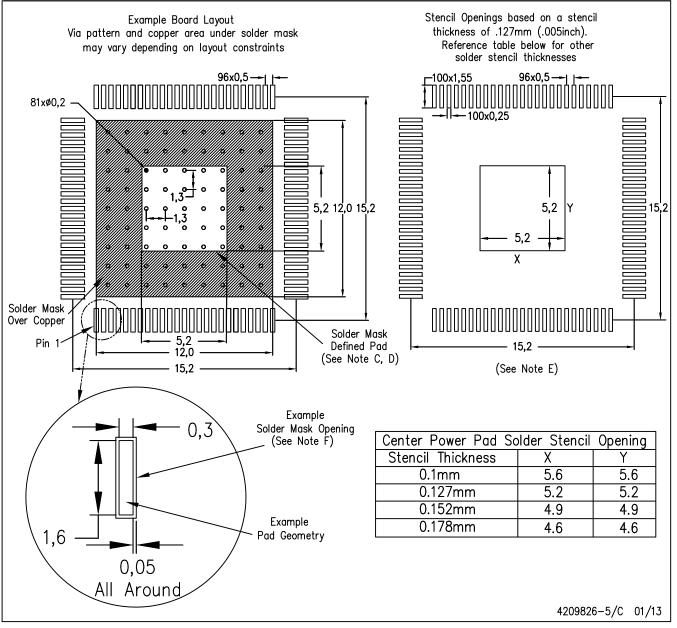

The TFP401A-Q1 device comes in Tl's thermally enhanced PowerPAD 100-TQFP package. The PowerPAD package is a 14-mm × 14-mm × 1-mm TQFP outline with 0.5-mm lead pitch. The PowerPAD package has a specially designed die mount pad that offers improved thermal capability over typical TQFP packages of the same outline. The TI 100-TQFP PowerPAD package offers a back-side solder plane that connects directly to the die mount pad for enhanced thermal conduction. There is no thermal requirement for soldering the back side of the TFP401A-Q1 device to the application board, because the device power dissipation is well within the package capability when not soldered. However, to minimize stress on peripheral pins, it is highly recommended to solder the thermal pad to PCB.

Soldering the back side of the device to the PCB ground plane is recommended for electrical considerations. Because the die pad is electrically connected to the chip substrate and hence to chip ground, connection of the PowerPAD's back side to a PCB ground plane helps to improve EMI, ground bounce, and power-supply noise performance.

表 8-2 outlines the thermal properties of the TI 100-TQFP PowerPAD package. The 100-TQFP non-PowerPAD package is included only for reference.

WITHOUT PowerPAD™ PACKAGE. PowerPAD™ PACKAGE. **PARAMETER** PowerPAD™ NOT CONNECTED TO PCB **CONNECTED TO PCB** PACKAGE THERMAL PLANE THERMAL PLANE(1) Theta-JA<sup>(1)</sup> (2) 45°C/W 27.3°C/W 17.3°C/W Theta-JC(1)(2) 3.11°C/W 0.12°C/W 0.12°C/W

2.7 W

表 8-2. TI 100-TQFP (14 mm × 14 mm × 1 mm) With 0.5-mm Lead Pitch

(1) Specified with 2-oz. (0.071 mm thick) Cu PCB plating.

1.6 W

(2) Airflow is at 0 LFM (0 m/s) (no airflow).

Maximum power dissipation(1)(2)(3)

(3) Measured at ambient temperature,  $T_A = 70$ °C.

Product Folder Links: TFP401A-Q1

4.3 W

# 9 Device and Documentation Support

### 9.1 接收文档更新通知

要接收文档更新通知,请导航至 ti.com 上的器件产品文件夹。点击*订阅更新* 进行注册,即可每周接收产品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

#### 9.2 支持资源

TI E2E™ 支持论坛是工程师的重要参考资料,可直接从专家获得快速、经过验证的解答和设计帮助。搜索现有解答或提出自己的问题可获得所需的快速设计帮助。

链接的内容由各个贡献者"按原样"提供。这些内容并不构成 TI 技术规范,并且不一定反映 TI 的观点;请参阅 TI 的《使用条款》。

#### 9.3 Trademarks

Panelbus<sup>™</sup>, PowerPAD<sup>™</sup>, and EPIC-5<sup>™</sup> are trademarks of Texas Instruments.

TI E2E™ is a trademark of Texas Instruments.

所有商标均为其各自所有者的财产。

#### 9.4 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 9.5 术语表

TI术语表本术语表列出并解释了术语、首字母缩略词和定义。

### 10 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Copyright © 2022 Texas Instruments Incorporated

www.ti.com 9-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status (1) | Material type | Package   Pins    | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|------------|---------------|-------------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

| TFP401AIPZPRQ1        | Active     | Production    | HTQFP (PZP)   100 | 1000   LARGE T&R      | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | TFP401AI         |

| TFP401AIPZPRQ1.A      | Active     | Production    | HTQFP (PZP)   100 | 1000   LARGE T&R      | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | TFP401AI         |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF TFP401A-Q1:

Catalog: TFP401A

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# PACKAGE OPTION ADDENDUM

www.ti.com 9-Nov-2025

● Enhanced Product : TFP401A-EP

NOTE: Qualified Version Definitions:

- Catalog TI's standard catalog product

- Enhanced Product Supports Defense, Aerospace and Medical Applications

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 30-Jan-2025

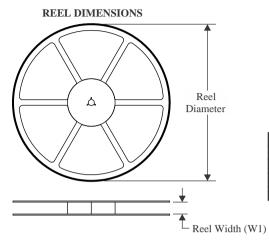

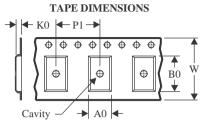

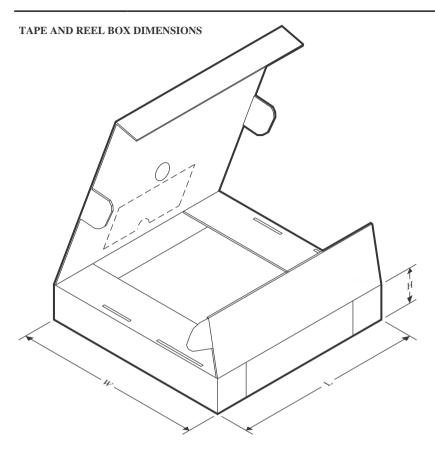

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

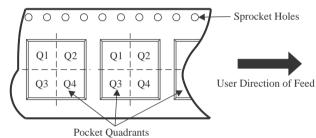

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing |     | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|-----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TFP401AIPZPRQ1 | HTQFP           | PZP                | 100 | 1000 | 330.0                    | 24.4                     | 17.0       | 17.0       | 1.5        | 20.0       | 24.0      | Q2               |

# PACKAGE MATERIALS INFORMATION

www.ti.com 30-Jan-2025

#### \*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TFP401AIPZPRQ1 | HTQFP        | PZP             | 100  | 1000 | 350.0       | 350.0      | 43.0        |

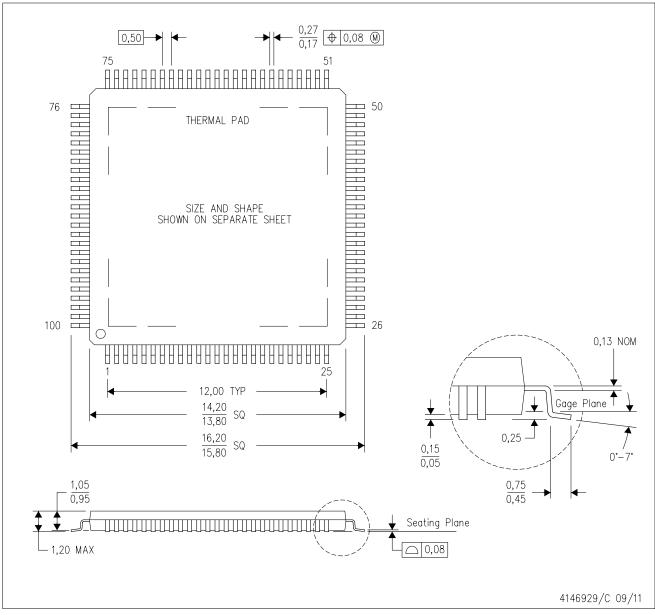

14 x 14 mm Pkg Body, 0.5 mm pitch 16 x 16 mm Pkg Area PLASTIC QUAD FLATPACK

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

PZP (S-PQFP-G100)

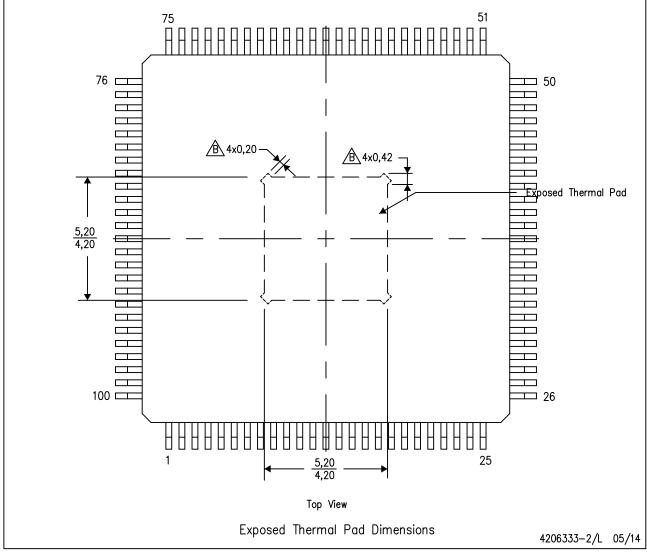

PowerPAD™ PLASTIC QUAD FLATPACK

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">www.ti.com</a>.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- F. Falls within JEDEC MS-026

PowerPAD is a trademark of Texas Instruments.

PZP (S-PQFP-G100)

PowerPAD™ PLASTIC QUAD FLATPACK

#### THERMAL INFORMATION