# TCAN1043A-Q1 Automotive Low-Power Fault Protected CAN FD Transceiver With Sleep Mode

## 1 Features

- AEC Q100 Qualified for automotive applications

- **Functional Safety-Capable**

- Documentation available to aid in functional safety system design

- Meets the requirements of ISO 11898-2:2016

- Wide input operational voltage range

- Supports classic CAN and CAN FD up to 8Mbps (TCAN1043A-Q1 or 5Mbps (TCAN1043AT-Q1)

- $V_{IO}$  level shifting supports: 1.7V to 5.5V

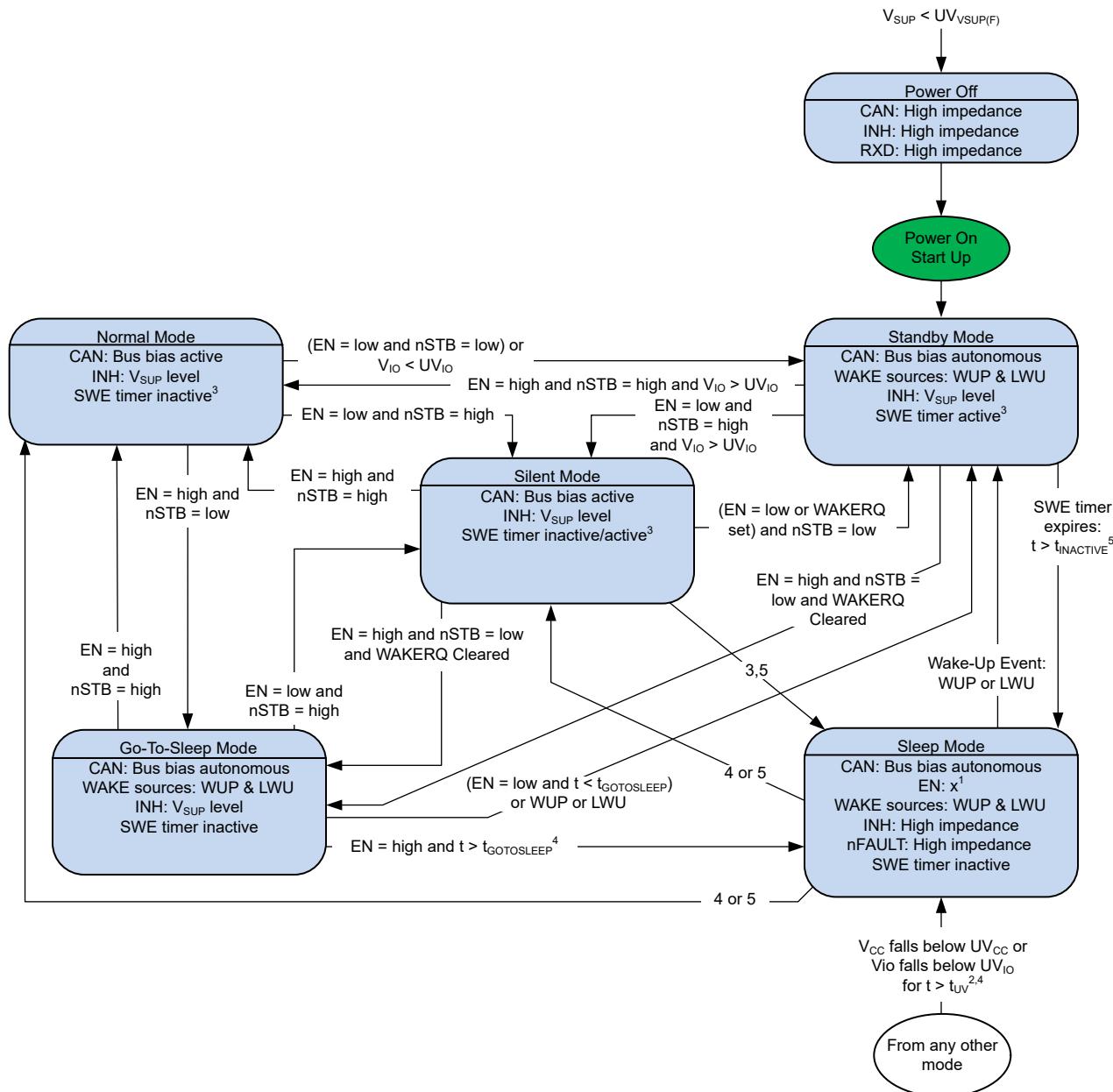

- Operating modes:

- Normal mode

- Silent mode

- Standby mode

- Low-power sleep mode

- High-voltage INH output for system power control

- Local wake-up support via the WAKE pin

- Sleep Wake Error (SWE) timer enables safe transition from standby mode to sleep mode in the event of a system power failure or software fault

- Allows for extended power-up time

- Defined behavior when unpowered

- Bus and IO terminals are high impedance (no load to operating bus or application)

- Protection features:

- $\pm 58V$  CAN bus fault tolerant

- Load dump support on  $V_{SUP}$

- IEC ESD protection

- Under-voltage protection

- Thermal shutdown protection

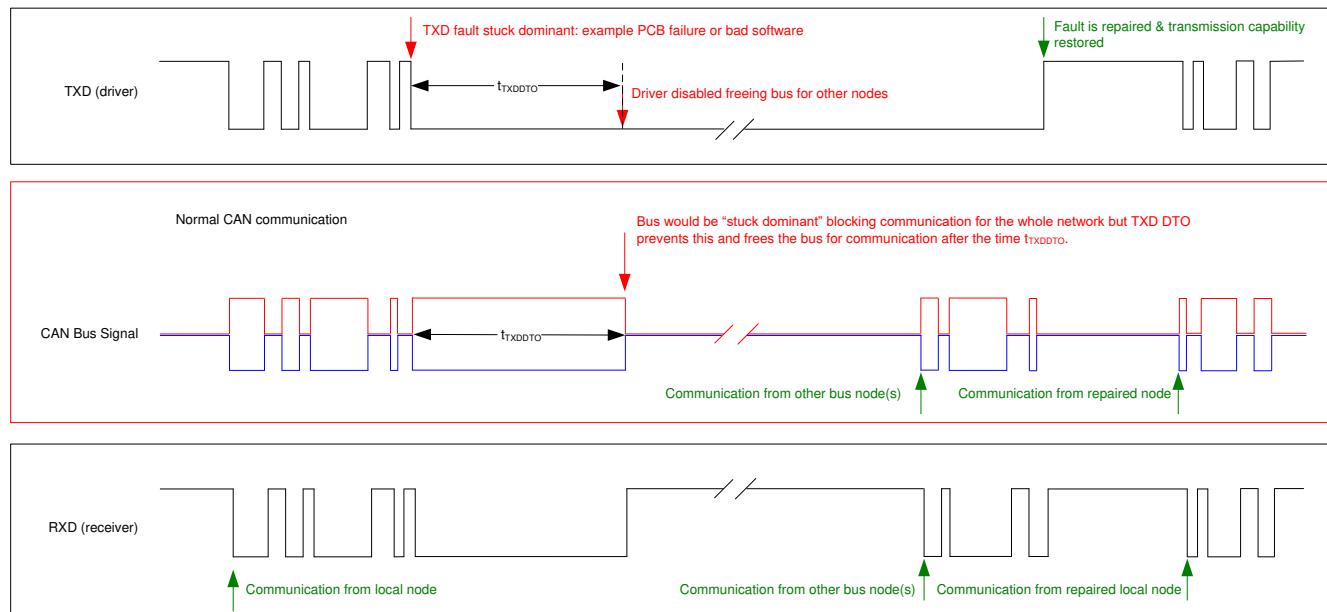

- TXD dominant state timeout (TXD DTO)

- Available in 14-pin leaded (SOT and SOIC) packages and leadless (VSON) package with wettable flanks for improved automated optical inspection (AOI) capability

## 2 Applications

- Body electronics and lighting

- Automotive gateway

- Advanced driver assistance systems (ADAS)

- Infotainment and cluster

- Hybrid, electric & powertrain systems

- Personal transport vehicles - electric bike

- Industrial transportation

## 3 Description

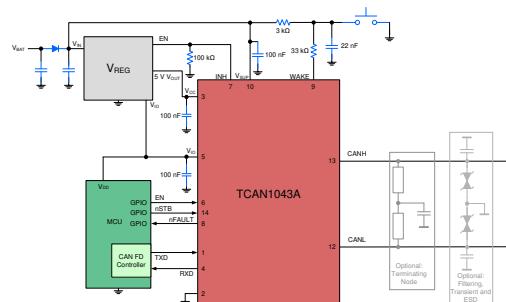

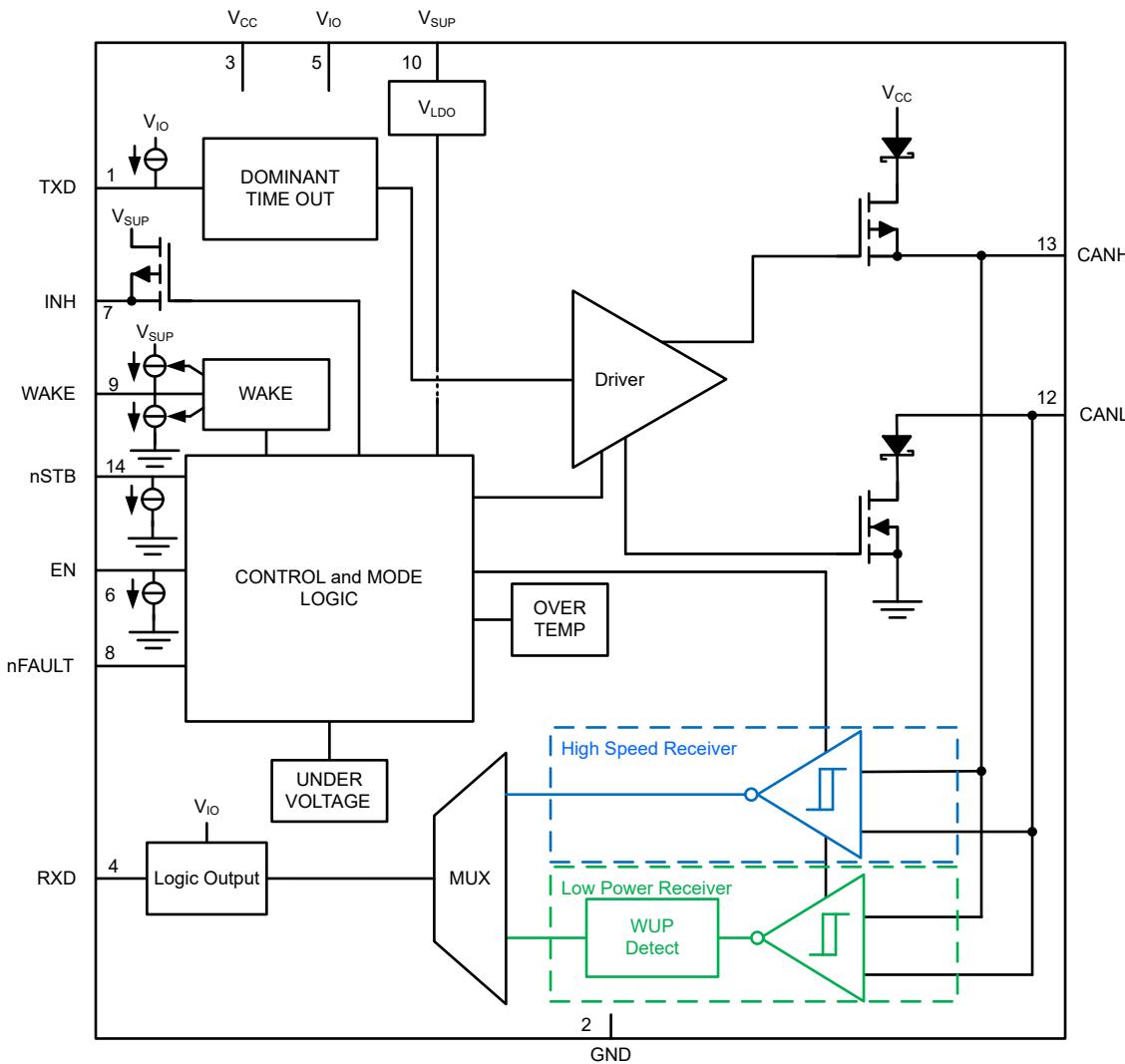

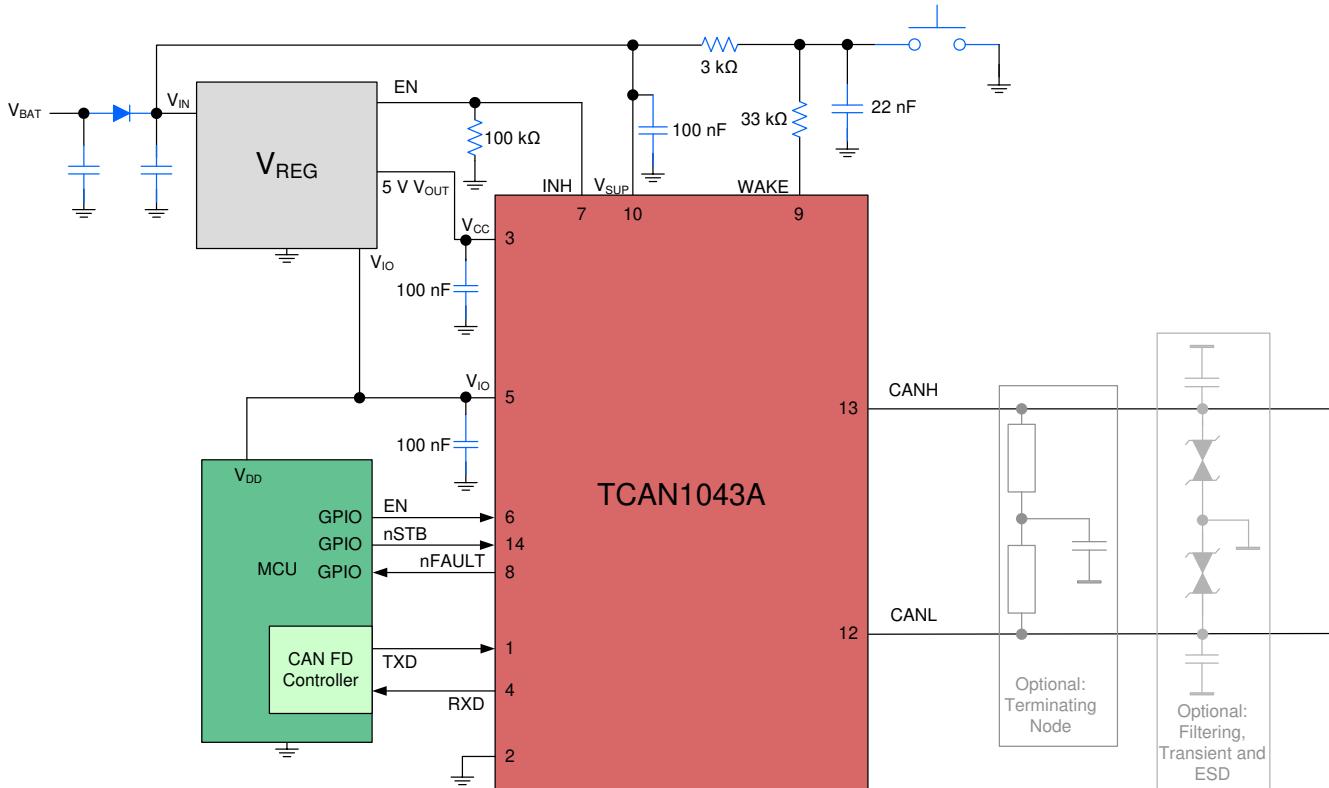

The TCAN1043A-Q1 is a high-speed Controller Area Network (CAN) transceiver that meets the physical layer requirements of the ISO 11898-2:2016 high-speed CAN specification. The device supports both classical CAN and CAN FD data rates up to 8 megabits per second (Mbps) (TCAN1043A-Q1) or 5Mbps (TCAN1043AT-Q1).

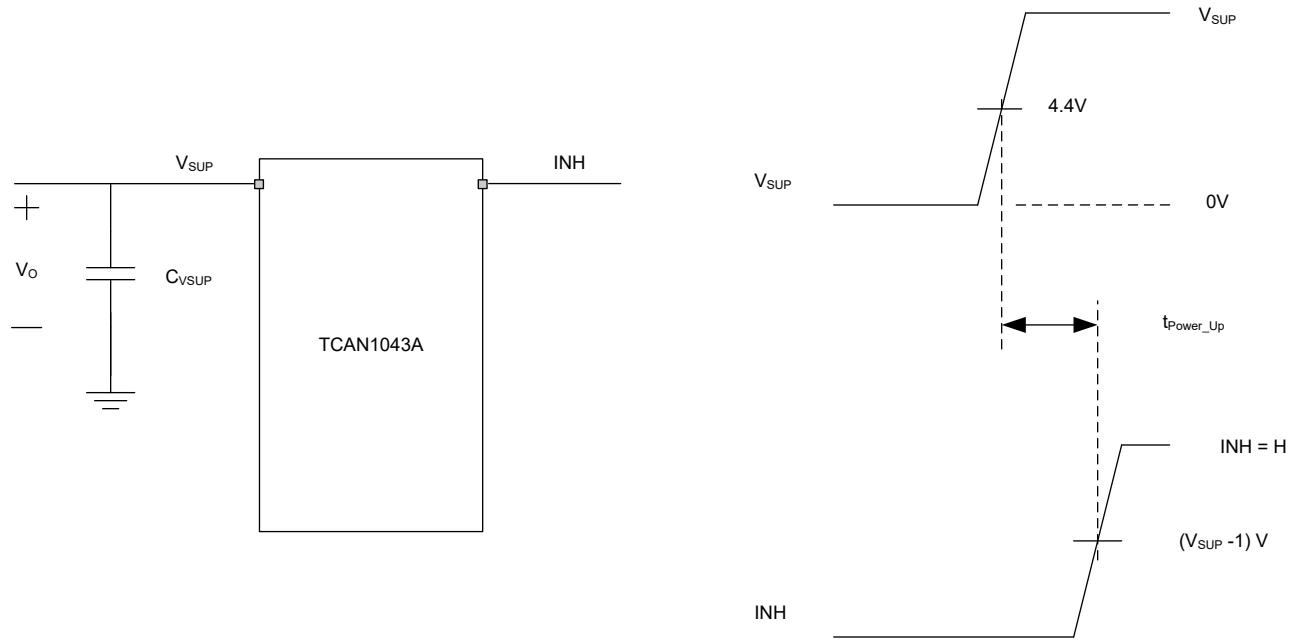

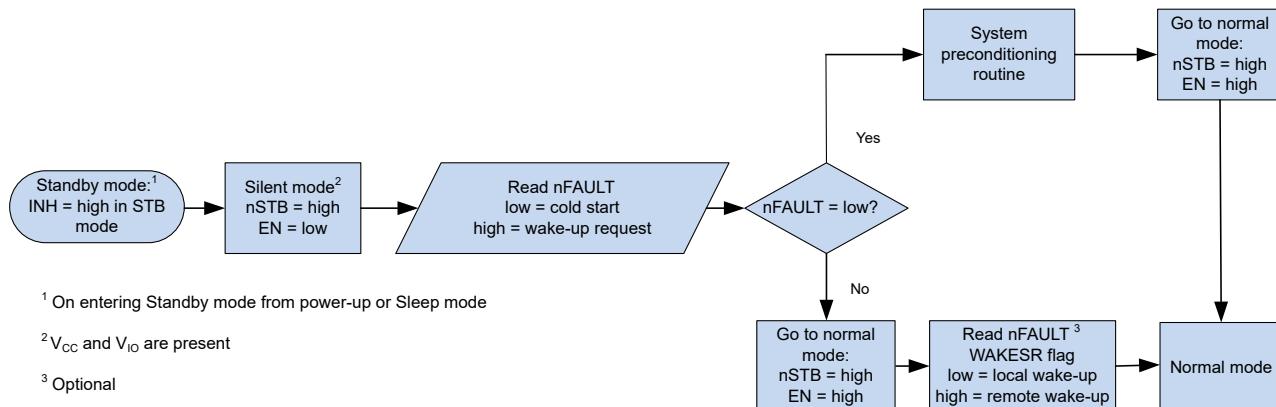

The TCAN1043A-Q1 allows for system-level reductions in battery current consumption by selectively enabling the various power supplies that may be present on a system via the INH output pin. This allows a low-current sleep state in which power is gated to all system components except for the TCAN1043A-Q1, while monitoring the CAN bus. When a wake-up event is detected, the TCAN1043A-Q1 initiates system start-up by driving INH high.

The TCAN1043A-Q1 features an SWE timer that enables a safe transition to Sleep mode after 4 minutes ( $t_{INACTIVE}$ ) of inactivity in Standby mode. Making sure the device is transitioned to low-power Sleep mode if the MCU fails to transition the device to Normal mode.

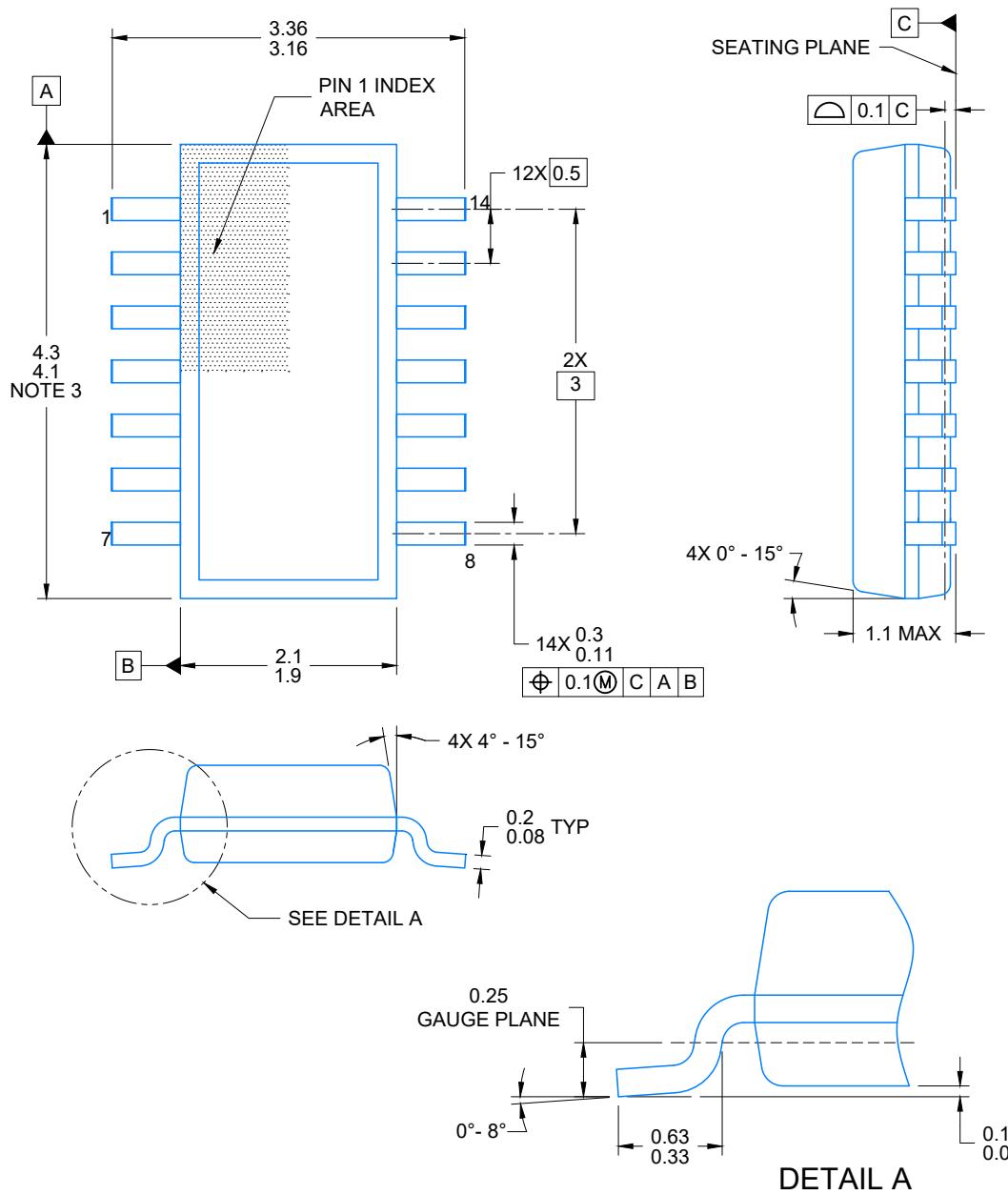

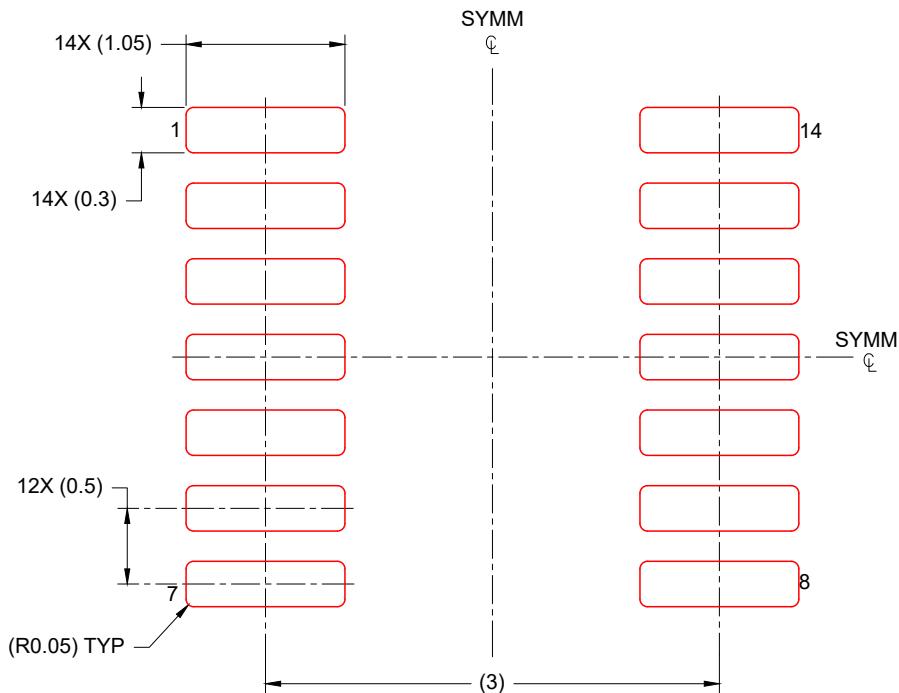

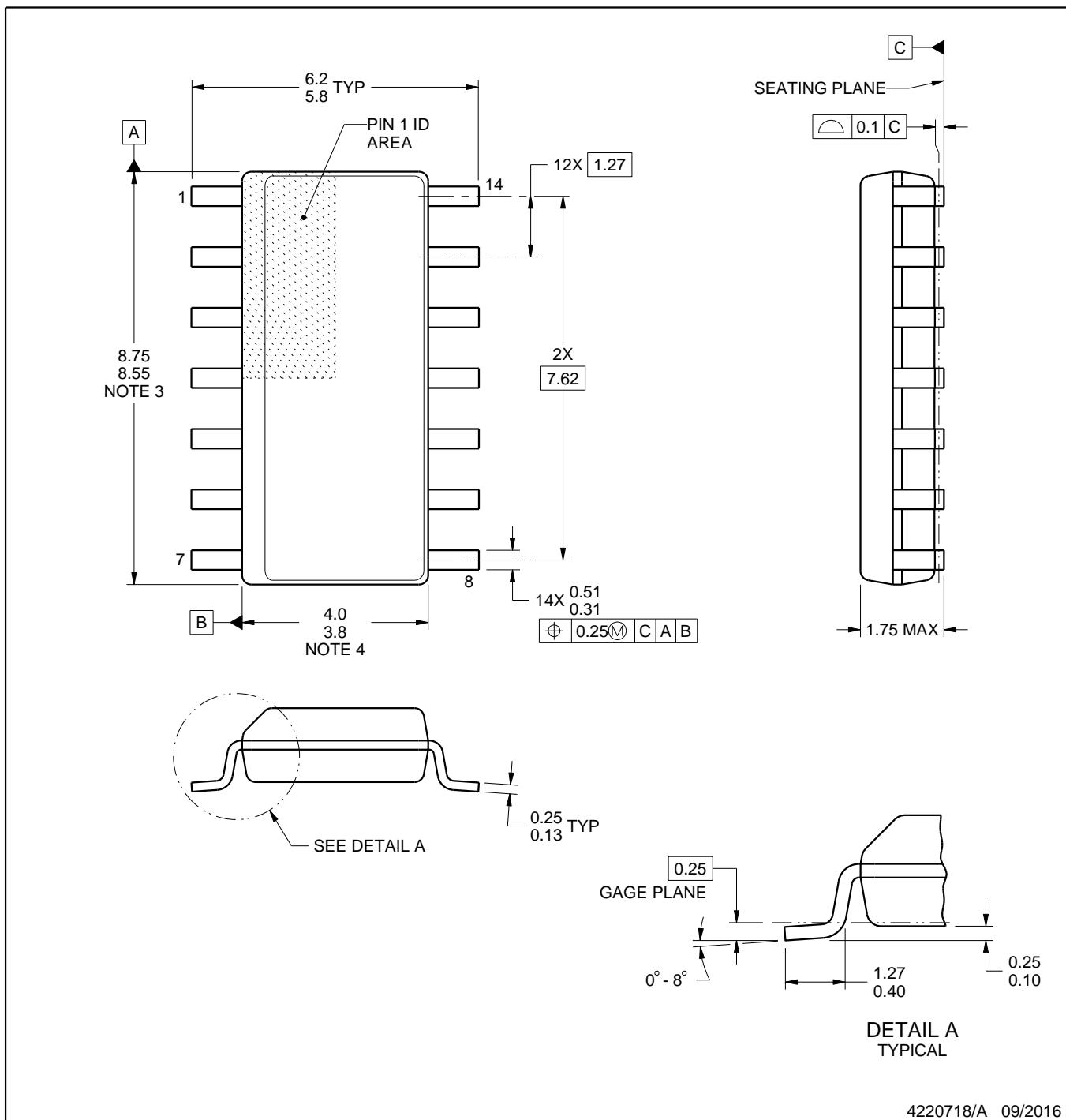

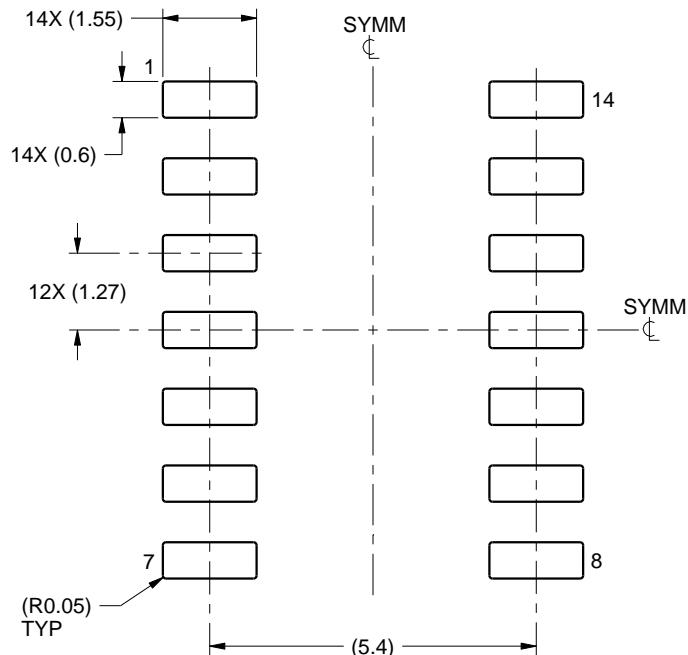

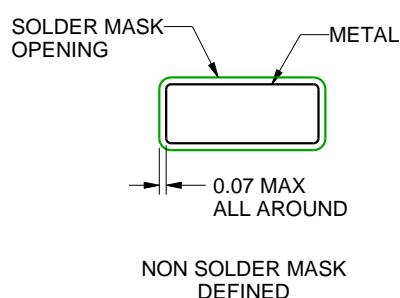

### Package Information

| PART NUMBER   | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|---------------|------------------------|-----------------------------|

| TCAN1043A-Q1  | SOT (DYY)              | 4.2mm x 3.26mm              |

|               | SOIC (D)               | 8.65mm x 6mm                |

|               | VSON (DMT)             | 4.5mm x 3mm                 |

| TCAN1043AT-Q1 | SOIC (D)               | 8.65mm x 6mm                |

|               | VSON (DMT)             | 4.5mm x 3mm                 |

(1) For more information, see [Section 11](#).

(2) The package size (length x width) is a nominal value and includes pins, where applicable.

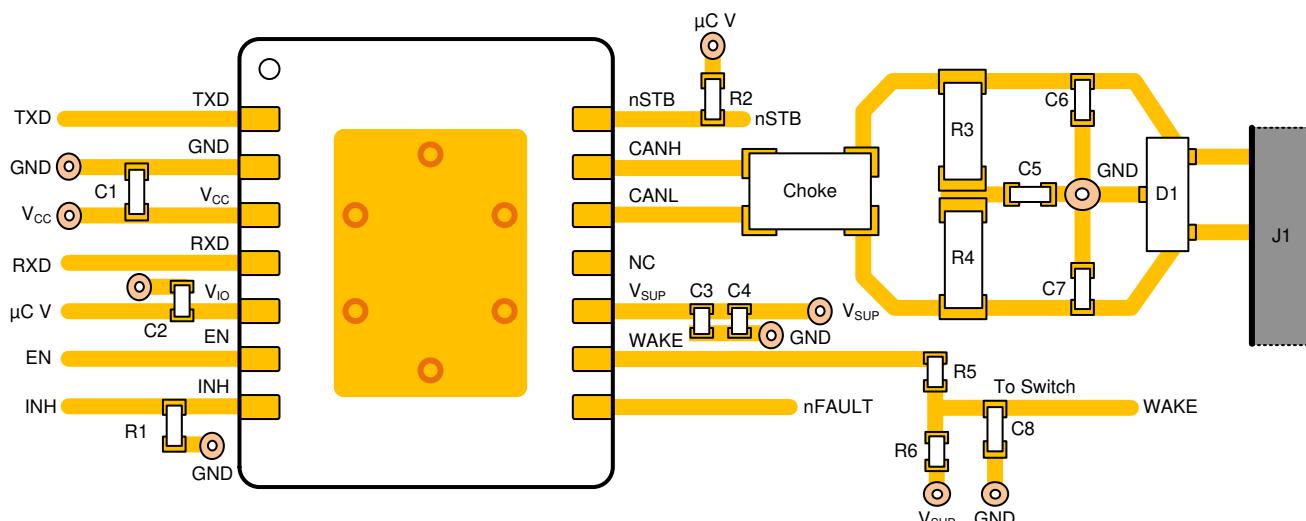

**Simplified Schematic**

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

## Table of Contents

|                                                 |           |                                                         |           |

|-------------------------------------------------|-----------|---------------------------------------------------------|-----------|

| <b>1 Features.....</b>                          | <b>1</b>  | 7.1 Overview.....                                       | <b>19</b> |

| <b>2 Applications.....</b>                      | <b>1</b>  | 7.2 Functional Block Diagram.....                       | <b>19</b> |

| <b>3 Description.....</b>                       | <b>1</b>  | 7.3 Feature Description.....                            | <b>20</b> |

| <b>4 Pin Configuration and Functions.....</b>   | <b>3</b>  | 7.4 Device Functional Modes.....                        | <b>27</b> |

| <b>5 Specifications.....</b>                    | <b>4</b>  | <b>8 Application Information Disclaimer.....</b>        | <b>38</b> |

| 5.1 Absolute Maximum Ratings.....               | 4         | 8.1 Application Information.....                        | 38        |

| 5.2 ESD Ratings.....                            | 4         | 8.2 Power Supply Recommendations.....                   | 40        |

| 5.3 ESD Ratings - IEC Specifications.....       | 4         | 8.3 Layout.....                                         | 41        |

| 5.4 Recommended Operating Conditions.....       | 5         | <b>9 Device and Documentation Support.....</b>          | <b>42</b> |

| 5.5 Thermal Information.....                    | 5         | 9.1 Documentation Support.....                          | 42        |

| 5.6 Power Dissipation Ratings.....              | 6         | 9.2 Receiving Notification of Documentation Updates.... | 42        |

| 5.7 Power Supply Characteristics.....           | 6         | 9.3 Support Resources.....                              | 42        |

| 5.8 Electrical Characteristics.....             | 8         | 9.4 Trademarks.....                                     | 42        |

| 5.9 Timing Requirements.....                    | 10        | 9.5 Electrostatic Discharge Caution.....                | 42        |

| 5.10 Switching Characteristics.....             | 12        | 9.6 Glossary.....                                       | 42        |

| 5.11 Typical Characteristics.....               | 14        | <b>10 Revision History.....</b>                         | <b>42</b> |

| <b>6 Parameter Measurement Information.....</b> | <b>15</b> | <b>11 Mechanical, Packaging, and Orderable</b>          |           |

| <b>7 Detailed Description.....</b>              | <b>19</b> | <b>Information.....</b>                                 | <b>43</b> |

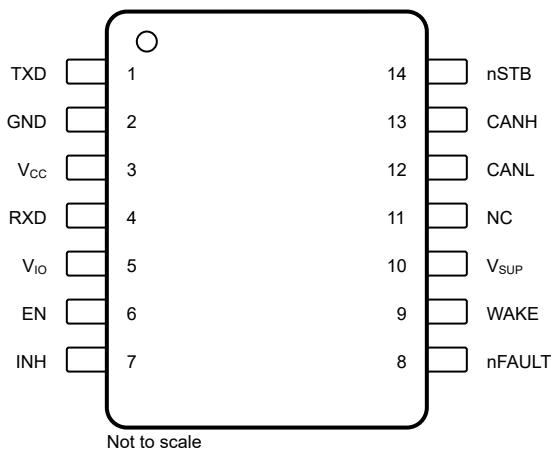

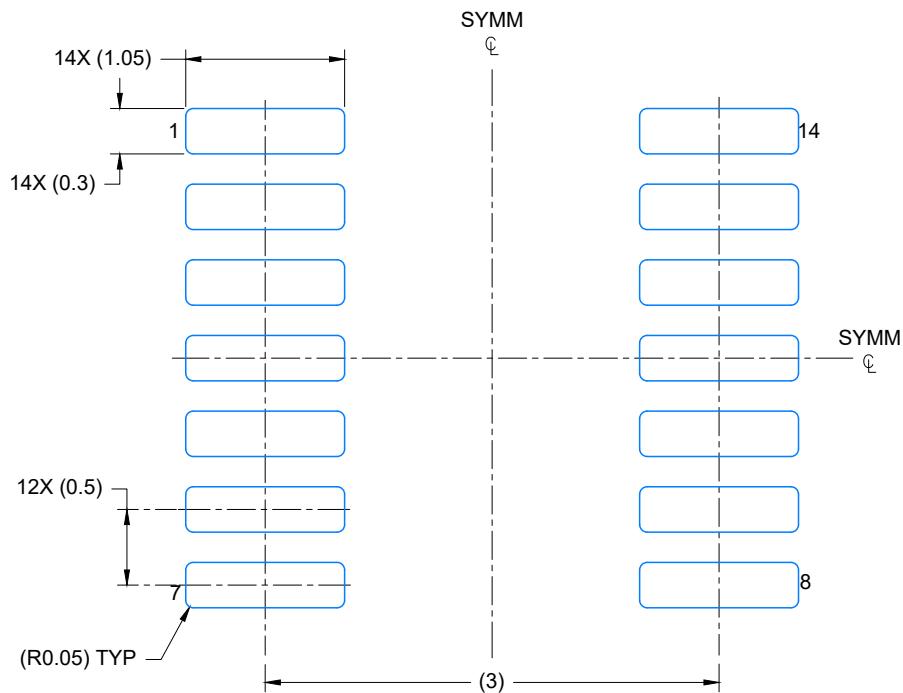

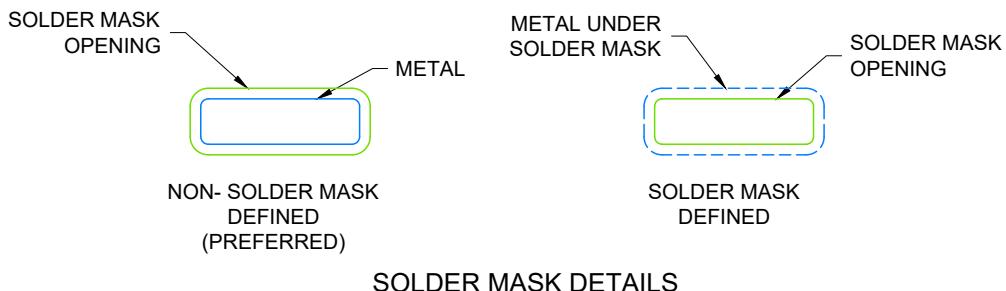

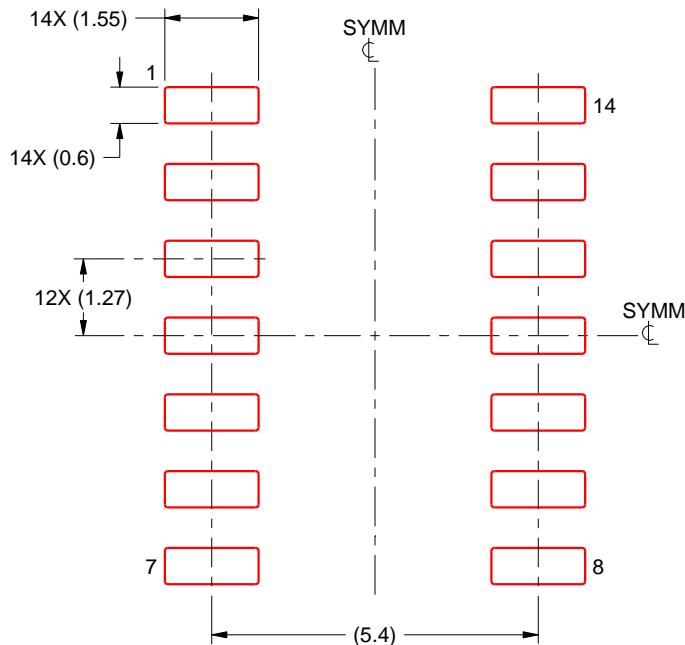

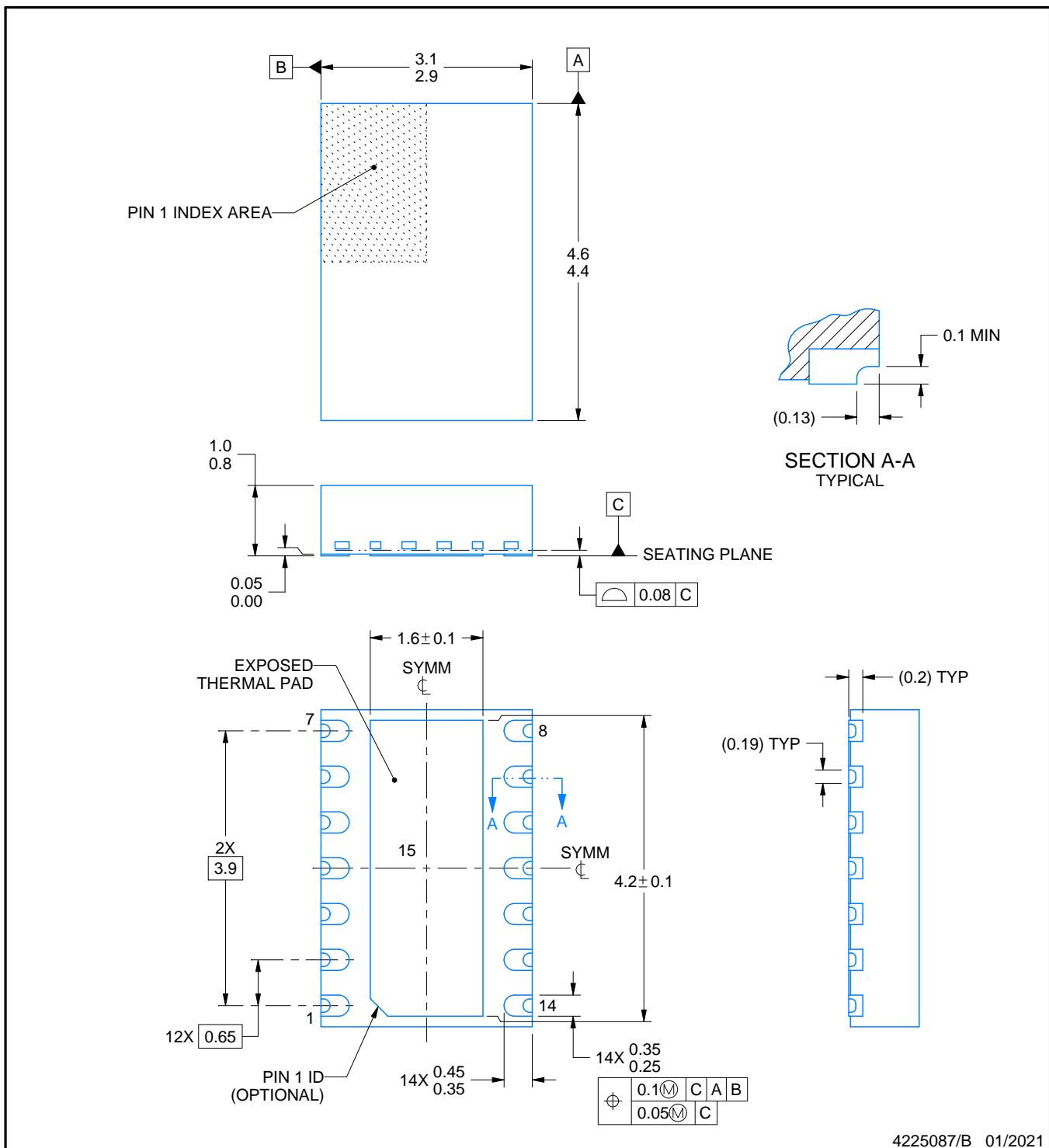

## 4 Pin Configuration and Functions

**Figure 4-1. D and DYY Packages, 14 Pin (SOIC) and (SOT) (Top View)**

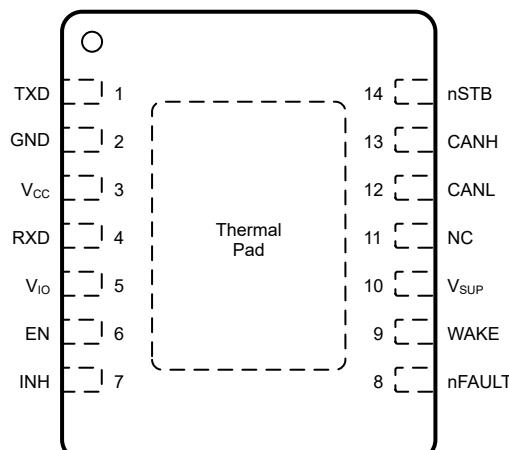

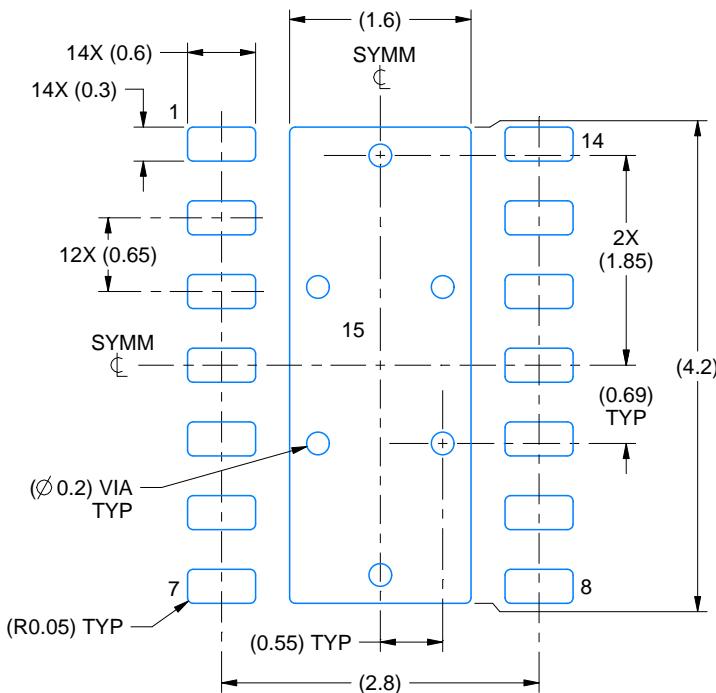

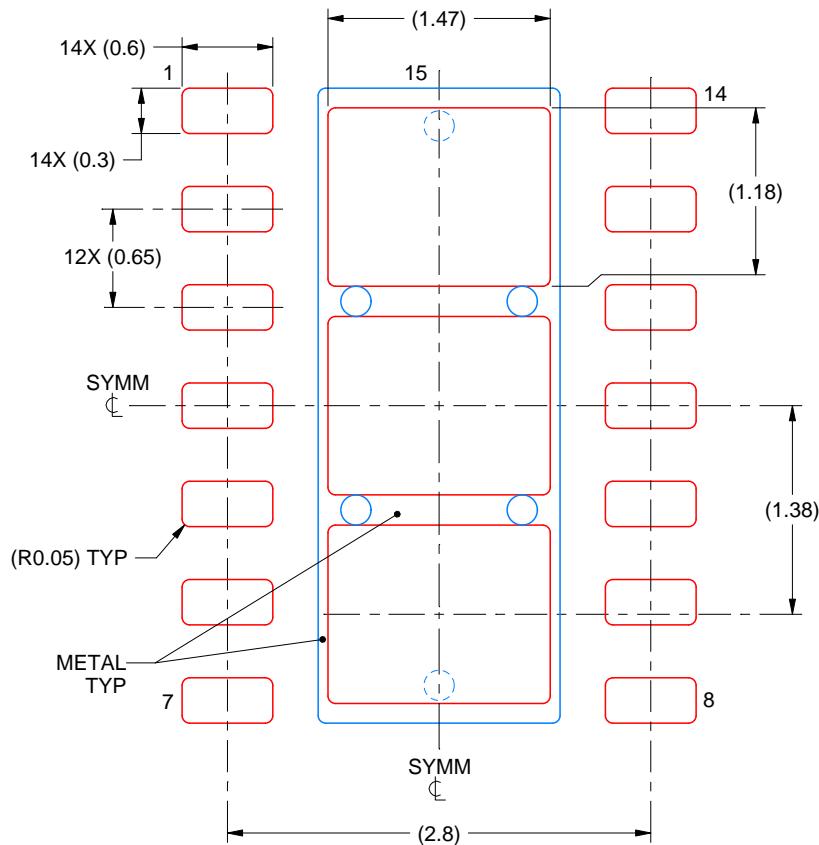

**Figure 4-2. DMT Package, 14 Pin (VSON) (Top View)**

| PINS             |     | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                |

|------------------|-----|---------------------|--------------------------------------------------------------------------------------------|

| NAME             | NO. |                     |                                                                                            |

| TXD              | 1   | I                   | CAN transmit data input, integrated pull-up                                                |

| GND              | 2   | GND                 | Ground connection                                                                          |

| V <sub>CC</sub>  | 3   | P                   | 5V transceiver supply                                                                      |

| RXD              | 4   | O                   | CAN receive data output, tri-state when V <sub>IO</sub> < UV <sub>IO</sub>                 |

| V <sub>IO</sub>  | 5   | P                   | I/O supply voltage                                                                         |

| EN               | 6   | I                   | Enable input for mode control, integrated pull-down                                        |

| INH              | 7   | O                   | Inhibit pin to control system voltage regulators and supplies, high-voltage                |

| nFAULT           | 8   | O                   | Fault output, inverted logic                                                               |

| WAKE             | 9   | I                   | Local WAKE input terminal, high voltage                                                    |

| V <sub>SUP</sub> | 10  | P                   | High-voltage supply from battery                                                           |

| NC               | 11  | NC                  | No connect, internally not connected                                                       |

| CANL             | 12  | I/O                 | Low-level CAN bus input/output line                                                        |

| CANH             | 13  | I/O                 | High-level CAN bus input/output line                                                       |

| nSTB             | 14  | I                   | Standby mode control input, integrated pull-down                                           |

| Thermal Pad      | —   | —                   | Connect the thermal pad to the printed circuit board (PCB) ground plane for thermal relief |

(1) I = input, O = output, P = power, GND = ground, NC = not connected

## 5 Specifications

### 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                       |                                                                                           | MIN  | MAX                                           | UNIT |

|-----------------------|-------------------------------------------------------------------------------------------|------|-----------------------------------------------|------|

| V <sub>SUP</sub>      | Supply voltage <sup>(2)</sup>                                                             | -0.3 | 45                                            | V    |

| V <sub>CC</sub>       | Supply voltage                                                                            | -0.3 | 6                                             | V    |

| V <sub>IO</sub>       | Supply voltage I/O level shifter                                                          | -0.3 | 6                                             | V    |

| V <sub>BUS</sub>      | CAN bus I/O voltage (CANH, CANL)                                                          | -58  | 58                                            | V    |

| V <sub>DIFF</sub>     | CAN bus differential voltage (V <sub>DIFF</sub> = V <sub>CANH</sub> - V <sub>CANL</sub> ) | -58  | 58                                            | V    |

| V <sub>WAKE</sub>     | WAKE input voltage                                                                        | -45  | 45 and V <sub>I</sub> ≤ V <sub>SUP</sub> +0.3 | V    |

| V <sub>INH</sub>      | INH pin voltage                                                                           | -0.3 | 45 and V <sub>O</sub> ≤ V <sub>SUP</sub> +0.3 | V    |

| V <sub>LOGIC</sub>    | Logic pin voltage                                                                         | -0.3 | 6                                             | V    |

| I <sub>O(LOGIC)</sub> | Logic pin output current                                                                  |      | 8                                             | mA   |

| I <sub>O(INH)</sub>   | Inhibit pin output current                                                                |      | 6                                             | mA   |

| I <sub>O(WAKE)</sub>  | WAKE pin output current                                                                   |      | 3                                             | mA   |

| T <sub>J</sub>        | Junction temperature                                                                      | -40  | 165                                           | °C   |

| T <sub>STG</sub>      | Storage temperature                                                                       | -65  | 150                                           | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute maximum ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If briefly operating outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not sustain damage, but it may not be fully functional. Operating the device in this manner may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) Able to support load dumps of up to 45 V for 300ms

### 5.2 ESD Ratings

|                  |                         |                                                         | VALUE                                                          | UNIT   |   |

|------------------|-------------------------|---------------------------------------------------------|----------------------------------------------------------------|--------|---|

| V <sub>ESD</sub> | Electrostatic discharge | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> | V <sub>SUP</sub> , CANH, CANL, and WAKE with respect to ground | ± 8000 | V |

|                  |                         |                                                         | All pins except V <sub>SUP</sub> , CANH, CANL, and WAKE        | ± 4000 | V |

|                  |                         | Charged device model (CDM), per AEC Q100-011            | All pins                                                       | ± 750  | V |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 5.3 ESD Ratings - IEC Specifications

|                  |                         |                                                         |                                                                       | VALUE   | UNIT |

|------------------|-------------------------|---------------------------------------------------------|-----------------------------------------------------------------------|---------|------|

| V <sub>ESD</sub> | Electrostatic discharge | CANH, CANL, V <sub>SUP</sub> , and WAKE terminal to GND | Unpowered Contact Discharge per ISO 10605 <sup>(1)</sup>              | ± 8000  | V    |

| V <sub>ESD</sub> | Electrostatic discharge | CANH and CANL terminal to GND                           | SAE J2962-2 per ISO 10605<br>Powered Contact Discharge <sup>(2)</sup> | ± 8000  | V    |

| V <sub>ESD</sub> | Electrostatic discharge | CANH and CANL terminal to GND                           | SAE J2962-2 per ISO 10605<br>Powered Air discharge <sup>(2)</sup>     | ± 15000 | V    |

## 5.3 ESD Ratings - IEC Specifications (continued)

|            |                                                                                   |                     | VALUE                                                                                     | UNIT     |

|------------|-----------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------|----------|

| $V_{TRAN}$ | Transient voltage per ISO-7637-2 (1)<br><br>CAN, $V_{SUP}$ , WAKE terminal to GND | Pulse 1             | - 100                                                                                     | V        |

|            |                                                                                   | Pulse 2             | 75                                                                                        | V        |

|            |                                                                                   | Pulse 3a            | - 150                                                                                     | V        |

|            |                                                                                   | Pulse 3b            | 100                                                                                       | V        |

|            | Transient voltage per ISO-7637-3 (2)                                              | CAN terminal to GND | Direct coupling capacitor "slow transient pulse" with 100 nF coupling capacitor - powered | $\pm 30$ |

- (1) Results given here are specific to the IEC 62228-3 Integrated circuits – EMC evaluation of transceivers – Part 3: CAN transceivers. Testing performed by IBEE Zwickau, EMC report available upon request.

- (2) Results given here are specific to the SAE J2962-2 Communication Transceivers Qualification Requirements - CAN. Testing performed by OEM-approved independent 3<sup>rd</sup> party, EMC report available upon request.

## 5.4 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|               |                                   | MIN | NOM | MAX | UNIT |

|---------------|-----------------------------------|-----|-----|-----|------|

| $V_{SUP}$     | Supply voltage                    | 4.5 | 40  | 40  | V    |

| $V_{IO}$      | I/O supply voltage                | 1.7 | 5.5 | 5.5 | V    |

| $V_{CC}$      | CAN transceiver supply voltage    | 4.5 | 5.5 | 5.5 | V    |

| $I_{OH(DO)}$  | Digital output high-level current | -2  |     |     | mA   |

| $I_{OL(DO)}$  | Digital output low-level current  |     | 2   | 2   | mA   |

| $I_{O(INH)}$  | Inhibit output current            |     | 1   | 1   | mA   |

| $T_J$         | Operating junction temperature    | -40 | 150 | 150 | °C   |

| $T_{SDR}$     | Thermal shutdown                  | 175 |     |     | °C   |

| $T_{SDF}$     | Thermal shutdown release          | 160 |     |     | °C   |

| $T_{SD(HYS)}$ | Thermal shutdown hysteresis       | 10  |     |     | °C   |

## 5.5 Thermal Information

| THERMAL METRIC (1)          |                                              | TCAN1043A-Q1 |      |            | UNIT |

|-----------------------------|----------------------------------------------|--------------|------|------------|------|

|                             |                                              | D (SOIC)     |      | DMT (VSON) |      |

|                             |                                              | 14 PINS      |      | 14 PINS    |      |

| $R_{\Theta JA}$             | Junction-to-ambient thermal resistance       | 87.1         | 39.7 | 91.0       | °C/W |

| $R_{\Theta JC(\text{top})}$ | Junction-to-case (top) thermal resistance    | 41.8         | 41.1 | 41.7       | °C/W |

| $R_{\Theta JB}$             | Junction-to-board thermal resistance         | 43.7         | 15.9 | 25.6       | °C/W |

| $\Psi_{JT}$                 | Junction-to-top characterization parameter   | 8.5          | 0.9  | 25.4       | °C/W |

| $\Psi_{JB}$                 | Junction-to-board characterization parameter | 43.3         | 15.9 | 1.1        | °C/W |

| $R_{\Theta JC(\text{bot})}$ | Junction-to-case (bottom) thermal resistance | N/A          | 6.6  | N/A        | °C/W |

- (1) For more information about traditional and new thermal metrics, see the [Semiconductor and IC Package Thermal Metrics application report](#).

## 5.6 Power Dissipation Ratings

| PARAMETER |                           | TEST CONDITIONS                                                                                                                                                                                                                                                                                                               | POWER DISSIPATION | UNIT |

|-----------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|

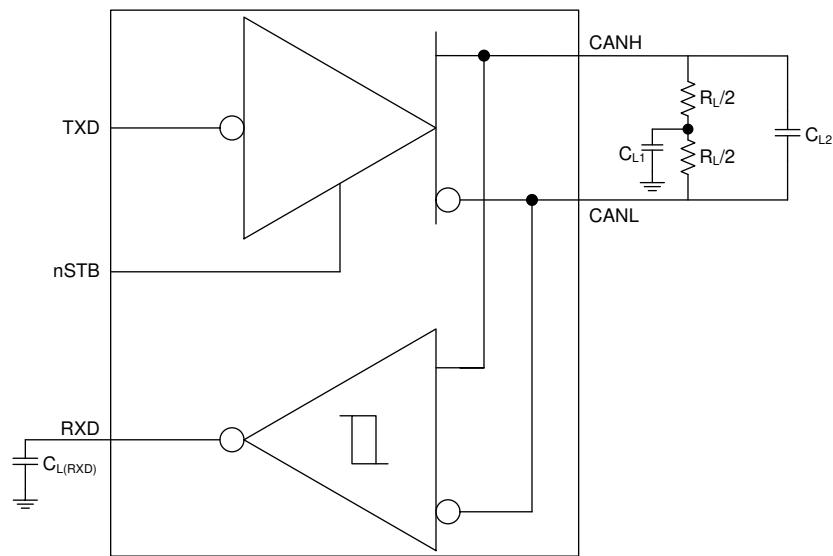

| $P_D$     | Average power dissipation | $V_{SUP} = 14 \text{ V}$ , $V_{CC} = 5 \text{ V}$ , $V_{IO} = 5 \text{ V}$ , $T_J = 27^\circ\text{C}$ , $R_L = 60 \Omega$ , $nSTB = 5 \text{ V}$ , $EN = 5 \text{ V}$ , $C_{L_RXD} = 15 \text{ pF}$ . Typical CAN operating conditions at 500 kbps with 25% transmission (dominant) rate.                                     | 62                | mW   |

|           |                           | $V_{SUP} = 14 \text{ V}$ , $V_{CC} = 5.5 \text{ V}$ , $V_{IO} = 5.5 \text{ V}$ , $T_J = 150^\circ\text{C}$ , $R_L = 50 \Omega$ , $nSTB = 5.5 \text{ V}$ , $EN = 5.5 \text{ V}$ , $C_{L_RXD} = 15 \text{ pF}$ . Typical high load CAN operating conditions at 1 Mbps with 50% transmission (dominant) rate and loaded network. | 135               | mW   |

## 5.7 Power Supply Characteristics

Over recommended operating conditions with  $T_J = -40^\circ\text{C}$  to  $150^\circ\text{C}$ , unless otherwise noted. All typical values are taken at  $25^\circ\text{C}$ ,  $V_{SUP} = 12 \text{ V}$ ,  $V_{IO} = 3.3 \text{ V}$ ,  $V_{CC} = 5 \text{ V}$  and  $R_L = 60 \Omega$

| PARAMETER                                         |                                                                              | TEST CONDITIONS                                                                                                                                       | MIN  | TYP  | MAX | UNIT |

|---------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|------|

| <b>Supply Voltage and Current Characteristics</b> |                                                                              |                                                                                                                                                       |      |      |     |      |

| $I_{SUP\_NORMAL}$                                 | Supply current<br>CAN active                                                 | Normal mode, silent mode, and go-to-sleep mode                                                                                                        |      | 130  |     | µA   |

| $I_{SUP\_STBY}$                                   | Supply current, Standby mode<br>CAN autonomous: inactive <sup>(2)</sup>      |                                                                                                                                                       |      | 60   |     | µA   |

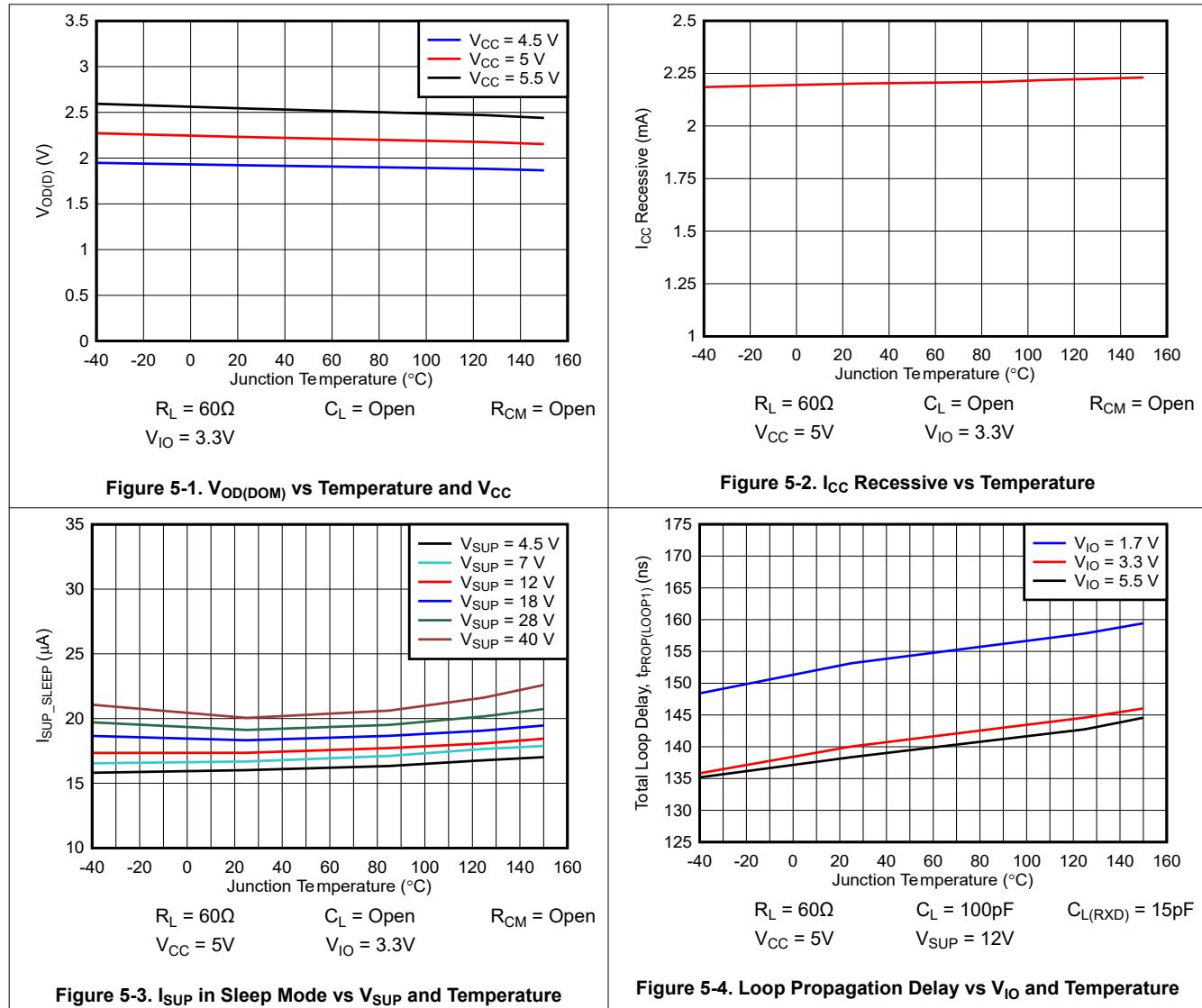

| $I_{SUP\_SLEEP}$                                  | Supply current, Sleep mode<br>CAN autonomous: inactive <sup>(2)</sup>        |                                                                                                                                                       | 18   | 30   |     | µA   |

| $I_{SUP\_BIAS}$                                   | Additional supply current when in CAN autonomous: active ( $I_{SUP(BIAS)}$ ) | $5.5 \text{ V} < V_{SUP} \leq 28 \text{ V}$ <a href="#">See Figure 6-3</a>                                                                            |      | 50   |     | µA   |

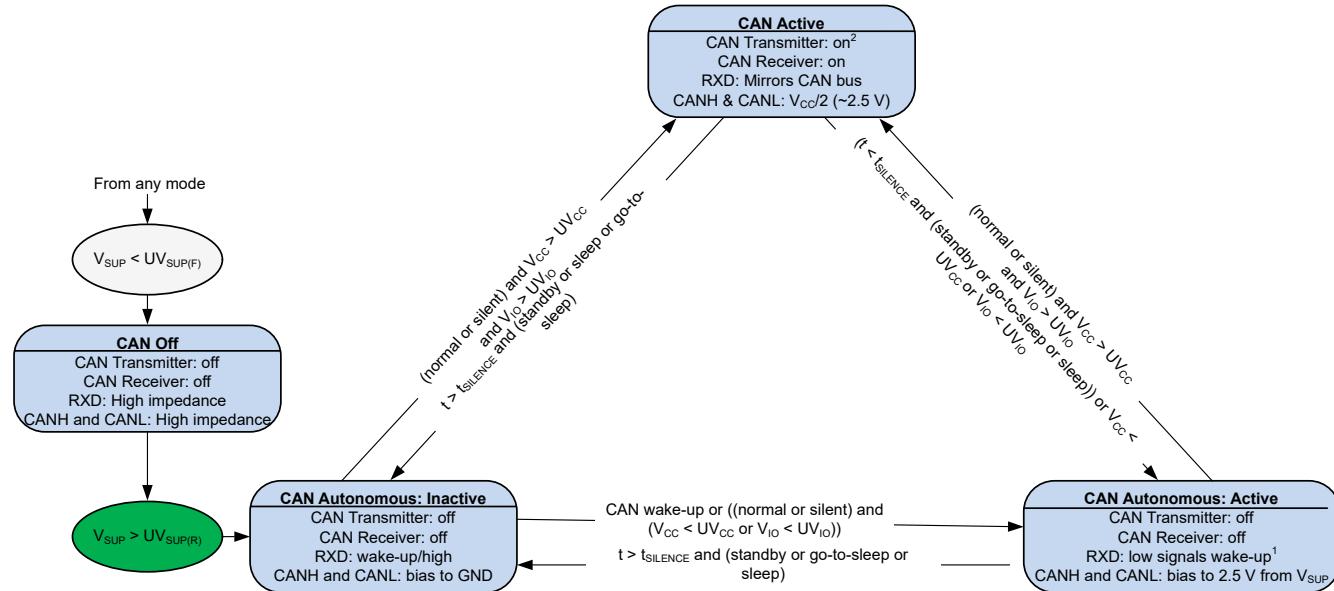

| $UV_{SUP(R)}$                                     | Undervoltage $V_{SUP}$ threshold rising                                      |                                                                                                                                                       | 3.85 | 4.4  |     | V    |

| $UV_{SUP(F)}$                                     | Undervoltage $V_{SUP}$ threshold falling                                     |                                                                                                                                                       | 3.5  | 4.25 |     | V    |

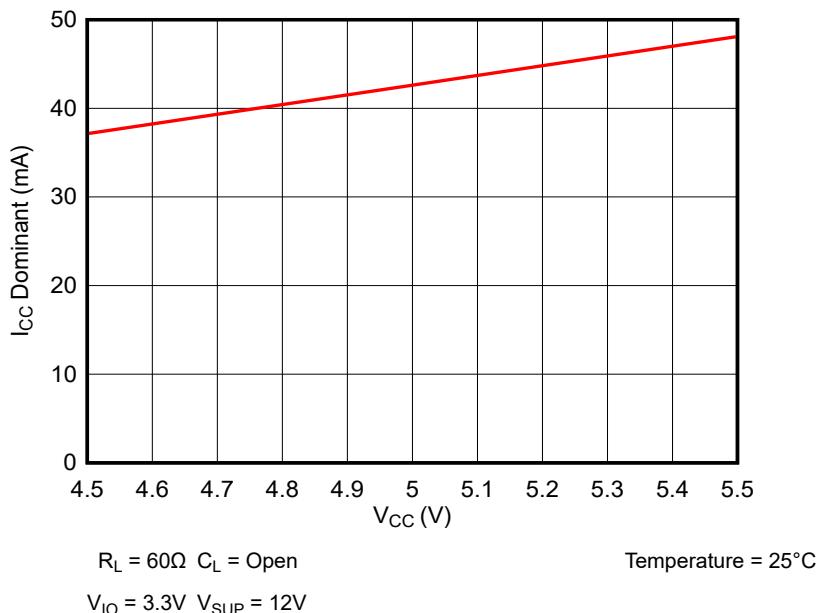

| $I_{CC\_NORMAL}$                                  | Supply current<br>CAN active: dominant                                       | Normal mode<br>$TXD = 0 \text{ V}$ , $R_L = 60 \Omega$ , $C_L = \text{open}$<br><a href="#">See Figure 6-3</a>                                        |      | 60   |     | mA   |

|                                                   |                                                                              | Normal mode<br>$TXD = 0 \text{ V}$ , $R_L = 50 \Omega$ , $C_L = \text{open}$<br><a href="#">See Figure 6-3</a>                                        |      | 70   |     | mA   |

|                                                   | $V_{CC}$ supply current normal mode<br>Dominant with bus fault               | Normal mode<br>$TXD = 0 \text{ V}$ , $R_L = \text{open}$ , $C_L = \text{open}$ , $CANH = -25 \text{ V}$<br><a href="#">See Figure 6-3</a>             |      | 110  |     | mA   |

|                                                   | Supply current<br>CAN active: recessive                                      | Normal mode<br>$TXD = 0 \text{ V}$ , $R_L = 50 \Omega$ , $C_L = \text{open}$<br><a href="#">See Figure 6-3</a>                                        |      | 5    |     | mA   |

| $I_{CC\_STBY}$                                    | Supply current, Standby mode<br>CAN autonomous: inactive                     | $T_J = -40^\circ\text{C}$ to $85^\circ\text{C}$<br>$EN = nSTB = 0 \text{ V}$<br><a href="#">See Figure 6-3</a>                                        |      | 2    |     | µA   |

|                                                   |                                                                              | Standby mode<br>$EN = nSTB = 0 \text{ V}$<br><a href="#">See Figure 6-3</a>                                                                           |      | 5    |     | µA   |

| $I_{CC\_SILENT}$                                  | Supply current, Silent and go-to-sleep mode                                  | Silent and go-to-sleep mode<br>$TXD = nSTB = V_{IO}$ , $R_L = 50 \Omega$ , $C_L = \text{open}$<br><a href="#">See Figure 6-3</a>                      |      | 2.5  |     | mA   |

| $I_{CC\_SLEEP}$                                   | Supply current, Sleep mode<br>CAN autonomous: inactive                       | Sleep mode $T_J = -40^\circ\text{C}$ to $85^\circ\text{C}$<br>$EN = 0 \text{ V}$ or $V_{IO}$ , $nSTB = 0 \text{ V}$<br><a href="#">See Figure 6-3</a> |      | 2    |     | µA   |

|                                                   |                                                                              | Sleep mode<br>$EN = 0 \text{ V}$ or $V_{IO}$ , $nSTB = 0 \text{ V}$<br><a href="#">See Figure 6-3</a>                                                 |      | 5    |     | µA   |

| $UV_{CC(R)}$                                      | Undervoltage $V_{CC}$ threshold rising                                       |                                                                                                                                                       | 4.1  | 4.4  |     | V    |

| $UV_{CC(F)}$                                      | Undervoltage $V_{CC}$ threshold falling                                      |                                                                                                                                                       | 3.5  | 3.9  |     | V    |

| $V_{HYS(UVCC)}$                                   | Hysteresis voltage on $UV_{CC}$                                              |                                                                                                                                                       | 50   | 240  | 320 | mV   |

## 5.7 Power Supply Characteristics (continued)

Over recommended operating conditions with  $T_J = -40^\circ\text{C}$  to  $150^\circ\text{C}$ , unless otherwise noted. All typical values are taken at  $25^\circ\text{C}$ ,  $V_{\text{SUP}} = 12 \text{ V}$ ,  $V_{\text{IO}} = 3.3 \text{ V}$ ,  $V_{\text{CC}} = 5 \text{ V}$  and  $R_L = 60 \Omega$

| PARAMETER                        |                                                 | TEST CONDITIONS                                                                              | MIN | TYP  | MAX  | UNIT          |

|----------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------|-----|------|------|---------------|

| $I_{\text{IO\_NORMAL}}$          | I/O supply current                              | Normal mode<br>RXD floating, TXD = 0 V                                                       |     | 200  |      | $\mu\text{A}$ |

|                                  | I/O supply current                              | Normal mode, standby mode, or go-to-sleep mode<br>RXD floating, TXD = $V_{\text{IO}}$        |     | 5    |      | $\mu\text{A}$ |

| $I_{\text{IO\_SLEEP}}$           | I/O supply current                              | Sleep mode $T_J = -40^\circ\text{C}$ to $85^\circ\text{C}$<br>$n_{\text{STB}} = 0 \text{ V}$ |     | 2.5  |      | $\mu\text{A}$ |

|                                  | I/O supply current                              | Sleep mode<br>$n_{\text{STB}} = 0 \text{ V}$                                                 |     | 5    |      | $\mu\text{A}$ |

| $UV_{\text{IO(R)}}$              | Under voltage $V_{\text{IO}}$ threshold rising  | Ramp up                                                                                      |     | 1.4  | 1.65 | V             |

| $UV_{\text{IO(F)}}$              | Under voltage $V_{\text{IO}}$ threshold falling | Ramp down                                                                                    | 1   | 1.25 |      | V             |

| $V_{\text{HYS}}(UV_{\text{IO}})$ | Hysteresis voltage on $UV_{\text{IO}}$          |                                                                                              | 30  | 60   | 160  | mV            |

- (1)  $I_{\text{SUP(BIAS)}}$  is calculated by subtracting the supply current in CAN autonomous inactive mode from the total supply current in CAN autonomous active mode

- (2) After a valid wake-up, the CAN transceiver switches to CAN autonomous active mode and the  $I_{\text{SUP(BIAS)}}$  current needs to be added to the specified  $I_{\text{SUP}}$  current in CAN autonomous inactive mode.

## 5.8 Electrical Characteristics

Over recommended operating conditions with  $T_J = -40^\circ\text{C}$  to  $150^\circ\text{C}$ , unless otherwise noted. All typical values are taken at  $25^\circ\text{C}$ ,  $V_{\text{SUP}} = 12 \text{ V}$ ,  $V_{\text{IO}} = 3.3 \text{ V}$ ,  $V_{\text{CC}} = 5 \text{ V}$  and  $R_L = 60 \Omega$

| PARAMETER                           |                                                                                                       | TEST CONDITIONS                                                                                                                        |                                                                                                                                                                                                                                  | MIN  | TYP  | MAX  | UNIT |

|-------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

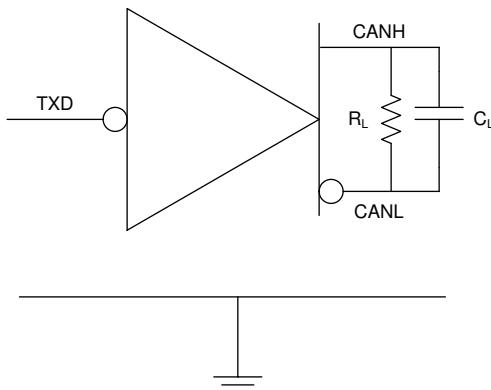

| <b>CAN Driver Characteristics</b>   |                                                                                                       |                                                                                                                                        |                                                                                                                                                                                                                                  |      |      |      |      |

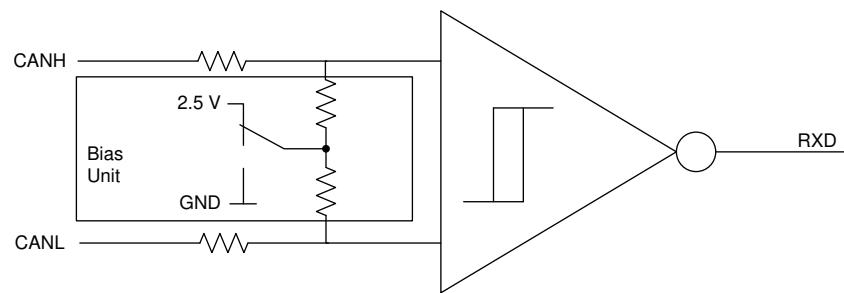

| $V_{O(D)}$                          | Dominant output voltage<br>Bus biasing active                                                         | CANH                                                                                                                                   | TXD = 0 V, $50 \leq R_L \leq 65 \Omega$ , $C_L = \text{open}$ , $R_{CM} = \text{open}$<br>See <a href="#">Figure 6-1</a> and <a href="#">Figure 6-4</a>                                                                          | 2.75 | 4.5  | 4.5  | V    |

|                                     |                                                                                                       | CANL                                                                                                                                   |                                                                                                                                                                                                                                  | 0.5  | 2.25 | 2.25 | V    |

| $V_{O(R)}$                          | Recessive output voltage<br>Bus biasing active                                                        |                                                                                                                                        | TXD = $V_{\text{IO}}$ , $R_L = \text{open}$ (no load), $R_{CM} = \text{open}$<br>See <a href="#">Figure 6-1</a> and <a href="#">Figure 6-4</a>                                                                                   | 2    | 3    | 3    | V    |

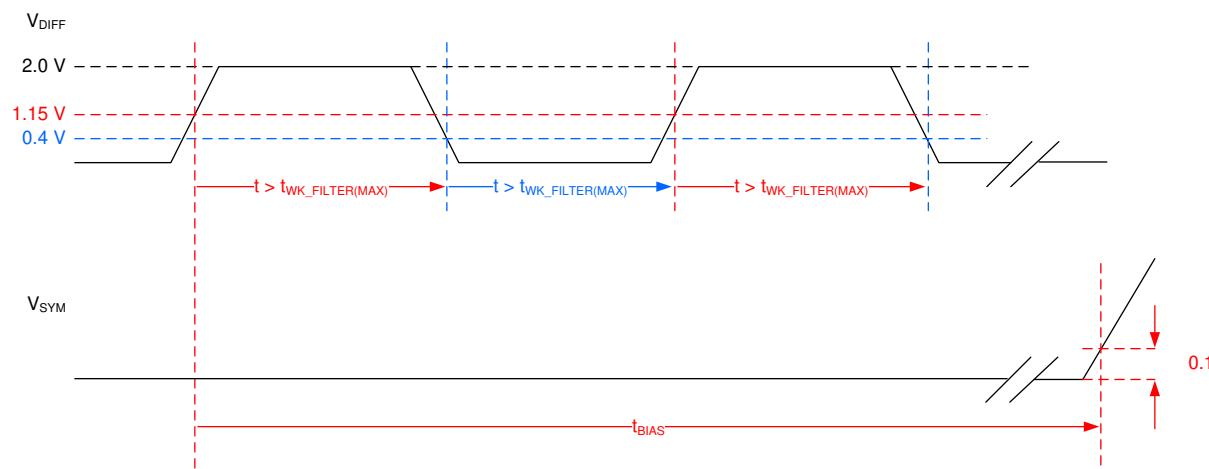

| $V_{\text{SYM}}$                    | Driver symmetry<br>Bus biasing active<br>$(V_{O(\text{CANH})} + V_{O(\text{CANL})}) / V_{\text{CC}}$  |                                                                                                                                        | nSTB = $V_{\text{IO}}$ , $R_L = 60 \Omega$ , $C_{\text{SPLIT}} = 4.7 \text{ nF}$ , $C_L = \text{Open}$ , $R_{CM} = \text{Open}$ , TXD = 250 kHz, 1 MHz, 2.5 MHz<br>See <a href="#">Figure 6-1</a> and <a href="#">Figure 6-4</a> | 0.9  | 1.1  | 1.1  | V/V  |

| $V_{\text{SYM\_DC}}$                | DC Driver symmetry<br>Bus biasing active<br>$V_{\text{CC}} - V_{O(\text{CANH})} - V_{O(\text{CANL})}$ |                                                                                                                                        | nSTB = $V_{\text{IO}}$ , $R_L = 60 \Omega$ , $C_L = \text{open}$<br>See <a href="#">Figure 6-1</a> and <a href="#">Figure 6-4</a>                                                                                                | -400 | 400  | 400  | mV   |

| $V_{OD(\text{DOM})}$                | Differential output voltage<br>Bus biasing active<br>Dominant                                         | CANH - CANL                                                                                                                            | nSTB = $V_{\text{IO}}$ , TXD = 0 V, $50 \Omega \leq R_L \leq 65 \Omega$ , $C_L = \text{open}$<br>See <a href="#">Figure 6-1</a> and <a href="#">Figure 6-4</a>                                                                   | 1.5  | 3    | 3    | V    |

|                                     |                                                                                                       | CANH - CANL                                                                                                                            | nSTB = $V_{\text{IO}}$ , TXD = 0 V, $45 \Omega \leq R_L \leq 70 \Omega$ , $C_L = \text{open}$<br>See <a href="#">Figure 6-1</a> and <a href="#">Figure 6-4</a>                                                                   | 1.4  | 3.3  | 3.3  | V    |

|                                     |                                                                                                       | CANH - CANL                                                                                                                            | nSTB = $V_{\text{IO}}$ , TXD = 0 V, $R_L = 2240 \Omega$ , $C_L = \text{open}$<br>See <a href="#">Figure 6-1</a> and <a href="#">Figure 6-4</a>                                                                                   | 1.5  | 5    | 5    | V    |

| $V_{OD(\text{REC})}$                | Differential output voltage<br>Bus biasing active<br>Recessive                                        | CANH - CANL                                                                                                                            | nSTB = $V_{\text{IO}}$ , TXD = $V_{\text{IO}}$ , $R_L = \text{open}$ , $C_L = \text{open}$<br>See <a href="#">Figure 6-1</a> and <a href="#">Figure 6-4</a>                                                                      | -50  | 50   | 50   | mV   |

| $V_{O(\text{STB})}$                 | Bus output voltage with<br>bus biasing inactive                                                       | CANH                                                                                                                                   | nSTB = 0 V, TXD = $V_{\text{IO}}$ , $R_L = \text{open}$ (no load),<br>$C_L = \text{open}$<br>See <a href="#">Figure 6-1</a> and <a href="#">Figure 6-4</a>                                                                       | -0.1 | 0.1  | 0.1  | V    |

|                                     |                                                                                                       | CANL                                                                                                                                   | nSTB = 0 V, TXD = $V_{\text{IO}}$ , $R_L = \text{open}$ (no load),<br>$C_L = \text{open}$<br>See <a href="#">Figure 6-1</a> and <a href="#">Figure 6-4</a>                                                                       | -0.1 | 0.1  | 0.1  | V    |

|                                     |                                                                                                       | CANH - CANL                                                                                                                            | nSTB = 0 V, TXD = $V_{\text{IO}}$ , $R_L = \text{open}$ (no load),<br>$C_L = \text{open}$<br>See <a href="#">Figure 6-1</a> and <a href="#">Figure 6-4</a>                                                                       | -0.2 | 0.2  | 0.2  | V    |

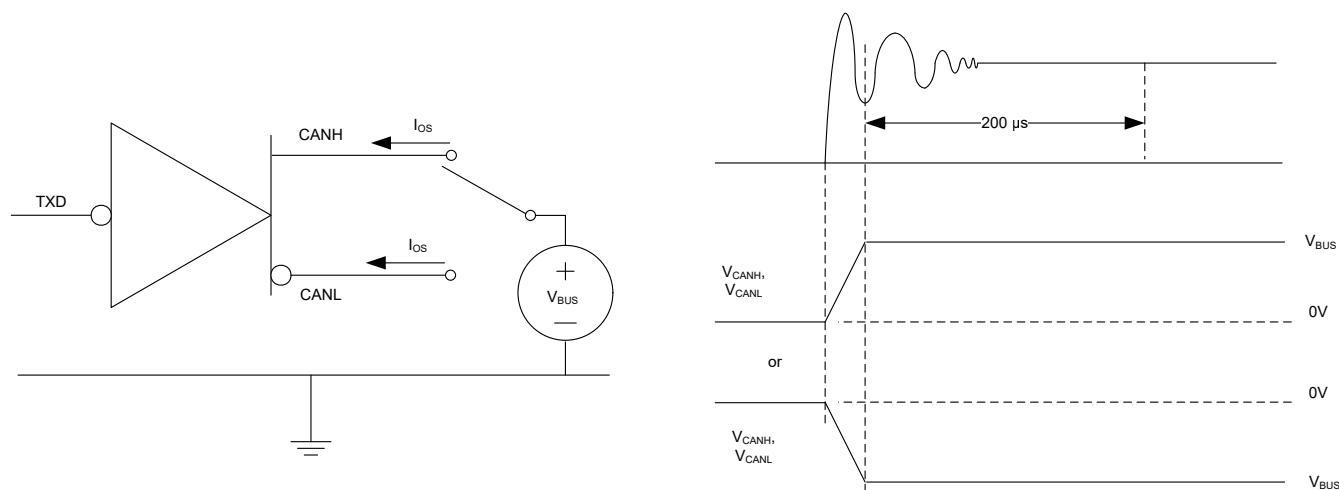

| $I_{OS(\text{DOM})}$                | Short-circuit steady-state output current<br>Bus biasing active<br>Dominant                           |                                                                                                                                        | nSTB = $V_{\text{IO}}$ , TXD = 0 V<br>$-15 \text{ V} \leq V_{(\text{CANH})} \leq 40 \text{ V}$<br>See <a href="#">Figure 6-1</a> and <a href="#">Figure 6-8</a>                                                                  | -100 |      |      | mA   |

|                                     |                                                                                                       |                                                                                                                                        | nSTB = $V_{\text{IO}}$ , TXD = 0 V<br>$-15 \text{ V} \leq V_{(\text{CANL})} \leq 40 \text{ V}$<br>See <a href="#">Figure 6-1</a> and <a href="#">Figure 6-8</a>                                                                  |      | 100  | 100  | mA   |

| $I_{OS(\text{REC})}$                | Short-circuit steady-state output current<br>Bus biasing active<br>Recessive                          |                                                                                                                                        | nSTB = $V_{\text{IO}}$ , $V_{\text{BUS}} = \text{CANH} = \text{CANL}$<br>$-27 \text{ V} \leq V_{\text{BUS}} \leq 42 \text{ V}$<br>See <a href="#">Figure 6-1</a> and <a href="#">Figure 6-8</a>                                  | -3   | 3    | 3    | mA   |

| <b>CAN Receiver Characteristics</b> |                                                                                                       |                                                                                                                                        |                                                                                                                                                                                                                                  |      |      |      |      |

| $V_{IT(\text{DOM})}$                | Receiver dominant state input voltage range<br>Bus biasing active                                     | nSTB = $V_{\text{IO}}$ , $-12 \text{ V} \leq V_{CM} \leq 12 \text{ V}$<br>See <a href="#">Figure 6-5</a> and <a href="#">Table 7-6</a> | 0.9                                                                                                                                                                                                                              | 8    | 8    | V    |      |

| $V_{IT(\text{REC})}$                | Receiver recessive state input voltage range<br>Bus biasing active                                    |                                                                                                                                        | -3                                                                                                                                                                                                                               | 0.5  | 0.5  | V    |      |

| $V_{\text{HYS}}$                    | Hysteresis voltage for input threshold<br>Bus biasing active                                          | nSTB = $V_{\text{IO}}$<br>See <a href="#">Figure 6-5</a> and <a href="#">Table 7-6</a>                                                 |                                                                                                                                                                                                                                  | 140  |      |      | mV   |

| $V_{\text{DIFF}(\text{DOM})}$       | Receiver dominant state input voltage range<br>Bus biasing inactive                                   | nSTB = 0 V, $-12 \text{ V} \leq V_{CM} \leq 12 \text{ V}$<br>See <a href="#">Figure 6-5</a> and <a href="#">Table 7-6</a>              | 1.150                                                                                                                                                                                                                            | 8    | 8    | V    |      |

| $V_{\text{DIFF}(\text{REC})}$       | Receiver recessive state input voltage range<br>Bus biasing inactive                                  |                                                                                                                                        | -3                                                                                                                                                                                                                               | 0.4  | 0.4  | V    |      |

| $V_{CM}$                            | Common mode range                                                                                     | nSTB = $V_{\text{IO}}$<br>See <a href="#">Figure 6-5</a> and <a href="#">Table 7-6</a>                                                 | -12                                                                                                                                                                                                                              | 12   | 12   | 12   | V    |

## 5.8 Electrical Characteristics (continued)

Over recommended operating conditions with  $T_J = -40^\circ\text{C}$  to  $150^\circ\text{C}$ , unless otherwise noted. All typical values are taken at  $25^\circ\text{C}$ ,  $V_{\text{SUP}} = 12\text{ V}$ ,  $V_{\text{IO}} = 3.3\text{ V}$ ,  $V_{\text{CC}} = 5\text{ V}$  and  $R_L = 60\ \Omega$

| PARAMETER                     |                                                                                              | TEST CONDITIONS                                                                              | MIN                    | TYP | MAX              | UNIT             |

|-------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------|-----|------------------|------------------|

| $I_{\text{OFF(LKG)}}$         | Power-off (unpowered) input leakage current CANH, CANL pins                                  | $V_{\text{SUP}} = 0\text{ V}$ , CANH = CANL = 5 V                                            |                        |     | 2.5              | $\mu\text{A}$    |

| $C_I$                         | Input capacitance to ground (CANH or CANL)<br><sup>(1)</sup>                                 |                                                                                              |                        |     | 20               | $\text{pF}$      |

| $C_{\text{ID}}$               | Differential input capacitance <sup>(1)</sup>                                                |                                                                                              |                        |     | 10               | $\text{pF}$      |

| $R_{\text{ID}}$               | Differential input resistance                                                                | $\text{TXD} = V_{\text{CC}} = V_{\text{IO}} = 5\text{ V}$ , nSTB = 5 V                       | 50                     | 100 | $\text{k}\Omega$ |                  |

| $R_{\text{IN}}$               | Input resistance (CANH or CANL)                                                              | $-12\text{ V} \leq V_{\text{CM}} \leq 12\text{ V}$                                           | 25                     | 50  | $\text{k}\Omega$ |                  |

| $R_{\text{IN(M)}}$            | Input resistance matching:<br>$[1 - R_{\text{IN(CANH)}} / R_{\text{IN(CANL)}}] \times 100\%$ | $V_{(\text{CANH})} = V_{(\text{CANL})} = 5\text{ V}$                                         | -1                     | 1   | %                |                  |

| $R_{\text{CBF}}$              | Valid differential load impedance range for bus fault circuitry                              | $R_{\text{CM}} = R_L$ , $C_L = \text{open}$                                                  | 45                     | 70  | $\Omega$         |                  |

| <b>TXD Characteristics</b>    |                                                                                              |                                                                                              |                        |     |                  |                  |

| $V_{\text{IH}}$               | High-level input voltage                                                                     |                                                                                              | 0.7                    |     |                  | $V_{\text{IO}}$  |

| $V_{\text{IL}}$               | Low-level input voltage                                                                      |                                                                                              |                        |     | 0.3              | $V_{\text{IO}}$  |

| $I_{\text{IH}}$               | High-level input leakage current                                                             | $\text{TXD} = V_{\text{IO}} = 5.5\text{ V}$                                                  | -2.5                   | 0   | 1                | $\mu\text{A}$    |

| $I_{\text{IL}}$               | Low-level input leakage current                                                              | $\text{TXD} = 0\text{ V}$ , $V_{\text{IO}} = 5.5\text{ V}$                                   | -115                   |     | -2.5             | $\mu\text{A}$    |

| $I_{\text{LKG(OFF)}}$         | Unpowered leakage current                                                                    | $\text{TXD} = 5.5\text{ V}$ , $V_{\text{SUP}} = V_{\text{IO}} = 0\text{ V}$                  | -1                     | 0   | 1                | $\mu\text{A}$    |

| $R_{\text{PU}}$               | Pull-up resistance to $V_{\text{IO}}$                                                        |                                                                                              | 40                     | 60  | 80               | $\text{k}\Omega$ |

| $C_I$                         | Input Capacitance                                                                            | $V_{\text{IN}} = 0.4 \times \sin(2 \times \pi \times 2 \times 10^6 \times t) + 2.5\text{ V}$ |                        | 5   |                  | $\text{pF}$      |

| <b>RXD Characteristics</b>    |                                                                                              |                                                                                              |                        |     |                  |                  |

| $V_{\text{OH}}$               | High-level output voltage                                                                    | $I_O = -2\text{ mA}$<br>See <a href="#">Figure 6-5</a>                                       | 0.8                    |     |                  | $V_{\text{IO}}$  |

| $V_{\text{OL}}$               | Low-level output voltage                                                                     | $I_O = 2\text{ mA}$<br>See <a href="#">Figure 6-5</a>                                        |                        |     | 0.2              | $V_{\text{IO}}$  |

| $I_{\text{LKG(OFF)}}$         | Unpowered leakage current                                                                    | $\text{RXD} = 5.5\text{ V}$ , $V_{\text{SUP}} = V_{\text{IO}} = 0\text{ V}$                  | -1                     |     | 1                | $\mu\text{A}$    |

| <b>nSTB Characteristics</b>   |                                                                                              |                                                                                              |                        |     |                  |                  |

| $V_{\text{IH}}$               | High-level input voltage                                                                     |                                                                                              | 0.7                    |     |                  | $V_{\text{IO}}$  |

| $V_{\text{IL}}$               | Low-level input voltage                                                                      |                                                                                              |                        |     | 0.3              | $V_{\text{IO}}$  |

| $I_{\text{IH}}$               | High-level input leakage current                                                             | $\text{nSTB} = V_{\text{IO}} = 5.5\text{ V}$                                                 | 0.5                    | 115 | $\mu\text{A}$    |                  |

| $I_{\text{IL}}$               | Low-level input leakage current                                                              | $\text{nSTB} = 0\text{ V}$ , $V_{\text{IO}} = 5.5\text{ V}$                                  | -1                     |     | 1                | $\mu\text{A}$    |

| $I_{\text{LKG(OFF)}}$         | Unpowered leakage current                                                                    | $\text{nSTB} = 5.5\text{ V}$ , $V_{\text{IO}} = 0\text{ V}$                                  | -1                     | 0   | 1                | $\mu\text{A}$    |

| $R_{\text{PD}}$               | Pull-down resistance                                                                         |                                                                                              | 40                     | 60  | 80               | $\text{k}\Omega$ |

| <b>nFAULT Characteristics</b> |                                                                                              |                                                                                              |                        |     |                  |                  |

| $V_{\text{OH}}$               | High-level output voltage                                                                    | $I_O = -2\text{ mA}$                                                                         | 0.8                    |     |                  | $V_{\text{IO}}$  |

| $V_{\text{OL}}$               | Low-level output voltage                                                                     | $I_O = 2\text{ mA}$                                                                          |                        |     | 0.2              | $V_{\text{IO}}$  |

| $I_{\text{LKG(OFF)}}$         | Unpowered leakage current                                                                    | $\text{nFAULT} = 5.5\text{ V}$ , $V_{\text{IO}} = 0\text{ V}$                                | -1                     | 0   | 1                | $\mu\text{A}$    |

| <b>EN Characteristics</b>     |                                                                                              |                                                                                              |                        |     |                  |                  |

| $V_{\text{IH}}$               | High-level input voltage                                                                     |                                                                                              | 0.7                    |     |                  | $V_{\text{IO}}$  |

| $V_{\text{IL}}$               | Low-level input voltage                                                                      |                                                                                              |                        |     | 0.3              | $V_{\text{IO}}$  |

| $I_{\text{IH}}$               | High-level input leakage current                                                             | $\text{EN} = V_{\text{CC}} = V_{\text{IO}} = 5.5\text{ V}$                                   | 0.5                    | 115 | $\mu\text{A}$    |                  |

| $I_{\text{IL}}$               | Low-level input leakage current                                                              | $\text{EN} = 0\text{ V}$ , $V_{\text{CC}} = V_{\text{IO}} = 5.5\text{ V}$                    | -1                     |     | 1                | $\mu\text{A}$    |

| $I_{\text{LKG(OFF)}}$         | Unpowered leakage current                                                                    | $\text{EN} = 5.5\text{ V}$ , $V_{\text{CC}} = V_{\text{IO}} = 0\text{ V}$                    | -1                     |     | 1                | $\mu\text{A}$    |

| $R_{\text{PD}}$               | Pull-down resistance                                                                         |                                                                                              | 40                     | 60  | 80               | $\text{k}\Omega$ |

| <b>WAKE Characteristics</b>   |                                                                                              |                                                                                              |                        |     |                  |                  |

| $V_{\text{IH}}$               | High-level input voltage                                                                     | Sleep mode                                                                                   | $V_{\text{SUP}} - 2$   |     |                  | V                |

| $V_{\text{IL}}$               | Low-level input voltage                                                                      |                                                                                              | $V_{\text{SUP}} - 3.5$ |     |                  | V                |

| $I_{\text{IH}}$               | High-level input leakage current <sup>(2)</sup>                                              | $\text{WAKE} = V_{\text{SUP}} - 1\text{ V}$                                                  | -3                     |     |                  | $\mu\text{A}$    |

| $I_{\text{IL}}$               | Low-level input leakage current <sup>(2)</sup>                                               | $\text{WAKE} = 1\text{ V}$                                                                   |                        |     | 3                | $\mu\text{A}$    |

## 5.8 Electrical Characteristics (continued)

Over recommended operating conditions with  $T_J = -40^\circ\text{C}$  to  $150^\circ\text{C}$ , unless otherwise noted. All typical values are taken at  $25^\circ\text{C}$ ,  $V_{\text{SUP}} = 12 \text{ V}$ ,  $V_{\text{IO}} = 3.3 \text{ V}$ ,  $V_{\text{CC}} = 5 \text{ V}$  and  $R_L = 60 \Omega$

| PARAMETER                    |                                                                                            | TEST CONDITIONS                  | MIN  | TYP | MAX | UNIT             |

|------------------------------|--------------------------------------------------------------------------------------------|----------------------------------|------|-----|-----|------------------|

| <b>INH Characteristics</b>   |                                                                                            |                                  |      |     |     |                  |

| $\Delta V_H$                 | High-level voltage drop from $V_{\text{SUP}}$ to INH ( $V_{\text{SUP}} - V_{\text{INH}}$ ) | $I_{\text{INH}} = -6 \text{ mA}$ |      | 0.5 | 1   | V                |

| $I_{\text{LKG}(\text{INH})}$ | Sleep mode leakage current                                                                 | $\text{INH} = 0 \text{ V}$       | -0.5 | 0.5 | 0.5 | $\mu\text{A}$    |

| $R_{\text{PD}}$              | Pull-down resistance                                                                       | Sleep mode                       | 2.5  | 4   | 6   | $\text{M}\Omega$ |

- (1) Specified by design and verified via bench characterization

- (2) To minimize system level current consumption, the WAKE pin will automatically configure itself based on the applied voltage to either an internal pull-up or pull-down current source. A high-level input results in an internal pull-up and a low-level input results in an internal pull-down.

## 5.9 Timing Requirements

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                          |                                                                                                                      | TEST CONDITIONS                                                                                                                 | MIN                                                                                                                                                                | TYP | MAX | UNIT          |               |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------------|---------------|

| <b>Supply Characteristics</b>      |                                                                                                                      |                                                                                                                                 |                                                                                                                                                                    |     |     |               |               |

| $t_{\text{PWRUP}}$                 | Time required for INH active after $V_{\text{SUP}} \geq UV_{\text{SUP}(\text{R})}$                                   | See <a href="#">Figure 6-10</a>                                                                                                 |                                                                                                                                                                    | 310 |     | $\mu\text{s}$ |               |

| $t_{\text{UV}}$                    | Undervoltage filter time $V_{\text{CC}}$ and $V_{\text{IO}}$ <sup>(1)</sup>                                          | $V_{\text{CC}} \leq UV_{\text{CC}}$ or $V_{\text{IO}} \leq UV_{\text{IO}}$                                                      | 100                                                                                                                                                                | 350 |     | ms            |               |

| $t_{\text{UV}(\text{RE-ENABLE})}$  | Re-enable time after undervoltage event <sup>(1)</sup>                                                               | Time for device to return to normal operation from a $UV_{\text{CC}}$ or $UV_{\text{IO}}$ undervoltage event                    |                                                                                                                                                                    | 200 |     | $\mu\text{s}$ |               |

| <b>Device Characteristics</b>      |                                                                                                                      |                                                                                                                                 |                                                                                                                                                                    |     |     |               |               |

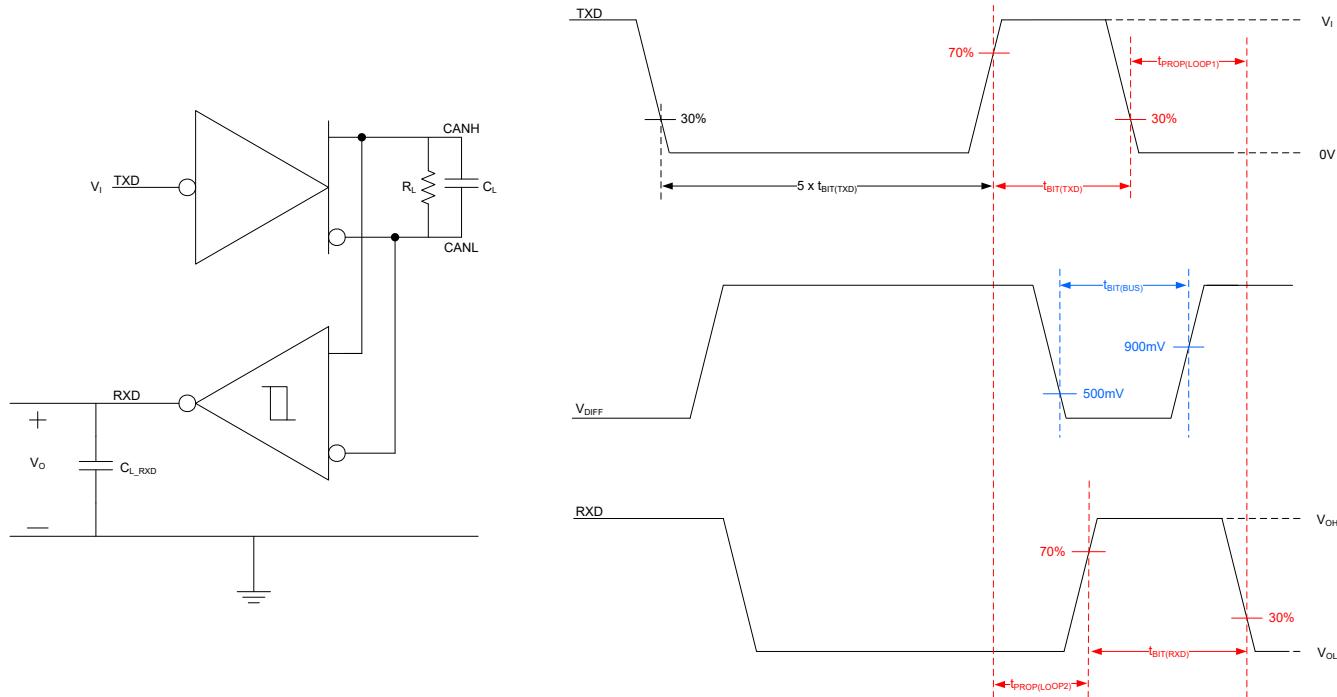

| $t_{\text{PROP}(\text{LOOP1})}$    | Total loop delay, driver input (TXD) to receiver output (RXD)<br>Recessive to dominant                               | TCAN1043A-Q1 Only                                                                                                               | $R_L = 60 \Omega$ , $C_L = 100 \text{ pF}$ , $C_{L(\text{RXD})} = 15 \text{ pF}$<br>See <a href="#">Figure 6-6</a>                                                 | 140 | 215 | ns            |               |

| $t_{\text{PROP}(\text{LOOP2})}$    | Total loop delay, driver input (TXD) to receiver output (RXD)<br>Dominant to recessive                               |                                                                                                                                 | $R_L = 60 \Omega$ , $C_L = 100 \text{ pF}$ , $C_{L(\text{RXD})} = 15 \text{ pF}$<br>See <a href="#">Figure 6-6</a>                                                 | 140 | 205 | ns            |               |

| $t_{\text{PROP}(\text{LOOP1})}$    | Total loop delay, driver input (TXD) to receiver output (RXD)<br>Recessive to dominant                               | TCAN1043AT-Q1 Only                                                                                                              | $R_L = 60 \Omega$ , $C_L = 100 \text{ pF}$ , $C_{L(\text{RXD})} = 15 \text{ pF}$<br>See <a href="#">Figure 6-6</a>                                                 | 170 | 255 | ns            |               |

| $t_{\text{PROP}(\text{LOOP2})}$    | Total loop delay, driver input (TXD) to receiver output (RXD)<br>Dominant to recessive                               |                                                                                                                                 | $R_L = 60 \Omega$ , $C_L = 100 \text{ pF}$ , $C_{L(\text{RXD})} = 15 \text{ pF}$<br>See <a href="#">Figure 6-6</a>                                                 | 170 | 255 | ns            |               |

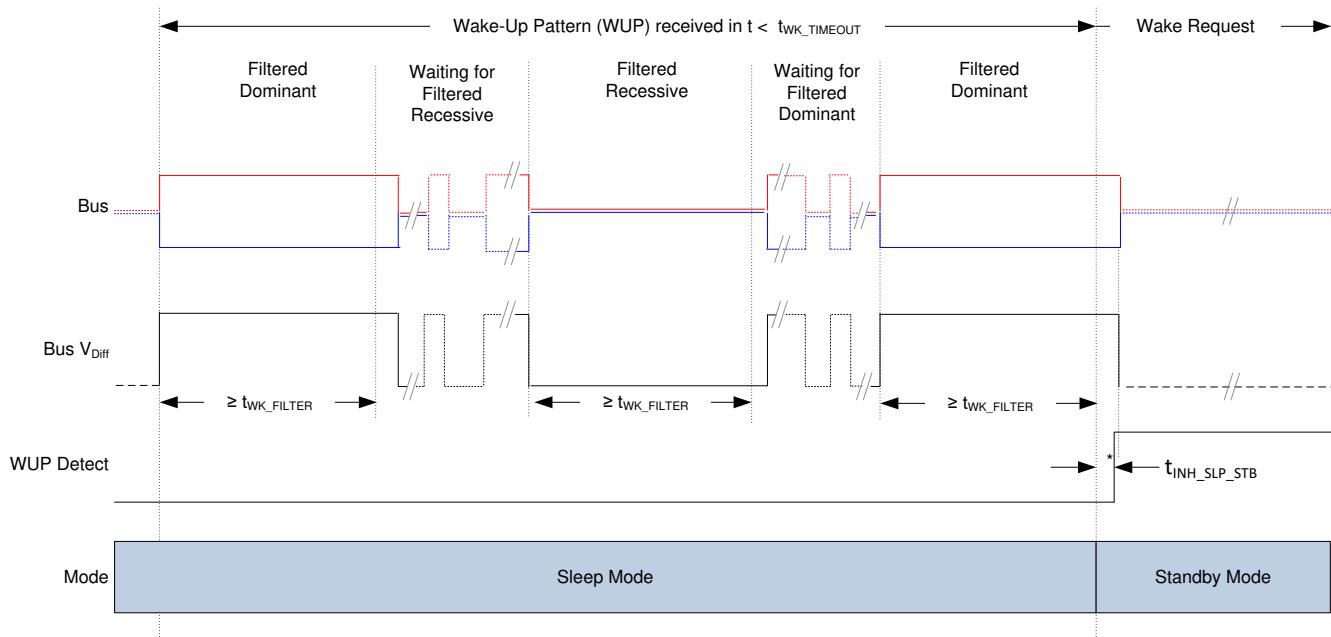

| $t_{\text{WK}(\text{TIMEOUT})}$    | Bus wake-up timeout value <sup>(1)</sup>                                                                             |                                                                                                                                 |                                                                                                                                                                    | 0.8 | 2   | ms            |               |

| $t_{\text{WK}(\text{FILTER})}$     | Bus time to meet filtered bus requirements for wake-up request <sup>(1)</sup>                                        |                                                                                                                                 |                                                                                                                                                                    | 0.5 | 1.8 | $\mu\text{s}$ |               |

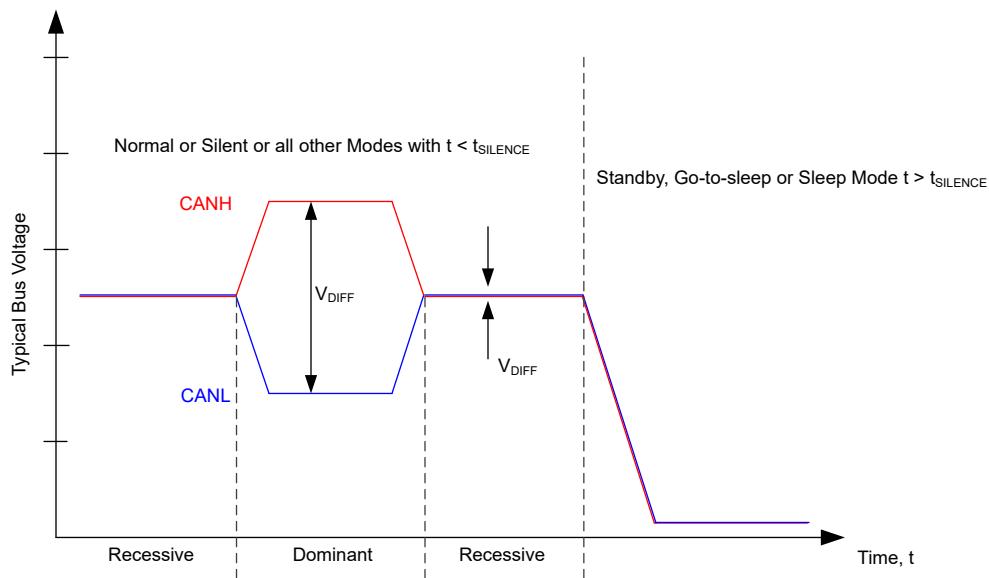

| $t_{\text{SILENCE}}$               | Timeout for bus inactivity <sup>(1)</sup>                                                                            |                                                                                                                                 | Timer is reset and restarted, when bus changes from dominant to recessive or vice versa                                                                            | 0.6 | 1.2 | s             |               |

| $t_{\text{INACTIVE}}$              | Standby mode SWE timer timeout period <sup>(1)</sup>                                                                 |                                                                                                                                 |                                                                                                                                                                    | 3   | 4   | 5             | min           |

| $t_{\text{BIAS}}$                  | Bus bias reaction time <sup>(1)</sup>                                                                                | Measured from the start of a dominant-recessive-dominant sequence (each phase 6 $\mu\text{s}$ ) until $V_{\text{SYM}} \geq 0.1$ | $n\text{STB} = \text{EN} = 0 \text{ V}$ , $R_L = 60 \Omega$ , $C_{\text{SPLIT}} = 4.7 \text{ nF}$<br>See <a href="#">Figure 6-9</a> and <a href="#">Figure 8-2</a> |     | 200 |               | $\mu\text{s}$ |

| $t_{\text{CBF}}$                   | Bus fault-detection time                                                                                             |                                                                                                                                 | $45 \leq R_{\text{CM}} \leq 70 \Omega$<br>$C_L = \text{open}$                                                                                                      | 2.5 |     |               | $\mu\text{s}$ |

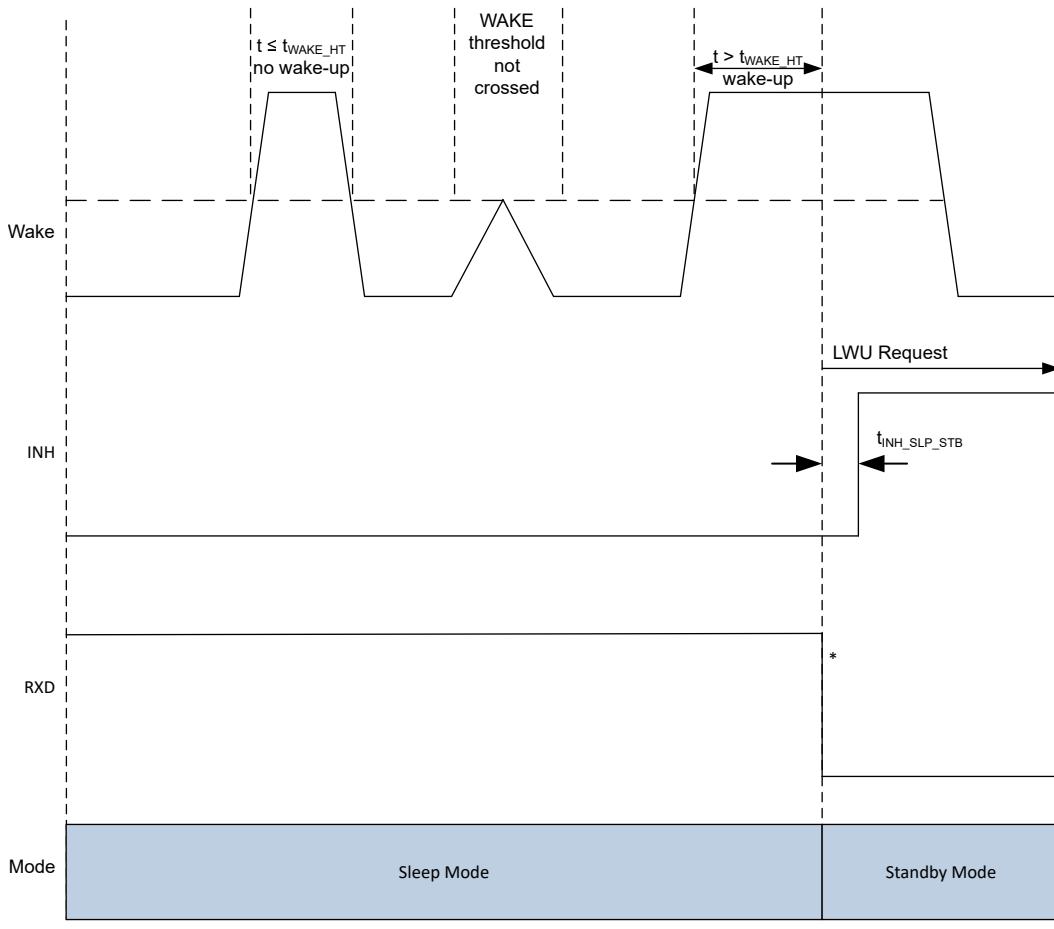

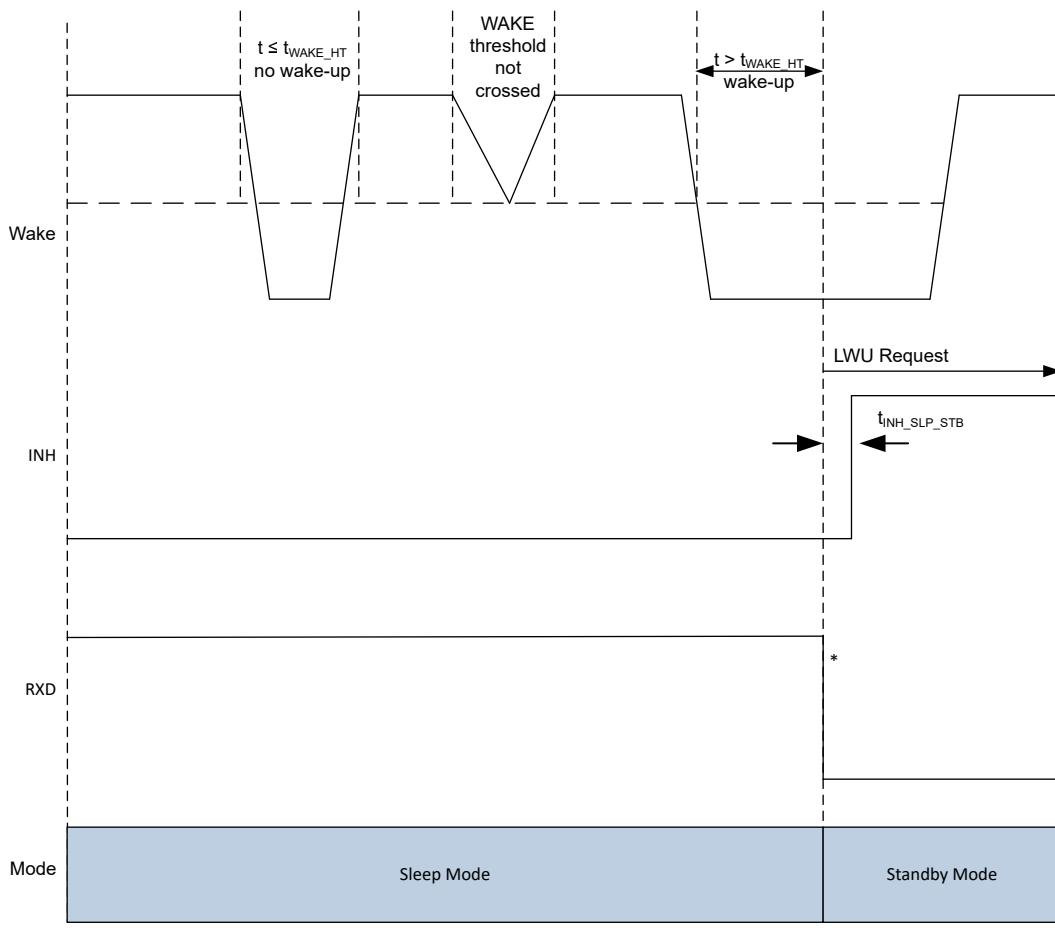

| $t_{\text{WAKE\_HT}}$              | Hold time for which WAKE pin voltage should be stable after the rising or falling edge on WAKE pin to recognize LWU. |                                                                                                                                 |                                                                                                                                                                    | 5   | 50  |               | $\mu\text{s}$ |

| <b>Mode Change Characteristics</b> |                                                                                                                      |                                                                                                                                 |                                                                                                                                                                    |     |     |               |               |

| $t_{\text{INH\_SLP\_STB}}$         | INH assertion time <sup>(1)</sup>                                                                                    |                                                                                                                                 |                                                                                                                                                                    | 100 |     | $\mu\text{s}$ |               |

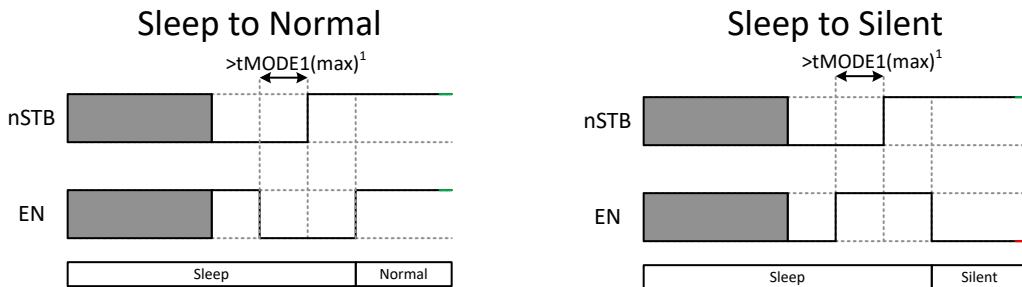

| $t_{\text{MODE1}}$                 | Mode change time from leaving the Sleep mode to entering Normal or Silent mode <sup>(1)</sup>                        | Time measured from $V_{\text{CC}}$ and $V_{\text{IO}}$ crossing UV thresholds to entering normal or silent mode.                |                                                                                                                                                                    | 20  |     | $\mu\text{s}$ |               |

| $t_{\text{MODE2}}$                 | Mode change time between normal, silent and standby mode and from sleep to standby mode <sup>(1)</sup>               | Mode change time between normal, silent and standby mode and from sleep to standby mode                                         |                                                                                                                                                                    | 10  |     | $\mu\text{s}$ |               |

## 5.9 Timing Requirements (continued)

over operating free-air temperature range (unless otherwise noted)

| PARAMETER              | TEST CONDITIONS                                                                      | MIN | TYP | MAX | UNIT |

|------------------------|--------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>GOTOSLEEP</sub> | Minimum hold time for transition to sleep mode <sup>(1)</sup><br>EN = H and nSTB = L | 20  | 50  |     | μs   |

- (1) Specified by design and verified via bench characterization

## 5.10 Switching Characteristics

Over recommended operating conditions with  $T_J = -40^\circ\text{C}$  to  $150^\circ\text{C}$ , unless otherwise noted. All typical values are taken at  $25^\circ\text{C}$ ,  $V_{\text{SUP}} = 12 \text{ V}$ ,  $V_{\text{IO}} = 3.3 \text{ V}$ ,  $V_{\text{CC}} = 5 \text{ V}$  and  $R_L = 60 \Omega$

| PARAMETER                       |                                                                                   | TEST CONDITIONS                                                       | MIN                                                                                                                                                                                                                      | TYP | MAX | UNIT |    |

|---------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|----|

| <b>Driver Characteristics</b>   |                                                                                   |                                                                       |                                                                                                                                                                                                                          |     |     |      |    |

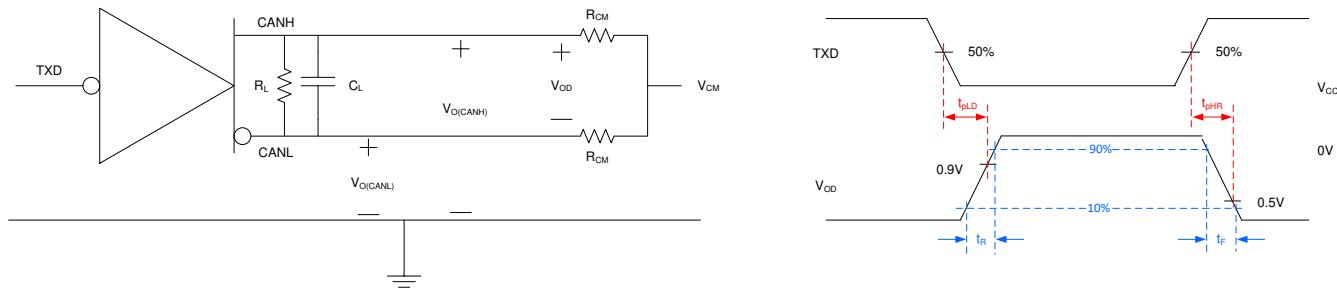

| $t_{\text{pHR}}$                | Propagation delay time, high TXD to driver recessive                              | TCAN1043AT-Q1 Only                                                    | $R_L = 60 \Omega$ , $C_L = 100 \text{ pF}$ , $R_{\text{CM}} = \text{open}$<br>See <a href="#">Figure 6-4</a>                                                                                                             | 30  | 80  | 140  | ns |

| $t_{\text{pLD}}$                | Propagation delay time, low TXD to driver dominant                                |                                                                       | $R_L = 60 \Omega$ , $C_L = 100 \text{ pF}$ , $R_{\text{CM}} = \text{open}$<br>See <a href="#">Figure 6-4</a>                                                                                                             | 30  | 80  | 140  | ns |

| $t_{\text{sk(p)}}$              | Pulse skew ( $ t_{\text{pHR}} - t_{\text{pLD}} $ )                                |                                                                       | $R_L = 60 \Omega$ , $C_L = 100 \text{ pF}$ , $R_{\text{CM}} = \text{open}$<br>See <a href="#">Figure 6-4</a>                                                                                                             |     | 8   |      | ns |

| $t_R$                           | Differential output signal rise time                                              |                                                                       | $R_L = 60 \Omega$ , $C_L = 100 \text{ pF}$ , $R_{\text{CM}} = \text{open}$<br>See <a href="#">Figure 6-4</a>                                                                                                             |     | 50  |      | ns |

| $t_F$                           | Differential output signal fall time                                              |                                                                       | $R_L = 60 \Omega$ , $C_L = 100 \text{ pF}$ , $R_{\text{CM}} = \text{open}$<br>See <a href="#">Figure 6-4</a>                                                                                                             |     | 50  |      | ns |

| $t_{\text{pHR}}$                | Propagation delay time, high TXD to driver recessive                              | TCAN1043A-Q1 variant only                                             | $R_L = 60 \Omega$ , $C_L = 100 \text{ pF}$ , $R_{\text{CM}} = \text{open}$<br>See <a href="#">Figure 6-4</a>                                                                                                             | 30  | 50  | 90   | ns |

| $t_{\text{pLD}}$                | Propagation delay time, low TXD to driver dominant                                |                                                                       |                                                                                                                                                                                                                          | 30  | 50  | 90   | ns |

| $t_{\text{sk(p)}}$              | Pulse skew ( $ t_{\text{pHR}} - t_{\text{pLD}} $ )                                |                                                                       |                                                                                                                                                                                                                          |     | 8   |      | ns |

| $t_R$                           | Differential output signal rise time                                              |                                                                       |                                                                                                                                                                                                                          |     | 50  |      | ns |

| $t_F$                           | Differential output signal fall time                                              |                                                                       |                                                                                                                                                                                                                          |     | 50  |      | ns |

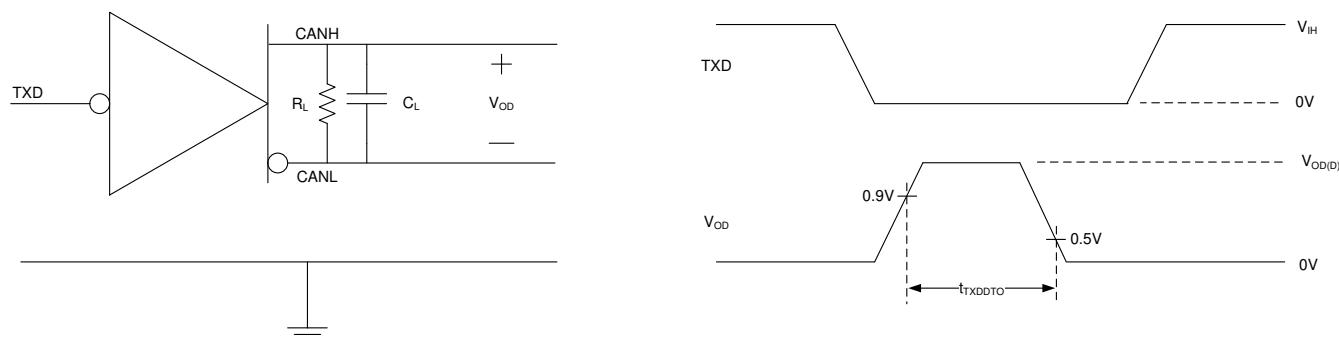

| $t_{\text{TXDDTO}}$             | Dominant timeout                                                                  |                                                                       | $\text{TXD} = 0 \text{ V}$ , $R_L = 60 \Omega$ , $C_L = \text{open}$<br>See <a href="#">Figure 6-7</a>                                                                                                                   | 1.2 |     | 3.8  | ms |

| <b>Receiver Characteristics</b> |                                                                                   |                                                                       |                                                                                                                                                                                                                          |     |     |      |    |

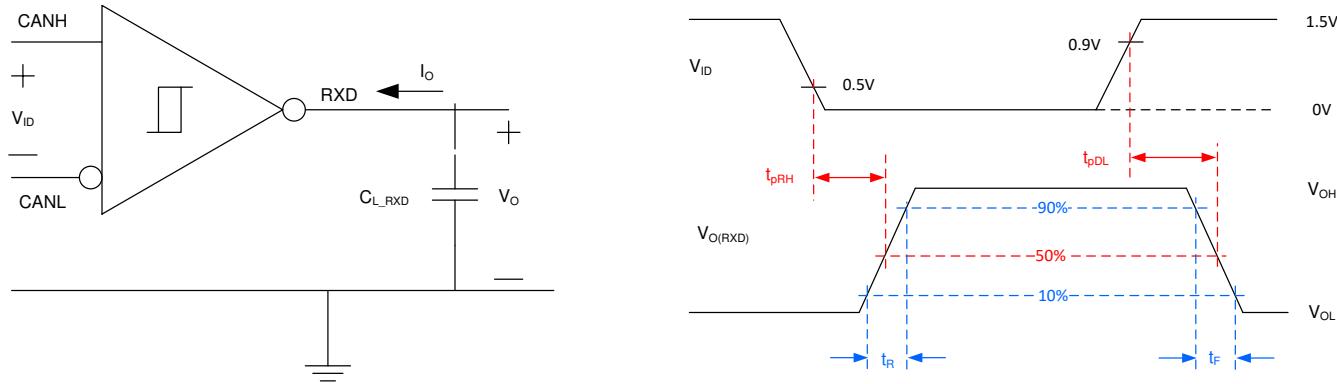

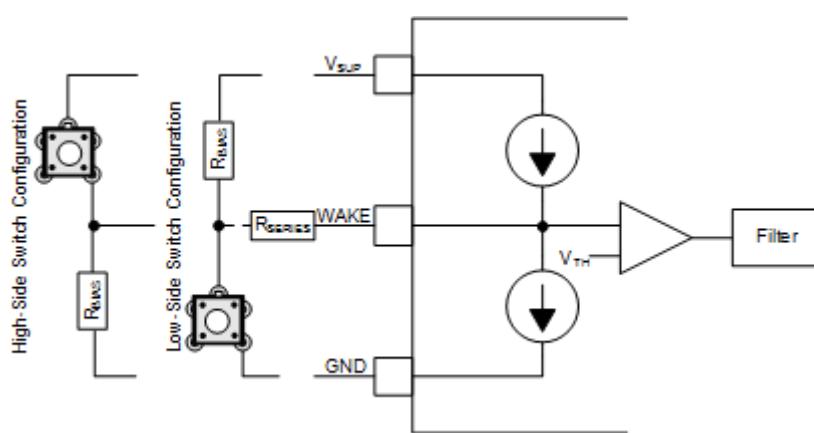

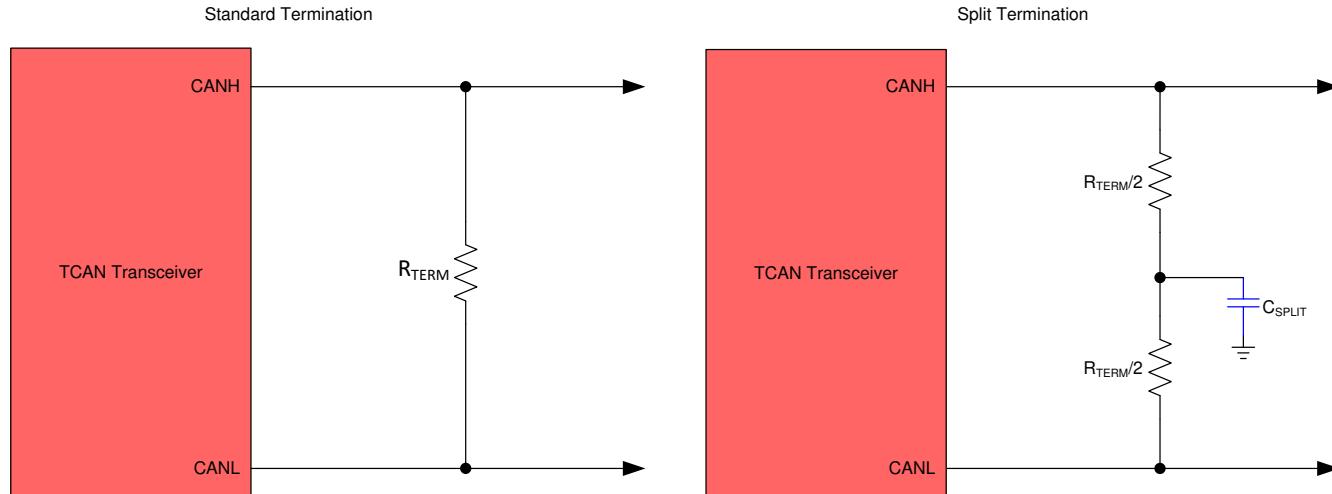

| $t_{\text{pRH}}$                | Propagation delay time, bus recessive input to high RXD                           | $C_{L(\text{RXD})} = 15 \text{ pF}$<br>See <a href="#">Figure 6-5</a> | $R_L = 60 \Omega$ , $C_L = \text{open}$<br>See <a href="#">Figure 6-5</a>                                                                                                                                                | 25  | 75  | 140  | ns |