TCA9539-Q1 ZHCSEZ2D - JANUARY 2014 - REVISED OCTOBER 2021

# 具有中断输出、复位引脚和配置寄存器的 TCA9539-Q1 汽车类低压 16 位 I<sup>2</sup>C 和 SMBus 低功耗 I/O 扩展器

## 1 特性

- AEC-Q100 (等级 1): 符合汽车应用要求

- 提供功能安全

- 可帮助进行功能安全系统设计的文档

- I<sup>2</sup>C 至并行端口扩展器

- 开漏电路低电平有效中断输出

- 低电平有效复位输入

- 5V 耐压输入和输出端口

- 兼容大多数微控制器

- 400kHz 快速 I<sup>2</sup>C 总线

- 极性反转寄存器

- 内部上电复位

- 加电时无干扰

- 通过两个硬件地址引脚寻址,以便使用多达4个器

- 锁存输出,用于直接驱动 LED

- 闩锁性能超过 100mA,符合 JESD 78 Ⅱ 类规范的

- ESD 保护性能超过 JESD 22 规范要求

- 2000V 人体放电模型 (A114-A)

- 1000V 带电器件模型 (C101)

# 2 应用

- 汽车信息娱乐系统、高级驾驶辅助系统 (ADAS)、 汽车车身电子装置、混合动力汽车 (HEV)、电动车 (EV) 和动力总成

- 工业自动化、工厂自动化、楼宇自动化、测试与测 量、电子销售点终端 (EPOS)

- I<sup>2</sup>C GPIO 扩展

## 3 说明

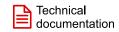

TCA9539-Q1 是一款 24 引脚器件,可为两线双向 I2C 总线(或 SMBus 协议)提供 16 位通用并行输入和输 出 (I/O) 扩展。该器件的工作电源电压 (V<sub>CC</sub>) 范围为 1.65V 至 3.6V, 并且支持 100kHz ( I<sup>2</sup>C 标准模式 ) 和 400kHz(I<sup>2</sup>C 快速模式)两种时钟频率。当开关、传 感器、按钮、LED、风扇以及其他相似器件需要额外的 I/O 时, I/O 扩展器 (如 TCA9539-Q1) 可提供简单解 决方案。

TCA9539-Q1 包括一项功能: 当输入端口状态发生变 化时,在 INT 引脚上生成中断。硬件可选地址引脚 A0 和 A1 最多允许四个 TCA9539-Q1 器件位于同一 I<sup>2</sup>C 总线上。也可以通过下电上电生成上电复位,将此器件 复位为默认状态。此外, TCA9539-Q1 还具有一个硬 件 RESET 引脚,可用于将器件复位为默认状态。

TCA9539-Q1 I<sup>2</sup>C I/O 扩展器符合汽车类应用的要求。

### 器件信息

| 器件型号       | 封装类型 <sup>(1)</sup> | 封装尺寸(标称值)       |

|------------|---------------------|-----------------|

| TCA9539-Q1 | TSSOP (24)          | 7.80mm × 4.40mm |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

简化版方框图

# **Table of Contents**

| 1 特性                                                    | 1 8.2 Functional Block Diagram                  | 16               |

|---------------------------------------------------------|-------------------------------------------------|------------------|

| 2 应用                                                    |                                                 | 17               |

| - <u>一</u> , <del>1</del>                               |                                                 | 18               |

| 4 Revision History                                      |                                                 | 18               |

| 5 Pin Configuration and Functions                       | 3 8.6 Register Maps                             | <mark>2</mark> 0 |

| 6 Specifications                                        |                                                 | <mark>2</mark> 9 |

| 6.1 Absolute Maximum Ratings                            |                                                 | <mark>2</mark> 9 |

| 6.2 ESD Ratings                                         |                                                 | 31               |

| 6.3 Recommended Operating Conditions                    |                                                 | 31               |

| 6.4 Thermal Information                                 |                                                 | 32               |

| 6.5 Electrical Characteristics                          | 44 D                                            | <mark>33</mark>  |

| 6.6 I <sup>2</sup> C Interface Timing Requirements      |                                                 | 33               |

| 6.7 RESET Timing Requirements                           |                                                 | 33               |

| 6.8 Switching Characteristics                           |                                                 |                  |

| 6.9 Typical Characteristics                             |                                                 |                  |

| 7 Parameter Measurement Information                     |                                                 |                  |

| 8 Detailed Description                                  |                                                 |                  |

| 8.1 Overview                                            |                                                 |                  |

|                                                         | s) to Revision D (October 2021)                 |                  |

|                                                         |                                                 |                  |

|                                                         | 目标。                                             |                  |

| Corrected the pin number for pins A0, SCI               | _, SDA, and VCC in the <i>TCA9539-Q1 Layout</i> | 32               |

| Changes from Revision B (April 2016) to R               | evision C (December 2018)                       | Page             |

| · Changed the appearance of the PW pinou                | t image                                         | 3                |

| Removed (5 V) from the V <sub>CC</sub> label in      9- | 1                                               | 25               |

| Changes from Revision A (September 201)                 | 5) to Revision B (April 2016)                   | Page             |

|                                                         | ( )                                             |                  |

|                                                         |                                                 |                  |

|                                                         |                                                 |                  |

| Changes from Revision * (January 2014) to               | Revision A (September 2015)                     | Page             |

Submit Document Feedback

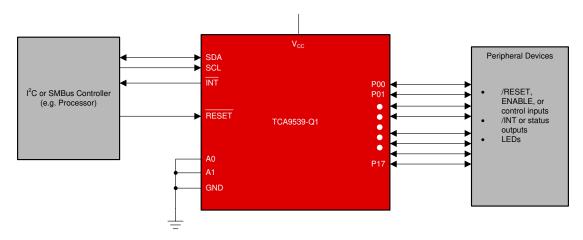

# **5 Pin Configuration and Functions**

图 5-1. PW Package, 24-Pin TSSOP, Top View

表 5-1. Pin Functions

|     | PIN             | 1/0 | DECORIDATION                                                                                                  |

|-----|-----------------|-----|---------------------------------------------------------------------------------------------------------------|

| NO. | NAME            | I/O | DESCRIPTION                                                                                                   |

| 1   | INT             | 0   | Interrupt open-drain output. Connect to V <sub>CC</sub> through a pull-up resistor                            |

| 2   | A1              | I   | Address input. Connect directly to V <sub>CC</sub> or ground                                                  |

| 3   | RESET           | I   | Active-low reset input. Connect to V <sub>CC</sub> through a pull-up resistor if no active connection is used |

| 4   | P00             | I/O | P-port input-output. Push-pull design structure. At power-on, P00 is configured as an input                   |

| 5   | P01             | I/O | P-port input-output. Push-pull design structure. At power-on, P01 is configured as an input                   |

| 6   | P02             | I/O | P-port input-output. Push-pull design structure. At power-on, P02 is configured as an input                   |

| 7   | P03             | I/O | P-port input-output. Push-pull design structure. At power-on, P03 is configured as an input                   |

| 8   | P04             | I/O | P-port input-output. Push-pull design structure. At power-on, P04 is configured as an input                   |

| 9   | P05             | I/O | P-port input-output. Push-pull design structure. At power-on, P05 is configured as an input                   |

| 10  | P06             | I/O | P-port input-output. Push-pull design structure. At power-on, P06 is configured as an input                   |

| 11  | P07             | I/O | P-port input-output. Push-pull design structure. At power-on, P07 is configured as an input                   |

| 12  | GND             | _   | Ground                                                                                                        |

| 13  | P10             | I/O | P-port input-output. Push-pull design structure. At power-on, P10 is configured as an input                   |

| 14  | P11             | I/O | P-port input-output. Push-pull design structure. At power-on, P11 is configured as an input                   |

| 15  | P12             | I/O | P-port input-output. Push-pull design structure. At power-on, P12 is configured as an input                   |

| 16  | P13             | I/O | P-port input-output. Push-pull design structure. At power-on, P13 is configured as an input                   |

| 17  | P14             | I/O | P-port input-output. Push-pull design structure. At power-on, P14 is configured as an input                   |

| 18  | P15             | I/O | P-port input-output. Push-pull design structure. At power-on, P15 is configured as an input                   |

| 19  | P16             | I/O | P-port input-output. Push-pull design structure. At power-on, P16 is configured as an input                   |

| 20  | P17             | I/O | P-port input-output. Push-pull design structure. At power-on, P17 is configured as an input                   |

| 21  | A0              | ı   | Address input. Connect directly to V <sub>CC</sub> or ground                                                  |

| 22  | SCL             | ı   | Serial clock bus. Connect to V <sub>CC</sub> through a pull-up resistor                                       |

| 23  | SDA             | I/O | Serial data bus. Connect to V <sub>CC</sub> through a pull-up resistor                                        |

| 24  | V <sub>CC</sub> | _   | Supply voltage                                                                                                |

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted) (1)

|                     |                                            |                             | MIN   | MAX   | UNIT |

|---------------------|--------------------------------------------|-----------------------------|-------|-------|------|

| V <sub>CC</sub>     | Supply voltage                             |                             | - 0.5 | 3.6   | V    |

| VI                  | Input voltage <sup>(2)</sup>               |                             | - 0.5 | 6     | V    |

| Vo                  | Output voltage <sup>(2)</sup>              |                             | - 0.5 | 6     | V    |

| I <sub>IK</sub>     | Input clamp current                        | V <sub>I</sub> < 0          |       | - 20  | mA   |

| I <sub>OK</sub>     | Output clamp current                       | V <sub>O</sub> < 0          |       | - 20  | mA   |

| I <sub>IOK</sub>    | Input-output clamp current                 | $V_O < 0$ or $V_O > V_{CC}$ |       | ±20   | mA   |

| I <sub>OL</sub>     | Continuous output low current              | $V_O = 0$ to $V_{CC}$       |       | 50    | mA   |

| I <sub>OH</sub>     | Continuous output high current             | $V_O = 0$ to $V_{CC}$       |       | - 50  | mA   |

| 1                   | Continuous current through GND             |                             |       | - 250 | mΛ   |

| Icc                 | Continuous current through V <sub>CC</sub> |                             |       | 160   | mA   |

| T <sub>j(MAX)</sub> | Maximum junction temperature               |                             |       | 135   | °C   |

| T <sub>stg</sub>    | Storage temperature                        |                             | - 65  | 150   | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 6.2 ESD Ratings

|                    |                         |                                                         | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> |       | V    |

| V <sub>(ESD)</sub> |                         | Charged-device model (CDM), per AEC Q100-011            | ±1000 | V    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                     |                           |                            |                                                                                            | MIN                   | MAX                   | UNIT |

|---------------------|---------------------------|----------------------------|--------------------------------------------------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>CC</sub>     | Supply voltage            |                            |                                                                                            | 1.65                  | 3.6                   | V    |

|                     |                           | SCL, SDA, A0, A1, RESET,   | SCL, SDA, A0, A1, RESET, INT <sup>(1)</sup> For P00 - P07, P10 - P17 configured as outputs |                       | 5.5                   | V    |

| $V_{I/O}$           | I/O ports voltage         | For P00 - P07, P10 - P17 c |                                                                                            |                       | 3.6                   | V    |

|                     |                           | For P00 - P07, P10 - P17 c | For P00 - P07, P10 - P17 configured as inputs <sup>(1)</sup>                               |                       | 5.5                   | V    |

| V <sub>IH</sub>     | High-level input voltage  | SCL, SDA, A0, A1, RESET,   | P07 - P00, P10 - P17                                                                       | 0.7 × V <sub>CC</sub> |                       | V    |

| V <sub>IL</sub>     | Low-level input voltage   | SCL, SDA, A0, A1, RESET,   | SCL, SDA, A0, A1, RESET, P07 - P00, P10 - P17                                              |                       | 0.3 × V <sub>CC</sub> | V    |

| I <sub>OH</sub>     | High-level output current | P00 - P07, P10 - P17       | P00 - P07, P10 - P17                                                                       |                       | - 10                  | mA   |

|                     |                           |                            | $T_j \le 65^{\circ}C$                                                                      |                       | 25                    |      |

|                     |                           |                            | T <sub>j</sub> = 85°C                                                                      |                       | 18                    |      |

| I <sub>OL</sub> (2) | Low-level output current  | P00 - P07, P10 - P17       | T <sub>j</sub> = 105°C                                                                     | °C                    |                       | mA   |

|                     |                           |                            | T <sub>j</sub> = 125°C                                                                     |                       | 4.5                   |      |

|                     |                           |                            | T <sub>j</sub> = 135°C                                                                     |                       | 3.5                   |      |

Product Folder Links: TCA9539-Q1

<sup>(2)</sup> The input negative voltage and output voltage ratings may be exceeded if the input and output current ratings are observed.

# 6.3 Recommended Operating Conditions (continued)

over operating free-air temperature range (unless otherwise noted)

|                     |                                |          |                             | MIN  | MAX | UNIT |

|---------------------|--------------------------------|----------|-----------------------------|------|-----|------|

|                     | Low-level output current       | INT, SDA | $T_j \leqslant 85^{\circ}C$ |      | 6   |      |

| I <sub>OL</sub> (2) |                                |          | T <sub>j</sub> = 105°C      |      | 3   | mA   |

| OL '                |                                |          | T <sub>j</sub> = 125°C      |      | 1.8 | IIIA |

|                     |                                |          | T <sub>j</sub> = 135°C      |      | 1.5 |      |

| T <sub>A</sub>      | Operating free-air temperature |          |                             | - 40 | 125 | °C   |

- (1) For voltages applied above V<sub>CC</sub>, an increase in I<sub>CC</sub> results.

- (2) The values shown apply to specific junction temperatures. See the #9.2.1.1 section on how to calculate the junction temperature.

### **6.4 Thermal Information**

|                        |                                              | TCA9539-Q1 |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC (1)                           | PW (TSSOP) | UNIT |

|                        |                                              | 24 PINS    |      |

| R <sub>0</sub> JA      | Junction-to-ambient thermal resistance       | 108.8      | °C/W |

| R <sub>θ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 54         | °C/W |

| R <sub>0</sub> JB      | Junction-to-board thermal resistance         | 62.8       | °C/W |

| ψJT                    | Junction-to-top characterization parameter   | 11.1       | °C/W |

| ψ ЈВ                   | Junction-to-board characterization parameter | 62.3       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

### 6.5 Electrical Characteristics

over recommended operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER                                       | TEST CONDITIONS                         | V <sub>cc</sub>           | MIN   | TYP (1) | MAX | UNIT |  |

|-------------------|-------------------------------------------------|-----------------------------------------|---------------------------|-------|---------|-----|------|--|

| V <sub>IK</sub>   | Input diode clamp voltage                       | I <sub>I</sub> = - 18 mA                | 1.65 V to 3.6 V           | - 1.2 |         |     | V    |  |

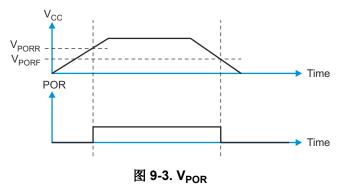

| V <sub>PORR</sub> | Power-on reset voltage, V <sub>CC</sub> rising  | V <sub>I</sub> = V <sub>CC</sub> or GND | 1.65 V to 3.6 V           |       | 1.2     | 1.5 | V    |  |

| V <sub>PORF</sub> | Power-on reset voltage, V <sub>CC</sub> falling | V <sub>I</sub> = V <sub>CC</sub> or GND | 1.65 V to 3.6 V           | 0.75  | 1       |     | V    |  |

|                   |                                                 |                                         | 1.65 V                    | 1.2   |         |     |      |  |

|                   |                                                 |                                         | 2.3 V                     | 1.8   |         |     |      |  |

|                   | P-port high-level output voltage (2)            | $I_{OH} = -8 \text{ mA}$                | 3 V                       | 2.6   |         |     |      |  |

| \ <u>\</u>        |                                                 | nge                                     | 3.6 V                     | 3.3   |         |     |      |  |

| V <sub>OH</sub>   |                                                 |                                         | 1.65 V                    | 1     |         |     |      |  |

|                   |                                                 | L = 10 mA                               | 2.3 V                     | 1.7   |         |     |      |  |

|                   |                                                 |                                         | $I_{OH} = -10 \text{ mA}$ | 3 V   | 2.5     |     |      |  |

|                   |                                                 |                                         | 3.6 V                     | 3.2   |         |     |      |  |

|                   | SDA                                             | V <sub>OL</sub> = 0.4 V                 |                           | 3     |         |     |      |  |

| ļ.                | P port <sup>(3)</sup>                           | V <sub>OL</sub> = 0.5 V                 | 1.65 V to 3.6 V           | 8     |         |     | mA   |  |

| I <sub>OL</sub>   | P port (4)                                      | V <sub>OL</sub> = 0.7 V                 | 1.05 V 10 3.6 V           | 10    |         |     |      |  |

|                   | INT                                             | V <sub>OL</sub> = 0.4 V                 |                           | 3     |         |     |      |  |

|                   | SCL, SDA                                        | V V OND 4.05 V                          | 1 65 V/to 2 6 V/          |       |         | ±1  |      |  |

| I <sub>I</sub>    | A0, A1, RESET                                   | $V_I = V_{CC}$ or GND                   | 1.65 V to 3.6 V           |       |         | ±1  | μA   |  |

| I <sub>IH</sub>   | P port                                          | $V_I = V_{CC}$                          | 1.65 V to 3.6 V           |       |         | 1   | μA   |  |

| I <sub>IL</sub>   | P port                                          | V <sub>I</sub> = GND                    | 1.65 V to 3.6 V           |       |         | - 1 | μA   |  |

# 6.5 Electrical Characteristics (continued)

over recommended operating free-air temperature range (unless otherwise noted)

|                 | PARAMETER      | TEST COND                                                         | ITIONS                                   | V <sub>cc</sub> | MIN | TYP (1) | MAX | UNIT |

|-----------------|----------------|-------------------------------------------------------------------|------------------------------------------|-----------------|-----|---------|-----|------|

|                 |                |                                                                   | _                                        | 3.6 V           |     | 10      | 30  |      |

|                 | Operating mode | $V_I = V_{CC}$ or GND, $I_O = 0$<br>I/O = inputs, $f_{SCI} = 400$ |                                          | 2.7 V           |     | 5       | 19  |      |

|                 |                | inputs, ISCL 400 KHz, No load                                     |                                          | 1.95 V          |     | 4       | 11  |      |

| I <sub>CC</sub> |                | $I_O = 0$ , $I/O = inputs$ , $f_{SCL} = 0$ kHz, no load           |                                          | 3.6 V           |     | 1.1     | 5   |      |

|                 | Standby mode   |                                                                   | $V_{I} = V_{CC}$ $V_{I} = GND$           | 2.7 V           |     | 1       | 4.5 | μΑ   |

|                 |                |                                                                   |                                          | 1.95 V          |     | 0.4     | 3.5 |      |

|                 |                |                                                                   |                                          | 3.6 V           |     | 1.1     | 13  |      |

|                 |                |                                                                   |                                          | 2.7 V           |     | 1       | 9.5 |      |

|                 |                |                                                                   |                                          | 1.95 V          |     | 0.4     | 6.5 |      |

| C <sub>i</sub>  | SCL            | V <sub>I</sub> = V <sub>CC</sub> or GND                           |                                          | 1.65 V to 3.6 V |     | 3       | 8   | pF   |

| _               | SDA            | V = V or CND                                                      |                                          | 1.65 V to 3.6 V |     | 3       | 9.5 | pF   |

| C <sub>io</sub> | P port         | AIO - ACC OL GIAD                                                 | V <sub>IO</sub> = V <sub>CC</sub> or GND |                 |     | 3.7     | 9.5 | pr   |

- (1) All typical values are at nominal supply voltage (1.8 V, 2.5 V, or 3.3 V,  $V_{CC}$ ) and  $T_A$  = 25°C.

- (2) Each I/O must be externally limited to the maximum allowed I<sub>OL</sub>, and each octal (P07 − P00 and P17 − P10) must be limited to a maximum current of 100 mA, for a device total of 200 mA at T<sub>i</sub> ≤ 85°C. See the #6.3 table for more information.

- (3) The total current sourced by all I/Os must be limited to 160 mÅ (80 mA for P07 P00 and 80 mA for P17 P10) for  $T_j \le 85^{\circ}$ C. See the #6.3 table for more information.

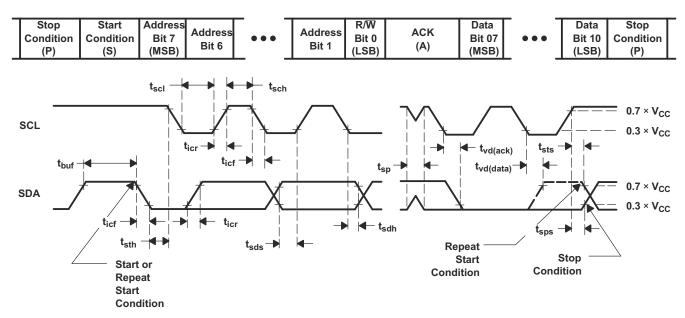

# 6.6 I<sup>2</sup>C Interface Timing Requirements

over recommended operating free-air temperature range (unless otherwise noted) (see <a>\bar{8}</a> 7-1)

|                       |                                                         |                                          | MIN | MAX  | UNIT |

|-----------------------|---------------------------------------------------------|------------------------------------------|-----|------|------|

| I <sup>2</sup> C BUS  | —STANDARD MODE                                          |                                          |     |      |      |

| f <sub>scl</sub>      | I <sup>2</sup> C clock frequency                        |                                          | 0   | 100  | kHz  |

| t <sub>sch</sub>      | I <sup>2</sup> C clock high time                        |                                          | 4   |      | μs   |

| t <sub>scl</sub>      | I <sup>2</sup> C clock low time                         |                                          | 4.7 |      | μs   |

| t <sub>sp</sub>       | I <sup>2</sup> C spike time                             |                                          |     | 50   | ns   |

| t <sub>sds</sub>      | I <sup>2</sup> C serial-data setup time                 |                                          | 250 |      | ns   |

| t <sub>sdh</sub>      | I <sup>2</sup> C serial-data hold time                  |                                          | 0   |      | ns   |

| t <sub>icr</sub>      | I <sup>2</sup> C input rise time                        |                                          |     | 1000 | ns   |

| t <sub>icf</sub>      | I <sup>2</sup> C input fall time                        |                                          |     | 300  | ns   |

| t <sub>ocf</sub>      | I <sup>2</sup> C output fall time                       | 10 pF to 400 pF bus                      |     | 300  | ns   |

| t <sub>buf</sub>      | I <sup>2</sup> C bus free time between stop and sta     | rt                                       | 4.7 |      | μs   |

| t <sub>sts</sub>      | I <sup>2</sup> C start or repeated start condition set  | ир                                       | 4.7 |      | μs   |

| t <sub>sth</sub>      | I <sup>2</sup> C start or repeated start condition hole | d                                        | 4   |      | μs   |

| t <sub>sps</sub>      | I <sup>2</sup> C stop condition setup                   |                                          | 4   |      | μs   |

| t <sub>vd(data)</sub> | Valid data time                                         | SCL low to SDA output valid              |     | 3.45 | μs   |

| t <sub>vd(ack)</sub>  | Valid data time of ACK condition                        | ACK signal from SCL low to SDA (out) low |     | 3.45 | μs   |

| C <sub>b</sub>        | I <sup>2</sup> C bus capacitive load                    |                                          |     | 400  | pF   |

|                                |                                  | MIN | MAX | UNIT |  |  |

|--------------------------------|----------------------------------|-----|-----|------|--|--|

| I <sup>2</sup> C BUS—FAST MODE |                                  |     |     |      |  |  |

| f <sub>scl</sub>               | I <sup>2</sup> C clock frequency | 0   | 400 | kHz  |  |  |

| t <sub>sch</sub>               | I <sup>2</sup> C clock high time | 0.6 |     | μs   |  |  |

| t <sub>scl</sub>               | I <sup>2</sup> C clock low time  | 1.3 |     | μs   |  |  |

| t <sub>sp</sub>                | I <sup>2</sup> C spike time      |     | 50  | ns   |  |  |

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

MAX UNIT MIN I<sup>2</sup>C serial-data setup time 100 ns  $t_{\sf sds}$ I<sup>2</sup>C serial-data hold time 0 ns  $t_{sdh}$ t<sub>icr</sub> I<sup>2</sup>C input rise time 20 300 ns  $20 \times (V_{CC} /$ I<sup>2</sup>C input fall time 300 ticf ns 5.5 V)  $20 \times (V_{CC} /$ I<sup>2</sup>C output fall time 10 pF to 400 pF bus 300  $t_{ocf}$ ns 5.5 V) I<sup>2</sup>C bus free time between stop and start 1.3  $t_{buf}$ μs I<sup>2</sup>C start or repeated start condition setup 0.6 μs  $t_{sts}$ I<sup>2</sup>C start or repeated start condition hold 0.6 μs  $t_{sth}$ I<sup>2</sup>C stop condition setup 0.6  $t_{sps}$ μs Valid data time SCL low to SDA output valid 0.9 μs t<sub>vd(data)</sub> ACK signal from SCL low to Valid data time of ACK condition 0.9 μs t<sub>vd(ack)</sub> SDA (out) low  $C_{\mathsf{b}}$ I<sup>2</sup>C bus capacitive load 400 pF

# **6.7 RESET Timing Requirements**

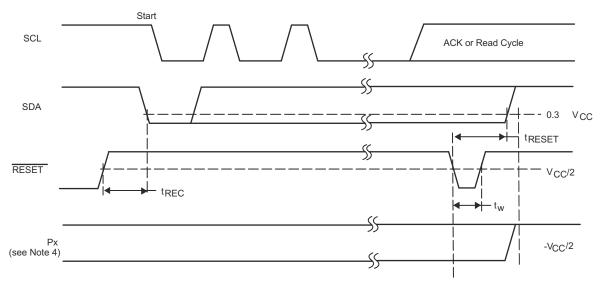

over recommended operating free-air temperature range (unless otherwise noted) (see 图 7-4)

|                  |                                                   | MIN MA | X UNIT |

|------------------|---------------------------------------------------|--------|--------|

| t <sub>W</sub>   | Reset pulse duration                              | 6      | ns     |

| t <sub>REC</sub> | Reset recovery time                               | 0      | ns     |

| •                | Time to reset; For V <sub>CC</sub> =2.3 V - 3.6 V | 400    | ns     |

| RESET            | Time to reset; For $V_{CC}$ = 1.65 V $-$ 2.3 V    | 550    | ns     |

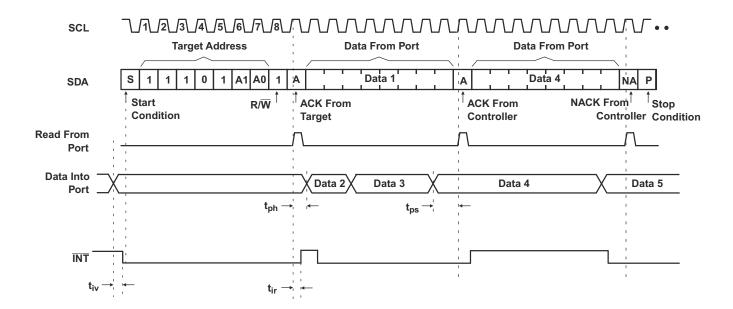

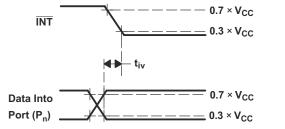

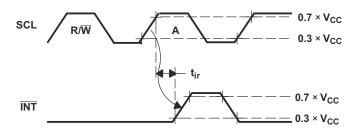

# 6.8 Switching Characteristics

over recommended operating free-air temperature range,  $C_L \le 100$  pF (unless otherwise noted) (see  $\boxtimes$  7-2 and  $\boxtimes$  7-3)

|                 | PARAMETER                                               | FROM<br>(INPUT) | TO<br>(OUTPUT) | MIN MAX | UNIT |

|-----------------|---------------------------------------------------------|-----------------|----------------|---------|------|

| t <sub>iv</sub> | Interrupt valid time                                    | P port          | ĪNT            | 4       | μs   |

| t <sub>ir</sub> | Interrupt reset delay time                              | SCL             | ĪNT            | 4       | μs   |

| t <sub>pv</sub> | Output data valid; For V <sub>CC</sub> = 2.3 V - 3.6 V  |                 |                | 200     | ns   |

|                 | Output data valid; For V <sub>CC</sub> = 1.65 V - 2.3 V |                 | P port         | 300     | ns   |

| t <sub>ps</sub> | Input data setup time                                   | P port          | SCL            | 150     | ns   |

| t <sub>ph</sub> | Input data hold time                                    | P port          | SCL            | 1       | μs   |

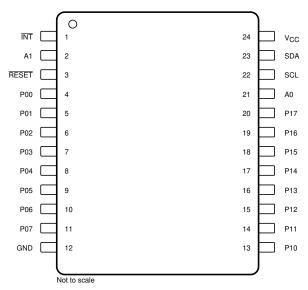

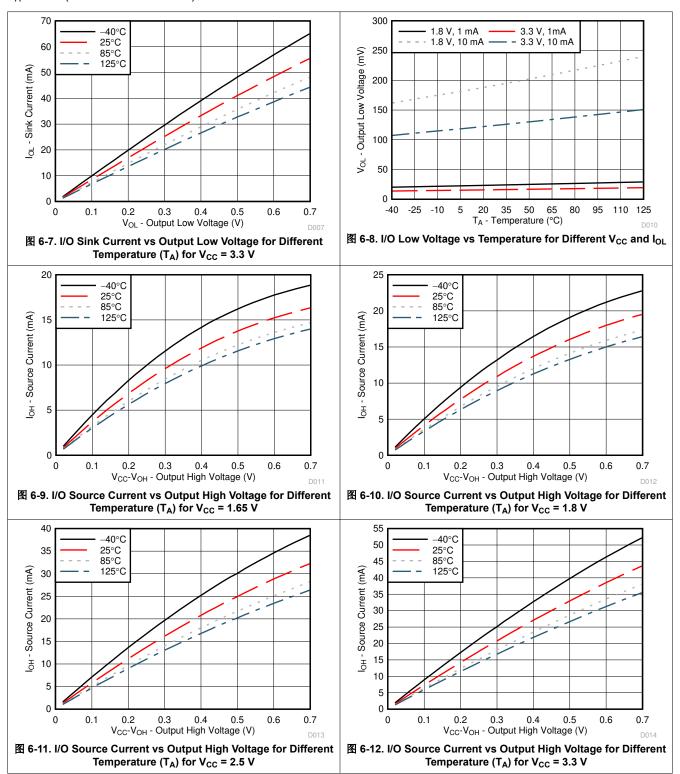

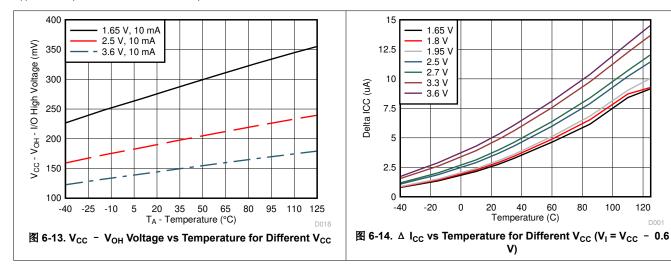

### **6.9 Typical Characteristics**

T<sub>A</sub> = 25°C (unless otherwise noted)

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

# 6.9 Typical Characteristics (continued)

T<sub>A</sub> = 25°C (unless otherwise noted)

# **6.9 Typical Characteristics (continued)**

T<sub>A</sub> = 25°C (unless otherwise noted)

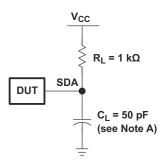

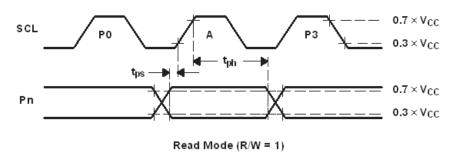

## 7 Parameter Measurement Information

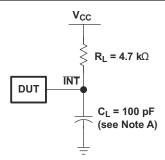

**SDA Load Configuration**

Voltage Waveforms

| BYTE | DESCRIPTION              |  |  |  |  |

|------|--------------------------|--|--|--|--|

| 1    | I <sup>2</sup> C address |  |  |  |  |

| 2, 3 | P-port data              |  |  |  |  |

- A. C<sub>L</sub> includes probe and jig capacitance.

- B. All inputs are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0$  = 50  $\Omega$ ,  $t_r/t_f \leq$  30 ns.

- C. All parameters and waveforms are not applicable to all devices.

图 7-1. I<sup>2</sup>C Interface Load Circuit and Voltage Waveforms

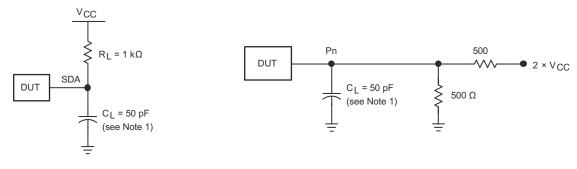

**Interrupt Load Configuration**

- A. C<sub>I</sub> includes probe and jig capacitance.

- B. All inputs are supplied by generators having the following characteristics: PRR  $\leq$  10 Hz,  $Z_O$  = 50  $\Omega$ ,  $t_r/t_f \leq$  30 ns.

- C. All parameters and waveforms are not applicable to all devices.

图 7-2. Interrupt Load Circuit and Voltage Waveforms

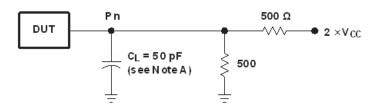

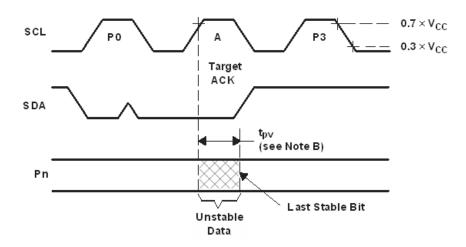

P-P ort Load Configuration

Write Mode (R/W = 0)

- A. C<sub>L</sub> includes probe and jig capacitance.

- B.  $t_{pv}$  is measured from 0.7 ×  $V_{CC}$  on SCL to 50% I/O ( $P_n$ ) output.

- C. All inputs are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_O$  = 50  $\Omega$ ,  $t_f/t_f \leq$  30 ns.

- D. The outputs are measured one at a time, with one transition per measurement.

- E. All parameters and waveforms are not applicable to all devices.

图 7-3. P-Port Load Circuit and Voltage Waveforms

SDA Load Configuration

P-Port Load Configuration

- A. C<sub>L</sub> includes probe and jig capacitance.

- B. All inputs are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_O$  = 50  $\Omega$ ,  $t_f/t_f \leq$  30 ns.

- C. The outputs are measured one at a time, with one transition per measurement.

- D. I/Os are configured as inputs.

- E. All parameters and waveforms are not applicable to all devices.

图 7-4. Reset Load Circuits and Voltage Waveforms

# 8 Detailed Description

### 8.1 Overview

The TCA9539-Q1 is a 16-bit I/O expander for the two-line bidirectional bus ( $I^2C$ ) designed for 1.65 V to 3.6 V,  $V_{CC}$  operation. It provides general-purpose remote I/O expansion for most microcontroller families via the  $I^2C$  interface, serial clock (SCL) and serial data (SDA).

The TCA9539-Q1 consists of two 8-bit Configuration (input or output selection), Input Port, Output Port, and Polarity Inversion (active-high or active-low operation) registers. At power-on, the I/Os are configured as inputs. The system controller can enable the I/Os as either inputs or outputs by writing to the configuration register bits. The data for each input or output is kept in the corresponding Input or output register. The polarity of the Input Port register can be inverted with the Polarity Inversion register. All registers can be read by the system controller.

The system controller can reset the TCA9539-Q1 in the event of a time-out or other improper operation by asserting a low in the  $\overline{\text{RESET}}$  input. The power-on reset puts the registers in their default state and initializes the I<sup>2</sup>C-SMBus state machine. Asserting  $\overline{\text{RESET}}$  causes the same reset-initialization to occur without depowering the part.

The TCA9539-Q1 open-drain interrupt (  $\overline{\text{INT}}$ ) output is activated when any input state differs from its corresponding Input Port register state and is used to indicate to the system controller that an input state has changed.

INT can be connected to the interrupt input of a microcontroller. By sending an interrupt signal on this line, the remote I/O can inform the microcontroller if there is incoming data on its ports without having to communicate via the I<sup>2</sup>C bus. Thus, the TCA9539-Q1 can remain a simple target device.

The TCA9539-Q1 is similar to the TCA9555, except for the removal of the internal I/O pull-up resistor, which greatly reduces power consumption when the I/Os are held low, replacement of A2 with  $\overline{RESET}$ , and a different address range. The TCA9539-Q1 is similar to the PCA9539 with lower voltage support (down to  $V_{CC}$  = 1.65 V), and also improved power-on reset circuitry for different application scenarios.

Two hardware pins (A0 and A1) are used to program and vary the fixed I<sup>2</sup>C address and allow up to four devices to share the same I<sup>2</sup>C bus or SMBus.

Copyright © 2021 Texas Instruments Incorporated

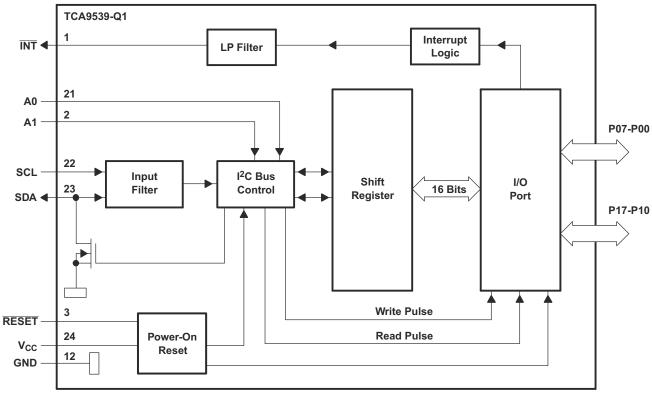

# 8.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

Pin numbers shown are for PW package.

All I/Os are set to inputs at reset.

图 8-1. Logic Diagram (Positive Logic)

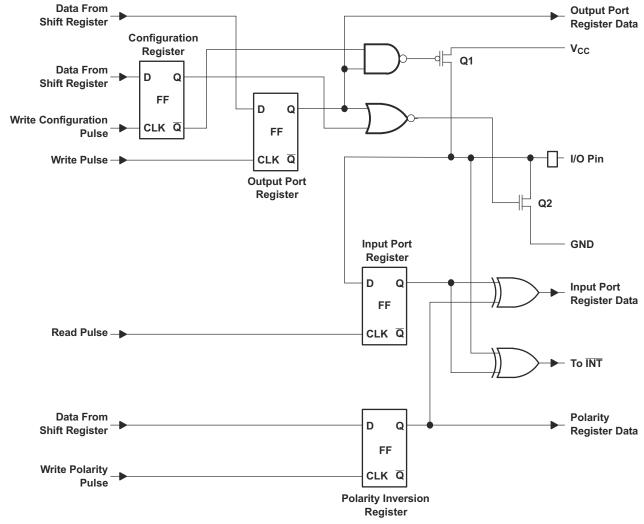

Copyright © 2016, Texas Instruments Incorporated

At power-on reset, all registers return to default values.

图 8-2. Simplified Schematic of P-Port I/Os

# 8.3 Feature Description

#### 8.3.1 I/O Port

When an I/O is configured as an input, FETs Q1 and Q2 are off, which creates a high-impedance input. The input voltage may be raised above  $V_{CC}$  to a maximum of 5.5 V.

If the I/O is configured as an output, Q1 or Q2 is enabled, depending on the state of the Output Port register. In this case, there are low-impedance paths between the I/O pin and either  $V_{CC}$  or GND. The external voltage applied to this I/O pin must not exceed the recommended levels for proper operation.

## 8.3.2 RESET Input

A reset can be accomplished by holding the  $\overline{\text{RESET}}$  pin low for a minimum of  $t_W$ . The TCA9539-Q1 registers and  $I^2\text{C-SMBus}$  state machine are held in their default states until  $\overline{\text{RESET}}$  is once again high. This input requires a pull-up resistor to  $V_{\text{CC}}$ , if no active connection is used.

#### 8.3.3 Interrupt (INT) Output

An interrupt is generated by any rising or falling edge of the port inputs in the input mode. After time,  $t_{iv}$ , the signal  $\overline{INT}$  is valid. Resetting the interrupt circuit is achieved when data on the port is changed to the original setting or data is read from the port that generated the interrupt. Resetting occurs in the read mode at the

acknowledge (ACK) bit after the rising edge of the SCL signal. Note that the  $\overline{\text{INT}}$  is reset at the ACK just before the byte of changed data is sent. Interrupts that occur during the ACK clock pulse can be lost (or be very short) because of the resetting of the interrupt during this pulse. Each change of the I/Os after resetting is detected and is transmitted as  $\overline{\text{INT}}$ .

Reading from or writing to another device does not affect the interrupt circuit, and a pin configured as an output cannot cause an interrupt. Changing an I/O from an output to an input may cause a false interrupt to occur if the state of the pin does not match the contents of the Input Port register. Because each 8-bit port is read independently, the interrupt caused by port 0 is not cleared by a read of port 1, or vice versa.

INT has an open-drain structure and requires a pull-up resistor to V<sub>CC</sub>.

#### 8.4 Device Functional Modes

#### 8.4.1 Power-On Reset

When power (from 0 V) is applied to  $V_{CC}$ , an internal power-on reset holds the TCA9539-Q1 in a reset condition until  $V_{CC}$  has reached  $V_{PORR}$ . At that point, the reset condition is released and the TCA9539-Q1 registers and I<sup>2</sup>C-SMBus state machine initialize to their default states. After that,  $V_{CC}$  must be lowered to  $V_{PORF}$  and then back up to the operating voltage for a power-reset cycle. See 8-3.

### 8.5 Programming

### 8.5.1 I<sup>2</sup>C Interface

The TCA9539-Q1 has a standard bidirectional  $I^2C$  interface that is controlled by a controller device in order to be configured or read the status of this device. Each target on the  $I^2C$  bus has a specific device address to differentiate between other target devices that are on the same  $I^2C$  bus. Many target devices require configuration upon startup to set the behavior of the device. This is typically done when the controller accesses internal register maps of the target, which have unique register addresses. A device can have one or multiple registers where data is stored, written, or read. For more information see *Understanding the I^2C Bus*, SLVA704.

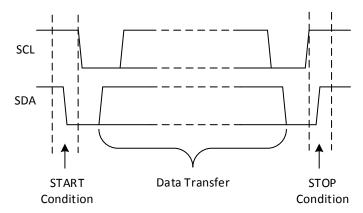

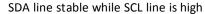

The physical  $I^2C$  interface consists of the serial clock (SCL) and serial data (SDA) lines. Both SDA and SCL lines must be connected to  $V_{CC}$  through a pull-up resistor. The size of the pull-up resistor is determined by the amount of capacitance on the  $I^2C$  lines. For further details, see  $I^2C$  Pull-up Resistor Calculation, SLVA689. Data transfer may be initiated only when the bus is idle. A bus is considered idle if both SDA and SCL lines are high after a STOP condition. See  $\frac{1}{2}$  8-1.

图 8-3 and 图 8-4 show the general procedure for a controller to access a target device:

- 1. If a controller wants to send data to a target:

- Controller-transmitter sends a START condition and addresses the target-receiver.

- · Controller-transmitter sends data to target-receiver.

- Controller-transmitter terminates the transfer with a STOP condition.

- 2. If a controller wants to receive or read data from a target:

- Controller-receiver sends a START condition and addresses the target-transmitter.

- · Controller-receiver sends the requested register to read to target-transmitter.

- Controller-receiver receives data from the target-transmitter.

· Controller-receiver terminates the transfer with a STOP condition.

图 8-3. Definition of Start and Stop Conditions

图 8-4. Bit Transfer

表 8-1 shows the interface definition.

表 8-1. Interface Definition

| BYTE                            | BIT     |     |     |     |     |     |     |         |  |  |

|---------------------------------|---------|-----|-----|-----|-----|-----|-----|---------|--|--|

| BITE                            | 7 (MSB) | 6   | 5   | 4   | 3   | 2   | 1   | 0 (LSB) |  |  |

| I <sup>2</sup> C target address | Н       | Н   | Н   | L   | Н   | A1  | A0  | R/W     |  |  |

| P0x I/O data bus                | P07     | P06 | P05 | P04 | P03 | P02 | P01 | P00     |  |  |

| P1x I/O data bus                | P17     | P16 | P15 | P14 | P13 | P12 | P11 | P10     |  |  |

# 8.6 Register Maps

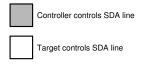

#### 8.6.1 Device Address

8-5 shows the address byte of the TCA9539-Q1.

图 8-5. TCA9539-Q1 Address

表 8-2 shows the address reference of the TCA9539-Q1.

表 8-2. Address Reference

| INP | UTS | I <sup>2</sup> C BUS TARGET ADDRESS |

|-----|-----|-------------------------------------|

| A1  | A0  | I C BUS IARGET ADDRESS              |

| L   | L   | 116 (decimal), 74 (hexadecimal)     |

| L   | Н   | 117 (decimal), 75 (hexadecimal)     |

| Н   | L   | 118 (decimal), 76 (hexadecimal)     |

| Н   | Н   | 119 (decimal), 77 (hexadecimal)     |

The last bit of the target address defines the operation (read or write) to be performed. A high (1) selects a read operation, while a low (0) selects a write operation.

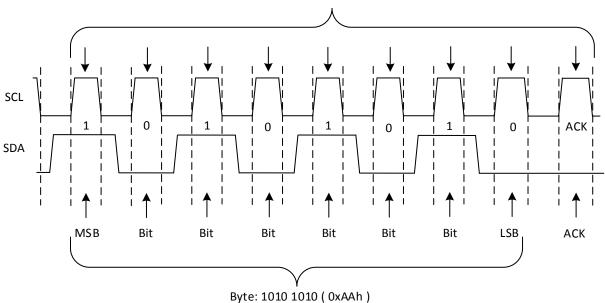

#### 8.6.2 Control Register And Command Byte

Following the successful acknowledgment of the address byte, the bus controller sends a command byte shown in  $\frac{1}{8}$  8-3 that is stored in the control register in the TCA9539-Q1. Three bits of this data byte state the operation (read or write) and the internal register (input, output, Polarity Inversion or Configuration) that is affected. This register can be written or read through the  $I^2C$  bus. The command byte is sent only during a write transmission.

When a command byte has been sent, the register pair that was addressed continues to be accessed by reads until a new command byte has been sent. 🛭 8-6 shows the control register bits.

图 8-6. Control Register Bits

表 8-3. Command Byte

| CONTRO | DL REGISTE | R BITS | COMMAND    | REGISTER                  | PROTOCOL        | POWER-UP  |

|--------|------------|--------|------------|---------------------------|-----------------|-----------|

| B2     | B1         | В0     | BYTE (HEX) | REGISTER                  | PROTOCOL        | DEFAULT   |

| 0      | 0          | 0      | 0x00       | Input Port 0              | Read byte       | XXXX XXXX |

| 0      | 0          | 1      | 0x01       | Input Port 1              | Read byte       | XXXX XXXX |

| 0      | 1          | 0      | 0x02       | Output Port 0             | Read-write byte | 1111 1111 |

| 0      | 1          | 1      | 0x03       | Output Port 1             | Read-write byte | 1111 1111 |

| 1      | 0          | 0      | 0x04       | Polarity Inversion Port 0 | Read-write byte | 0000 0000 |

| 1      | 0          | 1      | 0x05       | Polarity Inversion Port 1 | Read-write byte | 0000 0000 |

| 1      | 1          | 0      | 0x06       | Configuration Port 0      | Read-write byte | 1111 1111 |

| 1      | 1          | 1      | 0x07       | Configuration Port 1      | Read-write byte | 1111 1111 |

Submit Document Feedback

#### 8.6.3 Register Descriptions

The Input Port registers (registers 0 and 1) shown in 表 8-4 reflect the incoming logic levels of the pins, regardless of whether the pin is defined as an input or an output by the Configuration register. It only acts on read operation. Writes to these registers have no effect. The default value, X, is determined by the externally applied logic level.

Before a read operation, a write transmission is sent with the command byte to indicate to the  $I^2C$  device that the Input Port register is accessed next.

表 8-4. Registers 0 And 1 (Input Port Registers)

| Bit     | 10.7 | 10.6 | 10.5 | 10.4 | 10.3 | 10.2 | 10.1 | 10.0 |

|---------|------|------|------|------|------|------|------|------|

| Default | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| Bit     | I1.7 | I1.6 | I1.5 | I1.4 | I1.3 | I1.2 | I1.1 | I1.0 |

| Default | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

The Output Port registers (registers 2 and 3) shown in  $\frac{1}{8}$  8-5 show the outgoing logic levels of the pins defined as outputs by the Configuration register. Bit values in this register have no effect on pins defined as inputs. In turn, reads from this register reflect the value that is in the flip-flop controlling the output selection, not the actual pin value.

表 8-5. Registers 2 And 3 (Output Port Registers)

| Bit     | O0.7 | O0.6 | O0.5 | O0.4 | O0.3 | O0.2 | O0.1 | O0.0 |

|---------|------|------|------|------|------|------|------|------|

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| Bit     | 01.7 | O1.6 | O1.5 | 01.4 | O1.3 | 01.2 | 01.1 | O1.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

The Polarity Inversion registers (registers 4 and 5) shown in  $\frac{1}{8}$  8-6 allow Polarity Inversion of pins defined as inputs by the Configuration register. If a bit in this register is set (written with 1), the corresponding port pin's polarity is inverted. If a bit in this register is cleared (written with a 0), the corresponding port pin's original polarity is retained.

表 8-6. Registers 4 And 5 (Polarity Inversion Registers)

|         | •    | •    |      | `    |      | _    | ,    |      |

|---------|------|------|------|------|------|------|------|------|

| Bit     | N0.7 | N0.6 | N0.5 | N0.4 | N0.3 | N0.2 | N0.1 | N0.0 |

| Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| Bit     | N1.7 | N1.6 | N1.5 | N1.4 | N1.3 | N1.2 | N1.1 | N1.0 |

| Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

The Configuration registers (registers 6 and 7) shown in  $\frac{1}{8}$  8-7 configure the directions of the I/O pins. If a bit in this register is set to 1, the corresponding port pin is enabled as an input with a high-impedance output driver. If a bit in this register is cleared to 0, the corresponding port pin is enabled as an output.

表 8-7. Registers 6 And 7 (Configuration Registers)

|         | • •  | •    |      | •    | •    | -    | ,    |      |

|---------|------|------|------|------|------|------|------|------|

| Bit     | C0.7 | C0.6 | C0.5 | C0.4 | C0.3 | C0.2 | C0.1 | C0.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| Bit     | C1.7 | C1.6 | C1.5 | C1.4 | C1.3 | C1.2 | C1.1 | C1.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

#### 8.6.3.1 Bus Transactions

Data is exchanged between the controller and the TCA9539-Q1 through write and read commands, and this is accomplished by reading from or writing to registers in the target device.

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

Registers are locations in the memory of the target which contain information, whether it be the configuration information or some sampled data to send back to the controller. The controller must write information to these registers in order to instruct the target device to perform a task.

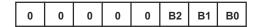

#### 8.6.3.1.1 Writes

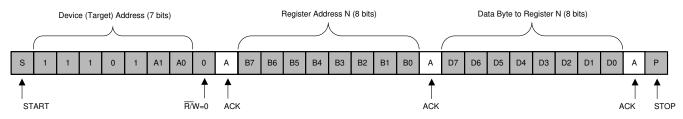

To write on the  $I^2C$  bus, the controller sends a START condition on the bus with the address of the target, as well as the last bit (the R/ $\overline{W}$  bit) set to 0, which signifies a write. After the target sends the acknowledge bit, the controller then sends the register address of the register to which it wishes to write. The target acknowledges again, letting the controller know it is ready. After this, the controller starts sending the register data to the target until the controller has sent all the data necessary (which is sometimes only a single byte), and the controller terminates the transmission with a STOP condition.

See the #8.6.2 section to see list of the TCA9539-Q1s internal registers and a description of each one.

8-7 shows an example of writing a single byte to a target register.

■ 8-7 shows an example of writing a single byte to a target register.

■ 8-7 shows an example of writing a single byte to a target register.

■ 8-7 shows an example of writing a single byte to a target register.

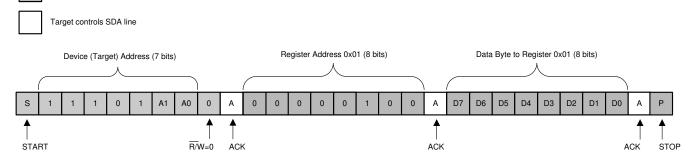

■ 8-8 shows an example of writing a single byte to a target register.

■ 8-8 shows an example of writing a single byte to a target register.

■ 8-8 shows an example of writing a single byte to a target register.

■ 8-8 shows an example of writing a single byte to a target register.

■ 8-8 shows an example of writing a single byte to a target register.

■ 8-8 shows a shows a shows a shows a show a

Write to one register in a device

Controller controls SDA line

图 8-7. Write to Register

8-9 shows the Write to the Polarity Inversion Register.

图 8-8. Write to the Polarity Inversion Register

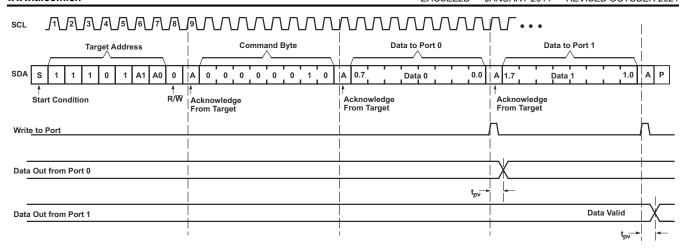

8-9 shows the Write to Output Port Registers

图 8-9. Write to Output Port Registers

#### 8.6.3.1.2 Reads

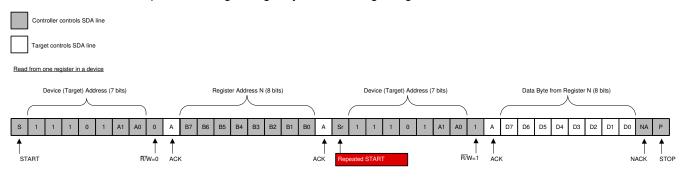

Reading from a target is very similar to writing, but requires some additional steps. In order to read from a target, the controller must first instruct the target which register it wishes to read from. This is done by the controller starting off the transmission in a similar fashion as the write, by sending the address with the R/ $\overline{W}$  bit equal to 0 (signifying a write), followed by the register address it wishes to read from. When the target acknowledges this register address, the controller sends a START condition again, followed by the target address with the R/ $\overline{W}$  bit set to 1 (signifying a read). This time, the target acknowledges the read request, and the controller releases the SDA bus but continues supplying the clock to the target. During this part of the transaction, the controller becomes the controller-receiver, and the target becomes the target-transmitter.

The controller continues to send out the clock pulses, but releases the SDA line so that the target can transmit data. At the end of every byte of data, the controller sends an ACK to the target, letting the target know that it is ready for more data. When the controller has received the number of bytes it is expecting, it sends a NACK, signaling to the target to halt communications and release the bus. The controller follows this up with a STOP condition.

If a read is requested by the controller after a POR without first setting the command byte via a write, the device NACKs until a command byte-register address is set as described above.

See the #8.6.2 section to see list of the TCA9539-Q1s internal registers and a description of each one.

8-10 shows an example of reading a single byte from a target register.

图 8-10. Read from Register

When a restart occurs after a single write request to a register, the requested register is used for the read request. Note that when reading multiple bytes of data. Data is clocked into the register on the rising edge of the ACK clock pulse before data is sent. The internal register value is also changed to the other register of the pair on the rising edge of the ACK clock pulse before data is sent. After the first byte is read, additional bytes may be read, but the data now reflect the information in the other register in the pair. For example, if Input Port 1 is read,

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

the next byte read is Input Port 0. If a restart occurs during a read, the data is lost because the internal register already has been changed to the next register in the pair.

There is no limitation on the number of data bytes received in one read transmission, but when the final byte is received, the bus controller must not acknowledge the data.

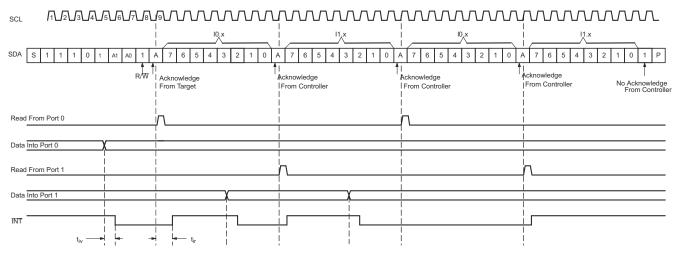

8 8-11 and 8 8-12 show two different scenarios of Read Input Port Register.

Transfer of data can be stopped at any time by a Stop condition. When this occurs, data present at the latest acknowledge phase is valid (output mode). It is assumed that the command byte previously has been set to 00 (Read Input Port register).

This figure eliminates the command byte transfer, a restart, and target address call between the initial target address call and actual data transfer from the P port (see the # 8.6.3.1.2 section for these details).

$\overline{\mathcal{M}}_{\mathcal{M}} \overline{\mathcal{M}}_{\mathcal{M}} \overline{\mathcal$ SCL Acknowledge From Target Acknowledge From Controller Acknowledge Acknowledge R/W From Controlle From Controlle No Acknowledge From Controller Read From Port 0 Data Into Port 0 Data 00 Data 01 Read From Port 1 Data Into Port 1 INT

图 8-11. Read Input Port Register, Scenario 1

Transfer of data can be stopped at any time by a Stop condition. When this occurs, data present at the latest acknowledge phase is valid (output mode). It is assumed that the command byte previously has been set to 00 (Read Input Port register).

This figure eliminates the command byte transfer, a restart, and target address call between the initial target address call and actual data transfer from the P port (see the # 8.6.3.1.2 section for these details).

图 8-12. Read Input Port Register, Scenario 2

# **Application and Implementation**

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 9.1 Application Information

Applications of the TCA9539-Q1 has this device connected as a target to an I<sup>2</sup>C controller (processor), and the I<sup>2</sup>C bus may contain any number of other target devices. The TCA9539-Q1 is typically in a remote location from the controller, placed close to the GPIOs to which the controller needs to monitor or control.

IO Expanders such as the TCA9539-Q1 are typically used for controlling LEDs (for feedback or status lights), controlling enable or reset signals of other devices, and even reading the outputs of other devices or buttons.

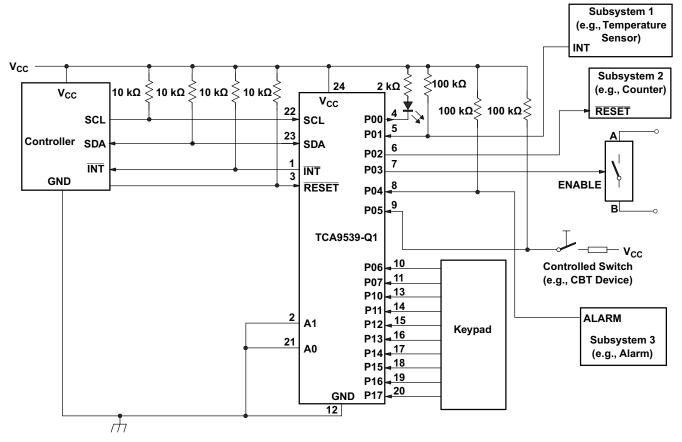

# 9.2 Typical Application

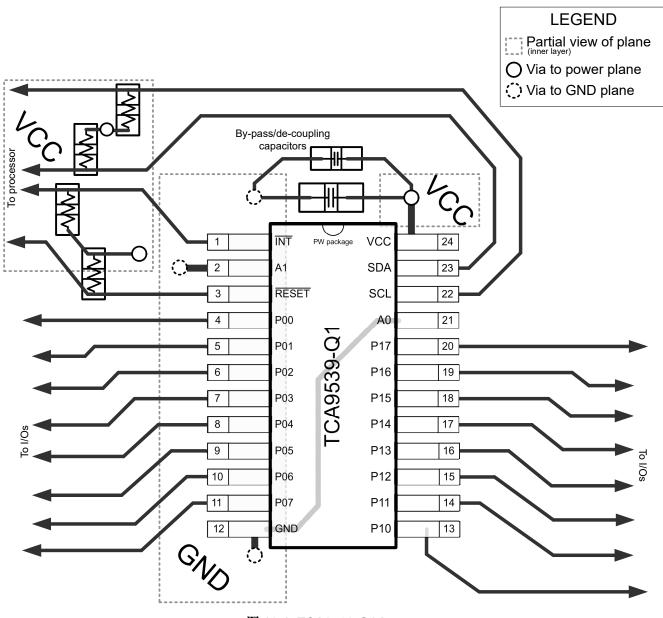

§ 9-1 shows an application in which the TCA9539-Q1 can be used.

Device address is configured as 1110100 for this example.

P00, P02, and P03 are configured as outputs.

P01 and P04 to P17 are configured as inputs.

Pin numbers shown are for the PW package.

图 9-1. Application Schematic

#### 9.2.1 Design Requirements

#### 9.2.1.1 Calculating Junction Temperature and Power Dissipation

When designing with the TCA9539-Q1, it is important that the # 6.3 not be violated. Many of the parameters of this device are rated based on junction temperature, so junction temperature must be calculated in order to verify that safe operation of the device is met. The basic equation for junction temperature is shown in 1.

$$T_{j} = T_{A} + (\theta_{JA} \times P_{d})$$

(1)

$$P_{d} \approx \left(I_{CC\_STATIC} \times V_{CC}\right) + \sum P_{d\_PORT\_L} + \sum P_{d\_PORT\_H}$$

(2)

方程式 2 is the approximation of power dissipation in the device. The equation is the static power plus the summation of power dissipated by each port (with a different equation based on if the port is outputting high, or outputting low. If the port is set as an input, then power dissipation is the input leakage of the pin multiplied by the voltage on the pin). Note that this ignores power dissipation in the  $\overline{\text{INT}}$  and SDA pins, assuming these transients to be small. They can easily be included in the power dissipation calculation by using to calculate the power dissipation in  $\overline{\text{INT}}$  or SDA while they are pulling low, and this gives maximum power dissipation.

$$P_{d\_PORT\_L} = (I_{OL} \times V_{OL})$$

(3)

方程式 3 shows the power dissipation for a single port which is set to output low. The power dissipated by the port is the  $V_{OL}$  of the port multiplied by the current it is sinking.

$$P_{d\_PORT\_H} = \left(I_{OH} \times (V_{CC} - V_{OH})\right) \tag{4}$$

方程式 4 shows the power dissipation for a single port which is set to output high. The power dissipated by the port is the current sourced by the port multiplied by the voltage drop across the device (difference between  $V_{CC}$  and the output voltage).

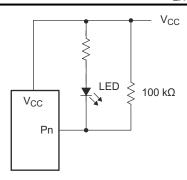

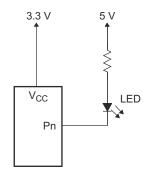

# 9.2.1.2 Minimizing I<sub>CC</sub> When I/Os Control LEDs

When an I/O is used to control an LED, normally it is connected to  $V_{CC}$  through a resistor (see  $\boxtimes$  9-1). Because the LED acts as a diode, when the LED is off, the I/O  $V_{IN}$  is about 1.2 V less than  $V_{CC}$ . The  $\triangle$   $I_{CC}$  parameter in the # 6.5 table show how  $I_{CC}$  increases as  $V_{IN}$  becomes lower than  $V_{CC}$ . For battery-powered applications, it is essential that the voltage of I/O pins is greater than or equal to  $V_{CC}$ , when the LED is off, to minimize current consumption.

$\boxtimes$  9-2 shows a high-value resistor in parallel with the LED.  $\boxtimes$  9-3 shows  $V_{CC}$  less than the LED supply voltage by at least 1.2 V. Both of these methods maintain the I/O  $V_{CC}$  at or above  $V_{CC}$  and prevent additional supply-current consumption when the LED is off.

Take care to make sure that the recommended maximum  $I_{OL}$  through the ports not be violated based upon junction temperature. See the #6.3 for more information.

图 9-2. High-Value Resistor In Parallel With LED

图 9-3. Device Supplied By Lower Voltage

#### 9.2.2 Detailed Design Procedure

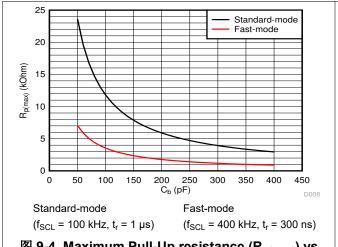

The pull-up resistors,  $R_P$ , for the SCL and SDA lines need to be selected appropriately and take into consideration the total capacitance of all targets on the  $I^2C$  bus. The minimum pull-up resistance is a function of  $V_{CC}$ ,  $V_{OL.(max)}$ , and  $I_{OL}$  as shown in  $\bar{\jmath}$   $\bar{z}$  5.

$$R_{p(min)} = \frac{V_{CC} - V_{OL(max)}}{I_{OL}}$$

(5)

The maximum pull-up resistance is a function of the maximum rise time,  $t_r$  (300 ns for fast-mode operation,  $f_{SCL}$  = 400 kHz) and bus capacitance,  $C_b$  as shown in 方程式 6.

$$R_{p(max)} = \frac{t_r}{0.8473 \times C_b}$$

(6)

The maximum bus capacitance for an  $I^2C$  bus must not exceed 400 pF for standard-mode or fast-mode operation. The bus capacitance can be approximated by adding the capacitance of the TCA9539-Q1,  $C_i$  for SCL or  $C_{io}$  for SDA, the capacitance of wires, connections, traces, and the capacitance of additional targets on the bus.

## 9.2.3 Application Curves

图 9-4. Maximum Pull-Up resistance  $(R_{p(max)})$  vs Bus Capacitance  $(C_b)$

图 9-5. Minimum Pull-Up Resistance ( $R_{p(min)}$ ) vs Pull-Up Reference Voltage ( $V_{CC}$ )

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

# 9 Power Supply Recommendations

# 9.1 Power-On Reset Requirements

In the event of a glitch or data corruption, TCA9539-Q1 can be reset to its default conditions by using the poweron reset feature. Power-on reset requires that the device go through a power cycle to be completely reset. This reset also happens when the device is powered on for the first time in an application.

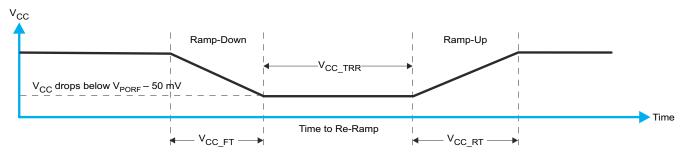

图 9-1.  $V_{CC}$  is Lowered Below the POR Threshold, then Ramped Back Up to  $V_{CC}$

表 9-1 specifies the performance of the power-on reset feature for TCA9539-Q1.

表 9-1. Recommended Supply Sequencing And Ramp Rates (1)

|                     | ** Tricoommonada Cappiy Coquonon                                                                                              | ng / ma rtamp rt | 4100 |     |     |            |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------|------|-----|-----|------------|

|                     | PARAMETER                                                                                                                     |                  | MIN  | TYP | MAX | UNIT       |

| V <sub>CC_FT</sub>  | Fall rate                                                                                                                     | See 图 9-1        | 0.1  |     |     | ms         |

| V <sub>CC_RT</sub>  | Rise rate                                                                                                                     | See 图 9-1        | 0.1  |     |     | ms         |

| V <sub>CC_TRR</sub> | Time to re-ramp (when $V_{CC}$ drops to $V_{POR\_MIN}{}^-50$ mV or when $V_{CC}$ drops to GND)                                | See 图 9-1        | 2    |     |     | μ <b>S</b> |

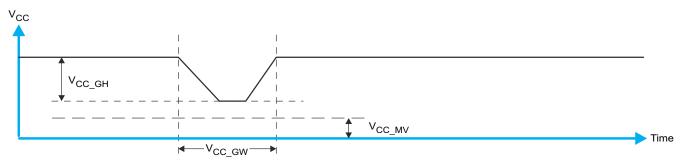

| V <sub>CC_GH</sub>  | The level (referenced to $V_{CC}$ ) that $V_{CC}$ can glitch down to, but not cause a functional disruption when $V_{CC\_GW}$ | See 图 9-2        |      |     | 1.2 | V          |

| V <sub>CC_MV</sub>  | The minimum voltage that $V_{CC}$ can glitch down to without causing a reset ( $V_{CC\_GH}$ must not be violated)             | See 图 9-2        | 1.5  |     |     | V          |

| V <sub>CC_GW</sub>  | Glitch width that does not cause a functional disruption                                                                      | See 图 9-2        |      |     | 10  | μs         |

| V <sub>PORF</sub>   | Voltage trip point of POR on falling V <sub>CC</sub>                                                                          |                  | 0.75 | 1   |     | V          |

| V <sub>PORR</sub>   | Voltage trip point of POR on rising V <sub>CC</sub>                                                                           |                  |      | 1.2 | 1.5 | V          |

|                     |                                                                                                                               |                  |      |     |     |            |

### (1) $T_A = -40$ °C to +125°C (unless otherwise noted)

Glitches in the power supply can also affect the power-on reset performance of this device. The glitch width  $(V_{CC\_GW})$  and height  $(V_{CC\_GH})$  are dependent on each other. The bypass capacitance, source impedance, and device impedance are factors that affect power-on reset performance.  $\ 9-2$  and  $\ 7-2$  provide more information on how to measure these specifications.

图 9-2. Glitch Width, Glitch Height, and Minimum Glitch Voltage

# 10 Layout

### 10.1 Layout Guidelines

For printed circuit board (PCB) layout of the TCA9539-Q1, common PCB layout practices must be followed but additional concerns related to high-speed data transfer such as matched impedances and differential pairs are not a concern for I<sup>2</sup>C signal speeds.

In all PCB layouts, it is a best practice to avoid right angles in signal traces, to fan out signal traces away from each other upon leaving the vicinity of an integrated circuit (IC), and to use thicker trace widths to carry higher amounts of current that commonly pass through power and ground traces. By-pass and de-coupling capacitors are commonly used to control the voltage on the  $V_{CC}$  pin, using a larger capacitor to provide additional power in the event of a short power supply glitch and a smaller capacitor to filter out high-frequency ripple. These capacitors must be placed as close to the TCA9539-Q1 as possible. These best practices are shown in  $\boxed{\$}$  10-1.

For the layout example provided in  $\boxtimes$  10-1, it would be possible to fabricate a PCB with only 2 layers by using the top layer for signal routing and the bottom layer as a split plane for power ( $V_{CC}$ ) and ground (GND). However, a 4 layer board is preferable for boards with higher density signal routing. On a 4 layer PCB, it is common to route signals on the top and bottom layer, dedicate one internal layer to a ground plane, and dedicate the other internal layer to a power plane. In a board layout using planes or split planes for power and ground, vias are placed directly next to the surface mount component pad which must attach to  $V_{CC}$  or GND and the via is connected electrically to the internal layer or the other side of the board. Vias are also used when a signal trace needs to be routed to the opposite side of the board, but this technique is not demonstrated in  $\boxtimes$  10-1.

# 10.2 Layout Example

图 10-1. TCA9539-Q1 Layout

# 11 Device and Documentation Support

# 11.1 Documentation Support

#### 11.1.1 Related Documentation

For related documentation see the following:

- Understanding the I2C Bus, SLVA704

- I2C Pull-up Resistor Calculation, SLVA689

- Introduction to Logic, SLVA700

- Maximum Clock Frequency of I2C Bus Using Repeaters, SLVA695

- I2C Bus Pull-Up Resistor Calculation, SLVA689

## 11.2 接收文档更新通知

要接收文档更新通知,请导航至 ti.com 上的器件产品文件夹。点击*订阅更新* 进行注册,即可每周接收产品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

#### 11.3 支持资源

TI E2E<sup>™</sup> 支持论坛是工程师的重要参考资料,可直接从专家获得快速、经过验证的解答和设计帮助。搜索现有解答或提出自己的问题可获得所需的快速设计帮助。

链接的内容由各个贡献者"按原样"提供。这些内容并不构成 TI 技术规范,并且不一定反映 TI 的观点;请参阅 TI 的《使用条款》。

### 11.4 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

所有商标均为其各自所有者的财产。

#### 11.5 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 11.6 术语表

TI术语表本术语表列出并解释了术语、首字母缩略词和定义。

## Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Copyright © 2021 Texas Instruments Incorporated

9-Nov-2025 www.ti.com

#### PACKAGING INFORMATION

| Orderable part number | Status (1) | Material type | Package   Pins  | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|------------|---------------|-----------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

| TCA9539QPWRQ1         | Active     | Production    | TSSOP (PW)   24 | 2000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | TCA539Q          |

| TCA9539QPWRQ1.A       | Active     | Production    | TSSOP (PW)   24 | 2000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | TCA539Q          |

| TCA9539QPWRQ1.B       | Active     | Production    | TSSOP (PW)   24 | 2000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | TCA539Q          |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF TCA9539-Q1:

Catalog: TCA9539

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 9-Nov-2025

NOTE: Qualified Version Definitions:

$_{\bullet}$  Catalog - TI's standard catalog product

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 9-Oct-2025

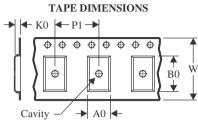

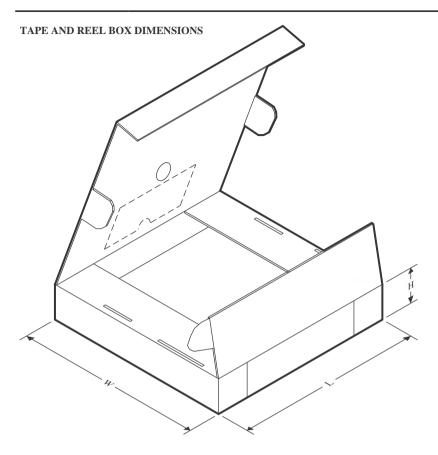

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

|   | Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | ` '  | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------|------------|------------|------------|-----------|------------------|

| ı | TCA9539QPWRQ1 | TSSOP           | PW                 | 24 | 2000 | 330.0                    | 16.4                     | 6.95 | 8.3        | 1.6        | 8.0        | 16.0      | Q1               |

**PACKAGE MATERIALS INFORMATION**

www.ti.com 9-Oct-2025

### \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| TCA9539QPWRQ1 | TSSOP        | PW              | 24   | 2000 | 353.0       | 353.0      | 32.0        |  |

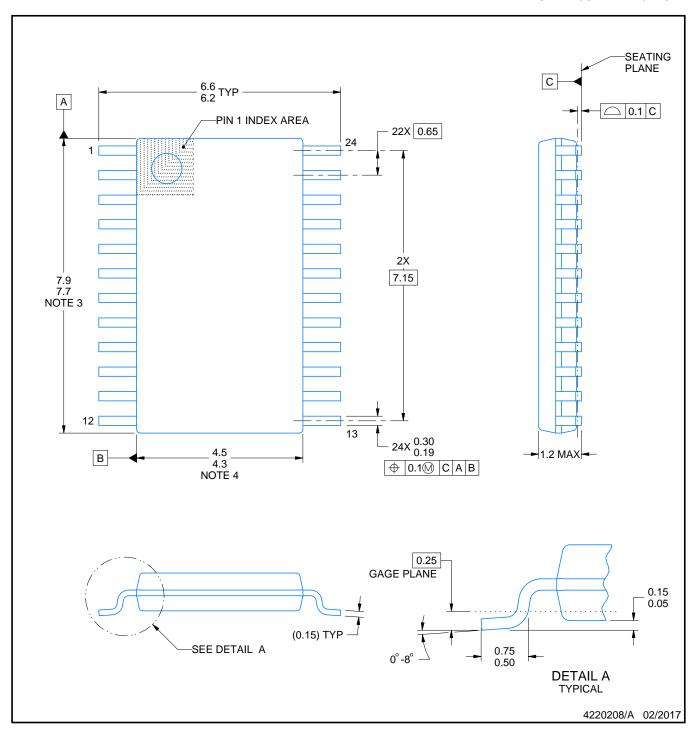

SMALL OUTLINE PACKAGE

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

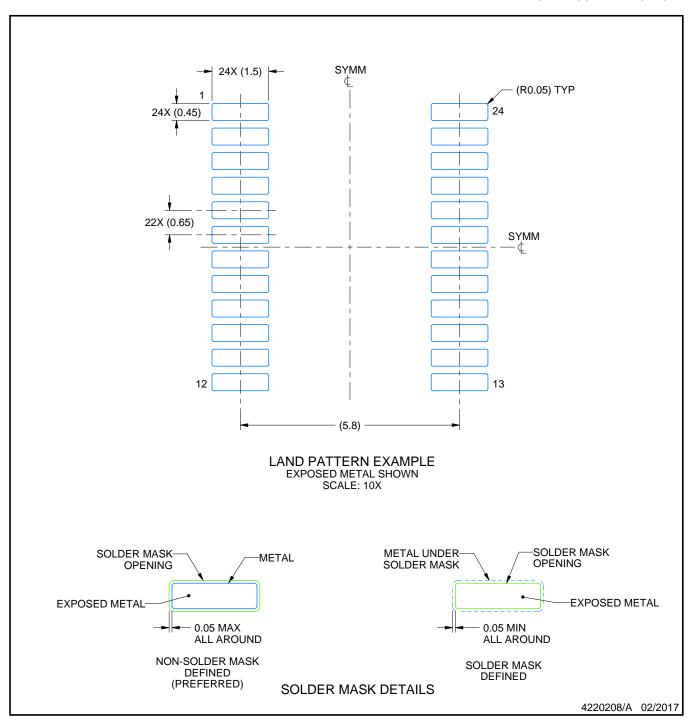

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

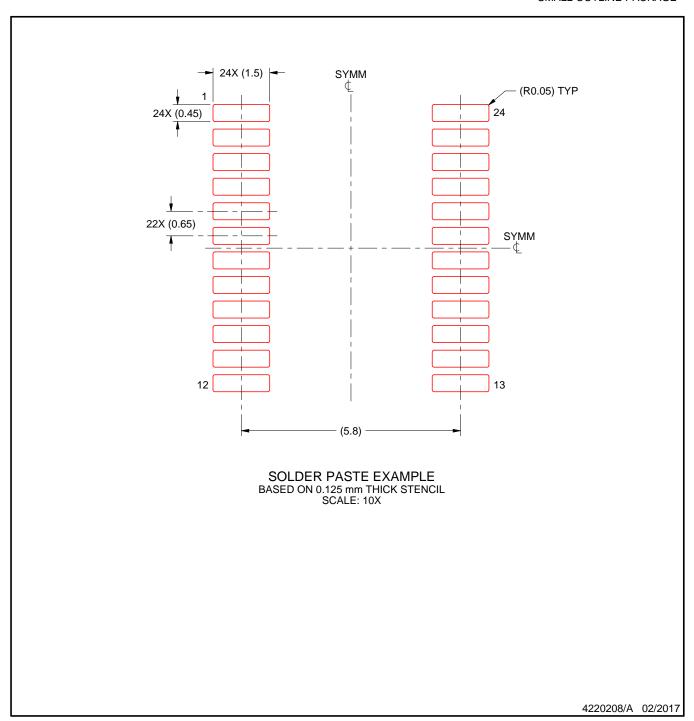

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

# 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月