LMX2571-EP

/ Texas INSTRUMENTS

ZHCSP40B - OCTOBER 2021 - REVISED JUNE 2022

# 具有 FSK 调制功能的 LMX2571-EP 低功耗、高性能 PLLatinum<sup>™</sup> 射频合成器

# 1 特性

- VID# : V62/21613-01XE

- -55 °C 至 +125 °C 工作温度

- 10MHz 至 1344MHz 范围内的任何频率

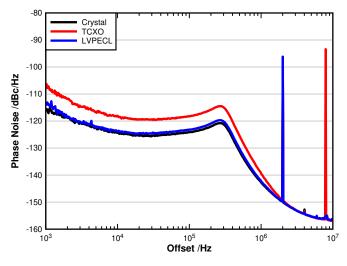

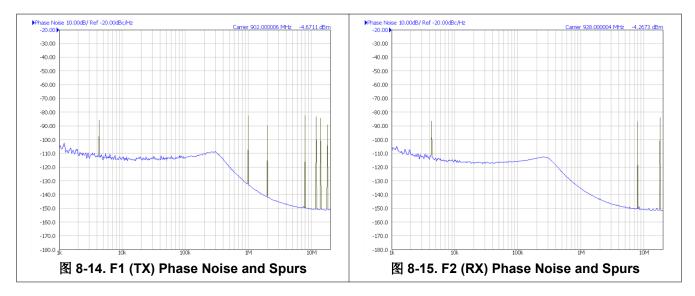

- 低相位噪声和毛刺

- -123dBc/Hz (在 480MHz 且偏移为 12.5kHz 时)

- -145dBc/Hz(在480MHz 且偏移为1MHz 时)

- 标准 PLL 本底噪声为 231dBc/Hz

- 杂散优于 75dBc/Hz

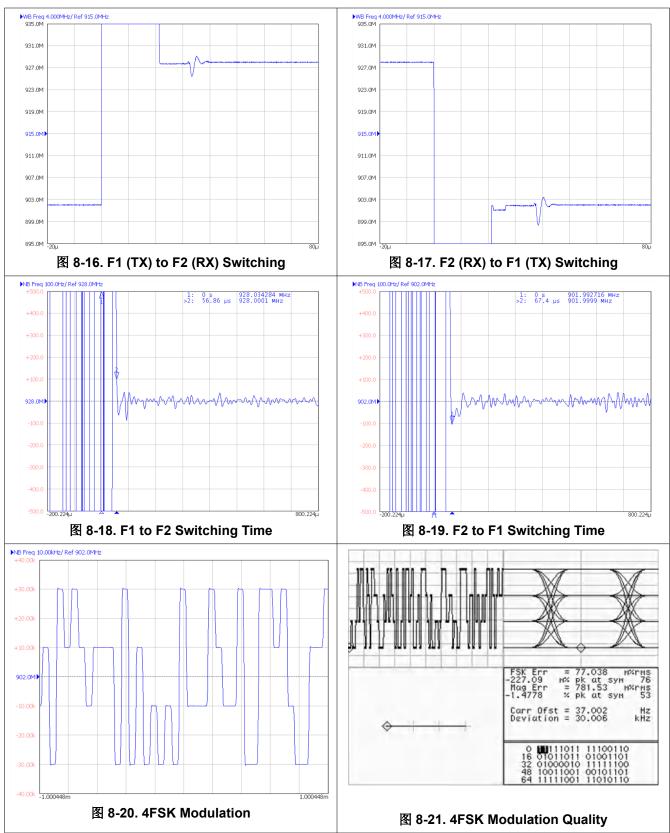

- 新型 FastLock 技术, 缩短了锁定时间

- 新型整数边界毛刺去除技术

- 集成 5V 电荷泵和输出分频器,用于外部 VCO 操作

- 2、4 和 8 电平或者任意电平数直接数字 FSK 调制

- 一个 TX/RX 输出或两个扇出输出

- 低电流消耗

- 39mA 典型合成器模式 (内部 VCO)

- 9mA 典型 PLL 模式 (外部 VCO)

- 24 位分数 N Δ-Σ 调制器

- LMX2571 与 LMX2571-EP 之间的功能差异

- LMX2571-EP 没有 TrCtl 引脚

- LMX2571-EP 没有 OSCin\* 引脚、差分模式和晶 振模式

# 2 应用

- 导引头前端

- 国防无线电

- 飞行器驾驶舱显示屏

- 飞行控制单元

- 无线基础设施

# 3 说明

LMX2571-EP 器件是一款低功耗、高性能的宽带 PLLatinum<sup>™</sup> 射频合成器,该器件集成了  $\Delta$ -Σ 分数 N PLL、多核电压控制振荡器 (VCO)、可编程输出分频器 和两个输出缓冲器。VCO 内核的工作频率高达 5.376GHz , 持续输出频率范围为 10MHz 至 1344MHz。

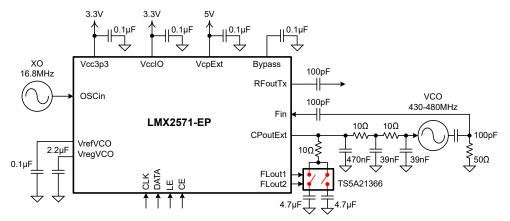

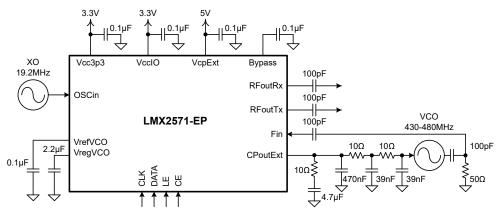

该合成器还可搭配外部 VCO 使用。在此配置下, 需使 用专用的 5V 电荷泵和输出分频器。

该合成器还包含一个独特的可编程乘法器,有助于去除 毛刺,即使毛刺落在整数边界,系统也仍能够使用任一 通道。

输出具有集成式 SPDT 开关,可用作 FDD 无线电应用 中的发送和接收开关。并且可同时导通两个开关,以便 同时提供双输出。

通过编程或引脚,LMX2571-EP 可支持直接数字 FSK 调制。此外,还支持离散电平 FSK、脉冲成形 FSK 以 及模拟 FM 调制。

该合成器采用了全新的 FastLock 技术,即使在外部 VCO 与窄带回路滤波器搭配使用时,用户也能够在不 到 1.5ms 的时间内从一个频率切换至另一频率。

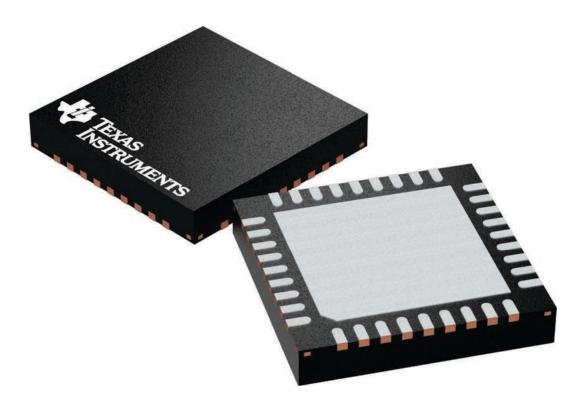

器件信息(1)

| HA 11 14 70.                 |           |                 |  |  |  |  |

|------------------------------|-----------|-----------------|--|--|--|--|

| 器件型号                         | 封装        | 封装尺寸 ( 标称值 )    |  |  |  |  |

| LMX2571-EP<br>V62/21613-01XE | VQFN (36) | 6.00mm × 6.00mm |  |  |  |  |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 (1) 录。

# **Table of Contents**

| 1 | 特性                                   | 1    |

|---|--------------------------------------|------|

|   | 应用                                   |      |

|   | ,<br>说明                              |      |

| 4 | Revision History                     |      |

|   | Pin Configuration and Functions      |      |

|   | Specifications                       |      |

|   | 6.1 Absolute Maximum Ratings         | 4    |

|   | 6.2 ESD Ratings                      | 4    |

|   | 6.3 Recommended Operating Conditions | 4    |

|   | 6.4 Thermal Information              | 5    |

|   | 6.5 Electrical Characteristics       | 5    |

|   | 6.6 Timing Requirements              | 8    |

|   | 6.7 Timing Diagrams                  |      |

|   | 6.8 Typical Characteristics          | 9    |

| 7 | Detailed Description                 | .12  |

|   | 7.1 Overview                         | .12  |

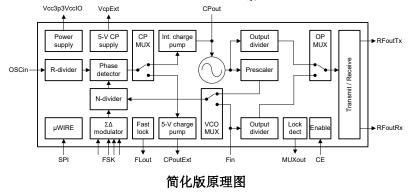

|   | 7.2 Functional Block Diagram         | .12  |

|   | 7.3 Feature Description              | .13  |

|   | 7.4 Device Functional Modes          |      |

|   | 7.5 Programming                      | . 18 |

| 7.6 Register Maps                       | 20              |

|-----------------------------------------|-----------------|

| 8 Application and Implementation        |                 |

| 8.1 Application Information             |                 |

| 8.2 Typical Applications                | 46              |

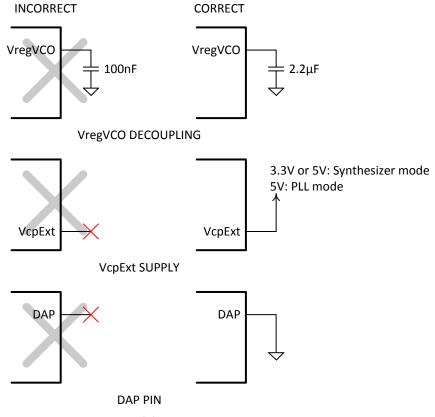

| 8.3 Do's and Don'ts                     |                 |

| 9 Power Supply Recommendations          |                 |

| 10 Layout                               |                 |

| 10.1 Layout Guidelines                  | 57              |

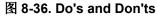

| 10.2 Layout Example                     | 57              |

| 11 Device and Documentation Support     |                 |

| 11.1 Device Support                     |                 |

| 11.2 Documentation Support              | 58              |

| 11.3 接收文档更新通知                           |                 |

| 11.4 支持资源                               | <u>58</u>       |

| 11.5 Trademarks                         |                 |

| 11.6 Electrostatic Discharge Caution    |                 |

| 11.7 术语表                                |                 |

| 12 Mechanical, Packaging, and Orderable |                 |

| Information                             | <mark>58</mark> |

|                                         |                 |

# **4 Revision History**

| Changes from Revision A (December 2021) to Revision B (June 2022)    | Page |

|----------------------------------------------------------------------|------|

| • 删除了对 TrCtl 引脚的所有引用                                                 | 1    |

| • 删除了"差分模式"                                                          | 1    |

| • 删除了"晶振模式"                                                          |      |

| Redefined the OSCin* pin to NC                                       |      |

| Added the Differences Between the LMX2571 and LMX2571-EP section     |      |

| Changes from Revision * (October 2021) to Revision A (December 2021) | Page |

| • 将数据表状态从"预告信息"更改为:量产数据                                              |      |

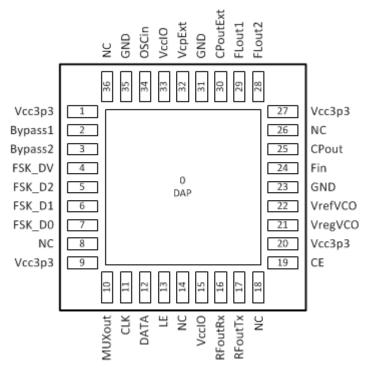

# **5** Pin Configuration and Functions

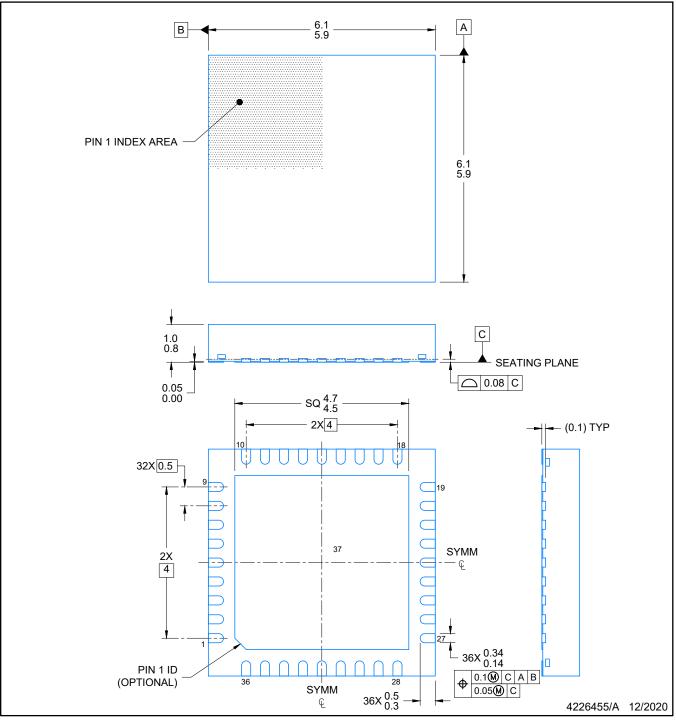

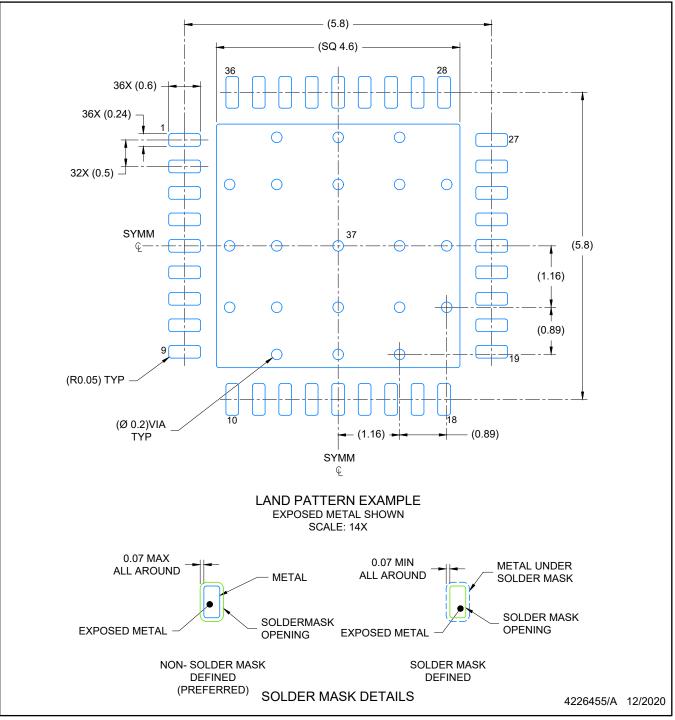

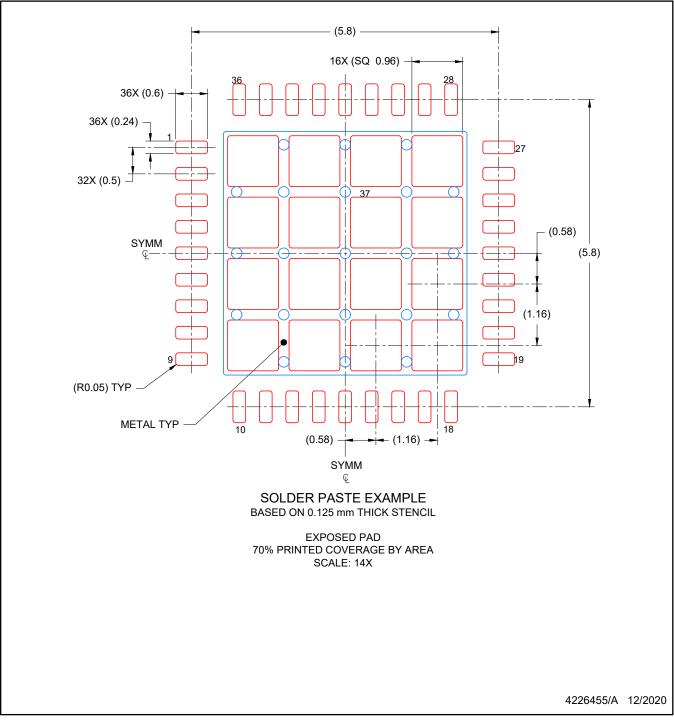

图 5-1. RHH Package 36-Pin VQFN Top View

#### 表 5-1. Pin Functions

| PIN      |     | ТҮРЕ   | DESCRIPTION                                                                                                     |  |  |

|----------|-----|--------|-----------------------------------------------------------------------------------------------------------------|--|--|

| NAME     | NO. |        | DESCRIPTION                                                                                                     |  |  |

| Bypass1  | 2   | Bypass | Place a 100-nF capacitor to GND.                                                                                |  |  |

| Bypass2  | 3   | Bypass | Place a 100-nF capacitor to GND.                                                                                |  |  |

| CE       | 19  | Input  | Chip Enable input. Active HIGH powers on the device.                                                            |  |  |

| CLK      | 11  | Input  | MICROWIRE clock input.                                                                                          |  |  |

| CPout    | 25  | Output | Internal VCO charge pump access point to connect to a 2 <sup>nd</sup> order loop filter.                        |  |  |

| CPoutExt | 30  | Output | 5-V charge pump output used in PLL mode (external VCO).                                                         |  |  |

| DAP      | GND | GND    | The DAP should be grounded.                                                                                     |  |  |

| DATA     | 12  | Input  | MICROWIRE serial data input.                                                                                    |  |  |

| Fin      | 24  | Input  | High-frequency, AC-coupled input pin for an external VCO. Leave it open or AC-coupled to GND if not being used. |  |  |

| FSK_D0   | 7   | Input  | FSK data bit 0 (FSK PIN mode) / I2S FS input (FSK I2S mode).                                                    |  |  |

| FSK_D1   | 6   | Input  | FSK data bit 1 (FSK PIN mode) / I2S DATA input (FSK I2S mode).                                                  |  |  |

| FSK_D2   | 5   | Input  | FSK data bit 2 (FSK PIN mode).                                                                                  |  |  |

| FSK_DV   | 4   | Input  | FSK data valid input (FSK PIN mode) / I2S CLK input (FSK I2S mode).                                             |  |  |

| FLout1   | 29  | Output | FastLock output control 1 for external switch. Output is HIGH when F1 is selected.                              |  |  |

| FLout2   | 28  | Output | FastLock output control 2 for external switch. Output is HIGH when F2 is selected.                              |  |  |

| GND      | 23  | GND    | VCO ground.                                                                                                     |  |  |

| GND      | 31  | GND    | Charge pump ground.                                                                                             |  |  |

| GND      | 35  | GND    | OSCin ground.                                                                                                   |  |  |

| LE       | 13  | Input  | MICROWIRE latch enable input.                                                                                   |  |  |

| MUXout   | 10  | Output | Multiplexed output that can be assigned to lock detect or readback serial data output.                          |  |  |

### 表 5-1. Pin Functions (continued)

| PIN     |                 | TYPE   | DESCRIPTION                                                                                                               |

|---------|-----------------|--------|---------------------------------------------------------------------------------------------------------------------------|

| NAME    | NO.             | 1176   | DESCRIPTION                                                                                                               |

| NC      | 14, 26          | NC     | Leave floating, do not connect to GND or power supply.                                                                    |

| OSCin   | 34              | Input  | Reference clock input.                                                                                                    |

| NC      | 8,18, 36        | NC     | These pins may be left floating or connected to GND.                                                                      |

| RFoutRx | 16              | Output | RF output used to drive receive mixer. Selectable open-drain or push-pull output.                                         |

| RFoutTx | 17              | Output | RF output used to drive transmit signal. Selectable open-drain or push-pull output.                                       |

| Vcc3p3  | 1, 9, 20,<br>27 | Supply | Connect to 3.3-V supply.                                                                                                  |

| VccIO   | 15, 33          | Supply | Supply for digital logic interface. Connect to 3.3-V supply.                                                              |

| VcpExt  | 32              | Supply | Supply for 5-V charge pump. Connect to 5-V supply in PLL mode. Connect to either 3.3-V or 5-V supply in synthesizer mode. |

| VrefVCO | 22              | Bypass | LDO output. Place a 100-nF capacitor to GND.                                                                              |

| VregVCO | 21              | Bypass | Bias circuitry for the VCO. Place a 2.2-µF capacitor to GND.                                                              |

# **6** Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                            | MIN   | MAX                   | UNIT |

|------------------|----------------------------|-------|-----------------------|------|

| V <sub>CC</sub>  | Power supply voltage       | - 0.3 | 3.6                   | V    |

| V <sub>IO</sub>  | IO supply voltage          | - 0.3 | 3.6                   | V    |

| V <sub>CP</sub>  | Charge pump supply voltage |       | 5.25                  | V    |

| V <sub>IN</sub>  | IO input voltage           |       | V <sub>CC</sub> + 0.3 | V    |

| TJ               | Junction temperature       | - 55  | 150                   | °C   |

| T <sub>stg</sub> | Storage temperature        | - 65  | 150                   | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 6.2 ESD Ratings

|                    |                                                                                |                                                                                     |       | VALUE | UNIT |

|--------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------|-------|------|

| V <sub>(ESD)</sub> | Human body model (HBM), per ANSI/ESDA/JEDEC<br>JS-001, all pins <sup>(1)</sup> |                                                                                     | ±1500 |       |      |

|                    | Electrostatic discharge                                                        | Charged device model (CDM), per ANSI/ESDA/<br>JEDEC JS-002, all pins <sup>(2)</sup> | ±500  | v     |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                                      |                                 | MIN             | NOM | MAX             | UNIT |

|-----------------|--------------------------------------|---------------------------------|-----------------|-----|-----------------|------|

| V <sub>CC</sub> | V <sub>CC</sub> Power supply voltage |                                 |                 | 3.3 | 3.45            | V    |

| V <sub>IO</sub> | IO supply voltage                    |                                 |                 |     | V <sub>CC</sub> | V    |

| V <sub>CP</sub> |                                      | PLL mode (external VCO)         |                 |     | 5               | V    |

|                 | Charge pump supply voltage           | Synthesizer mode (internal VCO) | V <sub>CC</sub> |     | 5               | v    |

| T <sub>A</sub>  | Ambient temperature                  |                                 | - 55            |     | 125             | °C   |

# 6.4 Thermal Information

|                        |                                              | LMX2571-EP |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | NJK (WQFN) | UNIT |

|                        |                                              | 36 PINS    |      |

| R <sub>0 JA</sub>      | Junction-to-ambient thermal resistance       | 32.9       | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 14.5       | °C/W |

| R <sub>0 JB</sub>      | Junction-to-board thermal resistance         | 6.3        | °C/W |

| Ψ <sub>JT</sub>        | Junction-to-top characterization parameter   | 0.2        | °C/W |

| Ψ <sub>JB</sub>        | Junction-to-board characterization parameter | 6.3        | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 2.0        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# **6.5 Electrical Characteristics**

$3.15 \text{ V} \leqslant \text{V}_{\text{CC}} \leqslant 3.45 \text{ V}, \text{ V}_{\text{IO}} = \text{V}_{\text{CC}}, -55 \text{ }^{\circ}\text{C} \leqslant \text{T}_{\text{A}} \leqslant 125 \text{ }^{\circ}\text{C}, \text{ except as specified. Typical values are at } \text{V}_{\text{CC}} = \text{V}_{\text{IO}} = 3.3 \text{ V}, \text{V}_{\text{CP}} = 3.3 \text{ V} \text{ or } 5 \text{ V} \text{ in synthesizer mode, } \text{V}_{\text{CP}} = 5 \text{ V} \text{ in PLL mode, } \text{T}_{\text{A}} = 25 \text{ }^{\circ}\text{C}.$

|                      | PARAMETER                    | TEST CO                                   | NDITIONS                        | MIN | TYP   | MAX | UNIT |  |

|----------------------|------------------------------|-------------------------------------------|---------------------------------|-----|-------|-----|------|--|

| CURREN               | T CONSUMPTION                |                                           |                                 |     |       |     |      |  |

|                      |                              |                                           | Configuration A <sup>(1)</sup>  |     | 39    |     |      |  |

|                      | Synthesizer mede             |                                           | Configuration B <sup>(2)</sup>  |     | 44    |     |      |  |

| I <sub>CC</sub>      | Synthesizer mode             |                                           | Configuration C <sup>(3)</sup>  |     | 46    |     |      |  |

|                      |                              | f <sub>OUT</sub> = 480 MHz, SE<br>OSCIN   | Configuration D <sup>(4)</sup>  |     | 51    |     | mA   |  |

|                      |                              |                                           | Configuration E <sup>(5)</sup>  |     | 9     |     |      |  |

| I <sub>PLL</sub>     | PLL mode                     |                                           | Configuration F <sup>(6)</sup>  |     | 15    |     |      |  |

|                      |                              |                                           | Configuration G <sup>(7)</sup>  |     | 21    |     |      |  |

| I <sub>PD</sub>      | Powerdown                    | CE = 0 V or POWERD<br>V, Push-pull output | DOWN = 1, V <sub>CC</sub> = 3.3 |     | 0.9   |     | mA   |  |

| OSCIN R              | EFERENCE INPUT               | I                                         |                                 |     |       |     |      |  |

| f <sub>OSCIN</sub>   | Input frequency              |                                           |                                 |     |       | 150 | MHz  |  |

| V <sub>OSCIN</sub>   | Input voltage <sup>(8)</sup> |                                           |                                 | 0.8 |       | 3.3 | V    |  |

| REFERE               | NCE INPUT PROGRAMMABLE MU    | JLTIPLIER                                 |                                 |     |       |     |      |  |

| f <sub>MULTin</sub>  | MULT input frequency         | MULT > Pre-divider                        |                                 | 10  |       | 30  | MHz  |  |

| f <sub>MULTout</sub> | MULT output frequency        |                                           |                                 | 60  |       | 130 |      |  |

| PLL                  | 1                            |                                           |                                 |     |       |     |      |  |

| f <sub>PD</sub>      | Phase detector frequency     |                                           |                                 | 10  |       | 130 | MHz  |  |

|                      |                              | Programmable<br>minimum value             | Internal charge pump            | :   | 312.5 |     |      |  |

|                      |                              |                                           | 5-V charge pump                 |     | 625   |     |      |  |

| K <sub>PD</sub>      | s                            | Per programmable                          | Internal charge pump            | :   | 312.5 |     | μA   |  |

| . 2                  |                              | step                                      | 5-V charge pump                 |     | 625   |     | 1 .  |  |

|                      |                              | Programmable<br>maximum value             | Internal charge<br>pump         | 7   | 187.5 |     |      |  |

|                      |                              |                                           | 5-V charge pump                 |     | 6875  |     |      |  |

| $3.15 \text{ V} \le \text{V}_{CC} \le 3.45 \text{ V}$ , $\text{V}_{IO}$ = $\text{V}_{CC}$ , $-55 \text{ °C} \le \text{T}_{A} \le 125 \text{ °C}$ , except as specified. Typical values are at $\text{V}_{CC}$ = $\text{V}_{IO}$ = $3.3 \text{ °C}$ | V, |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| $V_{CP}$ = 3.3 V or 5 V in synthesizer mode, $V_{CP}$ = 5 V in PLL mode, $T_A$ = 25 °C.                                                                                                                                                            |    |

|                                   | PARAMETER                                    | TEST CO                                                       | NDITIONS                            | MIN  | TYP     | MAX      | UNIT          |

|-----------------------------------|----------------------------------------------|---------------------------------------------------------------|-------------------------------------|------|---------|----------|---------------|

| PN <sub>PLL_1/f</sub>             | Normalized PLL 1/f noise <sup>(10)</sup>     |                                                               | Internal charge pump                |      | - 124   |          |               |

|                                   |                                              | At maximum charge                                             | 5-V charge pump                     |      | - 120   |          | dDo/Uz        |

| PN <sub>PLL_FLAT</sub>            | Normalized PLL noise floor <sup>(10)</sup>   | pump current                                                  | Internal charge pump                |      | - 231   |          | dBc/Hz        |

|                                   |                                              |                                                               | 5-V charge pump                     |      | - 226   |          |               |

|                                   |                                              | EXTVCO_CHDIV = 1                                              |                                     | 100  |         | 2000     |               |

| f <sub>RFIN</sub>                 | External VCO input frequency <sup>(11)</sup> | EXTVCO_CHDIV = 8,                                             | 10                                  | 100  |         | 1900     | MHz           |

|                                   |                                              | EXTVCO_CHDIV = 2,                                             | 3, 4, 5, 6, 7, 9                    | 100  |         | 1400     |               |

|                                   |                                              | $0.1 \mathrm{GHz} \leqslant \mathrm{f_{RFIN}} < 1 \mathrm{G}$ | GHz                                 | - 10 |         |          |               |

| P <sub>RFIN</sub>                 | External VCO input power                     | $1 \text{ GHz} \leq f_{\text{RFIN}} \leq 1.4$                 | GHz                                 | - 5  |         |          | dBm           |

|                                   |                                              | 1.4 GHz < $f_{RFIN} \le 2$ G                                  | GHz                                 | 0    |         |          |               |

| vco                               | 1                                            |                                                               |                                     |      |         |          |               |

| f <sub>VCO</sub>                  | VCO frequency                                |                                                               |                                     | 4300 |         | 5376     | MHz           |

| K <sub>VCO</sub>                  | VCO gain <sup>(12)</sup>                     | f <sub>VCO</sub> = 4800 MHz                                   |                                     |      | 56      |          | MHz/V         |

| $  \Delta T_{CL}  $               | Allowable temperature drift <sup>(13)</sup>  | VCO not being recalib<br>≤ 125 °C                             | rated, -40 °C $\leq$ T <sub>A</sub> |      |         | 165      | °C            |

| t <sub>VCOCAL</sub>               | VCO calibration time                         | f <sub>OSCIN</sub> = f <sub>PD</sub> = 100<br>MHz             |                                     |      | 140     |          | μs            |

|                                   |                                              |                                                               | 100 Hz offset                       |      | - 32.4  |          |               |

|                                   |                                              |                                                               | 1 kHz offset                        |      | - 62.3  |          |               |

|                                   |                                              | 6 400 MUL                                                     | 10 kHz offset                       |      | - 92.1  |          | - ID - /I I - |

| PNVCO                             | Open loop VCO phase noise                    | f <sub>OUT</sub> = 480 MHz                                    | 100 kHz offset                      |      | - 121.1 |          | dBc/Hz        |

|                                   |                                              |                                                               | 1 MHz offset                        |      | - 144.5 |          |               |

|                                   |                                              |                                                               | 10 MHz offset                       |      | - 156.8 |          |               |

| Outputs                           |                                              |                                                               |                                     |      |         |          |               |

| f                                 | RF output frequency                          | Synthesizer mode                                              |                                     | 10   |         | 1344     | MHz           |

| f <sub>оит</sub>                  | RF output frequency                          | PLL mode, RF output                                           | from buffer                         | 10   |         | 1400     | IVITIZ        |

| P <sub>TX</sub> , P <sub>RX</sub> | RF output power                              | f = 490 MU                                                    | Power control bit =                 |      | 0       |          | dBm           |

| H2 <sub>RFout</sub>               | Second harmonic                              | f <sub>OUT</sub> = 480 MHz                                    | 6                                   |      | - 25    |          | dBc           |

| DIGITAL FS                        | K MODULATION                                 | ŀ                                                             | · ·                                 |      |         |          |               |

| FSK <sub>Level</sub>              | FSK level <sup>(14)</sup>                    | FSK PIN mode                                                  |                                     | 2    |         | 8        |               |

| FSK <sub>Baud</sub>               | FSK baud rate <sup>(15)</sup>                | Loop bandwidth = 200                                          | kHz                                 |      | 100     |          | kSPs          |

| FSK <sub>Dev</sub>                | FSK deviation                                | Configuration H <sup>(16)</sup>                               |                                     |      | ±39     |          | kHz           |

| DIGITAL IN                        | TERFACE                                      |                                                               |                                     |      |         |          |               |

| V <sub>IH</sub>                   | High-level input voltage                     |                                                               |                                     | 1.4  |         | $V_{CC}$ | V             |

| V <sub>IL</sub>                   | Low-Level input voltage                      |                                                               |                                     |      |         | 0.4      | V             |

| I <sub>IH</sub>                   | High-level input current                     | V <sub>IH</sub> = 1.75 V                                      |                                     | - 25 |         | 25       | μA            |

| I <sub>IL</sub>                   | Low-Level input current                      | V <sub>IL</sub> = 0 V                                         | - 25                                |      | 25      | μA       |               |

| V <sub>OH</sub>                   | High-level output voltage                    | I <sub>OH</sub> = 500 μ A                                     | 2                                   |      |         | V        |               |

| V <sub>OL</sub>                   | Low-level input voltage                      | I <sub>OL</sub> = -500 μA                                     |                                     |      | 0       | 0.4      | V             |

(1)  $f_{OSCIN} = 19.44$  MHz, MULT = 1, Prescaler = 4,  $f_{PD} = 19.44$  MHz, one RF output, output type = push pull, output power = -3 dBm

(2) f<sub>OSCIN</sub> = 19.44 MHz, MULT = 1, Prescaler = 2, f<sub>PD</sub> = 19.44 MHz, one RF output, output type = push pull, output power = -3 dBm

(3)  $f_{OSCIN} = 19.44 \text{ MHz}$ , MULT = 5, Prescaler = 2,  $f_{PD} = 19.44 \text{ MHz}$ , one RF output, output type = push pull, output power = -3 dBm

(4)  $f_{OSCIN} = 19.44$  MHz, MULT = 5, Prescaler = 2,  $f_{PD} = 97.2$  MHz, one RF output, output type = push pull, output power = -3 dBm

(5)  $f_{OSCIN} = 19.44$  MHz, MULT = 1,  $f_{PD} = 19.44$  MHz, output from VCO

- (6)  $f_{OSCIN} = 19.44$  MHz, MULT = 1,  $f_{PD} = 19.44$  MHz, one RF output, output type = push pull, output power = -3 dBm

- (7) f<sub>OSCIN</sub> = 19.44 MHz, MULT = 1, f<sub>PD</sub> = 19.44 MHz, two RF outputs, output type = push pull, output power = -3 dBm

- (8) See OSCIN Configuration for definition of OSCIN input voltage.

- (9) This is referring to the total base charge pump current. In PLL mode, this is equal to EXTVCO\_CP\_IDN + EXTVCO\_CP\_IUP. In synthesizer mode, this is equal to CP\_IDN + CP\_IUP.

- (10) Measured with a clean OSCIN signal with a high slew rate using a wide loop bandwidth. The noise metrics model the PLL noise for an infinite loop bandwidth as:

- PLL\_Total = 10 \* log[10<sup>(PLL\_Flat / 10)</sup> + 10<sup>(PLL\_Flicker / 10)</sup>]

- $PLL\_Flat = PN1Hz + 20 * log(N) + 10 * log(f_{PD})$

- PLL\_Flicker = PN10kHz 10 \* log(Offset / 10 kHz) + 20 \* log( $f_{OUT}$  / 1 GHz)

- (11) For external VCO frequencies above 1.4 GHz, there are restrictions on the output divider and register R70 needs to be programmed to 0x046110.

- (12) The VCO gain changes as a function of the VCO core and frequency. See Integrated VCO for details.

- (13) Not tested in production. Ensured by characterization. Allowable temperature drift refers to programming the device at an initial temperature and allowing this temperature to drift WITHOUT reprogramming the device, and still have the device stay in lock. This change could be up or down in temperature and the specification does not apply to temperatures that go outside the recommended operating temperatures of the device.

- (14) The data showed here simply specifies the range of discrete FSK level that is supported in PIN mode. PIN mode supports 2-, 4- and 8level of FSK modulation. If arbitrary level of FSK modulation is desired, use FSK SPI™ FAST mode or FSK I2S mode. See Direct Digital FSK Modulation for details.

- (15) The baud rate is limited by the loop bandwidth of the PLL loop. As a general rule of thumb, it is desirable to have the loop bandwidth at least twice the baud rate.

- (16) f<sub>PD</sub> = 100 MHz, DEN = 224, CHDIV1 = 5, CHDIV2 = 2, Prescaler = 2, FSK step value = 32716, 32819. The maximum achievable frequency deviation depends on the configuration, see Direct Digital FSK Modulation for details.

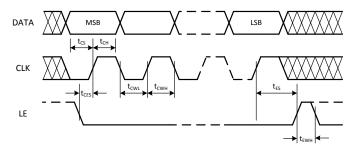

# 6.6 Timing Requirements

3.15 V  $\leqslant$  V<sub>CC</sub>  $\leqslant$  3.45 V, V<sub>IO</sub> = V<sub>CC</sub>, - 55 °C  $\leqslant$  T<sub>A</sub>  $\leqslant$  125 °C, except as specified. Typical values are at V<sub>CC</sub> = V<sub>IO</sub> = 3.3 V, T<sub>A</sub> = 25 °C.

|                  |                          |                | MIN NOM M | AX UNIT |

|------------------|--------------------------|----------------|-----------|---------|

| Timing           | Requirements             |                |           |         |

| t <sub>ES</sub>  | CLK to LE low time       |                | 5         | ns      |

| t <sub>CS</sub>  | DATA to CLK setup time   |                | 2         | ns      |

| t <sub>CH</sub>  | DATA to CLK hold time    |                | 2         | ns      |

| t <sub>CWH</sub> | CLK pulse width high     | See Figure 6-1 | 10        | ns      |

| t <sub>CWL</sub> | CLK pulse width low      |                | 10        | ns      |

| t <sub>CES</sub> | LE to CLK setup time     |                | 5         | ns      |

| t <sub>EWH</sub> | LE pulse width high      |                | 2         | ns      |

| t <sub>OD</sub>  | CLK to MUXOUT delay time |                |           | 8 ns    |

# 6.7 Timing Diagrams

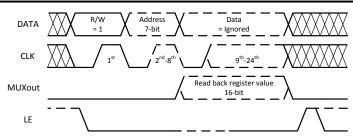

There are several other considerations for programming:

- A slew rate of at least 30 V/µs is recommended for the CLK, DATA and LE. The same apply for other digital control signals such as FSK\_D[0:2] and FSK\_DV signals.

- The DATA is clocked into a shift register on each rising edge of the CLK signal. On the rising edge of the 24<sup>th</sup> CLK, the data is transferred from the data field to the selected register bank.

- The LE pin may be held high after programming, causing the LMX2571-EP to ignore clock pulses.

- When CLK or DATA lines are shared between devices, it is recommended to divide down the voltage to the CLK, DATA, and LE pins closer to the minimum voltage. This provides better noise immunity.

- If the CLK and DATA lines are toggled while the VCO is in lock, as is sometimes the case when these lines are shared with other parts, the phase noise may be degraded during the time of this programming.

图 6-1. MICROWIRE Timing Diagram

# 6.8 Typical Characteristics

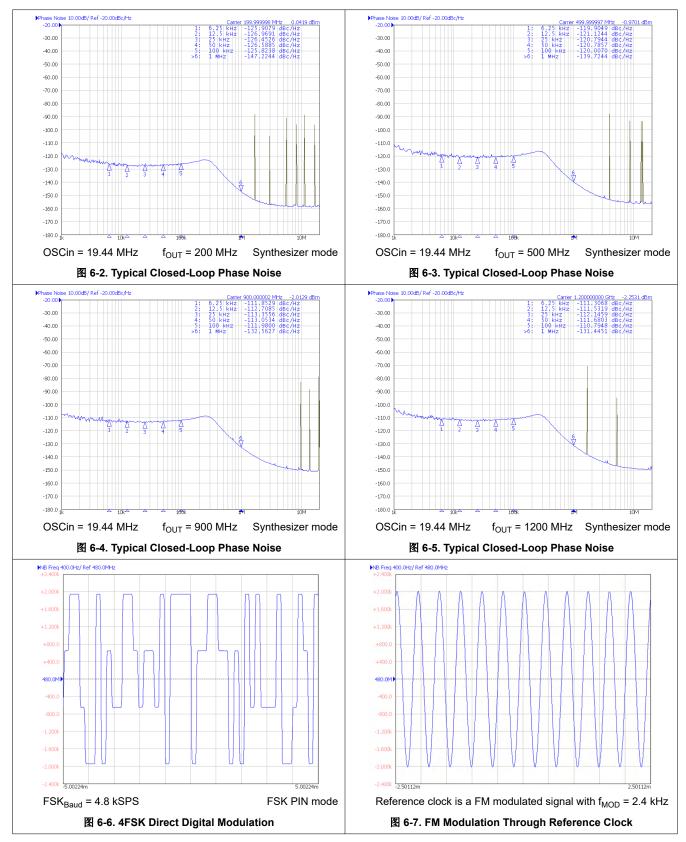

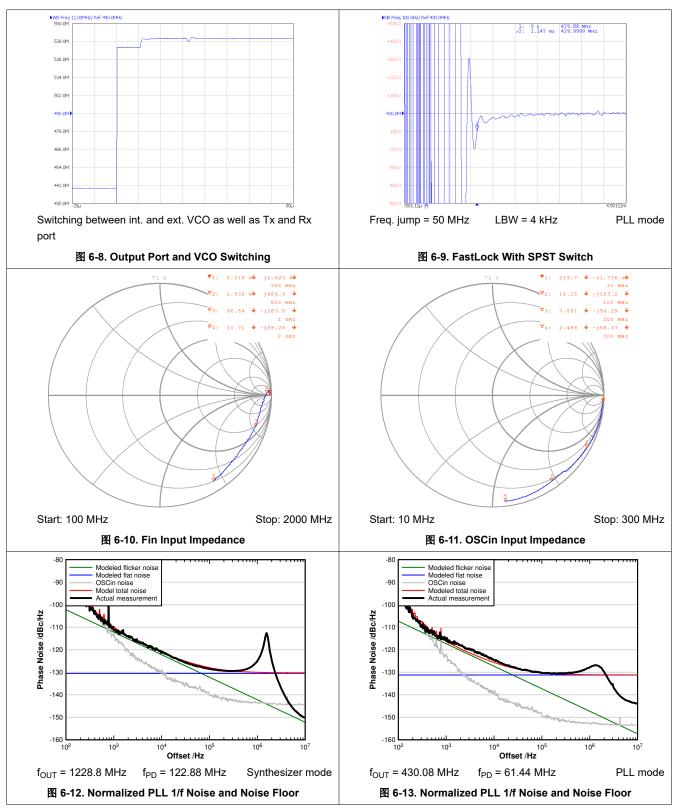

at T<sub>A</sub> = 25°C (unless otherwise noted)

# 6.8 Typical Characteristics (continued)

at T<sub>A</sub> = 25°C (unless otherwise noted)

# 6.8 Typical Characteristics (continued)

at  $T_A = 25^{\circ}C$  (unless otherwise noted)

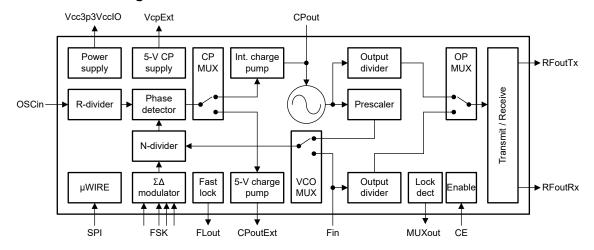

# 7 Detailed Description

# 7.1 Overview

The LMX2571-EP is a frequency synthesizer with low-noise, high-performance integrated VCOs. The 5-GHz VCO cores, together with the output channel dividers, can produce frequencies from 10 MHz to 1344 MHz. The LMX2571-EP supports two operation modes, synthesizer mode and PLL mode. In synthesizer mode, the entire device is used; in PLL mode the internal VCO is bypassed, and an external VCO is required to implement a complete synthesizer.

The PLL is a fractional-N PLL with programmable Delta Sigma modulator (first order to fourth order). The fractional denominator is of variable length and up to 24-bits long, providing a frequency step with very fine resolution.

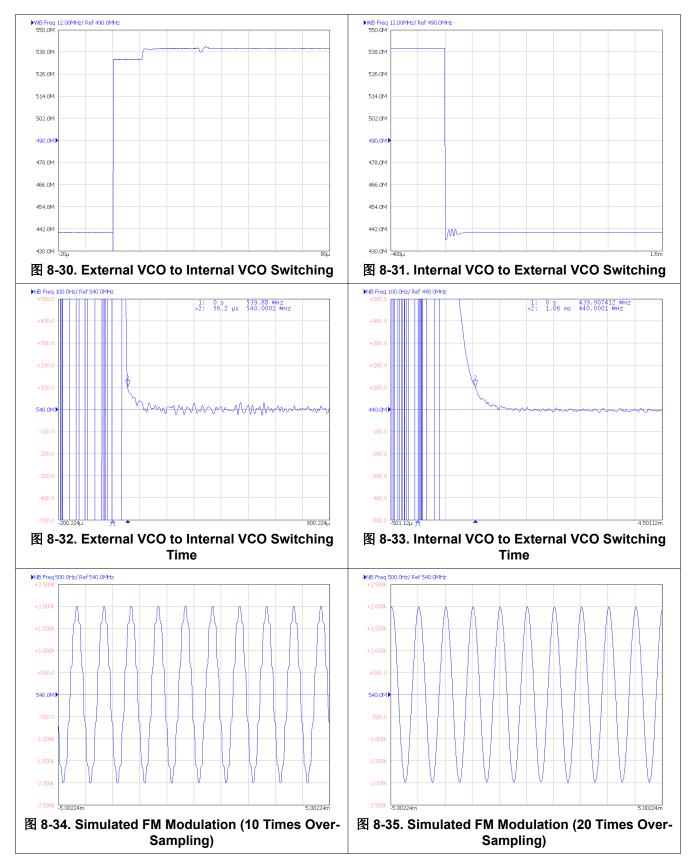

The internal VCO can be bypassed, allowing the use of an external VCO. A separate 5-V charge pump is dedicated for the external VCO, eliminating the need for an op-amp to support 5-V VCOs. A new advanced FastLock technique is developed to shorten the lock time to less than 1.5 ms, even there is a very narrow loop bandwidth.

A unique programmable multiplier is incorporated in the R-divider. The multiplier is used to avoid and reduce integer boundary spurs or to increase the phase detector frequency for higher performance.

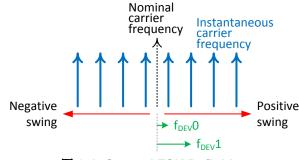

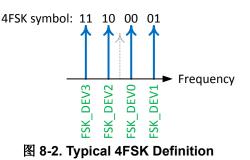

The LMX2571-EP supports direct digital FSK modulation, thus allowing a change in the output frequency by changing the N-divider value. The N-divider value can be programmed through MICROWIRE interface or through pins. Discrete 2-, 4- and 8-level FSK, as well as arbitrary-level FSK, are supported. Arbitrary-level FSK can be used to construct pulse-shaping FSK or analog-FM modulation.

The output has an integrated T/R switch, and the divided-down internal or external VCO signal can be output to either the TX port or the RX port. The switch can also be configured as a 1:2 fanout buffer, providing the signal on both outputs at the same time. In addition to port switching, the output frequency can be switched between two pre-defined frequencies, F1 and F2, simultaneously. This feature is ideal for use in FDD duplex system where the TX frequency is different from RX (LO) frequency.

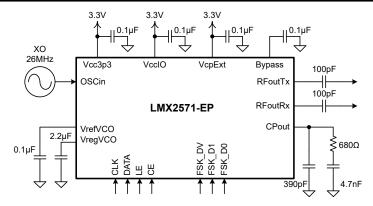

The LMX2571-EP requires only a single 3.3-V power supply. Digital logic interface is 1.8-V input compatible. The analog blocks power supplies use integrated LDOs, eliminating the need for high performance external LDOs.

Programming of the device is achieved through the MICROWIRE interface. The device can be powered down through a register programming or toggling the Chip Enable (CE) pin.

# 7.2 Functional Block Diagram

# 7.3 Feature Description

### 7.3.1 Differences Between the LMX2571 and LMX2571-EP

For both devices, pin 8 is not connected to the die and pins 14 and 26 are. However, tor the LMX2571-EP, both Pin 36 and Pin 18 are different and are true no connect pins, meaning that this pin is not connected to the die. This impacts some of the functionality of the device.

| Aspect          | Details             | LMX2571                   | LMX2571-EP                                 |

|-----------------|---------------------|---------------------------|--------------------------------------------|

|                 | Pin 36              | OSCin*                    | NC. There is no connection to the die.     |

|                 |                     |                           | Not Supported<br>R34[14]=0                 |

|                 | Differential leases | Supported                 | One may drive OSCin and pin 36 with a      |

| Defense heret   | Differential Input  | R34[14]=IPBUF_SE_DIFF_SEL | differential signal, but pin 36 is high    |

| Reference Input |                     |                           | impedance (open) and the signal is ignored |

|                 |                     |                           | at this pin.                               |

|                 |                     | Supported                 | Not Supported                              |

|                 | Crystal Mode        | R34[10]=XTAL_EN           | R34[10]=0                                  |

|                 |                     | R34[11]=XTAL_PWRCTRL      | R34[11]=2                                  |

|                 | Pin 18              | TrCtl                     | NC. There is no connection to the die.     |

|                 |                     | Supported                 | Software Only                              |

| Rx/Tx Switching | Dia Quaitataina     | R0[8]=F1F2_CTRL           | R0[8]=0                                    |

|                 | Pin Switching       | R0[10]=RXTX_POL           | R0[10]=0                                   |

|                 |                     | R0[11]=RXTX_CTL           | R0[11]=0                                   |

## 表 7-1. Differences Between LMX2571 and LMX2571-EP

### 7.3.2 Reference Oscillator Input

The OSCin pin is used as frequency reference input to the device. The OSCin pin can be driven single-ended with a CMOS clock.

The OSCin signal is used as a clock for VCO calibration, therefore a proper signal must be applied at the OSCin pin at the time of programming the R0 register. A higher slew rate tends to yield the best fractional spurs and phase noise, so a square wave signal is best for the OSCin pin. If using a sine wave, higher frequencies tend to yield better phase noise and fractional spurs due to their higher slew rates.

## 7.3.3 R-Dividers and Multiplier

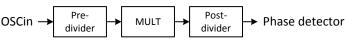

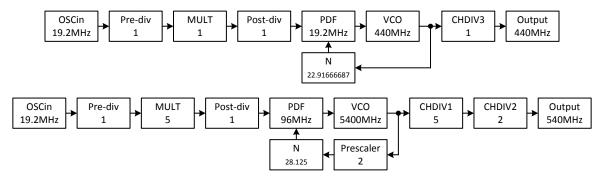

The R-divider consists of a Pre-divider, a Multiplier (MULT), and a Post-divider.

Both the Pre- and Post-dividers divide frequency down while the MULT multiplies frequency up. The purpose of adding a multiplier is to avoid and reduce integer boundary spurs or to increase the phase-detector frequency for higher performance. See *MULT Multiplier* for details. The phase detector frequency, f<sub>PD</sub>, is therefore equal to

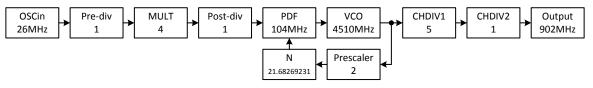

f<sub>PD</sub> = (f<sub>OSCin</sub> / Pre-divider) × (MULT / Post-divider)

(1)

When using the Multiplier (MULT > 1), there are some points to remember:

- The Multiplier must be greater than the Pre-divider.

- Using the multiplier may add noise, especially for multiplier values greater than 6.

## 7.3.4 PLL Phase Detector and Charge Pump

The phase detector compares the outputs of the Post-divider and N-divider and generates a correction current corresponding to the phase error. This charge pump current is programmable to different strengths. The pump

up and pump down currents are individually programmable, but should always programmed to the same value. The effective charge pump current is the sum of the up and down currents and multiplied by a gain multiplier. In other words, Effective Charge Pump Current = (Base Charge Pump Current) × (Gain Multiplier)

### 7.3.4.1 CPout Pin Charge Pump Current

When using internal VCO mode, the charge pump output is the CPout pin and the base charge pump current is programmable in 156.25 µA increments set by the CP\_IUP and CP\_IDN fields (see 表 7-2). This value is doubled and then multiplied by the charge pump gain value specified in  $\frac{1}{5}$  7-3.

| CP_IUP, CP_IDN | BASE CHARGE PUMP CURRENT (µA) |

|----------------|-------------------------------|

| 0              | Tri-State                     |

| 1              | 156.25                        |

| 2              | 312.5                         |

| 3              | 468.75.                       |

|                |                               |

| 7              | 1093.75                       |

| 8 or 16        | 1250                          |

| 9 or 17        | 1406.25                       |

|                |                               |

| 15 or 23       | 2343.75                       |

| 24             | 2500                          |

| 25             | 2656.25                       |

|                |                               |

| 31             | 3593.75                       |

# 表 7-2 Base Charge Pump Current When Using Internal VCO

#### 表 7-3. Charge Pump Gain Multiplier When Using Internal VCO

| CP_GAIN | GAIN MULTIPLIER |

|---------|-----------------|

| 0       | 1X              |

| 1       | 2X              |

| 2       | 1.5X            |

| 3       | 2.5X            |

## 7.3.4.2 Charge Pump Current When Using External VCO

When using external VCO mode, the charge pump output is the CPoutExt pin and the base charge pump current is programmable in 312.5 µA increments set by the EXTVCO CP IUP and EXTVCO CP IDN fields as shown in 表 7-4. Odd values for EXTVCO CP IUP and EXTVCO CP IDN are not valued. This value is doubled and then multiplied by the charge pump gain value specified in  $\frac{1}{8}$  7-5.

| EXTVCO_CP_IUP, EXTVCO_CP_IDN | BASE CHARGE PUMP CURRENT (µA) |

|------------------------------|-------------------------------|

| 0                            | Tri-state                     |

| 2                            | 312.5                         |

| 4                            | 625                           |

| 6                            | 937.5                         |

| 8 or 16                      | 1250                          |

| 10 or 18                     | 1562.5                        |

| 12 or 20                     | 1875                          |

| 14 or 22                     | 2187.5                        |

| 24                           | 2500                          |

# ۰.

| EXTVCO_CP_IUP, EXTVCO_CP_IDN | BASE CHARGE PUMP CURRENT (µA) |

|------------------------------|-------------------------------|

| 26                           | 2812.5                        |

| 28                           | 3125                          |

| 30                           | 3437.5                        |

表 7-4. Base Charge Pump Current in External VCO Mode (continued)

| 表 7-5. Charge | Pump Gain | Multiplier in | External V | CO Mode |

|---------------|-----------|---------------|------------|---------|

|---------------|-----------|---------------|------------|---------|

| EXTVCO_CP_GAIN | CHARGE PUMP GAIN MULTIPLIER |

|----------------|-----------------------------|

| 0              | 1X                          |

| 1              | 2X                          |

| 2              | 1.5X                        |

| 3              | 2.5X                        |

### 7.3.5 PLL N-Divider and Fractional Circuitry

The total N-divider value is determined by  $N_{integer}$  + NUM / DEN. The N-divider includes fractional compensation and can achieve any fractional denominator (DEN) from 1 to 16,777,215 (2<sup>24</sup> – 1). The integer portion,  $N_{integer}$ , is the whole part of the N-divider value and the fractional portion,  $N_{frac}$  = NUM / DEN, is the remaining fraction.  $N_{integer}$ , NUM and DEN are programmable.

The order of the delta sigma modulator is also programmable from integer mode to fourth order. There are several dithering modes that are also programmable. Dithering is used to reduce fractional spurs. In order to make the fractional spurs consistent, the modulator is reset any time that the R0 register is programmed.

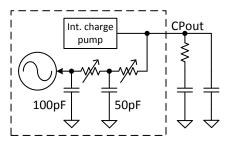

#### 7.3.6 Partially Integrated Loop Filter

The LMX2571-EP integrates the third and fourth pole of the loop filter. The values for the resistors can be programmed independently through the MICROWIRE interface. The larger the values of the resistors, the stronger the attenuation of the internal loop filter. This partially integrated loop filter can only be used in synthesizer mode.

图 7-2. Integrated Loop Filter

#### 7.3.7 Low-Noise, Fully Integrated VCO

The LMX2571-EP includes a fully integrated VCO. The VCO generates a frequency which varies with the tuning voltage from the loop filter. Output of the VCO is fed to a prescaler before going to the N-divider. The prescaler value is selectable between 2 and 4. In general, prescaler equals 2 will result in better phase noise especially when the PLL is operated in fractional-N mode. If the prescaler equals 4, however, the device will consume less current. The VCO frequency is related to the other frequencies and Prescaler as follows:

$f_{VCO} = f_{PD} \times N$ -divider × Prescaler

(2)

To reduce the VCO tuning gain, thus improving the VCO phase noise performance, the VCO frequency range is divided into several different frequency bands. This creates the need for frequency calibration to determine the correct frequency band given a desired output frequency. The VCO is also calibrated for amplitude to optimize phase noise. These calibration routines are activated any time that the R0 register is programmed with the FCAL\_EN bit equals one. It is important that a valid OSCin signal must present before VCO calibration begins.

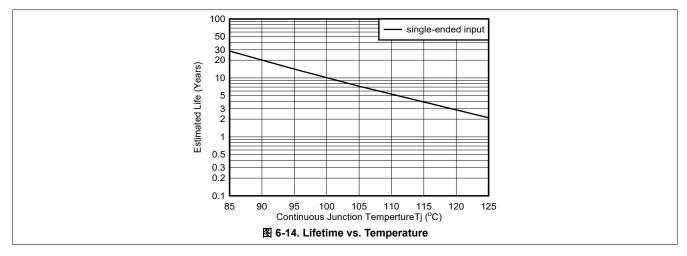

This device will support a full sweep of the valid temperature range of  $125^{\circ}C$  ( –  $40^{\circ}C$  to  $85^{\circ}C$ ) without having to recalibrate the VCO. This is important for continuous operation of the synthesizer under the most extreme temperature variation.

### 7.3.8 External VCO Support

The LMX2571-EP supports an external VCO in PLL mode. In PLL mode, the internal VCO and its associated charge pump are powered down, and a 5-V charge pump is switched in to support external VCO. No extra external low noise op-amp is required to support 5-V tuning range VCO. The external VCO output can be obtained directly from the VCO or from the RF output buffer of the device.

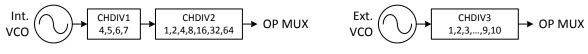

### 7.3.9 Programmable RF Output Divider

The internal VCO RF output divider consists of two sub-dividers; the total division value is equal to the multiplication of them. As a result, the minimum division is 4 while the maximum division is 448.

图 7-3. VCO Output Divider

There is only one output divider when external VCO is being used. This divider supports even and odd division, and its values are programmable between 1 and 10.

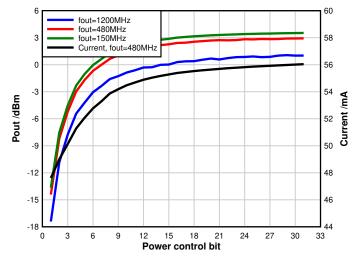

#### 7.3.10 Programmable RF Output Buffer

The RF output buffer type is selectable between push-pull and open-drain. If the open-drain buffer is selected, external pullup to VccIO is required. Regardless of output type, output power can be programmed to various levels. The RF output buffer can be disabled while still keeping the PLL in lock. See *RF Output Buffer Type* for details.

#### 7.3.11 Integrated TX, RX Switch

The LMX2571-EP integrates a T/R switch. The output from the internal VCO or external VCO divider will be routed to either the RFoutTx or RFoutRx ports, depending on the state of the F1F2\_SEL bit.

The T/R switch could also be configured as a fanout buffer to output the same signal at both RFoutTx and RFoutRx ports at the same time. All of these features are also programmable, see *Programming* for details.

### 7.3.12 Power Down

The LMX2571-EP can be powered up and down using the CE pin or the POWERDOWN bit. All registers are preserved in memory and the device may still be programmed when the device is in a powered down state. When the device comes out of the powered down state, do the following:

- 1. If it was powered-down by CE pin, pull CE pin HIGH

- 2. If it was powered-down by POWERDOWN bit, set POWERDOWN = 0 and FCAL\_EN = 0

- 3. Wait for 100-µs to have the internal LDOs settled down

- 4. Program register R0 with FCAL\_EN=1

## 7.3.13 Lock Detect

The MUXout pin of the LMX2571-EP can be configured to output a signal that indicates when the PLL is being locked. If lock detect is enabled while the MUXout pin is configured as a lock-detect output, when the device is locked the MUXout pin output is a logic HIGH voltage. When the device is unlocked, MUXout output is a logic LOW voltage.

## 7.3.14 FSK Modulation

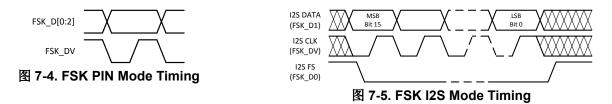

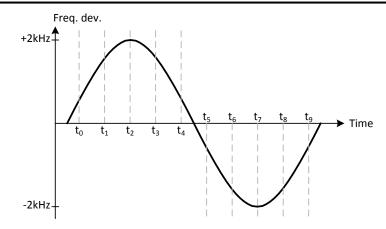

Direct digital FSK modulation is supported in LMX2571-EP. FSK modulation is achieved by changing the output frequency by changing the N-divider value. The LMX2571-EP supports four different types of FSK operation.

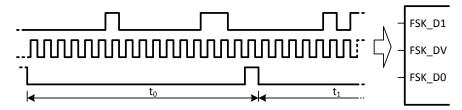

1. FSK PIN mode. LMX2571-EP supports 2-, 4-, and 8-level FSK modulation in PIN mode. In this mode, symbols are directly fed to the FSK\_D0, FSK\_D1, and FSK\_D2 pins. Symbol clock is fed to the FSK\_DV pin.

Symbols are latched into the device on the rising edge of the symbol clock. The maximum supported symbol clock rate is 1 MHz. The device has eight dedicated registers to prestore the desired FSK frequency deviations, with each register corresponding to one of the FSK symbols. The LMX2571-EP will change its output frequency according to the states on the FSK pins; no extra register programming is required.

- FSK SPI mode. This mode is identical to the FSK PIN mode with the exception that the control for the selected FSK level is not performed with external pins but with register R34. Each time when register R34 is programmed, change only the FSK\_DEV\_SEL field to select the desired FSK frequency deviation as stored in the dedicated registers.

- 3. FSK SPI FAST mode. In this mode, instead of selecting one of the prestored FSK level, change the FSK deviation directly by writing to the register R33, FSK\_DEV\_SPI\_FAST field. As a result, this mode supports arbitrary-FSK level, which is useful to construct pulse-shaping or analog-FM modulation.

- 4. FSK I2S mode. This mode is similar to the FSK SPI FAST mode, but the programming format is an I2S format on dedicated pins instead of SPI. The benefit of using I2S is that this interface could be shared and synchronous to other digital audio interfaces. The same FSK data input pins that are used in FSK PIN mode are reused to support I2S programming. In this mode only the 16 bits of DATA field is required to program. The data is transmitted on the high or low side of the frame sync (programmable in register R34,

FSK\_I2S\_FS\_POL). The unused side of the frame sync needs to be at least one clock cycle. In other words, 17 (16 + 1) CLK cycles are required at a minimum for one I2S frame. Maximum I2S clock rate is 100 MHz.

See Direct Digital FSK Modulation for FSK operation details.

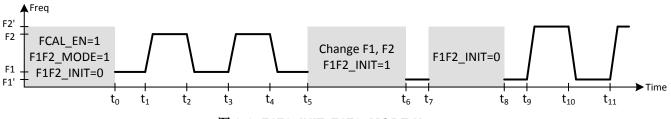

## 7.3.15 FastLock

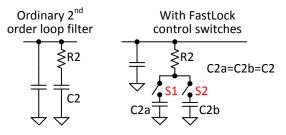

The LMX2571-EP includes a FastLock feature that can be used to improve the lock times in PLL mode when the loop bandwidth is small. In general, the lock time is approximately equal to 4 divided by the loop bandwidth. If the loop bandwidth is 1 kHz, then the lock time would be 4 ms. However, if the f<sub>PD</sub> is much higher than the loop bandwidth, cycle slipping may occur, and the actual lock time will be much longer. Traditional fastlock usually reduces lock time by increasing loop bandwidth during frequency switching. However, there is a limitation on the achievable maximum loop bandwidth due to limitation on charge-pump current and loop filter component values. In some cases, this kind of fastlock technique will make cycle slip even worse.

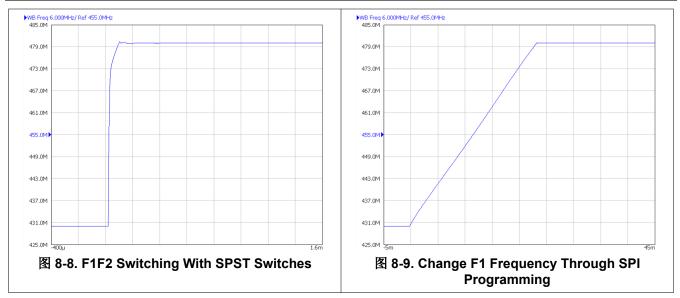

The LMX2571-EP adopts a new FastLock approach that eliminates the cycle slip problem. With an external analog SPST switch in conjunction with FastLock control of the LMX2571-EP, the lock time for a 100-MHz frequency switch could be settled in less than 1.5 ms. See *FastLock With External VCO* for details.

#### 7.3.16 Register Readback

The LMX2571-EP allows any of its registers to be read back. The MUXout pin can be programmed to support either lock-detect output or register-readback serial-data output. To read back a certain register value, follow the following steps:

- 1. Set the R/W bit to 1; the data field contents are ignored.

- 2. Send the register to the device; readback serial data outputs starting at the falling edge of the 8<sup>th</sup> clock cycle.

图 7-6. Register Readback Timing Diagram

# 7.4 Device Functional Modes

## 7.4.1 Operation Mode

The device can be operated in synthesizer mode or PLL mode.

- 1. Synthesizer mode. The internal VCO is adopted.

- 2. PLL mode. The device is operated as a standalone PLL; an external VCO is required to complete the loop.

## 7.4.2 Duplex Mode

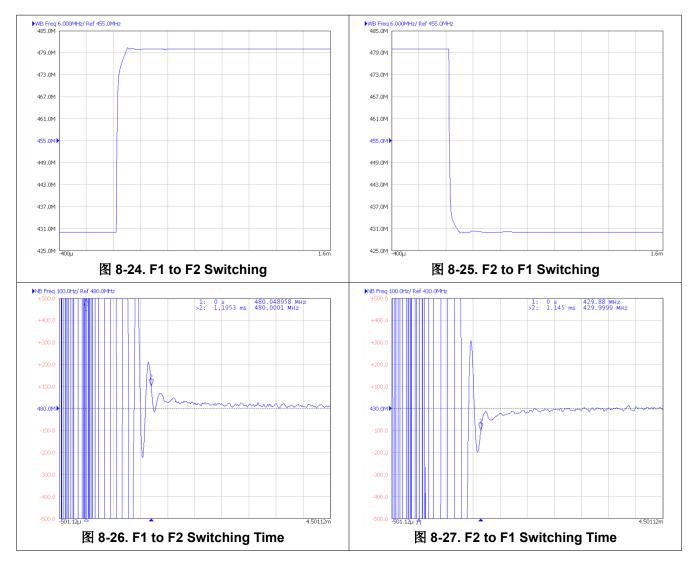

LMX2571-EP supports fast frequency switching between two predefined register sets, F1 and F2. This feature is good for duplex operation. The device supports three duplex modes:

- 1. Synthesizer duplex mode. Both F1 and F2 are operated in synthesizer mode.

- 2. PLL duplex mode. Both F1 and F2 are operated in PLL mode.

- 3. Synthesizer/PLL duplex mode. In this mode, F1 and F2 will be operated in different operation mode.

## 7.4.3 FSK Mode

LMX2571-EP supports four direct digital FSK modulation modes.

- 1. FSK PIN mode. 2-, 4-, and 8-level FSK modulation. Modulation data is fed to the device through dedicated pins.

- 2. FSK SPI mode. 2-, 4-, and 8-level FSK modulation. Pre-defined FSK deviation is selected through SPI programming.

- 3. FSK SPI FAST mode. This mode supports arbitrary-level FSK modulation. Desired FSK deviation is written to the device through SPI programming.

- 4. FSK I2S mode. Arbitrary-level FSK modulation is supported. Desired FSK deviation is fed to the device through dedicated pins.

## 7.5 Programming

The LMX2571-EP is programmed using several 24-bit registers. A 24-bit shift register is used as a temporary register to indirectly program the on-chip registers. The shift register consists of a data field, an address field, and a R/W bit. The MSB is the R/W bit. 0 means register write while 1 means register read. The following 7 bits, ADDR[6:0], form the address field which is used to decode the internal register address. The remaining 16 bits form the data field DATA[15:0]. While LE is low, serial data is clocked into the shift register upon the rising edge of clock. Serial data is shifted MSB first into the shift register when programming. When LE goes high, data is transferred from the data field into the selected active register bank. See 🔀 6-1 for timing diagram details.

## 7.5.1 Recommended Initial Power on Programming Sequence

When the device is first powered up, it must to be initialized, and the ordering of this programming is important. The sequence is listed below. After this sequence is completed, the device should be running and locked to the proper frequency.

- 1. Apply power to the device and ensure the Vcc pins are at the proper levels.

- 2. If CE is LOW, pull it HIGH.

- 3. Wait 100 µs for the internal LDOs to become stable.

- 4. Ensure that a valid reference is applied to the OSCin pin.

- 5. Program register R0 with RESET=1. This will ensure all the registers are reset to their default values.

6. Program in sequence registers R60, R58, R53, ..., R1 and then R0.

# 7.5.2 Recommended Sequence for Changing Frequencies

The recommended sequence for changing frequencies in different scenarios is as follows:

- 1. If the N-divider is changing, program the relevant registers, then program R0 with FCAL\_EN = 1.

- 2. In FSK SPI mode, FSK SPI FAST mode, and FSK I2S mode, the fractional numerator is changing; program the relevant registers only.

- 3. If switching frequency between F1 and F2, program the relevant control registers only toggle the F1F2\_SEL bit.

# 7.6 Register Maps

|      | 23  | 22 | 21  | 20 | 19   | 18 | 17 | 16 | 15                     | 14          | 13      | 12       | 11                                    | 10                                             | 9       | 8       | 7                       | 6                       | 5                      | 4                     | 3                     | 2                    | 1        | 0     | POR     |

|------|-----|----|-----|----|------|----|----|----|------------------------|-------------|---------|----------|---------------------------------------|------------------------------------------------|---------|---------|-------------------------|-------------------------|------------------------|-----------------------|-----------------------|----------------------|----------|-------|---------|

| REG. | R/W | AD | DRI |    | 6:0] |    | -  |    | DATA[15:0]             |             |         |          |                                       |                                                |         | 1       |                         | 1                       |                        |                       |                       |                      |          |       |         |

| R60  | R/W | 0  | 1   | 1  | 1    | 1  | 0  | 0  | 1                      | 0           | 1       | 0        | 0                                     | 0                                              | 0       | 0       | 0                       | 0                       | 0                      | 0                     | 0                     | 0                    | 0        | 0     | 3C4000h |

| R58  | R/W | 0  | 1   | 1  | 1    | 0  | 1  | 0  | 1                      | 0           | 0       | 0        | 1                                     | 1                                              | 0       | 0       | 0                       | 0                       | 0                      | 0                     | 0                     | 0                    | 0        | 0     | 3A0C00h |

| R53  | R/W | 0  | 1   | 1  | 0    | 1  | 0  | 1  | 0                      | 1           | 1       | 1        | 1                                     | 0                                              | 0       | 0       | 0                       | 0                       | 0                      | 0                     | 0                     | 1                    | 1        | 0     | 352802h |

| R47  | R/W | 0  | 1   | 0  | 1    | 1  | 1  | 1  | 0                      | DITH        | ERING   | 0        | 0 0 0 0 0 0 0 0 0 0 0 0 0 0           |                                                |         |         |                         |                         |                        |                       |                       | 2F0000h              |          |       |         |

| R46  | R/W | 0  | 1   | 0  | 1    | 1  | 1  | 0  | 0                      | 0           | 0       | 0        | 0                                     | 0                                              | 0       | 0       | 0                       | 0                       | 0                      | 1                     | 1                     | VCO_<br>SEL_<br>STRT | VCC      | D_SEL | 2E001Ah |

| R42  | R/W | 0  | 1   | 0  | 1    | 0  | 1  | 0  | 0                      | 0           | 0       | 0        | 0                                     | 0                                              | 1       | 0       | 0                       | 0                       | EXTVCO<br>_CP<br>_POL  |                       |                       | EXTVCO_              | CP_IDN   |       | 2A0210h |

| R41  | R/W | 0  | 1   | 0  | 1    | 0  | 0  | 1  | 0                      | 0           | 0       | 0        | 0 EXTVCO_CP_IUP EXTVCO_CP_GAIN CP_IDN |                                                |         |         |                         |                         |                        |                       |                       |                      | 290810h  |       |         |

| R40  | R/W | 0  | 1   | 0  | 1    | 0  | 0  | 0  | 0                      | 0           | 0       |          |                                       | CP_IL                                          | IP      |         | CP_                     | GAIN                    | 0                      | 1                     | 1                     | 1                    | 0        | 0     | 28101Ch |

| R39  | R/W | 0  | 1   | 0  | 0    | 1  | 1  | 1  | 0                      | 0           | 0       | 1        | 0                                     | 0                                              | 0       | 1       | 1                       | 1                       | 1                      | 1                     | SDO_LD_<br>SEL        | 0                    | 1        | LD_EN | 2711F0h |

| R35  | R/W | 0  | 1   | 0  | 0    | 0  | 1  | 1  | 0                      | 0           |         |          | MULT_WAITAUTOTX                       |                                                |         |         |                         |                         | OUTBUF<br>_RX<br>_TYPE | 230647h               |                       |                      |          |       |         |

| R34  | R/W | 0  | 1   | 0  | 0    | 0  | 1  | 0  | IPBUF<br>DIFF_<br>TERM | 0           | 0       | 1        | 0                                     | 0 0 0 FSK 123 FSK 125 FSK LEVEL FSK DEV SEL MC |         |         |                         |                         |                        | FSK_<br>MODE_<br>SEL0 | FSK_<br>MODE_<br>SEL1 | 221000h              |          |       |         |

| R33  | R/W | 0  | 1   | 0  | 0    | 0  | 0  | 1  |                        | 1           |         |          | FSK_DEV_SPI_FAST                      |                                                |         |         |                         |                         |                        |                       | 210000h               |                      |          |       |         |

| R32  | R/W | 0  | 1   | 0  | 0    | 0  | 0  | 0  |                        | FSK_DEV7_F2 |         |          |                                       |                                                |         |         |                         |                         | 200000h                |                       |                       |                      |          |       |         |

| R31  | R/W | 0  | 0   | 1  | 1    | 1  | 1  | 1  |                        |             |         |          |                                       |                                                |         | F       | SK_DEV6_F2              |                         |                        |                       |                       |                      |          |       | 1F0000h |

| R30  | R/W | 0  | 0   | 1  | 1    | 1  | 1  | 0  |                        |             |         |          |                                       |                                                |         | F       | SK_DEV5_F2              |                         |                        |                       |                       |                      |          |       | 1E0000h |

| R29  | R/W | 0  | 0   | 1  | 1    | 1  | 0  | 1  |                        |             |         |          |                                       |                                                |         | F       | SK_DEV4_F2              |                         |                        |                       |                       |                      |          |       | 1D0000h |

| R28  | R/W | 0  | 0   | 1  | 1    | 1  | 0  | 0  |                        |             |         |          |                                       |                                                |         | F٩      | SK_DEV3_F2              |                         |                        |                       |                       |                      |          |       | 1C0000h |

| R27  | R/W | 0  | 0   | 1  | 1    | 0  | 1  | 1  |                        |             |         |          |                                       |                                                |         | F       | SK_DEV2_F2              |                         |                        |                       |                       |                      |          |       | 1B0000h |

| R26  | R/W | 0  | 0   | 1  | 1    | 0  | 1  | 0  |                        |             |         |          |                                       |                                                |         | F       | SK_DEV1_F2              |                         |                        |                       |                       |                      |          |       | 1A0000h |

| R25  | R/W | 0  | 0   | 1  | 1    | 0  | 0  | 1  |                        |             |         |          |                                       | _                                              |         | F       | SK_DEV0_F2              |                         |                        |                       |                       |                      |          |       | 190000h |

| R24  | R/W | 0  | 0   | 1  | 1    | 0  | 0  | 0  | 0                      | 0           | 0       | 0        | 0                                     | FSK_E                                          | N       | EXTVC   | O_CHDIV_F2              |                         | EXTVCO<br>_SEL<br>_F2  |                       |                       | OUTBUF_TX            | _PWR_F2  |       | 180010h |

| R23  | R/W | 0  | 0   | 1  | 0    | 1  | 1  | 1  | 0                      | 0           | 0       |          | OU <sup>.</sup>                       | TBUF_RX                                        | _PWR_F2 |         | OUTBUF<br>_TX_EN<br>_F2 | OUTBUF<br>_RX_EN<br>_F2 | 0                      | 0                     | 0                     |                      | LF_R4_F2 |       | 1710A4h |

| R22  | R/W | 0  | 0   | 1  | 0    | 1  | 1  | 0  |                        | LF_R3_F2    |         |          | CHDIV2_                               | F2                                             | СН      | DIV1_F2 | F                       | PFD_DELAY_              | F2                     |                       |                       | MULT                 | _F2      |       | 168584h |

| R21  | R/W | 0  | 0   | 1  | 0    | 1  | 0  | 1  |                        |             |         | PLL_I    | PLL_R_F2 PLL_R_PRE_F2 1               |                                                |         |         |                         |                         |                        | 150101h               |                       |                      |          |       |         |

| R20  | R/W | 0  | 0   | 1  | 0    | 1  | 0  | 0  | PLL_N_<br>PRE_F2       | FR          | AC_ORDE | R_F2     |                                       |                                                |         |         |                         | PLL                     | N_F2                   |                       |                       |                      |          |       | 140028h |

| R19  | R/W | 0  | 0   | 1  | 0    | 0  | 1  | 1  |                        |             |         |          |                                       |                                                |         | PLL     | _DEN_F2[15:0            | 0]                      |                        |                       |                       |                      |          |       | 130000h |

| R18  | R/W | 0  | 0   | 1  | 0    | 0  | 1  | 0  |                        |             |         |          |                                       |                                                |         | PLL     | _NUM_F2[15:             | 0]                      |                        |                       |                       |                      |          |       | 120000h |

| R17  | R/W | 0  | 0   | 1  | 0    | 0  | 0  | 1  |                        |             |         | PLL_DEN_ | _F2[23:16                             | ]                                              |         |         |                         |                         | l                      | PLL_I                 | NUM_F2[23:1           | 6]                   |          |       | 110000h |

| R16  | R/W | 0  | 0   | 1  | 0    | 0  | 0  | 0  |                        | FSK_DEV7_F1 |         |          |                                       |                                                |         |         |                         |                         | 100000h                |                       |                       |                      |          |       |         |

LMX2571-EP ZHCSP40B - OCTOBER 2021 - REVISED JUNE 2022

|      | 23  | 22 | 21  | 20  | 19   | 18 | 17 | 16 | 15               | 14       | 13          | 12            | 11               | 10          | 9             | 8       | 7                                             | 6                       | 5     | 4      | 3           | 2        | 1       | 0       | POR    |

|------|-----|----|-----|-----|------|----|----|----|------------------|----------|-------------|---------------|------------------|-------------|---------------|---------|-----------------------------------------------|-------------------------|-------|--------|-------------|----------|---------|---------|--------|

| REG. | R/W | AD | DRE | SS[ | 6:0] |    | -  | -  | DATA[15:0]       |          |             |               |                  |             |               |         |                                               |                         |       |        |             |          |         |         |        |

| R15  | R/W | 0  | 0   | 0   | 1    | 1  | 1  | 1  |                  |          |             |               |                  |             |               | FS      | K_DEV6_F1                                     |                         |       |        |             |          |         |         | F0000h |

| R14  | R/W | 0  | 0   | 0   | 1    | 1  | 1  | 0  |                  |          |             |               |                  |             |               | FS      | K_DEV5_F1                                     |                         |       |        |             |          |         |         | E0000h |

| R13  | R/W | 0  | 0   | 0   | 1    | 1  | 0  | 1  |                  |          |             |               |                  |             |               | FS      | K_DEV4_F1                                     |                         |       |        |             |          |         |         | D0000h |

| R12  | R/W | 0  | 0   | 0   | 1    | 1  | 0  | 0  |                  |          |             |               |                  | FSK_DEV3_F1 |               |         |                                               |                         |       |        |             |          | C0000h  |         |        |

| R11  | R/W | 0  | 0   | 0   | 1    | 0  | 1  | 1  |                  |          |             |               | FSK_DEV2_F1      |             |               |         |                                               |                         |       |        |             | B0000h   |         |         |        |

| R10  | R/W | 0  | 0   | 0   | 1    | 0  | 1  | 0  |                  |          |             |               | FSK_DEV1_F1      |             |               |         |                                               |                         |       |        | A0000h      |          |         |         |        |

| R9   | R/W | 0  | 0   | 0   | 1    | 0  | 0  | 1  |                  |          | FSK_DEV0_F1 |               |                  |             |               |         |                                               |                         |       | 90000h |             |          |         |         |        |

| R8   | R/W | 0  | 0   | 0   | 1    | 0  | 0  | 0  | 0                | 0        | 0           | 0             | 0                | FSK_E       | N             | EXTVC   | D_CHDIV_F1 EXTVCO<br>_SEL OUTBUF_TX_PW<br>_F1 |                         |       |        |             | X_PWR_F1 |         | 80010h  |        |

| R7   | R/W | 0  | 0   | 0   | 0    | 1  | 1  | 1  | 0                | 0        | 0           |               | OU               | TBUF_RX_    | _PWR_F1       |         | OUTBUF<br>_TX_EN<br>_F1                       | OUTBUF<br>_RX_EN<br>_F1 | 0     | 0      | 0           |          | LF_R4_F | 1       | 710A4h |

| R6   | R/W | 0  | 0   | 0   | 0    | 1  | 1  | 0  |                  | LF_R3_F1 |             |               | CHDIV2_          | F1          | СН            | DIV1_F1 | F                                             | PFD_DELAY_I             | =1    |        |             | MUL      |         | 68584h  |        |

| R5   | R/W | 0  | 0   | 0   | 0    | 1  | 0  | 1  |                  |          |             | PLL_F         | R_F1             |             |               |         |                                               |                         |       | PLI    | R_PRE_F1    |          |         |         | 50101h |

| R4   | R/W | 0  | 0   | 0   | 0    | 1  | 0  | 0  | PLL_N_<br>PRE_F1 | FRAC     |             | ₹_F1          |                  |             |               |         |                                               | PLL                     | _N_F1 |        |             |          |         |         | 40028h |

| R3   | R/W | 0  | 0   | 0   | 0    | 0  | 1  | 1  |                  |          |             |               |                  |             |               | PLL_    | DEN_F1[15:0                                   | 0]                      |       |        |             |          |         |         | 30000h |

| R2   | R/W | 0  | 0   | 0   | 0    | 0  | 1  | 0  |                  |          |             |               | PLL_NUM_F1[15:0] |             |               |         |                                               |                         |       |        | 20000h      |          |         |         |        |

| R1   | R/W | 0  | 0   | 0   | 0    | 0  | 0  | 1  |                  |          |             | PLL_DEN_      | F1[23:16]        |             |               |         |                                               |                         |       | PLL_I  | NUM_F1[23:1 | 6]       |         |         | 10000h |

| R0   | R/W | 0  | 0   | 0   | 0    | 0  | 0  | 0  | 0                | 0        | RESET       | POWER<br>DOWN | 0                | 0           | F1F2_<br>INIT | 0       | F1F2_<br>MODE                                 | F1F2_<br>SEL            | 0     | 0      | 0           | 0        | 1       | FCAL_EN | 3h     |

The POR value is the power-on reset value that is assigned when the device is powered up or the RESET bit is asserted. POR is not a default working mode, all registers are required to program properly in order to make the device works as desired.

# 7.6.1 R60 Register (offset = 3Ch) [reset = 4000h]

|    | 图 7-7. R60 Register |    |    |    |    |   |       |       |   |   |   |   |   |   |   |

|----|---------------------|----|----|----|----|---|-------|-------|---|---|---|---|---|---|---|