LM53600-Q1, LM53601-Q1

JUNE 2015 - REVISED MAY 2021

# LM53600/01-Q1 0.65A/1A、36V 同步、2.1MHz 汽车级降压直流/直流转换器

# 1 特性

- 符合汽车应用要求

- 具有符合 AEC-Q100 标准的下列特性:

- 器件温度等级 1:-40°C 至 125°C 环境工作温度 范围

- 器件 HBM 分类等级 2

- 器件 CDM 分类等级 C5

- -40°C 至 150°C 的结温范围(可用)

- 宽工作输入电压范围: 3.55V 到 36V ( 瞬态电压高 达 42V)

- 提供扩展频谱选项

- 2.1MHz 固定开关频率

- 低静态电流:23 µ A

- 关断电流:1.8µA

- 可调、3.3V 或 5V 三种输出

- 最大电流负载:LM53600-Q1 为 650mA, LM53601-Q1 为 1000mA

- 引脚可选强制 PWM 模式

- 具有滤波和延迟释放功能的 RESET 输出

- 外部频率同步

- 内部补偿、软启动、电流限制和欠压锁定 (UVLO)

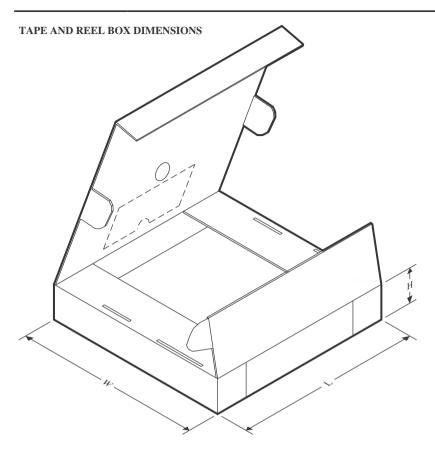

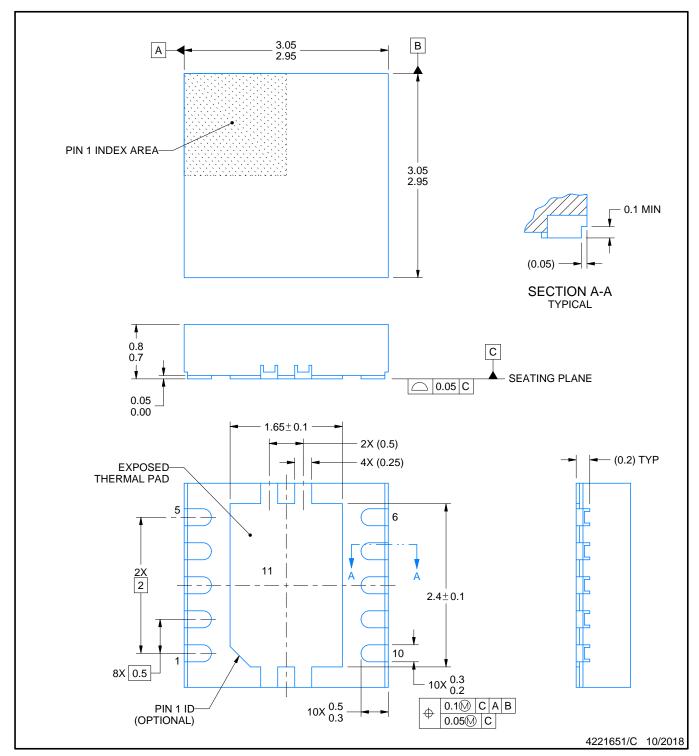

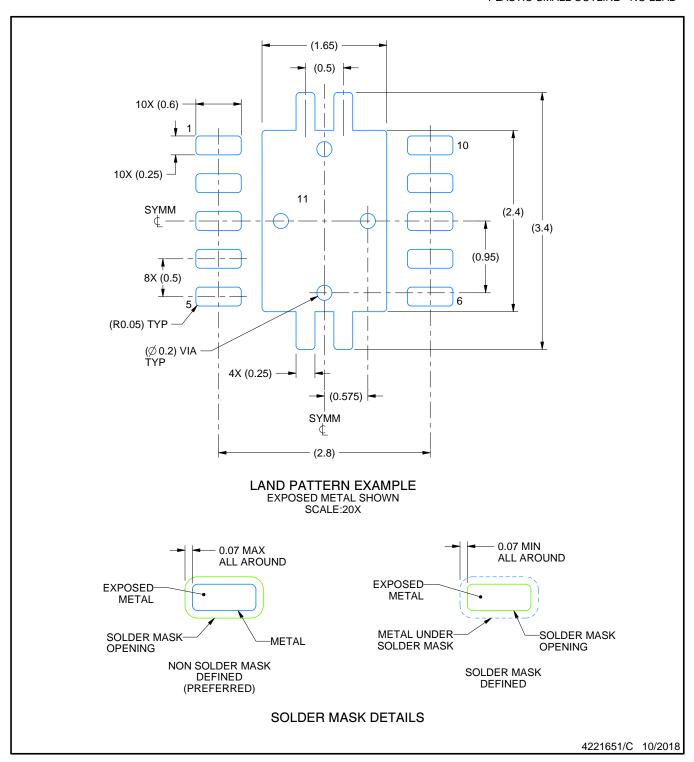

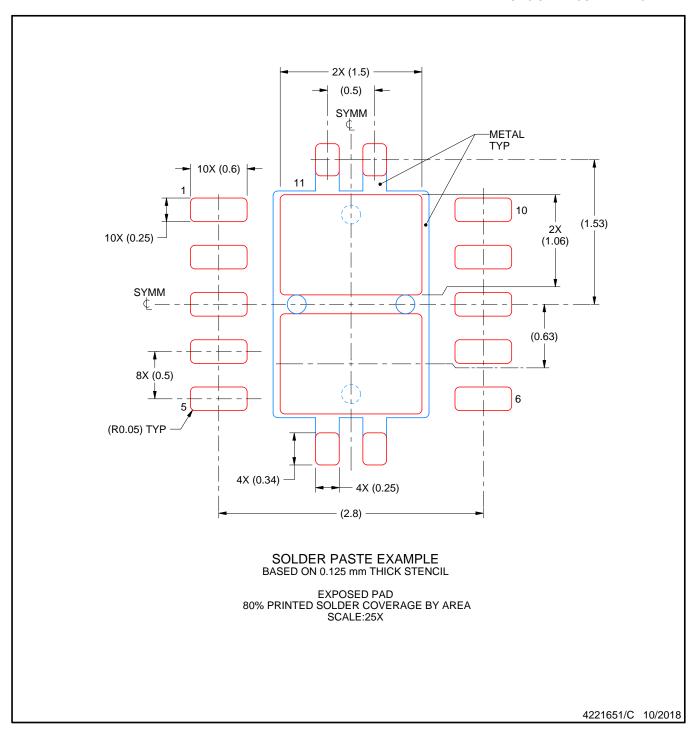

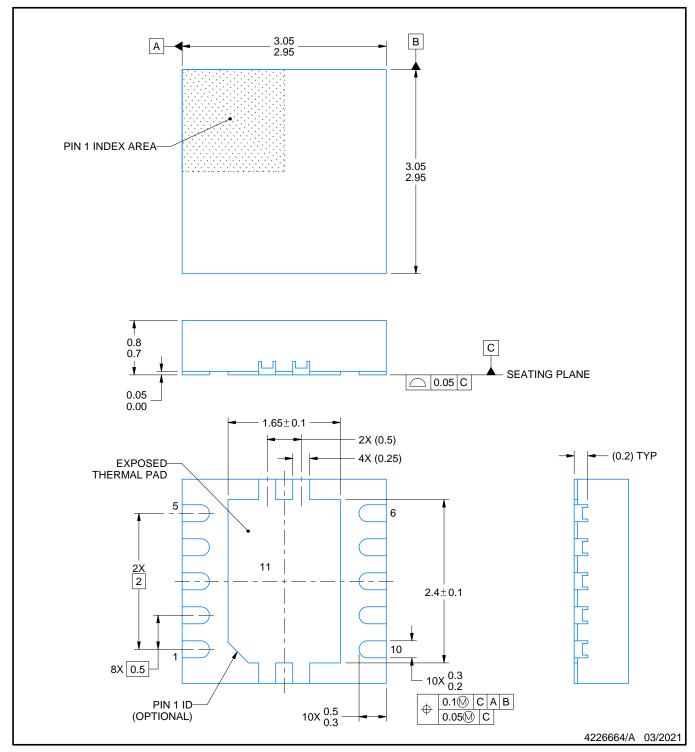

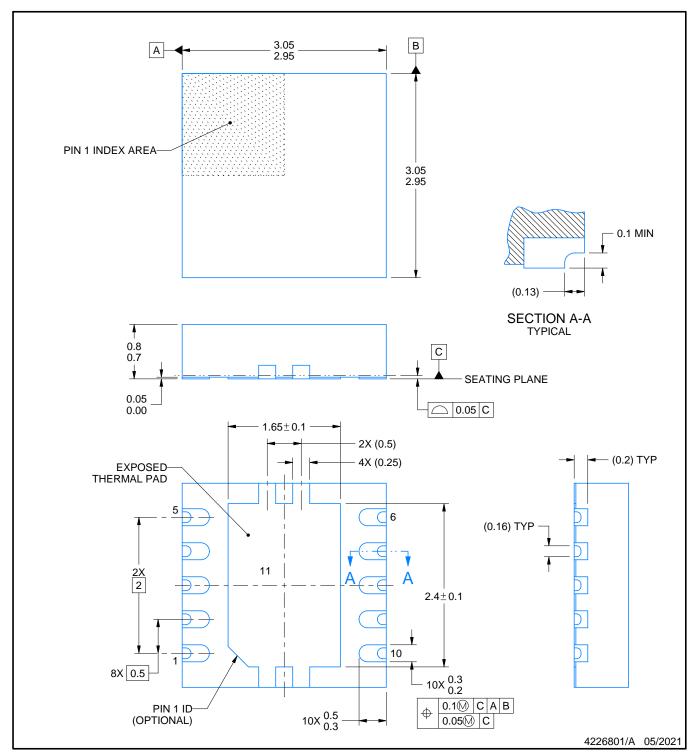

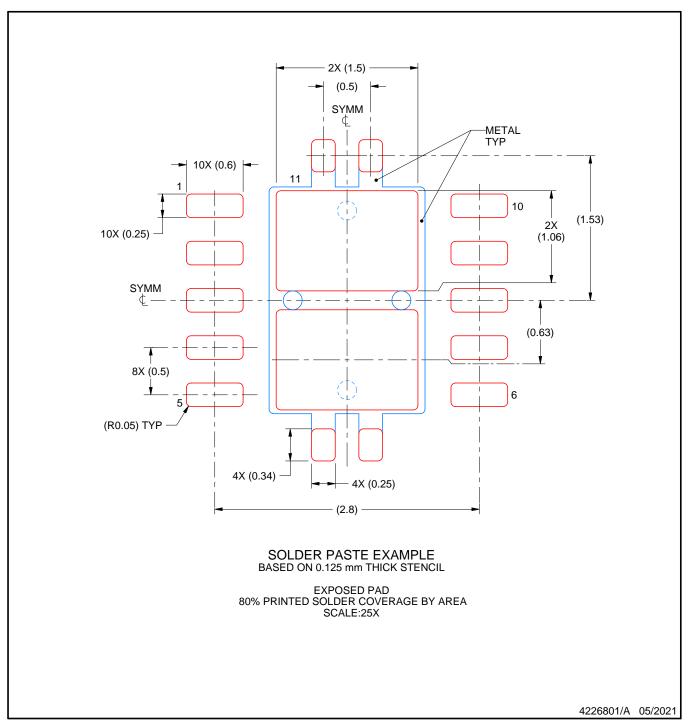

- 具有可湿性侧面和非可湿性侧面的 10 引脚 3mm x 3mm SON 封装

## 2 应用

- 汽车摄像头应用

- 汽车驾驶辅助系统

- 汽车车身应用

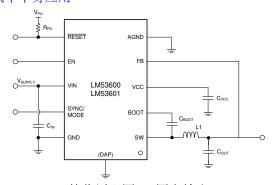

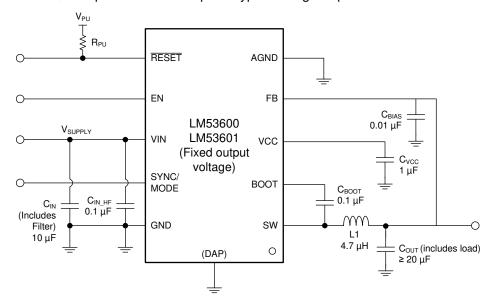

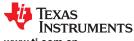

简化原理图 - 固定输出

# 3 说明

LM53600-Q1 和 LM53601-Q1 同步降压稳压器器件针 对汽车应用进行了优化,能够提供 5V、3.3V 的输出电 压或可调输出电压。LM53600-Q1 支持高达 650mA 的 负载电流,而 LM53601-Q1 支持高达 1000mA 的负载 电流。LM53600-Q1 和 LM53601-Q1 器件可利用高级 高速电路在 2.1MHz 的固定频率下实现从 18V 输入到 3.3V 输出的稳压。这两款器件采用创新型架构,在输 入电压仅为 3.8V 时也可提供 3.3V 稳压输出。输入电 压最高可达 36V,容许的最高瞬态电压达 42V,这简 化了输入浪涌保护设计。开漏复位输出具有滤波和延迟 释放功能,可提供正确的系统状态指示。凭借这一特 性,器件无需使用附加监控元件,这节省了成本和电路 板空间。这两款器件可在 PWM 和 PFM 两种模式之间 无缝切换,并且静态电流仅为 23µA,这确保了其在所 有负载条件下均可展现高效率和出色的瞬态响应。只需 很少的外部元件,因此印刷电路板 (PCB) 布局可以更 加紧凑。尽管 LM53600-Q1 和 LM53601-Q1 器件属于 Q1级,但均可在-40°C至150°C的结温范围内保证 电气特性。

#### 器件信息

| 器件型号       | 封装 <sup>(1)</sup> | 封装尺寸 ( 标称值 )    |

|------------|-------------------|-----------------|

| LM53600-Q1 | WSON (10)         | 3.00mm x 3.00mm |

| LM53601-Q1 | VV3014 (10)       | 3.00mm x 3.00mm |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 (1)

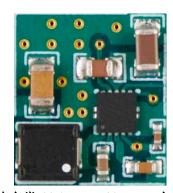

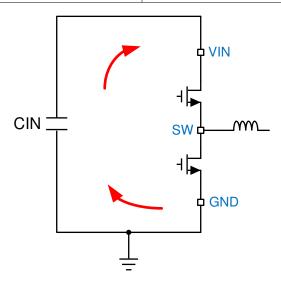

汽车类 11.2mm x 12.7mm 布局

# **Table of Contents**

| 1 特性                                                                               | 1             | 8.4 Device Functional Modes                            |                            |

|------------------------------------------------------------------------------------|---------------|--------------------------------------------------------|----------------------------|

| 2 应用                                                                               |               | 9 Applications and Implementation                      | 18                         |

| 3 说明                                                                               |               | 9.1 Application Information                            |                            |

| 4 Revision History                                                                 |               | 9.2 Typical Applications                               | 19                         |

| 5 Device Comparison                                                                |               | 9.3 Do's and Don't's                                   |                            |

| 6 Pin Configuration and Functions                                                  |               | 10 Power Supply Recommendations                        |                            |

| 7 Specifications                                                                   |               | 11 Layout                                              |                            |

| 7.1 Absolute Maximum Ratings                                                       |               | 11.1 Layout Guidelines                                 |                            |

| 7.2 ESD Ratings                                                                    |               | 11.2 Layout Example                                    |                            |

| 7.3 Recommended Operating Conditions                                               |               | 12 Device and Documentation Support                    |                            |

| 7.4 Thermal Information                                                            |               | 12.1 Documentation Support                             |                            |

| 7.5 Electrical Characteristics                                                     | 6             | 12.2 接收文档更新通知                                          | <mark>32</mark>            |

| 7.6 System Characteristics                                                         | 8             | 12.3 支持资源                                              | 32                         |

| 7.7 Timing Requirements                                                            |               | 12.4 Trademarks                                        | 32                         |

| 7.8 Typical Characteristics                                                        |               | 12.5 静电放电警告                                            | 32                         |

| 8 Detailed Description                                                             |               | 12.6 术语表                                               |                            |

| 8.1 Overview                                                                       | 11            | 13 Mechanical, Packaging, and Orderable                |                            |

| 8.2 Functional Block Diagram                                                       | 11            | Information                                            | 33                         |

| 8.3 Feature Description                                                            | 12            |                                                        |                            |

| Changes from Revision C (April 2021) to - 添加了非可湿性侧面选项                              |               | (May 2021)                                             | Page<br>1                  |

| Changes from Revision B (February 2016                                             | i) to Revisio | on C (April 2021)                                      | Page                       |

|                                                                                    | -             | ,                                                      |                            |

| Changes from Revision A (December 201                                              | 5) to Revis   | ion B (February 2016)                                  | Page                       |

| Updated tables in the Device Comparison                                            | n Table       |                                                        | 3                          |

|                                                                                    | •             | in Pin Functions table in <i>Pin Configuration and</i> |                            |

|                                                                                    |               |                                                        |                            |

|                                                                                    |               |                                                        |                            |

| - Changed $V_{out}$ to $V_{out\_3\_3V}$ , $V_{out\_5V}$ , and $V$                  |               | ble                                                    | 6                          |

|                                                                                    |               | ble3-V, 5-V, and ADJ output voltage options in ₹       | 7.6 table                  |

| <ul> <li>Corrected references for SNAU190 and S</li> </ul>                         |               | .3-V, 5-V, and ADJ output voltage options in 🏄         | <sup>7</sup> .6 table<br>8 |

| • Corrected references for SNAU190 and S  Changes from Revision * (June 2015) to F | SNAU191 in    | .3-V, 5-V, and ADJ output voltage options in #         | <sup>7</sup> .6 table<br>8 |

将器件状态从产品预览更改为量产数据......1

# **5 Device Comparison**

### LM53600-Q1 Devices

| Part Number <sup>(1)</sup> | Output Voltage | Spread<br>Spectrum | Package Qty (2) | Wettable (WF)/Non-Wettable Flanks (non-WF) |

|----------------------------|----------------|--------------------|-----------------|--------------------------------------------|

| LM53600AQDSXRQ1            | Adjustable     | No                 | 3000            | WF                                         |

| LM53600AQDSXTQ1            | Adjustable     | No                 | 250             | WF                                         |

| LM536003QDSXRQ1            | 3.3 V          | No                 | 3000            | WF                                         |

| LM536003QDSXTQ1            | 3.3 V          | No                 | 250             | WF                                         |

| LM536005QDSXRQ1            | 5.0 V          | No                 | 3000            | WF                                         |

| LM536005QDSXTQ1            | 5.0 V          | No                 | 250             | WF                                         |

| LM53600MQDSXRQ1            | Adjustable     | Yes                | 3000            | WF                                         |

| LM53600MQDSXTQ1            | Adjustable     | Yes                | 250             | WF                                         |

| LM53600NQDSXRQ1            | 3.3 V          | Yes                | 3000            | WF                                         |

| LM53600NQDSXTQ1            | 3.3 V          | Yes                | 250             | WF                                         |

| LM53600LQDSXRQ1            | 5.0 V          | Yes                | 3000            | WF                                         |

| LM53600LQDSXTQ1            | 5.0 V          | Yes                | 250             | WF                                         |

| LM53600MQUDSXRQ1           | Adjustable     | Yes                | 3000            | Non-WF                                     |

- (1) LM53600-Q1 devices have maximum recommended operating current of 650 mA.

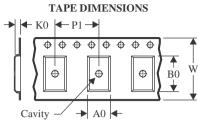

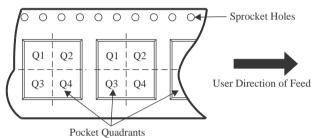

- (2) See Package Option Addendum for tape and reel details as well as links used to order parts.

## LM53601-Q1 Devices

| Part Number <sup>(1)</sup> | Output Voltage | Spread<br>Spectrum | Package Qty (2) | Wettable (WF)/Non-Wettable Flanks (non-WF) |

|----------------------------|----------------|--------------------|-----------------|--------------------------------------------|

| LM53601AQDSXRQ1            | Adjustable     | No                 | 3000            | WF                                         |

| LM53601AQDSXTQ1            | Adjustable     | No                 | 250             | WF                                         |

| LM536013QDSXRQ1            | 3.3 V          | No                 | 3000            | WF                                         |

| LM536013QDSXTQ1            | 3.3 V          | No                 | 250             | WF                                         |

| LM536015QDSXRQ1            | 5.0 V          | No                 | 3000            | WF                                         |

| LM536015QDSXTQ1            | 5.0 V          | No                 | 250             | WF                                         |

| LM53601MQDSXRQ1            | Adjustable     | Yes                | 3000            | WF                                         |

| LM53601MQDSXTQ1            | Adjustable     | Yes                | 250             | WF                                         |

| LM53601NQDSXRQ1            | 3.3 V          | Yes                | 3000            | WF                                         |

| LM53601NQDSXTQ1            | 3.3 V          | Yes                | 250             | WF                                         |

| LM53601LQDSXRQ1            | 5.0 V          | Yes                | 3000            | WF                                         |

| LM53601LQDSXTQ1            | 5.0 V          | Yes                | 250             | WF                                         |

| LM536015QUDSXRQ1           | 5.0 V          | No                 | 3000            | Non-WF                                     |

| LM536013QUDSXRQ1           | 3.3 V          | No                 | 3000            | Non-WF                                     |

| LM53601MQUDSXRQ1           | Adjustable     | Yes                | 3000            | Non-WF                                     |

- (1) LM53601-Q1 devices have maximum recommended operating current of 1000 mA.

- (2) See Package Option Addendum for tape and reel details as well as links used to order parts.

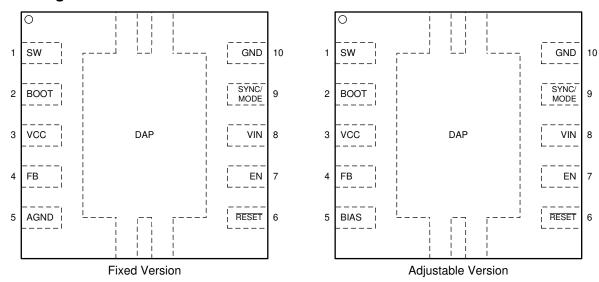

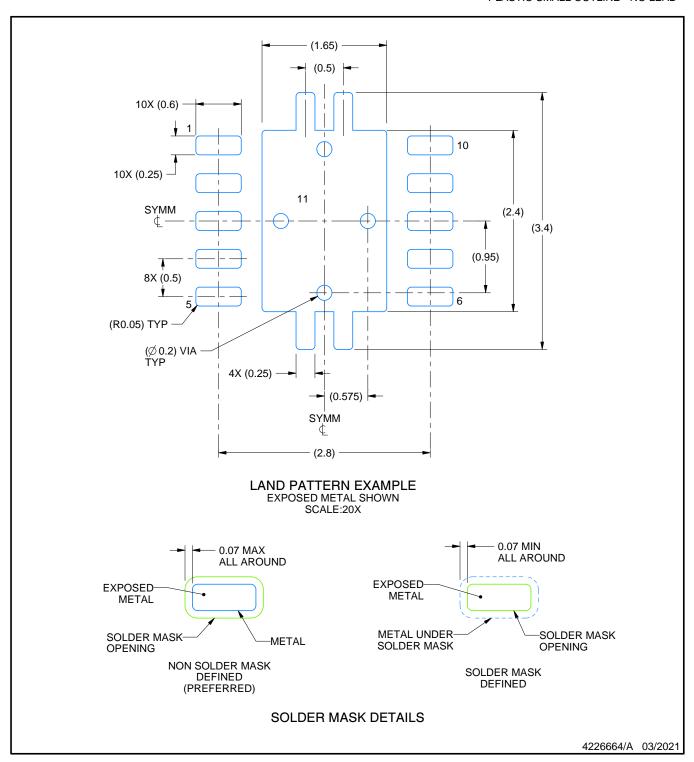

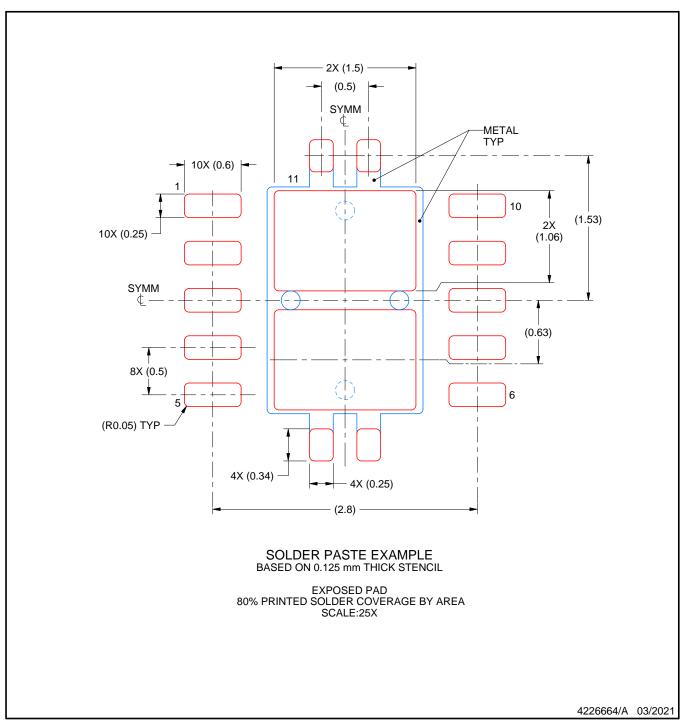

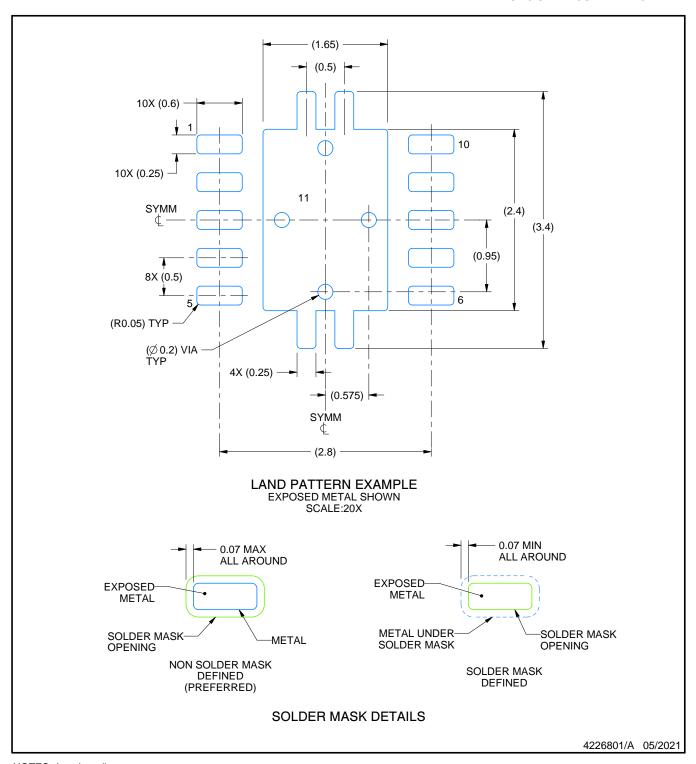

# **6 Pin Configuration and Functions**

图 6-1. DSX Package 10-Pin WSON Top View

表 6-1. Pin Functions

|                             | PIN                   | TYPE <sup>(1)</sup>                               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|-----------------------------|-----------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NO.                         | NAME                  | ITPE                                              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 1                           | SW                    | Р                                                 | Regulator switch node. Connect to output inductor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 2                           | воот                  | diode charges the capacitor while SW node is low. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 3                           | VCC                   | Р                                                 | Internal 3-V regulator output. Used as supply to internal control circuits. Connect a high quality 1.0- $\mu$ F capacitor from this pin to AGND for fixed versions or to GND for adjustable versions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 4                           | FB (Fixed Versions)   | I/P                                               | Fixed version only, this pin serves as feedback for output voltage as well as power source for VCC's regulator. Connect to output node. Place 10-nF bypass capacitor immediately adjacent to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 4                           | FB (ADJ<br>Version)   | I                                                 | ADJ version only, this pin serves as feedback for output voltage only. Connect to output through a voltage divider which determines output voltage set point.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 5                           | AGND (Fixed Version)  | G                                                 | Fixed versions only, this is the ground to which input signals and FB are compared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 3                           | BIAS (ADJ<br>Version) | Р                                                 | Power source for VCC's regulator. Connect to output node. Place 10-nF bypass capacitor immediately adjacent to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 6                           | RESET                 | 0                                                 | Open drain reset output. Connect to suitable voltage supply through a current limiting pull up resistor. High = regulator OK, Low = regulator fault. Will go low when EN = low. See Detailed Description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 7                           | EN                    | I                                                 | Enable input to regulator. High = on, Low = off. Can be connected to Vin. Do not float.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 8                           | VIN                   | I                                                 | Input supply to regulator. Connect input bypass capacitors directly between this pin and GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 9                           | SYNC/MODE             | I                                                 | This is a multifunction mode control input which is tolerant of voltages up to input voltage. With a valid synchronization signal at this pin, the device will switch in forced PWM mode at the external clock frequency and synchronize with it at the rising edge of the clock. See the <i>Electrical Characteristics</i> for synchronization signal specifications. With this input tied high, the device will switch at the internal clock frequency in forced PWM mode. With this input tied low, the device will switch at the internal clock frequency in AUTO mode with diode emulation at light load. Spread spectrum is disabled if there is a valid synchronization signal. Do not float. |  |  |  |

| 10                          | GND                   | G                                                 | Bypass to VIN immediately adjacent to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| DAP<br>(EXPO<br>SED<br>PAD) | Thermal,<br>GND       | Thermal                                           | Connect to ground - The sole function of the DAP interface is the thermal improvement of the device, a direct thermal connection to a ground plane is required. The DAP is not meant as an electrical interconnect. Electrical characteristics are not ensured.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

(1) G = Ground, I = Input, O = Output, P = Power

# 7 Specifications

# 7.1 Absolute Maximum Ratings

Over the recommended operating junction temperature range of - 40°C to 150°C (unless otherwise noted)

|                                                                          | MIN   | MAX     | UNIT |

|--------------------------------------------------------------------------|-------|---------|------|

| VIN to GND <sup>(1)</sup>                                                | - 0.3 | 42      |      |

| SW to GND <sup>(2)</sup>                                                 | - 0.3 | VIN+0.3 |      |

| BOOT to SW                                                               | - 0.3 | 3.6     |      |

| EN to GND (1)                                                            | - 0.3 | 42      | V    |

| BIAS to GND: LM53600-Q1/LM53601-Q1-ADJ                                   | - 0.3 | 16      | V    |

| FB to GND : LM53600-Q1/LM53601-Q1 - 3.3 V, LM53600-Q1/LM53601-Q1 - 5.0 V | - 0.3 | 16      |      |

| FB to GND : LM53600-Q1/LM53601-Q1-ADJ                                    | - 0.3 | 5.5     | -    |

| RESET to GND                                                             | - 0.3 | 8       |      |

| RESET sink current <sup>(3)</sup>                                        |       | 8       | mA   |

| SYNC/MODE to GND <sup>(1)</sup>                                          | - 0.3 | 42      |      |

| VCC                                                                      | - 0.3 | 3.6     | V    |

| GND <sup>(4)</sup> to AGND (Fixed version only)                          | - 1   | 2       |      |

| Storage temperature, T <sub>stg</sub>                                    | - 40  | 150     | °C   |

- (1) A maximum of 42 V can be sustained at this pin for a duration of  $\leq$ 100 ms at a duty cycle of  $\leq$ 1%.

- (2) A voltage of 2-V below GND and 2-V above VIN can appear on this pin for ≤200 ns with a duty cycle of ≤ 0.01%.

- (3) Do not exceed pin's voltage rating.

- (4) This specification applies to voltage durations of 1 µs or less. The maximum D.C. voltage should not exceed ±0.3 V.

# 7.2 ESD Ratings

|                    |                         |                                                         |                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------|-------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge |                                                         | VIN, SW, CBOOT                      | ±2000 |      |

|                    |                         | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> | EN, BIAS, RESET, FB, SYNC, PWM, VCC | ±2000 | V    |

|                    |                         | Charged device model (CDM), per AEC Q100-011            | Other pins                          | ±750  |      |

|                    |                         | Charged device moder (CDIVI), per ALC Q100-011          | Corner pins (1, 5, 6, and 10)       | ±750  |      |

(1) AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification

#### 7.3 Recommended Operating Conditions

Over the recommended operating junction temperature range of - 40°C to 150°C (unless otherwise noted)

| 1 0,                                                                          | 3                            | ,    | ,       |      |

|-------------------------------------------------------------------------------|------------------------------|------|---------|------|

|                                                                               |                              | MIN  | NOM MAX | UNIT |

| Input voltage range after startup <sup>(1)</sup>                              |                              | 3.8  | 36      | V    |

| Output voltage range                                                          | 5 V <sup>(2)</sup>           | 0    | 5.5     | V    |

| Output voltage range                                                          | 3.3 V <sup>(2)</sup>         | 0    | 3.63    | V    |

| Output adjustment range <sup>(3)</sup> for LM53600-Q1-ADJ <sup>(2)</sup> , LM | 153601-Q1-ADJ <sup>(2)</sup> | 3.3  | 6       | V    |

| Lood current range                                                            | LM53600-Q1                   | 0    | 650     | mA   |

| Load current range                                                            | LM53601-Q1                   | 0    | 1000    | ША   |

| Operating junction temperature <sup>(4)</sup>                                 |                              | - 40 | 150     | °C   |

- (1) An extended input voltage range to 3.55 V is possible; see # 7.6. See input UVLO in # 7.5 for startup conditions.

- (2) Output voltage should not be allowed to fall below 0 V during normal operation.

- 3) The LM53600-Q1 and LM53601-Q1 devices can operate outside of the listed range output voltage range. For output voltage outside of the listed range, contact Texas Instruments concerning alternate application circuit BOM and additional operational limitations such as higher I<sub>Q</sub>.

- (4) High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

### 7.4 Thermal Information

|                        | <i>w</i>                                     | LM53600-Q1,<br>LM53601-Q1 |      |

|------------------------|----------------------------------------------|---------------------------|------|

|                        | THERMAL METRIC(1)                            | DSX (WSON)                | UNIT |

|                        |                                              | 10 PINS                   |      |

| R <sub>θ JA</sub>      | Junction -to-ambient thermal resistance      | 46.2                      | °C/W |

| R <sub>0</sub> JC      | Junction -to-case (top) thermal resistance   | 31.5                      | °C/W |

| R <sub>0</sub> JB      | Junction -to-board thermal resistance        | 20.9                      | °C/W |

| Ф ЈТ                   | Junction- to-top characterization parameter  | 0.3                       | °C/W |

| Ф ЈВ                   | Junction-to-board characterization parameter | 21.0                      | °C/W |

| R <sub>θ</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 4.1                       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report (SPRA953).

## 7.5 Electrical Characteristics

Limits apply to the recommended operating junction temperature range of  $-40^{\circ}\text{C}$  to  $150^{\circ}\text{C}$ , unless otherwise noted. Minimum and maximum limits are ensured through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_j = 25^{\circ}\text{C}$ , and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{in} = 13.5 \text{ V}$ .

|                            | PARAMETER                                                                              | TEST CONDITIONS                                                                                       | MIN    | TYP    | MAX  | UNIT |

|----------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------|--------|------|------|

| $V_{FB}$                   | Initial output voltage accuracy                                                        | V <sub>in</sub> = 3.8 V to 36 V T <sub>j</sub> =25°C, Open<br>Loop                                    | - 1%   |        | 1%   |      |

|                            |                                                                                        | V <sub>in</sub> = 3.8 V to 36 V, Open Loop                                                            | - 1.5% |        | 1.5% |      |

| IQ                         | Operating quiescent current;                                                           | V <sub>in</sub> = 13.5 V, Not switching V <sub>bias</sub> = 5 V                                       |        | 6.5    |      |      |

|                            | measured at V <sub>IN</sub> pin                                                        | $V_{in}$ = 13.5 V, Not switching $V_{bias}$ = 5 V, $T_j$ = 85°C                                       |        |        | 16   | μA   |

| I <sub>B</sub>             | Bias current into BIAS pin for<br>adjustable versions and FB pin<br>for fixed versions | V <sub>in</sub> = 13.5 V, Not switching V <sub>bias</sub> = 5 V, Mode = 0 V                           |        | 46     | 80   | μ, , |

| I <sub>SD</sub>            | Shutdown quiescent current;                                                            | EN = 0, VIN = 13.5 V T <sub>j</sub> = 25°C                                                            |        | 1.8    |      |      |

|                            | measured at V <sub>IN</sub> pin                                                        | EN = 0, VIN = 13.5 V T <sub>j</sub> = 85°C                                                            |        |        | 3    | μA   |

| $V_{\text{in\_UVLO}}$      | Minimum input voltage to operate                                                       | Rising                                                                                                | 3.2    | 3.6    | 3.75 | V    |

| V <sub>in_UVLO _hyst</sub> | Minimum input voltage hysteresis                                                       | Hysteresis                                                                                            | 0.2    | 0.3    | 0.35 | V    |

| V <sub>reset_OV</sub>      | RESET upper threshold voltage                                                          | Rising, % of Vout                                                                                     | 105%   | 106.5% | 110% |      |

| V <sub>reset_UV</sub>      | RESET lower threshold voltage                                                          | Falling, % Vout                                                                                       | 92%    | 94%    | 97%  |      |

| V <sub>reset_guard</sub>   | Magnitude of RESET lower threshold difference from steady state output voltage         | Steady state output voltage and RESET threshold read at the same T <sub>J</sub> , and V <sub>IN</sub> | 3.9%   |        |      |      |

| V <sub>reset_hyst</sub>    | RESET hysteresis as a<br>percent of output voltage set<br>point                        |                                                                                                       |        | 1%     |      |      |

| V <sub>reset_valid</sub>   | Minimum input voltage for proper RESET function                                        | 50 $\mu$ A pull-up to RESET pin, EN = 0 V, T <sub>j</sub> = 25°C                                      |        |        | 1.5  | V    |

|                            |                                                                                        | 50 μA pull-up to RESET pin, Vin = 1.5 V, EN = 0 V, Τ <sub>j</sub> = 25°C                              |        |        | 0.4  |      |

| V <sub>OL</sub>            | Low level RESET function output voltage                                                | 0.5mA pull-up to RESET pin, Vin = 13.5 V, EN = 0 V                                                    |        |        | 0.4  | V    |

|                            |                                                                                        | 1mA pull-up to RESET pin, Vin = 13.5 V, EN = 3.3 V                                                    |        |        | 0.4  |      |

www.ti.com.cn

Limits apply to the recommended operating junction temperature range of -40°C to 150°C, unless otherwise noted. Minimum and maximum limits are ensured through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_j = 25$ °C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{in} = 13.5$  V.

|                           | PARAMETER                                                  | TEST CONDITIONS                                                                                             | MIN   | TYP    | MAX  | UNIT |

|---------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------|--------|------|------|

|                           |                                                            | V <sub>IN</sub> = 13.5 V, Center frequency with spread spectrum, PWM operation                              | 1.89  | 2.1    | 2.4  |      |

| -                         | Cuitabin a far average                                     | V <sub>IN</sub> = 13.5 V, Without spread spectrum, PWM operation                                            | 1.89  | 2.1    | 2.4  | MHz  |

| F <sub>sw</sub>           | Switching frequency                                        | V <sub>IN</sub> = 36 V, 3.3-V fixed output device<br>and adjustable devices regardless of<br>output voltage |       | 1.0    |      |      |

|                           |                                                            | V <sub>IN</sub> = 36 V, 5-V fixed output device                                                             |       | 1.5    |      |      |

| F <sub>SYNC</sub>         | Sync frequency range                                       | Output setting + 1 V < V <sub>IN</sub> < 18 V                                                               | 1.9   | 2.1    | 2.3  | MHz  |

| D <sub>SYNC</sub>         | Sync input duty cycle range                                | High state input < 5.5 V and > 2.3 V                                                                        | 25%   |        | 75%  |      |

|                           |                                                            | SYNC/MODE input high (MODE=FPWM)                                                                            | 1.5   |        |      |      |

| V <sub>SYNC/MODE</sub>    | SYNC/MODE input threshold voltage                          | SYNC/MODE input low (MODE = AUTO with diode emulation)                                                      |       |        | 0.4  | V    |

|                           |                                                            | SYNC/MODE input hysteresis                                                                                  | 0.185 |        | 1    |      |

| F <sub>SSS</sub>          | Frequency span of spread spectrum operation <sup>(2)</sup> |                                                                                                             |       | ±4%    |      |      |

| F <sub>PSS</sub>          | Spread spectrum pattern frequency <sup>(2)</sup>           |                                                                                                             |       |        | 30   | Hz   |

| loweren                   | SYNC/MODE leakage current                                  | Vin = 13.5 V, V <sub>SYNC/MODE</sub> = 3.3 V                                                                |       | 1      |      | μΑ   |

| SYNC/MODE                 |                                                            | V <sub>IN</sub> = V <sub>SYNC/MODE</sub> = 13.5 V                                                           |       | 5      |      |      |

|                           | Mode change transition time (2)                            | To FPWM Mode 20 mA load, V <sub>IN</sub> = 13.5 V                                                           |       | 100    |      | μs   |

| t <sub>MODE</sub>         |                                                            | To AUTO Mode 20-mA load, V <sub>IN</sub> = 13.5 V                                                           |       | 60     |      |      |

|                           | High side switch current limit                             | LM53600-Q1 Duty cycle approaches 0%                                                                         | 1.0   | 1.35   | 1.65 | А    |

| I <sub>L_HS</sub>         |                                                            | LM53601-Q1 Duty cycle approaches 0%                                                                         | 1.5   | 1.83   | 2.1  |      |

|                           |                                                            | LM53600-Q1                                                                                                  | 0.65  | 0.78   | 0.93 |      |

| $I_{L_LS}$                | Low side switch current limit                              | LM53601-Q1                                                                                                  | 1.0   | 1.2    | 1.43 | Α    |

| I <sub>L_ZC</sub>         | Zero-cross current limit<br>MODE/SYNC = Low                |                                                                                                             |       | - 0.01 |      | Α    |

|                           | Negative current limit MODE/                               | LM53600-Q1                                                                                                  |       | - 0.7  |      | ^    |

| L_NEG                     | SYNC = High                                                | LM53601-Q1                                                                                                  |       | - 0.7  |      | Α    |

| D                         | Davier aviitale au maaiatamaa                              | High side MOSFET Rdson                                                                                      |       | 220    |      | mΩ   |

| R <sub>dson</sub>         | Power switch on-resistance                                 | Low side MOSFET Rdson                                                                                       |       | 200    |      |      |

| V <sub>EN</sub>           | Enable input threshold voltage - rising                    | Enable rising                                                                                               | 1.7   | -      | 2.0  | V    |

| V <sub>EN_HYST</sub>      | Enable threshold hysteresis                                |                                                                                                             | 0.40  | -      | 0.55 | V    |

| V <sub>EN_WAKE</sub>      | Enable Wake-up threshold                                   |                                                                                                             | 0.4   |        |      | V    |

| EN                        | Enable pin input current                                   | V <sub>IN</sub> = V <sub>EN</sub> = 13.5 V                                                                  |       | 2.7    |      | μA   |

| N/                        | Internal Vcc voltage                                       | V <sub>IN</sub> = 13.5 V, V <sub>bias</sub> = 0 V                                                           |       | 3.05   |      | V    |

| V <sub>cc</sub>           |                                                            | V <sub>IN</sub> = 13.5 V, V <sub>bias</sub> = 3.3 V                                                         |       | 3.15   |      | v    |

| V <sub>cc_UVLO</sub>      | Internal Vcc input under voltage lock-out                  | VCC rising                                                                                                  |       | 2.7    |      | V    |

| V <sub>cc_UVLO_hyst</sub> | Input under voltage lock-out hysteresis                    | Hysteresis below V <sub>cc_uvlo</sub>                                                                       |       | 190    |      | mV   |

Limits apply to the recommended operating junction temperature range of  $-40^{\circ}$ C to  $150^{\circ}$ C, unless otherwise noted. Minimum and maximum limits are ensured through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_j = 25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{in} = 13.5 \text{ V}$ .

|                      | PARAMETER                                         | TEST CONDITIONS              | MIN   | TYP | MAX   | UNIT |

|----------------------|---------------------------------------------------|------------------------------|-------|-----|-------|------|

| I <sub>FB</sub>      | Input current from FB to AGND                     | LM53600-Q1-ADJ, FB = 1 V     |       | 20  |       | nA   |

| $V_{ref}$            | Reference voltage for ADJ                         | T <sub>j</sub> = 25°C        | 0.993 | 1   | 1.007 | V    |

| V ref                | option only                                       |                              | 0.985 | 1   |       | V    |

| R <sub>RESET</sub>   | Rdson of RESET output                             |                              |       | 50  | 120   | Ω    |

| T <sub>SD</sub>      | Thermal shutdown rising threshold <sup>(2)</sup>  |                              | 151   | 167 | 185   |      |

| T <sub>SDF</sub>     | Thermal shutdown falling threshold <sup>(2)</sup> |                              | 140   | 157 |       | °C   |

| T <sub>SD_hyst</sub> | Thermal shutdown hysteresis <sup>(2)</sup>        |                              |       | 10  |       |      |

| D                    |                                                   | Fsw = 2.1 MHz                |       | 76% |       |      |

| D <sub>max</sub>     | Maximum switch duty cycle <sup>(2)</sup>          | While in frequency fold back | 96%   |     |       |      |

- (1) High side current limit is a function of duty factor. Current limit value is highest at small duty factor and less at higher duty factors.

- (2) Ensured by design, statistical analysis and production testing of correlated parameters; not tested in production.

# 7.6 System Characteristics

The following specifications are ensured by design provided that the component values in the typical application circuit are used. These parameters are not ensured by production testing. Limits apply to the recommended operating junction temperature range of  $-40^{\circ}$ C to  $150^{\circ}$ C, unless otherwise noted. Minimum and Maximum limits are ensured through test, design or statistical correlation. Typical values represent the most likely parametric norm at Tj =  $25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply: Vin = 13.5 V.

|                                            | PARAMETER                                                                                               | TEST CONDITIONS                                                                                                    | MIN  | TYP  | MAX   | UNIT |  |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------|------|-------|------|--|

| V <sub>in_min</sub>                        | Minimum input voltage for full functionality at 500-mA load, after start-up                             | V <sub>OUT</sub> = 3.3 V                                                                                           |      |      | 3.55  | ٧    |  |

|                                            | Minimum input voltage for full functionality at 100% of max rated load, after start-up                  | V <sub>OUT</sub> = 3.3 V                                                                                           |      |      | 3.8   | V    |  |

| V                                          | Output voltage for 3.3-V option                                                                         | V <sub>IN</sub> = 4.0 V to 36 V, I <sub>OUT</sub> = Maximum recommended load current                               | 3.23 | 3.3  | 3.37  | , V  |  |

| $V_{IN} = 3.8 \text{ V to } 36 \text{ V},$ | V <sub>IN</sub> = 3.8 V to 36 V, I <sub>OUT</sub> =100 μA to 100 mA, typical value in Auto Mode         | 3.23                                                                                                               | 3.33 | 3.39 | V     |      |  |

| V Outroth valle are for 5 V anti-cr        |                                                                                                         | V <sub>IN</sub> = 5.8 V to 36 V, I <sub>OUT</sub> = Maximum recommended load current                               | 4.9  | 5    | 5.1   | V    |  |

| $V_{out\_5V}$                              | Output voltage for 5-V option                                                                           | V <sub>IN</sub> = 5.5 V to 36 V, I <sub>OUT</sub> =100 μA to 100 mA, typical value in Auto Mode                    | 4.9  | 5.05 | 5.125 | V    |  |

| V                                          | Output voltage ADJ option                                                                               | V <sub>IN</sub> = V <sub>OUT</sub> + 0.6 V to 36 V, I <sub>OUT</sub> = 100 mA, FPWM mode                           | - 2% |      | +2%   |      |  |

| $V_{out\_ADJ}$                             | Output voitage AD3 option                                                                               | V <sub>IN</sub> = V <sub>OUT</sub> + 0.6 V to 36 V, I <sub>OUT</sub> =100<br>μA to 100 mA, Auto mode               | - 2% |      | +2.5% |      |  |

|                                            | Load regulation for ADJ option <sup>(1)</sup>                                                           | V <sub>IN</sub> = V <sub>OUT</sub> + 1 V to 36 V, I <sub>OUT</sub> = 0 A to 1 A, T <sub>J</sub> = 125°C, FPWM mode |      | - 1% |       |      |  |

| I <sub>Q_VIN</sub> (2)                     | Input current to V <sub>IN</sub> node of DC/DC utilizing the LM53600-Q1/LM53601-                        | V <sub>IN</sub> = 13.5 V, V <sub>OUT</sub> = 3.3 V, I <sub>OUT</sub> = 0<br>A                                      |      | 23   |       | μA   |  |

|                                            | Q1                                                                                                      | V <sub>IN</sub> = 13.5 V, V <sub>OUT</sub> = 5 V, I <sub>OUT</sub> = 0 A                                           |      | 30   |       |      |  |

| V <sub>DROP1</sub>                         | Minimum input to output voltage differential to maintain regulation accuracy, without inductor DCR drop | V <sub>OUT</sub> =3.3 V, I <sub>OUT</sub> =1000 mA, +2/ -<br>3% output accuracy                                    |      |      | 0.6   | ٧    |  |

The following specifications are ensured by design provided that the component values in the typical application circuit are used. These parameters are not ensured by production testing. Limits apply to the recommended operating junction temperature range of  $-40^{\circ}$ C to  $150^{\circ}$ C, unless otherwise noted. Minimum and Maximum limits are ensured through test, design or statistical correlation. Typical values represent the most likely parametric norm at Tj =  $25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply: Vin = 13.5 V.

|                    | PARAMETER                                                                                                       | TEST CONDITIONS                                                                                         | MIN | TYP | MAX | UNIT |

|--------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>DROP2</sub> | Minimum input to output voltage differential to maintain $F_{SW} \geqslant 1.85$ MHz, without inductor DCR drop | V <sub>OUT</sub> = 3.3 V, I <sub>OUT</sub> =1000 mA, F <sub>SW</sub> = 1.85 MHz, 2% regulation accuracy |     |     | 2.0 | V    |

|                    | V <sub>IN</sub> = 13.5 V, V <sub>OUT</sub> = 5.0 V, I <sub>OUT</sub> = 1<br>A                                   |                                                                                                         | 85% |     |     |      |

| Efficiency         | Efficiency Typical Efficiency without inductor loss                                                             | V <sub>IN</sub> = 13.5 V, V <sub>OUT</sub> = 3.3 V, I <sub>OUT</sub> = 1<br>A                           |     | 80% |     |      |

| Linciency          |                                                                                                                 | V <sub>IN</sub> = 13.5 V, V <sub>OUT</sub> = 5.0 V, I <sub>OUT</sub> = 0.65 A                           |     | 86% |     |      |

|                    |                                                                                                                 | V <sub>IN</sub> = 13.5 V, V <sub>OUT</sub> = 3.3 V, I <sub>OUT</sub> = 0.65 A                           |     | 83% |     |      |

- (1) 125°C is worst case temperature for load regulation. Layout is critical since adjustable option does not have an AGND terminal.

- (2) See # 8.3.7 in # 8 for the meaning of this specification and how it can be calculated.

### 7.7 Timing Requirements

Limits apply to the recommended operating junction temperature range of  $-40^{\circ}$ C to  $150^{\circ}$ C, unless otherwise noted. Minimum and Maximum limits are ensured through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_j = 25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{in} = 13.5 \text{ V}$ .

|                           |                                                |                                                                                | MIN | NOM | MAX  | UNIT |

|---------------------------|------------------------------------------------|--------------------------------------------------------------------------------|-----|-----|------|------|

| t <sub>on</sub>           | Minimum switch on time <sup>(1)</sup>          | V <sub>IN</sub> = 18 V, I <sub>OUT</sub> = 500 mA                              |     | 50  | 80.5 |      |

| t <sub>off</sub>          | Minimum switch off time <sup>(1)</sup>         | I <sub>OUT</sub> = 500 mA                                                      |     | 90  | 125  | ns   |

| t <sub>reset_act</sub>    | Delay time to RESET high signal                |                                                                                | 4   | 6   | 8    | ms   |

| t <sub>reset_filter</sub> | Glitch filter time constant for RESET function |                                                                                |     | 24  |      | μs   |

| t <sub>SS</sub>           | Soft-start time                                | Time from first SW node pulse to Vref at 90%, V <sub>IN</sub> ≥4.2 V           | 1.3 | 3   | 4.5  | ms   |

| t <sub>EN</sub>           | Turn-on delay <sup>(2)</sup>                   | Time from EN high until first SW node pulse. $V_{IN}$ = 13.5, Cvcc = 1 $\mu$ F |     | 0.7 |      | ms   |

| t <sub>W</sub>            | Short circuit wait time (Hiccup time)          |                                                                                |     | 4.5 |      | ms   |

- (1) See #8

- (2) Ensured by design, statistical analysis and production testing of correlated parameters; not tested in production.

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

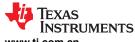

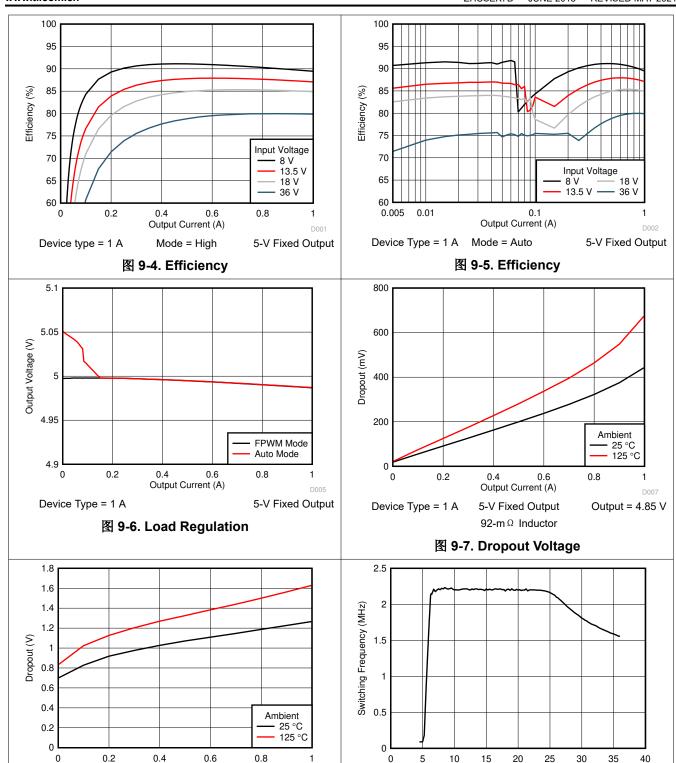

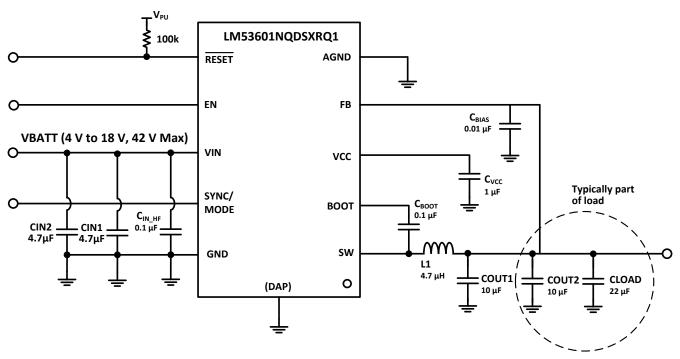

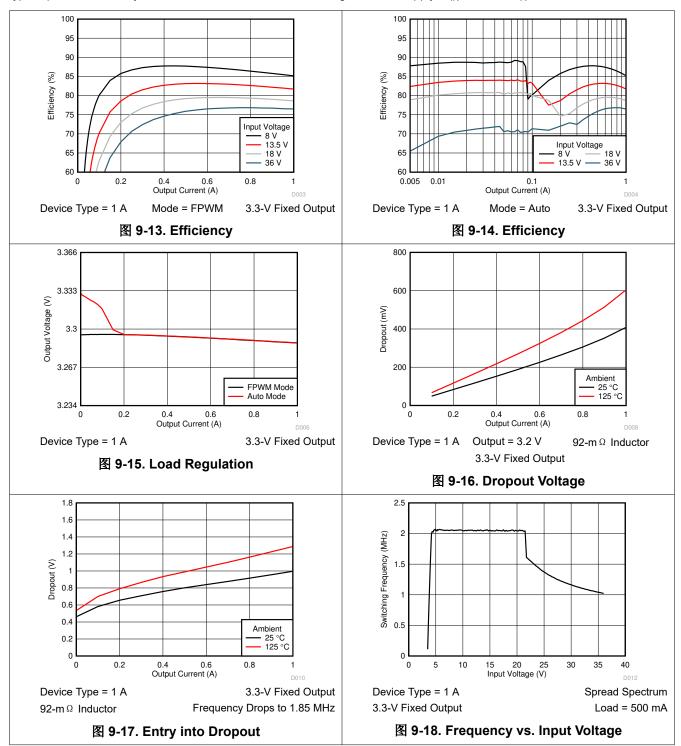

# 7.8 Typical Characteristics

$V_{IN}$  = 13.5 V,  $T_A$  = 25°C (unless otherwise noted). Specified temperatures are ambient.

# **8 Detailed Description**

### 8.1 Overview

The LM53600-Q1 and LM53601-Q1 devices are wide-input voltage range, low quiescent current, high-performance regulators with internal compensation designed specifically for the automotive market. These devices are designed to minimize end product cost and size while operating in demanding automotive environments. Normal operating frequency is 2.1 MHz allowing the use of small passive components. State of the art current limit allows the use of inductors that are smaller than those typically used in a 650mA or 1000mA regulator. 2.1MHz is above the AM band, allowing significant saving in input filtering. This part has a low unloaded current consumption eliminating the need for an external back-up LDO. The low shutdown current and high maximum operating voltage of the LM53600-Q1 and LM53601-Q1 devices also allows the elimination of an external load switch. To further reduce system cost, an advanced reset output is provided, which can often eliminate the use of an external reset or supervisory device.

The LM53600-Q1 and LM53601-Q1 devices are AEC Q1 qualified, and also have electrical characteristics ensured up to a maximum junction temperature of 150°C.

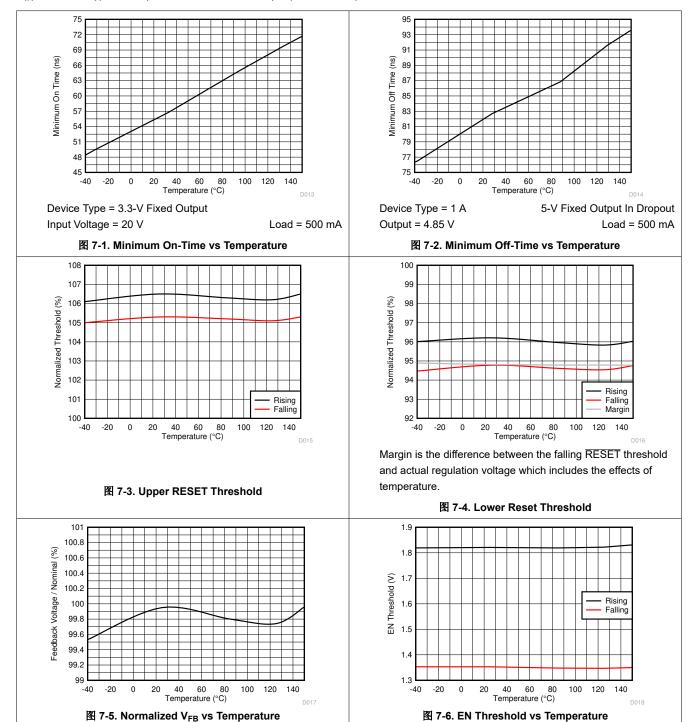

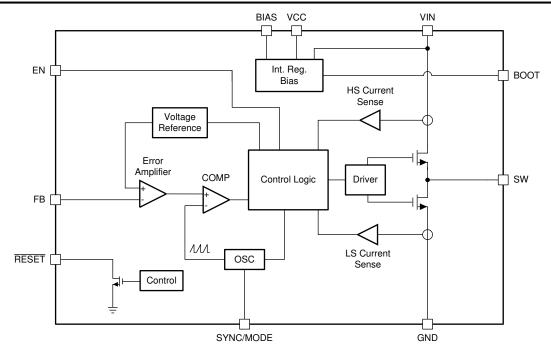

### 8.2 Functional Block Diagram

图 8-1. Fixed Versions

图 8-2. Adjustable Versions

### 8.3 Feature Description

#### 8.3.1 Control Scheme

The control scheme of the LM53600-Q1 and LM53601-Q1 devices allows this part to operate under a wide range of conditions with a low number of external components. Peak current mode control allows a wide range of input voltages and output capacitance values, while maintaining a constant switching frequency. Stable operation is maintained while output capacitance is changed during operation as well. This allows use in systems that require high performance during load transients and which have load switches which remove loads as system operating state changes. Short minimum on- and off-times ensure constant frequency regulation over a wide range of conversion ratios. These on- and off- times allow for a duty factor window of 13% to 77% at 2.1-MHz switching frequency.

This architecture uses frequency foldback in order to achieve low dropout voltage maintaining output regulation as the input voltage falls close to output voltage. The frequency foldback is smooth and continuous, and activated as off-time approaches its minimum. Under these conditions, the LM53600-Q1 and LM53601-Q1 devices operate much like a constant off-time converter allowing maximum duty cycle to reach 97%, which allows output voltage regulation with 600-mV dropout.

If input voltage exceeds approximately 21 V, frequency is reduced smoothly as a function of input voltage. This frequency reduction allows output voltage regulation and current mode control to operate with duty factor below 13%. Since current mode control continues at high input voltage insensitivity to output capacitance is maintained. This form of fold back will not be active if input voltage is below 18 V, insuring constant frequency operation over normal automotive operating conditions.

High input voltage foldback has two settings; see  $F_{SW}$  under 36-V input conditions for detail. Since adjustable output voltage versions fold back under high input voltage conditions as though output voltage were 3.3 V, larger inductance and output capacitance is required if an adjustable device is used with output voltage above 4.2 V. If a 4.7- $\mu$ H inductor is used in system with greater 4.2-V output using an adjustable device, the converter remains stable but may not achieve full output current when operating at high input voltages, such as 36 V, due to excessive inductor current ripple.

As load current is reduced, the LM53600-Q1 and LM53601-Q1 devices transition to light load mode if SYNC/MODE is low. In this mode, diode emulation is used to reduce RMS inductor current and switching frequency is reduced. Also, fixed voltage versions do not need a voltage divider connected to FB saving additional power. As

a result, only 23  $\mu$ A (typical, while converting 13.5 V to 3.3 V) is consumed to regulate output voltage if output is unloaded. Average output voltage increases slightly while lightly loaded.

#### 8.3.2 Soft-Start Function

Soft-start time is fixed internally at about 3.0 ms. Soft-start is achieved by ramping the internal reference. The LM53600-Q1 and LM53601-Q1 devices operate correctly even if there is a voltage present on output before activation of the LM53600-Q1 or LM53601-Q1.

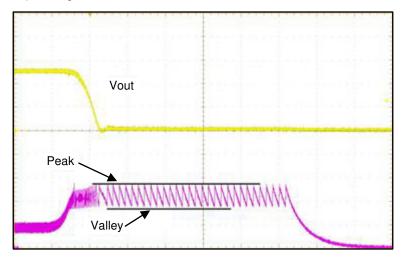

#### 8.3.3 Current Limit

The LM53600-Q1 and LM53601-Q1 devices use two current limits which allow the use of smaller inductors than systems utilizing a single current limit. A coarse high side or peak current limit is provided to protect against faults and saturated inductors. High side current limit limits the duration of high sides FET's on period during a given clock cycle. A precision valley current limit prevents excessive average output current from the Buck converter of the LM53600-Q1 and LM53601-Q1 devices. A new switching cycle is not initiated until inductor current drops below the valley current limit. This scheme allows use of inductors with saturation current rated less than twice the rated operating current of the LM53600-Q1 or LM53601-Q1.

图 8-3. Current Limit Operation

8-3 shows the response of the LM53600-Q1 or LM53601-Q1 device to a short circuit: Peak current limit prevents excessive peak current while valley current limit prevents excessive average inductor current. After a small number of cycles, hiccup mode is activated.

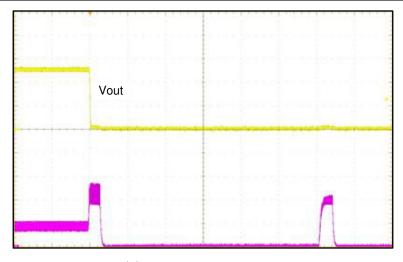

# 8.3.4 Hiccup Mode

In order to prevent excessive heating and power consumption under sustained short circuit conditions, a hiccup mode is included. If an over current condition is maintained, the LM53600-Q1 or LM53601-Q1 device shuts off its output and waits for  $t_W$  (approximately 4.5 ms), after which the LM53600-Q1 or LM53601-Q1 restarts operation beginning by activating soft start.

图 8-4. Hiccup Operation

№ 8-4 shows hiccup mode operation: The switch node of the LM53600-Q1 LM53601-Q1 is high impedance after a short circuit or over current persists for a short duration. Periodically, the LM53600-Q1 or LM53601-Q1 attempts to restart. If the short has been removed before one of these restart attempts, the LM53600-Q1 or LM53601-Q1 operates normally.

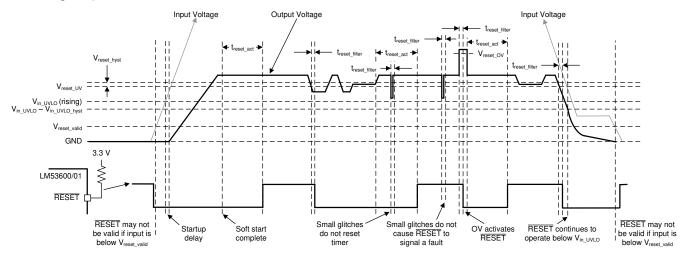

#### 8.3.5 RESET Function

While the reset function of the LM53600-Q1 and LM53601-Q1 devices resembles a standard power good function, its functionality is designed to replace a discrete reset IC, reducing BOM cost. There are three major differences between the reset function and the normal power good function seen in most regulators:

- A delay has been added for release of reset. See waveforms below.

- RESET output signals a fault (pulls its output to ground) while the part is disabled.

- RESET continues to operate with input voltage as low as 1.5 V. Below this input voltage, RESET output may be high impedance.

图 8-5. Reset Output Function Operation

The following table summarizes conditions that cause a fault to be flagged by  $\overline{\text{RESET}}$ . Once a fault is flagged,  $\overline{\text{RESET}}$  will not be released (become high impedance) until either there is no fault for  $t_{\text{reset\_act}}$  or VIN drops below  $V_{\text{reset}}$  valid.

Table showing conditions that cause RESET to signal a fault (pull low).

| FAULT CONDITION INITIATED                                                                                            | FAULT CONDITION ENDS (AFTER WHICH T <sub>reset_act</sub> MUST PASS BEFORE RESET OUTPUT IS RELEASED) |

|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| FB below V <sub>reset_UV</sub> for longer than t <sub>reset_filt</sub>                                               | FB above V <sub>reset_UV</sub> + V <sub>reset_hyst</sub> for longer than t <sub>reset_filt</sub>    |

| FB above V <sub>reset_OV</sub> for longer than t <sub>reset_filt</sub>                                               | FB below V <sub>reset_OV</sub> - V <sub>reset_hyst</sub> for longer than t <sub>reset_filt</sub>    |

| Junction temperature exceeds T <sub>SD</sub>                                                                         | Junction temperature falls below T <sub>SD</sub> - T <sub>SD_hyst</sub>                             |

| EN low                                                                                                               | t <sub>EN</sub> passes after EN becomes high <sup>(1)</sup>                                         |

| VIN falls below $V_{in\_UVLO}$ - $V_{in\_UVLO}_{hyst}$ or VCC pin falls below $V_{cc\_UVLO}$ - $V_{cc\_UVLO}_{hyst}$ | Voltage on V <sub>IN</sub> exceeds V <sub>in_UVLO</sub> and VCC exceed V <sub>cc_UVLO</sub>         |

(1) As an additional safety feature, RESET remains low until approximately 1ms after soft start ends even if all other conditions in this table are met and t<sub>reset act</sub> has passed. Lockout during soft start does not require t<sub>reset act</sub> to pass before RESET is released.

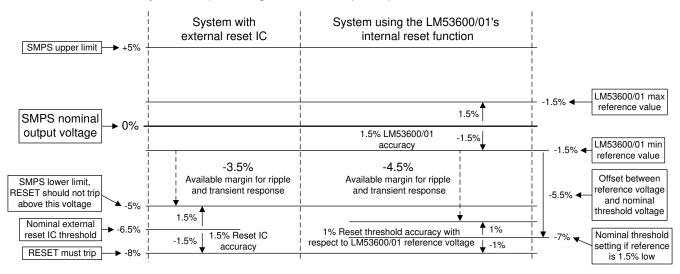

The threshold voltage for the RESET function is specified taking advantage of the availability of the LM53600-Q1 internal feedback threshold to the RESET circuit. This allows a maximum threshold of 97% of selected output voltage to be specified at the same time as 95.7% of actual operating point. The net result is a more accurate reset function while expanding the system allowance for transient response without the need for extremely accurate internal circuitry. See output voltage error stack up comparison, below.

图 8-6. Reset Threshold Voltage Stack Up

### 8.3.6 Forced PWM Operation

When constant frequency operation is more important than light load efficiency, the SYNC/MODE input of the LM53600-Q1 and LM53601-Q1 devices should be pulled high, or a valid synchronization input be provided. Once activated, this feature ensures that the switching frequency will stay above the AM frequency band, while operating between the minimum and maximum duty cycle limits. Essentially, the diode emulation feature is turned off in this mode. This means that the device will remain in CCM under light loads. Under conditions where the device must reduce the on-time or off-time below the ensured minimum to maintain regulation, the frequency will reduce to maintain the effective duty cycle required for regulation. This occurs for very high and very low input/output voltage ratios.

This feature may be activated and deactivated while the part is regulating without removing the load. This feature activates and deactivates gradually, over approximately 40 µs, preventing perturbation of output voltage. When in FPWM mode, a limited reverse current is allowed through the inductor allowing power to pass from the regulators output to its input.

Note that while FPWM is activated, larger currents pass through the inductor, if lightly loaded, than in *auto* mode. This may result in more EMI, though at a predictable frequency. Once loads are heavy enough to necessitate CCM operation, FPWM mode has no measurable effect on regulator operation.

## 8.3.7 Auto Mode Operation and IQ VIN

If SYNC/MODE is held low for a period greater than a few microseconds, the LM53600-Q1 and LM53601-Q1 devices will enable automatic power saving light load operation and diode emulation. In this mode, if peak current needed to regulate output voltage drops below a selected value, the clock of the LM53600-Q1 or LM53601-Q1 device slows to maintain regulation. The gain of this clock slowing circuit is low to maintain stability. Output voltage with no load is approximately 1% higher than with a load high enough to allow full frequency operation.

$I_{Q\_VIN}$  is the current consumed by a converter utilizing a LM53600-Q1 or LM53601-Q1 device while regulating without a load. While operating without a load, the LM53600-Q1 or LM53601-Q1 is only powering itself. The LM53600-Q1 and LM53601-Q1 device draws power from two sources, its VIN pin,  $I_Q$ , and either its FB pin for fixed versions or BIAS pin for adjustable versions,  $I_B$ . Since BIAS or FB is connected to the circuit's output, the power consumed is converted from input power with an effective efficiency,  $\eta_{eff}$ , of ~80%. Here, effective efficiency is the added input power needed when lightly loading the converter of the LM53600-Q1 and LM53601-Q1 devices is divided by the corresponding additional load. This allows unloaded current to be calculated as follows:

$$I_{Q_{VIN}} = I_{Q} + I_{EN} + (I_{B} + I_{div}) \frac{\text{Output Voltage}}{\eta_{eff} \times \text{Input Voltage}}$$

(1)

#### where

- I<sub>Q\_VIN</sub> is the current consumed by the Buck converter utilizing the LM53600-Q1 or LM53601-Q1 while unloaded.

- I<sub>O</sub> is the current drawn by the LM53600-Q1 or LM53601-Q1 from its VIN terminal. See I<sub>O</sub> in section 7.6.

- I<sub>EN</sub> is current drawn by the LM53600-Q1 or LM53601-Q1 from its EN terminal. Include this current if EN is connected to VIN. See I<sub>EN</sub> in section 7.6. Note that this current drops to a very low value if connected to a voltage less than 5 V.

- I<sub>B</sub> is bias/feedback current drawn by the LM53600-Q1 or LM53601-Q1 while the Buck converter utilizing it is unloaded. See I<sub>B</sub> in section 7.6.

- I<sub>div</sub> is the current drawn by the feedback voltage divider used to set output voltage for adjustable devices.

This current is zero for fixed output voltage devices.

- $\eta_{eff}$  is the light load efficiency of the Buck converter with  $I_{Q\_VIN}$  removed from the Buck converter's input current. 0.8 is a conservative value that can be used under normal operating conditions

Note that the EN pin consumes a few microamperes when tied to high; see  $I_{EN}$ . Add  $I_{EN}$  to  $I_{Q}$  as shown in the above equation if EN is tied to  $V_{IN}$ . If EN is tied to a voltage less than 5 V, virtually no current is consumed allowing EN to be used as a UVL once a voltage divider is added.

### 8.3.8 SYNC Operation

Often it is desirable to synchronize the operation of multiple regulators in a single system. This technique results in better defined EMI and can reduce the need for capacitance on some power rails. The LM53600-Q1 and LM53601-Q1 devices provide a SYNC/MODE input, which allows synchronization with an external clock. The LM53600-Q1/LM53601-Q1 implements an in-phase locking scheme – the rising edge of the clock signal provided to the input of the LM53600-Q1 or LM53601-Q1 device corresponds to turning on the high side device within the LM53600-Q1 or LM53601-Q1. This function is implemented using phase locking over a limited frequency range eliminating large glitches upon initial application of an external clock. The clock fed into the LM53600-Q1 or LM53601-Q1 device replaces the internal free running clock but does not affect frequency fold-back operation. Output voltage will continue to be well regulated with duty factors outside of the normal 15% through 77% range though at reduced frequency.

The device remains in FPWM mode and operates in CCM for light loads when synchronization input is provided.

#### 8.3.9 Spread Spectrum

The spread spectrum is a factory option. In order to find which parts have spread spectrum enabled, see # 5.

The purpose of the spread spectrum is to eliminate peak emissions at specific frequencies by spreading emissions across a wider range of frequencies than a part with fixed frequency operation. In most systems containing the LM53600-Q1 and LM53601-Q1 devices, low frequency conducted emissions from the first few harmonics of the switching frequency can be easily filtered. A more difficult design criterion is reduction of emissions at higher harmonics which fall in the FM band. These harmonics often couple to the environment through electric fields around the switch node. The LM53600-Q1 and LM53601-Q1 devices use a ±4% spread of frequencies which spread energy smoothly across the FM band but is small enough to limit sub-harmonic emissions below its switching frequency. Peak emissions at the part's switching frequency are only reduced by slightly less than 1 dB, while peaks in the FM band are typically reduced by more than 6dB.

The LM53600-Q1 and LM53601-Q1 devices use a cycle to cycle frequency hopping method based on a linear feedback shift register (LFSR). Intelligent pseudo random generator limits cycle to cycle frequency changes to limit output ripple. Pseudo random pattern repeats by approximately 7 Hz which is below the audio band.

The spread spectrum is only available while the clock of the LM53600-Q1 and LM53601-Q1 devices is free running at its natural frequency. Any of the following conditions overrides spread spectrum, turning it off:

- 1. An external clock is applied to the SYNC/MODE terminal.

- 2. The clock is slowed due to operation low input voltage this is operation in dropout.

- 3. The clock is slowed due to high input voltage input voltage above approximately 21 V disables spread spectrum.

- 4. The clock is slowed under light load in Auto mode this is normally not seen above 200 mA of load. In FPWM mode, spread spectrum is active even if there is no load.

#### 8.4 Device Functional Modes

#### 8.4.1 Shutdown

The LM53600-Q1 and LM53601-Q1 devices shut down most internal circuitry and both high side and low side power switches connected to its switch node under any of the following conditions:

- 1. EN is below V<sub>FN</sub>

- 2. VIN is below V<sub>in\_UVLO</sub>

- 3. Junction temperature exceeds T<sub>SD</sub>

Note that the above conditions have hysteresis. Also,  $\overline{\text{RESET}}$  remains active to a very low input voltage,  $V_{\text{reset valid}}$ .

### 8.4.2 FPWM Operation

If SYNC/MODE is above  $V_{SYNC/MODE}$  high or a valid synchronizing is applied to SYNC/MODE, constant frequency operation is maintained across load. This requires negative current be allowed in the inductor if load is light. If a large negative load is present, operation is halted by a reverse current limit,  $I_{L-NEG}$ .

# 8.4.3 Auto Mode Operation

If SYNC/MODE is below  $V_{SYNC/MODE}$  low, reverse current in the inductor is not allowed – this feature is called diode emulation. While load is heavy, operation is the same as in FPWM operation. If load is light, switching frequency is reduced saving energy and allowing regulation to be maintained. Note that while under loads which require moderate reduction of frequency, pulses often are seen if small groups, often called burst mode operation, which can increase output ripple. Under this condition, output ripple can be reduced by increasing output capacitance.

# 9 Applications and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

# 9.1 Application Information

The LM53600-Q1 and LM53601-Q1 are step-down DC - DC converters, typically used to convert a higher DC voltage to a lower DC voltage with a maximum output current of either 1 A or 650 mA. The following design procedure can be used to select components for the LM53600-Q1 or LM53601-Q1. Alternately, the WEBENCH® Design Tool may be used to generate a complete design. This tool utilizes an iterative design procedure and has access to a comprehensive database of components. This allows the tool to create an optimized design and allows the user to experiment with various design options.

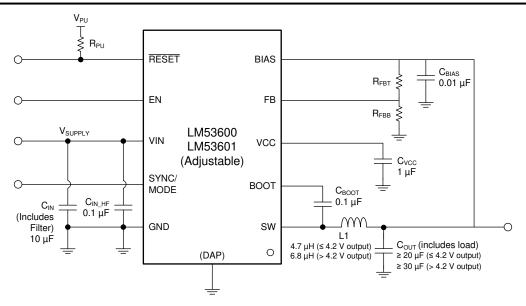

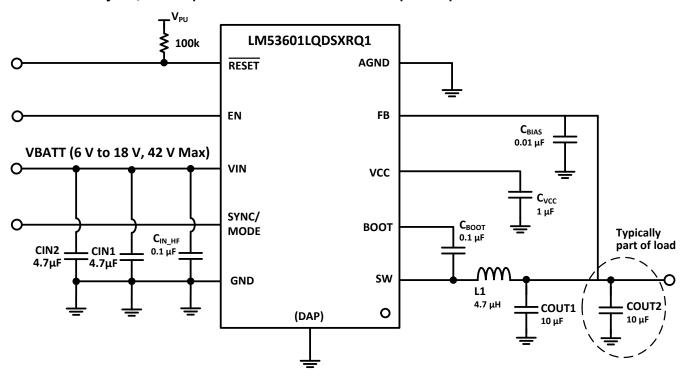

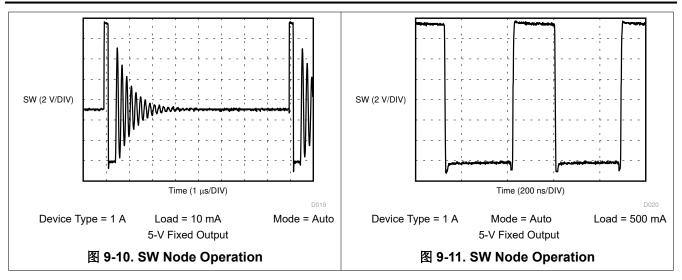

图 9-1 shows the minimum required application circuit for the fixed output voltage versions, while 图 9-2 shows the connections for complete processor control of the LM53601-Q1. Please refer to these figures while following the design procedures. 表 9-2 provides an example of typical design requirements.

图 9-1. Off Battery, Automotive, Fixed Output Voltage, Buck, 2.1 MHz, Spread Spectrum