# bq77908A 多节锂离子/聚合物电池精密保护器

**Not Recommended for New Designs**

## 1 特性

- 4, 5, 6, 7, 8 节串联电池保护

- 独立电池电压监控

- 适用于充电及放电控制的低侧 NMOS 场效应晶体管 (FET) 驱动器

- 与 1 mΩ 电流感测电阻器兼容

- 电源电压范围为 5.6 V 至 40 V

- 集成型 3.3 V 微功耗低压差 (LDO) 稳压器

- 低电源电流

- 正常模式: 50 μA、典型值

- 关断模式下低压差稳压器 (LDO) 关闭: 5 μA、典型值

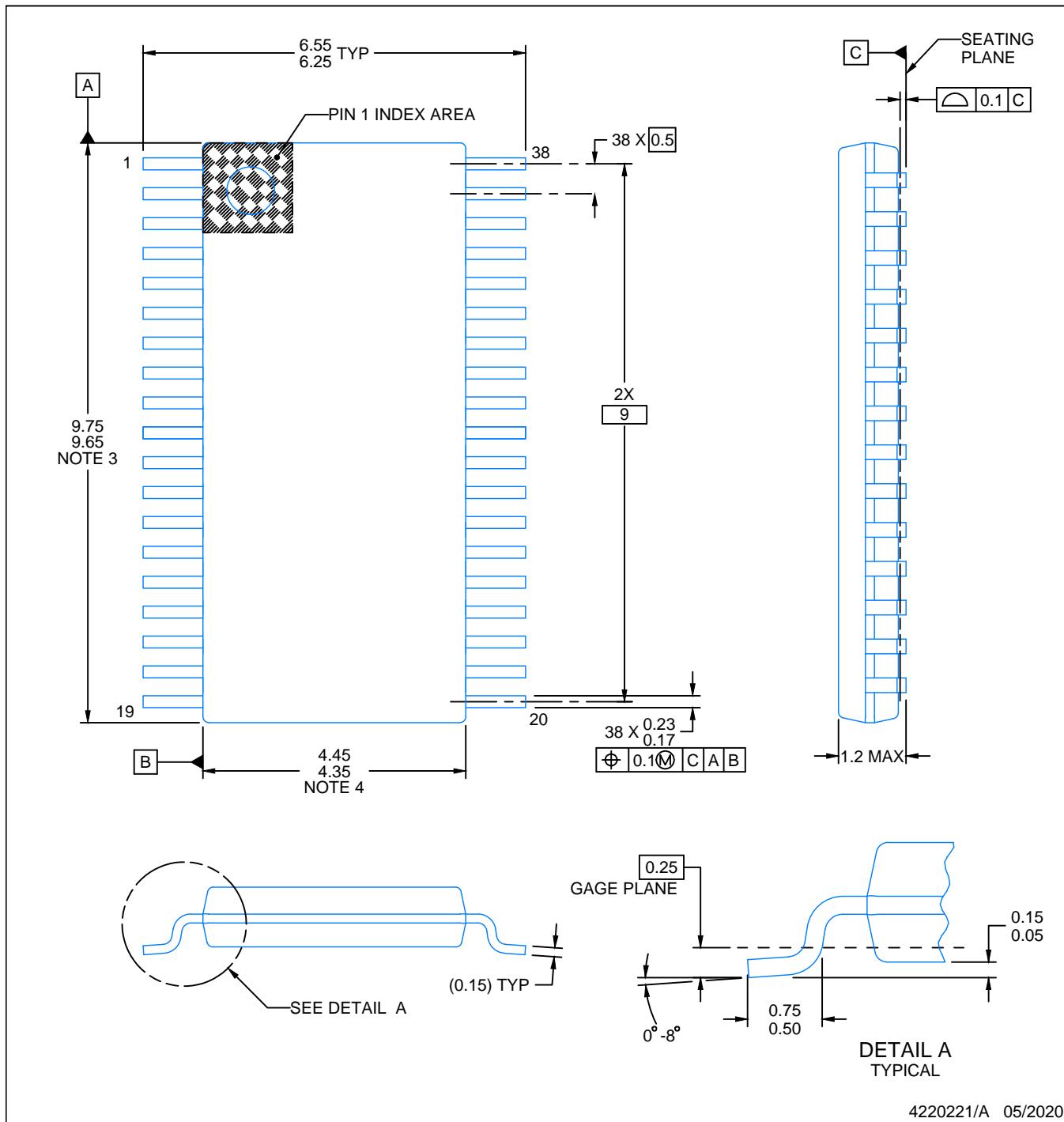

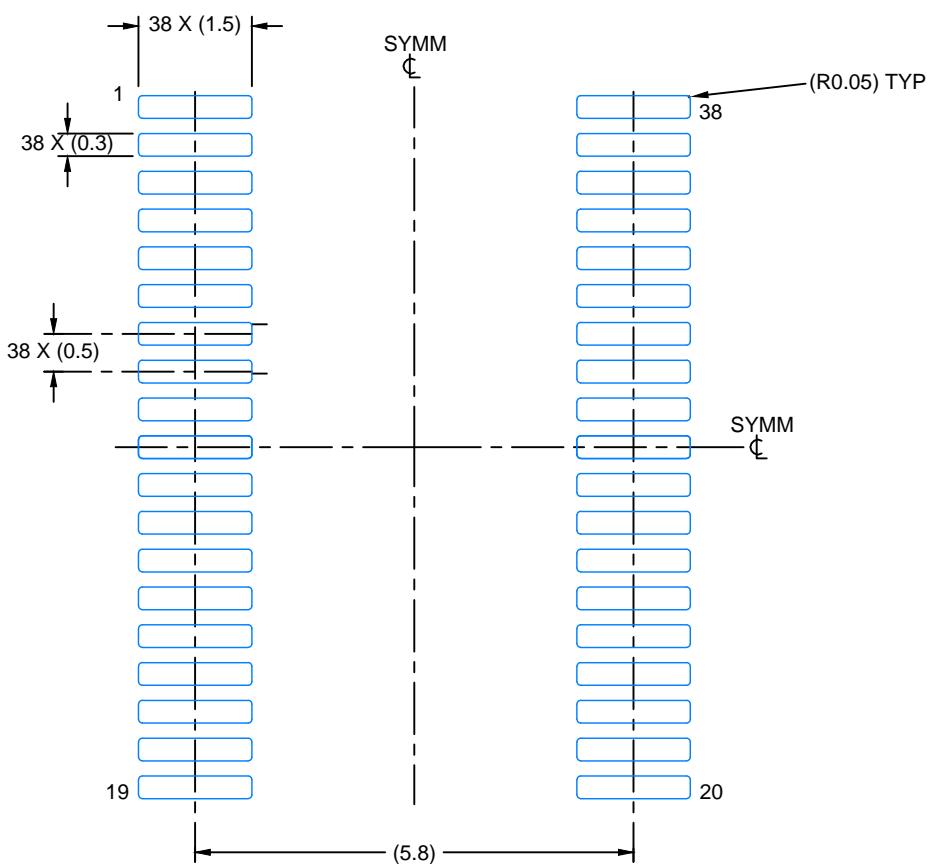

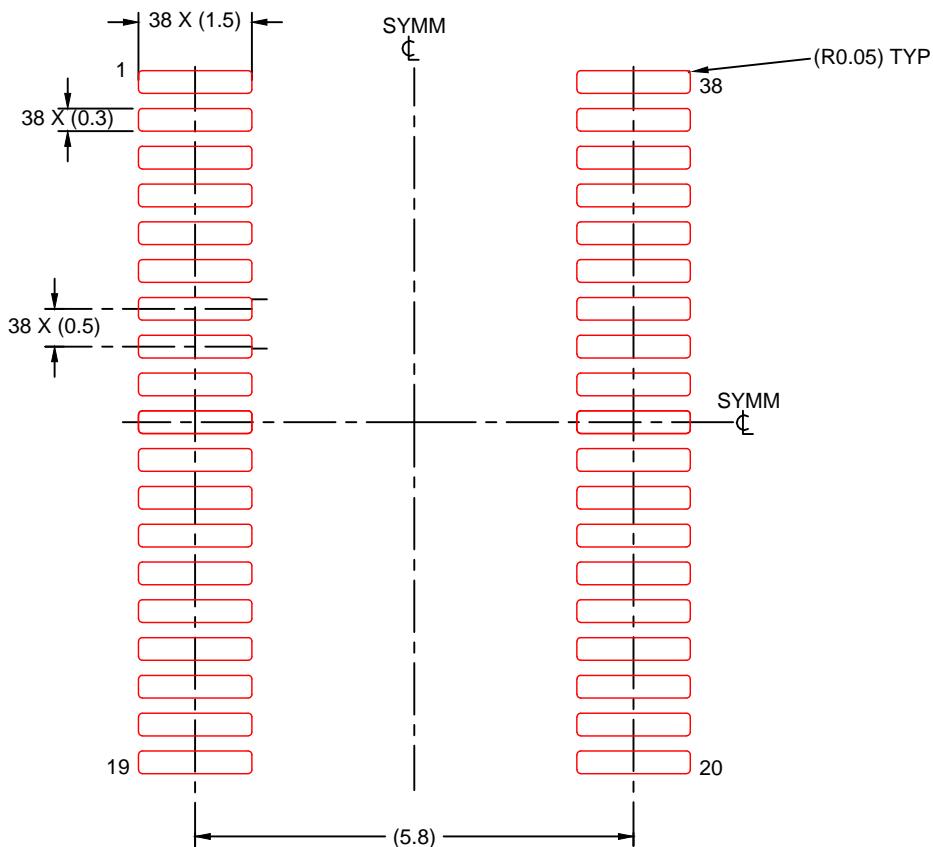

- 38 引脚薄型小尺寸 (TSSOP) 封装

- 内部 50 mA 自动电池均衡

## 2 应用范围

- 无绳电动工具

- 无绳草坪管理设备

- 电动自行车

- 不间断电源 (UPS)

- 轻型电动汽车 (LEV)

## 3 说明

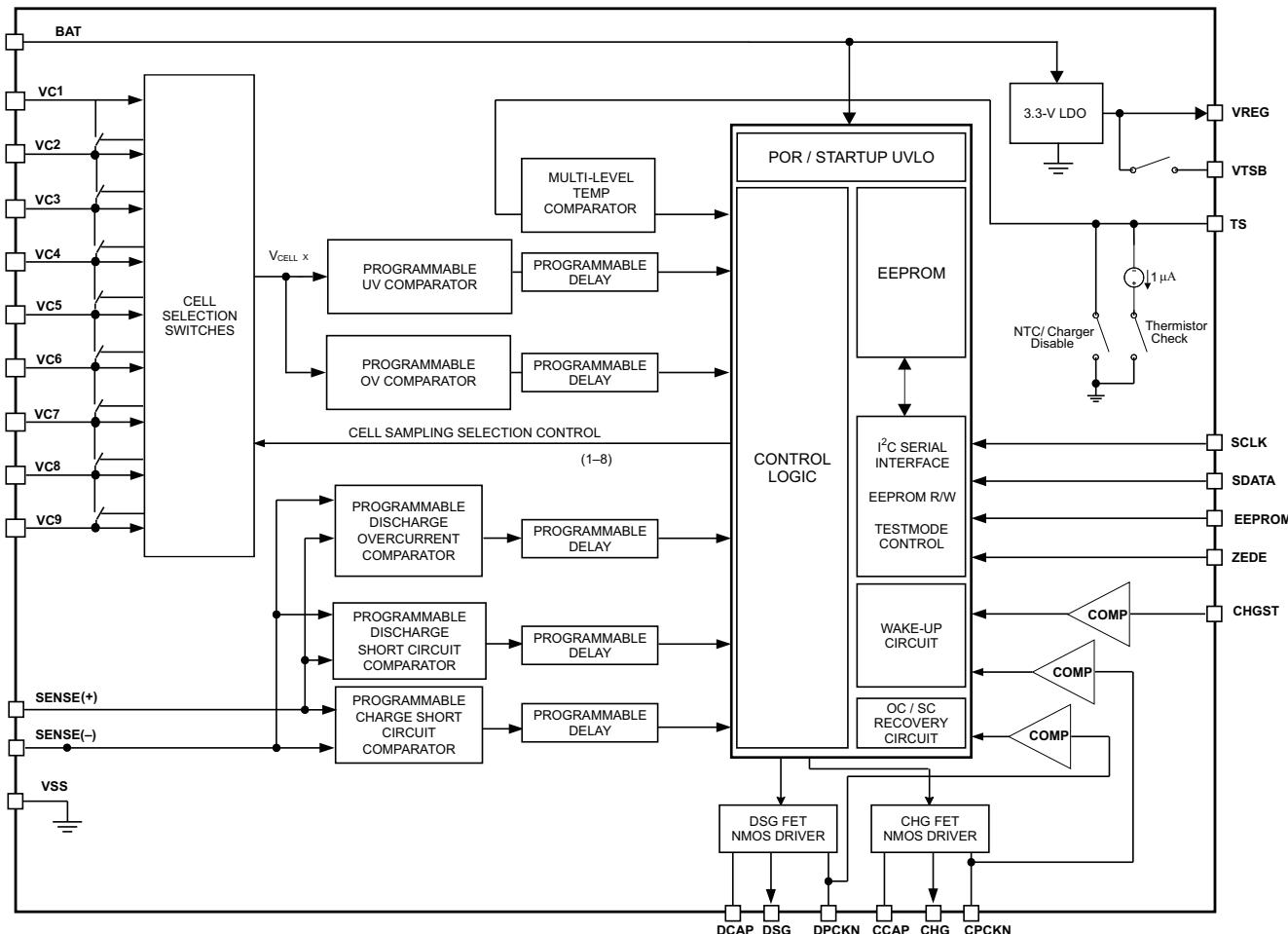

bq77908A 是一款用于锂离子和锂聚合物电池组的电池保护及电池均衡器件。

bq77908A 可监视 4 节到 8 节串联独立电池电压并提供可用于驱动 N 通道金属氧化物半导体场效应晶体管 (MOSFET) 的快速作用输出以中断电源通路。针对安全条件的激活延迟和恢复方法可在非易失性内存内完全编程。

使用内部 50 mA 电池电路可实现自动电池均衡。稳健均衡算法通过保持将所有电池电压保持在平衡状态来确保最佳性能。只有在充电过程中，才可将均衡配置为始终运行或者被完全禁用。

### 器件信息<sup>(1)</sup>

| 部件号      | 封装         | 封装尺寸 (标称值)      |

|----------|------------|-----------------|

| bq77908A | TSSOP (38) | 9.70mm x 4.40mm |

(1) 要了解所有可用封装，请见数据表末尾的可订购产品附录。

### WARNING

当熟悉电池组应用安全的合格技术人员按照本文档详述的指令进行有效集成操作时，bq77908A 系列产品集成电路可帮助系统设计人员大幅提升所用锂离子和锂聚合物电池组的安全性。在使用 bq77908A 之前必须完整阅读本数据表。

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

English Data Sheet: [SLUSAV5](#)

## 目录

|          |                                                         |          |            |                                       |           |

|----------|---------------------------------------------------------|----------|------------|---------------------------------------|-----------|

| <b>1</b> | <b>特性</b>                                               | <b>1</b> | <b>8</b>   | <b>Detailed Description</b>           | <b>11</b> |

| <b>2</b> | <b>应用范围</b>                                             | <b>1</b> | <b>8.1</b> | <b>Overview</b>                       | <b>11</b> |

| <b>3</b> | <b>说明</b>                                               | <b>1</b> | <b>8.2</b> | <b>Functional Block Diagram</b>       | <b>11</b> |

| <b>4</b> | <b>修订历史记录</b>                                           | <b>2</b> | <b>8.3</b> | <b>Feature Description</b>            | <b>11</b> |

| <b>5</b> | <b>说明（继续）</b>                                           | <b>3</b> | <b>8.4</b> | <b>Device Functional Modes</b>        | <b>25</b> |

| <b>6</b> | <b>Pin Configuration and Functions</b>                  | <b>4</b> | <b>8.5</b> | <b>Programming and Register Maps</b>  | <b>26</b> |

| <b>7</b> | <b>Specifications</b>                                   | <b>5</b> | <b>9</b>   | <b>Application and Implementation</b> | <b>37</b> |

| 7.1      | Absolute Maximum Ratings                                | 5        | 9.1        | Application Information               | 37        |

| 7.2      | Handling Ratings                                        | 6        | 10         | 器件和文档支持                               | 52        |

| 7.3      | Recommended Operating Conditions                        | 6        | 10.1       | 文档支持                                  | 52        |

| 7.4      | Thermal Information                                     | 7        | 10.2       | 商标                                    | 52        |

| 7.5      | Electrical Characteristics                              | 8        | 10.3       | 静电放电警告                                | 52        |

| 7.6      | Serial Communication Interface (for Configuration Only) | 10       | 10.4       | 术语表                                   | 52        |

|          |                                                         |          | 11         | 机械封装和可订购信息                            | 52        |

## 4 修订历史记录

## Changes from Original (February 2012) to Revision A

## Page

|                                                                                 |    |

|---------------------------------------------------------------------------------|----|

| • 已删除 应用范围部分中对医疗设备的介绍                                                           | 1  |

| • 已更改 the minimum values for discharge and charge short circuit                 | 12 |

| • 已添加 two table notes to 表 2                                                    | 12 |

| • 已添加 further detail to the DPCKN description                                   | 13 |

| • 已删除 an incorrect cross-reference label                                        | 15 |

| • 已添加 a default to Discharge Overcurrent Detection Delay Settings               | 31 |

| • 已添加 new table notes                                                           | 31 |

| • 已添加 a new WARNING                                                             | 31 |

| • 已添加 a default to SCD Delay Settings                                           | 32 |

| • 已更改 the delay for 0000 in Charge Short-Circuit Delay-Time Settings            | 33 |

| • 已添加 a new table note                                                          | 33 |

| • 已更改 the Cell-Balance Enable Control table                                     | 34 |

| • 已添加 application disclaimer note to the Application and Implementation section | 37 |

## 5 说明 (继续)

bq77908A 附加的高级安全特性包括控制分离电源通路 MOSFET 的功能, 一个非封闭式电池感测线路侦测机制, 以及侦测开短路外部温度传感器故障情况的功能。

### 可编程保护功能

- 宽泛的可编程检测阈值与延迟时间

- 可配置多个电池类型与应用需求:

- 电池过压

- 电池欠压

- 电池组放电过流

- 电池组放电短路

- 电池组充电短路电流

- 可变增益 ( $\times 1$  或  $\times 5$ ) 电流感测电路

- 与多种满足应用要求尺寸的电流感测电阻器 (1m $\Omega$  至 5m $\Omega$  典型值) 兼容

### 固定硬件保护功能

- 预设过温保护

- 开路电池检测

- 开路与短路热敏电阻器检测

- 低压保护能够在低电池电压条件下快速关闭 FET 以大大降低 FET 过热的风险。

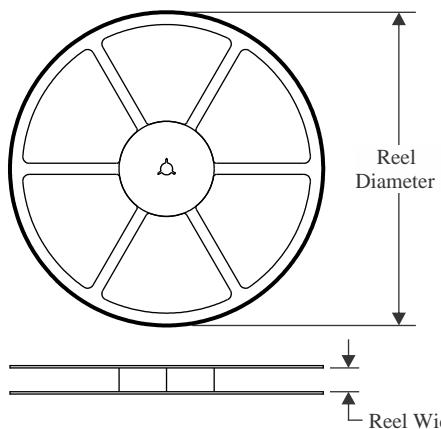

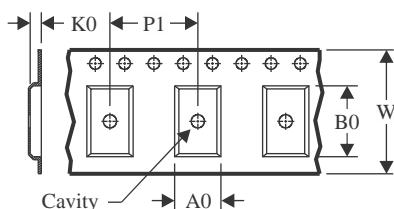

Table 1. Device Comparison Table

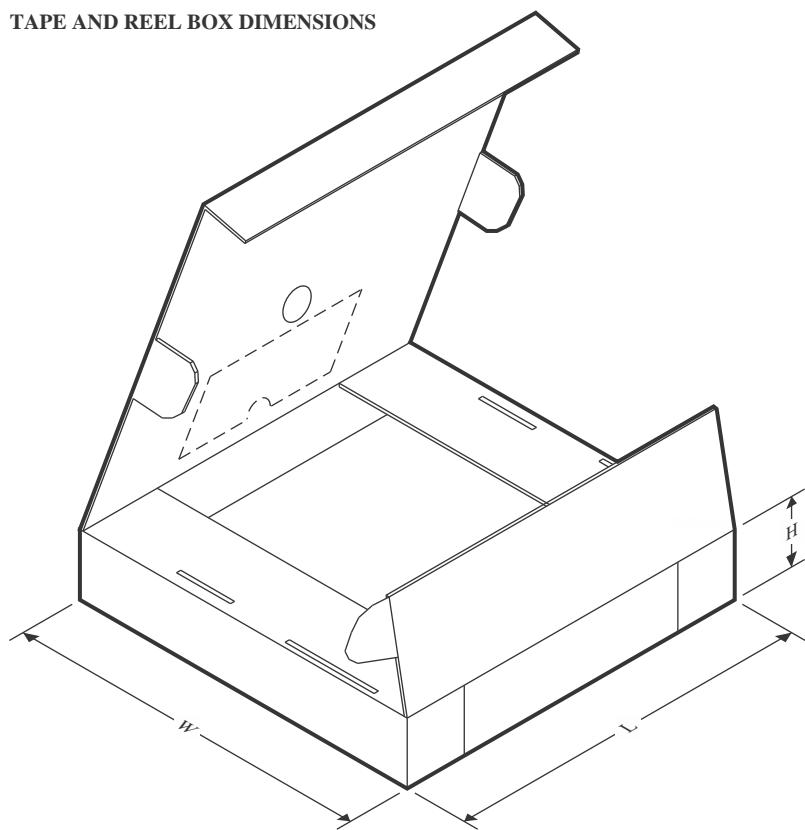

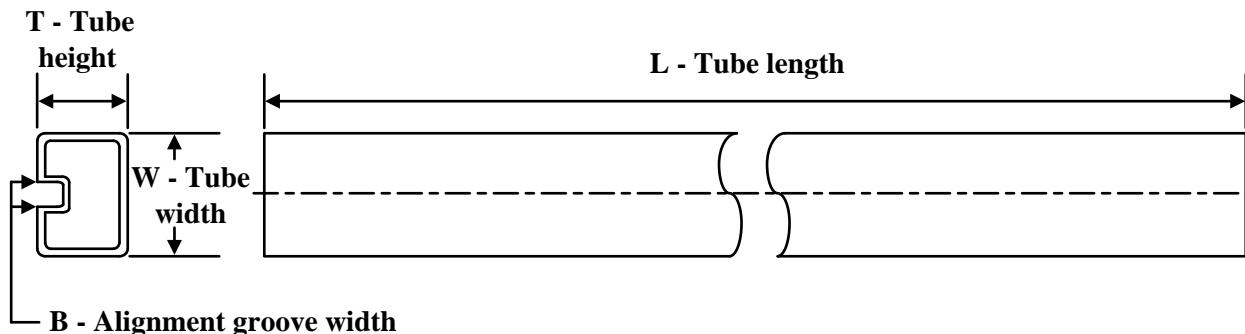

| PART NUMBER  | PACKAGE TYPE | PACKAGING       |

|--------------|--------------|-----------------|

| bq77908ADBT  | TSSOP        | 50-piece tube   |

| bq77908ADBTR | TSSOP        | 2000-piece reel |

## 6 Pin Configuration and Functions

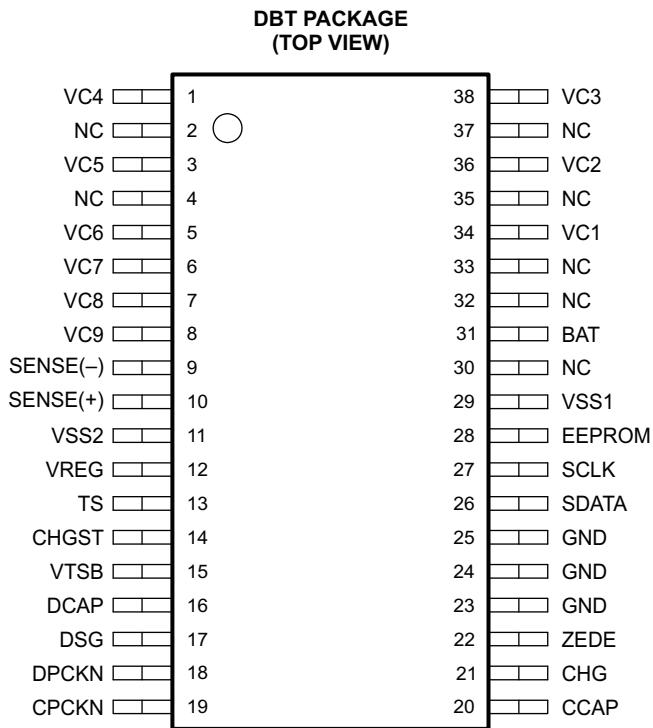

P0034-05

### Pin Functions

| PIN      |                          | DESCRIPTION                                                                                       |

|----------|--------------------------|---------------------------------------------------------------------------------------------------|

| NAME     | NO.                      |                                                                                                   |

| BAT      | 31                       | Power supply voltage, tied to highest cell(+)                                                     |

| CCAP     | 20                       | Energy storage capacitor for charge FET drive                                                     |

| CHG      | 21                       | Charge FET (n-channel) gate drive                                                                 |

| CHGST    | 14                       | Charger-status input, used to detect charger connection/wakeup                                    |

| CPCKN    | 19                       | Pack—charger negative terminal (charger return)                                                   |

| DCAP     | 16                       | Energy storage capacitor for discharge FET drive                                                  |

| DPCKN    | 18                       | Pack—discharge negative terminal (load return)                                                    |

| DSG      | 17                       | Discharge FET (n-channel) gate drive                                                              |

| EEPROM   | 28                       | EEPROM programming voltage input. Connect to VSS for normal operation.                            |

| GND      | 23, 24, 25               | Logic ground (not for power return or analog reference). Tie to VSS.                              |

| NC       | 2, 4, 30, 32, 33, 35, 37 | No connect (DO NOT CONNECT) externally. Failure to leave NC pins open can cause faulty operation. |

| SCLK     | 27                       | Serial-communication clock input used for EEPROM programming                                      |

| SDATA    | 26                       | Serial-communication data input/output used for EEPROM programming (open-drain)                   |

| SENSE(+) | 10                       | Current-sense input                                                                               |

| SENSE(-) | 9                        | Current-sense input                                                                               |

| TS       | 13                       | Temperature sensing input                                                                         |

| VC1      | 34                       | Sense-voltage input terminal for most-positive cell                                               |

| VC2      | 36                       | Sense-voltage input terminal for second-most-positive cell                                        |

| VC3      | 38                       | Sense-voltage input terminal for third-most-positive cell                                         |

| VC4      | 1                        | Sense-voltage input terminal for fourth-most-positive cell                                        |

| VC5      | 3                        | Sense-voltage input terminal for fifth-most-positive cell                                         |

**Pin Functions (continued)**

| PIN  |     | DESCRIPTION                                                                                                                                                                                                   |

|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | NO. |                                                                                                                                                                                                               |

| VC6  | 5   | Sense-voltage input terminal for sixth-most-positive cell                                                                                                                                                     |

| VC7  | 6   | Sense-voltage input terminal for seventh-most-positive cell                                                                                                                                                   |

| VC8  | 7   | Sense-voltage input terminal for eighthmost-positive (most-negative) cell                                                                                                                                     |

| VC9  | 8   | Most-negative cell(–) terminal (BAT–)                                                                                                                                                                         |

| VREG | 12  | Integrated 3.3-V regulator output                                                                                                                                                                             |

| VSS1 | 29  | Analog ground (substrate reference)                                                                                                                                                                           |

| VSS2 | 11  | Analog ground (substrate reference)                                                                                                                                                                           |

| VTSB | 15  | Thermistor bias supply (sourced from VREG)                                                                                                                                                                    |

| ZEDE | 22  | Zero Delay test mode pin. Enables serial communications interface and minimizes protection delay times when connected to logic high. Connect to VSS for normal operation. A strong connection is recommended. |

## 7 Specifications

### 7.1 Absolute Maximum Ratings<sup>(1)</sup>

Over-operating free-air temperature range (unless otherwise noted)

|                                      |                                                                  | MIN  | TYP                | MAX                                                             | UNIT |

|--------------------------------------|------------------------------------------------------------------|------|--------------------|-----------------------------------------------------------------|------|

| DC supply-voltage range, $V_{MAX}$   | BAT                                                              | –0.3 |                    | $(5 \times N) V$ , $N =$<br>number of cells implemented in pack | V    |

| Input voltage range, $V_{IN}$        | DPCKN                                                            | –0.3 |                    | 50                                                              | V    |

|                                      | CPCKN                                                            |      | $(BAT - 50)$       | $(BAT + 0.9) V$                                                 | V    |

|                                      | Cell-to-cell differential, $VC_x$ to $VC_{(x+1)}$ , $x = 1$ to 8 | –0.3 |                    | 9                                                               | V    |

|                                      | SENSE(+)                                                         | –3   |                    | 3                                                               | V    |

|                                      | SENSE(–)                                                         | –0.3 |                    | 50                                                              | V    |

|                                      | SCLK, SDATA, ZEDE <sup>(2)</sup>                                 | –0.3 |                    | 7                                                               | V    |

|                                      | TS, CHGST <sup>(3)(4)</sup>                                      | –0.3 |                    | BAT                                                             | V    |

|                                      | EEPROM                                                           | –0.3 |                    | 15                                                              | V    |

|                                      | Cell input $VC_x$ , $x = 1$ –8                                   |      | $(9 - x) \times 5$ |                                                                 | V    |

|                                      | Cell input VC9                                                   | –3   |                    | 3                                                               | V    |

| Output voltage range, $V_O$          | CHG referenced to CPCKN                                          | –0.3 |                    | 15                                                              | V    |

|                                      | DSG referenced to VSS                                            | –0.3 |                    | 15                                                              | V    |

|                                      | VTSB                                                             | –0.3 |                    | 5                                                               | V    |

| Current for cell balancing, $I_{CB}$ |                                                                  |      | 70                 |                                                                 | mA   |

| Regulator current, $I_{REG}$         |                                                                  |      | 45                 |                                                                 | mA   |

| Storage temperature range, $T_{stg}$ |                                                                  | –65  |                    | 150                                                             | °C   |

- (1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device and expose the system to potential safety risks, resulting from the damage to the IC. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability or cause damage to the device.

- (2) All signal/logic pins that may be connected to the pack external terminals are internally clamped to a maximum voltage of 5 V. If the external source driving these signals exceeds the clamp threshold, series resistance from the pin to the pack terminal is required to avoid overstress on the clamping circuit.

- (3) CHGST and TS pins are tolerant of applied overvoltage as noted to allow for charger single-fault tolerance. Normal operating range is typically 3.3 V or less at this pin; thus, high voltage seen here may correspond to a fault condition.

- (4) Although no damage results when  $CHGST = VSS - 0.3$  V, for proper operation at power up, CHGST must be  $\geq VSS - 0.25$  V.

## 7.2 Handling Ratings

|            |                                                              | MIN | MAX | UNIT |

|------------|--------------------------------------------------------------|-----|-----|------|

| $T_{STG}$  | Storage temperature range                                    | –65 | 150 | °C   |

| ESD Rating | Human body model (HBM) ESD stress voltage <sup>(1)</sup>     |     | 2   | kV   |

|            | Charged device model (CDM) ESD stress voltage <sup>(2)</sup> |     | 500 | V    |

| $T_{FUNC}$ | Functional Temperature                                       | –40 | 110 | °C   |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

Over-operating free-air temperature range (unless otherwise noted)

|                              |                                                                    | MIN                                                             | TYP     | MAX                         | UNIT  |

|------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------|---------|-----------------------------|-------|

| Supply voltage               | BAT <sup>(1)</sup>                                                 | 5.6 <sup>(2)</sup>                                              |         | 35 <sup>(3)</sup>           | V     |

| $V_I$<br>Input voltage range | Cell differential, $VC_x$ to $VC(x + 1)$ ,<br>( $x = 1$ to 8 )     | 1.4                                                             |         | 4.375                       | V     |

|                              | Cell input $VC_x$ , $x = 1$ – 8                                    |                                                                 |         | $(9 - x) \times$<br>4.375 V |       |

|                              | Cell input $VC_9$                                                  | –1                                                              |         | 1                           |       |

| $V_{IH}$                     | Logic-level input, high                                            | 0.8 $\times V_{REG}$                                            |         |                             | V     |

| $V_{IL}$                     | Logic-level input, low                                             |                                                                 |         | 0.2 $\times V_{REG}$        | V     |

| $V_{SENSE(+)}$               | Voltage applied at SENSE( $\pm$ )<br>pins                          |                                                                 | VSS – 1 | VSS + 1                     | V     |

| $V_{SENSE(-)}$               |                                                                    | –0.2                                                            |         | BAT                         | V     |

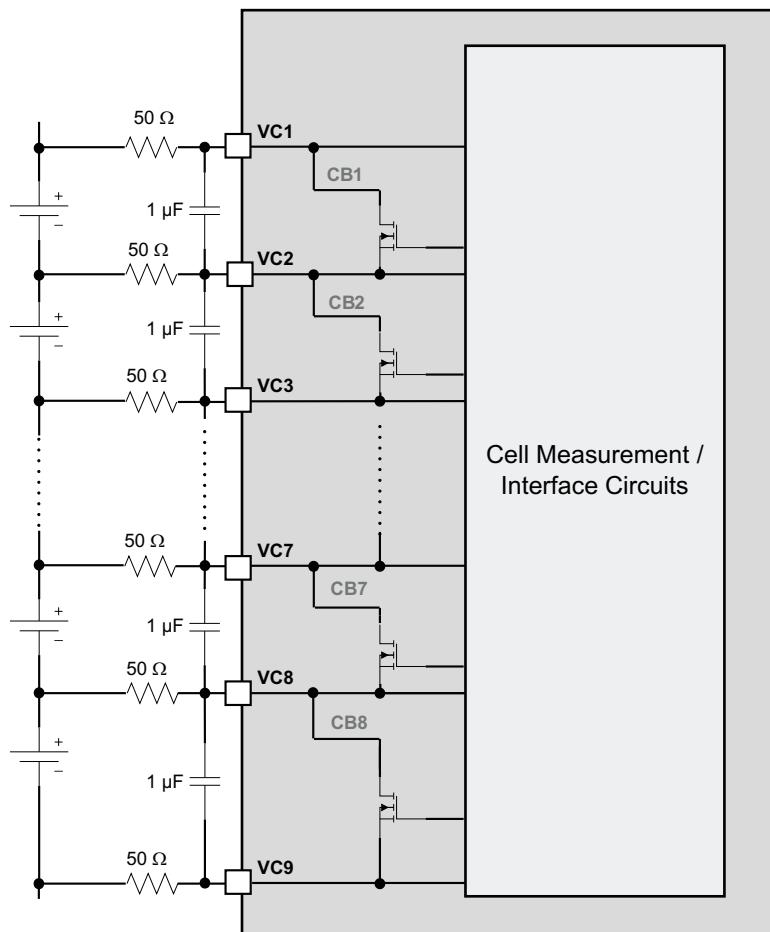

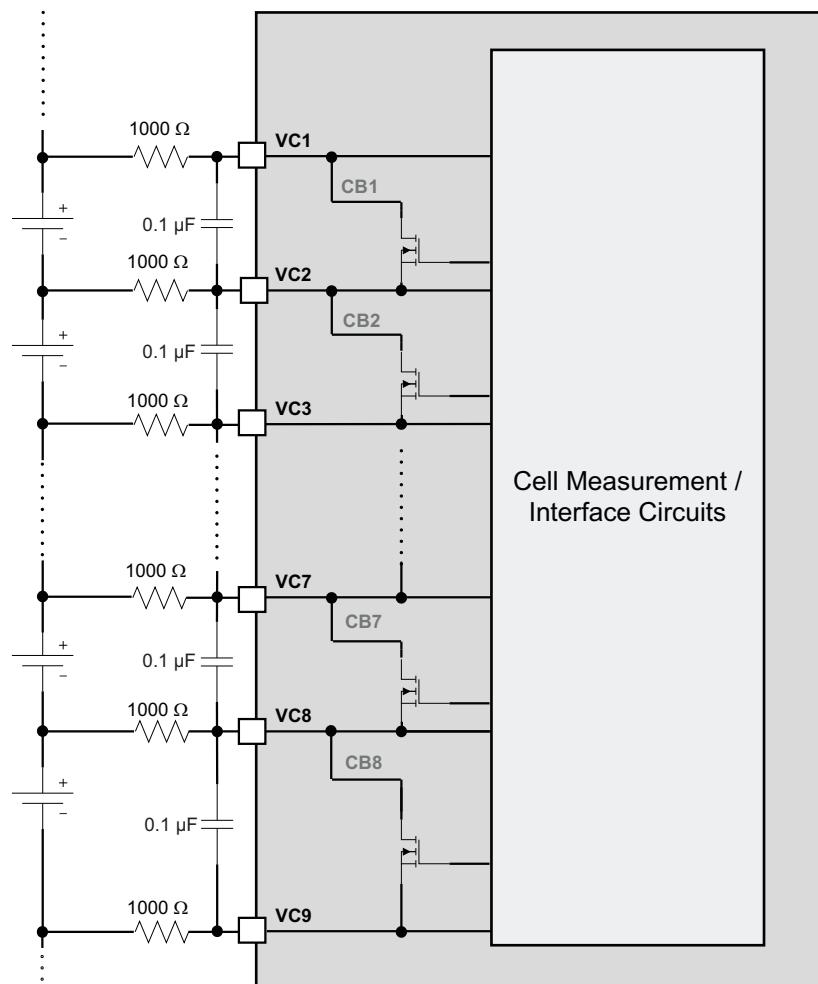

| $R_{VCX}$                    | Recommended $VC_x$ nominal<br>input resistance                     | 50                                                              | 100     | 1000                        | Ω     |

| $I_{REG}$                    | Regulator current                                                  |                                                                 |         | 10                          | mA    |

| $I_{CB}$                     | Cell balancing current                                             |                                                                 |         | 50                          | mA    |

| $C_{VCX}$                    | Recommended $VC_x$ nominal<br>input filter capacitance             |                                                                 |         | 1                           | μF    |

| $R_{CPCKN},$<br>$R_{DPCKN}$  | Recommended isolation-pin<br>input resistance                      |                                                                 | 100     |                             | Ω     |

| $R_{LDRM_DET}$               | Pulldown for load-removal<br>detection                             |                                                                 | 50      |                             | kΩ    |

| $C_{VREG}$                   | External 3.3-V REG capacitor                                       | 1                                                               |         |                             | μF    |

|                              | EEPROM number of writes                                            |                                                                 |         | 3                           | times |

| $T_{OPR}$                    | Operating temperature                                              | Meeting all specification limits                                | –25     | 85                          | °C    |

| $T_{FUNC}$                   | Functional temperature                                             | Operational but may be out of spec limits,<br>no damage to part | –40     | 100                         | °C    |

| $C_{CCAP},$<br>$C_{DCAP}$    | External capacitance on CCAP<br>and DCAP pins <sup>(4)</sup>       |                                                                 | 0.1     | 1                           | μF    |

| $R_P$                        | Serial communication interface<br>pullup resistance <sup>(5)</sup> | SCLK, SDATA                                                     |         | 2.2                         | kΩ    |

(1) The voltage rate of change at the BAT pin should be limited to a maximum of 1 V per  $\mu$ s in order to prevent unwanted device shutdown.

(2) Minimum voltage assumes 4-cell connection at 1.4 V/cell.

(3) Maximum voltage assumes 8-cell connection at 4.375 V/cell.

(4)  $C_{CCAP}$  and  $C_{DCAP}$  act as charge reservoirs for the CHG and DSG pins when driving large protection FETs. Minimum value is required for stability, independent of the CHG and DSG loading.

(5) Pullups for configuration of device during pack manufacturing. SCLK and SDATA should be pulled high or low in application.

### NOTE

Refer to the [Open-Cell Detection](#) overview in the [Application Information](#) section for a description of RVCX and CVCX sizing.

## 7.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> | bq77908A                                                           | UNIT  |

|-------------------------------|--------------------------------------------------------------------|-------|

|                               | DBT                                                                |       |

|                               | 38 PINS                                                            |       |

| $\theta_{JA}$                 | Junction-to-ambient thermal resistance, non-LDO <sup>(2)</sup>     | 71.7  |

| $\theta_{JA2}$                | Junction-to-ambient thermal resistance, LDO <sup>(2) (3)</sup>     | 115.8 |

| $\theta_{JCTop}$              | Junction-to-case (top) thermal resistance <sup>(4)</sup>           | 18.5  |

| $\theta_{JB}$                 | Junction-to-board thermal resistance <sup>(5)</sup>                | 33.9  |

| $\psi_{JT}$                   | Junction-to-top characterization parameter, non-LDO <sup>(6)</sup> | 1     |

| $\psi_{JT2}$                  | Junction-to-top characterization parameter, LDO <sup>(6) (3)</sup> | 38.9  |

| $\psi_{JB}$                   | Junction-to-board characterization parameter <sup>(7)</sup>        | 33.2  |

| $\theta_{JCbot}$              | Junction-to-case (bottom) thermal resistance <sup>(8)</sup>        | N/A   |

- (1) For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, [SPRA953](#).

- (2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) These metrics should be used only for calculating junction temperature due to power dissipation resulting from the  $I_{OUT}$  load on VREG. Junction temperature calculations for all other sources of power dissipation should use the standard values  $\theta_{JA}$  and  $\psi_{JT}$ .

- (4) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (5) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- (6) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- (7) The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- (8) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

## bq77908A

ZHCS758A—FEBRUARY 2012—REVISED OCTOBER 2014

www.ti.com.cn

## 7.5 Electrical Characteristics

$V_{CELL(n)} = 1.4$  to  $4.375$  for all cells,  $T_A = -25^\circ\text{C}$  to  $85^\circ\text{C}$ ,  $BAT = 5.6$  to  $35$  V; Typical values stated where  $T_A = 25^\circ\text{C}$  and  $BAT = 28.8$  V (unless otherwise noted)

| PARAMETER                                                                    | TEST CONDITIONS                                                                                                                                                    | MIN                    | TYP | MAX  | UNIT |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|------|------|

| <b>SUPPLY CURRENT</b>                                                        |                                                                                                                                                                    |                        |     |      |      |

| $I_{CC}$                                                                     | NORMAL-mode average supply current<br>CHG, DSG = on (no dc load), VREG = on,<br>$I_{REG} = 0$ mA, BAT = 28.8 V                                                     |                        | 50  | 75   | µA   |

| $I_{SHUTDOWN\_2}^{(1)}$                                                      | $V_{CELL} < V_{UV}$ , VREG = off (EEPROM set), CPCKN = 0.3 V                                                                                                       |                        | 5   | 17   | µA   |

|                                                                              | $V_{CELL} < V_{UV}$ , VREG = off (EEPROM set), CPCKN = 0.5 V                                                                                                       |                        | 20  | 60   |      |

| <b>INTERNAL POWER CONTROL (STARTUP, SHUTDOWN, GATE DRIVE UNDERTHRESHOLD)</b> |                                                                                                                                                                    |                        |     |      |      |

| $V_{STARTUP}$                                                                | Minimum voltage for initial power up <sup>(2)</sup><br>Measured at BAT pin                                                                                         |                        |     | 7    | V    |

| $V_{POR}^{(3)}$                                                              | LDO POR voltage – voltage on LDO that initiates a POR<br>$I_{LDO} = 2$ mA                                                                                          | 2.7                    |     | 3.2  | V    |

| $V_{GATE\_UV}$                                                               | FET gate shutdown threshold (voltage falling)<br>Measured at CCAP/DCAP pins                                                                                        | 4.5                    | 4.9 | 5.3  | V    |

| $V_{GATE\_UV\_H}$                                                            | FET gate shutdown hysteresis voltage<br>Measured at CCAP/DCAP pins                                                                                                 | 0.45                   |     | 0.7  | V    |

| <b>FET DRIVE<sup>(4)</sup></b>                                               |                                                                                                                                                                    |                        |     |      |      |

| $V_{(FETON)}$                                                                | Gate drive voltage at DSG and CHG pins for FET ON (enabled) conditions<br>BAT voltage = 35 V (gate-drive circuit in regulation mode), no dc load                   | 11                     | 12  | 14   | V    |

|                                                                              |                                                                                                                                                                    | 9                      |     |      |      |

|                                                                              |                                                                                                                                                                    | $>V_{GATE\_UV}$        |     |      |      |

| $V_{(FETOFF)}$                                                               | Gate drive voltage at DSG and CHG pins for FET OFF (disabled) conditions<br>$V_{O(FETOFFDSG)} = V_{(DSG)} - V_{GND}$<br>$V_{O(FETOFFCHG)} = V_{(VHG)} - V_{pack-}$ |                        |     | 0.2  | V    |

|                                                                              |                                                                                                                                                                    |                        |     | 0.2  |      |

| $t_r$                                                                        | Rise time, measured at IC pin (CHG or DSG)<br>$C_L = 50$ nF, BAT = 35 V                                                                                            | $V_{DSG}$ : 10% to 90% | 90  | 140  | µs   |

|                                                                              |                                                                                                                                                                    | $V_{CHG}$ : 10% to 90% | 90  | 140  |      |

|                                                                              |                                                                                                                                                                    | $V_{DSG}$ : 10% to 90% | 90  | 140  |      |

|                                                                              |                                                                                                                                                                    | $V_{CHG}$ : 10% to 90% | 90  | 140  |      |

| $t_f$                                                                        | Fall time, measured at IC pin (CHG or DSG)<br>$C_L = 50$ nF, BAT = 35 V                                                                                            | $V_{DSG}$ : 90% to 10% | 10  | 20   | µs   |

|                                                                              |                                                                                                                                                                    | $V_{CHG}$ : 90% to 10% | 20  | 40   |      |

|                                                                              |                                                                                                                                                                    | $V_{DSG}$ : 90% to 10% | 50  | 100  |      |

|                                                                              |                                                                                                                                                                    | $V_{CHG}$ : 90% to 10% | 50  | 100  |      |

| <b>VREG, INTEGRATED 3.3-V LDO</b>                                            |                                                                                                                                                                    |                        |     |      |      |

| $V_{REG}$                                                                    | Output-voltage regulation under all line, load, temperature conditions<br>$I_{OUT} = 10$ mA (maximum dc load) <sup>(5)</sup>                                       | 3.1                    | 3.3 | 3.55 | V    |

|                                                                              |                                                                                                                                                                    | $I_{OUT} = 0.2$ mA     | 3.1 | 3.3  | 3.55 |

| $I_{SC}$                                                                     | Short-circuit current limit<br>VREG = 0 V, forced external short (thermally protected) <sup>(6)</sup>                                                              | 20                     |     | 45   | mA   |

- For predictable shutdown current, the voltage at CPCKN with respect to VSS must be controlled. In the parallel FET case, CPCKN is clamped through the body diode of the charge FET. In the series FET case, external circuitry is required to keep CPCKN from floating. Contact TI for recommended application circuits.

- At this voltage, the LDO has sufficient voltage to maintain regulation. The POR then enables the charger-detect logic. Logic is held in reset until inserted into charger and LDO has reached  $V_{POR}$ . The part still operates below 7 V to the spec limit of 5.6 V.

- $V_{POR}$  and  $V_{REG}$  are derived from the same internal reference, so that the MAX value of  $V_{POR}$  and the MIN value of VREG do not occur at the same time.

- FET drive is disabled if voltage at CCAP or DCAP pins  $< V_{GATE\_UV}$ . Turnoff due to gate-drive undervoltage condition meets the same timing requirements as logic-initiated gate turnoff.

- Electrical Characteristics assume that  $I_{OUT} = 0$  so that the internal junction temperature ( $T_J$ ) is effectively equal to the ambient temperature ( $T_A$ ). For larger non-zero values of  $I_{OUT}$ ,  $T_J$  can be significantly higher than  $T_A$ . In these cases,  $T_J$  should be substituted for  $T_A$  in the test and operating conditions.  $T_J$  can be calculated from the device power dissipation as described under Thermal Characteristics. The device power dissipation due to  $I_{OUT}$  is  $(VBAT - VREG) \times I_{OUT}$ .

- Regulator shuts down prior to current-limit maximum specification if junction temperature exceeds safe range.

## Electrical Characteristics (接下页)

$V_{CELL(n)} = 1.4$  to  $4.375$  for all cells,  $T_A = -25^\circ\text{C}$  to  $85^\circ\text{C}$ ,  $BAT = 5.6$  to  $35$  V; Typical values stated where  $T_A = 25^\circ\text{C}$  and  $BAT = 28.8$  V (unless otherwise noted)

| PARAMETER                                                     |                                                                                              | TEST CONDITIONS                                                                     | MIN                          | TYP          | MAX | UNIT             |

|---------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------|--------------|-----|------------------|

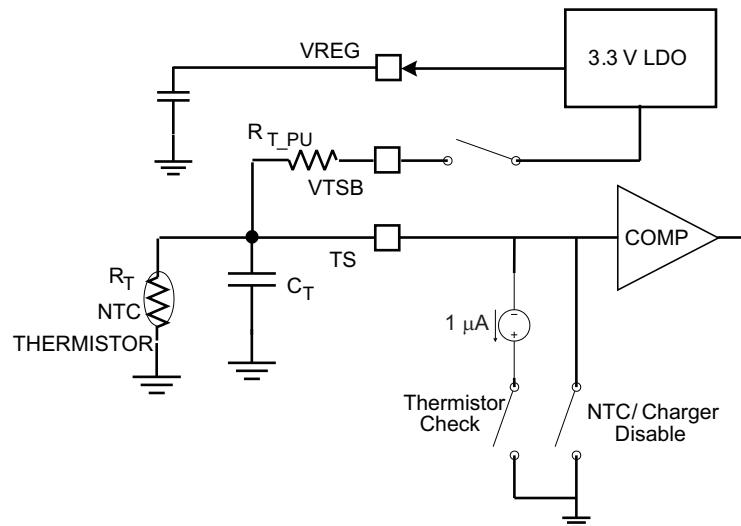

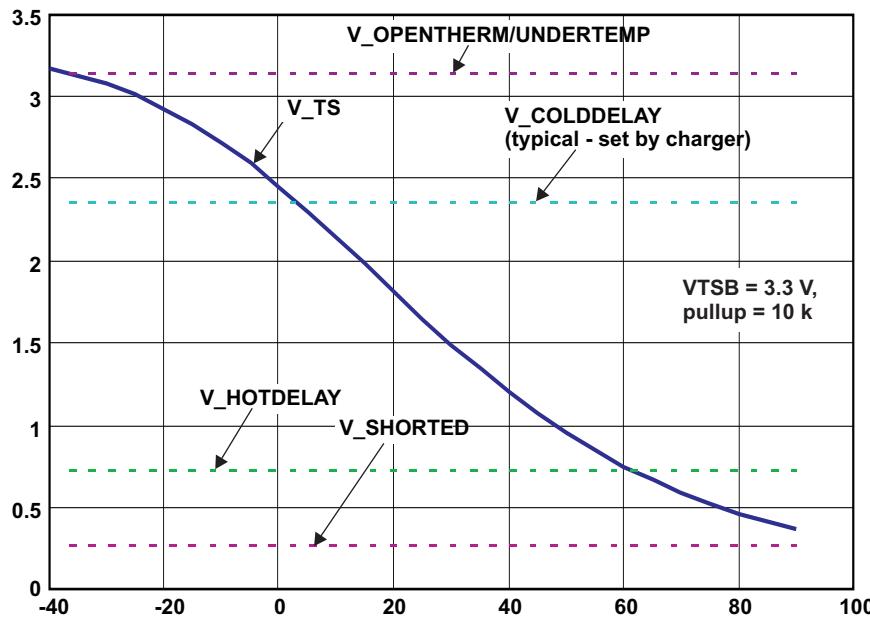

| <b>TS TEMPERATURE SENSING</b>                                 |                                                                                              |                                                                                     |                              |              |     |                  |

| $r_{DS(on)}$                                                  | VTSB pin pullup resistance                                                                   | $I_{OUT} = -1$ mA at VTSB pin, $r_{DS(on)} = (V_{REG} - V_{VTSB}) / 1$ mA           |                              | 50           | 150 | $\Omega$         |

|                                                               | TS pin fault-signal pulldown resistance                                                      | $OV_{\_CTRL} = 1$ , $V_{CELL} > V_{OV}$                                             |                              | 50           | 150 |                  |

| $I_{TS\_PD}$                                                  | TS pin thermistor check pulldown current                                                     | TS = 3.3 V (externally driven)                                                      | 1                            | 2            | 4   | $\mu\text{A}$    |

| $t_{THERM\_CHECK}$                                            | Thermistor fault sampling interval                                                           |                                                                                     |                              | 4            |     | s                |

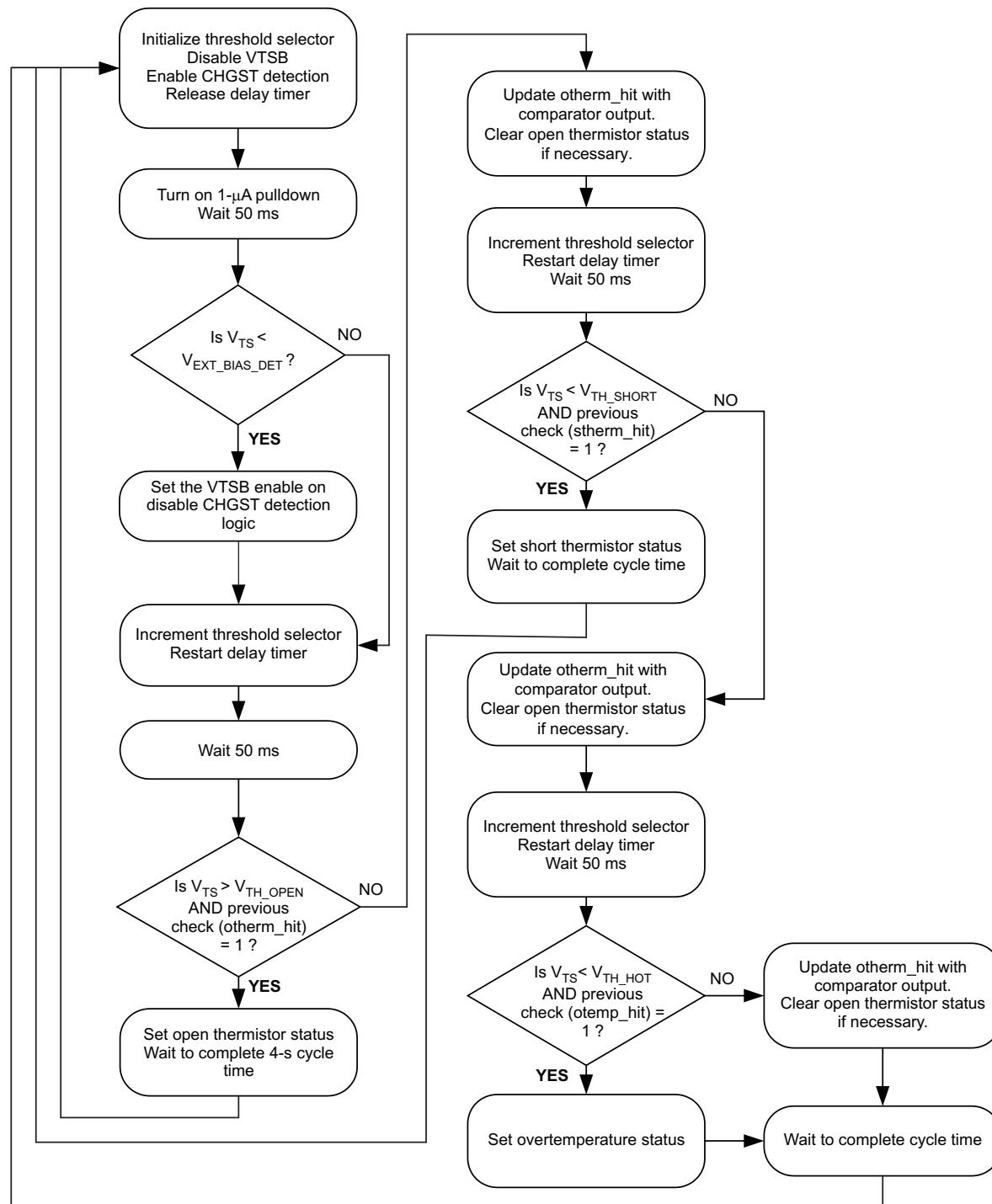

| $V_{EXT\_BIAS\_DET}$                                          | Thermistor external-bias supply-detection threshold                                          | Internal VTSB supply off                                                            | 13%                          | 15%          | 17% | VREG             |

| $V_{HOT}$                                                     | Overtemperature-detection threshold (ratiometric to VTSB)                                    | Internal VTSB supply on, no external bias                                           | 17%                          |              | 21% | VREG             |

| $V_{TH\_SHORT}$                                               | Thermistor short-detection trip threshold (ratiometric to VTSB)                              | Internal VTSB supply on, no external bias                                           | 1%                           |              | 10% | VREG             |

| $V_{TH\_HYST}$                                                | TS comparator hysteresis                                                                     | Hysteresis for short, open, and overtemperature comparators                         | 3%                           |              | 8%  | VREG             |

| $V_{TH\_OPEN}$                                                | Thermistor open detection (ratiometric to VTSB)                                              | Internal VTSB supply on, no external bias                                           | 90%                          |              | 98% | VREG             |

| <b>CELL BALANCE</b>                                           |                                                                                              |                                                                                     |                              |              |     |                  |

| $R_{BAL}$                                                     | Cell-balance internal resistance <sup>(7)</sup>                                              | $r_{DS(on)}$ for internal FET switch, $T_A = 0^\circ\text{C}$ to $50^\circ\text{C}$ | $V_{CELL} = CBV_{MAX} = 3.9$ | -50%         | 10  | 50%              |

|                                                               |                                                                                              |                                                                                     | $V_{CELL} = CBV_{MAX} = 3.2$ | -50%         | 20  | 50%              |

|                                                               |                                                                                              |                                                                                     | $V_{CELL} = CBV_{MAX} = 2.5$ | -50%         | 30  | 50%              |

| $t_{CELL\_BAL\_CHECK}$                                        | Cell balancing update interval                                                               |                                                                                     |                              | 7.5          |     | min              |

| <b>OPEN-CELL CONNECTION</b>                                   |                                                                                              |                                                                                     |                              |              |     |                  |

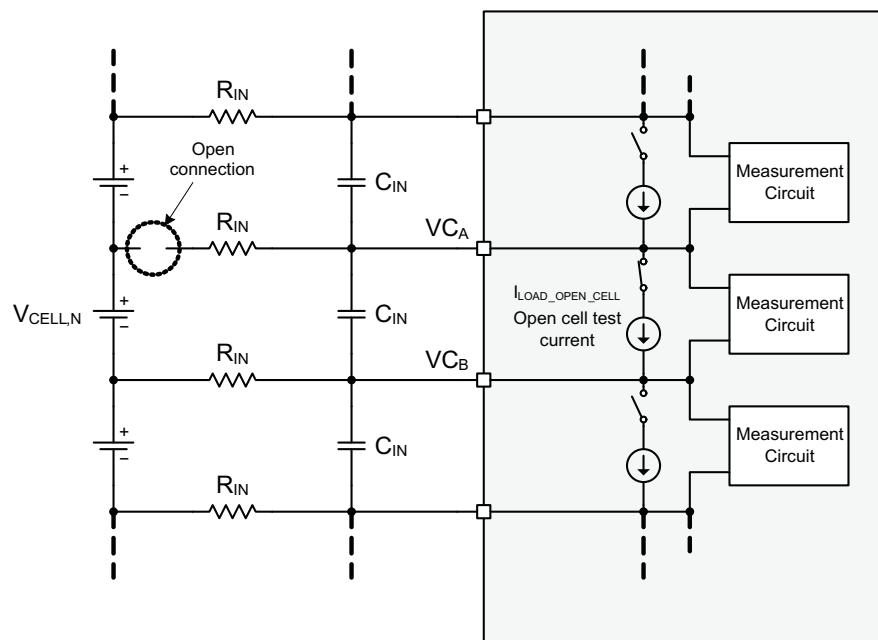

| $I_{LOAD\_OPEN\_CELL}$ <sup>(8)</sup>                         | Cell loading during open-cell detect                                                         |                                                                                     | 75                           |              | 450 | $\mu\text{A}$    |

| $t_{OPEN\_CELL\_CHECK}$                                       | Open-cell fault-sampling interval ( $N = \text{total number of cells in pack}$ )             |                                                                                     |                              | $4 \times N$ |     | s                |

| $R_{OPEN\_CELL}$                                              | Minimum impedance from cell terminal to $VCx$ input that is interpreted as an open condition |                                                                                     |                              |              | 100 | $\text{k}\Omega$ |

| <b>BATTERY-PROTECTION-THRESHOLD TOLERANCES<sup>(9)</sup></b>  |                                                                                              |                                                                                     |                              |              |     |                  |

| $\Delta V_{OV}$                                               | OV detection threshold accuracy for $V_{OV} = 4.2$ V <sup>(10)</sup>                         | $T_A = 0^\circ\text{C}$ to $50^\circ\text{C}$                                       | -25                          |              | 25  | $\text{mV}$      |

|                                                               |                                                                                              | $T_A = -25^\circ\text{C}$ to $85^\circ\text{C}$                                     | -50                          |              | 50  |                  |

| $\Delta V_{UV}$                                               | OV detection threshold accuracy for $V_{OV} = 3.2$ V <sup>(10)</sup>                         | $T_A = 0^\circ\text{C}$ to $50^\circ\text{C}$                                       | -50                          |              | 50  | $\text{mV}$      |

|                                                               |                                                                                              | $T_A = -25^\circ\text{C}$ to $85^\circ\text{C}$                                     | -75                          |              | 75  |                  |

| $\Delta V_{UV}$                                               | UV detection threshold accuracy                                                              | $T_A = -25^\circ\text{C}$ to $85^\circ\text{C}$                                     | -100                         |              | 100 | $\text{mV}$      |

| $\Delta V_{SCD}$<br>$\Delta V_{OCD}$                          | OCC/SCD detection threshold accuracy                                                         | $T_A = -25^\circ\text{C}$ to $85^\circ\text{C}$                                     | -20%                         |              | 20% |                  |

| $\Delta V_{SCC}$                                              | SCC detection threshold accuracy                                                             | $V_{SCC}$ from 10 mV to 15 mV                                                       | -3                           |              | 3   | $\text{mV}$      |

|                                                               |                                                                                              | $V_{SCC} > 15$ mV                                                                   | -20%                         |              | 20% |                  |

| <b>BATTERY PROTECTION DELAY-TIME TOLERANCES<sup>(9)</sup></b> |                                                                                              |                                                                                     |                              |              |     |                  |

| $\Delta t_{OV}$                                               | OV detection delay time accuracy                                                             | Default EEPROM setting                                                              | -15%                         |              | 15% |                  |

| $\Delta t_{UV}$                                               | UV detection delay time accuracy                                                             |                                                                                     | -15%                         |              | 15% |                  |

| $\Delta t_{SCD}$                                              | OCD/SCD detection delay time accuracy                                                        | $t_{SCD}$ Max                                                                       | -15%                         |              | 15% |                  |

| $\Delta t_{SCC}$                                              | SCD detection delay time accuracy                                                            |                                                                                     | -15%                         |              | 15% |                  |

- (7) Balance current is not internally limited. External series resistance must be used to ensure balance current is below 50 mA maximum to limit IC internal power dissipation.

- (8) This current is sufficient to detect an open-cell condition down to 100  $\text{k}\Omega$  across the cell from circuitry outside of the bq77908A. The average current from this loading is less than 1  $\mu\text{A}$  for a 8-cell configuration.

- Application Note:* When using this part with other devices that connect to the battery cells, care must be taken to avoid excessive parallel capacitances on the cell input pins.

- (9) Nominal values are set by EEPROM programming; see EEPROM table for possible values.

- (10) Standard production parts are calibrated at 4.2 V. An additional OV threshold accuracy shift of 25 mV per volt of OV set point is possible. Contact TI for calibration options at set point voltages other than 4.2 V.

## Electrical Characteristics (接下页)

$V_{CELL(n)}$  = 1.4 to 4.375 for all cells,  $T_A$  =  $-25^{\circ}\text{C}$  to  $85^{\circ}\text{C}$ , BAT = 5.6 to 35 V; Typical values stated where  $T_A$  =  $25^{\circ}\text{C}$  and BAT = 28.8 V (unless otherwise noted)

| PARAMETER                               | TEST CONDITIONS                                                                                                                                     | MIN                | TYP  | MAX  | UNIT            |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|------|-----------------|

| <b>CHARGER DETECTION<sup>(11)</sup></b> |                                                                                                                                                     |                    |      |      |                 |

| $V_{CHG\_DET1}$                         | Voltage at CHGST pin, referenced to VSS, to determine charger present (charger insertion detected when voltage at CHGST pin > $V_{CHG\_DET1}$ )     | 5.6 V < BAT < 35 V | 0.3  | 0.5  | 0.7 V           |

| <b>LOAD REMOVAL DETECTION</b>           |                                                                                                                                                     |                    |      |      |                 |

| $V_{OPEN\_LOAD}$                        | Voltage at DPCKN, referenced to VSS, with DSG FET disabled to detect load removal (load removal detected when voltage at DPCKN < $V_{OPEN\_LOAD}$ ) | 5.6 V < BAT < 35 V | 1.5  | 2    | 2.5 V           |

| $R_{DSG\_GND}$                          | Internal resistance between DPCKN and VSS                                                                                                           | 5.6 V < BAT < 35 V | 1000 | 1500 | 3000 k $\Omega$ |

| <b>EEPROM LIFETIME</b>                  |                                                                                                                                                     |                    |      |      |                 |

| $T_{DR}$                                | Data retention                                                                                                                                      | 5.6 V < BAT < 35 V | 10   |      | years           |

(11) Alternate charger detection options are available using the CPCKN pin. Contact TI for additional configuration versions.

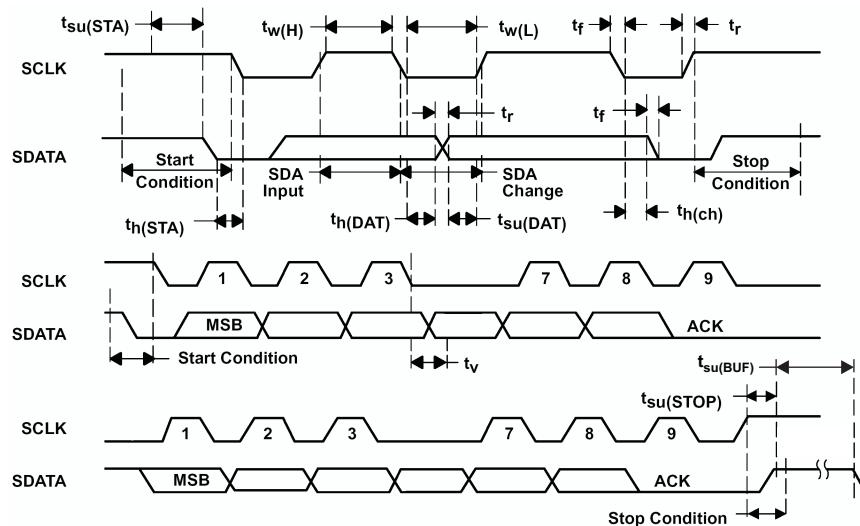

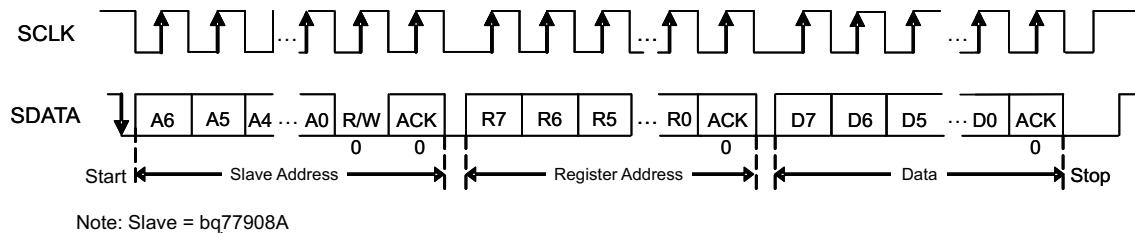

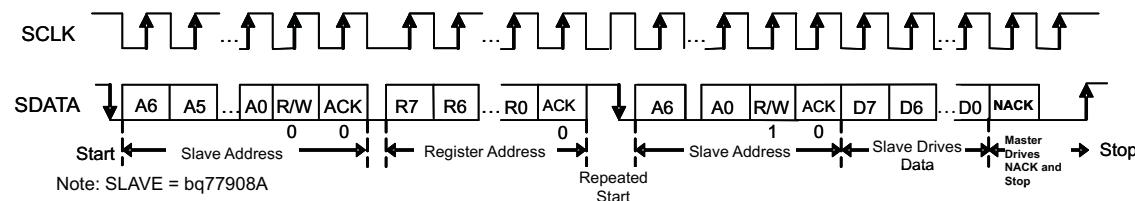

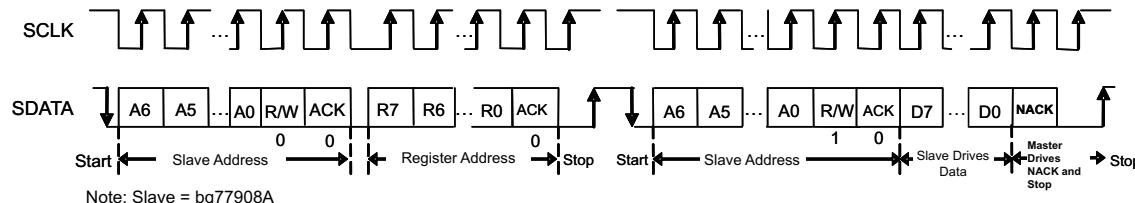

## 7.6 Serial Communication Interface (for Configuration Only)

BAT = 5.6 V to 35 V,  $T_A$  =  $-25^{\circ}\text{C}$  to  $85^{\circ}\text{C}$

| PARAMETER                                                                              | MIN | MAX  | UNIT          |

|----------------------------------------------------------------------------------------|-----|------|---------------|

| $t_r$ SCLK, SDATA rise time                                                            |     | 1000 | ns            |

| $t_f$ SCLK, SDATA fall time                                                            |     | 300  | ns            |

| $t_{w(H)}$ SCLK pulse duration, high                                                   |     | 8    | $\mu\text{s}$ |

| $t_{w(L)}$ SCLK pulse duration, low                                                    |     | 10   | $\mu\text{s}$ |

| $t_{su(STA)}$ Setup time for START condition                                           |     | 9.4  | $\mu\text{s}$ |

| $t_{h(STA)}$ START condition hold time after which the first clock pulse is generated. |     | 8    | $\mu\text{s}$ |

| $t_{su(DAT)}$ Data setup time                                                          |     | 250  | ns            |

| $t_{h(DAT)}$ Data hold time                                                            |     | 0    | $\mu\text{s}$ |

| $t_{su(STOP)}$ Setup time for STOP condition                                           |     | 8    | $\mu\text{s}$ |

| $t_{su(BUF)}$ Time the bus must be free before new transmission can start              |     | 9.4  | $\mu\text{s}$ |

| $t_v$ Clock low to data out valid                                                      |     | 900  | ns            |

| $t_{h(CH)}$ Data out hold time after clock low                                         |     | 0    | ns            |

| $f_{SCL}$ Clock frequency                                                              | 0   | 50   | k $\text{Hz}$ |

## 8 Detailed Description

### 8.1 Overview

The bq77908A battery protection and cell balancing device for Li-Ion and Li-Polymer battery packs monitors 4- to 8-series individual cell voltages and provides fast-acting outputs that may be used to drive N-channel MOSFETs to interrupt the power path. Activation delays and recovery methods for safety conditions are fully programmable in non-volatile memory.

Automatic cell balancing is provided using internal 50-mA cell circuits. A robust balancing algorithm ensures optimum performance by maintaining all cell voltages in balance. Balancing may be configured to operate at all times, only during charge, or can be disabled completely.

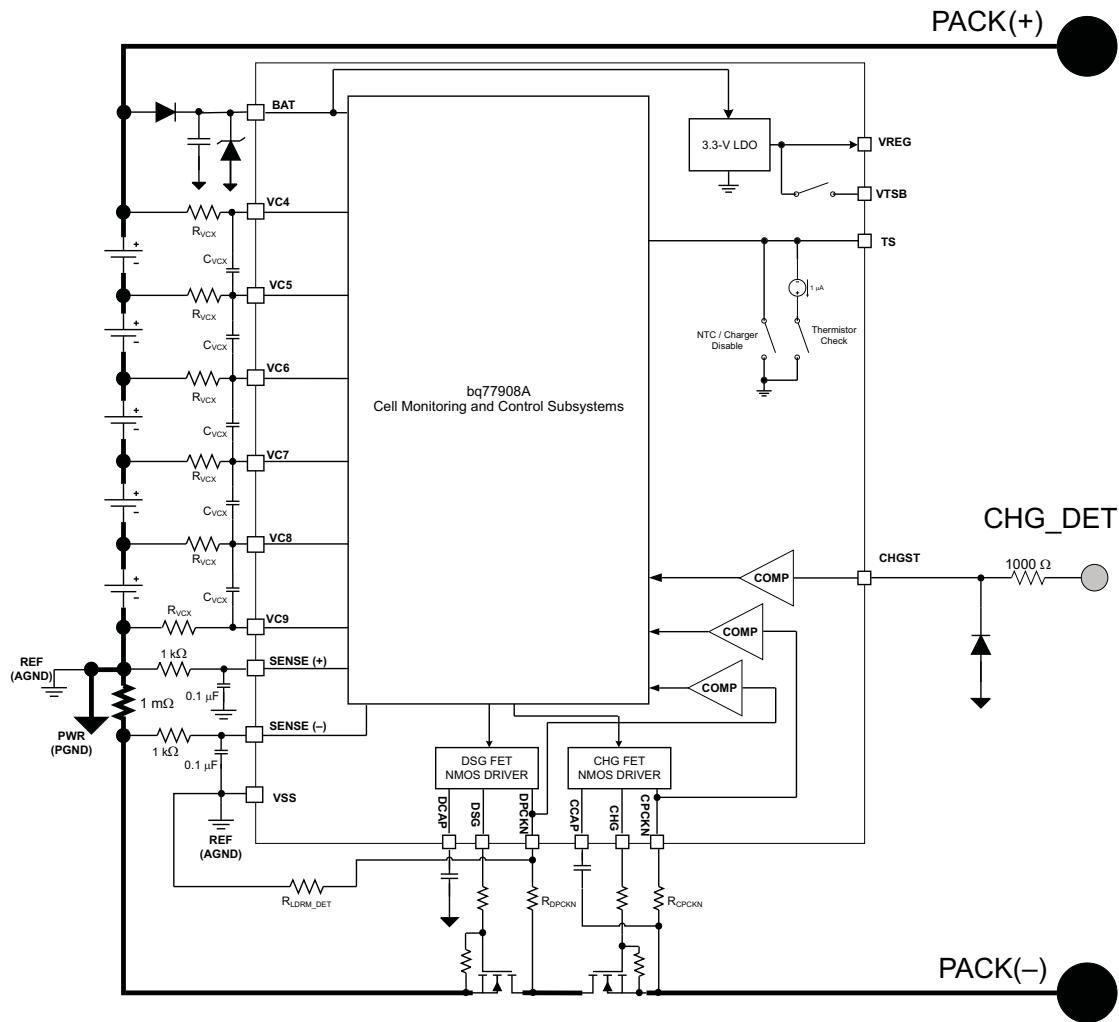

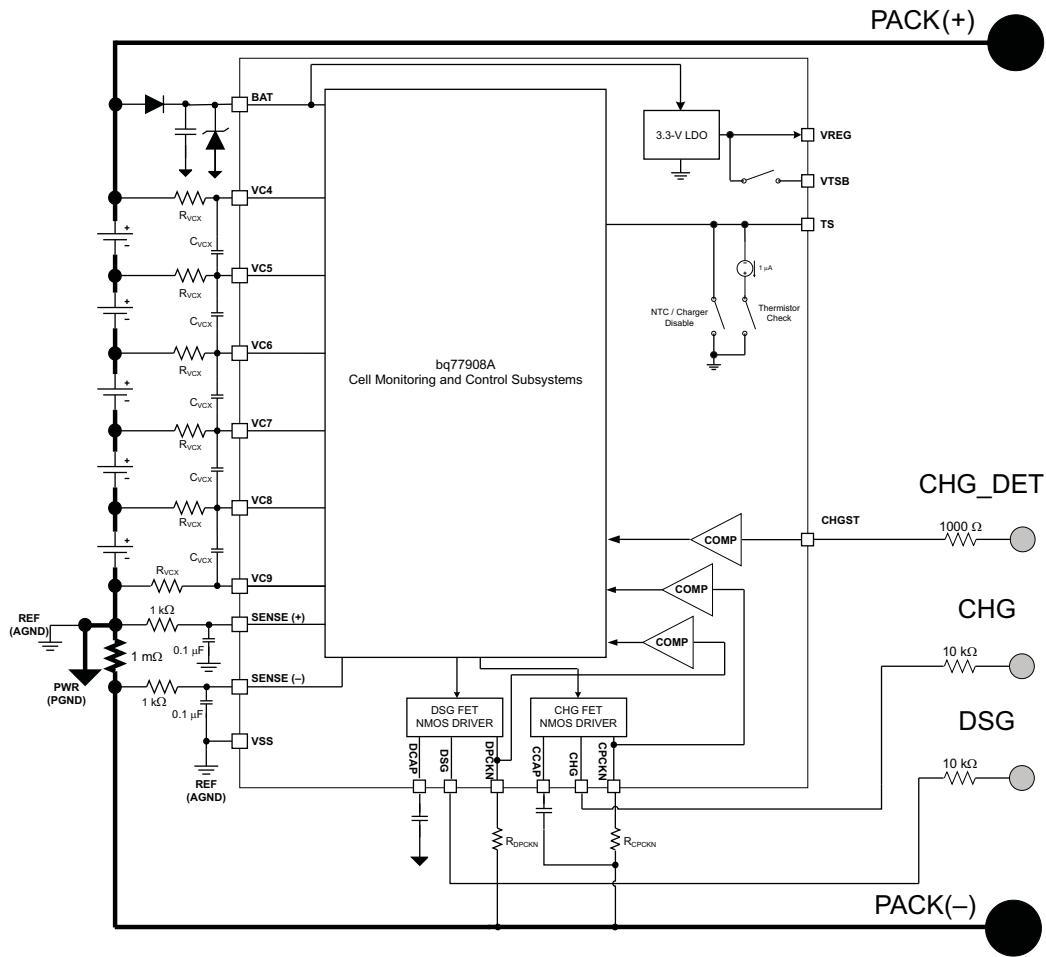

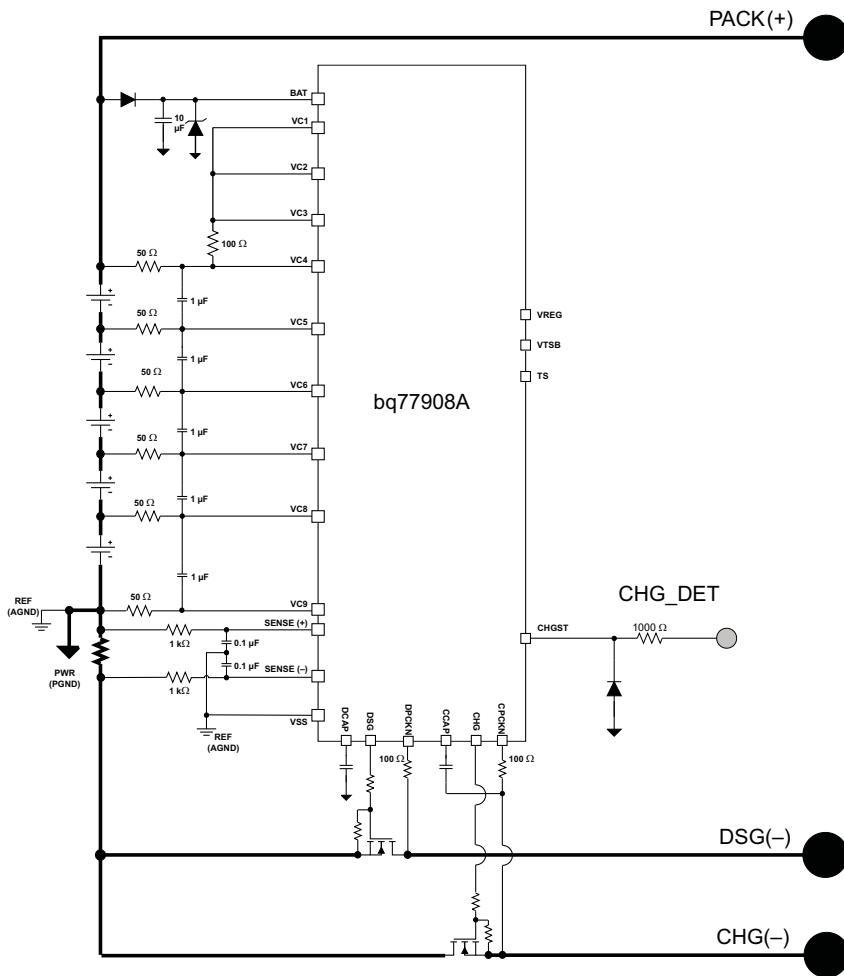

### 8.2 Functional Block Diagram

### 8.3 Feature Description

#### 8.3.1 Programmable Protection Functions

The bq77908A provides the following types of protection functions:

- Cell overvoltage

- Cell undervoltage

- Discharge overcurrent

- Discharge-current short circuit

- Charge-current short circuit

## Feature Description (接下页)

All of the voltage/current and time-delay thresholds can be adjusted for a specific application by programming the EEPROM settings of the IC. The ranges available are shown in [表 2](#).

### CAUTION

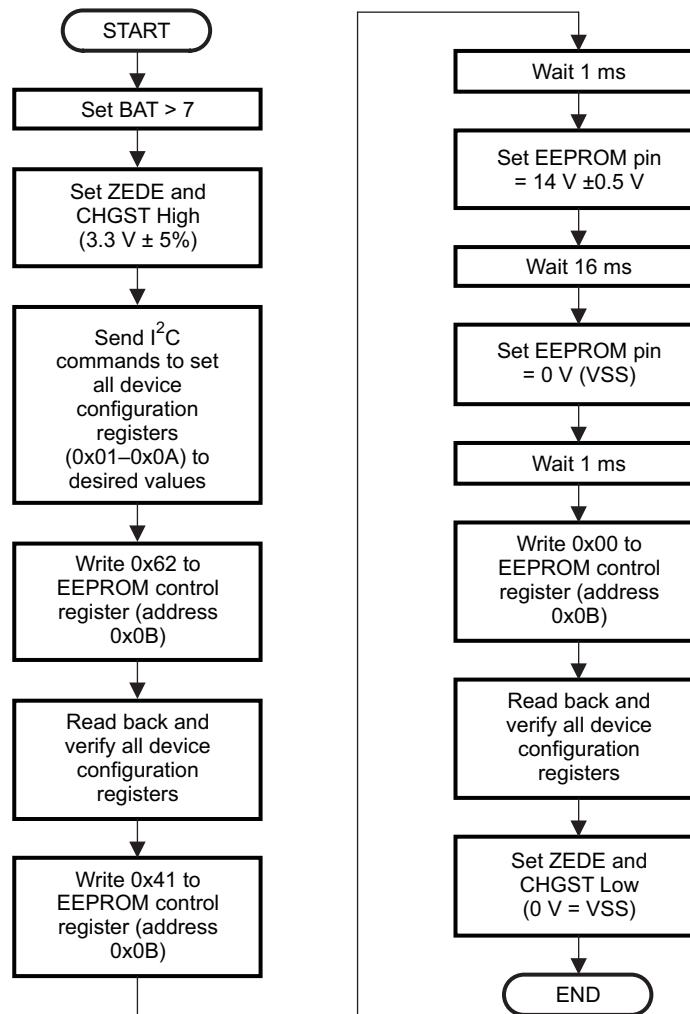

Only a maximum of three EEPROM write cycles per byte should be performed to ensure long-term data retention stability. (For circuit development purposes, the EEPROM may be rewritten many times.)

**表 2. Detection Voltage, Detection Delay Time Summary**

| PARAMETER               |                                                      | RANGE<br>(EEPROM Selected) | MIN         | MAX         | STEP           |

|-------------------------|------------------------------------------------------|----------------------------|-------------|-------------|----------------|

| Overvoltage             | Cell voltage                                         |                            | 2.8 V       | 4.375 V     | 25 mV          |

|                         | Delay                                                |                            | 0.5 s       | 2.25 s      | 0.25 s         |

|                         | Hysteresis                                           |                            | 0 mV        | 300 mV      | 25 mV or 50 mV |

| Undervoltage            | Cell voltage                                         |                            | 1.4 V       | 2.9 V       | 100 mV         |

|                         | Delay                                                |                            | 500 ms      | 32 s        | Binary spacing |

|                         | Hysteresis                                           |                            | 400 mV      | 1600 mV     | 400 mV         |

| Discharge overcurrent   | SENSE(–) pin voltage with respect to SENSE(+) (Low)  |                            | 25 mV       | 100 mV      | 5 mV           |

|                         | SENSE(–) pin voltage with respect to SENSE(+) (High) |                            | 125 mV      | 500 mV      | 25 mV          |

|                         | Delay <sup>(1)</sup>                                 |                            | 20 ms       | 300 ms      | 20 ms          |

|                         |                                                      |                            | 400 ms      | 2000 ms     | 100 ms         |

| Discharge short circuit | SENSE(–) pin voltage with respect to SENSE(+) (Low)  |                            | 40 mV       | 190 mV      | 10 mV          |

|                         | SENSE(–) pin voltage with respect to SENSE(+) (High) |                            | 200 mV      | 950 mV      | 50 mV          |

|                         | Delay <sup>(2)</sup>                                 |                            | 120 $\mu$ s | 960 $\mu$ s | 60 $\mu$ s     |

|                         |                                                      |                            | Slow        | 50 ms       | 1500 ms        |

| Charge short circuit    | SENSE(–) pin voltage with respect to SENSE(+) (Low)  |                            | –10 mV      | –85 mV      | 5 mV           |

|                         | SENSE(–) pin voltage with respect to SENSE(+) (High) |                            | –50 mV      | –425 mV     | 25 mV          |

|                         | Delay                                                |                            | 120 $\mu$ s | 960 $\mu$ s | 60 $\mu$ s     |

(1) If cell balancing during discharge is enabled, then the maximum permitted delay setting is 180 ms.

(2) If cell balancing during discharge is enabled, then the maximum permitted delay setting is 100 ms.

### 8.3.1.1 Cell Overvoltage Detection and Recovery

The CHG FET is turned off if any one of the cell voltages remains higher than  $V_{OV}$  for a period greater than  $t_{OV}$ . As a result, the cells are protected from an overcharge condition. After an overvoltage event occurs, the all cells must relax to less than  $(V_{OV} - V_{HYST})$  to allow recovery.

The  $V_{OV}$ ,  $t_{OV}$ , and  $V_{HYST}$  values can be set via the EEPROM bits OVT, OVD, and OVH.

### 8.3.1.2 Cell Undervoltage Detection and Recovery

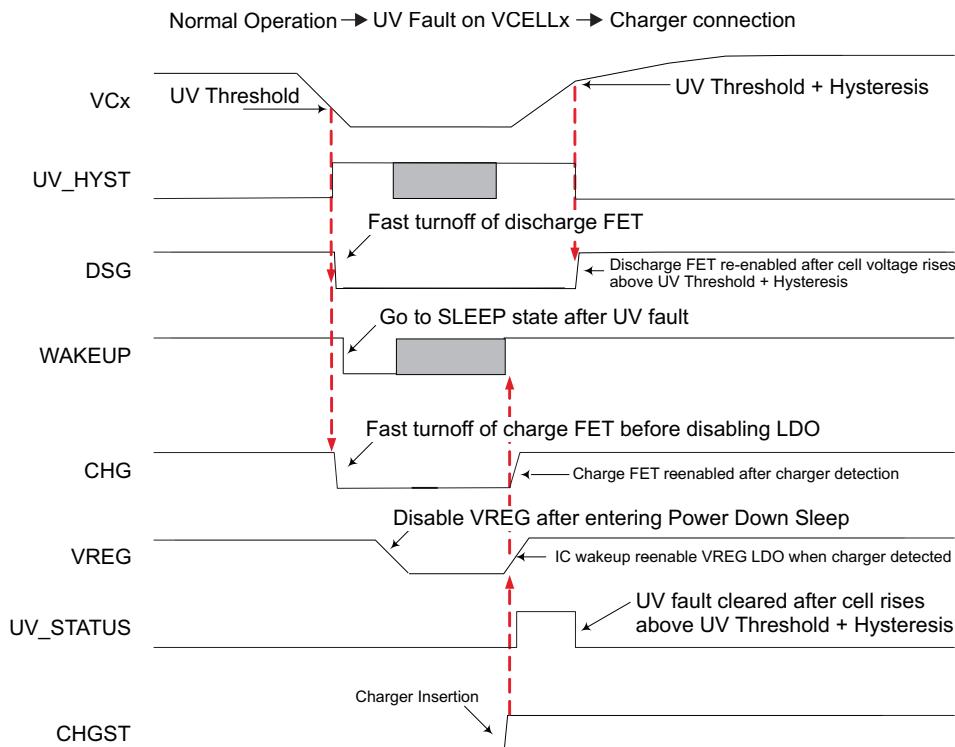

When any one of the cell voltages falls below  $V_{UV}$ , for a period of  $t_{UV}$ , the bq77908A enters the undervoltage protection state. The DSG FET is turned off, and depending on configuration, the device could enter the SHUTDOWN mode. Both  $V_{UV}$  and  $t_{UV}$  can be configured via EEPROM bits UVT and UVD.

The recovery (fault release) is controlled by the EEPROM configuration bit UV\_REC.

If UV\_REC = 0, the DSG FET is re-enabled when **all** the cell voltages increase back above the  $V_{UV}$  threshold level plus the hysteresis value; there is no time-delay part of the recovery. In this case, when UV\_REC = 0 and under high load currents, the  $V_{CELL}$  voltages could recover to  $>UV + hyst$  very quickly, re-enabling the FETs and allowing the high load current to persist. Care should be taken when using this UV\_REC = 0 mode, as the power MOSFETs could oscillate rapidly.

**WARNING**

**To minimize application safety risk, care should be taken to properly set overcurrent and cell undervoltage trip thresholds, because it is possible that a fully charged pack with a continuous high discharge load can oscillate in and out of the undervoltage condition. This may result in overheating of the cells or protection MOSFETs due to the potentially high-duty-cycle operation.**

If  $UV\_REC = 1$ , the DSG FET is re-enabled when **all** the cell voltages increase back above the  $V_{UV}$  threshold level plus the hysteresis value **AND** the load is removed.

Current is interrupted by opening the FETs, and at this point the cell voltages may quickly recover above the  $UV + hyst$  levels if the battery pack is not completely depleted. However, the external load may remain attached. When the external load is removed, the IC detects load removal and reconnects the DSG FET.

If  $UV\_REC\_DLY = 1$  and any cell remains below the  $V_{UV}$  threshold level plus the hysteresis for longer than 8 seconds, the device enters SHUTDOWN mode. If  $UV\_REC\_DLY = 0$ , the device does **not** enter the SHUTDOWN mode from the cell undervoltage fault condition.

The LDO is turned off during the SHUTDOWN mode. Insertion into a charger is required to recover from the SHUTDOWN mode.

Charger detection methods are discussed in later sections, such as [Application Information](#).

#### **8.3.1.3 Overcurrent in Discharge (OCD) Detection**

The OCD detection feature senses an overload current by measuring the voltage across the sense resistor. When an overload condition is detected, both of the power FETs are disabled to prevent damage to the cells and FET components. Criteria for fault recovery depend on the state of the SOR (EEPROM bit). Overcurrent trip level ( $V_{OCD}$ ) and blanking time delay ( $t_{OCD}$ ) are programmable via EEPROM bits OCDT and OCDD to match individual application requirements.

#### **8.3.1.4 Short Circuit in Discharge (SCD) Detection**

The SCD detection function senses severe discharge current by measuring the voltage across the sense resistor. When a short circuit is detected, both of the power FETs are disabled to prevent damage to the cells and FET components. Criteria for fault recovery depend on the state of the SOR (EEPROM bit). Short-circuit trip level ( $V_{SCD}$ ) and blanking time delay ( $t_{SCD}$ ) are programmable via EEPROM bits SCDT and SCDD to match individual application requirements.

#### **8.3.1.5 Load Removal Detection/OCD and SCD Fault Recovery**

The part includes an internal high-impedance connection between the DPCKN and VSS pins of approximately  $1.5\text{ M}\Omega$ . An external load (for example power tool motor winding), if still connected to the pack terminals, would present a very low impedance relative to the high internal pulldown resistance.

**注**

If the external load presents additional capacitance, then an external pulldown may be required between the DPCKN and VSS pins. This extra pulldown does not increase battery load current when the external load is removed.

If the DSG power FET is disabled after an overload or short-circuit event, the voltage at the DPCKN is approximately equivalent to the BAT voltage potential while an external load (for example, power tool motor) is present at the pack terminals. When the external load is removed, the high-value internal resistance pulls down the DPCKN potential to the internal VSS level. An internal comparator monitors the DPCKN terminal voltage during the protection state. DPCKN must rise above  $V_{OPEN\_LOAD}$  within approximately 75  $\mu\text{s}$  for the load to be detected. When the DPCKN voltage falls to  $< V_{OPEN\_LOAD}$  (approximately 2 V), the load removal is detected. Fault recovery from an OCD or SCD event depends on the state of the SOR EEPROM bit.

If  $SOR = 0$ , the FETs are re-enabled only after the external load removal is detected.

If  $SOR = 1$ , the FETs are re-enabled after the load is removed **and** a charger insertion is detected.

(Details of charger presence detection methods are discussed in later sections.)

### 8.3.1.6 Short Circuit in Charge (SCC) Detection

The SCC detection function senses severe charge current by measuring the voltage across the sense resistor. In this case, the voltage is negative (opposite polarity of OCD and SCD detection). When a short circuit is detected, both of the power FETs are disabled to prevent damage to the cells and FET components. Short-circuit trip level ( $V_{SCD}$ ) and blanking time delay ( $t_{SCD}$ ) are programmable via EEPROM bits SCCT and SCCD to match individual application requirements.

注

The current sensing element must be located along a common charge and discharge path in order to protect against both charge and discharge current faults. This is particularly important to note for parallel FET configurations or configurations that combine the FET with the sense element.

### 8.3.1.7 Short Circuit in Charge Recovery

An SCC fault is cleared after charger removal is detected. (See later sections for details of charger insertion and removal detection methods.)

## 8.3.2 Fixed Hardware Fault-Protection Functions

The bq77908A provides a number of fixed protection settings for hardware faults as listed:

- Open-cell connection

- Pack voltage *Brownout* condition—power FET protection

- Charger-enable temperature range

- Open thermistor connection

- Shorted thermistor connection

- Overtemperature protection

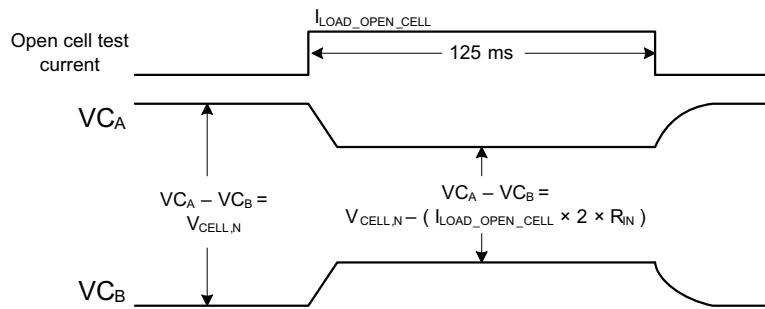

### 8.3.2.1 Open-Cell Connection

A mechanical or assembly fault in the pack can cause a high-impedance or broken connection between the IC cell sense pins and the actual cells. During operation, the bq77908A periodically checks the validity of the individual cell voltage reading by applying a micropower pulsed load across each cell. If the connection between the pin and the cell is opened, the apparent cell voltage will collapse and a fault (permanent failure) condition is detected. The open-cell detection reading is taken at a time interval of  $t_{OPEN\_CELL\_CHECK}$ , as specified in the parametric tables. Recommended external filter-capacitor maximum value is also listed in the *Recommended Operating Conditions*. Because an open-cell fault may be considered as a permanent failure, the fault detection logic must detect two consecutive open-cell conditions prior to activating the protection condition for an open-cell fault. Due to the nature of open-cell fault conditions, other *apparent* faults may be observed during an open-cell condition.

Summary of open-cell detection-logic operation:

- For an N-cell battery pack, the bq77908A always protects (by opening the FETs) in some manner within the  $2 \times N \times t_{OPEN\_CELL\_CHECK}$  time frame (sampling interval is  $t_{OPEN\_CELL\_CHECK}$ , and two successive open-cell faults are required to avoid nuisance tripping).

- Because an open-cell connection results in a floating VCx input, a UV or an OV fault may be detected before the open-cell fault due to their shorter fault filter times. Furthermore, the OV or UV condition may not be stable and the fault may recover during the open-cell check interval (that is, the FETs may toggle). In all cases the open-cell fault is detected within the open-cell fault filter time and the FETs are shut off until the recovery conditions are satisfied.

- The LDO shuts down following the detection of an open-cell fault, provided that a charger is not detected. When the pack is awakened following this, the open-cell fault is initially cleared (FETs closed) and must be re-evaluated over the filter time before the fault is again registered. Charger detection inhibits LDO shutdown; however, once the charger is disconnected, the LDO then shuts down, provided that the recovery conditions have not yet been satisfied.

### 8.3.2.2 Additional Fault Protection Functions

The brownout protection functionality is discussed in the [IC Internal Power Control](#) section of this document. Thermistor fault detection, charger/thermistor interface and control are discussed in the [Application Information](#) section.

### 8.3.3 IC Internal Power Control

#### 8.3.3.1 Power-On Reset/UVLO

On initial application of power to the BAT pin, the IC internal power supply rail begins to ramp up. The IC contains an internal undervoltage lockout (UVLO)/power-on reset (POR) circuit that prevents operation until the BAT voltage is sufficient to ensure predictable start-up and operation. All power for the IC internal circuitry is derived from the BAT pin. The UVLO/POR start-up threshold is specified in the parametric table as  $V_{STARTUP}$ . Once the BAT voltage has exceeded this level, the internal LDO regulator and control circuitry are enabled and continue to operate even if BAT falls below  $V_{STARTUP}$ . If the BAT pin falls below the operational range given under *Recommended Operating Conditions*, the device powers down.

On initial power up, the state of the output MOSFET drive pins (CHG and DSG) is indeterminate until the voltage on BAT reaches the  $V_{STARTUP}$  threshold. No load should be applied during this period.

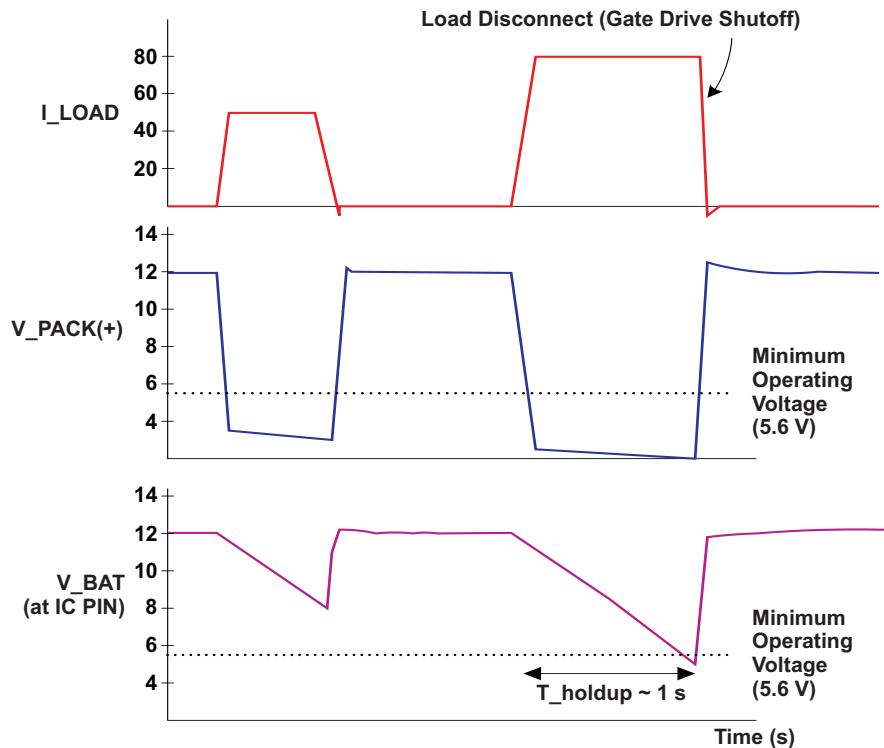

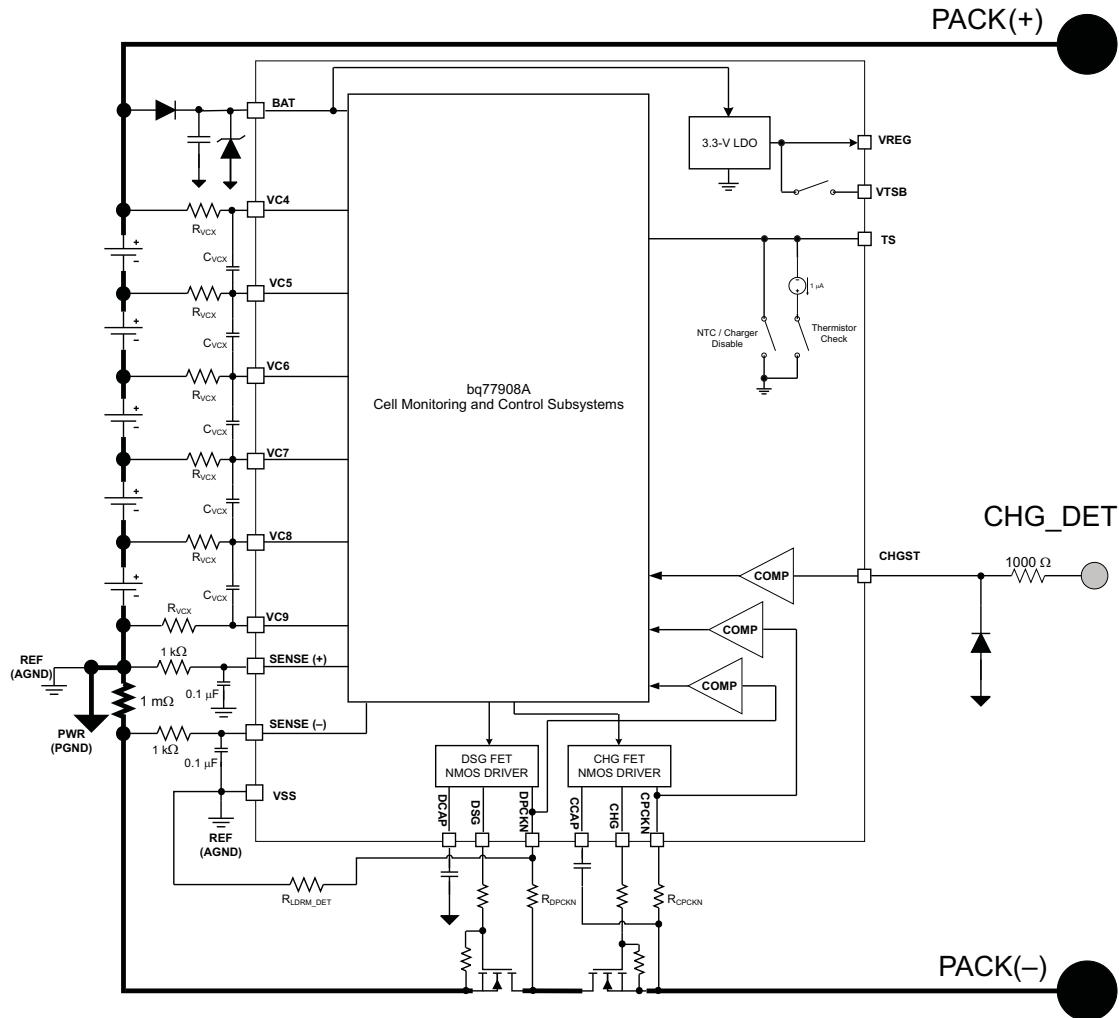

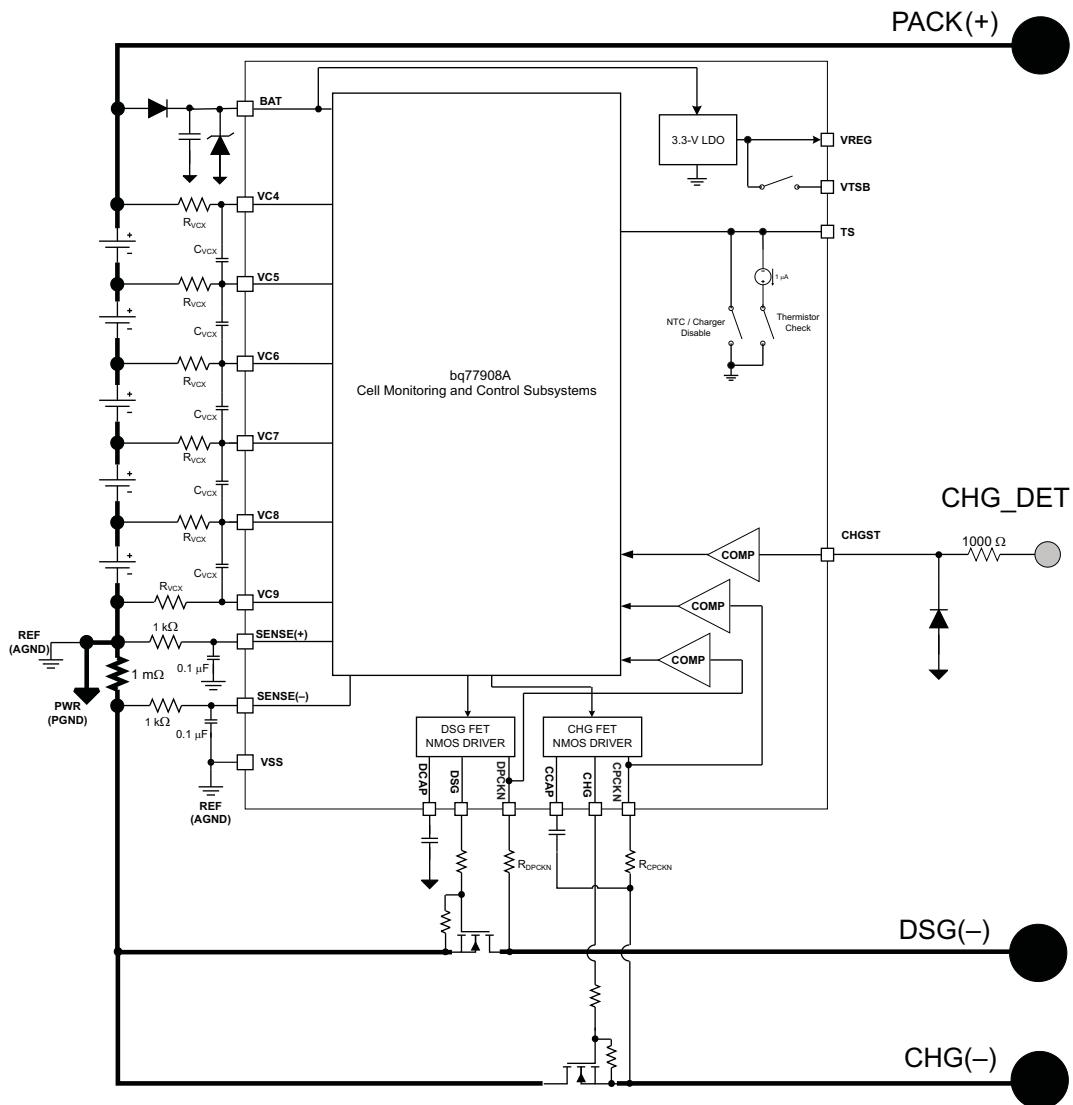

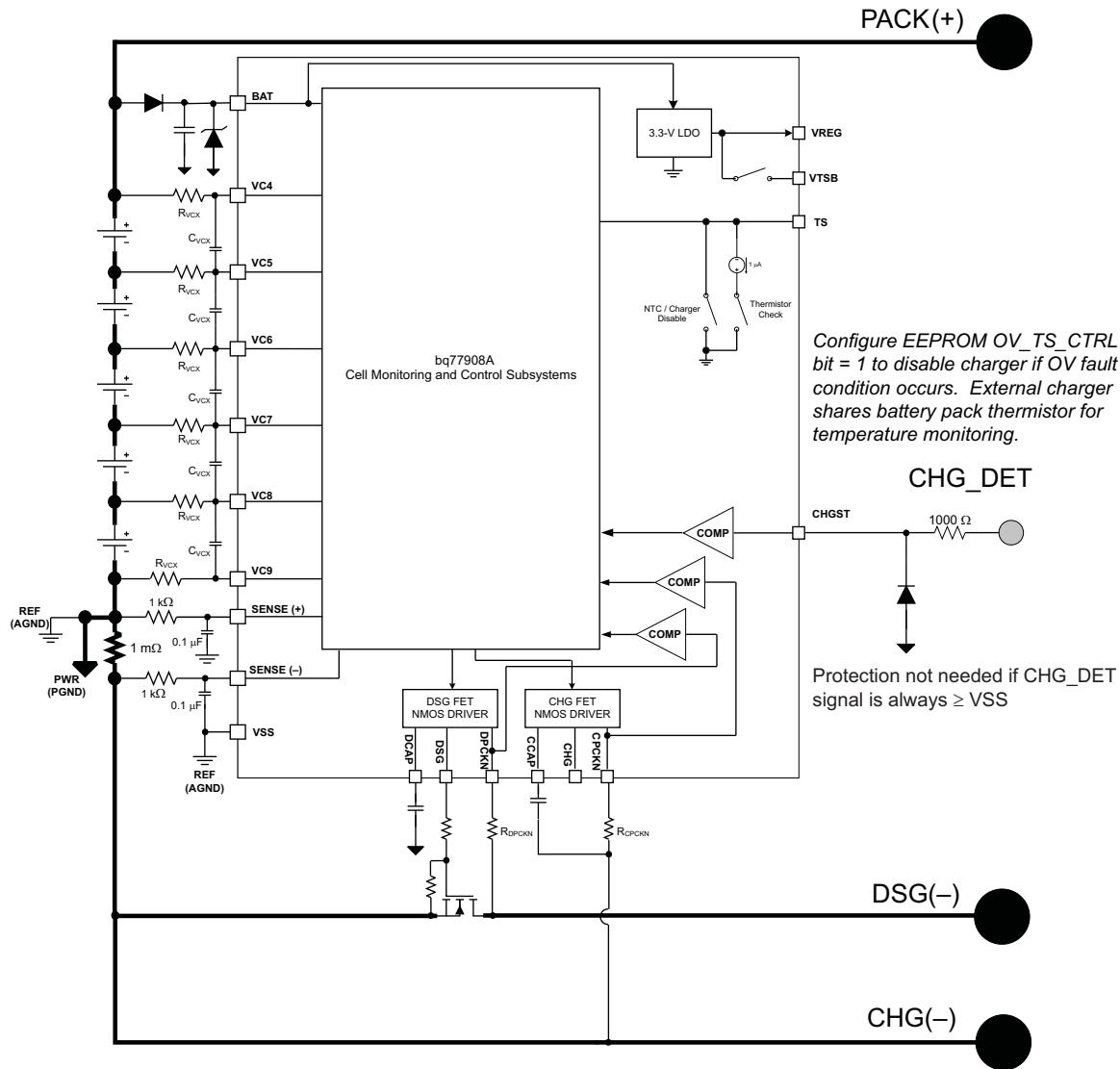

#### 8.3.3.2 BAT Holdup/Brownout Protection Functionality

The BAT pin is used to power the IC internal circuitry, and should be supplied through a diode and held up with a capacitor placed near the IC as shown in the application diagrams (see [图 2](#)). The external diode prevents discharge of the IC power rail during external transients on the PACK(+) node.

This allows the bq77908A to maintain proper control of the pack and system during brownout conditions.

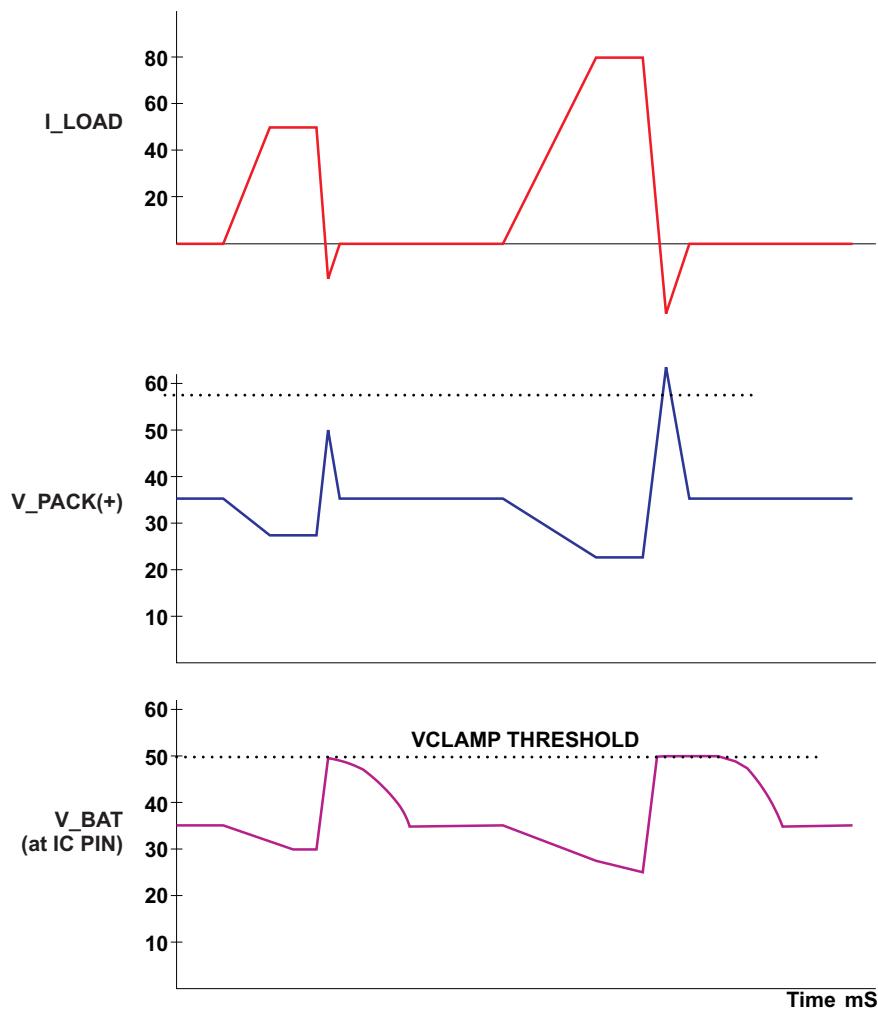

Brownout is defined as a situation during which the stack voltage collapses to a voltage below the minimum operating voltage of the IC (~5.6 V) for a short duration (~1 s). A typical application case is shown below. Additional examples are provided in the [Application Information](#) section later in this document.

If there are short-duration sags in the PACK(+) voltage (typically due to high load transients), the operating current for the IC is momentarily provided by the external capacitor. Assuming that there is no external load on the VREG (LDO output) pin, the IC draws approximately 50- $\mu$ A average current from the capacitor. The holdup time before the IC goes into SHUTDOWN mode depends on the initial pack voltage. For a normal *low battery* initial condition using a 4-cell stack, the cells may be in the range of 3 V/cell or 12 V total for the pack voltage. If a load transient occurs at this point, and the pack voltage sags down to below the IC POR threshold, the voltage at the BAT pin is held above 5 V for slightly greater than one second using a 10- $\mu$ F capacitor.

Waveforms typical of a load transient during low pack voltage conditions are shown as follows. In the first load transient, the PACK(+) rail momentarily collapses but the load is disconnected before the holdup time limit is exceeded. In the second load transient, the load is left on for a duration exceeding the holdup capability, so when the IC operating voltage reaches the gate-drive undervoltage limit, the external power FETs are disabled to disconnect the load.

图 1. Load Transient Examples

### 8.3.3.3 BAT Voltage Peak Detection/Transient Suppression

The use of an external diode and holdup capacitor allows the IC to provide controlled operation during brownout conditions. However, when the battery pack is at a high level, a different issue must be considered.

During normal operation of power equipment, load transients may induce high-voltage pulses on the PACK(+) rail that exceed the steady-state dc voltage output of the battery pack. In some cases, these transient voltages can exceed the battery rail by several volts. The voltage at the BAT pin may be *held up* to these higher voltages for a longer duration because the diode prevents the capacitor from discharging back into the cell stack after the transient pulses decay. When the dc level of the battery pack voltage is near 35 Vdc, high-current load disconnection may cause transients that would exceed the absolute maximum ratings of the device.

The BAT pin incorporates an internal Zener clamp that dissipates any transient voltage at the BAT pin that exceeds 50 V. This internal clamp has very limited energy absorption ability. Therefore, additional external circuitry is required for transient suppression, depending on the application environment. A Zener or equivalent rated at  $<5\ \Omega$  and  $>3\text{ W}$  is recommended.

### 8.3.3.4 BAT Voltage Rate of Change

In addition to providing the holdup function, the filter components at the BAT pin serve to limit the maximum voltage rate of change. The voltage rate of change at the BAT pin should be limited to a maximum of 1 V per  $\mu\text{s}$  in order to prevent unwanted device shutdown.

图 2. Example 5-Cell, Series FET Configuration Schematic Using bq77908A

Waveforms illustrative of load transients during high pack voltage conditions are shown here.

图 3. High-Voltage Load-Transient Waveforms

#### 8.3.3.5 FET Gate Drive Control

As noted in the previous section, the BAT voltage at the IC pin is held up slightly longer than the external PACK(+) voltage using the external diode/capacitor to feed the BAT rail. Thus, if the BAT pin voltage at the IC sags, the external voltage sag will have exceeded the holdup time, and the IC is no longer able to operate for an extended period of time. At this point, the DSG and CHG gate drive outputs are actively driven low. The FET driver stages use two additional external capacitors (connected at the CCAP and DCAP pins) to maintain a local power reservoir dedicated to the gate drive circuitry, as the system (BAT) voltage may be collapsing during the time that the FETs are being turned off. The FETs are turned off when the voltage at the CCAP and/or DCAP pins falls below  $V_{GATE\_UV}$ .

By turning off the FETs quickly, the system avoids the condition of insufficient gate drive due to low battery voltage.

注

If the FET gate drive is not high enough, the power components may not be in their linear operating region, and could overheat due to resistive losses at high load currents.

In the case of a system undervoltage condition, both FETs are disabled within 500  $\mu$ s maximum; in all cases the FET fall time is less than fall time specified in the *Electrical Characteristics* section (FET Drive). During initial power up, once the UVLO threshold has been reached and the IC powers up fully, the rise time of the FET gate drive signal is also < 200  $\mu$ s. This assumes a nominal gate capacitance of 50 nF as specified in the *Electrical Characteristics* tables.

**注**

Selection of power FETs should consider the resistive losses that may occur during the undefined voltage range during power up from a complete collapse of battery voltage and holdup capacitance.

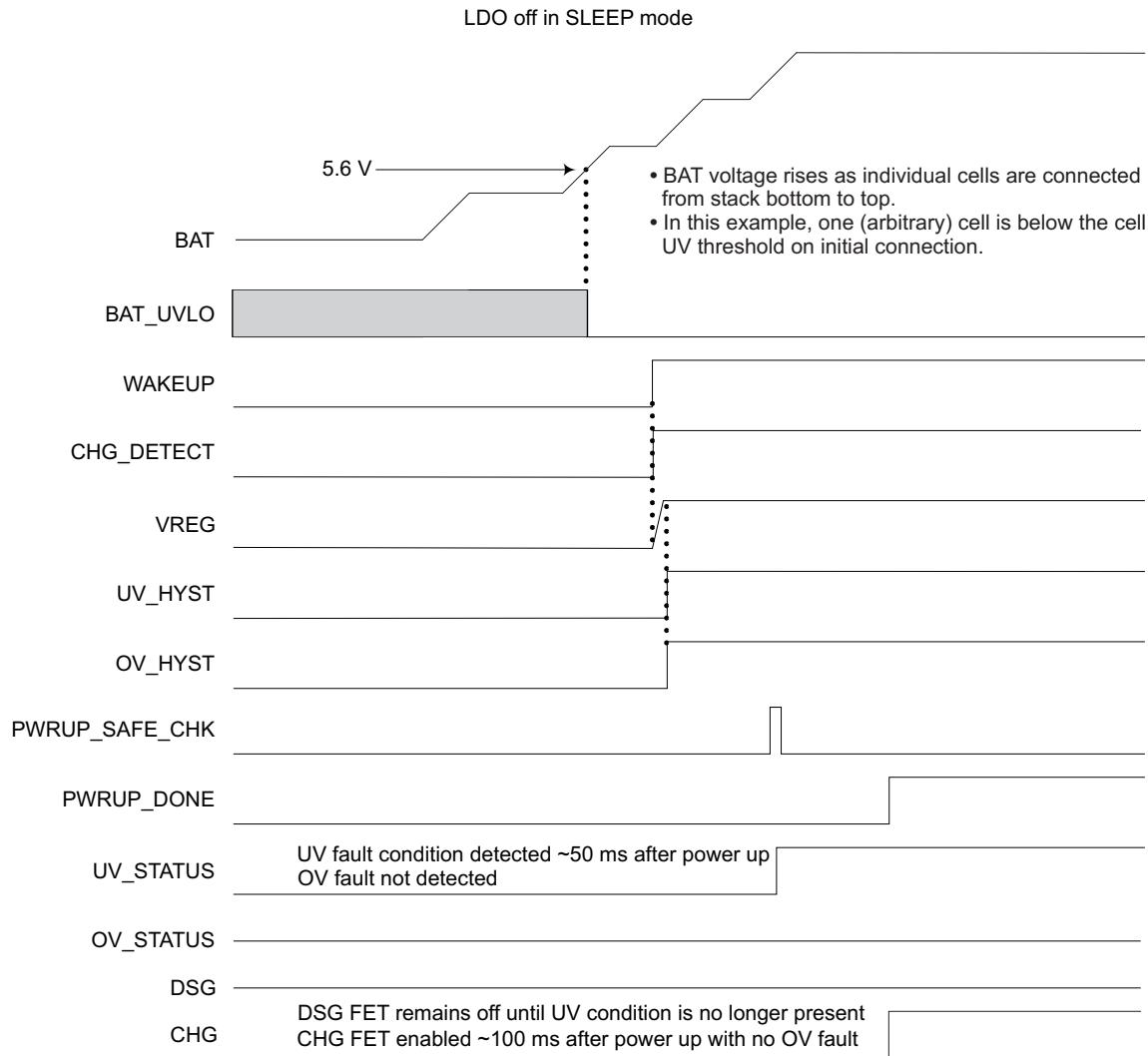

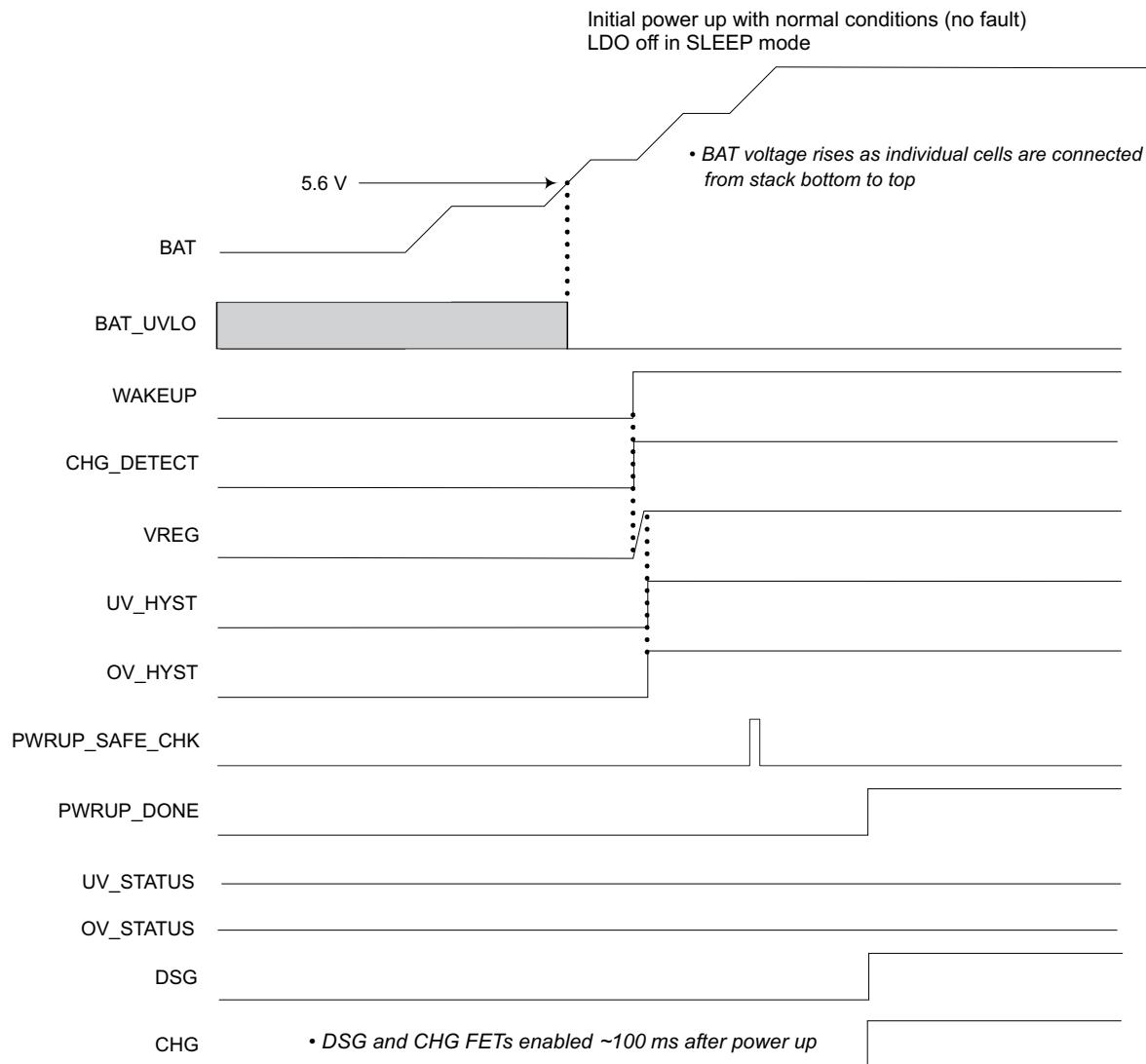

### 8.3.4 Initial Power Up

#### 8.3.4.1 Cell Connection

The IC design allows connection of the cells in any order. For EEPROM programming, only the VSS and BAT terminals must be connected to allow the device to communicate using the serial communication interface.

For normal pack assembly, the recommended connection procedure is to start with the VSS connection, followed by the (+) terminal of the lowest (most negative) cell, and continuing up the stack to the top (most positive) cell. The BAT voltage shown in [Start-Up Timing](#) assumes this connection sequence is used.

#### 8.3.4.2 Power-Up Sequence and Continuous Fault-Detection Logic

The bq77908A goes through a fixed set of safety checks on each power-up sequence. The same checks are performed on each recovery cycle from the SHUTDOWN state (after a charger is detected).

For each power up, the following tests are made. If any of the conditions indicate a fault, the IC goes into the appropriate protection state. External connections may be required for fault recovery (such as load removal or insertion into charger). *The device goes through a power-up sequence in < 100 ms, assuming no faults exist.*

After the release of the internal digital reset, the logic begins a power-up safety check. Two internal signals, designated PWRUP\_SAFE\_CHK and PWRUP\_DONE, control the sequence.

When PWRUP\_DONE is low, the following conditions are forced:

1. CHG and DSG external pins/gate drive signals are low.

2. UV\_HYST = HI (internal logic signal—use hysteresis level above UV threshold to clear fault)

3. OV\_HYST = HI (internal logic signal—use hysteresis level below OV threshold to clear fault)

After 50 ms of time has elapsed, a pulse of PWRUP\_SAFE\_CHK performs a check of each of the following circuits (with all time delays disabled):

1. UV comparator

2. OV comparator

3. OCD comparator

4. SCD comparator

If a fault condition was found for any of the above protection circuits, an internal fault status bit is set. For another 50 ms, the circuit has a chance to recover if the sample was corrupted. At the end of 100 ms, the PWRUP\_DONE signal is released. If no faults exist, the CHG, DSG, UV\_HYST, and OV\_HYST return to their normal-mode state.

Several of the protection circuits were not included in the power-up sequence (SCC, OT, TS, TO, OC). These faults are checked after the power-up sequence is completed.

**注**

This check is only performed on a power up from LDO-off or a digital reset occurring (that is, POR state).

### 8.3.4.3 Start-Up Timing