ZHCSI92D - MAY 2018 - REVISED NOVEMBER 2020

具有增强处理能力和低功率损耗的 TAS5805M 23W、无电感器、 数字输入、立 体声、闭环 D 类音频放大器

# 1 特性

• 支持多路输出配置

TEXAS

INSTRUMENTS

- 2.0 模式 (8Ω, 21V, THD+N=1%) 下可提供 2 × 23W 的功率

- 单声道模式 (4Ω, 21V, THD+N=1%) 下可提 供 45W 的功率

- 优异的音频性能

- 1W、1kHz、PVDD = 12V 条件下 THD+N ≤ 0.03%

- SNR ≥ 107dB(A 加权),噪声级别 < 40µV<sub>RMS</sub>

- 低静态电流(混合调制)

- PVDD = 13.5V 且使用 22µH + 0.68µF 滤波器的 情况下为 16.5mA

- 灵活的电源配置

- PVDD: 4.5V 至 26.4V

- DVDD 和 I/O: 1.8V 或 3.3V

- 灵活的音频 I/O

- I<sup>2</sup>S、LJ、RJ、TDM、3 线数字音频接口(无需 MCLK)

- 支持 32、44.1、48、88.2、96kHz 采样速率

- 可支持音频监控、子通道或回声消除的 SDOUT

- 增强的音频处理能力

- 多频带高级 DRC 和 AGL

- 2×15 个 BQ

- 热折返、直流阻断

- 输入混合器、输出交叉开关

- 电平计

- 5个 BQ + 单频带 DRC + THD 管理器 (用于低 音炮通道)

- 声场定位器 (SFS) 选项

- 集成式自保护

- 邻近的引脚对引脚短路不会造成损坏

- 过流错误 (OCE)

- 过热警告 (OTW)

- 过热错误 (OTE)

- 欠压/过压锁定 (UVLO/OVLO)

- 可轻松进行系统集成

- I<sup>2</sup>C 软件控制

- 解决方案尺寸更小

- 与开环器件相比,所需的无源器件更少

- 对于 PVDD ≤ 14V 的大多数情况,可实现无 电感器操作(铁氧体磁珠)

# 2 应用

• LCD 电视、OLED 电视

- 无线扬声器、智能扬声器(带语音助理)

- 条形音箱、有线扬声器、书架立体声系统

- 台式计算机、笔记本电脑

- AV 接收器、智能家居和物联网电器

## 3 说明

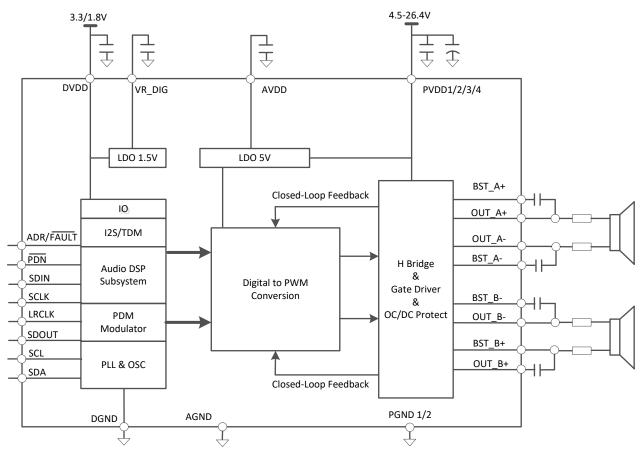

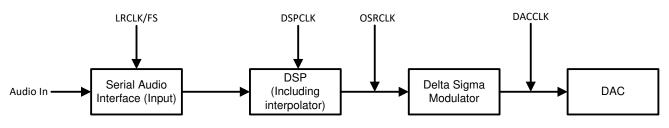

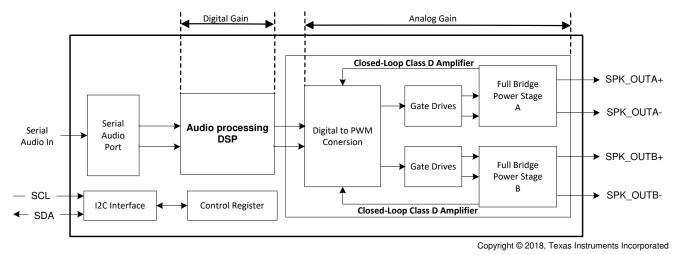

TAS5805M 是一款高效立体声闭环 D 类放大器,可提 供具有低功率耗散和丰富声音的低成本数字输入解决方 案。该器件的集成音频处理器和 96kHz 架构支持高级 音频处理流程 ( 包括 SRC、每通道 15 个 BQ、音量控 制、音频混合、3频带4阶 DRC、全频带 AGL、THD 管理器和电平计)。

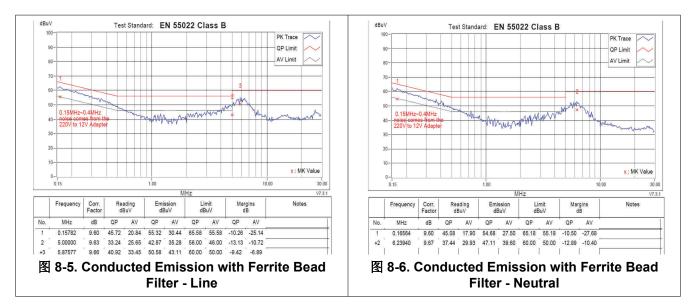

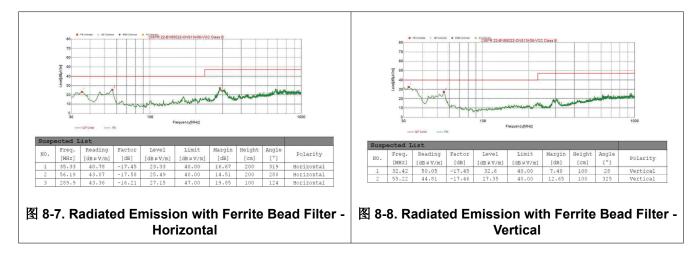

TAS5805M 采用 TI 的专有混合调制方案, 消耗超低的 静态电流(13.5V PVDD 下为 16.5mA),从而能够延 长便携式音频应用中的电池寿命。凭借先进的 EMI 抑 制技术,设计人员可以利用廉价的铁氧体磁珠滤波器来 减小布板空间并降低系统成本。

| 器件信息     |                   |               |  |

|----------|-------------------|---------------|--|

| 器件型号     | 封装 <sup>(1)</sup> | 封装尺寸(标称值)     |  |

| TAS5805M | TSSOP (28) PWP    | 9.7mm × 4.4mm |  |

如需了解所有可用封装,请参阅产品说明书末尾的可订购产品 (1) 附录。

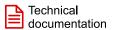

简化版方框图

# **Table of Contents**

| 1 | 特性1                                   |

|---|---------------------------------------|

| 2 | 应用1                                   |

|   | 说明1                                   |

|   | Revision History2                     |

|   | Pin Configuration and Functions       |

| 6 | Specifications                        |

|   | 6.1 Absolute Maximum Ratings7         |

|   | 6.2 ESD Ratings7                      |

|   | 6.3 Recommended Operating Conditions7 |

|   | 6.4 Thermal Information               |

|   | 6.5 Electrical Characteristics8       |

|   | 6.6 Timing Requirements 11            |

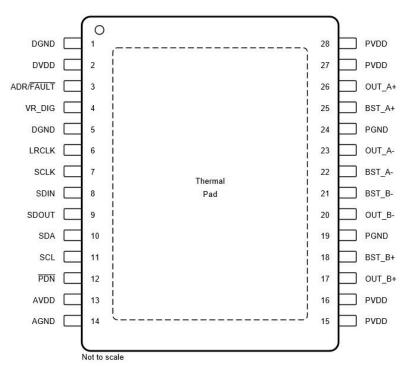

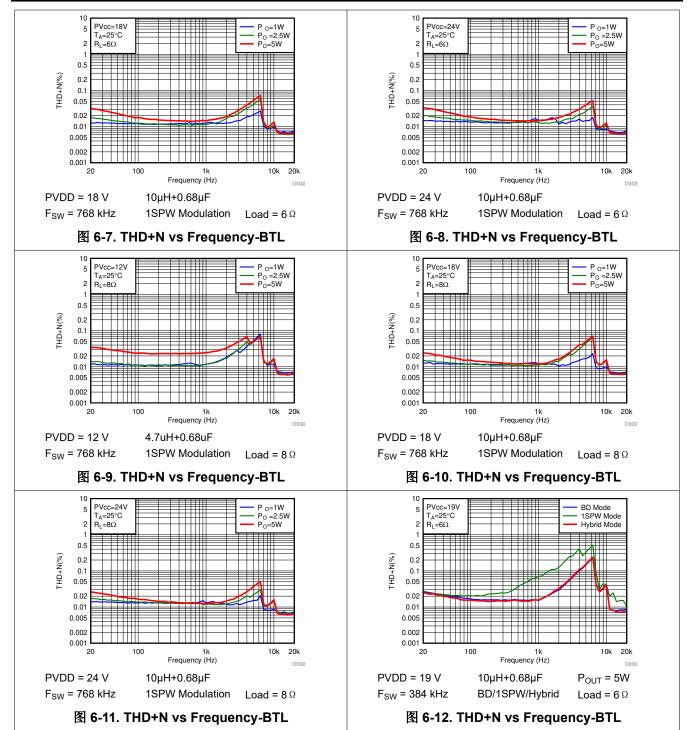

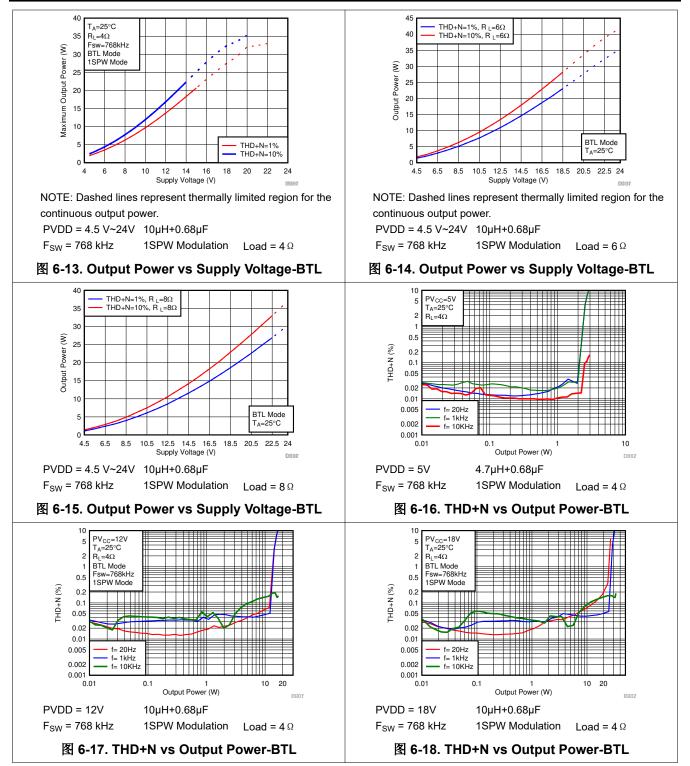

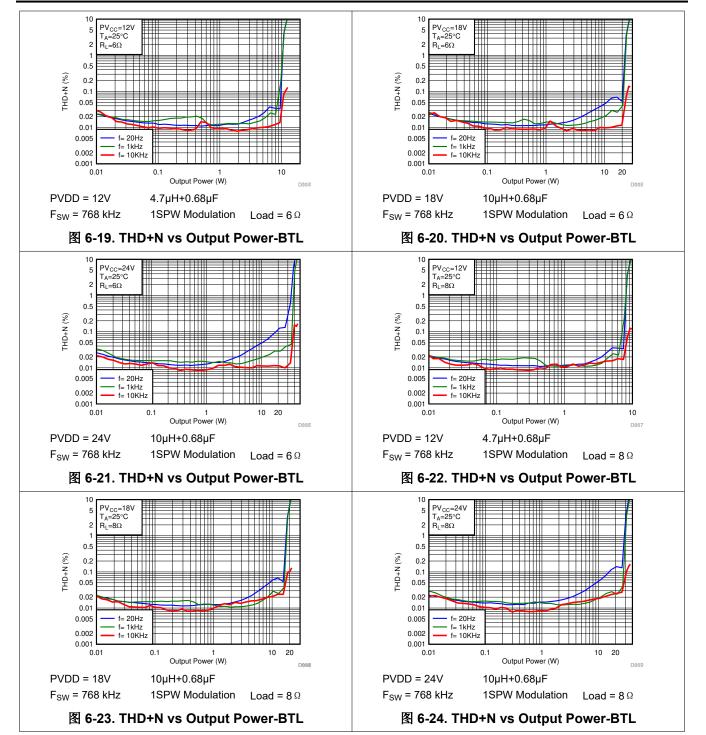

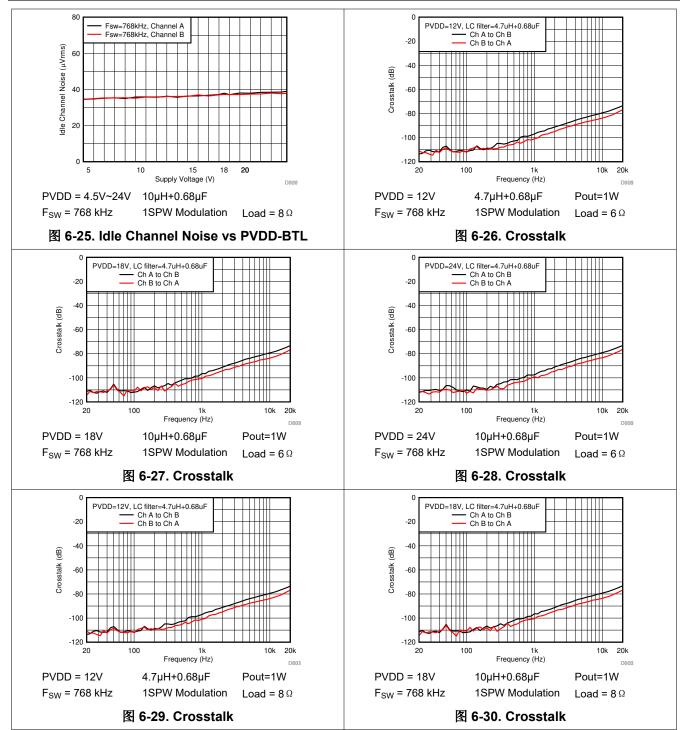

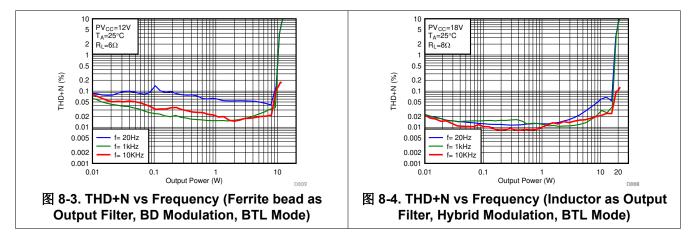

|   | 6.7 Typical Characteristics12         |

| 7 | Detailed Description                  |

|   | 7.1 Overview                          |

|   | 7.2 Functional Block Diagram          |

|   | 7.3 Feature Description               |

|   |                                       |

| 7.4 Device Functional Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| 7.5 Programming and Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| 7.6 Register Maps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 47 |

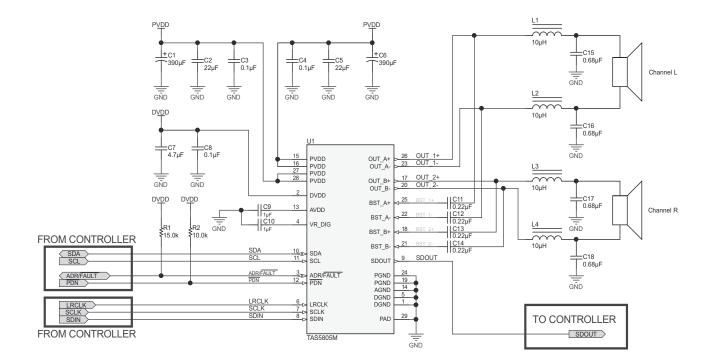

| 8 Application and Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 77 |

| 8.1 Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 77 |

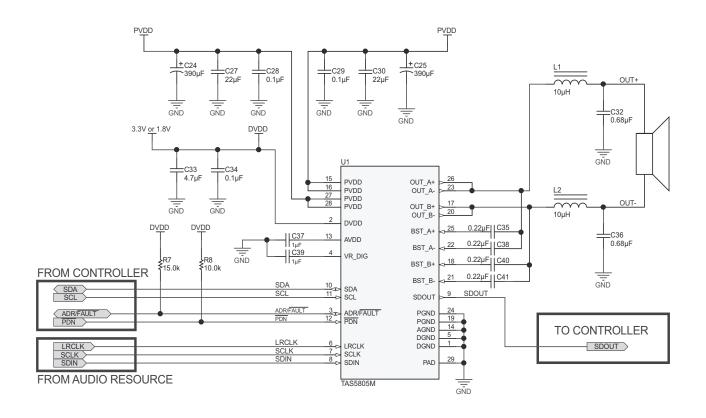

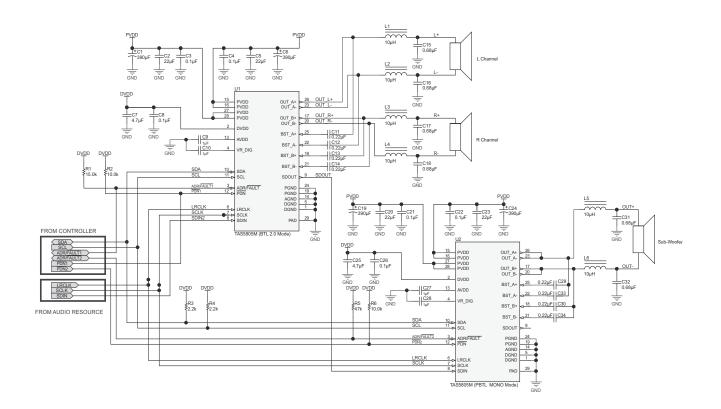

| 8.2 Typical Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

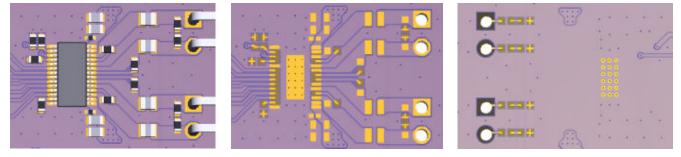

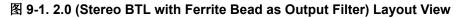

| 9 Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| 9.1 Layout Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 89 |

| 9.2 Layout Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 10 Device and Documentation Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 92 |

| 10.1 Device Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 10.2 Receiving Notification of Documentation Updates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 93 |

| 10.3 支持资源                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 93 |

| 10.4 Trademarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 93 |

| 10.5 静电放电警告                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 93 |

| and the second |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

**4 Revision History** 注:以前版本的页码可能与当前版本的页码不同

| CI | nanges from Revision C (December 2018) to Revision D (November 2020)                                   | Page |

|----|--------------------------------------------------------------------------------------------------------|------|

| •  | Added note 1 to the Recommended Operating Conditions                                                   | 7    |

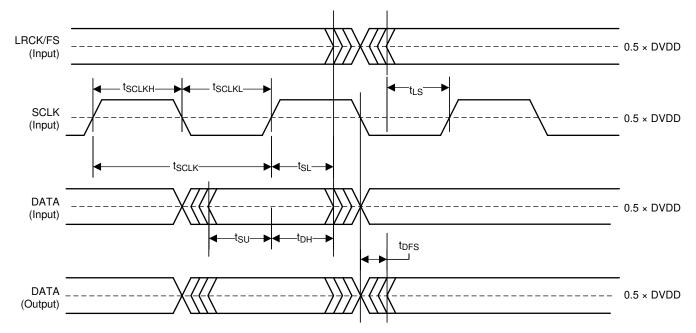

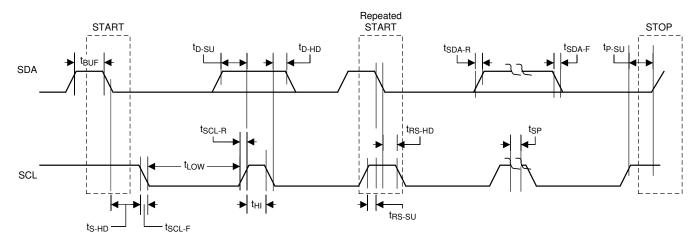

| •  | Added capacitve load for each bus line, Cb = 400 pf to the I2C timming parameters in the <i>Timing</i> |      |

|    | Requirements                                                                                           | 11   |

| •  | Change the I2C BUS Timming-Standard. Data Hold Time max value from 900 ns to 3450 ns in the Timi       | ing  |

|    | Requirements                                                                                           | 11   |

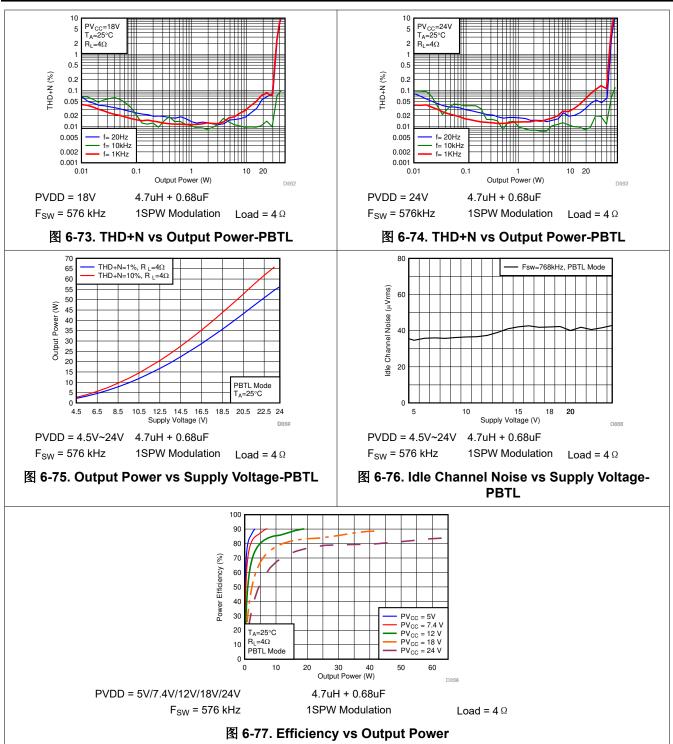

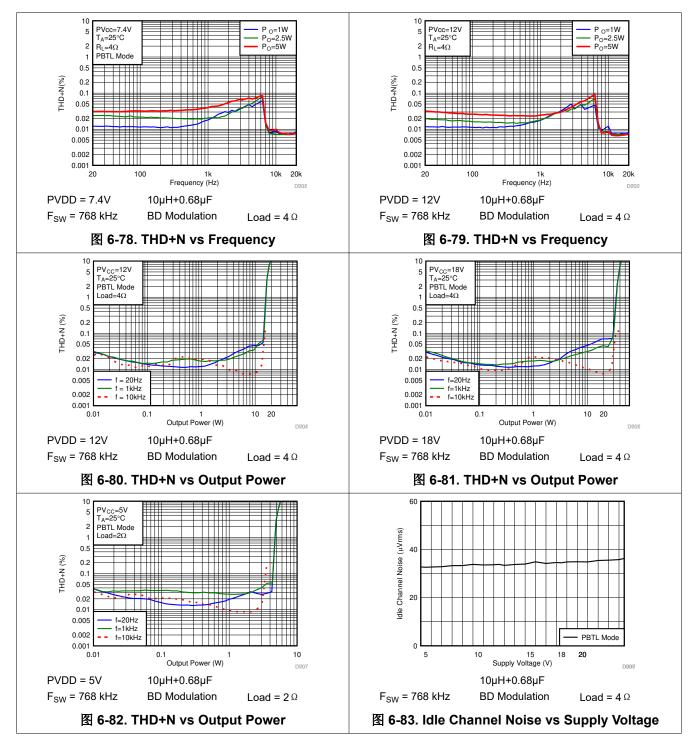

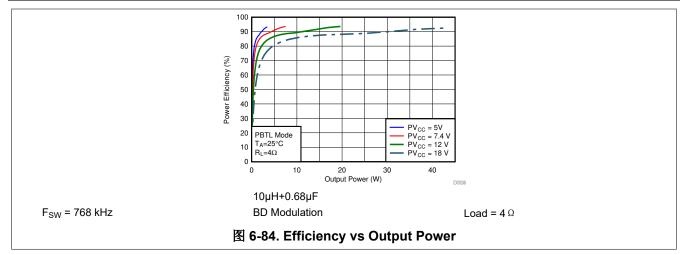

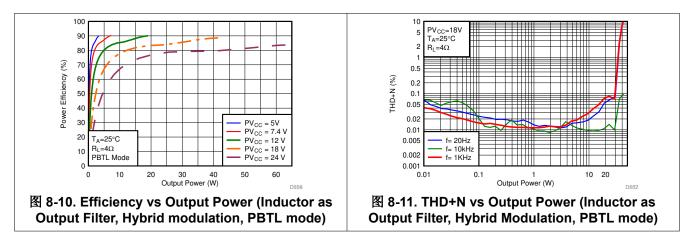

| •  | Added efficiency plot and 1%/10% THD+N output power vs PVDD plot for 4- Ω load                         |      |

| •  | Added notes the Hybrid Modulation section                                                              | 40   |

| •  | Added Speaker DC Protection, Device Over Temperature Protection, Device Over Voltage/Under Voltage     | ge   |

|    | Protection, and Clock Fault sections                                                                   | 46   |

| C | hanges from Revision B (October 2018) to Revision C (December 2018) | Page |

|---|---------------------------------------------------------------------|------|

| • | Added 图 7-14                                                        | 45   |

| • | Added 图 7-15                                                        | 45   |

| С | hanges from Revision A (July 2018) to Revision B (October 2018)      | Page |

|---|----------------------------------------------------------------------|------|

| • | 在 <i>说明</i> 中将"(13.5V PVDD 下小于 16.5mA)"更改为"(13.5V PVDD 下为 16.5mA)"   | 1    |

| • | Changed the Typical Characteristics graphs                           |      |

| • | Added the Clock Halt Auto-recover section                            |      |

| • | Added the Sample Rate on the Fly Change section                      | 31   |

|   | Added the Thermal Foldback section.                                  |      |

|   | Changed the Device State Control section                             |      |

|   | Changed the DSP Memory Book, Page and BQ Coefficients Update section |      |

| • | Added the Example Use section                                        | 43   |

|   | Deleted 010:310K in 表 7-9                                            |      |

|   | Added the Inductor Selections section                                |      |

| • | Added the Step 2: Speaker Tuning section                             |      |

|   | Changed the Development Support section                              |      |

Page

## Changes from Revision \* (May 2018) to Revision A (July 2018)

• 发布为"量产数据"......1

# **Device Comparison Table**

| ORDERABLE PART RECOMMENDED<br>NUMBER PVDD RANGE |                 | Audio Process Flows                                              | R <sub>DS(ON)</sub> |

|-------------------------------------------------|-----------------|------------------------------------------------------------------|---------------------|

| TAS5805M 4.5 V to 26.4 V                        |                 | Enhanced Audio Process Flows with ROM Fixed                      | 180 m Ω             |

| TAS5707/TAS5711                                 | 8 V to 26 V     | Basic Audio Process Flow with ROM Fixed                          | <b>180 m</b> Ω      |

| TAS5825M                                        | 4.5 V to 26.4 V | Flexible Advanced Audio Process Flows with Smart-Amp<br>Features | 90 m Ω              |

# **5** Pin Configuration and Functions

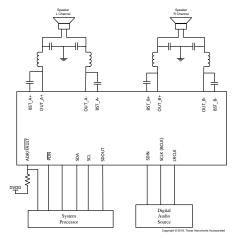

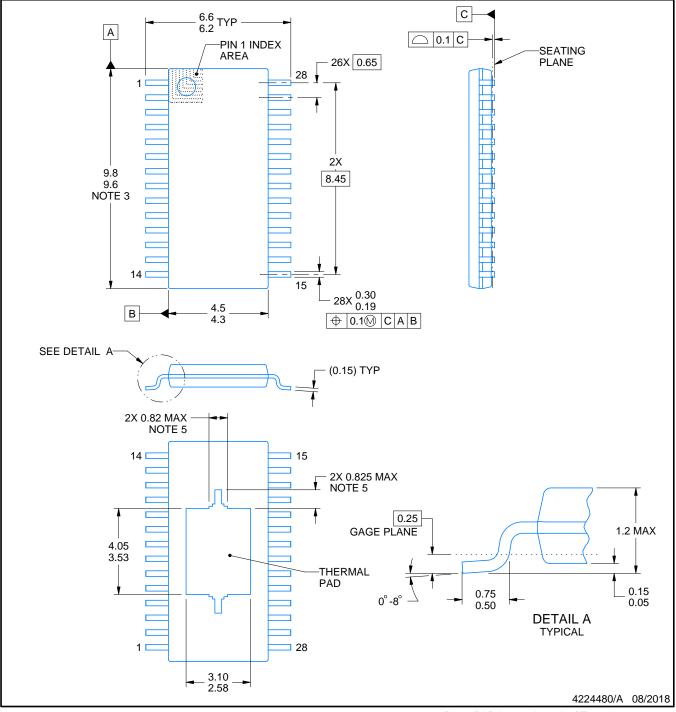

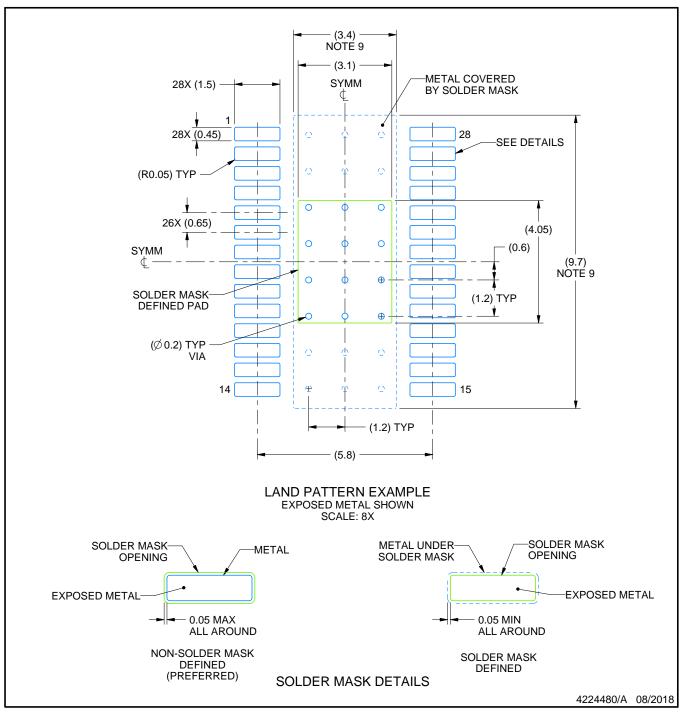

## 图 5-1. PWP Package, 28-Pin TSSOP,

#### 表 5-1. Pin Functions

| PIN        |                 | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                     |  |

|------------|-----------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME       | NO.             | ITPE                | DESCRIPTION                                                                                                                                                                                                                                                                     |  |

| DGND       | 1, 5            | Р                   | Digital ground                                                                                                                                                                                                                                                                  |  |

| DVDD       | 2               | Р                   | 3.3-V or 1.8-V digital power supply                                                                                                                                                                                                                                             |  |

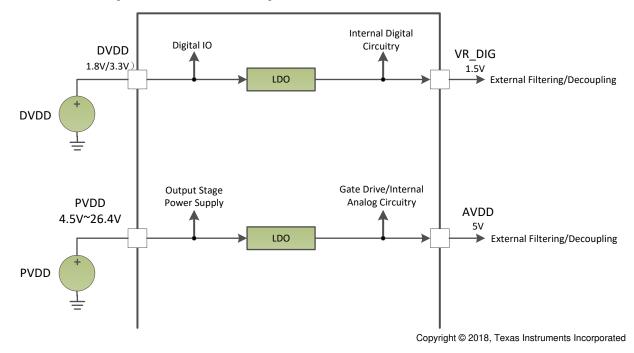

| VR_DIG     | 4               | Р                   | Internally regulated 1.5-V digital supply voltage. This pin must not be used to drive external devices                                                                                                                                                                          |  |

| ADR/ FAULT | 3               | DI/O                | Different I <sup>2</sup> C device address can be set by selecting different pull up resistor to DVDD, see $\frac{1}{8}$ 7-5 for details. After power up, ADR/ FAULT can be redefine as FAULT, go to Page0, Book0, set register 0x61 = 0x0b first, then set register 0x60 = 0x01 |  |

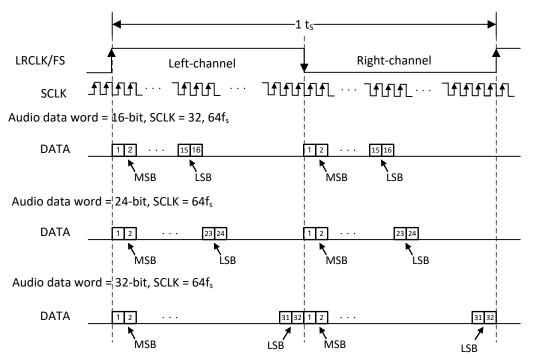

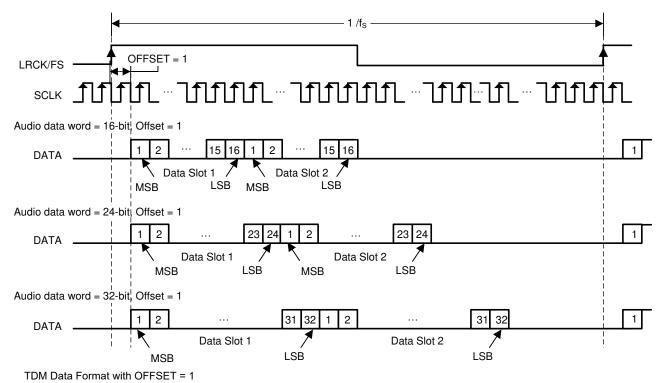

| LRCLK      | 6               | DI                  | Word select clock for the digital signal that is active on the serial port's input data line. In I <sup>2</sup> S, LJ and RJ, this corresponds to the left channel and right channel boundary. In TDM mode, this corresponds to the frame sync boundary                         |  |

| SCLK       | 7               | DI                  | Bit clock for the digital signal that is active on the input data line of the serial data port.                                                                                                                                                                                 |  |

| SDIN       | 8               | DI                  | Data line to the serial data port                                                                                                                                                                                                                                               |  |

| SDOUT      | 9               | DO                  | Serial Audio data output. The source data can be Pre-DSP or Post-DSP data, by setting the register 0x30h.                                                                                                                                                                       |  |

| SDA        | 10              | DI/O                | 2C serial control data interface input/output                                                                                                                                                                                                                                   |  |

| SCL        | 11              | DI                  | I2C serial control clock input                                                                                                                                                                                                                                                  |  |

| PDN        | 12              | DI                  | Power Down, active-low. PDN place the amplifier in Shutdown, turn off all internal regulators. Low, Power Down Device; High, Enable Device.                                                                                                                                     |  |

| AVDD       | 13              | Р                   | Internally regulated 5-V analog supply voltage. This pin must not be used to drive external devices                                                                                                                                                                             |  |

| AGND       | 14              | Р                   | Analog ground                                                                                                                                                                                                                                                                   |  |

| PVDD       | 15,16,27,<br>28 | Ρ                   | PVDD voltage input                                                                                                                                                                                                                                                              |  |

| PGND       | 19,24           | Р                   | Ground reference for power device circuitry. Connect this pin to system ground.                                                                                                                                                                                                 |  |

| OUT_A+     | 26              | 0                   | Positive pin for differential speaker amplifier output A+                                                                                                                                                                                                                       |  |

| BST_A+     | 25              | Ρ                   | Connection point for the OUT_A+ bootstrap capacitor which is used to create a power supply for the high-side gate drive for OUT_A+                                                                                                                                              |  |

| OUT_A-     | 23              | 0                   | Negative pin for differential speaker amplifier output A-                                                                                                                                                                                                                       |  |

## 表 5-1. Pin Functions (continued)

| PIN<br>NAME NO. |                                                                                                                                   | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                            |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

|                 |                                                                                                                                   |                     | DESCRIPTION                                                                                                                            |  |

| BST_A-          | 22 P Connection point for the OUT_A- bootstrap capacitor which is used to create a power supply for the high-sid drive for OUT_A- |                     |                                                                                                                                        |  |

| BST_B-          | 21                                                                                                                                | Р                   | P Connection point for the OUT_B- bootstrap capacitor which is used to create a power supply for the high-side gar<br>drive for OUT_B- |  |

| OUT_B-          | 20                                                                                                                                | 0                   | Negative pin for differential speaker amplifier output B                                                                               |  |

| BST_B+          | 18                                                                                                                                | Р                   | Connection point for the OUT_B+ bootstrap capacitor which is used to create a power supply for the high-side gate drive for OUT_B+     |  |

| OUT_B+          | 17                                                                                                                                | 0                   | Positive pin for differential speaker amplifier output B+                                                                              |  |

| PowerPAD™       |                                                                                                                                   | Р                   | Connect to the system Ground                                                                                                           |  |

(1) AI = Analog input, AO = Analog output, DI = Digital Input, DO = Digital Output, DI/O = Digital Bi-directional (input and output), P = Power, G = Ground (0 V)

## 6 Specifications

## 6.1 Absolute Maximum Ratings

Free-air room temperature 25°C (unless otherwise noted) (1)

|                           |                                               | MIN   | MAX                     | UNIT |

|---------------------------|-----------------------------------------------|-------|-------------------------|------|

| DVDD                      | Low-voltage digital supply                    | - 0.3 | 3.9                     | V    |

| PVDD                      | PVDD supply                                   | - 0.3 | 30                      | V    |

| V <sub>I(DigIn)</sub>     | DVDD referenced digital inputs <sup>(2)</sup> | - 0.5 | V <sub>DVDD</sub> + 0.5 | V    |

| V <sub>I(SPK_OUTxx)</sub> | Voltage at speaker output pins                | - 0.3 | 32                      | V    |

| T <sub>A</sub>            | Ambient operating temperature                 | - 25  | 85                      | °C   |

| T <sub>stg</sub>          | Storage temperature                           | - 40  | 125                     | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) DVDD referenced digital pins include: ADR/ FAULT, LRCLK, SCLK, SCL, SDA, SDIN, PDN

## 6.2 ESD Ratings

|                                 |                         |                                                                                | VALUE | UNIT |

|---------------------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostati |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 |      |

| V <sub>(ESD)</sub>              | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted) see (1)

|                      |                             |                                        | MIN                                                 | NOM | MAX  | UNIT |

|----------------------|-----------------------------|----------------------------------------|-----------------------------------------------------|-----|------|------|

| V                    | Power supply inputs         | DVDD                                   | 1.62                                                |     | 3.63 | V    |

| V <sub>(POWER)</sub> | Fower supply inputs         | PVDD                                   | 4.5                                                 |     | 26.4 | v    |

| R <sub>SPK</sub>     | Minimum speaker load        | BTL Mode (4.5V≤PVDD≤26.4V)             | VOUT <sub>PEAK</sub> /<br>OCE <sub>THRES</sub>      | 6   |      | Ω    |

| R <sub>SPK</sub>     | Minimum speaker load        | PBTL Mode (4.5V≪PVDD≪26.4V)            | VOUT <sub>PEAK</sub> /<br>(2×OCE <sub>THRES</sub> ) | 4   |      | Ω    |

| L <sub>OUT</sub>     | Minimum inductor value in L | C filter under short-circuit condition | 1                                                   | 4.7 |      | μH   |

(1) The minimal speaker load been limited by OCE Threshold, if output peak current <5A, TAS5805M also supports lower speaker load with High PVDD. For BTL, the OCE Threshold is 5A (Typical); For PBTL, the OCE Threshold is 10A (Typical). The minimal speaker load depends on the output peak voltage.</p>

## 6.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              |                                  | TAS5805M<br>TSSOP (PWP)<br>28 PINS |                              |        |  |

|-------------------------------|----------------------------------------------|----------------------------------|------------------------------------|------------------------------|--------|--|

|                               |                                              | JEDEC<br>STANDARD<br>2-LAYER PCB | JEDEC<br>STANDARD<br>4-LAYER PCB   | TAS5805MEVM-4<br>4-LAYER PCB | – UNIT |  |

| R <sub>0 JA</sub>             | Junction-to-ambient thermal resistance       | N/A                              | 29.1                               | 24                           | °C/W   |  |

| R <sub>0 JC(top)</sub>        | Junction-to-case (top) thermal resistance    | N/A                              | 21.8                               | N/A                          | °C/W   |  |

| R <sub>0 JB</sub>             | Junction-to-board thermal resistance         | N/A                              | 8.2                                | N/A                          | °C/W   |  |

| ψ <sub>JT</sub>               | Junction-to-top characterization parameter   | N/A                              | 0.3                                | 1.5                          | °C/W   |  |

| ¢јв                           | Junction-to-board characterization parameter | N/A                              | 8.1                                | 7.6                          | °C/W   |  |

| R <sub>0 JC(bot)</sub>        | Junction-to-case (bottom) thermal resistance | N/A                              | 2.2                                | N/A                          | °C/W   |  |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## **6.5 Electrical Characteristics**

Free-air room temperature 25°C (unless otherwise noted)

|                                                                    | PARAMETER                                                                                                                                                                                                                                                                                                                        | TEST CONDITIONS                                                                                                                                                                                                                                                                                                          | MIN  | ТҮР                                | MAX     | UNIT                      |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------|---------|---------------------------|

| DIGITAL I/O                                                        |                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                          |      |                                    |         |                           |

| IIH                                                                | Input logic high current level<br>for DVDD referenced digital<br>input pins                                                                                                                                                                                                                                                      | V <sub>IN(DigIn)</sub> = V <sub>DVDD</sub>                                                                                                                                                                                                                                                                               |      |                                    | 10      | μA                        |

| IIL                                                                | Input logic low current level for<br>DVDD referenced digital input<br>pins                                                                                                                                                                                                                                                       | V <sub>IN(DigIn)</sub> = 0 V                                                                                                                                                                                                                                                                                             |      |                                    | - 10    | μA                        |

| V <sub>IH(Digin)</sub>                                             | Input logic high threshold for<br>DVDD referenced digital inputs                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                          | 70%  | ·                                  |         | V <sub>DVDD</sub>         |

| V <sub>IL(Digin)</sub>                                             | Input logic low threshold for<br>DVDD referenced digital inputs                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                          |      |                                    | 30%     | V <sub>DVDD</sub>         |

| V <sub>OH(Digin)</sub>                                             | Output logic high voltage level                                                                                                                                                                                                                                                                                                  | I <sub>OH</sub> = 2 mA                                                                                                                                                                                                                                                                                                   | 80%  |                                    |         | V <sub>DVDD</sub>         |

| V <sub>OL(Digin)</sub>                                             | Output logic low voltage level                                                                                                                                                                                                                                                                                                   | $I_{OH} = -2 \text{ mA}$                                                                                                                                                                                                                                                                                                 |      |                                    | 20%     | V <sub>DVDD</sub>         |

| I <sup>2</sup> C CONTROL F                                         | PORT                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                        |      |                                    |         |                           |

| C <sub>L(I2C)</sub>                                                | Allowable load capacitance for each I <sup>2</sup> C line                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                          |      |                                    | 400     | pF                        |

| f <sub>SCL(fast)</sub>                                             | Support SCL frequency                                                                                                                                                                                                                                                                                                            | No wait states, fast mode                                                                                                                                                                                                                                                                                                |      |                                    | 400     | kHz                       |

| f <sub>SCL(slow)</sub>                                             | Support SCL frequency                                                                                                                                                                                                                                                                                                            | No wait states, slow mode                                                                                                                                                                                                                                                                                                |      |                                    | 100     | kHz                       |

| SERIAL AUDIO                                                       | PORT                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                        |      |                                    |         |                           |

| t <sub>DLY</sub>                                                   | Required LRCLK/FS to SCLK rising edge delay                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                          | 5    |                                    |         | ns                        |

| D <sub>SCLK</sub>                                                  | Allowable SCLK duty cycle                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                          | 40%  |                                    | 60%     |                           |

| f <sub>S</sub>                                                     | Supported input sample rates                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                          | 32   |                                    | 96      | kHz                       |

| SCLK                                                               | Supported SCLK frequencies                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                          | 32   |                                    | 64      | f <sub>S</sub>            |

| f <sub>SCLK</sub>                                                  | SCLK frequency                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                          |      |                                    | 24.576  | MHz                       |

|                                                                    | LIFIER (ALL OUTPUT CONFIGUR                                                                                                                                                                                                                                                                                                      | ATIONS)                                                                                                                                                                                                                                                                                                                  |      |                                    |         |                           |

| I <sub>cc</sub>                                                    | Quiescent supply current on<br>DVDD                                                                                                                                                                                                                                                                                              | PDN=2V, DVDD=3.3V, Play mode                                                                                                                                                                                                                                                                                             |      | 18                                 |         | mA                        |

| I <sub>cc</sub>                                                    | Quiescent supply current on<br>DVDD                                                                                                                                                                                                                                                                                              | PDN=2V, DVDD=3.3V, Sleep mode                                                                                                                                                                                                                                                                                            |      | 0.75                               |         | mA                        |

| I <sub>cc</sub>                                                    | Quiescent supply current on<br>DVDD                                                                                                                                                                                                                                                                                              | PDN=2V, DVDD=3.3V, Deep Sleep mode                                                                                                                                                                                                                                                                                       |      | 0.75                               |         | mA                        |

| l <sub>cc</sub>                                                    | Quiescent supply current on<br>DVDD                                                                                                                                                                                                                                                                                              | PDN=0V, DVDD=3.3V, Shutdown mode                                                                                                                                                                                                                                                                                         |      | 5.5                                |         | μA                        |

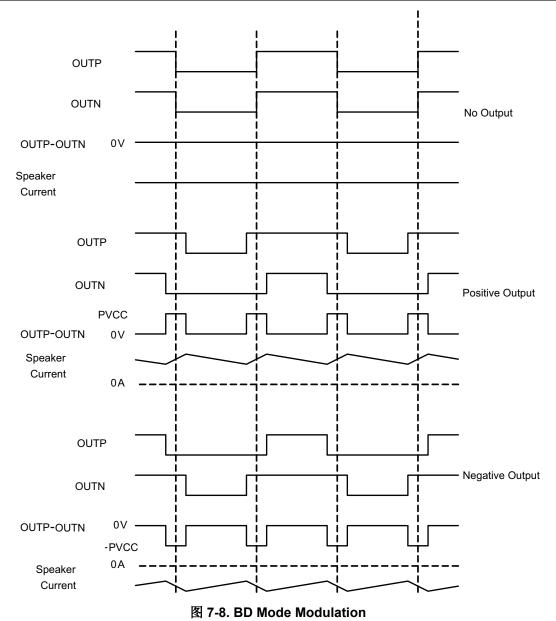

| l <sub>cc</sub>                                                    | Quiescent supply current on<br>PVDD                                                                                                                                                                                                                                                                                              | PDN=2V,, PVDD=13.5V, LC filter=10uH+0.68uF,<br>Fsw=768kHz, BD Modulation, Play mode                                                                                                                                                                                                                                      |      | 32.5                               |         | mA                        |

| 1                                                                  | Quiescent supply current on                                                                                                                                                                                                                                                                                                      | PDN=2V,, PVDD=13.5V, LC filter=22uH+0.68uF,                                                                                                                                                                                                                                                                              |      | 40 F                               |         | mA                        |

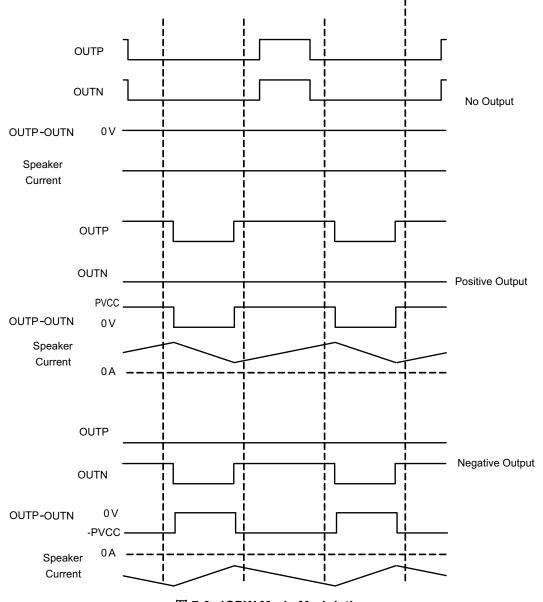

| °cc                                                                | PVDD                                                                                                                                                                                                                                                                                                                             | Fsw=384kHz, Hybrid Modulation, Play mode                                                                                                                                                                                                                                                                                 |      | 16.5                               |         |                           |

|                                                                    |                                                                                                                                                                                                                                                                                                                                  | Fsw=384kHz, Hybrid Modulation, Play mode PDN=2V, PVDD=13.5V, Output Hiz Mode                                                                                                                                                                                                                                             |      | 10.5                               |         | mA                        |

| cc                                                                 | PVDD<br>Quiescent supply current on                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                          |      |                                    |         | mA<br>mA                  |

| lcc                                                                | PVDD<br>Quiescent supply current on<br>PVDD<br>Quiescent supply current on                                                                                                                                                                                                                                                       | PDN=2V, PVDD=13.5V, Output Hiz Mode                                                                                                                                                                                                                                                                                      |      | 10.4                               |         |                           |

| lcc<br>lcc                                                         | PVDD         Quiescent supply current on                                                                                                                                      | PDN=2V, PVDD=13.5V, Output Hiz Mode<br>PDN=2V, PVDD=13.5V, Sleep Mode                                                                                                                                                                                                                                                    |      | 10.4<br>7.2                        |         | mA                        |

| lcc<br>lcc<br>lcc                                                  | PVDD         Quiescent supply current on                                    | PDN=2V, PVDD=13.5V, Output Hiz Mode         PDN=2V, PVDD=13.5V, Sleep Mode         PDN=2V, PVDD=13.5V, Deep Sleep Mode                                                                                                                                                                                                   |      | 10.4<br>7.2<br>120                 | 10      | mA<br>μA                  |

| loc<br>loc<br>loc<br>loc<br>toff                                   | PVDD         Quiescent supply current on         PVDD                       | PDN=2V, PVDD=13.5V, Output Hiz Mode         PDN=2V, PVDD=13.5V, Sleep Mode         PDN=2V, PVDD=13.5V, Deep Sleep Mode         PDN=0V, PVDD=13.5V, Shutdown Mode                                                                                                                                                         | 4.87 | 10.4<br>7.2<br>120                 | 10 29.5 | mA<br>μA<br>μA            |

| lcc<br>lcc<br>lcc<br>lcc<br>lcc<br>toff                            | PVDD         Quiescent supply current on         PVDD         Turn-off Time | PDN=2V, PVDD=13.5V, Output Hiz Mode         PDN=2V, PVDD=13.5V, Sleep Mode         PDN=2V, PVDD=13.5V, Deep Sleep Mode         PDN=0V, PVDD=13.5V, Shutdown Mode         Excluding volume ramp         Value represents the "peak voltage" disregarding clipping due to lower PVDD).                                     | 4.87 | 10.4<br>7.2<br>120                 |         | mA<br>μA<br>μA<br>ms      |

| Icc<br>Icc<br>Icc<br>Icc<br>Icc<br>toff<br>Av(spk_амр)<br>бspk_амр | PVDD         Quiescent supply current on         PVDD         Turn-off Time         Programmable Gain                        | PDN=2V, PVDD=13.5V, Output Hiz Mode         PDN=2V, PVDD=13.5V, Sleep Mode         PDN=2V, PVDD=13.5V, Deep Sleep Mode         PDN=0V, PVDD=13.5V, Shutdown Mode         Excluding volume ramp         Value represents the "peak voltage" disregarding clipping due to lower PVDD).         Measured at 0 dB input(1FS) | 4.87 | 10.4       7.2       120       7.2 |         | mA<br>μA<br>μA<br>ms<br>V |

# 6.5 Electrical Characteristics (continued)

Free-air room temperature 25°C (unless otherwise noted)

|                           | PARAMETER                                                                       | TEST CONDITIONS                                                                                                                | MIN TYP | MAX | UNIT  |

|---------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------|-----|-------|

| R <sub>DS(on)</sub>       | Drain-to-source on resistance<br>of the individual output<br>MOSFETs            | FET + Metallization                                                                                                            | 180     |     | mΩ    |

| OCE <sub>THRES</sub>      | Over-Current Error Threshold                                                    | OUTxx Overcurrent Error Threshold                                                                                              | 5       |     | А     |

| OVE <sub>THRES(PVDD</sub> | PVDD over voltage error threshold                                               |                                                                                                                                | 28      |     | V     |

| UVE <sub>THRES(PVDD</sub> | PVDD under voltage error<br>threshold                                           |                                                                                                                                | 4.2     |     | V     |

| OTE <sub>THRES</sub>      | Over temperature error threshold                                                |                                                                                                                                | 160     |     | °C    |

| OTE <sub>Hystersis</sub>  | Over temperature error<br>hysteresis                                            |                                                                                                                                | 10      |     | °C    |

| OTW <sub>THRES</sub>      | Over temperature warning level                                                  | Read by register 0x73 bit3                                                                                                     | 135     |     | °C    |

| SPEAKER AMPI              | LIFIER (STEREO BTL)                                                             |                                                                                                                                |         |     |       |

| V <sub>os</sub>           | Amplifier offset voltage                                                        | Measured differentially with zero input data,<br>programmable gain configured with 29.5 Vp gain,<br>$V_{PVDD}$ = 12 V, BD Mode | - 6.5   | 6.5 | mV    |

|                           |                                                                                 | V <sub>PVDD</sub> = 21V, SPK_GAIN = 24.8 Vp/FS, R <sub>SPK</sub> = 8<br>Ω, f = 1 kHz, THD+N = 1%, 1SPW Mode                    | 23      |     | W     |

|                           | Continuous Output power (per<br>channel)                                        | V <sub>PVDD</sub> = 21 V, SPK_GAIN = 24.8 Vp/FS, R <sub>SPK</sub> = 8<br>Ω, f = 1 kHz, THD+N = 10%, 1SPW Mode                  | 27.5    |     | W     |

|                           |                                                                                 | $V_{PVDD}$ = 18 V, SPK_GAIN = 20.8 Vp/FS, R <sub>SPK</sub> = 6<br>$\Omega$ , f = 1 kHz, THD+N = 1%, BD Mode                    | 21      |     | W     |

| <b>C</b>                  |                                                                                 | V <sub>PVDD</sub> = 18 V, SPK_GAIN = 20.8 Vp/FS, R <sub>SPK</sub> = 6<br>Ω, f = 1 kHz, THD+N = 10%, BD Mode                    | 25      |     | W     |

| P <sub>O(SPK)</sub>       |                                                                                 | $V_{PVDD}$ = 12 V, SPK_GAIN = 13.9 Vp/FS, R <sub>SPK</sub> = 6<br>$\Omega$ , f = 1 kHz THD+N = 1%, BD Mode                     | 9.9     |     | W     |

|                           |                                                                                 | $V_{PVDD}$ = 12 V, SPK_GAIN = 13.9 Vp/FS, R <sub>SPK</sub> = 6<br>$\Omega$ , f = 1 kHz THD+N = 10%, BD Mode                    | 12      |     | W     |

|                           |                                                                                 | $V_{PVDD}$ = 13.5 V, SPK_GAIN = 15.6 Vp/FS, R <sub>SPK</sub><br>= 6 $\Omega$ , f = 1 kHz THD+N = 1%, BD Mode                   | 12      |     | W     |

|                           |                                                                                 | V <sub>PVDD</sub> = 13.5 V, SPK_GAIN = 15.6 Vp/FS, R <sub>SPK</sub><br>= 6 Ω, f = 1 kHz THD+N = 10%, BD Mode                   | 15      |     | W     |

|                           | Total harmonic distortion and noise                                             | V <sub>PVDD</sub> = 12 V, Fsw=768kHz, SPK_GAIN = 13.9<br>Vp/FS, LC-filter, BD Mode                                             | 0.03%   |     |       |

| THD+N <sub>SPK</sub>      | (P <sub>O</sub> = 1 W, f = 1 KHz, R <sub>SPK</sub> = 6 $\Omega$ )               | V <sub>PVDD</sub> = 18 V, Fsw=768kHz, SPK_GAIN = 20.8<br>Vp/FS, LC-filter, BD Mode                                             | 0.03%   |     |       |

| 1                         | Idle channel noise(A-weighted)                                                  | $V_{PVDD}$ = 12 V, Fsw=768kHz, LC-filter, Load=6 $\Omega$                                                                      | 37      | 37  |       |

| CN(SPK)                   |                                                                                 | $V_{PVDD}$ = 18 V, Fsw=768kHz, LC-filter, Load=6 $\Omega$                                                                      | 38      |     | μVrms |

| DR                        | Dynamic range                                                                   | A-Weighted, -60 dBFS method. P <sub>VDD</sub> = 24 V,<br>SPK_GAIN = 29.5 Vp/FS                                                 | 106     |     | dB    |

| SND                       | Signal to point ratio                                                           | A-Weighted, referenced to 1% THD+N output level,<br>PVDD=24V                                                                   | 111     |     | dB    |

| SNR                       | Signal-to-noise ratio                                                           | A-Weighted, referenced to 1% THD+N output level,<br>PVDD=13.5V                                                                 | 107.5   |     | dB    |

| K <sub>SVR</sub>          | Power supply rejection ratio                                                    | Injected Noise = 1 KHz, 1 V <sub>rms</sub> , PVDD = 12 V, input<br>audio signal = digital zero                                 | 72      |     | dB    |

| X-talk <sub>SPK</sub>     | Cross-talk (worst case<br>between left-to-right and right-<br>to-left coupling) | f = 1 kHz                                                                                                                      | 100     |     | dB    |

## 6.5 Electrical Characteristics (continued)

Free-air room temperature 25°C (unless otherwise noted)

| PARAMETER            |                                                                             | TEST CONDITIONS                                                                                                                                                                                                                           | MIN TYP | MAX | UNIT |

|----------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|------|

|                      |                                                                             | $V_{\text{PVDD}}$ = 12 V, SPK_GAIN = 13.9 Vp/FS, R_{\text{SPK}} = 4 $\Omega$ , f = 1kHz, THD+N = 1%, BD Mode                                                                                                                              | 15.4    |     | W    |

| _                    | Continuous Output Dowor                                                     | $V_{PVDD}$ = 12 V, SPK_GAIN = 13.9 Vp/FS, R <sub>SPK</sub> = 4 $\Omega$ , f = 1kHz, THD+N = 10%, BD Mode                                                                                                                                  | 18.5    |     | W    |

| P <sub>O(SPK)</sub>  | Continuous Output Power                                                     | V <sub>PVDD</sub> = 18V, SPK_GAIN = 22.1 Vp/FS, R <sub>SPK</sub> = 4<br>Ω, f = 1kHz, THD+N = 1%, BD Mode                                                                                                                                  | 33.6    |     | W    |

|                      |                                                                             | V <sub>PVDD</sub> = 18 V, SPK_GAIN = 22.1 Vp/FS, R <sub>SPK</sub> = 4<br>Ω, f = 1kHz, THD+N = 10%, BD Mode                                                                                                                                | 41      |     | W    |

| THD+N <sub>SPK</sub> | Total harmonic distortion and<br>noise<br>(P <sub>O</sub> = 1 W, f = 1 kHz) | $V_{\text{PVDD}}$ = 12 V, SPK_GAIN = 16.5 Vp/FS, 4.7uH + 0.68uF filter, R_{\text{SPK}} = 4 $\Omega$ , BD Mode                                                                                                                             | 0.06%   |     |      |

|                      |                                                                             | $\label{eq:VPVDD} \begin{array}{l} V_{PVDD} \texttt{=} \texttt{24 V}, SPK\_GAIN\texttt{=} \texttt{29.5 Vp/FS}, \texttt{4.7uH}\texttt{+} \\ \texttt{0.68uF filter}, R_{SPK}\texttt{=} \texttt{4} \ \Omega, \texttt{1SPW Mode} \end{array}$ | 0.07%   |     |      |

| DR                   | Dynamic range                                                               | A-Weighted, -60 dBFS method, PVDD = 24V,<br>SPK_GAIN = 29.5 Vp/FS                                                                                                                                                                         | 106     |     | dB   |

| SNR                  | Signal-to-noise ratio                                                       | A-Weighted, referenced to 1% THD+N output level,<br>PVDD=13.5V                                                                                                                                                                            | 107.7   |     | dB   |

|                      |                                                                             | A-Weighted, referenced to 1% THD+N output level, PVDD=24V                                                                                                                                                                                 | 111     |     | dB   |