🕳 Order

Now

ZHCS146C - DECEMBER 2011 - REVISED APRIL 2020

# 用于生物电势测量的 ADS129x 低功耗、双通道、24 位模拟前端

Technical

Documents

## 1 特性

- 两个低噪声 PGA 和两个高分辨率 ADC (ADS1292 和 ADS1292R)

- 低功耗: 335µW/通道

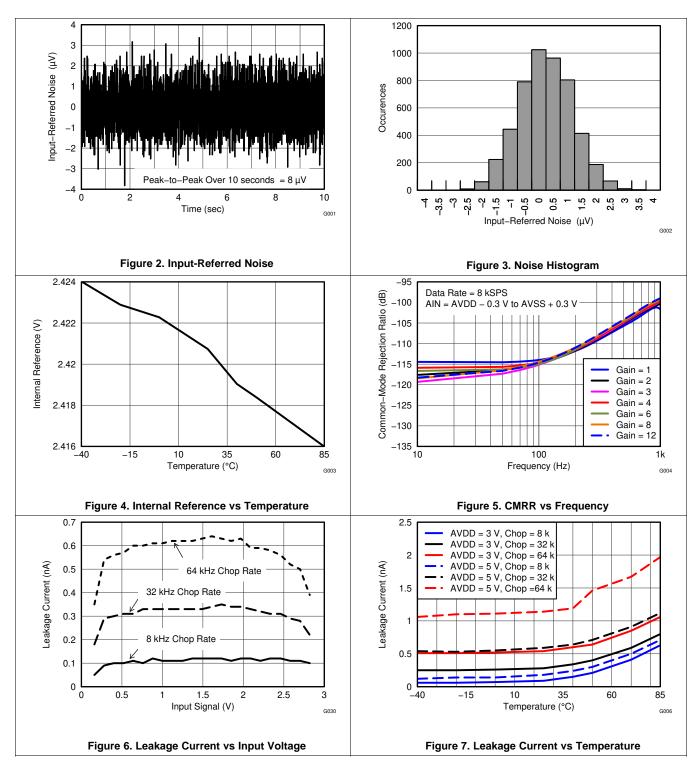

- 输入参考噪声: 8μV<sub>PP</sub> (150Hz 带宽, G = 6)

- 输入偏置电流: 200pA

- 数据速率: 125SPS 至 8kSPS

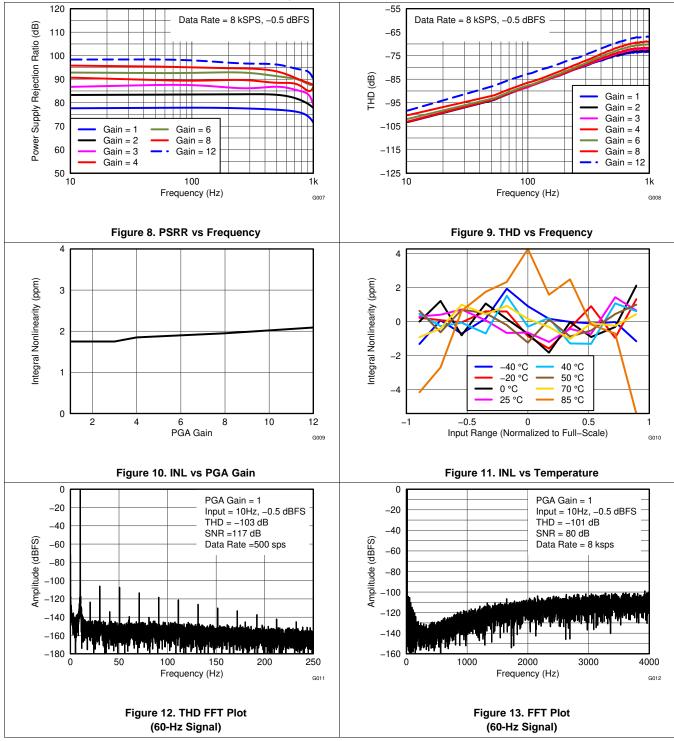

- CMRR: 120dB

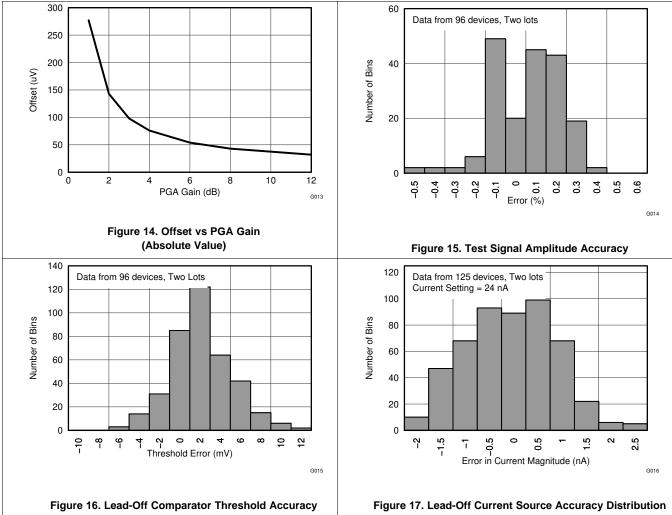

- 可编程增益: 1、2、3、4、6、8 或 12

- 电源: 单极或者双极

- 模拟: 2.7V 至 5.25V

- 数字: 1.7V 至 3.6V

- 内置右腿驱动放大器、持续断线检测、测试信号

- 集成型呼吸阻抗测量 (ADS1292R)

- 内置振荡器和基准

- 灵活的断电、待机模式

- SPI™兼容串行接口

- 工作温度范围: -40°C 至 +85°C

- 2 应用

- 医疗仪器 (ECG) 包括:

- 患者监护:动态心电图 (Holter)、事件、压力和 生命体征,包括心电图、AED 和远程医疗

- 个人护理和健身监视器

(心率、呼吸和 ECG)

- 高精度、同步、多通道数据采集

## 3 说明

🧷 Tools &

Software

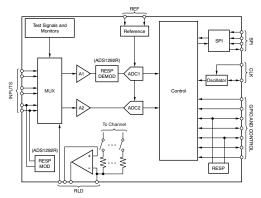

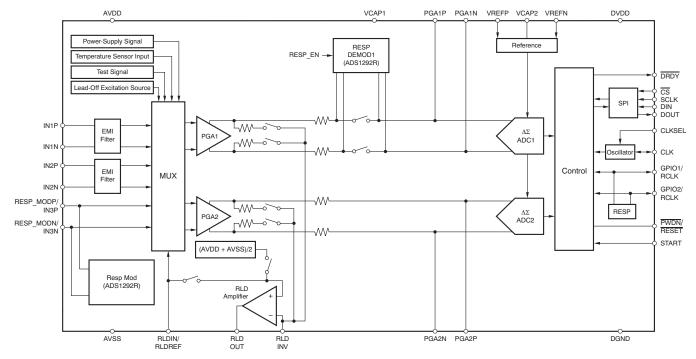

ADS1291、ADS1292 和 ADS1292R 是多通道同步采 样 24 位 Δ-Σ 模数转换器 (ADC),它们具有内置的可编 程增益放大器 (PGA)、内部基准和板载振荡器。

Support &

Community

22

ADS1291、ADS1292 和 ADS1292R 包含 便携式 低 功耗医疗心电图 (ECG)、体育和健身 应用通常所需的 所有功能。

凭借高集成度和出色的性能,ADS1291、ADS1292和 ADS1292R可在显著减少尺寸、功耗和总体成本的前 提下创建可扩展的医疗仪器系统。

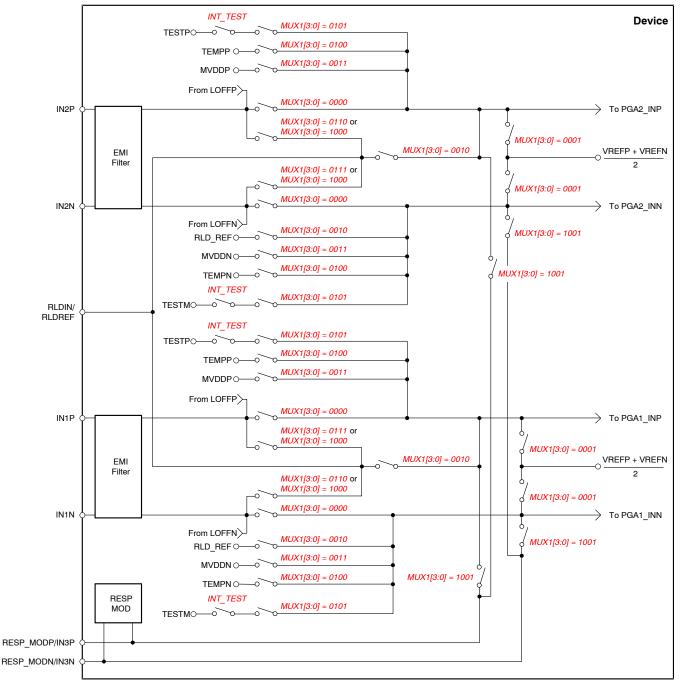

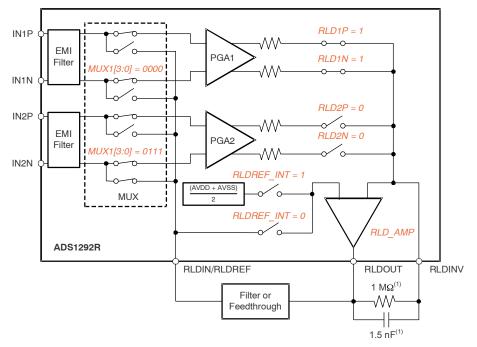

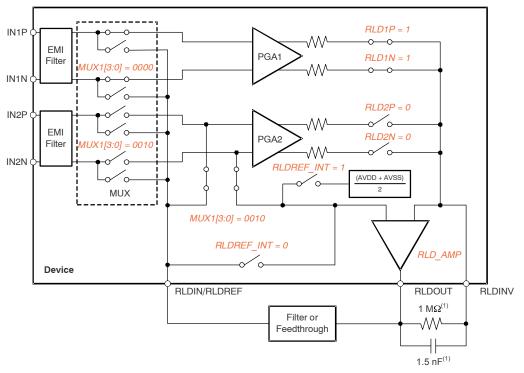

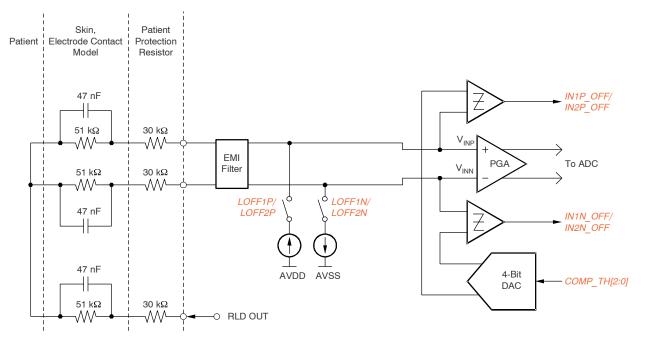

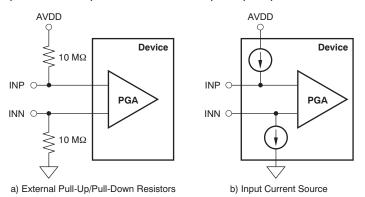

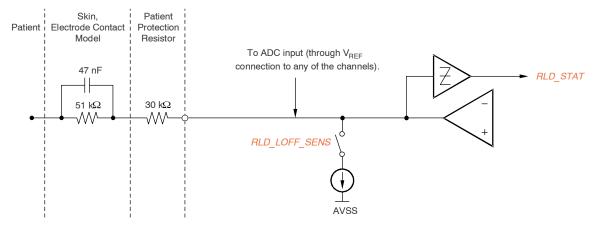

ADS1291、ADS1292 和 ADS1292R 每通道具有灵活的输入多路复用器,此多路复用器可独立连接至内部生成的信号,实现测试、温度和持续断线检测。此外,可选择输入通道的任一配置生成右腿驱动 (RLD) 输出信号。ADS1291、ADS1292 和 ADS1292R 工作时的数据速率高达 8kSPS。通过器件内部激励灌电流或拉电流,可在器件内部执行持续断线检测。ADS1292R 版本包括一个完全集成的呼吸阻抗测量功能。

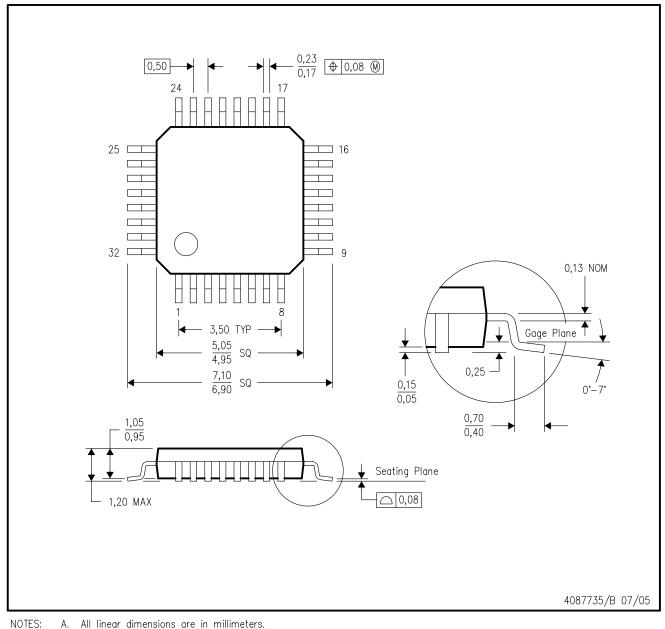

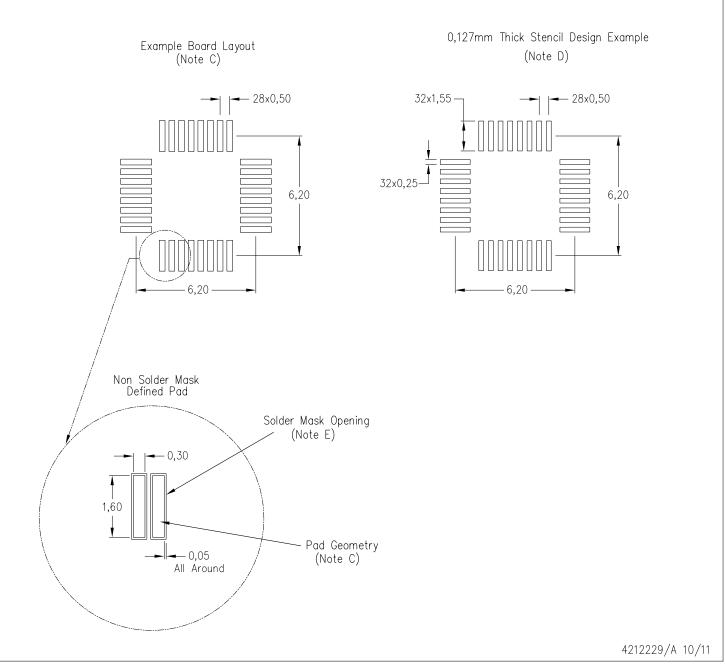

这些器件采用 5mm × 5mm、32 引脚薄型四方扁平封装 (TQFP) 和 4mm x 4mm、32 引脚无引线四方扁平 封装 (VQFN)。额定工作温度范围 –40°C 至 +85°C。

器件信息(1)

| 器件型号    | 封装        | 封装尺寸(标称值)       |  |  |  |  |  |

|---------|-----------|-----------------|--|--|--|--|--|

| ADS129x | TQFP (32) | 5.00mm × 5.00mm |  |  |  |  |  |

| ADS129X | VQFN (32) | 4.00mm × 4.00mm |  |  |  |  |  |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

## ADS1291, ADS1292, ADS1292R

ZHCS146C-DECEMBER 2011-REVISED APRIL 2020

## 目录

9

13

| 1 | 特性   |                                    |

|---|------|------------------------------------|

| 2 | 应用   | 1                                  |

| 3 | 说明   | 1                                  |

| 4 | 修订   | 历史记录                               |

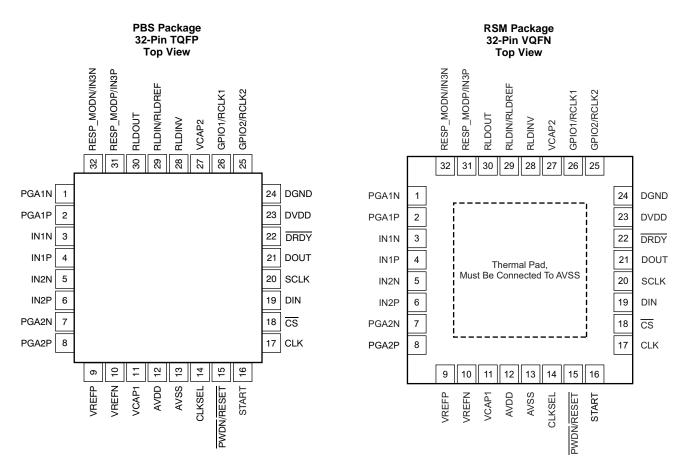

| 5 | Pin  | Configuration and Functions 4      |

| 6 | Spe  | cifications                        |

|   | 6.1  | Absolute Maximum Ratings 6         |

|   | 6.2  | ESD Ratings6                       |

|   | 6.3  | Recommended Operating Conditions 6 |

|   | 6.4  | Thermal Information 6              |

|   | 6.5  | Electrical Characteristics7        |

|   | 6.6  | Timing Requirements 11             |

|   | 6.7  | Typical Characteristics 12         |

| 7 | Para | ameter Measurement Information 15  |

|   | 7.1  | Noise Measurements 15              |

| 8 | Deta | ailed Description 18               |

|   | 8.1  | Overview 18                        |

|   | 8.2  | Functional Block Diagram 18        |

|   | 8.3  | Feature Description 19             |

## 4 修订历史记录

2

注: 之前版本的页码可能与当前版本有所不同。

## Changes from Revision B (September 2012) to Revision C

| • | 已添加 添加了器件信息表、ESD 额定值表、首页图的标题、建议运行条件表、特性说明部分、器件功能模式部                                                                                                                                                                     |      |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|   | 分、应用和实施部分、电源相关建议部分、布局部分、器件和文档支持部分以及机械、封装和可订购信息部分                                                                                                                                                                        | 1    |

| • | 已更改 将 CMRR 值从 105dB 更改为 120dB (位于特性 部分)                                                                                                                                                                                 | 1    |

| • | 已更改 更改了 <i>应用</i> 部分                                                                                                                                                                                                    | 1    |

| • | 已更改 通篇将 QFN 更改为 VQFN                                                                                                                                                                                                    | 1    |

| • | Added thermal pad data to RDM pin out package drawing                                                                                                                                                                   | 4    |

| • | Changed <i>Pin Functions</i> title from <i>Pin Assignments</i> , changed <i>Terminal</i> column header to <i>Pin</i> , and corrected format to show both package options                                                | 4    |

| • | Changed function and description of RESP_MODN/IN3N and RESP_MODP/IN3P pins, changed function of RLDOUT pin from <i>Analog input</i> to <i>Analog output</i> , and added Thermal Pad row to <i>Pin Assignments</i> table | 4    |

| • | Deleted Family and Ordering Information table                                                                                                                                                                           | 6    |

| • | Changed CMRR parameter values from –105 dB to 105 dB (minimum) and from –120 dB to 120 dB (typical) in<br>Electrical Characteristics table                                                                              |      |

| • | Changed Noise Measurements section: deleted SNR equation, changed DYN RANGE and EFF RESOL column headers in section tables                                                                                              | . 15 |

| • | Added last sentence to Internal Respiration Circuitry with External Clock (ADS1292R) section                                                                                                                            | . 39 |

| • | Changed denominator of equation 10                                                                                                                                                                                      | . 41 |

| • | Changed first paragraph of Data Output (DOUT) section                                                                                                                                                                   | . 42 |

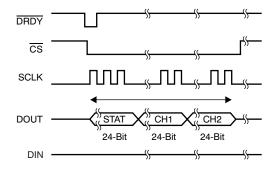

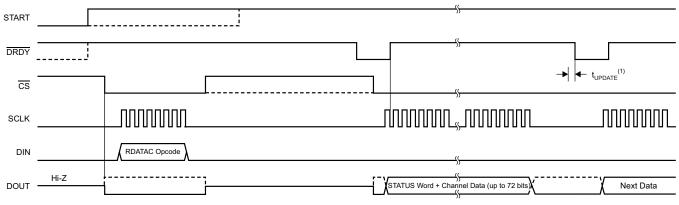

| • | Changed RDATAC Usage figure                                                                                                                                                                                             | . 48 |

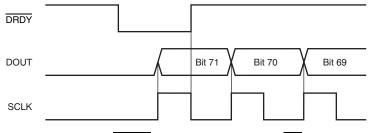

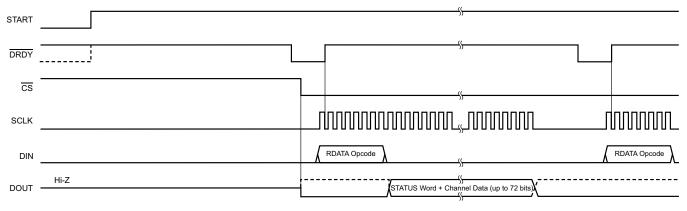

| • | Changed RDATA Usage figure                                                                                                                                                                                              | . 49 |

| • | Changed ADS1292R Application section to fulfill Typical Application section                                                                                                                                             |      |

## EXAS STRUMENTS

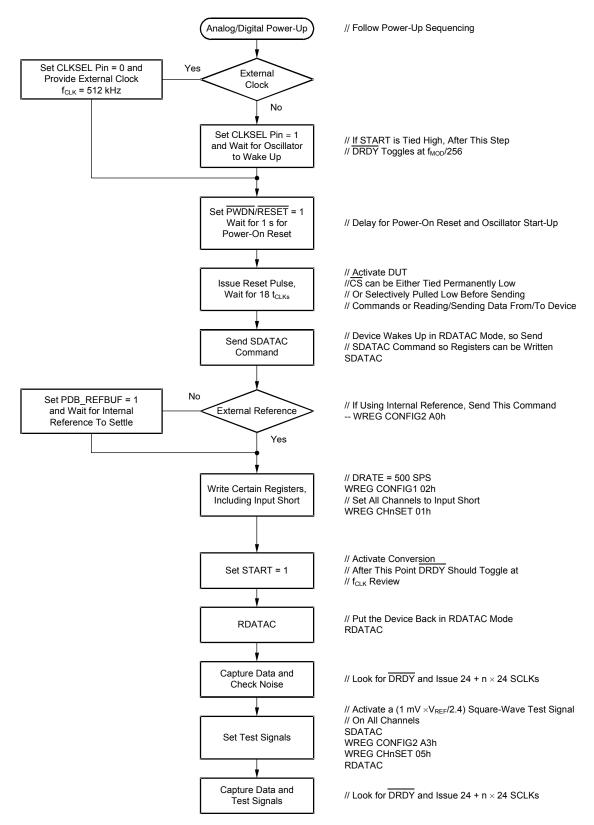

8.4 Device Functional Modes...... 41 8.5 Programming...... 41 8.6 Register Maps..... 51 Application and Implementation ...... 62

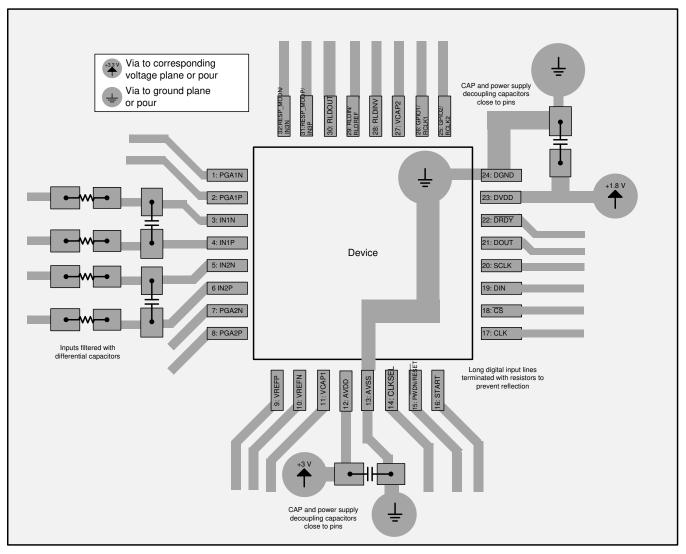

10.1 Power-Up Sequencing ...... 65 11.1 Layout Guidelines ...... 66 11.2 Layout Example ..... 69 12 器件和文档支持...... 70 12.1 相关链接...... 70 12.2 接收文档更新通知 ...... 70 12.5 静电放电警告...... 70 机械、封装和可订购信息......70

www.ti.com.cn

Page

Page

ZHCS146C – DECEMBER 2011 – REVISED APRIL 2020

# Changes from Revision A (March 2012) to Revision B Page • 已添加 向器件图形添加了 QFN 封装 1 • Added QFN pin out drawing 4 • Changed AVSS to DGND row in Absolute Maximum Ratings table 6 • Changed parameters of Supply Current (RLD Amplifier Turned Off) section in Electrical Characteristics table 10 • Changed description of bit 6 in LOFF\_STATUS: Lead-Off Status register 59

#### Changes from Original (December 2011) to Revision A

| • | 己更改 更改了器件图形                                                                                                                                     |      |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | 己更改 将器件状态从"混合状态"更改为"生产数据"                                                                                                                       | 1    |

| • | 已更改 更改了第二个 "特性" 项目符号                                                                                                                            | 1    |

| • | Updated Family and Ordering Information table                                                                                                   |      |

| • | Moved ADS1292R to production status                                                                                                             | 6    |

| • | Deleted footnote 2 from Family and Ordering Information table                                                                                   | 6    |

| • | Changed values of AVDD to AVSS and DVDD to DGND rows in Absolute Maximum Ratings table                                                          | 6    |

| • | Changed Operating temperature range parameter in Absolute Maximum Ratings table                                                                 | 6    |

| • | Changed DC Channel Performance, INL parameter test conditions in Electrical Characteristics table                                               | 7    |

| • | Changed AC Channel Performance, SNR and THD parameters test conditions in Electrical Characteristics table                                      | 7    |

| • | Added third Channel Performance, THD parameter row to Electrical Characteristics table                                                          | 7    |

| • | Added Digital Filter section to Electrical Characteristics table                                                                                | 8    |

| • | Deleted Right Leg Drive Amplifier, <i>Quiescent power consumption</i> parameter test condition from Electrical Characteristics table            | 8    |

| • | Changed Respiration, Impedance measurement noise parameter test conditions in Electrical Characteristics table                                  | 8    |

| • | Changed Respiration, Maximum modulator current parameter in Electrical Characteristics table                                                    | 8    |

| • | Changed Power-Supply Requirements, Digital supply parameter in Electrical Characteristics table                                                 | 9    |

| • | Changed first I <sub>DVDD</sub> Supply Current, Normal mode parameter test conditions in Electrical Characteristics table                       | . 10 |

| • | Changed 3-V Power Dissipation, Quiescent power dissipation, per channel parameter typical specifications in<br>Electrical Characteristics table | . 10 |

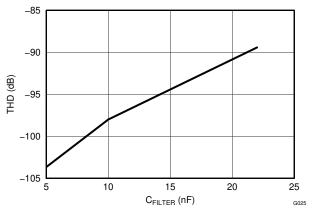

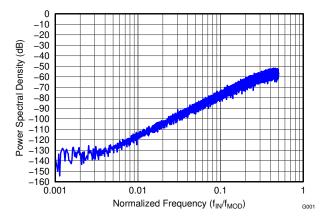

| • | Added C <sub>FILTER</sub> to Typical Characteristics conditions                                                                                 | 12   |

| • | Updated Figure 5                                                                                                                                | 12   |

| • | Updated Figure 9 and Figure 12                                                                                                                  | 12   |

| • | Changed description of CHnSET setting in Supply Measurements (MVDDP, MVDDN) section                                                             | . 21 |

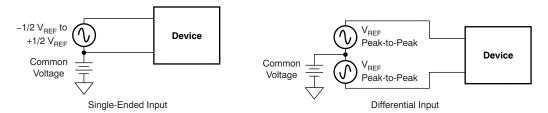

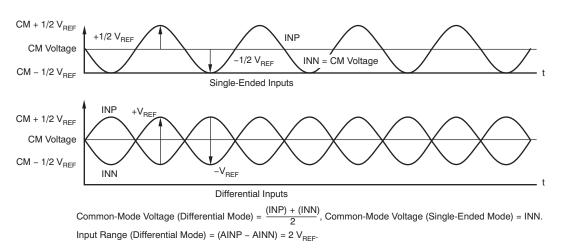

| • | Changed second paragraph of PGA Settings and Input Range section                                                                                | . 23 |

| • | Changed description of PD_REFBUF bit in the <i>Reference</i> section                                                                            | . 27 |

| • | Updated second column title in Table 9                                                                                                          | 28   |

| • | Updated Figure 33                                                                                                                               | 30   |

| • | Updated Figure 42                                                                                                                               | 38   |

| • | Added description of Figure 43, Figure 43, and Table 12 to Internal Respiration Circuitry with External Clock (ADS1292R) section                | . 39 |

| • | Updated description of DOUT and DRDY in RDATAC: Read Data Continuous section                                                                    | . 48 |

| • | Updated RLD_STAT in address 08h of Table 16                                                                                                     | 51   |

| • | Changed description of bit 1 in CONFIG2: Configuration Register 2                                                                               | 53   |

| • | Changed descriptions of bits[3:0] in CH2SET: Channel 2 Settings                                                                                 | . 56 |

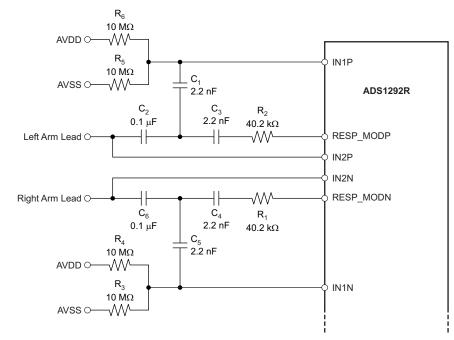

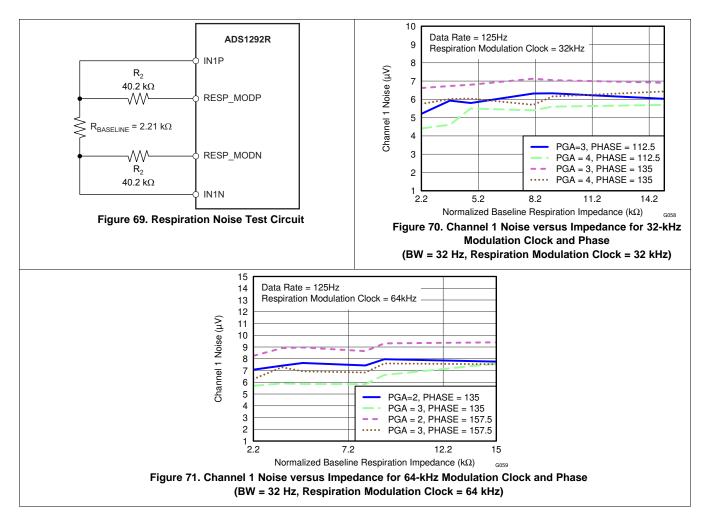

| • | Updated Figure 70 and Figure 71                                                                                                                 | 64   |

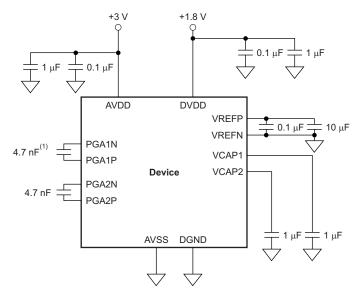

| • | Updated Figure 73 and added footnote 1                                                                                                          |      |

| • | Updated Figure 74 and added footnote 1                                                                                                          | 68   |

|   |                                                                                                                                                 |      |

## 5 Pin Configuration and Functions

## **Pin Functions**

| PIN |                     |                     | FUNCTION               | DESCRIPTION                                           |  |

|-----|---------------------|---------------------|------------------------|-------------------------------------------------------|--|

| NO. | PBS (TQFP)          | RSM (VQFN)          | FUNCTION               | DESCRIPTION                                           |  |

| 1   | PGA1N               | PGA1N               | Analog output          | PGA1 inverting output                                 |  |

| 2   | PGA1P               | PGA1P               | Analog output          | PGA1 noninverting output                              |  |

| 3   | IN1N <sup>(1)</sup> | IN1N <sup>(1)</sup> | Analog input           | Differential analog negative input 1                  |  |

| 4   | IN1P <sup>(1)</sup> | IN1P <sup>(1)</sup> | Analog input           | Differential analog positive input 1                  |  |

| 5   | IN2N <sup>(1)</sup> | IN2N <sup>(1)</sup> | Analog input           | Differential analog negative input 2                  |  |

| 6   | IN2P <sup>(1)</sup> | IN2P <sup>(1)</sup> | Analog input           | Differential analog positive input 2                  |  |

| 7   | PGA2N               | PGA2N               | Analog output          | PGA2 inverting output                                 |  |

| 8   | PGA2P               | PGA2P               | Analog output          | PGA2 noninverting output                              |  |

| 9   | VREFP               | VREFP               | Analog<br>input/output | Positive reference voltage                            |  |

| 10  | VREFN               | VREFN               | Analog input           | Negative reference voltage; must be connected to AVSS |  |

| 11  | VCAP1               | VCAP1               | _                      | Analog bypass capacitor                               |  |

| 12  | AVDD                | AVDD                | Supply                 | Analog supply                                         |  |

| 13  | AVSS                | AVSS                | Supply                 | Analog ground                                         |  |

| 14  | CLKSEL              | CLKSEL              | Digital input          | Master clock select                                   |  |

| 15  | PWDN/RESET          | PWDN/RESET          | Digital input          | Power-down or system reset; active low                |  |

| 16  | START               | START               | Digital input          | Start conversion                                      |  |

| 17  | CLK                 | CLK                 | Digital input          | Master clock input                                    |  |

| 18  | CS                  | CS                  | Digital input          | Chip select                                           |  |

| 19  | DIN                 | DIN                 | Digital input          | SPI data in                                           |  |

Connect unused analog inputs to AVDD. (1)

## Pin Functions (continued)

| PIN       |                                   |                                   |                         | DESCRIPTION                                                                                               |  |

|-----------|-----------------------------------|-----------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------|--|

| NO.       | PBS (TQFP)                        | RSM (VQFN)                        | FUNCTION                | DESCRIPTION                                                                                               |  |

| 20        | SCLK                              | SCLK                              | Digital input           | SPI clock                                                                                                 |  |

| 21        | DOUT                              | DOUT                              | Digital output          | SPI data out                                                                                              |  |

| 22        | DRDY                              | DRDY                              | Digital output          | Data ready; active low                                                                                    |  |

| 23        | DVDD                              | DVDD                              | Supply                  | Digital power supply                                                                                      |  |

| 24        | DGND                              | DGND                              | Supply                  | Digital ground                                                                                            |  |

| 25        | GPIO2/RCLK2                       | GPIO2/RCLK2                       | Digital<br>input/output | General-purpose I/O 2 or resp clock 2 (ADS1292R)                                                          |  |

| 26        | GPIO1/RCLK1                       | GPIO1/RCLK1                       | Digital<br>input/output | General-purpose I/O 1 or resp clock 1 (ADS1292R)                                                          |  |

| 27        | VCAP2                             | VCAP2                             | _                       | Analog bypass capacitor                                                                                   |  |

| 28        | RLDINV                            | RLDINV                            | Analog input            | Right leg drive inverting input; connect to AVDD if not used                                              |  |

| 29        | RLDIN/<br>RLDREF                  | RLDIN/<br>RLDREF                  | Analog input            | Right leg drive input to MUX or RLD amplifier noninverting input; connect to AVDD if not used             |  |

| 30        | RLDOUT                            | RLDOUT                            | Analog output           | Right leg drive output                                                                                    |  |

| 31        | RESP_MODP/<br>IN3P <sup>(1)</sup> | RESP_MODP/<br>IN3P <sup>(1)</sup> | Analog<br>output/input  | P-side respiration excitation signal for respiration (analog output) or auxiliary input 3P (analog input) |  |

| 32        | RESP_MODN/<br>IN3N <sup>(1)</sup> | RESP_MODN/<br>IN3N <sup>(1)</sup> | Analog<br>output/input  | N-side respiration excitation signal for respiration (analog output) or auxiliary input 3N (analog input) |  |

| Power Pad | —                                 | Pad                               | —                       | Thermal pad; must be connected to AVSS                                                                    |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                |                      | MIN        | MAX        | UNIT |

|------------------------------------------------|----------------------|------------|------------|------|

| AVDD to AVSS                                   |                      | -0.3       | 5.5        | V    |

| DVDD to DGND                                   |                      | -0.3       | 3.9        | V    |

| AVSS to DGND                                   |                      | -3         | 0.2        | V    |

| Analog input to AVSS                           |                      | AVSS – 0.3 | AVDD + 0.3 | V    |

| Digital input to DVDD                          |                      | DVSS - 0.3 | DVDD + 0.3 | V    |

| Input current to any pi                        | n except supply pins |            | ±10        | mA   |

| Input ourrent                                  | Momentary            |            | ±100       | ~ ^  |

| Input current                                  | Continuous           |            | ±10        | mA   |

| Operating temperature range                    |                      | -40        | +85        | °C   |

| Maximum junction temperature (T <sub>J</sub> ) |                      |            | 150        | °C   |

| Storage temperature,                           | T <sub>stg</sub>     | -60        | +150       | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                              | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>            | ±1000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{\rm (2)}$ | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                    | MIN  | NOM | MAX  | UNIT |

|----------------|------------------------------------|------|-----|------|------|

| AVDD           | Analog power supply, AVDD to AVSS  | 2.7  | 5   | 5.25 | V    |

| DVDD           | Digital power supply, DVDD to DGND | 1.7  | 3   | 3.6  | V    |

|                | Analog input voltage               | AVSS |     | AVDD | V    |

|                | Digital input voltage              | DVSS |     | DVDD | V    |

| T <sub>A</sub> | Operating ambient temperature      | -40  |     | 85   | °C   |

## 6.4 Thermal Information

|                       |                                              | ADS1291, ADS |            |      |

|-----------------------|----------------------------------------------|--------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PBS (TQFP)   | RSM (VQFN) | UNIT |

|                       |                                              | 32 PINS      | 32 PINS    |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 68.4         | 33.7       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 25.9         | 36.4       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 30.5         | 25.2       | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.5          | 0.2        | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 24.3         | 7.4        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | n/a          | 2.2        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC package thermal metrics application report.

## 6.5 Electrical Characteristics

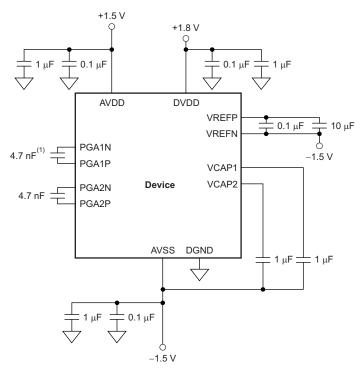

minimum and maximum specifications apply from –40°C to +85°C; typical specifications are at +25°C; all specifications are at DVDD = 1.8 V, AVDD – AVSS = 3 V<sup>(1)</sup>, V<sub>REF</sub> = 2.42 V, external  $f_{CLK}$  = 512 kHz, data rate = 500 SPS,  $C_{FILTER}$  = 4.7 nF<sup>(2)</sup>, and gain = 6 (unless otherwise noted)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PARAMETER                             | TEST CONDITIONS                                                      | MIN                  | ТҮР            | MAX  | UNIT         |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------|----------------------|----------------|------|--------------|--|--|--|

| Image: Section of the Wise HoldonTest ConditionsMinTYPMAXUnitANALOG INPUTS $\pm V_{REF}$ / gainVInput common-mode range $\pm V_{REF}$ / gainVInput common-mode rangeSee the Input Common-Mode Range<br>subsection of the PGA Settings and Input<br>Range sectionVInput capacitance20pFInput bias current (PGA chop = 8 kHz) $T_A = +25^{\circ}C$ , input = 1.5 V $\pm 1$ nAChop rates other than 8 kHzSee Pace Detect sectionNODC input impedanceNo pull-up or pull-down current source1000MQCurrent source lead-off detection (nA),<br>AVS + 0.6 V < AIN < AVDD - 0.6 V |                                       |                                                                      |                      |                |      |              |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       |                                                                      | ±V <sub>REF</sub>    | / gain         |      | V            |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Input common-mode range               |                                                                      | subsection of the PG | A Settings and |      |              |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Input capacitance                     |                                                                      |                      | 20             |      | pF           |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       | $T_A = +25^{\circ}C$ , input = 1.5 V                                 |                      |                | ±200 | pА           |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Input bias current (PGA chop = 8 kHz) | $T_A = -40^{\circ}C$ to +85°C, input = 1.5 V                         |                      | ±1             |      | nA           |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       | Chop rates other than 8 kHz                                          | See Pace D           | etect section  |      |              |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       | No pull-up or pull-down current source                               | 1000                 |                |      | MΩ           |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DC input impedance                    |                                                                      |                      | 500            |      | MΩ           |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       |                                                                      |                      | 100            |      | MΩ           |  |  |  |

| PGA PE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RFORMANCE                             |                                                                      |                      |                |      |              |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Gain settings                         |                                                                      | 1, 2, 3, 4           | , 6, 8, 12     |      |              |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Bandwidth                             | (see PGA Settings and Input Range section                            |                      | 8.5            |      | kHz          |  |  |  |

| ADC PE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RFORMANCE                             |                                                                      |                      |                |      |              |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Resolution                            |                                                                      | 24                   |                |      | Bits         |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Data rate                             | f <sub>CLK</sub> = 512 kHz                                           | 125                  |                | 8000 | SPS          |  |  |  |

| CHANN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | EL PERFORMANCE (DC Performance)       |                                                                      |                      |                |      |              |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       | Gain = $6^{(3)}$ , 10 seconds of data                                |                      | 8              |      | $\mu V_{PP}$ |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Input-referred noise                  | Gain = 6, 256 points, 0.5 seconds of data                            |                      | 8              | 11   | $\mu V_{PP}$ |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       | Gain settings other than 6,<br>data rates other than 500 SPS         | See Noise Meas       | urements secti | on   |              |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Integral nonlinearity                 | Full-scale with gain = 6, best fit                                   |                      | 2              |      | ppm          |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Offset error                          |                                                                      |                      | ±100           |      | μV           |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Offset error drift                    |                                                                      |                      | 2              |      | μV/°C        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Offset error with calibration         |                                                                      |                      | 15             |      | μV           |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Gain error                            | Excluding voltage reference error                                    |                      | ±0.1           | ±0.2 | % of FS      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Gain drift                            | Excluding voltage reference drift                                    |                      | 2              |      | ppm/°C       |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Gain match between channels           |                                                                      |                      | 0.2            |      | % of FS      |  |  |  |

| CHANN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | EL PERFORMANCE (AC performance)       | · ·                                                                  |                      |                | I    |              |  |  |  |

| CMRR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Common-mode rejection ratio           | $f_{CM} = 50 \text{ Hz and } 60 \text{ Hz}^{(4)}$                    | 105                  | 120            |      | dB           |  |  |  |

| PSRR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Power-supply rejection ratio          | $f_{PS} = 50$ Hz and 60 Hz                                           |                      | 90             |      | dB           |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Crosstalk                             | f <sub>IN</sub> = 50 Hz and 60 Hz                                    |                      | -120           |      | dB           |  |  |  |

| SNR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Signal-to-noise ratio                 | f <sub>IN</sub> = 10 Hz input, gain = 6                              |                      | 107            |      | dB           |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       | 10 Hz, –0.5 dBFs, C <sub>FILTER</sub> = 4.7nF                        |                      | -104           |      | dB           |  |  |  |

| THD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Total harmonic distortion             | 100 Hz, –0.5 dBFs, C <sub>FILTER</sub> = 4.7nF                       |                      | -95            |      | dB           |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       | ADS1292R channel 1, 10 Hz, -0.5 dBFS,<br>C <sub>FILTER</sub> = 47 nF |                      | -82            |      | dB           |  |  |  |

(1) Performance is applicable for 5-V operation as well. Production testing for limits is performed at 3 V.

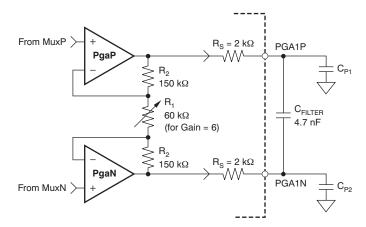

(2) C<sub>FILTER</sub> is the capacitor accross the PGA outputs; see the PGA Settings and Input Range section for details.

(3) Noise data measured in a 10-second interval. Test not performed in production. Input-referred noise is calculated with input shorted (without electrode resistance) over a 10-second interval.

(4) CMRR is measured with a common-mode signal of AVSS + 0.3 V to AVDD – 0.3 V. The values indicated are the minimum of the two channels.

## **Electrical Characteristics (continued)**

minimum and maximum specifications apply from –40°C to +85°C; typical specifications are at +25°C; all specifications are at DVDD = 1.8 V, AVDD – AVSS = 3 V<sup>(1)</sup>, V<sub>REF</sub> = 2.42 V, external  $f_{CLK}$  = 512 kHz, data rate = 500 SPS,  $C_{FILTER}$  = 4.7 nF<sup>(2)</sup>, and gain = 6 (unless otherwise noted)

|                 | PARAMETER                     | TEST CONDITIONS                                                                                                                                        | MIN TYP                | MAX        | UNIT              |

|-----------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------|-------------------|

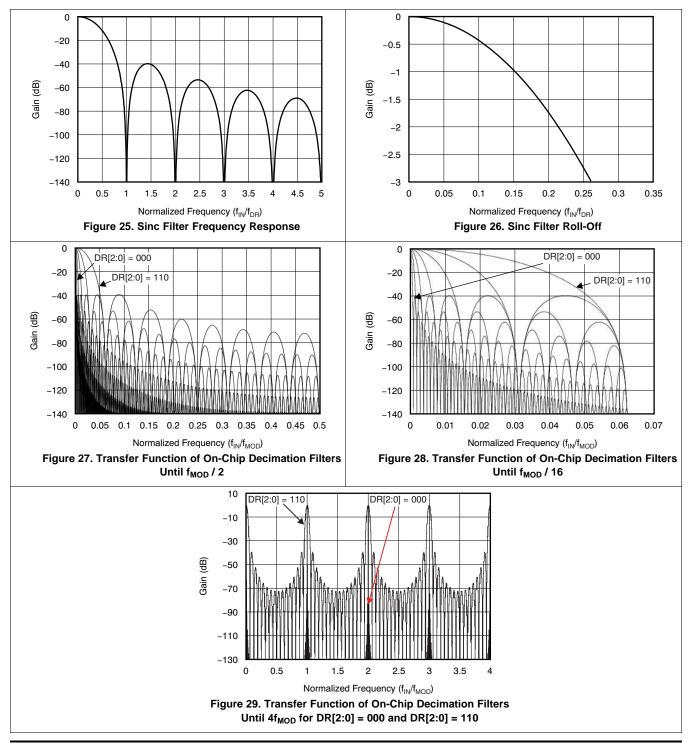

| DIGITAL         | FILTER                        |                                                                                                                                                        | l                      |            |                   |

|                 | -3-dB bandwidth               |                                                                                                                                                        | 0.262 f <sub>DF</sub>  | 1          | Hz                |

|                 | Digital filter settling       | Full setting                                                                                                                                           | 4                      | Ļ          | Conversion        |

| RIGHT L         | EG DRIVE (RLD) AMPLIFIER      |                                                                                                                                                        | I                      |            |                   |

|                 | RLD integrated noise          | BW = 150 Hz                                                                                                                                            | 1.4                    |            | μV <sub>RMS</sub> |

| GBP             | Gain bandwidth product        | 50 kΩ    10 pF load, gain = 1                                                                                                                          | 100                    | )          | kHz               |

| SR              | Slew rate                     | 50 kΩ    10 pF load, gain = 1                                                                                                                          | 0.07                   | ,          | V/µs              |

| THD             | Total harmonic distortion     | f <sub>IN</sub> = 100 Hz, gain = 1                                                                                                                     | -85                    | i          | dB                |

| CMIR            | Common-mode input range       |                                                                                                                                                        | AVSS + 0.3             | AVDD - 0.3 | V                 |

|                 | Common-mode resistor matching | Internal 200-kΩ resistor matching                                                                                                                      | 0.1                    |            | %                 |

| I <sub>SC</sub> | Short-circuit current         |                                                                                                                                                        | 1.1                    |            | mA                |

|                 | Quiescent power consumption   |                                                                                                                                                        | 5                      | ;          | μA                |

| LEAD-O          | FF DETECT                     |                                                                                                                                                        |                        |            |                   |

|                 | Frequency                     | See Register Map section for settings                                                                                                                  | 0, f <sub>DR</sub> / 4 |            | kHz               |

|                 |                               | ILEAD_OFF [1:0] = 00                                                                                                                                   | 6                      | ;          | nA                |

|                 |                               | ILEAD_OFF [1:0] = 01                                                                                                                                   | 22                     | 2          | nA                |

|                 | Current                       | ILEAD_OFF [1:0] = 10                                                                                                                                   | 6                      | ;          | μA                |

|                 |                               | ILEAD_OFF [1:0] = 11                                                                                                                                   | 22                     | 2          | μA                |

|                 | Current accuracy              |                                                                                                                                                        | ±10                    | )          | %                 |

|                 | Comparator threshold accuracy |                                                                                                                                                        | ±10                    | )          | mV                |

| RESPIRA         | ATION (ADS1292R)              |                                                                                                                                                        |                        |            |                   |

|                 |                               | Internal source                                                                                                                                        | 32, 64                 |            | kHz               |

|                 | Frequency                     | External source                                                                                                                                        | 32                     | 64         | kHz               |

|                 | Phase shift                   | See Register Map section for settings                                                                                                                  | 0 112.5                | 168.75     | Degrees           |

|                 | Impedance range               | I <sub>RESP</sub> = 30 µA                                                                                                                              | 2000                   | 10,000     | Ω                 |

|                 | Impedance measurement noise   | 0.05-Hz to 2-Hz brick wall filter, 32-kHz<br>modulation clock, phase = 112.5,<br>using $I_{RESP}$ = 30 µA with 2-k $\Omega$ baseline load,<br>gain = 4 | 40                     | )          | $m\Omega_{PP}$    |

|                 | Maximum modulator current     | Using Internal reference                                                                                                                               | 100                    | )          | μΑ                |

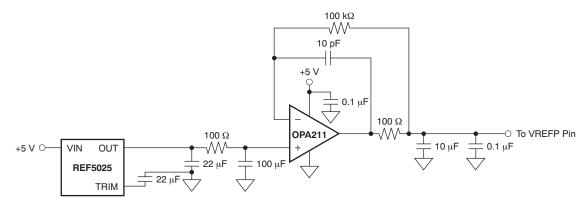

| EXTERN          |                               | 1 -                                                                                                                                                    | 1                      |            |                   |

|                 |                               | 3-V supply V <sub>REF</sub> = (VREFP – VREFN)                                                                                                          | 2 2.5                  | VDD - 0.3  | V                 |

|                 | Reference input voltage       | 5-V supply V <sub>REF</sub> = (VREFP – VREFN)                                                                                                          | 2 4                    | VDD - 0.3  | V                 |

| VREFN           | Negative input                |                                                                                                                                                        | AVSS                   | -          | V                 |

| VREFP           | Positive input                |                                                                                                                                                        | AVSS + 2.5             | ;          | V                 |

|                 | Input impedance               |                                                                                                                                                        | 120                    |            | kΩ                |

## **Electrical Characteristics (continued)**

minimum and maximum specifications apply from –40°C to +85°C; typical specifications are at +25°C; all specifications are at DVDD = 1.8 V, AVDD – AVSS = 3 V<sup>(1)</sup>, V<sub>REF</sub> = 2.42 V, external  $f_{CLK}$  = 512 kHz, data rate = 500 SPS,  $C_{FILTER}$  = 4.7 nF<sup>(2)</sup>, and gain = 6 (unless otherwise noted)

|                 | PARAMETER                  | R                        | TEST CONDITIONS                                                       | MIN        | TYP         | MAX       | UNIT   |

|-----------------|----------------------------|--------------------------|-----------------------------------------------------------------------|------------|-------------|-----------|--------|

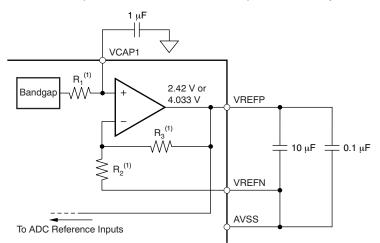

| INTERN          | AL REFERENCE               |                          | T                                                                     |            |             |           |        |

|                 | Output voltage             |                          | Register bit CONFIG2.VREF_4V = 0                                      |            | 2.42        |           | V      |

|                 | Oulput Voltage             |                          | Register bit CONFIG2.VREF_4V = 1                                      |            | 4.033       |           | V      |

|                 | Output current drive       |                          | Available for external use                                            |            | 100         |           | μA     |

|                 | V <sub>REF</sub> accuracy  |                          |                                                                       |            | ±0.5        |           | %      |

|                 | Internal reference drift   |                          | $-40^{\circ}C \le T_{A} \le +85^{\circ}C$                             |            | 45          |           | ppm/°C |

|                 | Start-up time              |                          | Settled to 0.2% with 10-µF capacitor on VREFP pin                     |            | 100         |           | ms     |

|                 | Quiescent current cons     | sumption                 |                                                                       |            | 20          |           | μΑ     |

| SYSTEN          | MONITORS                   |                          |                                                                       |            |             |           |        |

|                 | Analog supply reading      | error                    |                                                                       |            | 1           |           | %      |

|                 | Digital supply reading     | error                    |                                                                       |            | 1           |           | %      |

|                 |                            |                          | From power-supply ramp after power-on reset (POR) to DRDY low         |            | 32          |           | ms     |

|                 | Device wake up             |                          | From power-down mode to DRDY low                                      |            | 10          |           | ms     |

|                 |                            |                          | From STANDBY mode to DRDY low                                         |            | 10          |           | ms     |

|                 | VCAP1 settling time        |                          | 1% accuracy                                                           |            | 0.5         |           | S      |

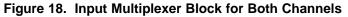

|                 | Temperature sensor         | Voltage                  | $T_A = +25^{\circ}C$                                                  |            | 145         |           | mV     |

|                 | reading                    | Coefficient              |                                                                       |            | 490         |           | μV/°C  |

| TEST SI         | GNAL                       | 1                        |                                                                       | 1          |             |           |        |

|                 | Signal frequency           |                          | See Register Map section for settings                                 | At c       | dc and 1 Hz |           | Hz     |

|                 | Signal voltage             |                          | See Register Map section for settings                                 |            |             | mV        |        |

|                 | Accuracy                   |                          |                                                                       |            | ±2          |           | %      |

| CLOCK           | -                          |                          |                                                                       |            |             |           |        |

|                 | Internal oscillator clock  | frequency                | Nominal frequency                                                     |            | 512         |           | kHz    |

|                 |                            |                          | T <sub>A</sub> = +25°C                                                |            |             | ±0.5      | %      |

|                 | Internal clock accuracy    | /                        | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$ |            |             | ±1.5      | %      |

|                 | Internal oscillator start- | up time                  |                                                                       |            | 32          |           | μS     |

|                 | Internal oscillator powe   | -                        |                                                                       |            | 30          |           | μW     |

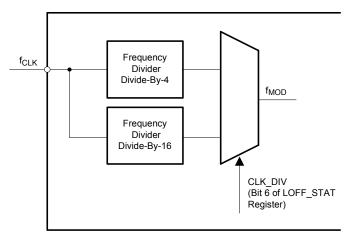

|                 |                            |                          | CLKSEL pin = 0, CLK_DIV = 0                                           | 485        | 512         | 562.5     | kHz    |

|                 | External clock input fre   | equency                  | CLKSEL pin = 0, CLK_DIV = 1                                           | 1.94       | 2.048       | 2.25      | MHz    |

| DIGITAL         | INPUT/OUTPUT               |                          |                                                                       |            |             |           |        |

| V <sub>IH</sub> |                            | DVDD = 1.8 V to 3.6 V    |                                                                       | 0.8 DVDD   | D           | VDD + 0.1 | V      |

| V <sub>IL</sub> |                            | DVDD = 1.8 V to<br>3.6 V |                                                                       | -0.1       |             | 0.2 DVDD  | V      |

| V <sub>IH</sub> |                            | DVDD = 1.7 V to<br>1.8 V |                                                                       | DVDD - 0.2 |             |           | V      |

| V <sub>IL</sub> | Logic level                | DVDD = 1.7 V to<br>1.8 V |                                                                       |            |             | 0.2       | V      |

| V <sub>он</sub> |                            | DVDD = 1.7 V to<br>3.6 V | I <sub>OH</sub> = -500 μA                                             | 0.9 DVDD   |             |           | V      |

| V <sub>OL</sub> |                            | DVDD = 1.7 V to<br>3.6 V | I <sub>OL</sub> = +500 μA                                             |            |             | 0.1 DVDD  | V      |

| I <sub>IN</sub> |                            | Input current            | 0 V < V <sub>DigitalInput</sub> < DVDD                                | -10        |             | +10       | μΑ     |

| POWER           | -SUPPLY REQUIREMEN         | ITS                      |                                                                       |            |             |           |        |

| AVDD            | Analog supply              | AVDD – AVSS              |                                                                       | 2.7        | 3           | 5.25      | V      |

| DVDD            | Digital supply             | DVDD – DGND              |                                                                       | 1.7        | 1.8         | 3.6       | V      |

| -               | AVDD – DVDD                |                          |                                                                       | -2.1       |             | 3.6       | V      |

## **Electrical Characteristics (continued)**

minimum and maximum specifications apply from –40°C to +85°C; typical specifications are at +25°C; all specifications are at DVDD = 1.8 V, AVDD – AVSS = 3 V<sup>(1)</sup>, V<sub>REF</sub> = 2.42 V, external  $f_{CLK}$  = 512 kHz, data rate = 500 SPS,  $C_{FILTER}$  = 4.7 nF<sup>(2)</sup>, and gain = 6 (unless otherwise noted)

|           | PARAMETER              | 1                 | TEST CONDITIONS                       | MIN      | TYP  | MAX  | UNIT |

|-----------|------------------------|-------------------|---------------------------------------|----------|------|------|------|

| SUPPLY CU | JRRENT (RLD Amplif     | ier Turned Off)   |                                       |          |      |      |      |

|           |                        | ADS1292 and       | AVDD – AVSS = 3 V                     |          | 205  |      | μA   |

| 1,        | AVDD                   | ADS1292R          | AVDD – AVSS = 5 V                     |          | 250  |      | μA   |

|           |                        | ADS1292 and       | DVDD = 3.3 V                          |          | 75   |      | μA   |

| Ic        | DOVDD                  | ADS1292R          | DVDD = 1.8 V                          |          | 32   |      | μA   |

| POWER DIS | SIPATION (Analog S     | Supply = 3 V, RLD | Amplifier Turned Off)                 |          |      | 1    |      |

|           |                        | ADS1292 and       | Normal mode                           |          | 670  | 740  | μW   |

| G         | Quiescent power        | ADS1292R          | Standby mode                          |          | 160  |      | μW   |

|           | lissipation            | 100/00/           | Normal mode                           |          | 450  | 495  | μW   |

|           |                        | ADS1291           | Standby mode                          |          | 160  |      | μW   |

| C         | Quiescent power        | ADS1292R          | Normal mode                           |          | 335  |      | μW   |

|           | lissipation, per       | ADS1292           | Normal mode                           |          | 335  |      | μW   |

| с         | hannel                 | ADS1291           | Normal mode                           |          | 450  |      | μW   |

| POWER DIS | SIPATION (Analog S     | Supply = 5 V, RLD | Amplifier Turned Off)                 | <b>I</b> |      |      |      |

|           |                        | ADS1292 and       | Normal mode                           |          | 1300 |      | μW   |

| G         | Quiescent power        | ADS1292R          | Standby mode                          |          | 340  |      | μW   |

| d         | lissipation            | 100/00/           | Normal mode                           |          | 950  |      | μW   |

|           |                        | ADS1291           | Standby mode                          |          | 340  |      | μW   |

| C         | Quiescent power        | ADS1292R          | Normal mode                           |          | 670  |      | μW   |

| d         | lissipation, per       | ADS1292           | Normal mode                           |          | 670  |      | μW   |

| с         | hannel                 | ADS1291           | Normal mode                           |          | 860  |      | μW   |

| POWER DIS | SIPATION IN POWE       | R-DOWN MODE       | - I                                   | <u>и</u> |      |      |      |

|           |                        | DVDD = 1.8 V      |                                       |          | 1    |      | μW   |

| A         | Analog supply = 3 V    | DVDD = 3.3 V      |                                       |          | 4    |      | μW   |

|           |                        | DVDD = 1.8 V      |                                       |          | 5    |      | μW   |

| A         | Analog supply = 5 V    | DVDD = 3.3 V      |                                       |          | 10   |      | μW   |

| EMPERAT   | URE                    |                   | · · · · · · · · · · · · · · · · · · · |          |      |      |      |

| S         | Specified temperature  | range             |                                       | -40      |      | +85  | °C   |

| C         | Operating temperature  | range             |                                       | -40      |      | +85  | °C   |

| S         | Storage temperature ra | ange              |                                       | -60      |      | +150 | °C   |

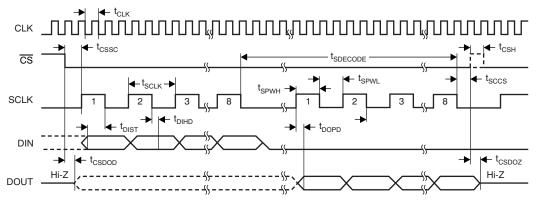

## 6.6 Timing Requirements

specifications apply from –40°C to +85°C; load on D\_{OUT} = 20 pF || 100 k $\Omega$

|                      |                                                             | 2.7 V ≤ | DVDD ≤ 3.6 V | 1.7 V | ≤ DVDD ≤ | ≤ 2 V |                   |

|----------------------|-------------------------------------------------------------|---------|--------------|-------|----------|-------|-------------------|

|                      |                                                             | MIN     | NOM MAX      | MIN   | NOM      | MAX   | UNIT              |

|                      | Master clock period (CLK_DIV bit of LOFF_STAT register = 0) | 1775    | 2170         | 1775  |          | 2170  | ns                |

| t <sub>CLK</sub>     | Master clock period (CLK_DIV bit of LOFF_STAT register = 1) | 444     | 542          | 444   |          | 542   | ns                |

| t <sub>CSSC</sub>    | CS low to first SCLK, setup time                            | 6       |              | 17    |          |       | ns                |

| t <sub>SCLK</sub>    | SCLK period                                                 | 50      |              | 66.6  |          |       | ns                |

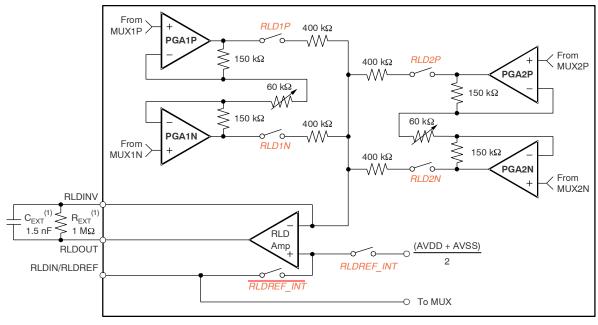

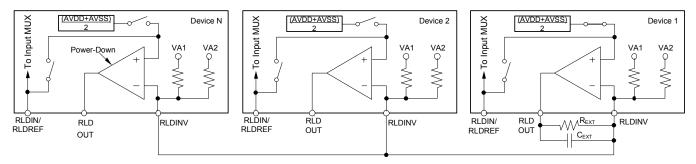

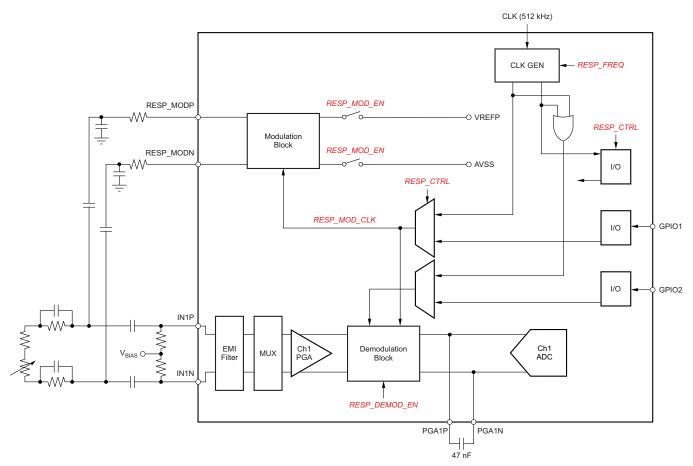

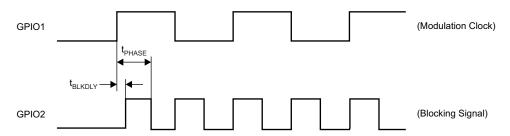

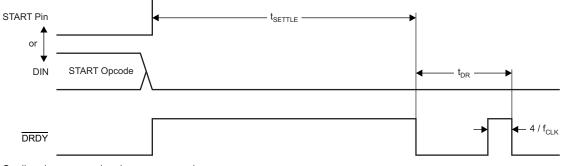

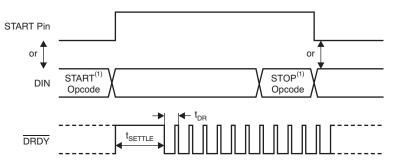

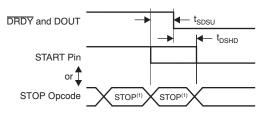

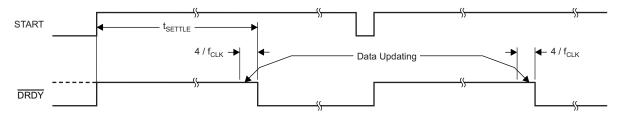

| t <sub>SPWH, L</sub> | SCLK pulse width, high and low                              | 15      |              | 25    |          |       | ns                |