# AM335x Power Estimation Tool

### **ABSTRACT**

The Power Estimation Tool (PET) allows you to gain insight into the power consumption of select Sitara processors. The tool includes the ability for you to choose multiple application scenarios and understand the power consumption as well as how advanced power saving techniques can be applied to further reduce overall power consumption.

|    | Contents                                                    |    |

|----|-------------------------------------------------------------|----|

| 1  | Introduction                                                | 2  |

| 2  | Input Spreadsheet                                           |    |

| 3  | Spreadsheet Upload                                          | 8  |

| 4  | Power Analysis Report                                       | 8  |

| 5  | References                                                  | 10 |

|    | List of Figures                                             |    |

| 1  | Macro Buttons                                               | 2  |

| 2  | Section D of the AM335x PET Input Spreadsheet               | 8  |

|    | List of Tables                                              |    |

| 1  | Section A of AM335x PET Input Spreadsheet                   | 3  |

| 2  | Typical Power Modes                                         | 4  |

| 3  | Section B of the AM335x Input Spreadsheet                   | 5  |

| 4  | PG1.0 VDD_CORE Operating Performance Points for ZCZ Package | 5  |

| 5  | PG1.0 VDD_MPU Operating Performance Points for ZCZ Package  | 5  |

| 6  | PG1.0 VDD_CORE Operating Performance Points for ZCE Package | 6  |

| 7  | PG2.1 VDD_CORE Operating Performance Points for ZCZ Package | 6  |

| 8  | PG2.1 VDD_MPU Operating Performance Points for ZCZ Package  |    |

| 9  | PG2.1 VDD_CORE Operating Performance Points for ZCE Package | 7  |

| 10 | Section C of the AM335x PET Input Spreadsheet               | 7  |

| 11 | Power Estimation Report                                     | 9  |

| 12 | Maximum Module Utilization                                  | 10 |

#### **Trademarks**

Cortex is a trademark of ARM Limited.

All other trademarks are the property of their respective owners.

Introduction www.ti.com

#### 1 Introduction

PET is comprised of three modules:

Input Spreadsheet – Downloadable spreadsheet in which users input device parameters needed for their application. Parameters include IP activities and loadings, desired power states, and power management usages. For advanced users, multiple operating conditions can be applied along with time slots for each state.

- 2. Spreadsheet Upload Upon completion of the input spreadsheet, you can then upload the spreadsheet to TI for the power consumption analysis. Registration and legal agreement acceptance is required for the upload.

- 3. Power Analysis Report Contains the information on power consumption based on the spreadsheet upload. The report that includes leakage, active and total average power, as well as power management voltages, will be sent to you via email.

NOTE: The AM335x PET applies to AM3352, AM3354, AM3356, AM3357, AM3358 and AM3359 devices.

## 2 Input Spreadsheet

**Download AM335x PET Input Spreadsheet** here. There are two types of input spreadsheets: the Simplified input spreadsheet is designed for estimating the power for a single application scenario and the Advanced input spreadsheet has additional columns (slots) for multiple application scenarios. The power estimates from the Advanced spreadsheet will be an average power of the multiple application scenarios (slots) configured in the input spreadsheet.

The input spreadsheet consists of four sections: High-Level System Configuration, Processors, Peripherals, and Analog Modules. To use the input spreadsheet, modify the input fields with their appropriate usage parameters. Cells that are designed for user input are light green in color. Simply configure the light green cells to a value most closely aligned with your intended scenario.

Briefly, the purpose of each of the four sections is:

- Section A: configure the high-level system configuration such as junction temperature and power estimation mode

- Section B: configure processor subsystem components

- Section C: configure peripherals

- · Section D: configure analog modules

#### 2.1 Macro Buttons

The spreadsheet includes macros. If you can not run macros, review your excel security settings described in the following articles:

Change macro security settings in Excel (Office 2007)

Enable macros to run (Office 2003).

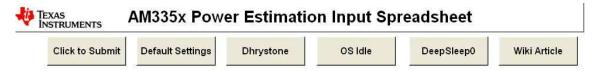

The input spreadsheet has command buttons to run macros as shown in Figure 1.

Figure 1. Macro Buttons

- "Click to Submit" Navigate to PET spreadsheet upload page.

- "Default Settings" Clear all settings and configure them to the default values.

- "Dhrystone" Configure settings to the Dhrystone benchmark example application scenario. [MPU intensive, high power use case]

www.ti.com Input Spreadsheet

"OS Idle" - Configure settings to Linux OS Idle example application scenario. [MPU idle, medium power use case]

- "DeepSleep0" Configure settings to DS0 example application scenario. [MPU off, low power use case]

- "Wiki Article" Navigate to this wiki article.

## 2.2 Section A: High-Level System Configuration

This section allows you to select the device revision, choose DDR type and loading, set a junction temperature (not ambient temperature) between 0°C and 105°C, power estimation mode, SmartReflex AVS (Adaptive Voltage Scaling) and Dual-Voltage I/O VDDSHVx voltages as shown in Table 1.

Table 1. Section A of AM335x PET Input Spreadsheet [1] [2]

| Device Revision           | PG2.1  |

|---------------------------|--------|

| DDR Type                  | DDR3   |

| DDR Loading               | 1      |

| Junction Temperature (°C) | 25     |

| Power Estimation Mode     | Тур    |

| Smart Reflex              | off    |

| VDDSHV1 Voltage (V)       | 1.8    |

| VDDSHV2 Voltage (V)       | 1.8    |

| VDDSHV3 Voltage (V)       | 1.8    |

| VDDSHV4 Voltage (V)       | 1.8    |

| VDDSHV5 Voltage (V)       | 1.8    |

| VDDSH61 Voltage (V)       | 1.8    |

| Power Mode                | Active |

| Dynamic Power Switching   | Off    |

- (1) MAX: Worst case power consumption

- (2) TYP: Typical case power consumption

- Device Revision: PG2.1, PG1.0 (evaluate PG2.1)

- DDR Type: mDDR, DDR2, DDR3, DDR3L,None

- DDR Loading: 0, 1, 2 (corresponds to the number of DDR devices in the system)

- Junction Temperature (°C): 0 ~ 105 (negative values are not supported in the tool)

- Power Estimation Mode: Max, Typ ('Max' accounts for the worst-case silicon process variation)

- SmartReflex: On, Off

- VDDSHVx Voltage [V]: 1.8 or 3.3

- Power Mode: Active, Standby, DeepSleep1, DeepSleep0, RTC Only

- Dynamic Power Switching: On, Off (currently only supported for PD\_GFX)

Input Spreadsheet www.ti.com

## **Table 2. Typical Power Modes**

| Power Modes | Application State                                                                                                                                                                                                                                                                                                                          | Power Domains, Clocks, and Voltage Supply States                                                                                                                                                                                                                 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Active      | All Features                                                                                                                                                                                                                                                                                                                               | Power supplies: All power supplies are ON. VDD_MPU = 1.1 V (nom) VDD_CORE = 1.1 V (nom) Clocks: Main Oscillator (OSC0) = ON All DPLLs are locked. Power domains: PD_PER = ON PD_MPU = ON PD = GFX = ON or OFF (depending on use case) PD_WKUP = ON DDR is active |

| Standby     | DDR memory is in self-refresh and contents are preserved. Wakeup from any GPIO. Cortex™-A8 context and register contents are lost and must be saved before entering standby. On exit, context must be restored from DDR. For wakeup, boot ROM executes and branches to system resume.                                                      | Power supplies: All power supplies are ON. VDD_MPU = 0.95 V (nom) VDD_CORE = 0.95 V (nom) Clocks: Main Oscillator (OSC0) = ON All DPLLs are in bypass. Power domains: PD_PER = ON PD_MPU = OFF PD = GFX = OFF PD_WKUP = ON DDR is in self-refresh.               |

| Deepsleep1  | On-chip peripheral registers are preserved. Cortex-A8 context/registers are lost, so the application needs to save them to the L3 OCMC RAM or DDR before entering DeepSleep. DDR is in self-refresh. For wakeup, boot ROM executes and branches to system resume.                                                                          | Power supplies: All power supplies are ON. VDD_MPU = 0.95 V (nom) VDD_CORE = 0.95 V (nom) Clocks: Main Oscillator (OSC0) = OFF All DPLLs are in bypass. Power domains: PD_PER = ON PD_MPU = OFF PD = GFX = OFF PD_WKUP = ON DDR is in self-refresh.              |

| Deepsleep0  | PD_PER peripheral and Cortex-A8/MPU register information will be lost. On-chip peripheral register (context) information of PD-PER domain needs to be saved by application to SDRAM before entering this mode. DDR is in self-refresh. For wakeup, boot ROM executes and branches to peripheral context restore followed by system resume. | Power supplies: All power supplies are ON. VDD_MPU = 0.95 V (nom) VDD_CORE = 0.95 V (nom) Clocks: Main Oscillator (OSC0) = OFF All DPLLs are in bypass. Power domains: PD_PER = ON PD_MPU = OFF PD = GFX = OFF PD_WKUP = ON DDR is in self-refresh.              |

| RTC-Only    | RTC timer remains active and all other device functionality is disabled.                                                                                                                                                                                                                                                                   | Power supplies: All power supplies are OFF except. VDDS_RTC, VDD_MPU = 0 V VDD_CORE = 0 V Clocks: Main Oscillator (OSC0) = OFF Power domains: All power domains are OFF.                                                                                         |

www.ti.com Input Spreadsheet

The spreadsheet presents information only for the full-featured devices in the AM335x family. However, since the spreadsheet breaks out the power consumption due to each module in the full-featured device, estimates for the other devices in the AM335x family can be obtained by setting zero for the modules not present in the device under consideration. This ensures that active power from the non-applicable modules are not included in the power tally. The device differences are summarized at the overview section in AM335x Device Evaluation Wiki.

#### 2.3 Section B: Processors

This section allows you to set an operating performance point (OPP) for MPU domain and CORE domain, MPU utilization and SGX utilization as shown in Table 3.

Table 3. Section B of the AM335x Input Spreadsheet

| CORE OPP            | OPP100 |

|---------------------|--------|

| MPU OPP             | OPP100 |

| MPU Frequency (Mhz) | 600    |

| ARM Subsystem  | Utilization % |

|----------------|---------------|

| Cortex-A8      | 0             |

| Cortex-A8 NEON | 0             |

| SGX Subsystem (for SGX-enabled devices only) | Utilization % |

|----------------------------------------------|---------------|

| SGX                                          | 0             |

The OPP options supported for the MPU voltage domain (VDD\_MPU) and the CORE voltage domain (VDD\_CORE) are shown in the following tables.

Table 4. PG1.0 VDD\_CORE Operating Performance Points for ZCZ Package [1]

| VDD_CORE                  |         | VDD_CORE |         |                 |          |          |                        |

|---------------------------|---------|----------|---------|-----------------|----------|----------|------------------------|

| OPP Device<br>Rev "Blank" | MIN     | NOM      | MAX     | DDR3, DDR3L [2] | DDR2 [2] | mDDR [2] | L3 and L4              |

| OPP100                    | 1.056 V | 1.100 V  | 1.144 V | 400 MHz         | 266 MHz  | 200 MHz  | 200 MHz and<br>100 MHz |

| OPP50                     | 0.912 V | 0.950 V  | 0.988 V | _               | 125 MHz  | 90 MHz   | 100 MHZ and<br>50 MHz  |

<sup>(1)</sup> Frequencies in this table indicate maximum performance for a given OPP condition.

Table 5. PG1.0 VDD\_MPU Operating Performance Points for ZCZ Package [1]

| VDD CORE OPP       |         |         |         |          |

|--------------------|---------|---------|---------|----------|

| Device Rev "Blank" | MIN     | NOM     | MAX     | ARM (A8) |

| Turbo              | 1.210 V | 1.260 V | 1.326 V | 720 MHz  |

| OPP120             | 1.152 V | 1.200 V | 1.248 V | 600 MHz  |

| OPP100 [2]         | 1.056 V | 1.100 V | 1.144 V | 500 MHz  |

| OPP100 [3]         | 1.056 V | 1.100 V | 1.144 V | 275 MHz  |

<sup>(1)</sup> Frequencies in this table indicate maximum performance for a given OPP condition.

<sup>(2)</sup> This parameter represents the maximum memory clock frequency. Since data is transferred on both edges of the clock, double-data rate (DDR), the maximum data rate is two times the maximum memory clock frequency defined in this table.

<sup>(2)</sup> Applies to all orderable AM335\_ZCZ\_50 (500-MHz speed grade) or higher devices.

<sup>(3)</sup> Applies to all orderable AM335\_ZCZ\_27 (275-MHz speed grade) devices.

Input Spreadsheet www.ti.com

#### Table 6. PG1.0 VDD\_CORE Operating Performance Points for ZCE Package [1]

| VDD_CORE             | VDD_MPU [2] |         |         |          |                    |          |          |                        |

|----------------------|-------------|---------|---------|----------|--------------------|----------|----------|------------------------|

| OPP Rev "A" or Newer | MIN         | NOM     | MAX     | ARM (A8) | DDR3,<br>DDR3L [3] | DDR2 [3] | mDDR [3] | L3 and L4              |

| OPP100               | 1.056 V     | 1.100 V | 1.144 V | 500 MHz  | 400 MHz            | 266 MHz  | 200 MHz  | 200 MHz and<br>100 MHz |

| OPP100               | 1.056 V     | 1.100 V | 1.144 V | 275 MHz  | 400 MHz            | 266 MHz  | 200 MHz  | 200 MHz and<br>100 MHz |

- (1) Frequencies in this table indicate maximum performance for a given OPP condition.

- (2) VDD\_MPU is emerged with VDD\_CORE on the ZCE package.

- (3) This parameter represents the maximum memory clock frequency. Since data is transferred on both edges of the clock, double-data rate (DDR), the maximum data rate is two times the maximum memory clock frequency defined in this table.

Table 7. PG2.1 VDD\_CORE Operating Performance Points for ZCZ Package [1]

| VDD_MPP              | VDD_CORE    |         |                 | DDD0 DDD01 |          |           |                        |

|----------------------|-------------|---------|-----------------|------------|----------|-----------|------------------------|

| OPP Rev "A" or Newer | MIN NOM MAX |         | DDR3, DDR3L [2] | DDR2 [2]   | mDDR [2] | L3 and L4 |                        |

| OPP100               | 1.056 V     | 1.100 V | 1.144 V         | 400 MHz    | 266 MHz  | 200 MHz   | 200 MHz and<br>100 MHz |

| OPP50                | 0.912 V     | 0.950 V | 0.988 V         | _          | 125 MHz  | 90 MHz    | 100 MHZ and<br>50 MHz  |

- (1) Frequencies in this table indicate maximum performance for a given OPP condition.

- (2) This parameter represents the maximum memory clock frequency. Since data is transferred on both edges of the clock, double-data rate (DDR), the maximum data rate is two times the maximum memory clock frequency defined in this table.

Table 8. PG2.1 VDD\_MPU Operating Performance Points for ZCZ Package [1]

| VDD CORE OPP     |         |         |         |          |

|------------------|---------|---------|---------|----------|

| Rev "A" or Newer | MIN     | NOM     | MAX     | ARM (A8) |

| Nitro            | 1.272 V | 1.325 V | 1.378 V | 1 GHz    |

| Turbo            | 1.210 V | 1.260 V | 1.326 V | 800 MHz  |

| OPP120           | 1.152 V | 1.200 V | 1.248 V | 720 MHz  |

| OPP100 [2]       | 1.056 V | 1.100 V | 1.144 V | 600 MHz  |

| OPP100 [3]       | 1.056 V | 1.100 V | 1.144 V | 300 MHz  |

| OPP50            | 0.912 V | 0.950 V | 0.988 V | 300 MHz  |

- (1) Frequencies in this table indicate maximum performance for a given OPP condition.

- (2) Applies to all orderable AM335\_ZCZ\_50 (500-MHz speed grade) or higher devices.

- (3) Applies to all orderable AM335\_ZCZ\_27 (275-MHz speed grade) devices.

www.ti.com Input Spreadsheet

Table 9. PG2.1 VDD\_CORE Operating Performance Points for ZCE Package [1]

| VDD_CORE                  | VDD_MPU [2] |         |         |          |                    |          |          |                        |

|---------------------------|-------------|---------|---------|----------|--------------------|----------|----------|------------------------|

| OPP Device<br>Rev "Blank" | MIN         | NOM     | MAX     | ARM (A8) | DDR3,<br>DDR3L [3] | DDR2 [3] | mDDR [3] | L3 and L4              |

| OPP100                    | 1.056 V     | 1.100 V | 1.144 V | 600 MHz  | 400 MHz            | 266 MHz  | 200 MHz  | 200 MHz and<br>100 MHz |

| OPP100                    | 1.056 V     | 1.100 V | 1.144 V | 300 MHz  | 400 MHz            | 266 MHz  | 200 MHz  | 200 MHz and<br>100 MHz |

| OPP50                     | 0.912 V     | 0.950 V | 0.988 V | 300 MHz  | _                  | 125 MHz  | 90 MHz   | 100 MHz and<br>50 MHz  |

- (1) Frequencies in this table indicate maximum performance for a given OPP condition.

- (2) VDD\_MPU is emerged with VDD\_CORE on the ZCE package.

- (3) This parameter represents the maximum memory clock frequency. Since data is transferred on both edges of the clock, double-data rate (DDR), the maximum data rate is two times the maximum memory clock frequency defined in this table.

Module utilization is the percentage of the available MHz at the selected OPP needed to meet the scenario processing requirement.

A separate utilization entry is provided for the Cortex-A8 ARM processor and the NEON SIMD engine.

- Cortex-A8 (ARM Cortex-A8 processor core): 0 100 %

- Cortex-A8 NEON (General purpose SIMD engine): 0 100 %

For the graphics accelerator subsystem, a separate utilization entry is provided:

SGX (2D/3D graphics accelerator engine): 0 - 100 %

## 2.4 Section C: Peripherals

This section is used to configure the activity on peripheral modules as shown in Table 10.

Table 10. Section C of the AM335x PET Input Spreadsheet

| Module Name                                                                   | Utilization % |  |

|-------------------------------------------------------------------------------|---------------|--|

| EDMA                                                                          | 0             |  |

| EMIF                                                                          | 0             |  |

| GPMC                                                                          | 0             |  |

| OCMC-RAM                                                                      | 0             |  |

| LCDC                                                                          | 0             |  |

| USB                                                                           | 0             |  |

| Ethernet MAC                                                                  | 0             |  |

| PRUSS                                                                         | 0             |  |

| McASP1                                                                        | 0             |  |

| McASP2                                                                        | 0             |  |

| MMC1                                                                          | 0             |  |

| MMC2                                                                          | 0             |  |

| MMC3                                                                          | 0             |  |

| Misc: Peripheral (UART, SPI, I2C, CAN, GPIO, eHRPWM, eQEP, RTC, and so forth) | 0             |  |

For each of the modules, enter module utilization as a percentage (0-100). A separate utilization entry is provided for the following modules:

- Enhanced Direct Memory Access (EDMA) controller

- External Memory Interface (EMIF) controller

- General-Purpose Memory Controller (GPMC)

- On-Chip Memory Controller and RAM (OCMC-RAM)

- LCD Controller (LCDC)

Input Spreadsheet www.ti.com

- Universal Serial Bus (USB)

- Ethernet MAC

- Programmable Real-Time Unit Subsystem (PRUSS)

- MultiChannel Audio Serial Port (McASP)

- MultiMedia Card (MMC) host controller

- Misc. PERIPHERALS (other miscellaneous peripherals such as universal asynchronous receiver/transmitter (UART), serial peripheral interface (SPI), inter-integrated circuit (I2C), controller area network (CAN, general-purpose input/output (GPIO), enhanced high-resolution pulse-width modulator (eHRPWM), enhance quadrature encoder pulse (eQEP) and real-time clock (RTC) modules)

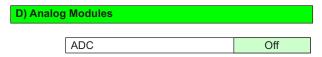

#### 2.5 Section D: Analog Modules

Section D enables a configuration for analog modules in the AM335x as shown in Figure 2.

Figure 2. Section D of the AM335x PET Input Spreadsheet

• ADC (A/D converter): On, Off

#### 3 Spreadsheet Upload

Upload your AM335x PET Input Spreadsheet here.

Upon completion of the input spreadsheet, upload the spreadsheet to TI for the power consumption analysis. Registration and legal agreement acceptance is required for the upload.

## 4 Power Analysis Report

#### 4.1 Power Estimation Report Sheet

The power estimation tool generates a power analysis report in a spreadsheet format (see Table 11). The estimated values are leakage, active and total average power over the time during the entire application scenario. The report also lists per power rail groups. When SmartReflex (AVS) is enabled, MPU and CORE voltage rails show controlled voltages by SmartReflex.

Input file name: am335x\_pet\_input\_example.xls

Junction Temperature (°C)

Device Process: nominal

ARM Clock Freq [MHz]: NITRO (1000)

www.ti.com Power Analysis Report

#### **Table 11. Power Estimation Report**

|                           | Volta | Voltage (V) |         | Current (A) |         | Power (W) |  |

|---------------------------|-------|-------------|---------|-------------|---------|-----------|--|

|                           | MIN   | MAX         | Leakage | Active      | Average | Total     |  |

| VDD_MPU                   | 1.33  | 1.33        | 0.002   | 0.542       | 0.544   | 0.72315   |  |

| VDD_CORE                  | 1.10  | 1.10        | 0.002   | 0.170       | 0.171   | 0.18828   |  |

| VDDS_DPLL [1]             | 1.80  | 1.80        | 0.000   | 0.007       | 0.007   | 0.01195   |  |

| VDDS_SRAM [2]             | 1.80  | 1.80        | 0.005   | 0.000       | 0.005   | 0.00815   |  |

| VDDS_DDR                  | 1.50  | 1.50        | 0.000   | 0.003       | 0.003   | 0.00533   |  |

| VDDS_1P8 [3]              | 1.80  | 1.80        | 0.000   | 0.002       | 0.002   | 0.00348   |  |

| VDDS_3P3 [4]              | 3.30  | 3.30        | 0.000   | 0.000       | 0.000   | 0.00016   |  |

| VDDA1P8V_USB0/1, VDDA_ADC | 1.80  | 1.80        | 0.000   | 0.000       | 0.000   | 0.00090   |  |

| VDDA3P3V_USB0/1           | 3.30  | 3.30        | 0.000   | 0.000       | 0.000   | 0.00000   |  |

| Total                     |       |             |         |             |         | 0.94140   |  |

- VDDS\_DPLL includes VDDS\_PLL\_MPU, VDDS\_PLL\_CORE\_LCD and VDDS\_PLL\_DDR power supplies.

- 2. VDDS\_SRAM includes VDDS\_SRAM\_CORE\_BG and VDDS\_SRAM\_MPU\_BB power supplies.

- 3. VDDS\_1P8 includes VDDS, VDDS\_RTC, VDDS\_OSC and 1.8 V VDDSHVx power supplies.

- 4. VDDS\_3P3 inclues 3.3 V VDDSHVx power supplies.

Power consumption in the AM335x device consists of:

- Leakage power due to leakage current, and dependent on temperature and device process

- Active power due to transistor switching, and independent of temperature

The AM335x Power Estimation Tool models temperature and device process effects on device power consumption. Active power consumption is the power that is consumed by portions of the AM335x that are performing some processing. Active power is independent of temperature, but dependent on voltage and module activity levels.

Power Analysis Report www.ti.com

#### 4.2 Module Utilization Sheet

The available bandwidth for each module depends on the device interconnects architecture and the selected CORE OPP. The power estimation tool calculates current module bandwidth from utilization entered by you and shows the results for each time slot with the maximum available bandwidth for the selected OPP in a separate worksheet (see Table 12).

**Table 12. Maximum Module Utilization**

|              | Slot 0 | Slot 0  | Unit |  |

|--------------|--------|---------|------|--|

| Module       | Max    | Current |      |  |

| Cortex A8    | 1000   | 850     | MHz  |  |

| SGX          | 1600   | 0       | MBps |  |

| EDMA         | 800    | 0       | MBps |  |

| EMIF         | 3200   | 1280    | MBps |  |

| GPMC         | 800    | 0       | MBps |  |

| OCMC-RAM     | 800    | 0       | MBps |  |

| LCDC         | 800    | 240     | MBps |  |

| USB          | 800    | 0       | MBps |  |

| Ethernet MAC | 800    | 0       | MBps |  |

| PRUSS        | 800    | 0       | MBps |  |

| MCASP1       | 800    | 0       | MBps |  |

| MCASP2       | 800    | 0       | MBps |  |

| MMC1         | 800    | 0       | MBps |  |

| MMC2         | 800    | 0       | MBps |  |

| MMC3         | 800    | 0       | MBps |  |

| Misc         | 6800   | 120     | MBps |  |

The following note and limitation applies to the AM335x Power Estimation Tool:

It is up to you to input reasonable utilization numbers for the MPU subsystem for the purposes of maximum power analysis. 90-100% loading on the subsystem is not realistic for most application scenarios.

#### 5 References

- 1. AM335x Power Consumption Summary

- AM3359, AM3358, AM3357, AM3356, AM3354, AM3352 Sitara™ AM335x ARM® Cortex™-A8 Microprocessors (MPUs) Data Manual (SPRS717)

- 3. AM335x ARM® Cortex™-A8 Microprocessors (MPUs) Technical Reference Manual (SPRUH73)

- 4. AM35x Power Estimation Tool

- 5. AM/DM37x Power Estimation Spreadsheet

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated