## Application Note

## 电路板布局对 LDO 热性能影响的经验分析

Gerard Copeland

## 摘要

本应用报告研究了印刷电路板 (PCB) 布局对低压降 (LDO) 稳压器热性能的影响，特别是结至环境热阻  $\theta_{JA}$ 。此参数是针对 TPS745 ( WSON 封装 ) 、TPS7B82-Q1 ( TO-252 封装 ) 和 TLV755P ( SOT-23 封装 ) 器件测量的。每款器件均在五种布局下进行测试，这五种布局的内层与外层铜覆盖率依次递增。增加铜覆盖量会降低  $\theta_{JA}$ ，但这种改善效果会达到一个收益递减的临界点。铜覆盖对于具有散热焊盘的封装更有效。这些结果旨在为系统设计人员提供布局技巧，从而提高热性能。尽管本研究测试的器件仅为 LDO，但报告中关于 PCB 布局的影响分析及结论，同样适用于其他存在功耗的器件。

## 内容

|                           |    |

|---------------------------|----|

| <b>1 简介</b>               | 2  |

| <b>2 过程</b>               | 6  |

| <b>3 测试结果与讨论</b>          | 7  |

| <b>4 结语</b>               | 11 |

| <b>5 未来研究方向</b>           | 11 |

| <b>6 参考资料</b>             | 11 |

| <b>7 修订历史记录</b>           | 12 |

| <b>A 热测试电路板布局</b>         | 13 |

| A.1 TPS745 (WSON) 图       | 13 |

| A.2 TPS7B82-Q1 (TO-252) 图 | 18 |

| A.3 TLV755P (SOT-23) 图    | 23 |

| <b>B 热测试结果</b>            | 28 |

| B.1 热性能数据                 | 28 |

## 商标

所有商标均为其各自所有者的财产。

## 1 简介

LDO 具有相对简单性和成本优势，因此是电子电源设计中最常见的 DC/DC 转换器。随着应用日益集成化与小型化，电源设计需向更小尺寸、更低成本方向发展，这导致 LDO 的使用量不断增加。由于 LDO 属于线性转换器，本身存在功耗，因此热性能成为系统设计中愈发重要的考量因素。尽管 JEDEC 已制定了半导体热性能参数的统一测量与报告标准，但该标准在热性能优化方面尚未完善。影响热性能的最重要因素之一在于系统设计人员，即 PCB 布局。本应用报告旨在研究 PCB 布局对 LDO 热性能的影响，为设计人员提供参考。尽管此前已有 [《采用小型 SMD 封装的 LDO 热性能》应用报告](#) 和 [《AN-1520 确保外露封装实现出色热阻的电路板布局布线指南》应用报告](#) 探讨过该主题，但本研究通过在功能性场景下采集数据，力求提升结论的实用性。该设置包括带有无源器件（模拟 TI 评估模块 (EVM)）的功能 PCB 布局以及通过有源供电进行的热性能测量。有源供电是指将 LDO 置于正常工作状态，并通过改变输入电压与负载电流来增加器件功耗，使器件结区产生热量。

评估半导体热性能最常用的参数是结到环境热阻  $\theta_{JA}$ 。[方程式 1](#) 显示，该参数定义为器件每消耗 1 瓦功率时，器件工作温度与结温差值，公式如下：

$$\theta_{JA} = \frac{T_J - T_A}{P_D} \quad (1)$$

在特定功耗水平下，设计中  $\theta_{JA}$  越小，器件结温越低，从而可提升器件寿命与可靠性。[《半导体和 IC 封装热指标》应用报告](#) 指出，对  $\theta_{JA}$  影响较大的两个因素是 PCB 布局与 IC 封装。TPS745 ( WSON 封装)、TPS7B82-Q1 ( TO-252 封装) 和 TLV755P ( SOT-23 封装) 三款 LDO 采用五种不同的 PCB 布局进行了测试，以探究上述两个因素对热性能的影响程度。

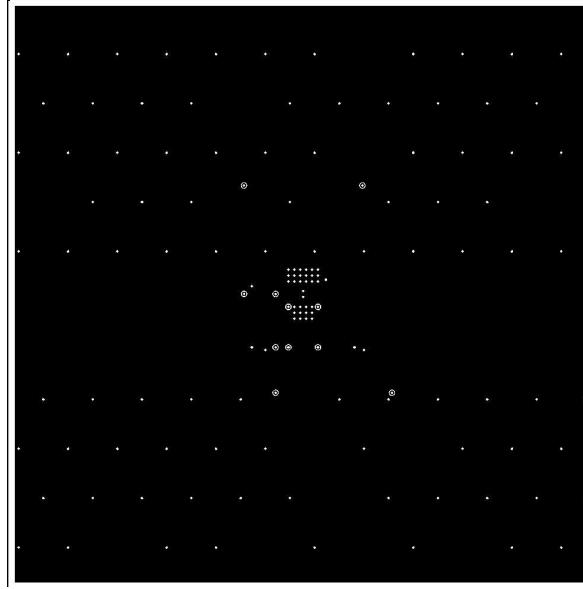

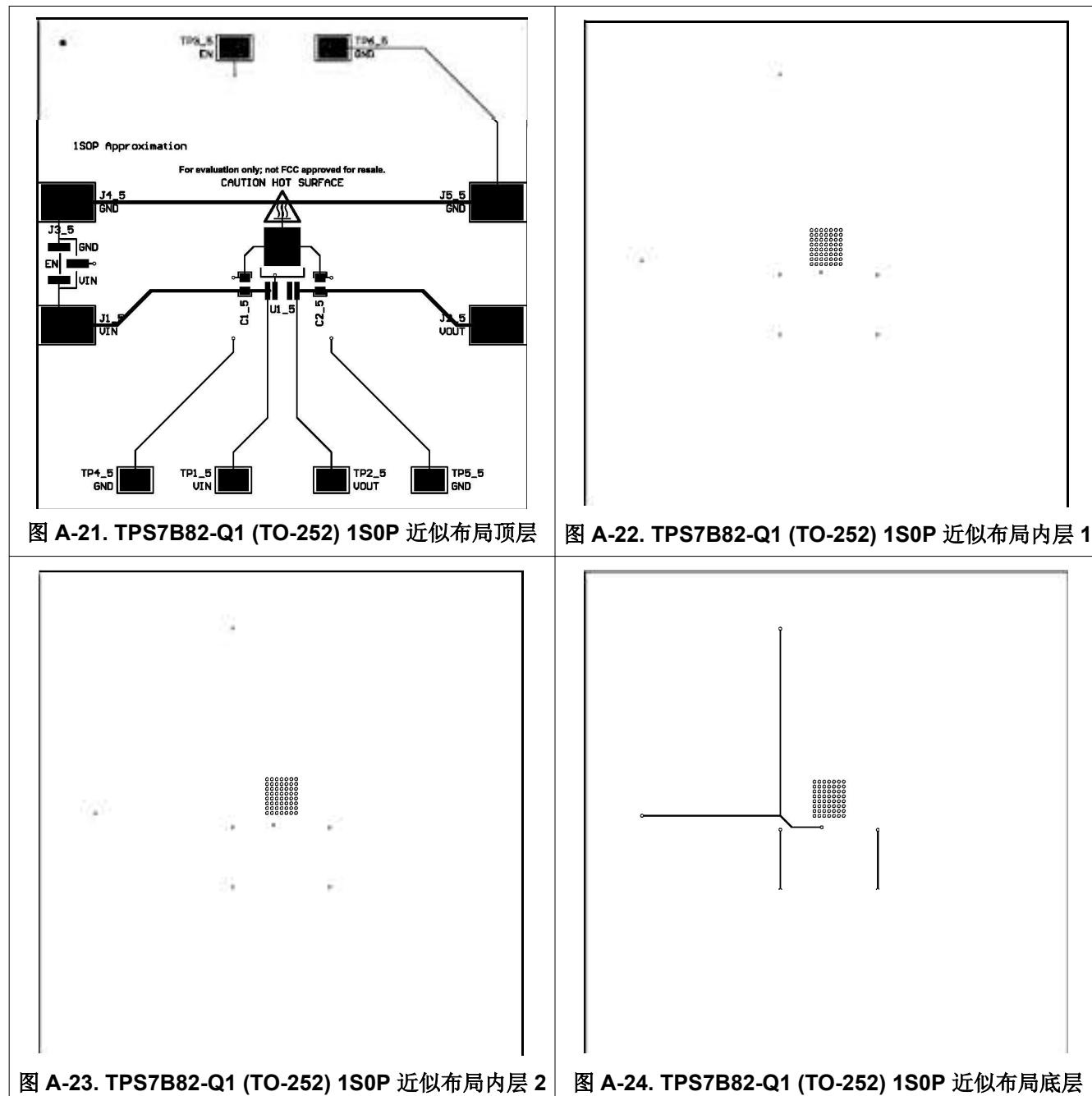

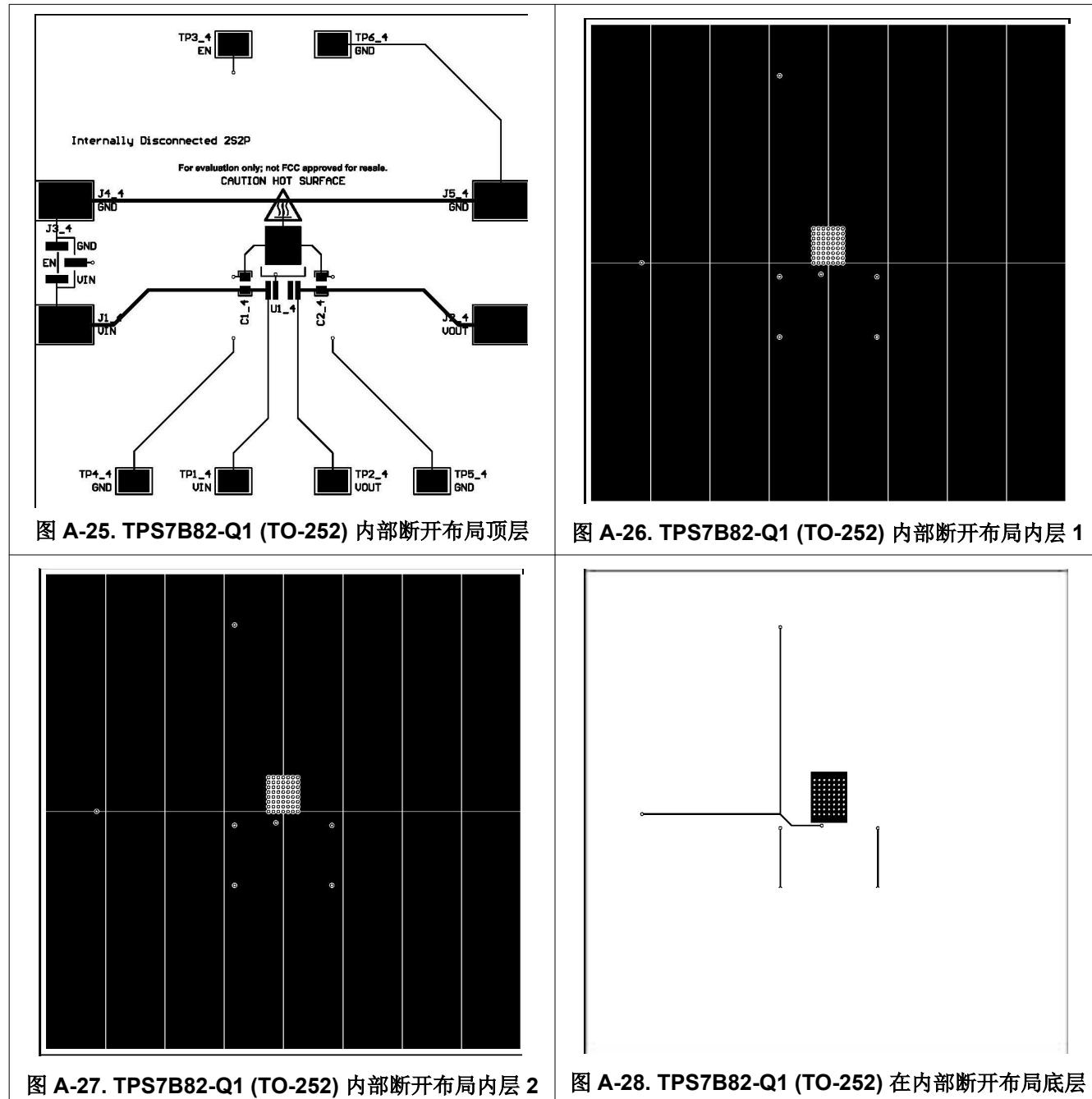

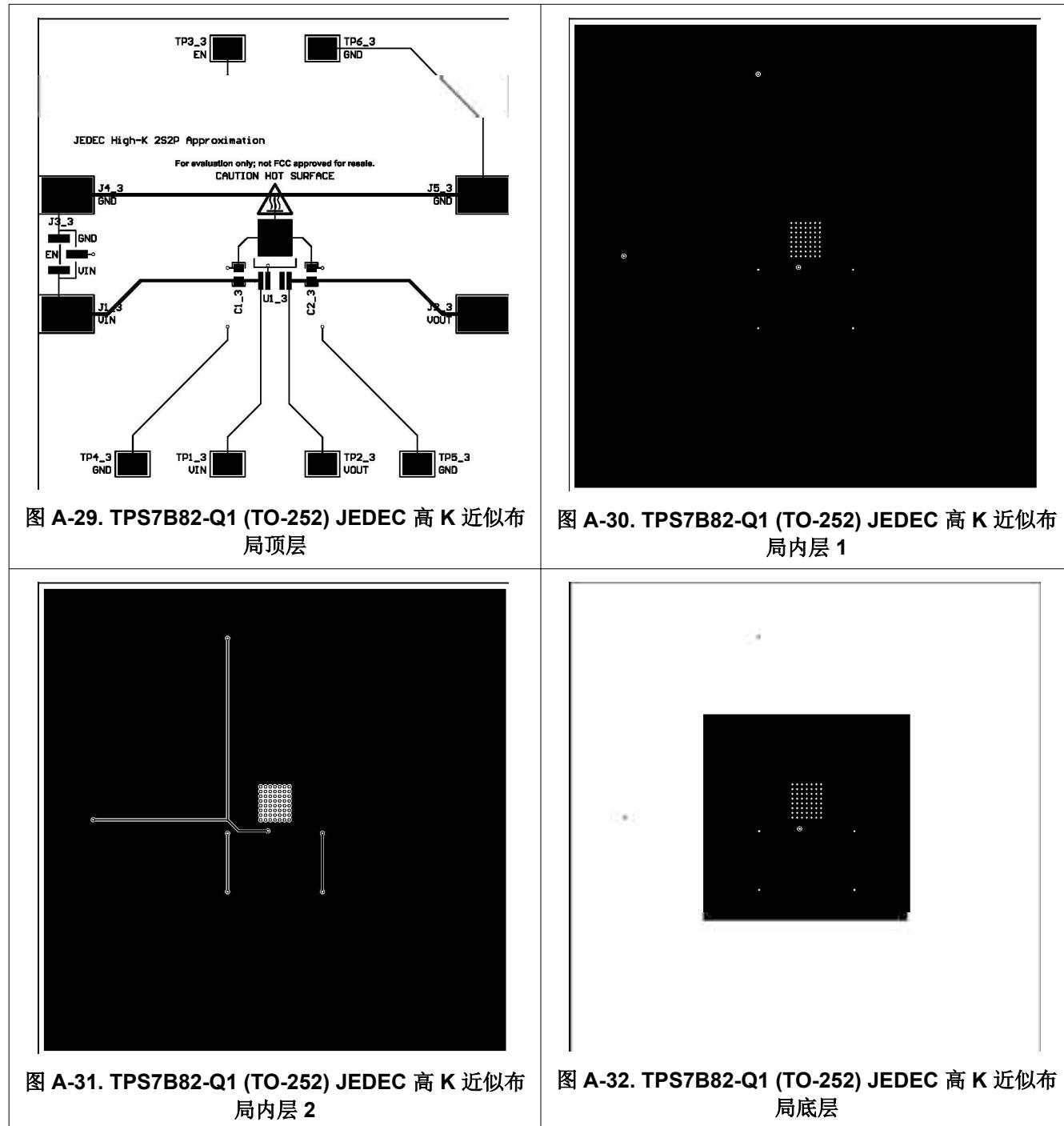

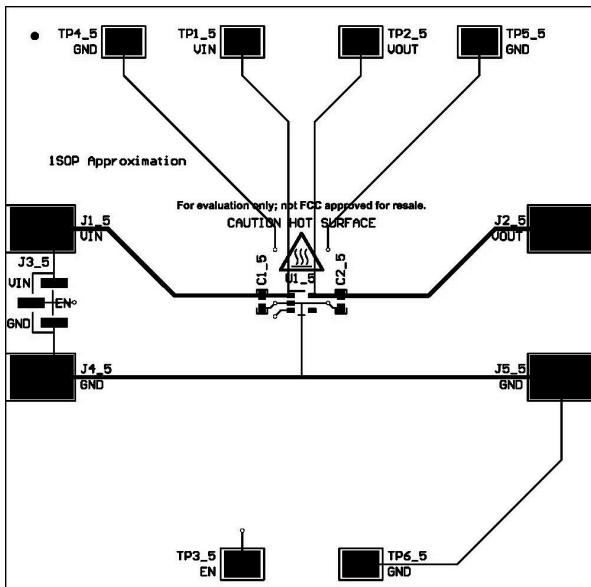

半导体热性能受气流、海拔、环境温度等多种外部因素影响，因此 JEDEC 需针对  $\theta_{JA}$  和其他热指标制定标准化的测量流程与测试板。为了完成本应用报告的测试，针对每种封装设计了两类测试板布局，即 <https://www.jedec.org/system/files/docs/JESD51-3.PDF> 中介绍的低效导热性测试板的近似布局和 <https://www.jedec.org/system/files/docs/jesd51-7.PDF> 中介绍的高有效导热性测试板的近似布局，除此之外，还额外设计了三种定制化布局。每块电路板的面积与层叠结构均遵循 JEDEC 标准测试板近似布局：4 层 PCB，面积为 9in<sup>2</sup> (3 英寸 x 3 英寸)。外层铜箔厚度为 2 盎司，内层铜箔厚度为 1 盎司。为每种封装制作的五种布局中，与器件相连的铜箔量逐渐增加，此举旨在测量结到环境热阻  $\theta_{JA}$ ，并验证其与铜箔覆盖率之间的反比关系。为提高三款封装测试结果的一致性，每种布局中用于散热的铜箔量均保持一致。按铜箔含量从低到高排序，这些布局类型分别命名为：

- 1S0P 近似布局

- 内部断开布局

- JEDEC 高 K 近似布局

- 热增强型

- 热饱和型

根据 <https://www.jedec.org/system/files/docs/JESD51-9.pdf> 中规定的 JEDEC 标准，所有 WSON 和 TO-252 布局的散热焊盘处均设有散热过孔。这些散热过孔的直径为 20 毫米 (mm)，孔径为 10 毫米，铜镀层厚度为 17 微米。

选用两个不同的  $\theta_{JA}$  值作为比较基准。第一种是  $\theta_{JA, datasheet}$ ，该值以  $R_{\theta, JA}$  形式标注在各器件数据手册的“热信息”表格中。 $\theta_{JA, datasheet}$  通过 JEDEC 高 K 热量测试板的热模型推导得出，是设计人员评估热性能最常用的参数。第二个值为  $\theta_{JA,1S0P}$ ，该值通过 1S0P 近似布局实测得出。此值提供了最坏情况布局的预期热性能示例。

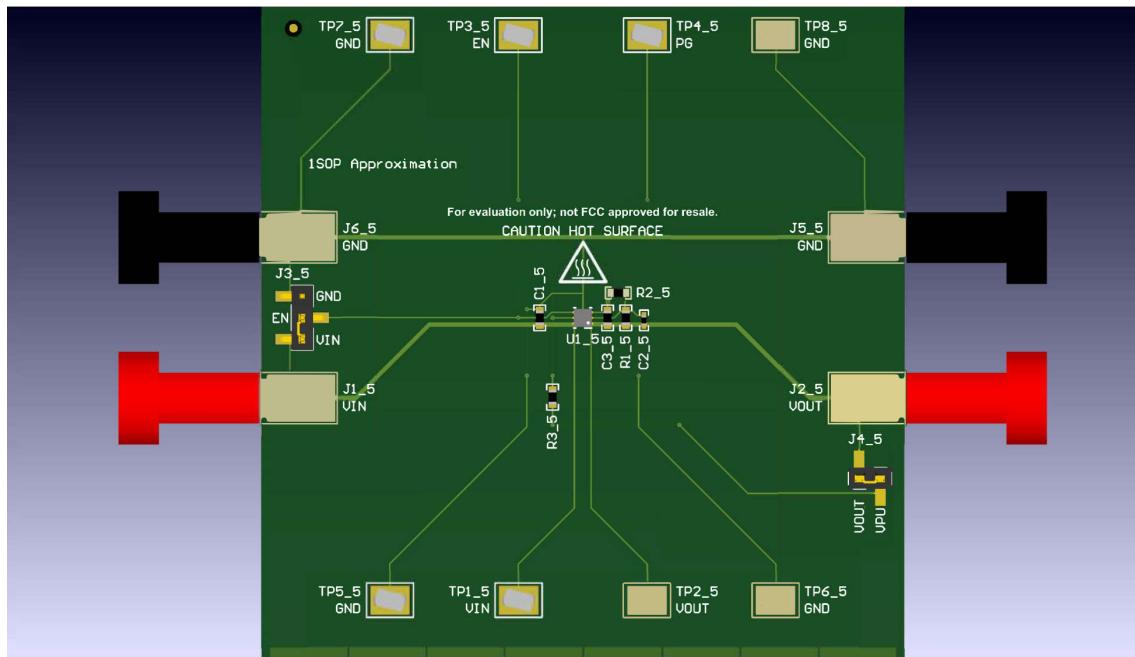

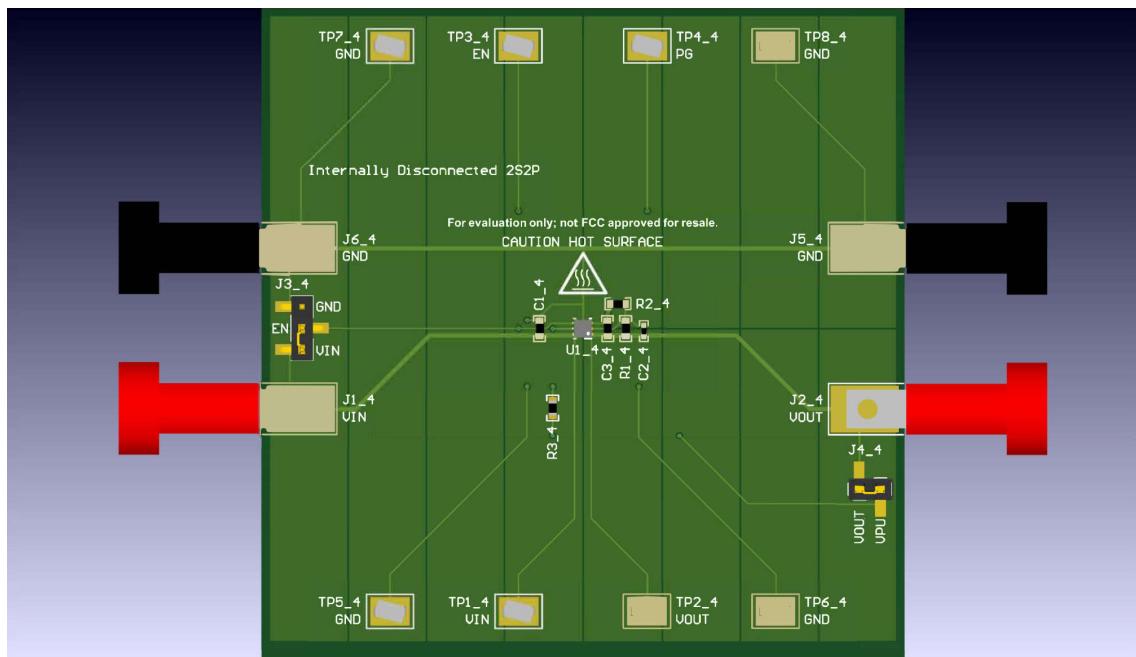

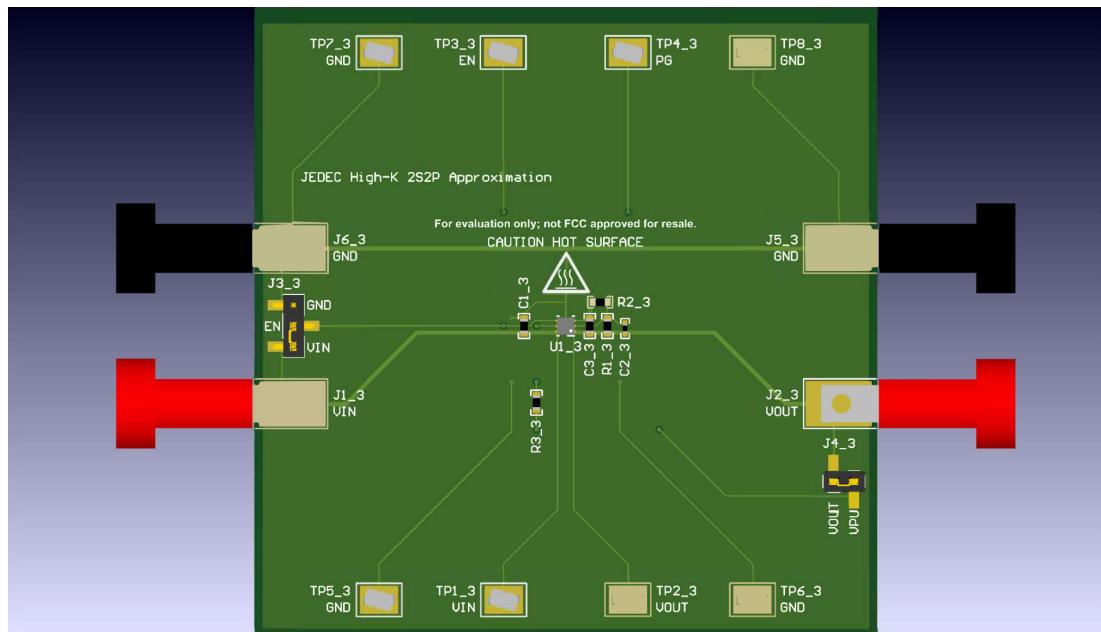

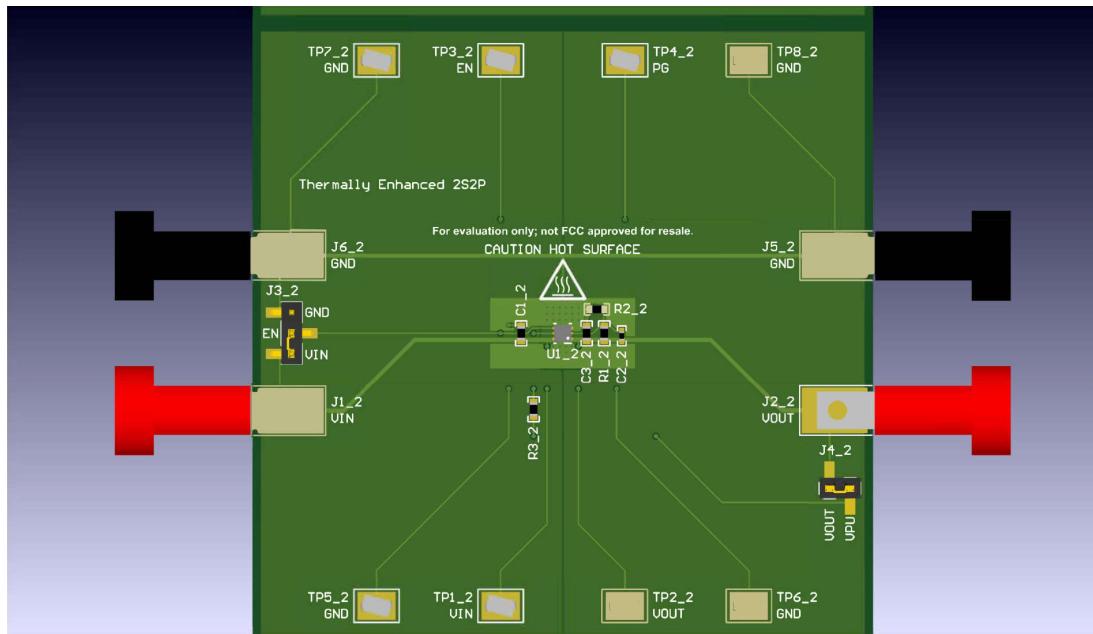

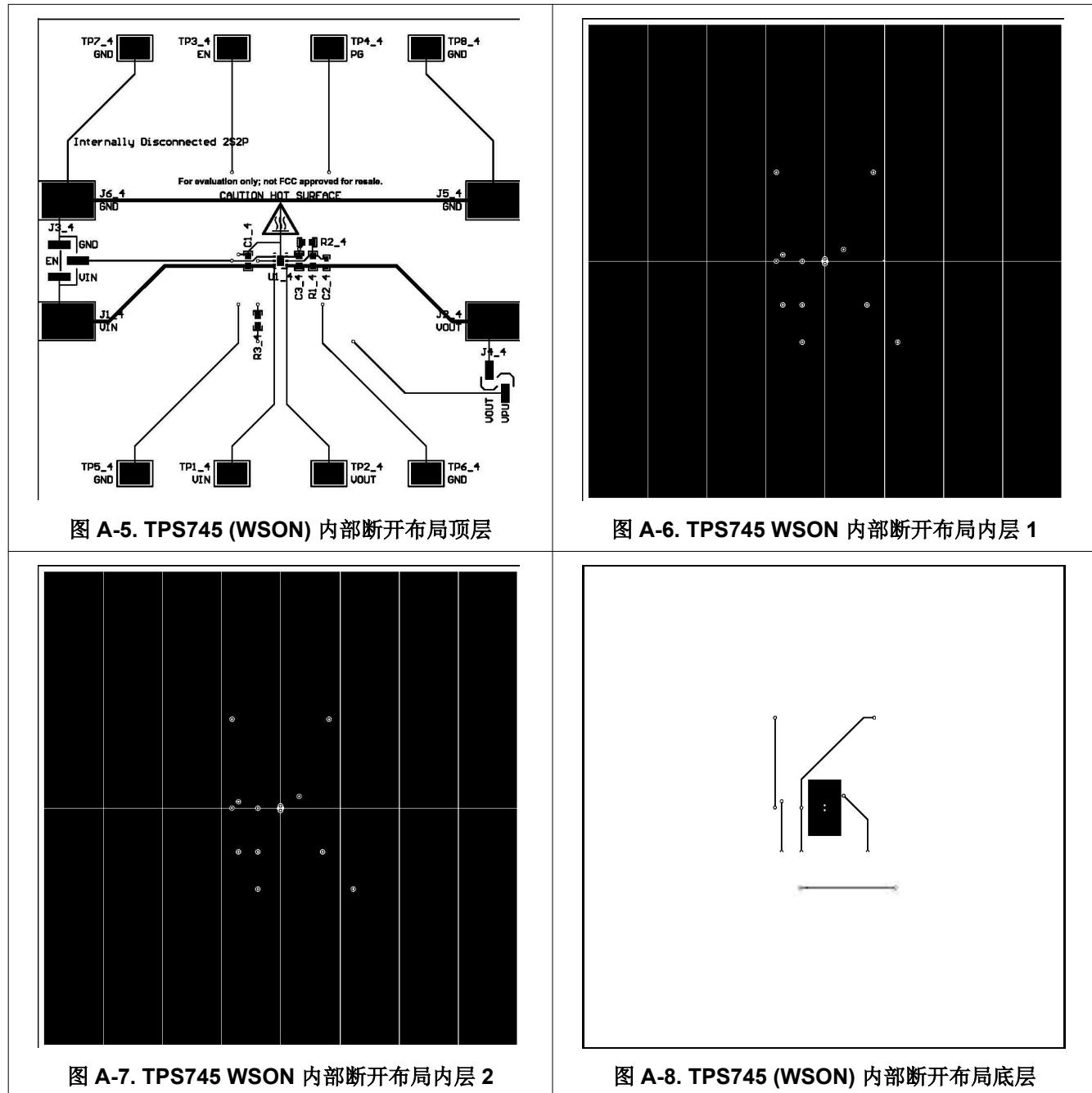

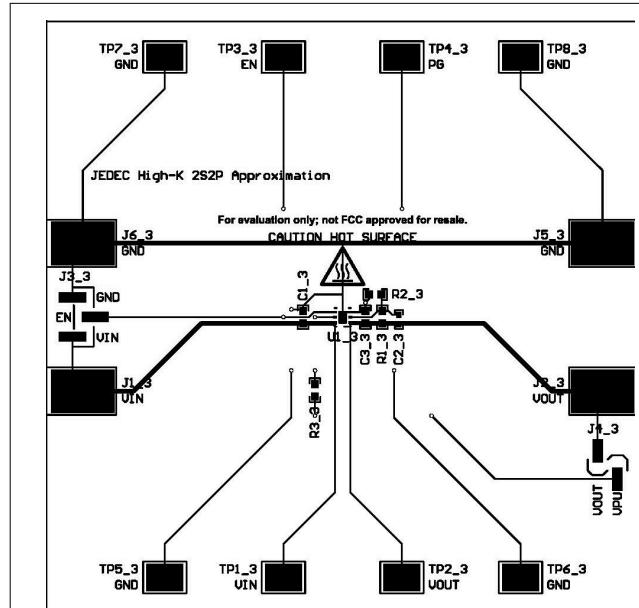

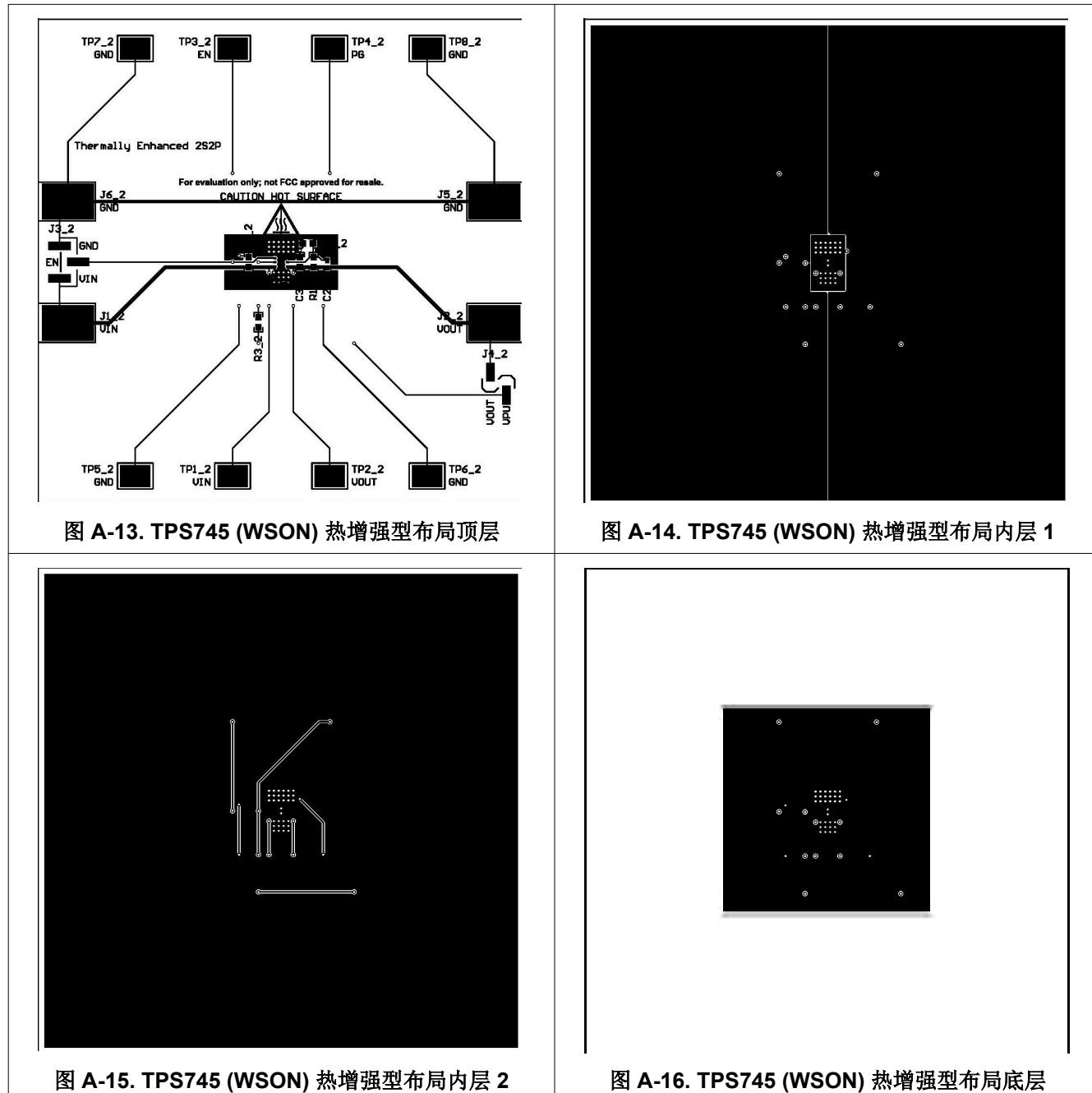

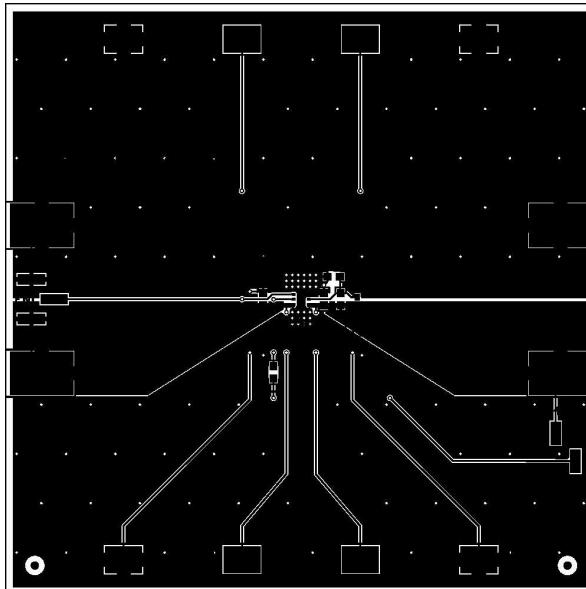

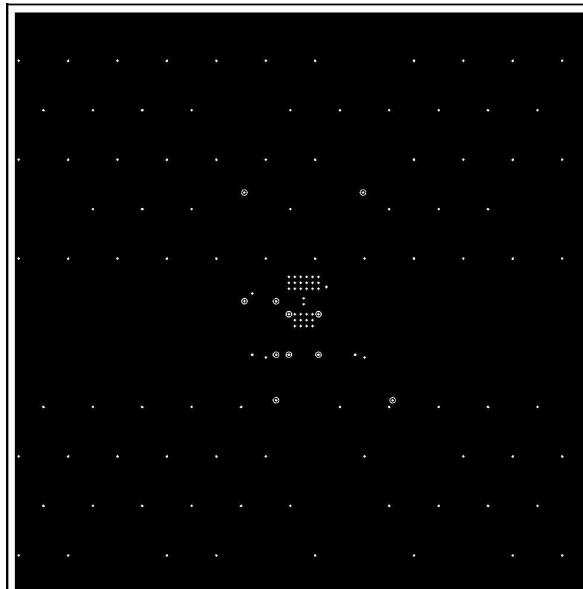

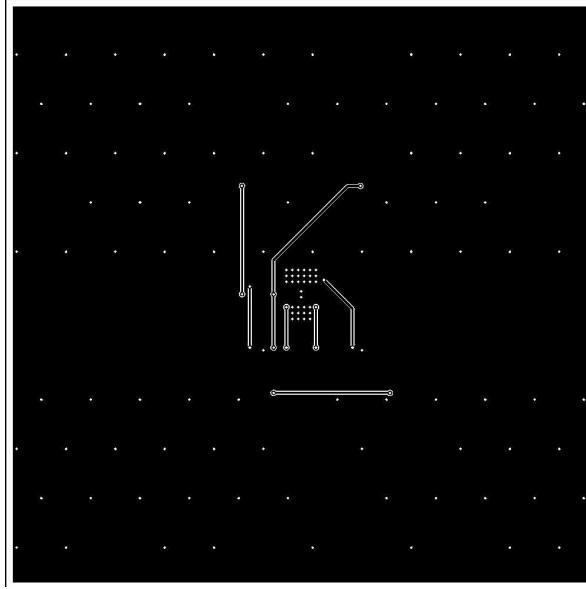

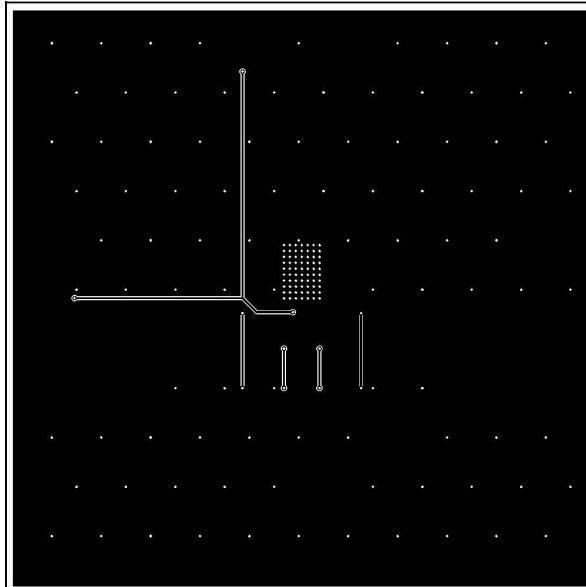

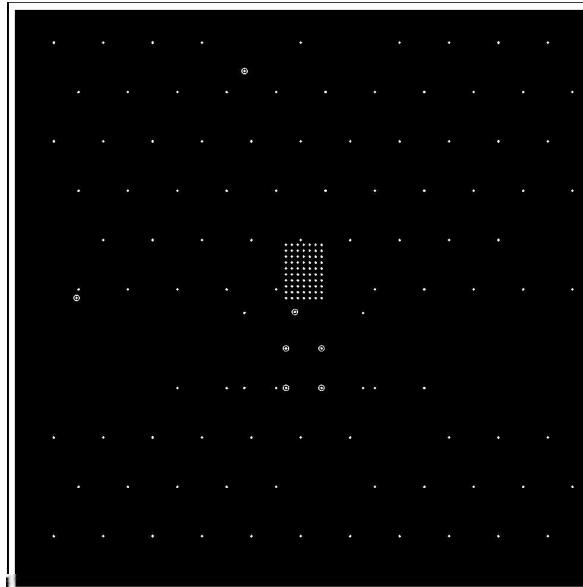

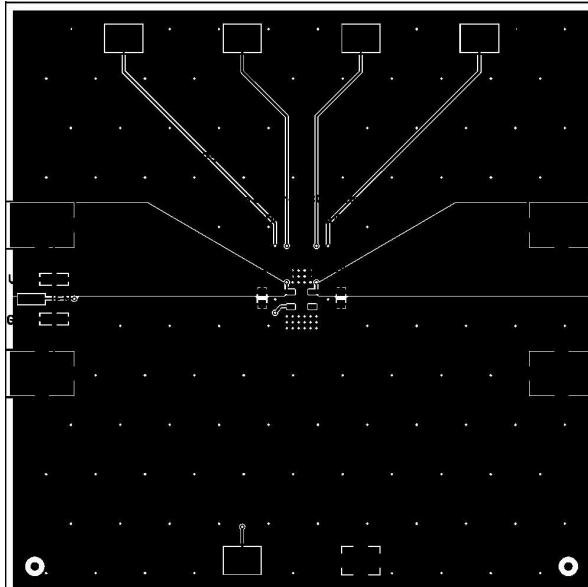

图 1-1 至图 1-5 显示了为采用 WSON 封装的 TPS745 设计的每个布局所生成的 3D 图像。每种布局的四层板结构图可参见附录 A。[表 1-1](#) 提供了每种设计布局和覆铜的说明。

表 1-1. 布局标识与说明

| 电路板            | 属性      | 说明                              | 连接的铜面积 (in <sup>2</sup> ) | 断开的铜面积 (in <sup>2</sup> ) |

|----------------|---------|---------------------------------|---------------------------|---------------------------|

| 1SOP 近似布局      | 顶层      | 仅走线                             | 无                         | 无                         |

|                | 内层 1    | 无铜                              |                           |                           |

|                | 内层 2    | 无铜                              |                           |                           |

|                | 底层      | 仅走线                             |                           |                           |

|                | 额外的散热过孔 | 无                               |                           |                           |

| 内部断开布局         | 顶层      | 仅走线                             | 0.07                      | 16.8                      |

|                | 内层 1    | 中等面积、未连接、不连续的铜平面 <sup>(1)</sup> |                           |                           |

|                | 内层 2    | 中等面积、未连接、不连续的铜平面 <sup>(1)</sup> |                           |                           |

|                | 底层      | 走线及一个小型接地平面                     |                           |                           |

|                | 额外的散热过孔 | 无                               |                           |                           |

| JEDEC 高 K 近似布局 | 顶层      | 仅走线                             | 10.2                      | 8.53                      |

|                | 内层 1    | 一个较大的接地平面                       |                           |                           |

|                | 内层 2    | 走线和一个大的未连接平面                    |                           |                           |

|                | 底层      | 一个中等接地平面                        |                           |                           |

|                | 额外的散热过孔 | 无                               |                           |                           |

| 热增强型           | 顶层      | 走线及一个小型接地平面                     | 10.5                      | 8.43                      |

|                | 内层 1    | 小型接地平面及两个未连接铜平面                 |                           |                           |

|                | 内层 2    | 走线及一个中型接地平面                     |                           |                           |

|                | 底层      | 一个中等接地平面                        |                           |                           |

|                | 额外的散热过孔 | 仅器件周围                           |                           |                           |

| 热饱和型           | 顶层      | 大型接地平面及电源平面                     | 34.1                      | 无                         |

|                | 内层 1    | 一个较大的接地平面                       |                           |                           |

|                | 内层 2    | 走线及一个大型接地平面                     |                           |                           |

|                | 底层      | 一个较大的接地平面                       |                           |                           |

|                | 额外的散热过孔 | 器件周围和整个 PCB                     |                           |                           |

(1) 旨在模拟无专用接地平面的高密度应用场景。

图 1-1. TPS745 (WSON) 1SOP 近似布局

图 1-2. TPS745 (WSON) 内部断开布局

图 1-3. TPS745 (WSON) JEDEC 高 K 近似布局

图 1-4. TPS745 (WSON) 热增强型布局

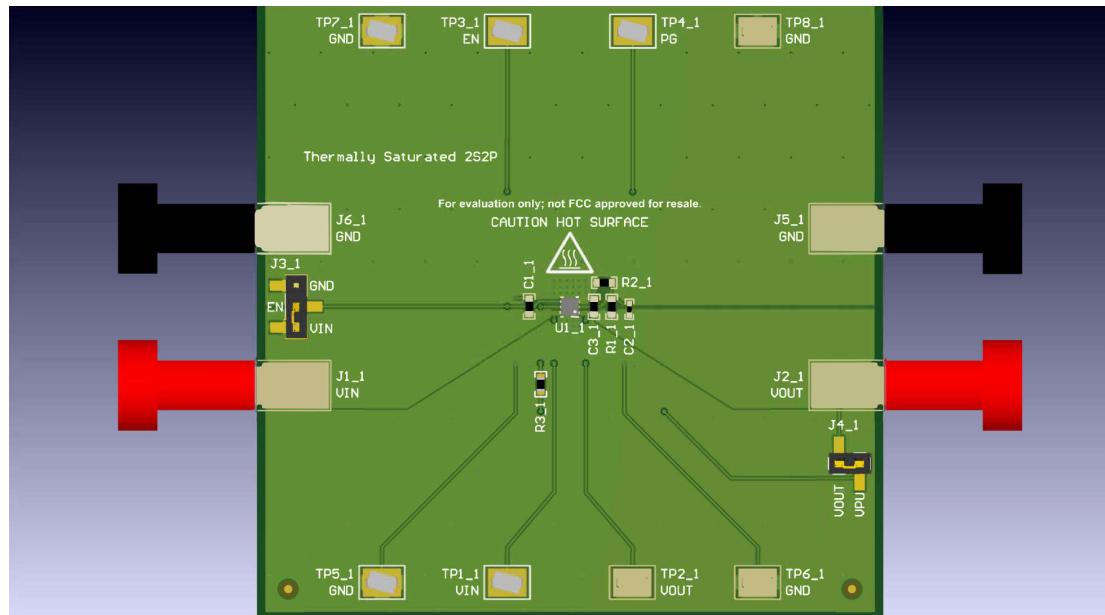

图 1-5. TPS745 (WSON) 热饱和型布局

## 2 过程

大多数现代 LDO 均具备热关断功能，可防止器件在高结温下遭受严重损坏。在特定功耗水平下，带有热关断功能的 LDO 存在最高工作环境温度阈值，可触发热关断，器件随即停止工作。方程式 2 展示了用热关断温度替代结温的过程，以及对公式方程式 1 的推导整理：

$$T_{A,max} = T_{SD} - \theta_{JA} \times P_D \quad (2)$$

《现场测量 LDO 热阻抗》应用报告说明，该公式提供了一种无需直接接触器件结区即可测得结到环境热阻  $\theta_{JA}$  的方法。首先，选择较低的功耗值，使此时器件的最高工作环境温度基本等于其热关断温度。使用高温烘箱设定环境温度，并让 LDO 在该温度下恒温放置 5 分钟。随后需关闭高温烘箱以停止气流流动，因 JEDEC 标准模型默认无强制对流条件。接着使用示波器监测 LDO 是否关闭输出。若出现输出停止的情况，表明热关断功能已被触发。如果 LDO 未进入热关断状态，则升高环境温度并重复上述流程，直至确定最高工作环境温度。针对逐步升高的不同功耗水平重复上述流程，以便在使用公式方程式 2 计算  $\theta_{JA}$  时获得足够数据用于线性回归分析。

该流程的测量精度存在一定局限性，因测量过程中环境温度与功耗易发生变化。为确保自然对流而关闭高温烘箱，会导致环境温度逐渐下降。同时，高温烘箱产生的对流冷却效应消失，会导致器件结温升高。由于 LDO 基准带隙随温度漂移，其输出电压会降低，进而导致传输晶体管的功耗增加。高温烘箱的测量精度通常为  $\pm 2^\circ\text{C}$ ，这也会降低测得的  $\theta_{JA}$  的准确性，为解决这些局限性，必须选择大范围的功耗水平，以覆盖宽泛的最高环境温度区间。方程式 2 显示  $\theta_{JA}$  定义为这两个变量之间趋势线的斜率。因此，验证温度与功耗在宽范围内保持线性关系可以提高  $\theta_{JA}$  测量的可信度。

该流程的主要优势在于相对简单。由于无需对 PCB 或 LDO 进行改装即可测量特定电路板温度或结温，该流程可用于任意电路板的  $\theta_{JA}$  测量；尽管精度略有损失，但能提供更贴近实际应用的 PCB 布局与测试环境，对系统设计人员更具参考价值。鉴于本应用报告的目标是通过研究多封装下 PCB 布局与热性能的普遍趋势为设计人员提供参考，因此优先构建贴近实际应用的测试环境。

### 3 测试结果与讨论

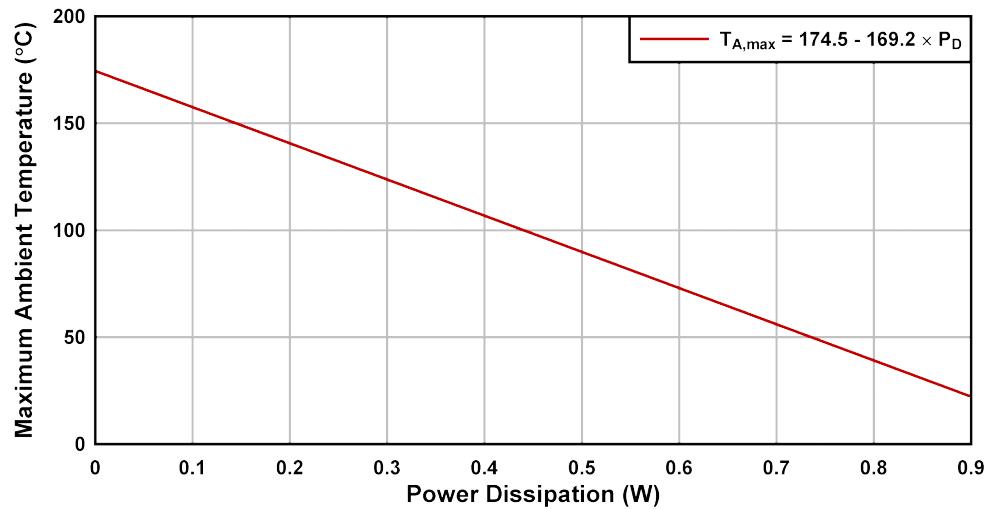

图 3-1 展示了 1S0P 近似布局下，TPS745 ( WSON 封装 ) 的最高环境温度与功率耗散间的关系。趋势线的斜率表明  $\theta_{JA}$  为 169.2 C/W。所收集数据的范围和线性度支持方程式 2 中所述的 LDO 功率耗散与最高工作环境温度之间的预期关系。

图 3-1. TPS745 (WSON) 1S0P 近似布局测试结果

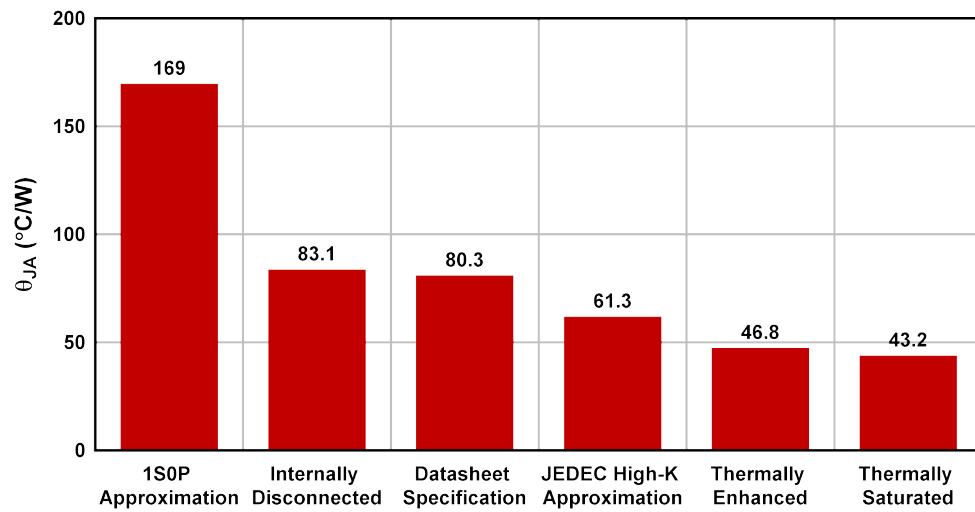

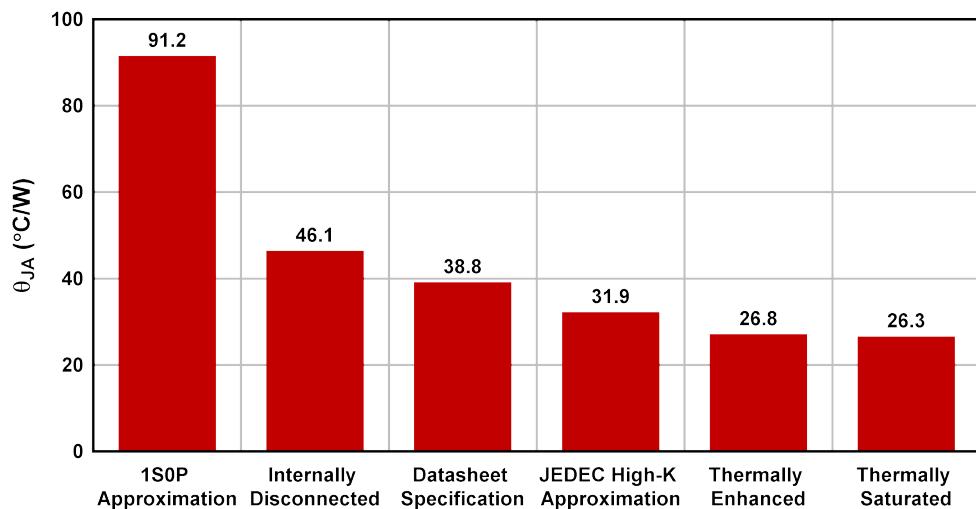

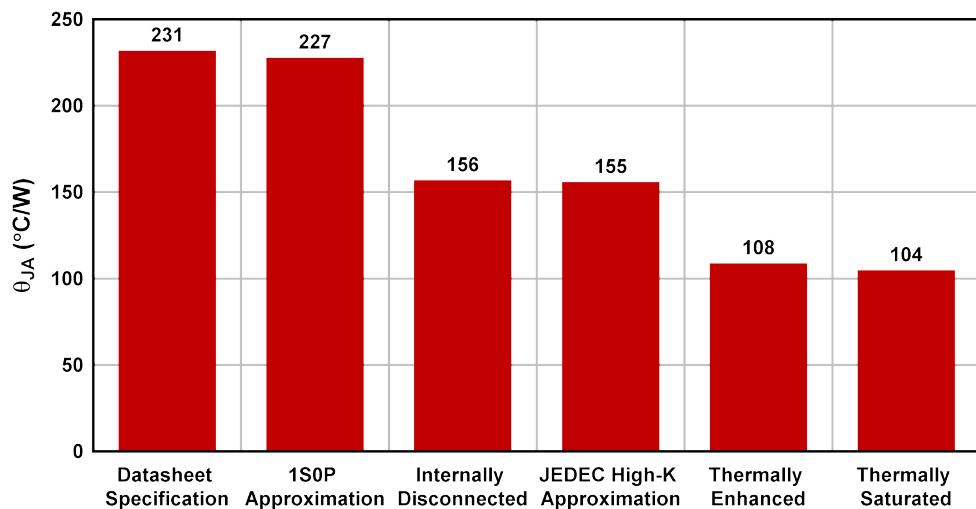

所有封装与布局的同类数据可参见附录 B。图 3-2 和图 3-3 分别给出了 TPS745 (WSON) 和 TPS7B82-Q1 (TO-252) 的  $\theta_{JA}$  实测值。在全部五种布局下，这两款封装的热性能呈现出相似趋势。尽管仅连接的铜面积为 0.07 in<sup>2</sup>，但内部断开的布局仍可将  $\theta_{JA}$  降低近 50%，这表明，即使内层铜箔未直接与 LDO 相连，在内部层增加铜箔也能显著提升热性能。剩下的布局中，随着铜用量和散热过孔数量逐渐增加， $\theta_{JA}$  会持续下降但降幅渐小，最终最大降幅略超 70%。基于所采集的数据，高效热布局对于 WSON 与 TO-252 封装至关重要。如果布局热效率低下， $\theta_{JA}$  会显著高于数据手册规定值，进而导致热性能计算更为复杂、最高工作环境温度降低，并可能导致器件寿命与可靠性下降。

图 3-2. TPS745 (WSON)  $\theta_{JA}$  与电路板布局间的关系

图 3-3. TPS7B82-Q1 (TO-252)  $\theta_{JA}$  与电路板布局间的关系

图 3-4 显示了 TLV755P (SOT-23) 的  $\theta_{JA}$  实测值。SOT-23 封装的  $\theta_{JA}$  存在差异，原因是该封装无散热焊盘。JEDEC 标准不允许在高 K 热测试板上为没有散热焊盘的封装添加散热过孔。少量热量能够消散到内层和底层，因此 1SOP 近似布局与 JEDEC 高 K 测试板的热模型（数据手册规格即源于此模型）之间的性能非常相似。为避免多种不同布局呈现完全一致的性能，器件下方的内部断开布局中增设了一个散热过孔，用于连接顶层接地走线与底层接地平面。相比之下，JEDEC 高 K 近似布局具有相似的性能，它有两个过孔，将顶部接地走线连接到内部层。尽管 JEDEC 高 K 近似布局中增加了铜箔，但额外增加一个散热过孔所带来的热传导能力提升有限，不足以使  $\theta_{JA}$  获得显著改善。

与 JEDEC 高 K 近似板相比，热增强型和热饱和型板的  $\theta_{JA}$  减少了约 33%，明显大于 TPS745 和 TPS7B82-Q1 在相同对比条件下的降幅。这是因为 SOT-23 封装中没有散热焊盘。热增强型和热饱和型布局是唯一在顶层包含铜平面的布局。该封装因无散热焊盘，大部分热量需通过顶层散发。因此，在顶层设置铜平面的散热效果更为显著。此外，热增强型封装和热饱和封装中增设的散热过孔，是热量传导至内层与底层的唯一途径。相比之下，TPS745 和 TPS7B82-Q1 的布局在散热焊盘正下方已设有散热过孔，因此额外增加散热过孔的效果会有所减弱。

图 3-4. TLV755P (SOT-23)  $\theta_{JA}$  与电路板布局间的关系

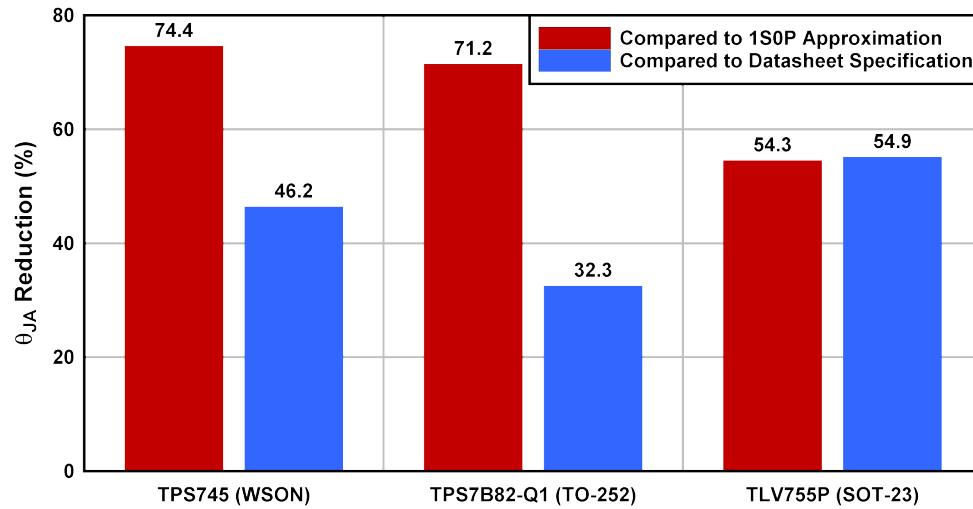

图 3-5 比较了 PCB 布局与封装类型的有效性。有效性以  $\theta_{JA}$  的降低百分比来衡量。由方程式 3 的计算结果可知，根据封装类型的不同，高效热布局可使数据手册中规定的  $\theta_{JA}$  降低 32% 至 55%。数据表中规定的  $\theta_{JA}$  可用于对 LDO 的结温升高值进行保守估算。但参考方程式 2 可知，使用高效散热的布局后，结温的实际升高值可降低

32% 至 55%。考虑到这一改善效果，设计时可选择更高的工作环境温度、更高的功耗水平或二者的某种组合。通过方程式 4 与 1SOP 近似布局进行比较，可以看出采用高效散热型布局的重要性。与这种最差情况布局相比，高效热布局的实测  $\theta_{JA}$  降至前者的 1/4。

$$\text{Reduction of } \theta_{JA} \text{ compared to Datasheet Specification} = \left( 1 - \frac{\theta_{JA,\text{saturated}}}{\theta_{JA,\text{datasheet}}} \right) \times 100 \quad (3)$$

$$\text{Reduction of } \theta_{JA} \text{ compared to 1SOP Approximation} = \left( 1 - \frac{\theta_{JA,\text{saturated}}}{\theta_{JA,1SOP}} \right) \times 100 \quad (4)$$

图 3-5. 各器件的  $\theta_{JA}$  降低情况

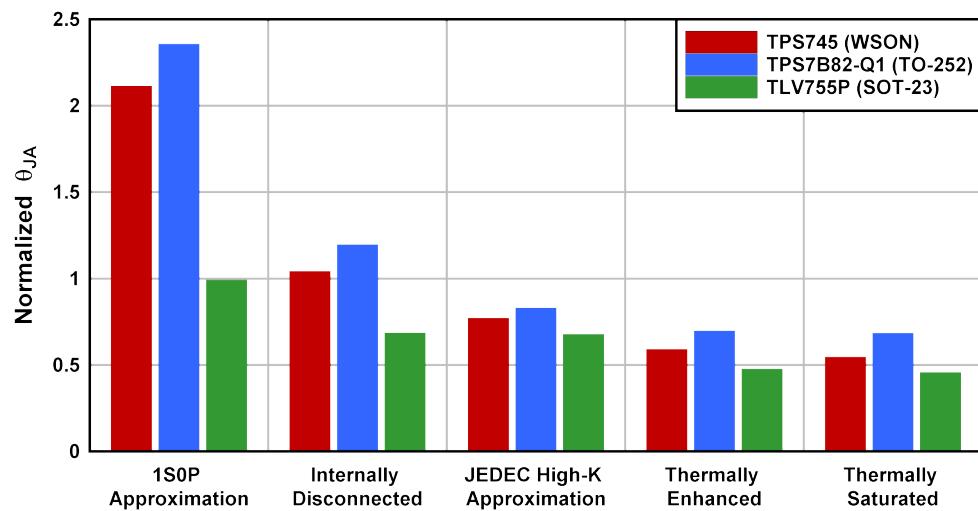

图 3-6 使用方程式 5 对图 3-2、图 3-3 和图 3-4 中的结果相对于数据手册规格进行了归一化处理。

$$\theta_{JA,\text{normalized}} = \frac{\theta_{JA,\text{measured}}}{\theta_{JA,\text{datasheet}}} \quad (5)$$

该图汇总了三种封装的采集数据，以阐明本研究的重要结论。首先，PCB 铜含量与  $\theta_{JA}$  之间呈反比关系，且随着铜含量增加，这种反比关系会逐渐趋于饱和。无论采用何种封装，均可观察到这一关系。如 1SOP 近似布局与内部断开布局之间的显著下降所示，这表明铜箔无需与 LDO 直接连接，即可改善热性能。在器件周围增设散热过孔可为 LDO 产生的热量提供更多传导至内层与底层的路径，从而同样能改善热性能。对于 SOT-23 这类无专用散热焊盘的封装，此类散热过孔尤为重要。然而，从热增强型布局和热饱和型布局之间改善幅度极小可看出，额外散热过孔对  $\theta_{JA}$  的改善会趋于饱和。

图 3-6. 每个器件的归一化  $\theta_{JA}$  与电路板布局间的关系

## 4 结语

LDO 在结至环境热阻  $\theta_{JA}$  方面的热性能在很大程度上取决于 PCB 设计。但 PCB 对热性能的影响最终受限于 LDO 的封装类型。具有散热焊盘的封装（例如 WSON 和 TO-252 封装）具有更强的散热能力，因此与最坏情况的 1SOP 近似布局相比，其  $\theta_{JA}$  整体降幅更大，分别达到 74% 和 71%。SOT-23 封装体积更小，但仍有 54% 的显著降低。图 3-5 表明，与数据手册规格相比，采用热优化布局可使  $\theta_{JA}$  降低 32% 至 55%。该结果表明，使用数据表中规定的  $\theta_{JA}$  进行热性能计算，得到的是偏保守的热性能估算值。但设计人员需注意，高效热布局可支持更高的工作环境温度、更高的功耗水平，或同时兼具这两项优势。

图 3-6 表明，无论采用何种封装，随着 PCB 铜含量增加，热性能提升会逐渐趋于饱和。对于这三款封装，热增强型布局的铜面积约为热饱和型布局的一半，但其  $\theta_{JA}$  的差异在 8% 以内。同样，通过增加散热过孔实现的热性能提升也会趋于饱和。从热饱和型布局的结果可知，在 PCB 上额外增加过孔所带来的好处很小。采用类似热增强型布局的设计，即可实现足够的热性能。对于更紧凑的设计，可参见图 3-4，该图展示了 TLV755P (SOT-23) 的测量结果。这些结果表明，需最大限度增加顶层与底层的铜含量，因为这两层不受额外 PCB 材料包裹，是散热效率最高的区域。只需在器件周围增设散热过孔，即可将 LDO 产生的热量有效传导至其他铜层。在使用没有散热焊盘的封装（例如 SOT-23 封装）进行设计时，这些过孔尤为重要。在这些情况下，也可将散热过孔直接设置在器件正下方，即热量产生最多的区域。根据 <https://www.jedec.org/system/files/docs/JESD51-9.pdf>，带有散热焊盘的封装需在散热焊盘区域设置尽可能多的散热过孔。最后，所有内部断开布局图 3-6 的数据表明，如果可能，必须在内层上加入额外的覆铜，即便这些铜箔未直接与 LDO 相连，也能对热性能产生积极影响。

## 5 未来研究方向

未来研究可围绕以下几个方向展开。研究上述布局或类似布局对超小尺寸（小于  $1\text{mm}^2$ ）封装（例如传统上热性能较差的 DSBGA 和 X2SON）热性能的影响。由于小尺寸封装本身散热能力较弱，与 WSON、TO-252 及 SOT-23 封装相比，PCB 布局对其热性能的影响可能会更小。本研究另一个更复杂的延伸方向是：构建一个公式或品质因数 (FOM)，将连接铜面积、非连接铜面积、这些区域相对于电路板层叠的位置、散热过孔数量等因素纳入其中。该 FOM 将与电路板等效热阻抗相关联，可用于为特定布局的预期结到环境热阻  $\theta_{JA}$  提供更具针对性的数值。

## 6 参考资料

1. 《采用小型 SMD 封装的 LDO 热性能》应用报告

2. 《AN-1520 外露焊盘封装实现最佳热阻的电路板布局布线指南》应用报告

3. 《半导体和 IC 封装热指标》

4. 《含引线的表面贴装封装对应的低效导热性测试板》

5. 《含引线的表面贴装封装对应的高效导热性测试板》

6. 《空间阵列表面贴装封装散热测量测试板》

7. 《现场测量 LDO 的热阻抗》应用报告

## 7 修订历史记录

注：以前版本的页码可能与当前版本的页码不同

| Changes from Revision * (February 2019) to Revision A (September 2025) | Page              |

|------------------------------------------------------------------------|-------------------|

| • 更新了整个文档中的表格、图和交叉参考的编号格式.....                                         | <a href="#">2</a> |

## A 热测试电路板布局

### A.1 TPS745 (WSON) 图

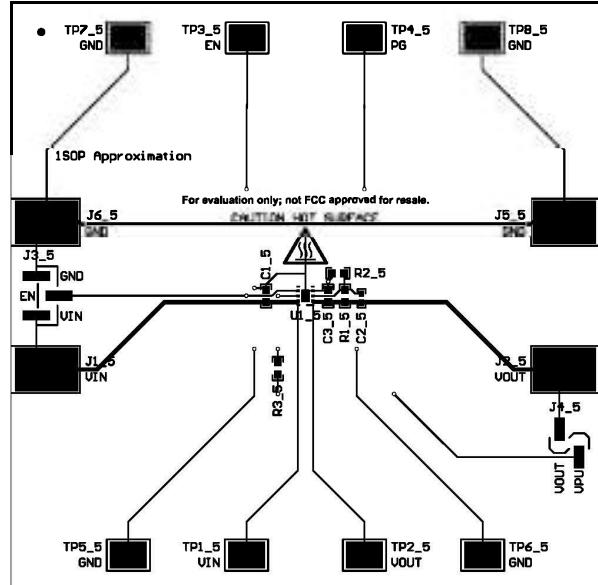

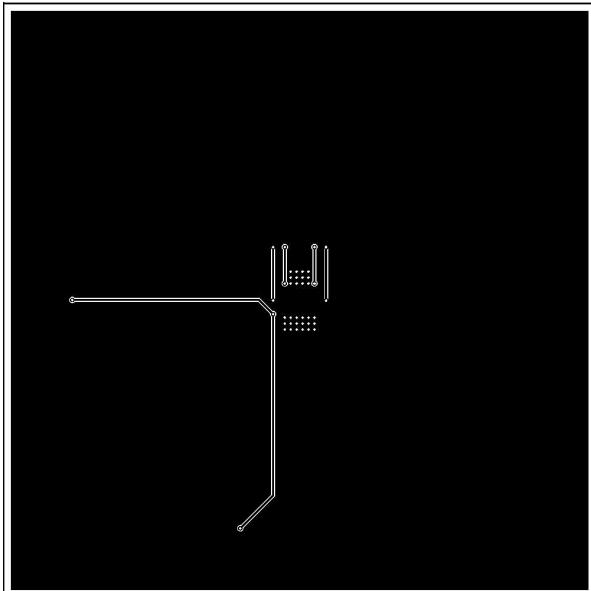

#### A.1.1 1S0P 近似布局图

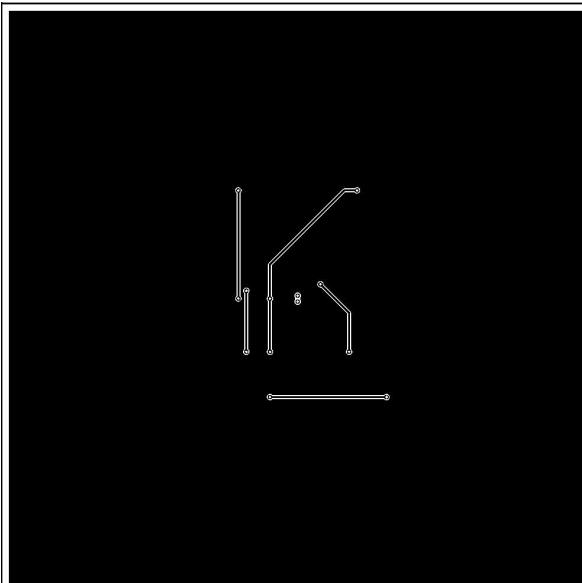

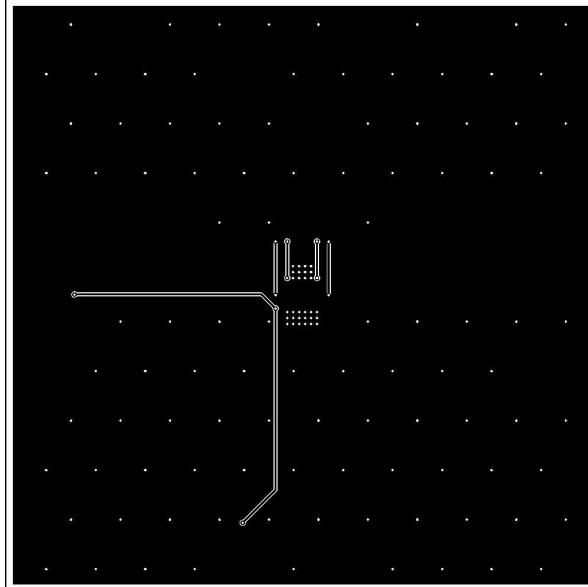

图 A-1. TPS745 (WSON) 1S0P 近似布局顶层

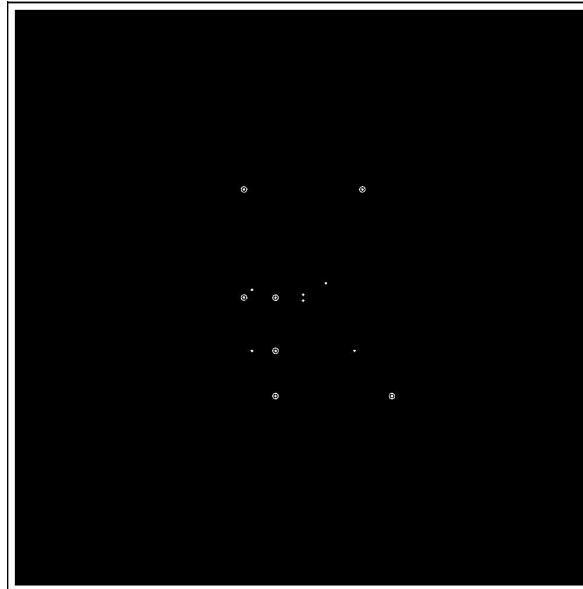

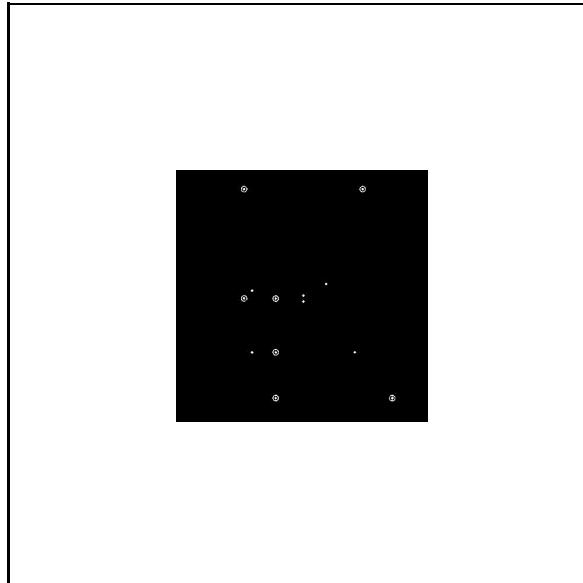

图 A-2. TPS745 (WSON) 1S0P 近似布局内层 1

图 A-3. TPS745 (WSON) 1S0P 近似布局内层 2

图 A-4. TPS745 (WSON) 1S0P 近似布局底层

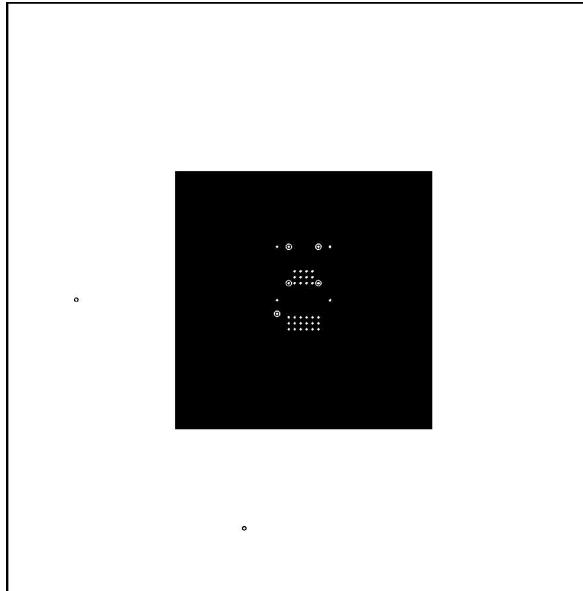

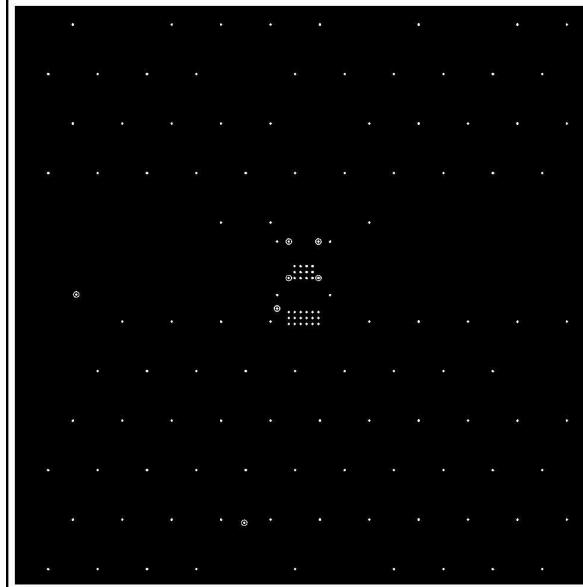

**A.1.2 内部断开布局图**

### A.1.3 JEDEC 高 K 近似布局图

图 A-9. TPS745 (WSON) JEDEC 高 K 近似布局顶层

图 A-10. TPS745 (WSON) JEDEC 高 K 近似布局内层 1

图 A-11. TPS745 (WSON) JEDEC 高 K 近似布局内层

2

图 A-12. TPS745 (WSON) JEDEC 高 K 近似布局底层

**A.1.4 热增强型布局图**

### A.1.5 热饱和型布局图

图 A-17. TPS745 (WSON) 热饱和型布局顶层

图 A-18. TPS745 (WSON) 热饱和型布局内层 1

图 A-19. TPS745 (WSON) 热饱和型布局内层 2

图 A-20. TPS745 (WSON) 热饱和型布局底层

## A.2 TPS7B82-Q1 (TO-252) 图

### A.2.1 1SOP 近似布局图

### A.2.2 内部断开布局图

### A.2.3 JEDEC 高 K 近似布局图

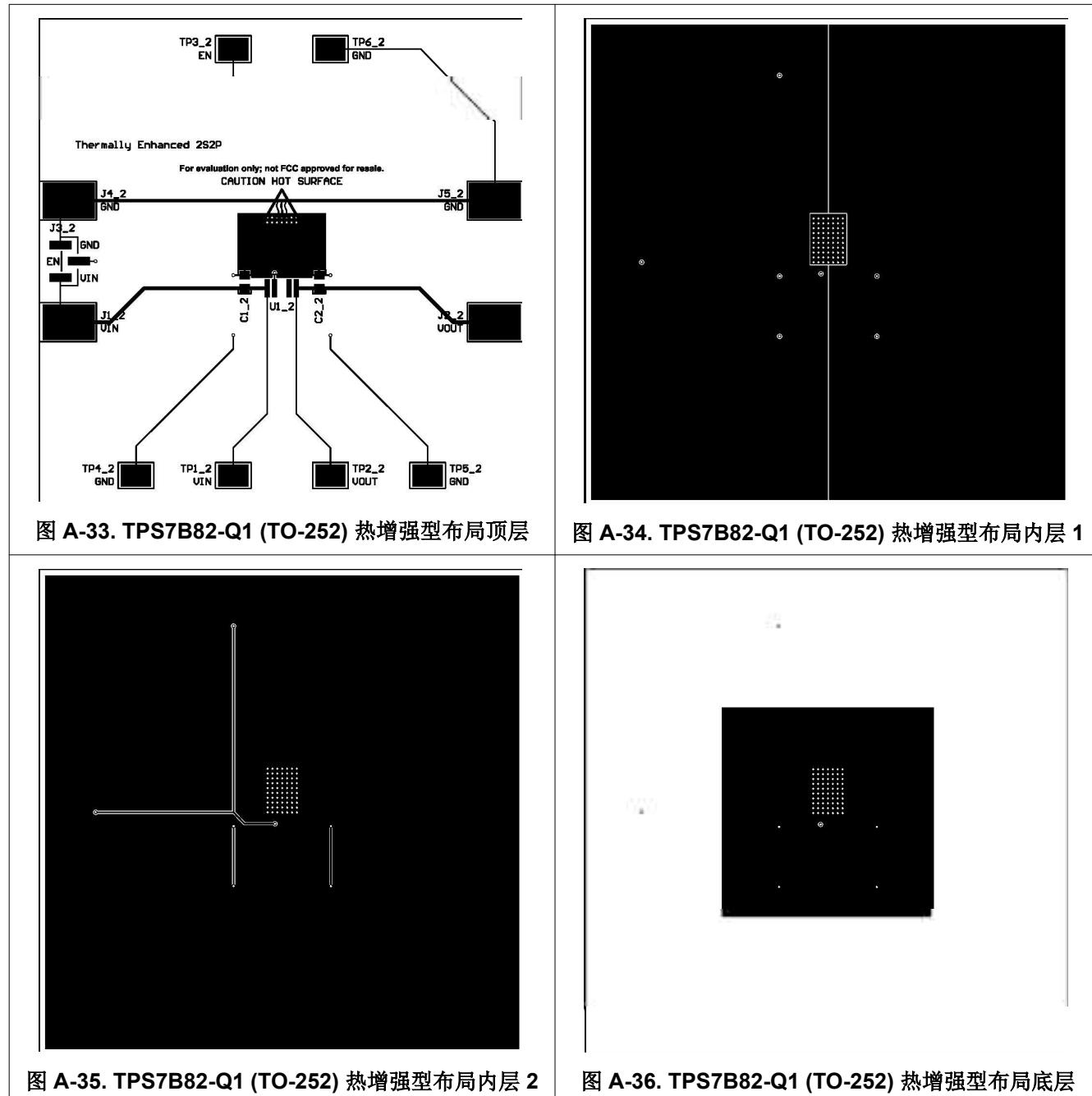

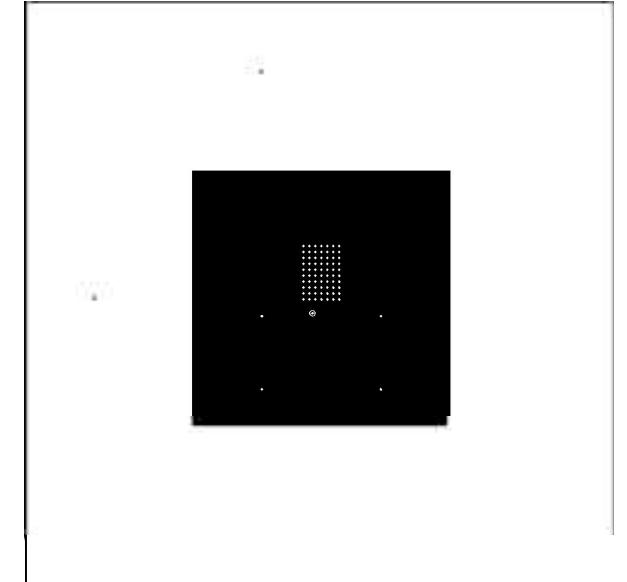

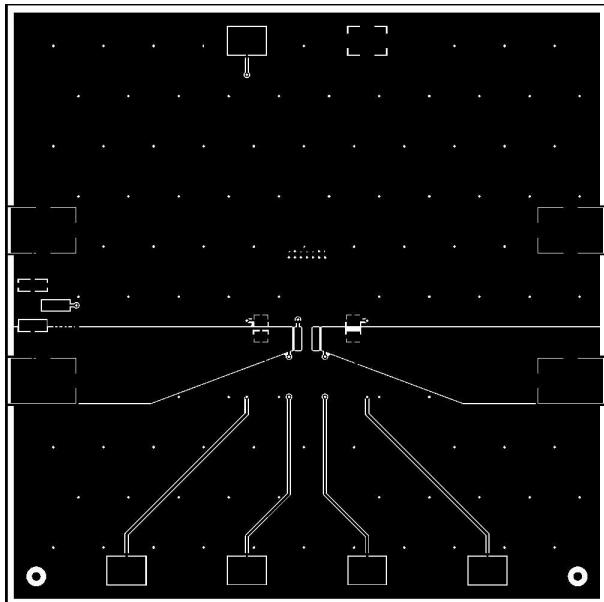

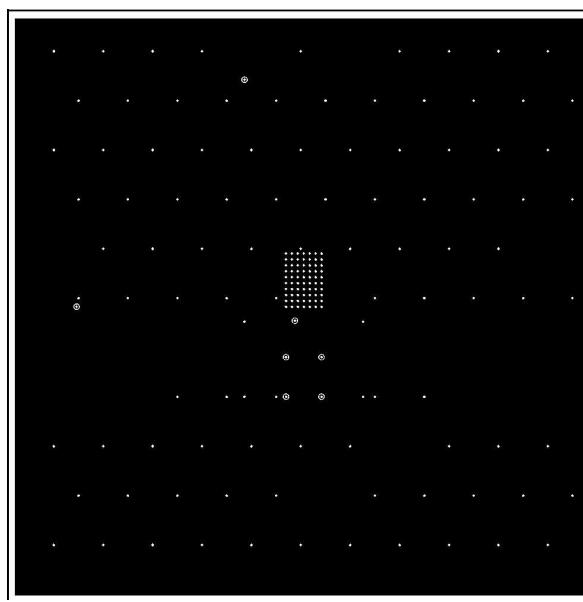

#### A.2.4 热增强型布局图

图 A-33. TPS7B82-Q1 (TO-252) 热增强型布局顶层

图 A-34. TPS7B82-Q1 (TO-252) 热增强型布局内层 1

图 A-35. TPS7B82-Q1 (TO-252) 热增强型布局内层 2

图 A-36. TPS7B82-Q1 (TO-252) 热增强型布局底层

### A.2.5 热饱和型布局图

图 A-37. TPS7B82-Q1 (TO-252) 热饱和型布局顶层

图 A-38. TPS7B82-Q1 (TO-252) 热饱和型布局内层 1

图 A-39. TPS7B82-Q1 (TO-252) 热饱和型布局内层 2

图 A-40. TPS7B82-Q1 (TO-252) 热饱和型布局底层

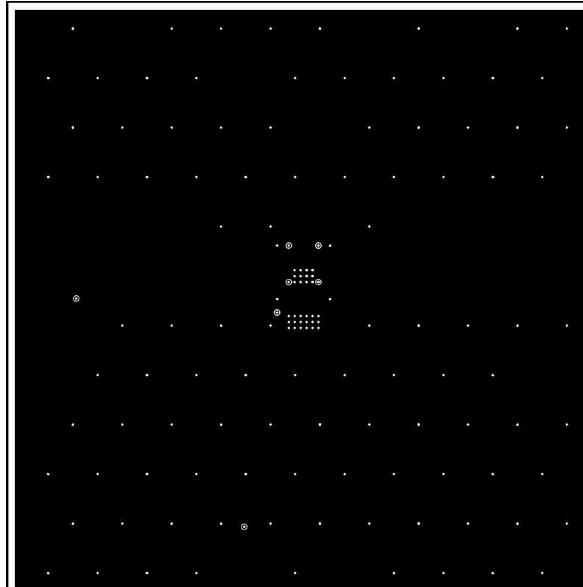

### A.3 TLV755P (SOT-23) 图

#### A.3.1 1SOP 近似布局图

图 A-41. TLV755P (SOT-23) 1SOP 近似布局顶层

图 A-42. TLV755P (SOT-23) 1SOP 近似布局内层 1

图 A-43. TLV755P (SOT-23) 1SOP 近似布局内层 2

图 A-44. TLV755P (SOT-23) 1SOP 近似布局底层

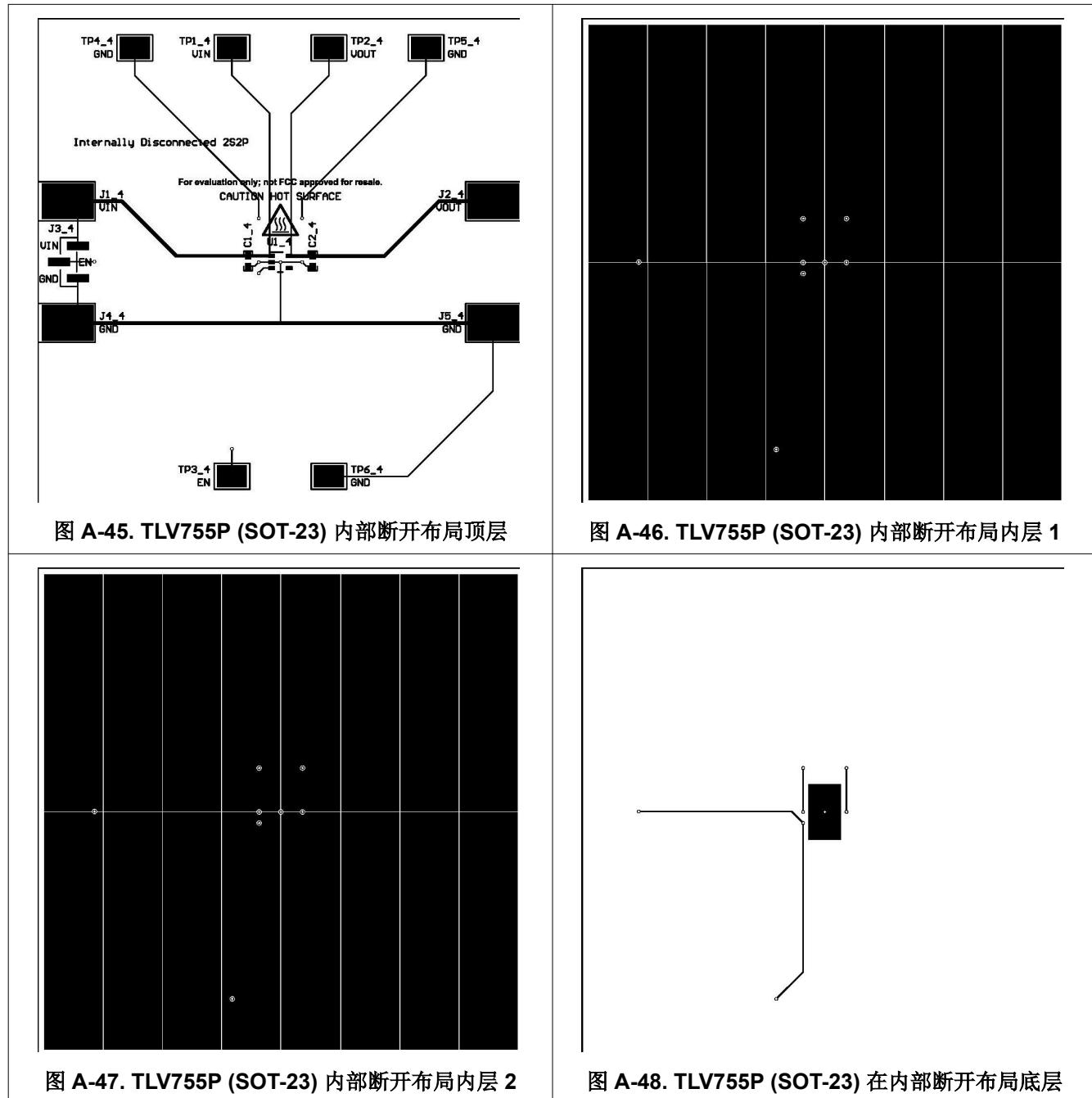

**A.3.2 内部断开布局图**

图 A-45. TLV755P (SOT-23) 内部断开布局顶层

图 A-46. TLV755P (SOT-23) 内部断开布局内层 1

图 A-47. TLV755P (SOT-23) 内部断开布局内层 2

图 A-48. TLV755P (SOT-23) 在内部断开布局底层

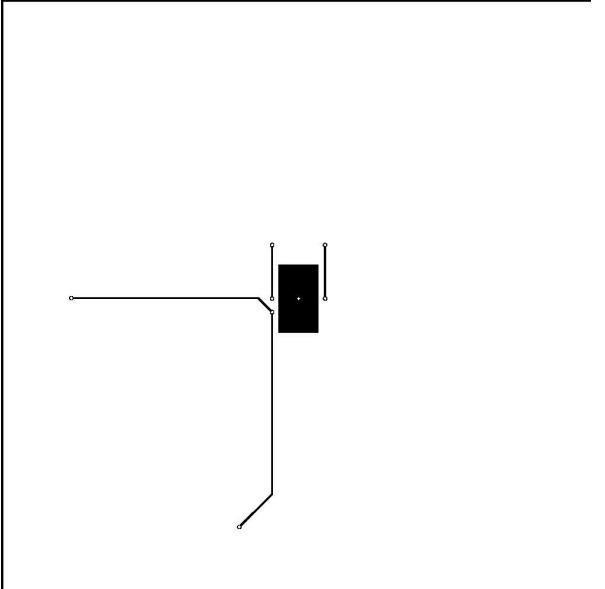

### A.3.3 JEDEC 高 K 近似布局图

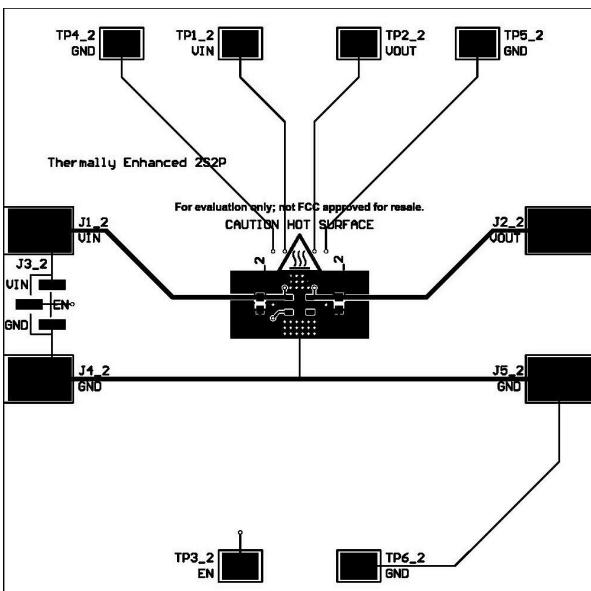

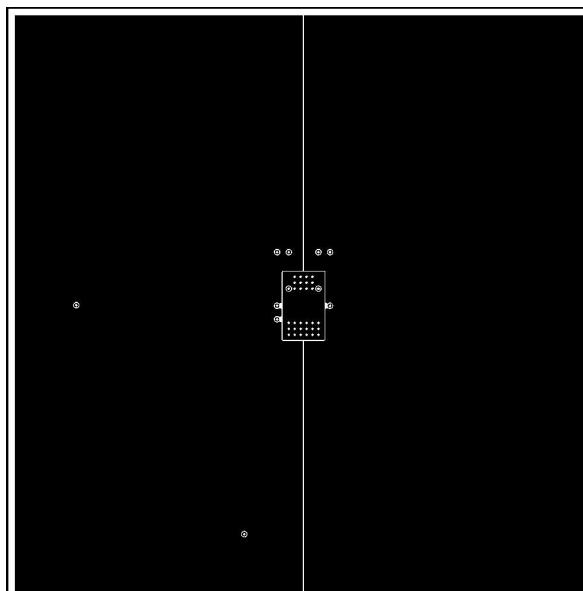

图 A-49. TLV755P (SOT-23) JEDEC 高 K 近似布局顶层

图 A-50. TLV755P (SOT-23) JEDEC 高 K 近似布局内层 1

图 A-51. TLV755P (SOT-23) JEDEC 高 K 近似布局内层 2

图 A-52. TLV755P (SOT-23) JEDEC 高 K 近似布局底层

**A.3.4 热增强型图**

图 A-53. TLV755P (SOT-23) 热增强型布局顶层

图 A-54. TLV755P (SOT-23) 热增强型布局内层 1

图 A-55. TLV755P (SOT-23) 热增强型布局内层 2

图 A-56. TLV755P (SOT-23) 热增强型布局底层

### A.3.5 热饱和型布局图

图 A-57. TLV755P (SOT-23) 热饱和型布局顶层

图 A-58. TLV755P (SOT-23) 热饱和型布局内层 1

图 A-59. TLV755P (SOT-23) 热饱和型布局内层 2

图 A-60. TLV755P (SOT-23) 热饱和型布局底层

## B 热测试结果

### B.1 热性能数据

表 B-1. 最高环境温度与功率耗散间的关系

| 电路板            | TPS745 (WSON)      |                         | TPS7B82-Q1 (TO-252) |                         | TLV755P (SOT-23)   |                         |

|----------------|--------------------|-------------------------|---------------------|-------------------------|--------------------|-------------------------|

|                | P <sub>D</sub> (W) | T <sub>A,max</sub> (°C) | P <sub>D</sub> (W)  | T <sub>A,max</sub> (°C) | P <sub>D</sub> (W) | T <sub>A,max</sub> (°C) |

| 1SOP 近似布局      | 0.00               | 175                     | 0.00                | 182                     | 0.00               | 165                     |

|                | 0.26               | 130                     | 0.51                | 135                     | 0.20               | 124                     |

|                | 0.51               | 88                      | 1.00                | 90                      | 0.39               | 80                      |

|                | 0.90               | 23                      | 1.70                | 27                      | 0.62               | 24                      |

| 内部断开布局         | 0.00               | 178                     | 0.00                | 178                     | 0.00               | 164                     |

|                | 0.59               | 129                     | 1.00                | 134                     | 0.25               | 126                     |

|                | 1.14               | 83                      | 1.95                | 88                      | 0.49               | 88                      |

| JEDEC 高 K 近似布局 | 0.00               | 178                     | 0.00                | 180                     | 0.00               | 163                     |

|                | 0.74               | 130                     | 1.53                | 133                     | 0.27               | 122                     |

|                | 1.49               | 87                      | 3.01                | 84                      | 0.53               | 81                      |

| 热增强型           | 0.00               | 179                     | 0.00                | 178                     | 0.00               | 166                     |

|                | 0.83               | 135                     | 1.77                | 129                     | 0.36               | 128                     |

|                | 1.73               | 98                      | 3.51                | 84                      | 0.69               | 91                      |

| 热饱和型           | 0.00               | 177                     | 0.00                | 177                     | 0.00               | 164                     |

|                | 0.84               | 139                     | 1.81                | 128                     | 0.38               | 127                     |

|                | 1.64               | 106                     | 3.62                | 82                      | 0.76               | 85                      |

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，您将全额赔偿，TI 对此概不负责。

TI 提供的产品受 [TI 销售条款](#)、[TI 通用质量指南](#) 或 [ti.com](#) 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品，否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025，德州仪器 (TI) 公司

最后更新日期：2025 年 10 月