*Application Note*

# 使用单个 LVC MOS 振荡器驱动多个负载

Connor Lewis, Subhayan Nath, William Pfennigwerth, Harish Ramesh

## 摘要

为了降低成本并简化 BOM，有些系统的设计人员想要在时钟信号完整性不关键的应用中使用单个时钟源来驱动多个负载。低频单端 LVC MOS 时钟信号是这种成本削减的良好目标，因为抖动要求通常比较宽松，而且相对于需要计时的接收器，振荡器的成本可能较高。但是，这种技术会引起许多关于具体路由实施及对信号完整性影响的问题。负载共位对信号完整性有何影响？多个负载之间可接受的最长布线长度是多少？在保持上升或下降时间可接受的同时，单个时钟源可驱动多少个接收器？这对振铃和信号反射有何影响？本应用手册讨论了将布线拆分为多个负载的传输线路影响，并根据使用 LMK6C 和 CDC6C 低抖动、高性能、体声波 (BAW) 固定频率 LVC MOS 振荡器的 IBIS 仿真结果提供了一些推荐的拓扑。

## 内容

|                        |           |

|------------------------|-----------|

| <b>1 简介和测试方法</b>       | <b>2</b>  |

| <b>2 仿真设置</b>          | <b>3</b>  |

| <b>3 布线拓扑和仿真结果</b>     | <b>4</b>  |

| 3.1 单线路                | 4         |

| 3.2 星型线路               | 6         |

| 3.3 分离线路               | 7         |

| 3.4 星型线路与分离线路          | 8         |

| <b>4 实验室测量</b>         | <b>9</b>  |

| 4.1 实验室测量设置            | 9         |

| 4.2 实验室测量结果以及与仿真数据的相关性 | 10        |

| <b>5 负载之间的布线长度不匹配</b>  | <b>12</b> |

| <b>6 应用示例：FPD-Link</b> | <b>14</b> |

| <b>7 总结</b>            | <b>15</b> |

| <b>8 参考资料</b>          | <b>15</b> |

| <b>9 修订历史记录</b>        | <b>16</b> |

## 商标

所有商标均为其各自所有者的财产。

## 1 简介和测试方法

在高频或长布线长度条件下为系统提供时钟信号时，电缆和 PCB 布线通常被视为传输线路而不是简单的电线。一般来说，当通过布线或电缆的传播延迟大于信号上升时间的 0.25 倍时，估计就需要考虑传输线路影响。例如，由 FR-4 材料制成的典型 PCB 的信号传播延迟约为 150ps/in。假设信号上升时间为 1ns，则任何超过 1.5 英寸的布线都可能具有类似于传输线路的行为，如不解决，可能会出现信号完整性问题。

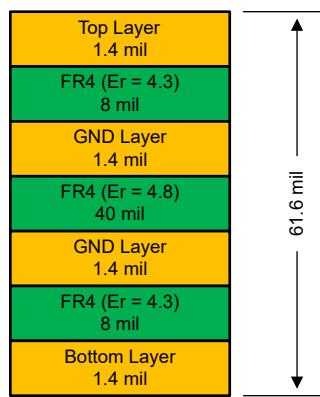

以下仿真结果显示了使用不同布线方案通过单个 LVC MOS 振荡器驱动多个负载的影响。为了执行仿真，我们在 Altium Designer 中设计了 4 层的层叠，并确定了产生标称  $50\Omega$  特征布线阻抗所需的布线宽度。选择这种特殊的层叠是为了确保具有标称  $50\Omega$  阻抗的布线能够与 0201 无源器件的焊盘尺寸紧密匹配，从而使信号通过板载电阻器和电容器时产生的反射最小。

借助这种层叠，我们设计了一系列的 PCB 布局来模拟几种将驱动器连接到多个负载的不同方法。然后，转换了布局文件用于 IBIS SI 仿真，并使用 25MHz TI BAW 振荡器作为驱动器。

图 1-1. 负载板仿真中使用的层叠

表 1-1. 使用负载板层叠时的布线阻抗与厚度

| 布线厚度 (mil) | 布线的特征阻抗 ( $Z_0$ ) |

|------------|-------------------|

| 9          | $60\Omega$        |

| 13         | $50\Omega$        |

| 20         | $40\Omega$        |

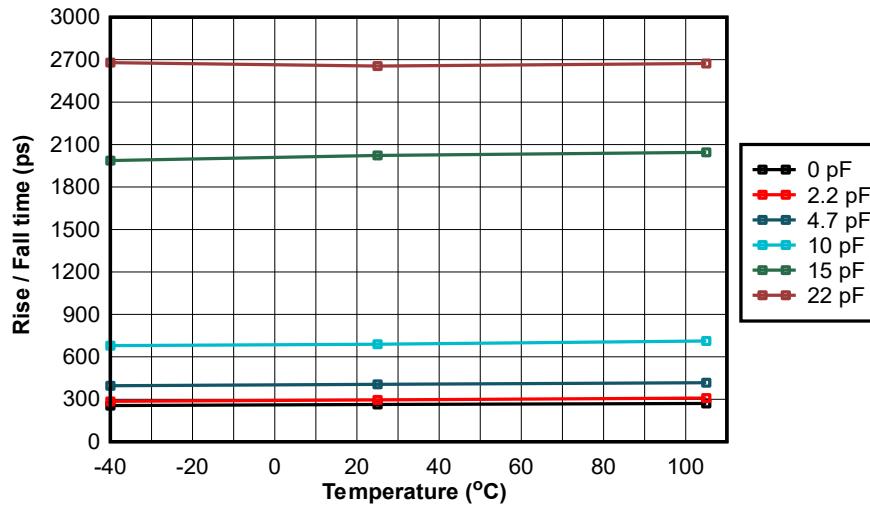

在连接到多个负载时，可以放置线路电阻器以实现  $50\Omega$  阻抗匹配。每种布线方案使用  $10\text{pF}$  的组合电容驱动一个、两个或四个负载。为了确保布线拓扑是唯一改变的变量，所有测试配置中的总负载电容都保持恒定。[图 1-2](#) 演示了增加 LVC MOS 振荡器输出上的总容性负载如何增加上升和下降时间并降低性能。通过使用恒定的  $10\text{pF}$  负载来考虑驱动四个负载的最坏情况（每个负载的标称负载电容为  $2.5\text{pF}$ ），从实验中消除了这一影响因素。[节 3](#) 提供了所测试的各种布线和负载拓扑的更深入说明。

图 1-2. 输出频率为 25MHz、电源电压为 3.3V 时，LMK6C 上升或下降时间 (ps) 与温度和负载电容间的关系

## 2 仿真设置

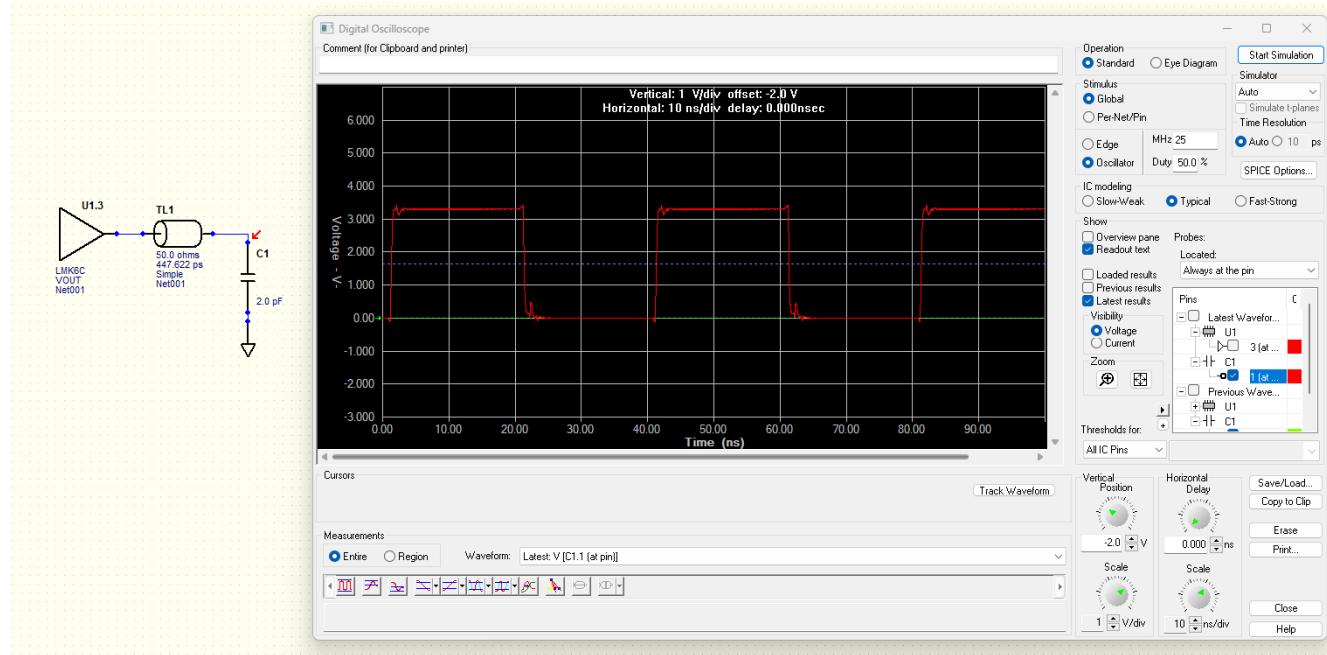

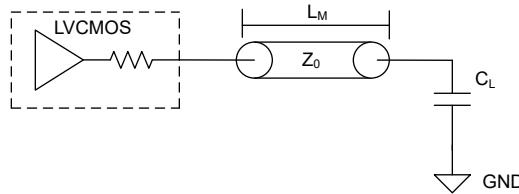

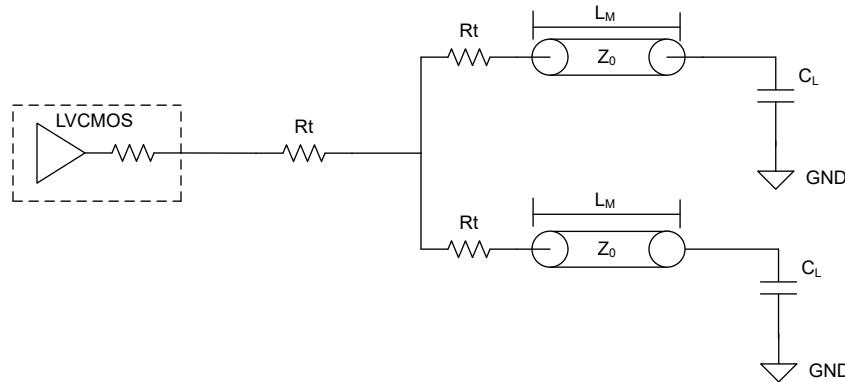

IBIS SI 仿真在 MentorGraphics 的 Hyperlynx 工具中运行。Altium 板级配置文件被导出为自由形式的 SI 原理图，从而据此对传输线路和存根对实际 PCB 布线和层堆叠的影响进行建模。图 2-1 显示了具有 LVCMS 时钟驱动器、传输线路模型和负载电容的简版仿真示例。将 PCB 布局提取到 SI 模型后，电路中会添加一系列传输线路模型，用于表示布线互连、无源器件焊盘、存根和其他影响布线阻抗的因素。Hyperlynx 波形查看器允许用户更改时钟振荡频率以及时间和垂直缩放，这与传统示波器类似。探头需放置在负载电容器而非驱动器处，以模拟接收器在实际系统中可以检测的内容。

图 2-1. Hyperlynx SI 仿真设置

### 3 布线拓扑和仿真结果

#### 3.1 单线路

这是单端信号的典型配置。为了实现出色的信号完整性，建议采用单线路配置，因为节点数会减少到每条线路仅有一个负载。单线路、单负载配置用作所测试的其他拓扑的基准。

图 3-1. 单线路、单负载拓扑

当驱动多个负载且负载之间的间隔较小时，单线路、多负载配置是不错的选择。这种拓扑的一些常见用例包括驱动同一器件上的两个时钟输入引脚或多个靠近放置的器件。在本研究中，负载之间的距离需要限制在 1 英寸以下，才能被视为单线路配置。假设每个负载与主线路之间的距离相等，因此每个接收器的  $L_s$  长度相同。

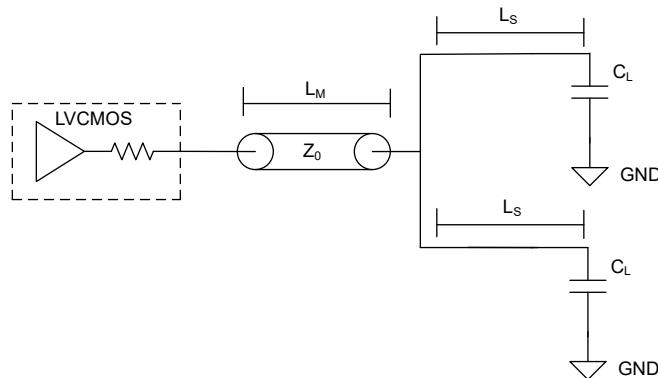

图 3-2. 单线路、多负载拓扑

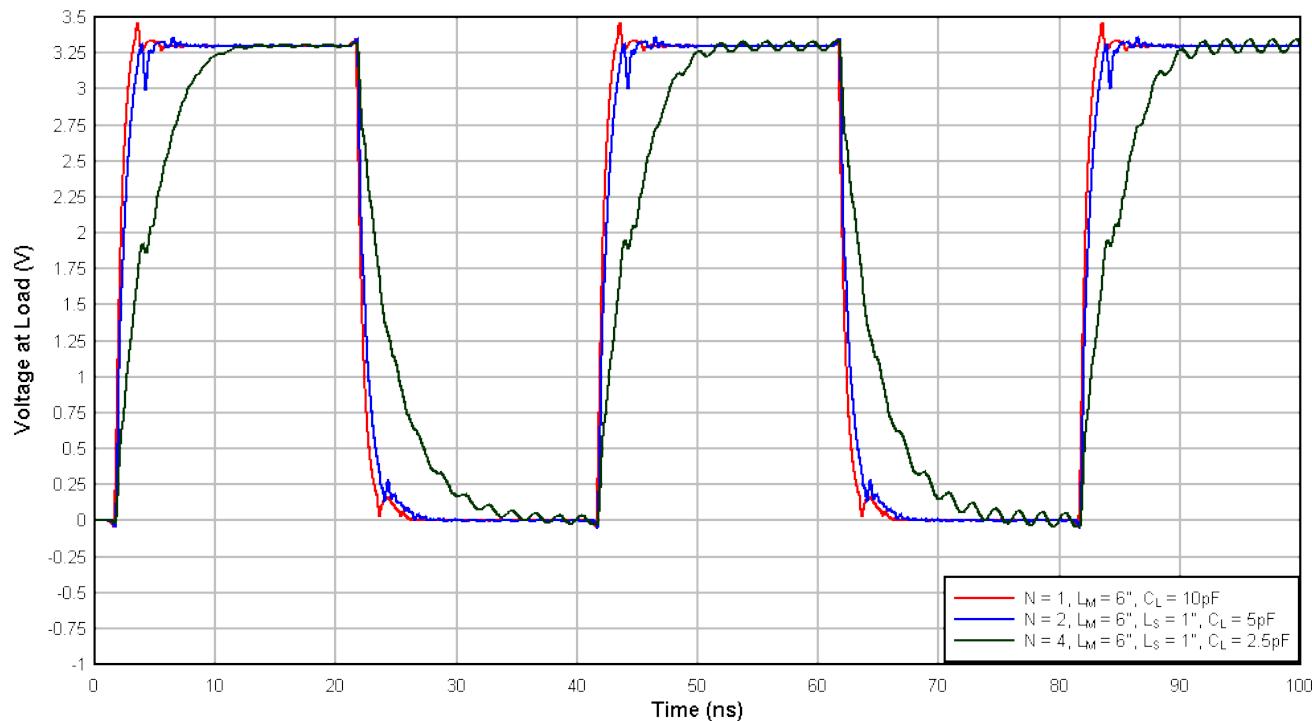

图 3-3. 单线路仿真结果

表 3-1. 单线路上升或下降时间

| 负载数量 | 布线长度 - $L_M$ | 上升时间 (ns) | 下降时间 (ns) |

|------|--------------|-----------|-----------|

| 1    | 6"           | 0.676     | 0.763     |

| 2    | 6"           | 0.938     | 1.105     |

| 4    | 6"           | 4.010     | 3.946     |

对于单线路配置，驱动两个负载会产生可接受的信号质量，上升和下降时间仅略微延长，几乎没有可测量的反射失真。

添加四个负载后，上升/下降时间显著延长，但波形中的反射仍然极小。

### 3.2 星型线路

星型线路配置是一种未在电路板上并置多个负载时的备选设计。这种配置从驱动器的单条输出线路开始，然后在更靠近接收器一侧的位置进行分支。星型线路布线类似于单线路方法，但接收器之间的间隔超过 1 英寸。

这种配置添加了线路电阻器 ( $R_t$ ) 以帮助进行阻抗匹配，因此驱动器会看到连续的  $50\Omega$  阻抗。 $R_t$  根据方程式 1 进行计算得出。

$$R_t = \frac{N-1}{N+1} \times Z_0 \quad (1)$$

其中  $N$  等于要驱动的负载数量， $Z_0$  等于布线的特性阻抗。

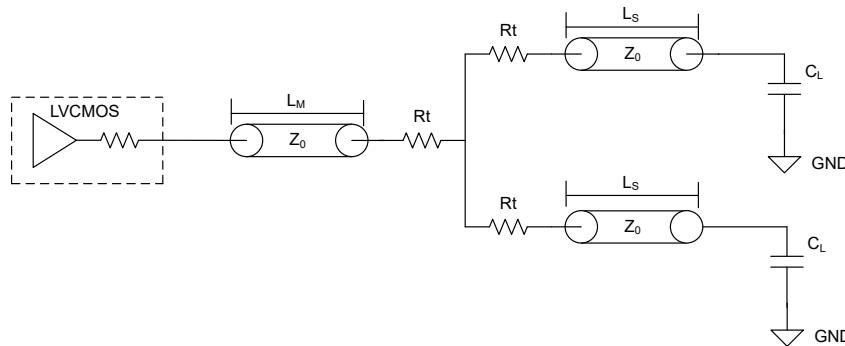

图 3-4. 星型线路拓扑

图 3-5. 星型线路仿真结果

表 3-2. 星型线路上升/下降时间

| 负载数量 | 布线长度 - $L_s$ | 上升时间 (ns) | 下降时间 (ns) |

|------|--------------|-----------|-----------|

| 2    | 2"           | 1.858     | 2.206     |

| 2    | 6"           | 2.839     | 3.980     |

星型线路配置与单线路配置类似，仅使用 2 英寸的拆分布线长度时，我们可以看到上升和下降时间增加，并会出现非常轻微的纹波。随着布线长度增加到 6 英寸，纹波会加剧，上升/下降时间会进一步增加。虽然该信号可以满足某些接收器的要求，但进一步增加分离线路长度可能会导致信号完整性不可接受。

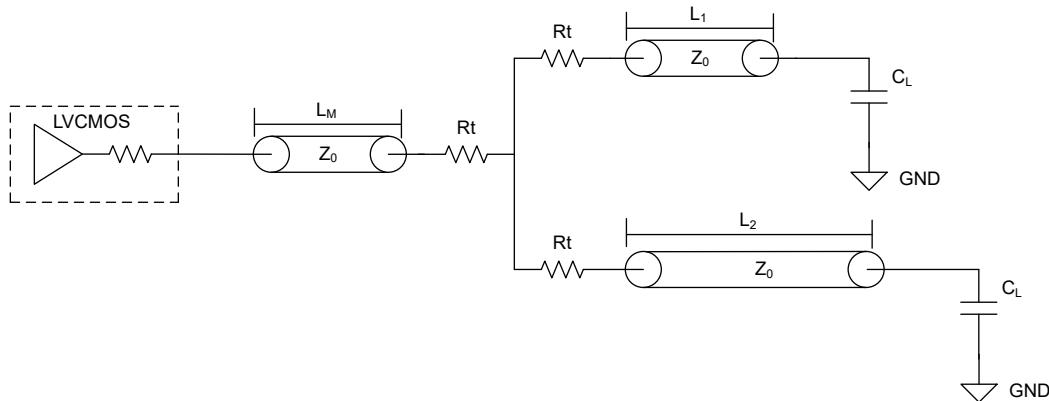

### 3.3 分离线路

当多个负载未在电路板上并置时，可以使用分离线路配置。在这种拓扑中，布线分支到驱动器附近，在大部分布线距离内充当独立的传输线路。

再次根据 [方程式 1](#) 添加用于阻抗匹配的线路电阻器 ( $R_t$ )。

图 3-6. 分离线路拓扑

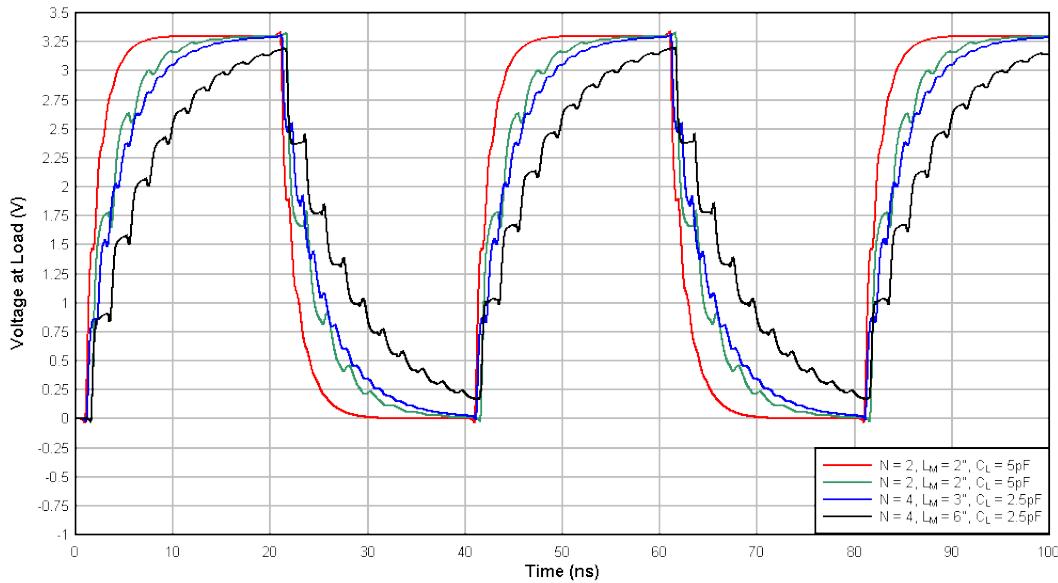

图 3-7. 分离线路仿真结果

表 3-3. 分离线路上升或下降时间

| 负载数量 | 布线长度 - $L_M$ | 上升时间 (ns) | 下降时间 (ns) |

|------|--------------|-----------|-----------|

| 2    | 2"           | 1.971     | 2.228     |

| 2    | 6"           | 3.762     | 4.556     |

| 4    | 3"           | 4.781     | 5.630     |

| 4    | 6"           | 7.998     | 10.16     |

在拆分线路配置中，负载数量和线路长度对信号完整性的影响比星型线路拓扑更大。随着负载增多以及布线长度增加，信号完整性会恶化并伴随更严重的振铃和更长的上升/下降时间。

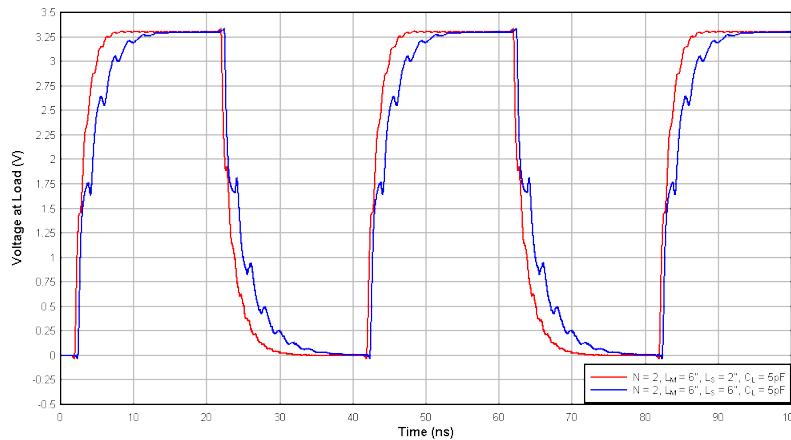

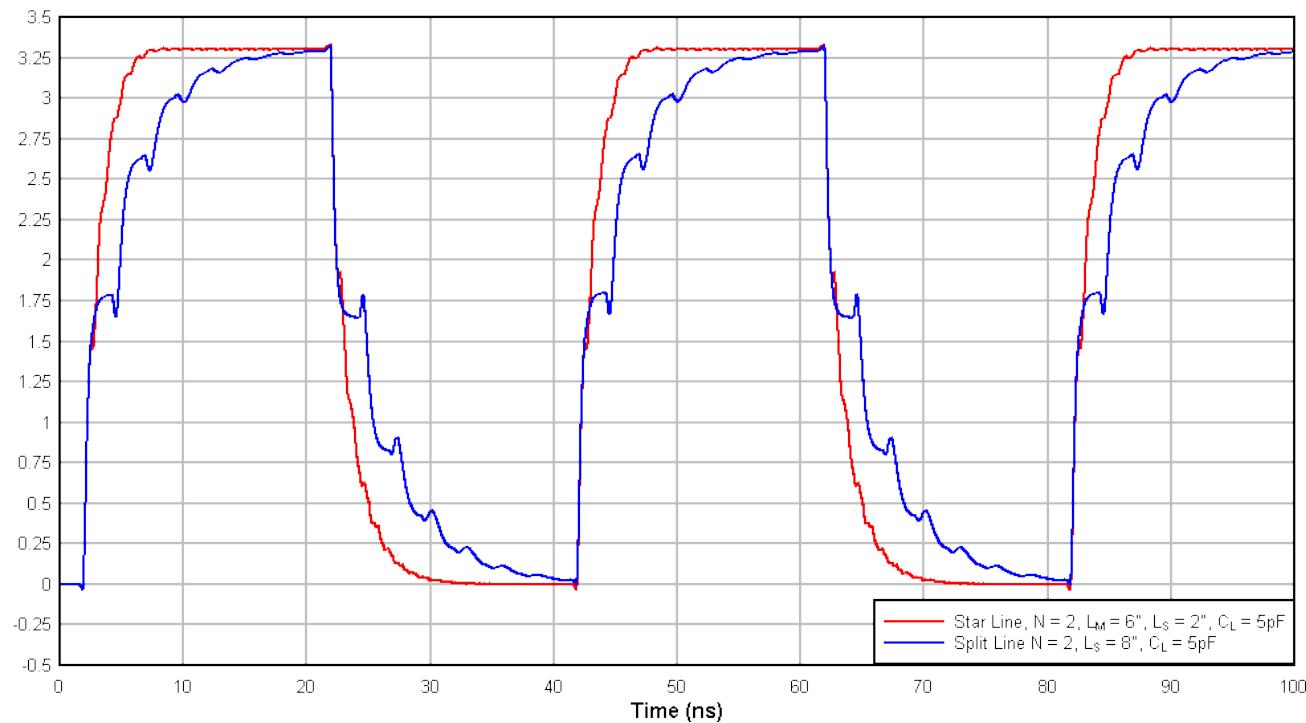

### 3.4 星型线路与分离线路

在驱动两个负载、每个负载的电容为  $5\text{pF}$  并使用总长 8 英寸 PCB 布线的情况下，下面比较了星型线路和分离线路拓扑。如图 3-8 所示，星型线路方法可实现更好的信号完整性以及更短的上升或下降时间。

图 3-8. 星型线路与分离线路仿真结果

## 4 实验室测量

### 4.1 实验室测量设置

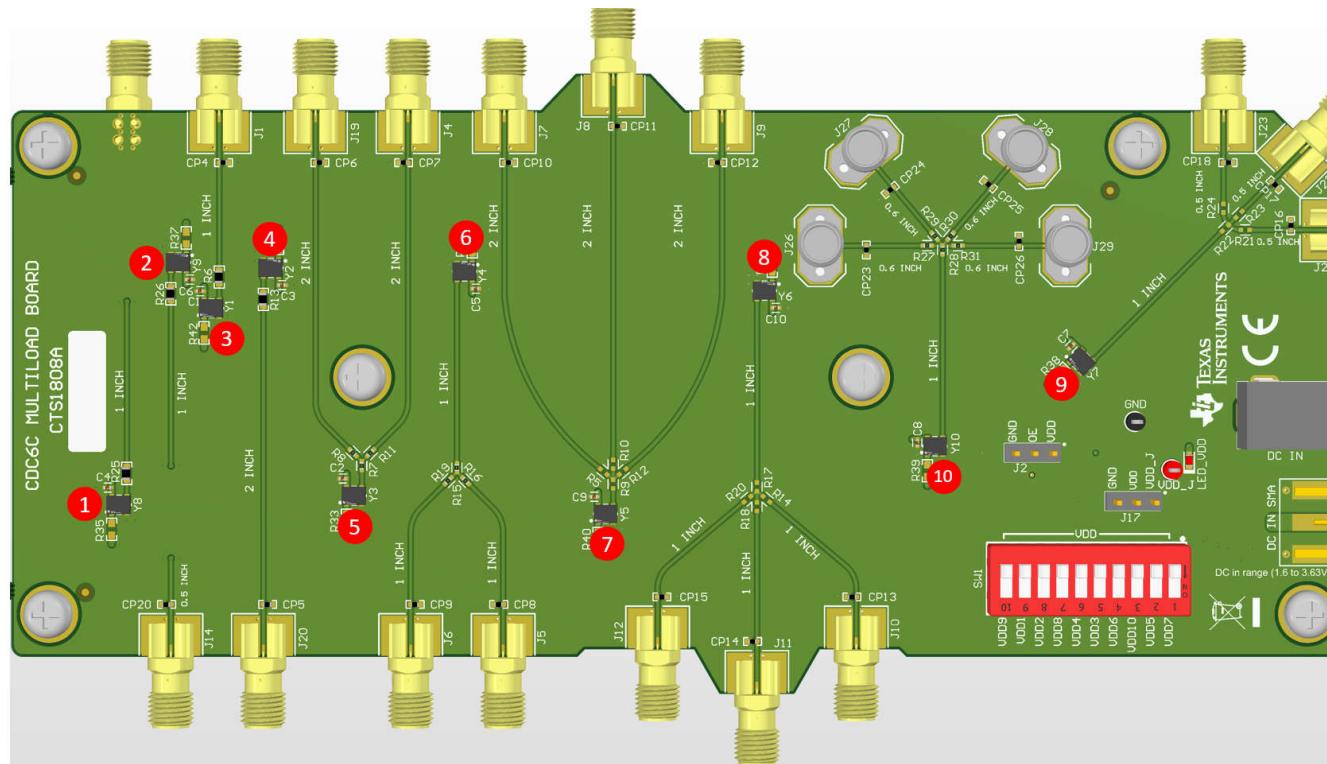

为了确认仿真结果的结论，我们设计了一个采用多种布线方案的负载板。该负载板从板载 LVCMS 振荡器扇出时钟输出，以使用具有不同布线长度的拆分线路和星型线路拓扑进行负载。负载板包含以下布线配置：

1. 2 英寸单布线，含 1 个过孔

2. 2 英寸单布线，含 2 个过孔

3. 1 英寸单布线，无过孔

4. 2 英寸单布线，无过孔

5. 2 英寸布线扇出至 2 个负载，在驱动器附近拆分（拆分线路拓扑）

6. 2 英寸布线扇出至 2 个负载，在负载附近拆分（星型线路拓扑）

7. 2 英寸布线扇出至 3 个负载，在驱动器附近拆分（拆分线路拓扑）

8. 2 英寸布线扇出至 3 个负载，在负载附近拆分（星型线路拓扑）

9. 1.5 英寸布线扇出至 3 个负载，在负载附近拆分（星型线路拓扑）

10. 1.6 英寸布线扇出至 4 个负载，在负载附近拆分（星型线路拓扑）

负载板设计以及用于添加额外布线长度的测试板的图片如 图 4-1 所示：

图 4-1. 振荡器多负载扇出板

负载板的层堆叠与仿真负载板相匹配，如 图 1-1 所示。

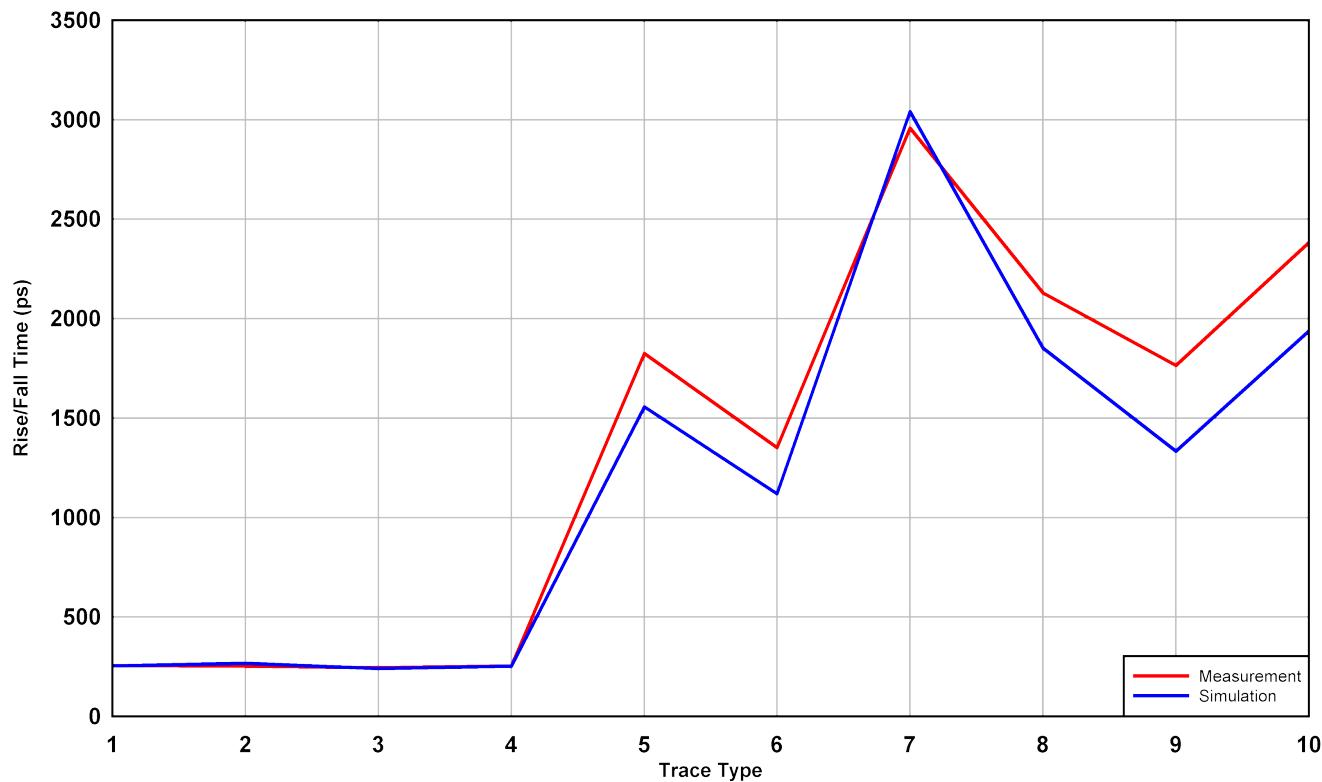

## 4.2 实验室测量结果以及与仿真数据的相关性

在每个输出端的负载电容为  $2\text{pF}$  的情况下，按照 [节 2](#) 中所述的程序提取电路板布局参数，并在 Hyperlynx 中运行信号完整性仿真。使用此电路板收集的测量结果以及与基于仿真结果的预测值的比较如下所示。

**表 4-1. 多负载板上，不同布线拓扑的上升或下降时间和抖动结果**

| 跟踪类型 | 跟踪说明              | 抖动 (fs) 测量 | 上升时间 (ps) 测量 | 下降时间 (ps) 测量 | 上升时间 (ps) 仿真 | 下降时间 (ps) 仿真 |

|------|-------------------|------------|--------------|--------------|--------------|--------------|

| 1    | 2 英寸单线路，含 1 个过孔   | 335        | 250          | 263          | 263          | 245          |

| 2    | 2 英寸单线路，含 2 个过孔   | 335        | 249          | 257          | 270          | 266          |

| 3    | 1 英寸单线路，无过孔       | 333        | 238          | 254          | 277          | 204          |

| 4    | 2 英寸单线路，无过孔       | 334        | 251          | 259          | 263          | 244          |

| 5    | 2 英寸双线路，在驱动器附近拆分  | 336        | 1780         | 1870         | 1475         | 1640         |

| 6    | 2 英寸双线路，在负载附近拆分   | 332        | 1283         | 1422         | 1050         | 1190         |

| 7    | 2 英寸三线路，在驱动器附近拆分  | 350        | 2895         | 3023         | 2904         | 3180         |

| 8    | 2 英寸三线路，在负载附近拆分   | 350        | 2051         | 2210         | 1715         | 1990         |

| 9    | 1.5 英寸三线路，在负载附近拆分 | 349        | 1693         | 1837         | 1248         | 1420         |

| 10   | 1.6 英寸四线路，在负载附近拆分 | 376        | 2385         | 2380         | 1796         | 2080         |

从 [表 4-1](#) 中显示的结果可以看出，布线拓扑几乎不会影响抖动性能。请注意，抖动测量是用包含内部  $50\Omega$  终端的相位噪声分析仪进行的，与高阻抗纯电容负载相比，它可以减少在接收器处测得的反射。仿真测量结果的上升/下降时间趋势与实验室测量结果密切相关。[图 4-2](#) 中 x 轴的布线编号与 [表 4-1](#) 中使用的编号方案和 [图 4-1](#) 上的标签相对应。随着布线扇出的增加，仿真结果的耦合度与实验室测量结果相比降低。这主要是因为未在测试设置中对 SMA 适配器、电缆和探头的寄生电容进行建模。根据实验室测量结果与仿真数据之间的相关性，预计仿真上升/下降时间结果与实际测量结果的裕度在  $\pm 25\%$  的范围内。此裕度考虑了器件间差异、影响寄生电容和特性布线阻抗的 PCB 覆铜厚度制造容差以及其他环境因素。总而言之，驱动多个负载时，系统设计人员可以放心地使用 **IBIS** 仿真为不同布线方案估算时钟信号的上升/下降时间和信号完整性。

在所有布线拓扑中，当负载为  $2\text{pF}$  时，输出振幅保持轨到轨的规定范围内，但会随着负载数量或总负载电容的增加而降低。在仿真和实际实验室测量中，在负载附近进行拆分（星型线路拓扑）布线可实现更好的性能。

图 4-2. 仿真与测量：多负载板上，不同布线拓扑的平均上升或下降时间结果

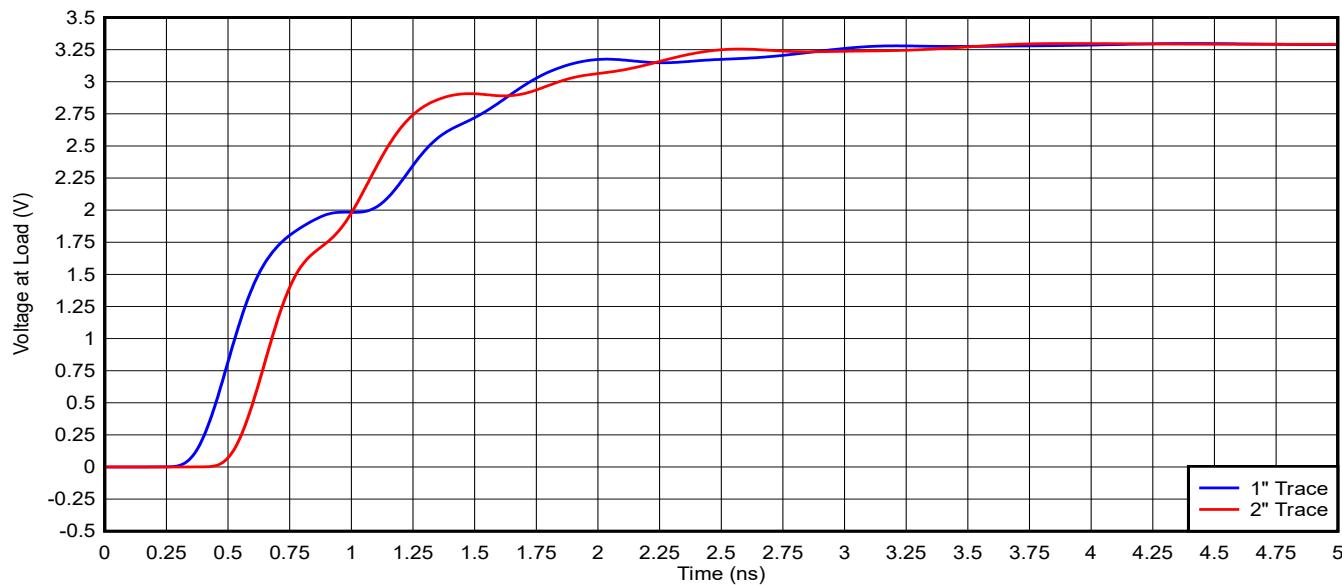

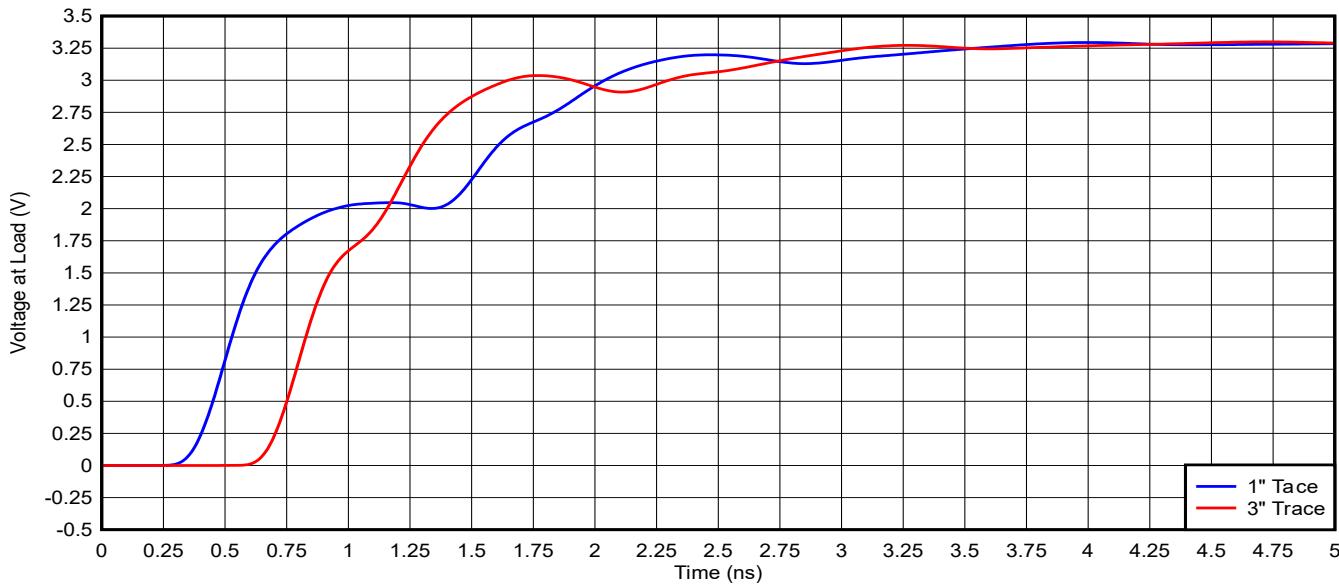

## 5 负载之间的布线长度不匹配

图 5-1. 驱动多个负载时的布线长度不匹配

如果在驱动多个负载时接收器之间的布线长度不匹配，则可能会发生过多的信号反射。当布线长度不匹配时，可能会基于到每个接收器的路径之间的传播延迟差异而引发振铃。例如，考虑这样一种情况：LVC MOS 驱动器被分离来驱动多个负载，其中一个负载距离驱动器 1 英寸而另一个负载距离驱动器 3 英寸。典型的 PCB 布线长度的传播延迟约为 150ps。在这种情况下，信号从驱动器传输到接收器时，较短的路径可能有大约 150ps 的传播延迟。较长的路径可能具有大约 450ps 的传播延迟。

典型的 LVC MOS 接收器具有高输入阻抗，因此几乎所有的功率都从通过传输线从接收器反射回来，直到该传输线端接在驱动器为止。在信号完全通过较长路径传播之前，来自较短路径的信号可能会开始从负载反射回来。从更靠近驱动器的负载的角度来看，上升沿可以看到传播延迟（本例中为 450ps - 150ps = 300ps）之间的差值处出现下冲，并且较长的路径可以看到过冲。时钟信号的下降沿可能会产生相反的影响。接收器之间的不匹配越长，过冲和振铃可能就越严重。为了保持信号完整性并尽可能减小过度反射的影响，在使用 LVC MOS 驱动器驱动多个负载时，请将信号路径之间的传播延迟差保持在 100ps 以下。

以下各图显示了多个负载之间布线长度不匹配的仿真结果。

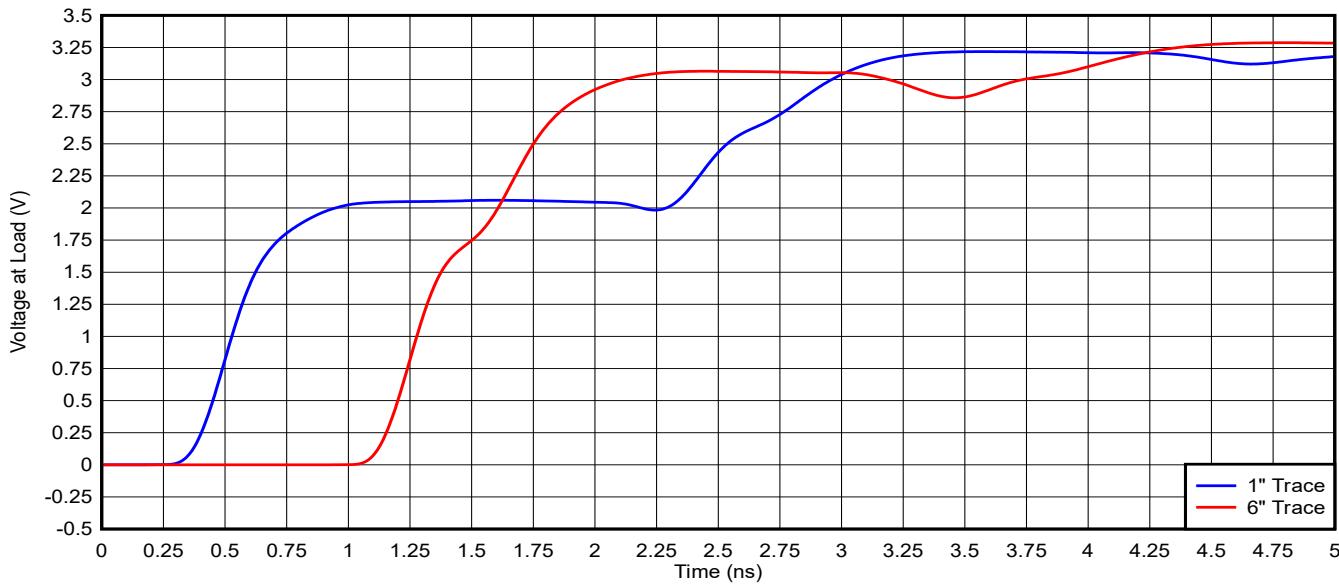

图 5-2 显示了星型线路拓扑， $R_t = 17 \Omega$ ，传播延迟 = 150ps/英寸的布线长度。

图 5-2. 布线长度不匹配：具有 1" 和 2" 布线的上升沿

图 5-3 显示了星型线路拓扑， $R_t = 17 \Omega$ ，传播延迟 = 150ps/英寸的布线长度。

图 5-3. 布线长度不匹配：具有 1" 和 3" 布线的上升沿

图 5-4 显示了星型线路拓扑， $R_t = 17 \Omega$ ，传播延迟 = 150ps/英寸的布线长度。

图 5-4. 布线长度不匹配：具有 1" 和 6" 布线的上升沿

在多个负载的长度均不匹配的情况下，结果可能是类似阶跃响应，在不同的时间间隔内有一系列反射，而不是干净的上升沿。

## 6 应用示例 : FPD-Link

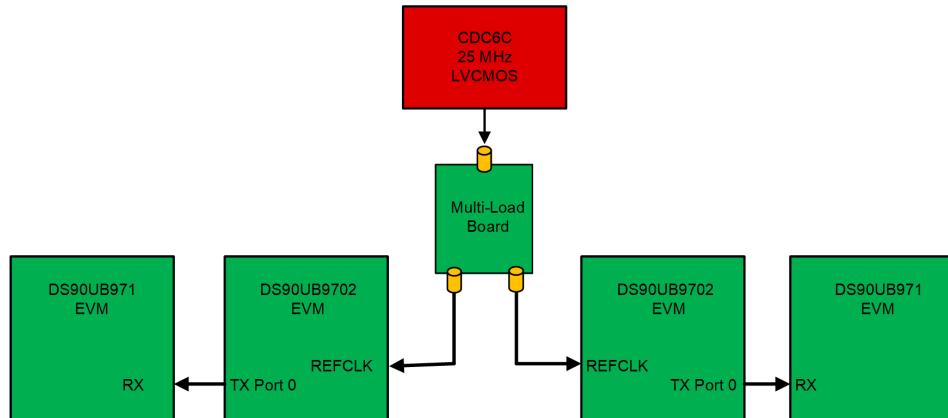

在大多数应用中，FPD-Link 器件需要使用外部 REFCLK，通常为 25MHz 或 27MHz LVCMOS。对于该实验，一个 LVCMOS 振荡器为两个 DS90UB971 串行器和 US90UB9702 解串器对生成了 REFCLK 信号。REFCLK 通过 CDC6C BAW 振荡器生成，并在多负载板上使用布线 3 扇出到两个 FPD-Link 串行器/解串器对（扇出到 2 个负载，2 英寸的布线长度，在振荡器附近拆分）。较小的测试板用于额外增加 2 英寸的布线长度，总共 4 英寸。在两个 DS90UB9702 EVM 上，SMA 转 2 引脚母接头电缆将多负载板与外部 REFCLK 接头连接了起来。

图 6-1. 为 2 个 FPD-Link 串行器/解串器对提供 REFCLK 的 CDC6C : 方框图

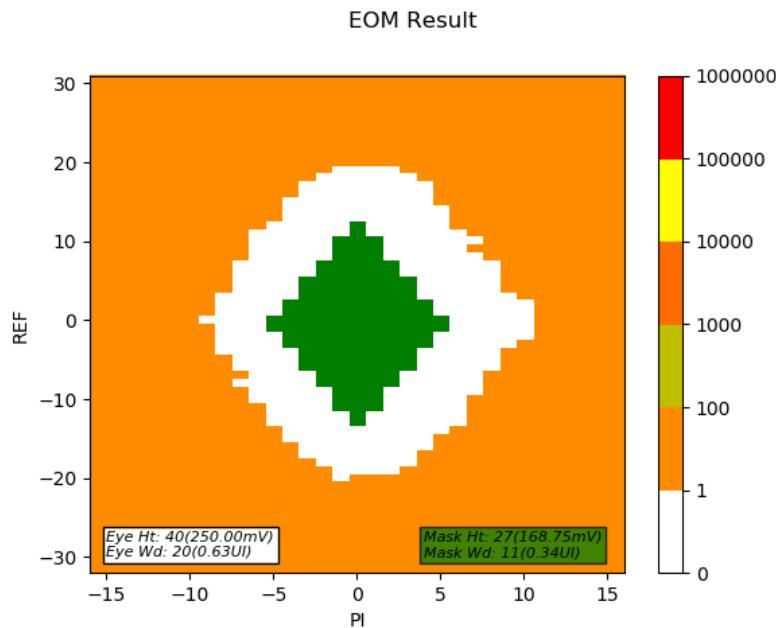

由于两个 FPD-Link 串行器/解串器对共享一个 REFCLK，因此建立链路不会出现任何错误。执行眼图张开度裕量 (EOM) 测试以确保每个对都生成稳定的链路。两个 DS90UB971/9702 对能够在一系列 EQ 设置中与共享的 REFCLK 信号同时保持链路。此测试可确认在某些应用中，这可以针对单个 LVCMOS 振荡器驱动多个负载。

图 6-2. FPD-Link 眼图张开度裕量 (EOM) 结果

## 7 总结

这些仿真结果和实验室测量结果显示，有一些因素决定了在系统中使用单个 LVC MOS 振荡器驱动多个负载是否可行。使用单个 LVC MOS 振荡器驱动多个负载始终会在某种程度上降低信号完整性。为了获得最佳性能，可以使用 [时钟缓冲器](#) 来限制需要直接由振荡器驱动的负载数量。

使用单个振荡器驱动多个负载的指导原则：

- 将负载数量限制为 2，以最大限度地减少因上升或下降时间缩短、信号反射过多和信号振幅减少造成的性能下降

- 如星型线路拓扑中所示，在分支到各个接收器之前，尽可能增加公共布线长度

- 限制接收器的总电容以缩短上升/下降时间

这些指导原则可作为在系统中驱动多个负载的基本原则。通过减少负载数量、缩短分支布线长度并减少总寄生和接收器电容，您可以最大限度减轻在系统中使用单个振荡器驱动多个负载所带来的负面影响。星型线路拓扑是最符合这种布线情况的模型。如果需要优先考虑实现绝对最佳性能，那么绝不能将布线分成多个负载，而是可以使用 [4 通道输出 LVC MOS 1.8V 缓冲器](#) 等时钟缓冲器来扇出时钟信号并驱动多个负载。

## 8 参考资料

- 德州仪器 (TI) , [LMK6x 低抖动、高性能 BAW 振荡器](#) 数据表。

- 德州仪器 (TI) , [CDC6Cx 低功耗 LVC MOS 输出 BAW 振荡器](#)，数据表。

- 德州仪器 (TI) , [LMK1C110x 1.8V、2.5V 和 3.3V LVC MOS 时钟缓冲器系列](#) 数据表。

## 9 修订历史记录

| Changes from Revision A (April 2025) to Revision B (May 2025) | Page |

|---------------------------------------------------------------|------|

| • 添加了负载之间的布线长度不匹配一节.....                                      | 12   |

| Changes from Revision * (August 2024) to Revision A (April 2025) | Page |

|------------------------------------------------------------------|------|

| • 更新了整个文档中的表格、图和交叉参考的编号格式.....                                   | 1    |

| • 添加了仿真设置部分.....                                                 | 3    |

| • 更新了单线路终端图像.....                                                | 4    |

| • 更新了星型线路终端图像.....                                               | 6    |

| • 更新了拆分线路终端图像.....                                               | 7    |

| • 更新了图像.....                                                     | 8    |

| • 添加了实验室测量设置部分.....                                              | 9    |

| • 添加了实验室测量结果以及与仿真数据的相关性部分.....                                   | 10   |

| • 添加了应用示例： <b>FPD-Link</b> 部分.....                               | 14   |

| • 向适用于驱动多个负载的指南和一般建议添加了更多详细信息.....                               | 15   |

| • 添加了 <b>CDC6Cx</b> 数据表参考.....                                   | 15   |

## 重要通知和免责声明

TI“按原样”提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任：(1) 针对您的应用选择合适的 TI 产品，(2) 设计、验证并测试您的应用，(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更，恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务，TI 对此概不负责。

TI 提供的产品受 [TI 的销售条款](#) 或 [ti.com](#) 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址 : Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

版权所有 © 2025 , 德州仪器 (TI) 公司