ZHCSDM5G March 2012 – December 2014 LMK00105

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史

- 5 Pin Configuration and Diagrams

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11器件和文档支持

- 12机械、封装和可订购信息

1 特性

- 5 个低电压互补金属氧化物半导体 (LVCMOS) 输出,频率范围为直流至 200MHz

- 通用输入

- 低电压正射极耦合逻辑 (LVPECL)

- 低压差分信令 (LVDS)

- 主机时钟信号电平 (HCSL)

- 短截线串联端接逻辑 (SSTL)

- LVCMOS 和低电压晶体管-晶体管逻辑电路 (LVTTL)

- 晶体振荡器接口

- 晶振输入频率:10 至 40MHz

- 输出偏斜:6ps

- 附加相位抖动

- 156.25MHz(12kHz 至 20MHz)时为 30fs

- 低传播延迟

- 由 3.3V 或 2.5V 内核电源电压供电运行

- 可调输出电源

- 每组均可选择 1.5V、1.8V、2.5V 和 3.3V

- 24 引脚超薄型四方扁平无引线 (WQFN) 封装封装 (4.0mm × 4.0mm ×

0.8mm)

2 应用

- 针对射频拉远单元 (RRU) 应用的 LO 基准分布

- 同步光网络 (SONET),以太网,光纤信道线路接口卡

- 光传输网络

- 千兆无源光网络 (GPON) 光线路终端 (OLT) / 光网络单元 (ONU)

- 服务器和存储局域网络互连

- 医疗成像

- 便携式测试和测量

- 高端 A/V

3 说明

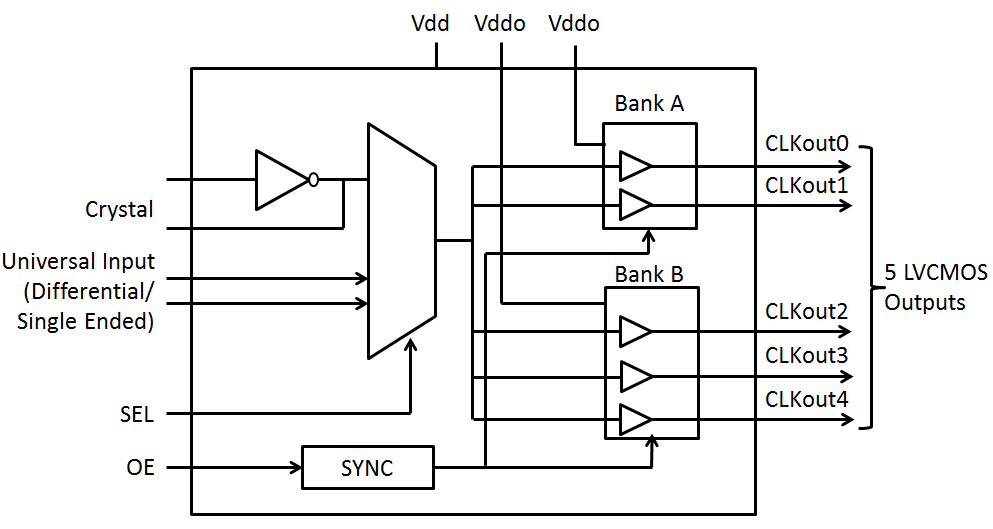

LMK00105 是一款高性能、低噪声 LVCMOS 扇出缓冲器,可通过差分、单端或晶振输入实现五路超低抖动时钟。 LMK00105 支持同步输出使能功能,可确保无毛刺脉冲运行。 这款缓冲器具有超低偏斜、低抖动和高电源抑制比 (PSRR) 等诸多优势,因此非常适合各类网络互连、电信、服务器和存储局域网络互连、RRU LO 基准分布、医疗和测试设备应用。

内核电压可设置为 2.5V 或 3.3V,而输出电压可设置为 1.5V、1.8V、2.5V 或 3.3V。通过引脚编程功能可轻松配置 LMK00105。

器件信息(1)

| 器件型号 | 封装 | 封装尺寸(标称值) |

|---|---|---|

| LMK00105 | WQFN (24) | 4.00mm x 4.00mm |

- 如需了解所有可用封装,请见数据表末尾的可订购产品附录。

功能方框图