# Performance of LVDS With Different Cables

Elliott Cole, P.E.

Mixed Signal Products

#### ABSTRACT

This application report focuses on cables for use with LVDS devices rather than printed-circuit board interconnections. After a brief introduction to LVDS, the signal quality of seven different cables is evaluated using eye pattern measurements and TI's LVDS evaluation modules (EVMs). Since data transmission cable covers a wide range of cost and performance, this paper provides guidance for cable selection, signaling rates, and transmission distance.

The effects of crosstalk and jitter are included to reflect real-world concerns in telecommunications switching equipment, LAN bridges and routers, printers, copiers, facsimile machines, and other equipment that processes data at high rates.

#### Contents

| 1 Introduction |                                                    |    |  |  |

|----------------|----------------------------------------------------|----|--|--|

| 2              | The Data Interchange Circuit                       | 3  |  |  |

|                | 2.1 Driver                                         |    |  |  |

|                | 2.2 Transmission Line                              |    |  |  |

|                | 2.3 Cable Selection                                | 4  |  |  |

|                | 2.4 TIA/EIA-568A                                   | 5  |  |  |

|                | 2.5 Cables Tested                                  | 6  |  |  |

|                | 2.6 Termination                                    | 7  |  |  |

|                | 2.7 Receiver                                       | 7  |  |  |

|                | 2.8 Measurements                                   | 7  |  |  |

| 3              | Test Setup                                         | 8  |  |  |

| •              | 3.1 The Evaluation Module (EVM)                    |    |  |  |

|                | 3.2 Stimulus Equipment                             |    |  |  |

|                | 3.3 Jitter Measurement                             |    |  |  |

| 4              | Results                                            | 10 |  |  |

| -              | 4.1 Receiver Input Jitter vs Signaling Rate        |    |  |  |

| 5              | Conclusions                                        | 14 |  |  |

|                | 5.1 Signaling Rate                                 |    |  |  |

|                | 5.2 Cable Length and Signaling Rate                |    |  |  |

|                | 5.3 Cable Length, Signaling Rate, and the Receiver | 15 |  |  |

| 6              | Acronyms and Glossary                              | 18 |  |  |

| 7              | References                                         | 19 |  |  |

| -              |                                                    |    |  |  |

# List of Figures

| Simplified Circuit Diagram of Transmitter  | . 4                                       |

|--------------------------------------------|-------------------------------------------|

| Permissible Attenuation on a CAT5 Cable    | . 6                                       |

| Test Setup Schematic                       | . 9                                       |

| Typical Eye Pattern                        | . 9                                       |

| Input Jitter vs Signaling Rate for Cable A | 10                                        |

| Input Jitter vs Signaling Rate for Cable B | 11                                        |

| Input Jitter vs Signaling Rate for Cable C | 11                                        |

| Input Jitter vs Signaling Rate for Cable D | 12                                        |

| Input Jitter vs Signaling Rate for Cable E | 12                                        |

|                                            |                                           |

| Input Jitter vs Signaling Rate for Cable G | 13                                        |

| Pinput Jitter vs Signaling Rate            | 15                                        |

| Jitter Increase Through a Receiver         | 16                                        |

| Actual vs Predicted Output Jitter          | 17                                        |

|                                            | Simplified Circuit Diagram of Transmitter |

# List of Tables

| 1 | Attenuation Constants                                    | . 6 |

|---|----------------------------------------------------------|-----|

| 2 | Signaling Rates (Mbps) vs Cable Length (m) for 5% Jitter | 14  |

# 1 Introduction

One of the most frequently asked questions about data transmission applications is, "How fast and how far?" The interconnection between a data line driver and receiver may be the most important factor in determining the answer, especially now that signaling rates are in the order of hundreds of megabits per second (Mbps). Texas Instruments' families of low-voltage differential signaling (LVDS) line circuits, such as the SN65LVDS31 quadruple line driver and SN65LVDS32 quadruple line receiver, enable signaling rates in excess of 400 Mbps, and using such TIA/EIA-644 standard devices may result in cable performance being the determining factor in the overall system performance.

In data transmission circuits, the output voltage transition time of a line driver is often the limiting factor in determining a maximum signaling rate. This is usually due to an output stage not being fast enough to provide a *decent* pulse, however it is also related to noise margin, crosstalk, and radiated and conducted emissions. Since many conventional line drivers have a single-ended output with a voltage swing of several volts, the signaling rate may be further constrained by an increase in power dissipation as signaling rates increase.

LVDS is a data transmission standard that utilizes a balanced interface and a low voltage swing to solve many of the problems associated with existing signaling technologies. Lower signal amplitudes reduce the power used by the line circuits and balanced signaling reduces noise coupling to allow higher signaling rates.

LVDS, as standardized in TIA/EIA-644, specifies a theoretical maximum signaling rate of 1.923 Gbps. In practice, the maximum signaling rate is determined by the quality of the transmission media between the line driver and receiver. Since a transmission line's length and characteristics determine the maximum usable signaling rate, this report looks at some of the dependencies and interactions between these cable characteristics and the signaling rate.

# 2 The Data Interchange Circuit

Each data interchange circuit contains four elements: line driver, transmission line, line termination, and line receiver. The following sections briefly describe the task of each of these components and what is used for the measurements of this report.

# 2.1 Driver

The task of a line driver is to convert the data signal from one electrical layer to another. In most cases, the signal is converted from a single-ended logic signal (such as TTL) to the appropriate level of amplitude and common-mode voltage required to drive a transmission line of the interface circuit. The driver function is defined such that it does not include any encoding or decoding functions.

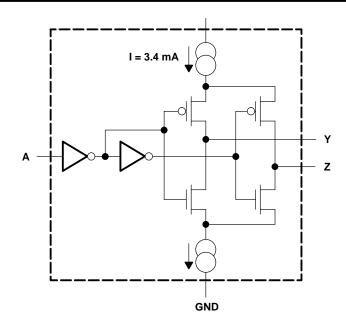

The driver used for this report is the LVDS evaluation module (EVM), equipped with the SN65LVDS31 quadruple line driver. The differential output delivers a typical current of 3.4 mA, which produces a differential voltage magnitude of 340 mV across a 100- $\Omega$  load. This is a current-mode driver as opposed to the more common voltage-mode driver. Figure 1 shows an equivalent schematic diagram of the driver circuit.

Figure 1. Simplified Circuit Diagram of Transmitter

# 2.2 Transmission Line

Since the output of the SN65LVDS31 driver changes state in about 500 ps, an interconnection to the receiver can be closely modeled as a time delay and a resistive load, the transmission line's characteristic impedance ( $Z_0$ ). This model is valid for transmission distances greater than a few centimeters.

TIA/EIA-644 LVDS specifies the use of  $90-\Omega$  to  $132-\Omega$  transmission lines (although other values may also be used in nonstandard applications). Beyond this basic model, the actual interconnection has other characteristics that ultimately limit the distance or signaling rate.

A variety of application and environment-specific cable types is readily available, each with advantages and disadvantages for a specific application. Therefore, the choice of cable needs to be subjectively evaluated for each new application.

The major concerns are:

- Signaling rate

- Cable length

- Single-ended or (balanced) differential signaling

- Point-to-point, multidrop or multipoint configuration

- Noise margin

- Flexibility

- Costs

# 2.3 Cable Selection

Depending on the specific application and environment, the following decisions need to be addressed:

- Unshielded or shielded (taped, braided or combination of both)?

- Round or flat?

- Coaxial cable, multiconductor, or twisted pair (TP)?

The need for shielding depends mainly on the noise environment. For long transmission lines, a braided or served shield is recommended to ensure good isolation between the signal lines and the environment. However, this type of shielding is permeable at high frequencies, and double-shielded cables that are both taped and braided typically perform better.

Multiconductor cables are cheaper and easier to handle than twisted-pair or coaxial cables, especially in terms of termination. While twisted pair is less expensive and more flexible than coax, it generally does not provide the noise immunity and bandwidth available with coaxial cables. Nevertheless differential data transmission requires a balanced pair of conductors.

The answer to the *round or flat-cable* question is usually determined by the environment. For internal applications with low noise, a flat untwisted cable is usually adequate. However, in noisy environments, shielding is often required and industry standards call for shielded twisted pair (STP) cable. Also, in recent years, shielded flat cable has become available.

For balanced (or differential) data transmission, such as LVDS, twisted-pair cable is recommended since it provides two identical conductors to transmit the signal and its complement. Any distortion effects both conductors equally, therefore the differential signal does not change.

# 2.4 TIA/EIA-568A

Since cable quality contributes strongly to signal quality, cable quality should be evaluated in detail. One standard, TIA/EIA-568-A Commercial Building Telecommunications Cabling Standard defines the transmission requirements for commercial building telecommunication wiring. It classifies cabling into different categories based upon attenuation and crosstalk losses over frequency. Twisted-pair is classified in different categories, abbreviated by CATX. CAT3 is characterized up to 16 MHz, CAT4 to a maximum of 20 MHz, and CAT5 for 100 MHz and above.

A new revision of this standard under development adds categories to address the cable requirements of high-speed data communications. The higher performing cables of this STP-specification are called CAT7, while the unshielded twisted-pair (UTP) cable (with lower performance) are classified as CAT6. So far, there is *no official* CAT designation on these cables; however, some manufacturers have announced availability of products capable of supporting signaling rates in the gigabit per second (Gbps) region. Presently some of these manufacturers are using terms such as *Enhanced* CAT5 or CAT5+. One of the cables investigated in this report will likely be classified as CAT7 (based upon the requirements presently contained in the proposed revision to the standard).

Although the tests for this writing employ a  $100-\Omega$  unshielded twisted-pair (UTP) cable, the standard does not specify a particular type of shielding, as long as the requirements given for a particular class of UTP cable are met. The following parameters are for CAT5 cable. Cat4 is not widely used and is therefore not covered in this report. Values in [brackets] apply to CAT3 where they differ from CAT5:

- The dc resistance of the cable should not exceed 9.38  $\Omega$ /100 m.

- The mutual capacitance is limited to a maximum of 5.6 nF/100 m [6.6 nF/100 m]. The capacitance with respect to ground must not exceed 330 pF over the frequency range of 1 kHz to the maximum specified frequency.

- The line impedance must be 100  $\Omega \pm 15\%$  for the bandwidth of 1 MHz up to the maximum frequency applied.

- The propagation delay time on the line should not exceed 5.7 ns/m (at 10 MHz). The skew (difference between two lines of a pair) is not specified, even though it has a significant impact on signal quality at high signaling rates.

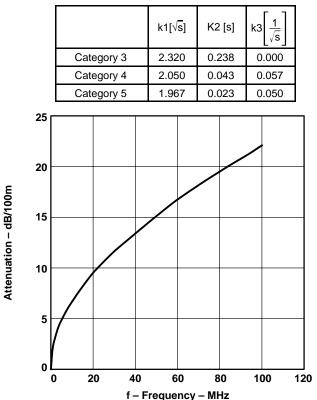

- The permissible attenuation is calculated with the formula:

Attentuation(f) =

$$k1\sqrt{f} + k2 \times 7 + \frac{k3}{\sqrt{f}}$$

where f is the applied frequency (1)

The constants that should be applied for 0.772 MHz up to the highest frequency referenced are listed in Table 1 and shown graphically in Figure 2 for CAT5 cables.

#### Table 1. Attenuation Constants

Figure 2. Permissible Attenuation on a CAT5 Cable

#### 2.5 Cables Tested

Seven different cables are tested using the LVDS EVM. Each EVM contains one SN65LVDS31 quad line driver and one SN65LVDS32 quad line receiver, and each of the cables listed below is tested as the interconnection media between the LVDS driver and receiver.

It is important to note that cable manufacturers offer a wide array of products to support different requirements, and that performance of a particular cable in this application should not be taken as an indication of how the cable would perform in the application the manufacturer intended. These cables were developed prior to the approval and release of the TIA/EIA-644 LVDS specification, and therefore could not have been optimized with that application in mind.

- Cable A: CAT 3, specified up to 16 MHz, no shield, outside conductor diameter  $\oslash$  0,52 mm

- Cable B: CAT 5, specified up to 100 MHz, no shield,  $\emptyset$  0,52 mm

- Cable C: CAT 5, specified up to 100 MHz, taped over all shield,  $\varnothing$  0,52 mm

- Cable D: CAT 5 (exceeding CAT 5), specified up to 300 MHz, braided over all shield plus taped individual shield for any pair, Ø 0,64 mm (AWG22)

- Cable E: CAT 5 (exceeding CAT 5), specified up to 350 MHz, Ø 0,64 mm (AWG22), no shield

- Cable F: CAT 5 (exceeding CAT 5), specified up to 350 MHz, self-shielded, Ø 0,64 mm (AWG22)

- Cable G: Twin-axial cable, specified up 1 GHz, (AWG 26)

At the time of this writing, the price for an enhanced CAT 5 cable is around two dollars per meter, and the CAT5 STP cable costs are about half of that. UTP cables are considerably less expensive.

The TIA/EIA-644 standard deals with the electrical characteristics of the data interchange only. The mechanical specifications, bus structure, protocol, and timing are left to the referencing standard.

# 2.6 Termination

Termination is used at the end of a transmission line to minimize reflections back into the line, and when using LVDS with its high switching speed, termination is mandatory. Under steady state conditions, the LVDS *current-mode* driver requires termination resistance to develop a differential voltage across the signal pair. High frequency components may reflect back if the characteristic impedance of the transmission line is not matched.

The allowable reflection for a system depends upon its design and ultimate noise margin, but generally matching the nominal characteristic impedance of the cable to  $\pm 10\%$  of the termination resistor value is sufficient. For this report, a 100  $\Omega$  differential termination across the inputs of the LVDS receiver is used.

# 2.7 Receiver

The receiver's purpose is to detect the signal on the transmission line and translate it back to standard logic levels. In this case, the LVDS receiver detects the difference voltage between the lines of the signal pair and determines whether it is a high or low logic level. The polarity of this voltage difference determines whether the logical state is high or low.

For the measurements described in this report, the Texas Instruments LVDS EVM containing one SN65LVDS32 receiver is used. Its maximum differential threshold voltage of  $\pm$ 100 mV and other characteristics comply with the TIA/EIA-644 Standard on the Electrical Characteristics of LVDS Interface Circuits. The LVTTL compatible output levels provide signals applicable for a wide range of down-stream hardware.

#### 2.8 Measurements

Measurements are performed on different cable types and lengths while varying the signaling rate. For each measurement, a pseudo-random binary signal (PRBS) with a non-return-to-zero (NRZ) format is used. Also, the experiments are conducted in a standard laboratory environment at room temperature, where a considerable amount of electronic equipment is in operation.

PRBS patterns are applied to the input of the transmitter; then eye patterns are measured at the input of the receiver. Tests are performed on cables A through F with lengths of 1, 5, and 10 meters (only a 10 meter length is available for the testing of cable G). Since all cables tested contained four twisted pairs, crosstalk is created by transmitting through two of the twisted pairs in one direction while the remaining two pairs are driven in the opposite direction. All of the data listed is measured with the four transmitters in operation.

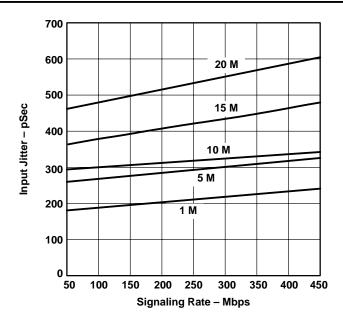

Also, since system level jitter is suspected to be a function of both signaling rate and cable length, additional tests are performed with UTP CAT5 cable lengths up to 20 meters while varying the signaling rate from 50 Mbps to 450 Mbps in 50-Mbps increments.

# 3 Test Setup

# 3.1 The Evaluation Module (EVM)

The LVDS evaluation module (EVM) contains one SN65LVDS31 quad line driver and one SN65LVDS32 quad line receiver. All four channels of the line driver are utilized to simulate crosstalk by transmitting in opposite directions and staggering the PRBS input to each driver channel by 0.5 ns.

The EVM is modified by installing solder posts (Berg Electronics Series 66951) at each driver channel output (8 posts) and each receiver channel input (8 posts). These posts are soldered directly to the EVM's connector pads so that contact can be made by the insertion of a wire conductor directly into the solder post to facilitate changing cables. Care should be taken in the preparation of each cable to avoid any propagation delay caused by a difference in length of the twisted pair.

The EVM is CE-certified and available via distribution, and detailed information on the EVM is available on the TI Home page: *Low Voltage Differential Signaling (LVDS) Evaluation Module (EVM) for Quad Drivers and Receivers* User's Guide, literature number SLLU016.

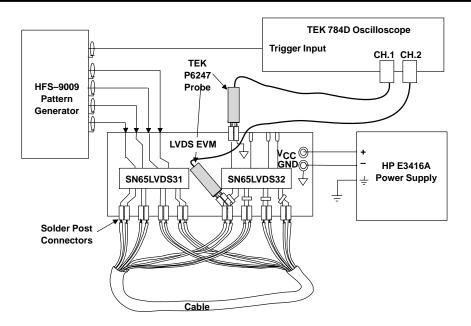

# 3.2 Stimulus Equipment

A HP E3615A dc power supply provides the required Vcc of 3.3 Vdc for both the LVDS31 quad line driver and the LVDS32 quad line receiver. A Tektronix HFS9009 signal generator is then used to generate NRZ data into the four channels of the LVDS32 line driver. This HFS9009 is capable of generating pseudo-random binary sequence (PRBS) data pattern rates up to 630 Mbps, and the data pattern applied repeats the PRBS sequence after 2<sup>16</sup>-1 bits (or 64K bits).

At high data rates, the influence of equipment used to measure a signal of concern should be minimized, therefore probe heads should behave like a low-capacitance, high-impedance load with high bandwidth. For this test, a Tektronix 784D oscilloscope with a Tektronix P6247 differential probe is used—both the scope and probe have a bandwidth of 1 GHz and a capacitive load of less than 1 pF. For signals in the range of 400 Mbps and above, an even higher bandwidth is recommended (as a rule of thumb, the fifth harmonic, i.e., 2 GHz, should be detected), but at this time, no faster differential probe head is available. The basic test setup is shown in Figure 3.

Figure 3. Test Setup Schematic

### 3.3 Jitter Measurement

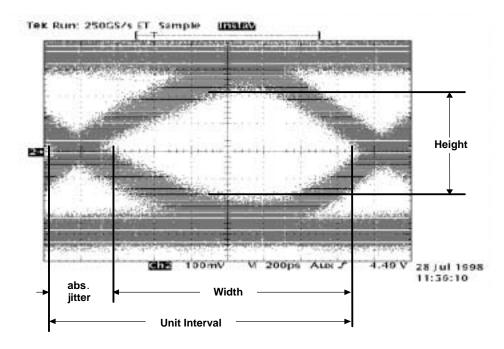

The eye pattern is a useful tool to measure the overall signal quality at the end of a transmission line. It includes all of the effects of systemic and random distortion, and shows the time during which the signal may be considered valid. A typical eye pattern is illustrated in Figure 4 with the significant attributes identified.

Figure 4. Typical Eye Pattern

Several characteristics of the eye pattern indicate the signal quality of the transmission circuit. The height or *opening* of the eye above or below the receiver threshold level at the sampling instant is the noise margin of the system. The spread of the transitions across the receiver thresholds measures the peak-to-peak jitter of the data signal. The signal rise and fall times can be measured relative to the 0% and 100% levels provided by the long series of low and high levels.

Jitter is the time frame during which the logic state transition of a signal occurs. The jitter may be given either as an absolute number or as a percentage with reference to the unit interval (UI). This UI or *bit length* equals the reciprocal value of the signaling rate, and the time during which a logic state is valid is just the UI minus the jitter. Percent jitter (the jitter time divided by the UI times I00) is more commonly used and it represents the portion of UI during which a logic state should be considered indeterminate.

# 4 Results

# 4.1 Receiver Input Jitter vs Signaling Rate

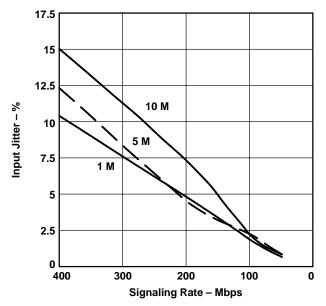

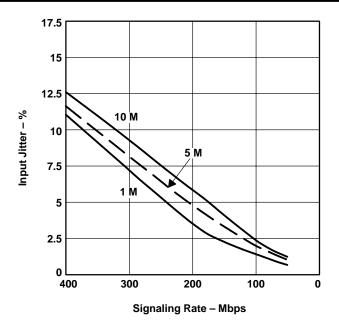

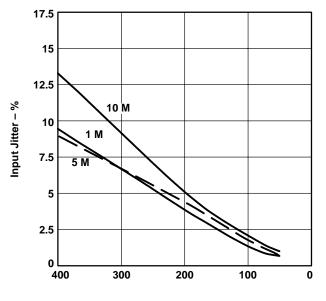

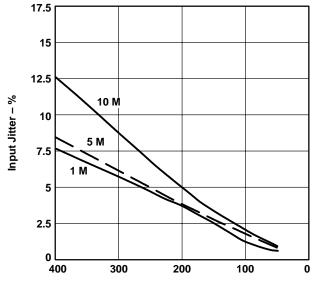

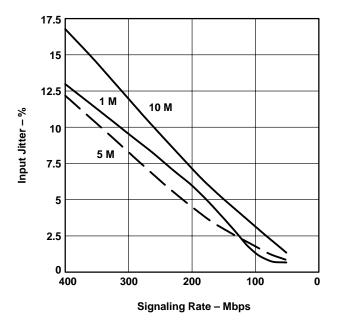

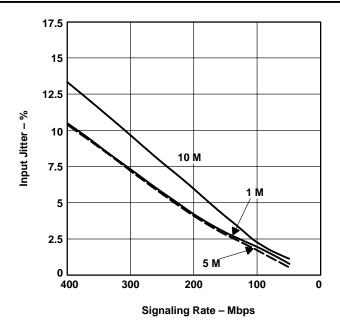

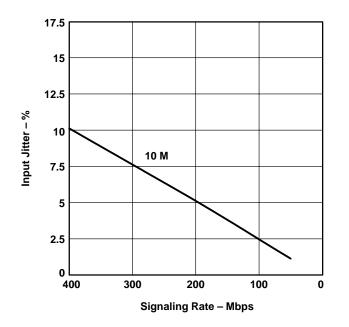

Jitter at the input of the receiver is measured at the zero voltage differential, then calculated with respect to the duration of the unit interval. The results are expressed as a percentage of the unit in Figures 5 through 11.

Figure 5. Input Jitter vs Signaling Rate for Cable A

Figure 6. Input Jitter vs Signaling Rate for Cable B

Signaling Rate – Mbps

Figure 7. Input Jitter vs Signaling Rate for Cable C

Signaling Rate – Mbps

Figure 8. Input Jitter vs Signaling Rate for Cable D

Figure 9. Input Jitter vs Signaling Rate for Cable E

Figure 10. Input Jitter vs Signaling Rate for Cable F

Figure 11. Input Jitter vs Signaling Rate for Cable G

# 5 Conclusions

# 5.1 Signaling Rate

As one would expect, jitter (as a percent of UI) presented to the input of a receiver increased linearly with the signaling rate in all measured cables. The rate of that increase is a relative measure of the high-frequency characteristics of the cable.

The results are summarized in Table 2, which displays the signaling rates that resulted in a jitter of 5% of UI present at the input to the LVDS32 receiver. System tolerance to jitter is highly application dependent, and typically, maximum allowable jitter tolerances range from 5% to 20% depending upon actual system requirements (TIA/EIA-644). Note that this data was collected with signals present on the other two twisted wire pairs in the cable.

| CABLE     |     |     |     |     |     |     |      |

|-----------|-----|-----|-----|-----|-----|-----|------|

| LENGTH, m | Α   | в   | С   | D   | Е   | F   | G    |

| 1         | 240 | 200 | 240 | 270 | 180 | 230 | #N/A |

| 5         | 205 | 210 | 230 | 250 | 215 | 230 | #N/A |

| 10        | 180 | 150 | 195 | 200 | 145 | 180 | 195  |

Table 2. Signaling Rates (Mbps) vs Cable Length (m) for 5% Jitter

Test results show that as expected, slightly better performance was achieved with the shielded cables C and D than the unshielded Cables E and F. It is difficult to identify the noise coupling source as inter-system or intra-system, but if electromagnetic noise is a concern shielding should be used. Clearly cable D provided the highest potential signaling rate at each measured length even though its specifications claim characterization up to only 300 MHz compared to 350 MHz for the others.

While the effects of crosstalk were included in all measurements, the results do not clearly demonstrate that the direction of data flow on adjacent lines had any significant impact on jitter magnitude. However, transmitting data through a single channel and signal pair may reduce the absolute jitter by up to 10%.

Note the similarity in signaling rates for the 1-m and 5-m lengths of cables B, E, and F, and that for cables B and E, the 5-m length actually exceeds the signaling rate for 1 m. Near-end crosstalk effects at the 1-m length may explain this counterintuitive result.

# 5.2 Cable Length and Signaling Rate

Additional measurements are taken on a CAT5 UTP cable similar to Cable B in order to collect more data for the analysis of the near-linear relationship of these two parameters.

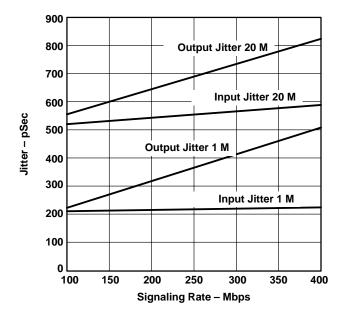

Figure 12. Input Jitter vs Signaling Rate

As expected, jitter increases with longer cables. Note on the plot of Figure 12 that although each length of cable provides a near-linear jitter response over the entire range of signaling rates, each slope increases slightly as the cable length increases. The input jitter, even at shorter cable lengths, may have a significant impact on system performance. For example, the input jitter measured on the 1m cable at 400 Mbps is 225 ps, which already represents 5% jitter at 220 Mbps and does not yet include other jitter contributors such as the receiver.

# 5.3 Cable Length, Signaling Rate, and the Receiver

The receiver also adds jitter to the system as seen in Figure 13. The plot displays two important factors: first, jitter increases with cable length, and second, jitter introduced by the receiver is a near-linear function of signaling rate (approximately 1 ps per Mbps).

Figure 13. Jitter Increase Through a Receiver

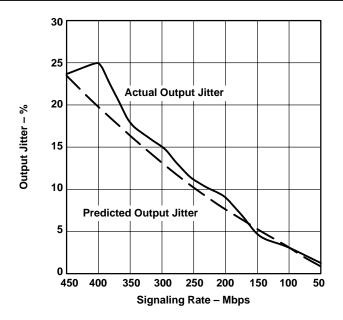

An approximate equation is developed from the data gathered for Figures 12 and 13 in which system jitter (cable plus receiver) can be estimated closely as a function of both cable length and signaling rate. This equation is in the slope/intercept form of y = ax + b times a scaled multiple developed from the ratios of jitter magnitude, cable length, and signaling rate for the high and low data points. This quantity is then normalized by the divisor. This equation approximates *percent* output jitter through an LVDS32 receiver, given the cable length (m) and signaling rate (Mbps), and is valid for cable lengths from 5 m to 20 m and signaling rates of 100 Mbps up to 400 Mbps.

$$\frac{\left[\left[1 + \left[\frac{0.0023x(S.R.)}{1 + \frac{(C.L. - 1)}{7.63}}\right]\right] \times \left[(200 + (15 \times C.L.)) \times S.R\right]\right]}{10,000} = \% \text{ Jitter}$$

(2)

Where S.R. is the signaling rate in Mbps and C.L. is cable length in meters.

The equation is a straight line approximation, and a plot of the actual jitter performance versus the predicted jitter performance with a 5 meter cable (using Equation 1) is shown in Figure 14.

Figure 14. Actual vs Predicted Output Jitter

This data is based upon the CAT5 cables tested, and the reader should be advised that a marginal cable which minimally meets the requirements of CAT5 may yield actual performance less than the results predicted here using Equation 2.

# 6 Acronyms and Glossary

| ANSI               | American National Standard Institute                      |

|--------------------|-----------------------------------------------------------|

| Attenuation        | Decrease of magnitude, usually expressed in dB            |

| AWG                | American wire gauge, diameter of the conductor,           |

|                    | increasing with decreasing AWG, AWG24 equals              |

|                    | 0.52 mm, AWG22 equals 0.64 mm                             |

| BERT               | Bit error rate tester                                     |

| CAT                | Category, here used as a classification for cable quality |

| EIA                | Electronic Industries Association                         |

| EMI                | Electromagnetic interference, susceptibility to and       |

|                    | emission of electromagnetic distortions                   |

| LVDS               | Low voltage differential signaling, new transmission      |

|                    | Standard for balanced interfacing with levels of          |

|                    | approximately 300 mV                                      |

| Mutual capacitance | Capacitance between the two conductors of one             |

|                    | transmission pair                                         |

| NRZ                | Nonreturn to zero, signaling mode, containing a dc        |

|                    | component                                                 |

| STP                | Shielded twisted pair cable                               |

| TIA                | Telecommunications Industry Association                   |

| TP                 | Twisted pair cable                                        |

| UI                 | Unit interval or bit duration, bit length                 |

| UTP                | Unshielded twisted pair cable                             |

| SRL                | Structural return loss                                    |

| NEXT               | Near end crosstalk                                        |

# 7 References

- 1. Data sheet SN55LVDS31, SN65LVDS31, SN65LVDS3487, SN65LVDS9638 (Literature Number SLLS261)

- 2. Data sheet High-Speed Differential Line Receiver (Literature Number SLLS262)

- 3. Design note Low Voltage Differential Signaling (LVDS) Design Notes (Literature Number SLLA014)

- 4. Application report *Printed Circuit Board Layout for Improved Electromagnetic Compatibility* (Literature Number SDZAE06)

- 5. Application report What a Designer Should Know (Literature Number SDZAE03)

- 6. Seminar manual Data Transmission Design Seminar (Literature Number SLLDE01)

- 7. Seminar manual Digital Design Seminar (Literature Number SDYDE01)

- 8. Seminar manual *Linear Design Seminar* (Literature Number SLYDE05)

- 9. Paper Communicate, Issue June 1998

- 10. LVDS Standard (TIA/EIA 644)

- 11. Commercial Building Telecommunications Cabling Standard (ANSI/TIA/EIA-568-A)

- 12. DVB-TM Ad hoc Group Physical Interfaces DVB-PI-232 Revised TM1449 Rev 2 Interfaces for CATV/SMATV Headends and Similar Professional Equipment

- 13. IEEE 1596.3-1995 Draft Standard for Low-Voltage Differential Signals (LVDS) for Scalable Coherent Interfaces (SCI) Draft 1.3

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated