# NanoStar <sup>™</sup> & NanoFree <sup>™</sup> 300µm Solder Bump Wafer Chip-Scale Package Application

Jim Rosson

High Performance Analog—MAKE Packaging

#### ABSTRACT

The NanoStar<sup>™</sup> Wafer Chip-Scale Package (WCSP) is a family of bare die packages developed for applications that require the smallest possible package. WCSP provides electrical interconnection via solder spheres attached to the die and is aligned with JEDEC package standard MO–211[1]. NanoStar, with advanced materials engineering technology, has demonstrated excellent board level reliability that allows it to be used without the need for underfill adhesives, unlike conventional solder-bumped Flip Chip devices. This advanced design allows standard, low-cost surface-mount technology (SMT) assembly processes to be used successfully. This application guide provides the necessary design and reliability information to apply the NanoStar 300µm solder bump packages.

#### Contents

| 1   | Introduction                                                                  | . 3 |

|-----|-------------------------------------------------------------------------------|-----|

|     | 1.1 Package Offerings and Nomenclature                                        | . 4 |

| 2   | Physical Description                                                          | . 5 |

|     | 2.1 Package Characteristics                                                   |     |

|     | 2.2 NanoStar Package Dimensions                                               |     |

|     | <ul><li>2.3 Thermal Performance</li><li>2.4 Board Level Reliability</li></ul> |     |

| •   | -                                                                             |     |

| 3   | Printed Circuit Board Assembly         3.1 PCB Design Guidelines              |     |

|     | 3.2 PCB Land Pattern Recommendations                                          |     |

|     | 3.3 Solder Paste Stencil Design                                               |     |

|     | 3.4 Component Placement                                                       | 15  |

|     | 3.5 Reflow                                                                    |     |

| 4   | Tape and Reel Information                                                     | 17  |

|     | 4.1 Material Specifications                                                   | 17  |

| 5   | Symbolization                                                                 | 19  |

| 6   | Features and Benefits                                                         | 20  |

| 7   | Conclusion                                                                    | 21  |

| Ack | nowledgments                                                                  | 21  |

|     | erences                                                                       |     |

|     |                                                                               |     |

Trademarks are the property of their respective owners.

### List of Figures

| Figure 1. NanoStar™WCSP, SOT–23, & SC–70 Size Comparison                  | 3  |

|---------------------------------------------------------------------------|----|

| Figure 2. NanoStar WCSP                                                   | 5  |

| Figure 3. Direct Bump WCSP Construction Cross-Section                     | 5  |

| Figure 4. RDL WCSP Construction Cross-Section                             | 6  |

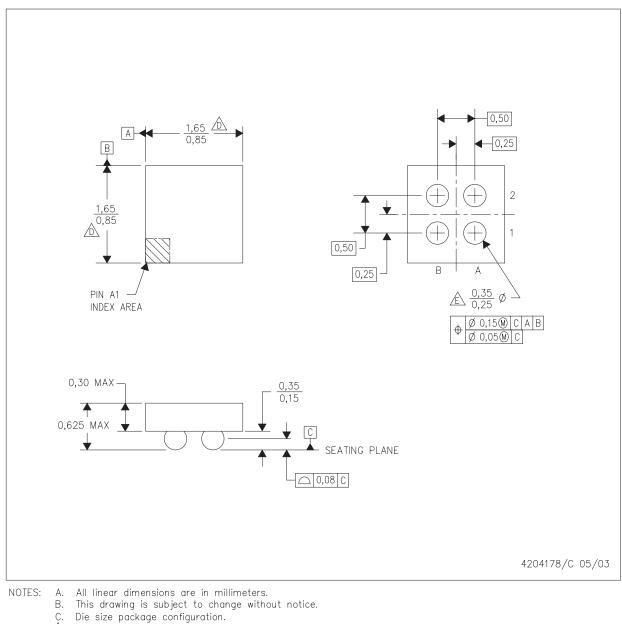

| Figure 5. YEB Package Dimensions                                          | 7  |

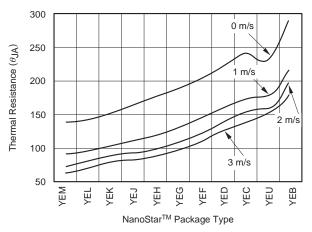

| Figure 6. JEDEC 1S0P Thermal Performance Data Graph                       | 8  |

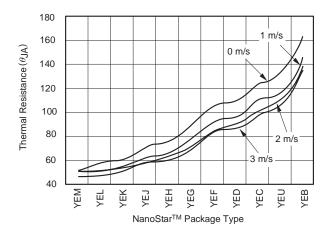

| Figure 7. JEDEC 2S2P Thermal Performance Data Graph                       | 8  |

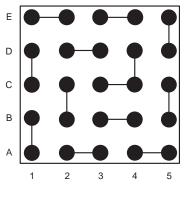

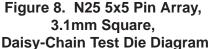

| Figure 8. N25 5x5 Pin Array, 3.1mm Square, Daisy-Chain Test Die Diagram   | 11 |

| Figure 9. N12 3x4 Pin Array, 2.14mm x 1.5mm, Daisy-Chain Test Die Diagram | 11 |

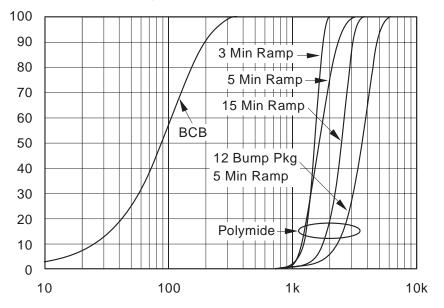

| Figure 10. 12-Site Thermal Cycle Test BLR Test Board                      | 11 |

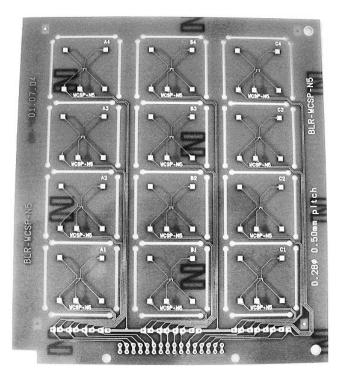

| Figure 11. N25 TCT Weibull Comparison of Ramp Rates and Materials         | 12 |

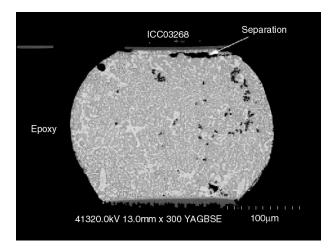

| Figure 12. Typical Tin-Lead BLR Solder Fatigue Crack                      | 13 |

| Figure 13. Enlargement of Crack Area in Figure 12                         | 13 |

| Figure 14. Typical Lead-Free BLR Solder Fatigue Crack                     | 13 |

| Figure 15. Enlargement of Crack Area in Figure 14                         | 13 |

| Figure 16. Example of 5x5 Array Balanced Routing Pattern                  | 14 |

| Figure 17. Recommended Solder Land Pattern Outline                        | 15 |

| Figure 18. Recommended Reflow Profiles                                    | 16 |

| Figure 19. Pocket Tape Dimensions                                         | 17 |

| Figure 20. Pocket Tape Dimensions                                         | 18 |

| Figure 21. Carrier-Tape Cavity Quadrant Location for Pin 1, per EIA–481B  | 19 |

#### List of Tables

| Table 1. | NanoStar $^{\scriptscriptstyle \rm M}$ & NanoFree $^{\scriptscriptstyle \rm M}$ 300 $\mu m$ Solder Bump Package Family Summary $\ldots\ldots\ldots$ | . 4 |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2. | Simulated Thermal Resistance Data                                                                                                                   | 9   |

| Table 3. | Board-Level Reliability Test Matrix                                                                                                                 | 10  |

| Table 4. | NanoStar Board Level Reliability Summary                                                                                                            | 12  |

| Table 5. | Recommended PCB Solder Land Pattern                                                                                                                 | 14  |

| Table 6. | Recommended Solder Stencil Pattern                                                                                                                  | 15  |

| Table 7. | Recommended Critical Reflow Parameters                                                                                                              | 17  |

| Table 8. | Common Tape Dimensions by Designator                                                                                                                | 18  |

| Table 9. | Reel Specifications                                                                                                                                 | 18  |

| Table 10 | . Device-Marking Guidelines                                                                                                                         | 19  |

## 1 Introduction

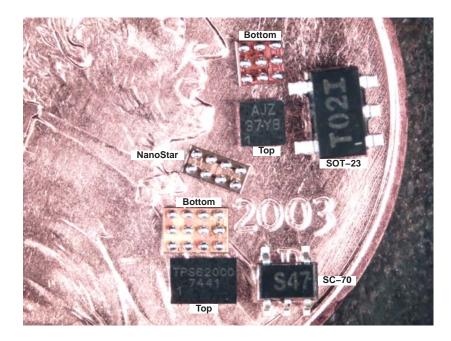

In today's mobile environment, there seems to be an insatiable market demand for the smallest and lightest possible electronic products with high reliability. Electronics manufacturers are designing smaller and smaller products with each generation and release. Many different types of packages have been developed to meet this need. Popular package sizes such as MSOP, SOT–23, SC–70, and QFN outlines are quite large in comparison to a die size or wafer-level chip-scale package. (See Figure 1.) There are several names for die size packages, including Flip Chip (FC), Wafer-Level Chip Scale Package (WLCSP), and Wafer Scale Package (WSP). Regardless of the package name, however, the benefits to a die size package are clear: the smallest possible form factor for an integrated circuit silicon die is the die itself.

TI utilizes new advanced polymer technology materials to enhance the board-level reliability of the NanoStar <sup>™</sup> 300µm solder ball packages. Many suppliers of WCSP packages use relatively brittle re-passivation polymeric materials. While these brittle materials work well for some applications, they have been shown to have poorer performance for 300µm solder sphere-bumped devices.[2] As a result of the new polymer technology available in the NanoStar package, TI customers do not have to experience premature device or reliability failures caused by brittle repassivation and often seen in competitive parts.

Figure 1. NanoStar<sup>™</sup> WCSP, SOT-23, & SC-70 Size Comparison

There are many challenges in interconnecting the micron-level world of silicon to enable bare die use in the millimeter-based world of SMT assembly. The proper system design for a die size package application is critical. NanoStar WCSP has been developed in 4–36 pin packages to enable high performance products to be as small as possible. A summary of the available packages is provided in Section 1.1. This package size not only enables smaller products, but also provides improved electrical performance. The performance increase is a direct result of shorter interconnections and, consequently, reduced parasitic losses due to interconnect length.

NanoStar WCSP adds other visible features, as well. All NanoStar devices are laser-marked to provide device identification and production lot tracking. Most analog NanoStar devices also have a protective backside surface coating to improve performance. This opaque coating reduces the parametric shifts that can occur due to the light sensitivity of IC structures. The coating allows a WCSP to provide the same level of consistent performance obtained from a molded package device.

This application note provides the necessary information to apply NanoStar technology with maximum success. The enclosed mechanical, electrical, and thermal package information, in addition to printed circuit board (PCB) design recommendations and reliability data, are the culmination of another enabling technology developed for Texas Instruments' customers.

#### 1.1 Package Offerings and Nomenclature

Table 1 shows the initial NanoStar WCSP package family lineup. As customer demand increases and more devices use the TI WCSP, this list is expected to grow. Please visit the TI web site for the latest list of products that use the NanoStar package family.

While the NanoStar name covers this entire WCSP family, TI also uses the NanoFree<sup>™</sup> term to differentiate devices that are available in lead-free solder alloys. For ease of reading, this document applies to both versions, and will typically use only the NanoStar name. Where differences are noted for lead-free packages, the NanoFree name will be specifically inserted.

| Package Designator <sup>(2)</sup> | Minimum "D" | Maximum "D" | Minimum "E" | Maximum "E" | Array Pinout |

|-----------------------------------|-------------|-------------|-------------|-------------|--------------|

| YEB, YZB                          | 0.85        | 1.65        | 0.85        | 1.65        | 4            |

| YEC, YZC                          | 1.35        | 2.15        | 0.85        | 1.65        | 6            |

| YED, YZD                          | 1.85        | 2.65        | 0.85        | 1.65        | 8            |

| YEF, YZF                          | 1.35        | 2.15        | 1.35        | 2.15        | 9            |

| YEG, YZG                          | 1.85        | 2.65        | 1.35        | 2.15        | 12           |

| YEH, YZH                          | 1.85        | 2.65        | 1.85        | 2.65        | 16           |

| YEJ, YZJ                          | 2.35        | 3.15        | 1.85        | 2.65        | 20           |

| YEK, YZK                          | 2.35        | 3.15        | 2.35        | 3.15        | 25           |

| YEL, YZL                          | 2.35        | 3.65        | 2.35        | 3.15        | 30           |

| YEM, YZM                          | 2.85        | 3.65        | 2.85        | 3.65        | 36           |

| YEU, YZU <sup>(3)</sup>           | 0.95        | 1.45        | 1.25        | 1.75        | 5            |

Table 1. NanoStar<sup>™</sup> & NanoFree<sup>™</sup> 300µm Solder Bump Package Family Summary<sup>(1)</sup>

NOTE 1: Package availability varies based on currently released products. Some of the above packages may not be available. Please reference the TI web site (www.ti.com) for released packages.

NOTE 2: A Z designator indicates NanoFree devices.

NOTE 3: Staggered array device.

The NanoStar WCSP packages in this report are referred to as simply NanoStar or WCSP packages. The NanoStar 300µm package family currently encompasses the three-letter TI package designators YEB, YEC, YED, YEF, YEG, YEH, YEJ, YEK, YEL, YEM and YEU for tin-lead solder bumped devices. NanoFree<sup>™</sup> Lead-Free solder bumped devices will use the package designators YZB, YZC, YZD, YZF, YZG, YZH, YZJ, YZK, YZL, YZM and YZU. The lead-free WCSP packages are the exact same dimensions as the lead-containing counterparts.

## 2 Physical Description

#### 2.1 Package Characteristics

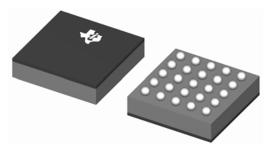

The NanoStar package family is a Die Size BGA as identified by the JEDEC standards organization [3]. Simplistically, the package is the silicon die with solder interconnects located on the active surface, and identification marking on the die backside. (See Figure 2.) These solder interconnects are placed on the PCB through conventional SMT processes to form a working circuit. TI has developed two different construction technologies to enable broad use of the WCSP in a variety of applications. These two approaches are called *Direct Bump* (or *Bump-On-Pad* [BOP]) and *Re-Distribution Layer* (RDL) technology.

Figure 2. NanoStar WCSP

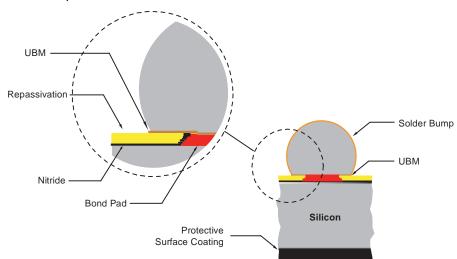

The TI Direct Bump technology is used on devices designed specifically to use WCSP. The solder bump is placed directly on the device bond pad that is normally reserved for the wire bonding process in conventional packaging. A cross-sectional view of direct bump construction is given in Figure 3. The construction consists of:

- A protective polymer re-passivation layer (to cover the delicate silicon surface)

- Under-bump metal (UBM) contact

- 300μm solder sphere

Figure 3. Direct Bump WCSP Construction Cross-Section

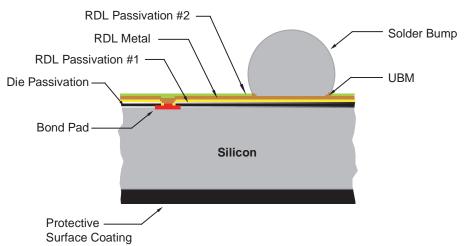

Texas Instruments' RDL technology can be used on devices designed for WCSP as well as other package types. This method allows introduction of a broader portfolio of devices that may not have the production volume to justify the tooling costs of a brand new device. Using RDL technology, the solder bump is placed on a bond pad specially created in a different location than the bond pad originally designed for the wire bonding process.

A cross-sectional view of a typical RDL application is given in Figure 4. RDL construction consists of:

- A protective polymer re-passivation layer (to cover the delicate silicon surface)

- A copper metal layer to move the interconnect to the proper array location

- A second polymer layer to insulate the RDL layer

- Under-bump metal (UBM) contact

- 300µm solder sphere

Figure 4. RDL WCSP Construction Cross-Section

#### 2.2 NanoStar Package Dimensions

Typical NanoStar package dimensions are shown in Figure 5. Current released package drawings are available through the TI web site (www.ti.com). These package drawings are generic for each array footprint. The drawings provide details of solder bump tolerances, package thickness, and basic size information. Keep in mind that NanoStar is a die size package; therefore, the exact package outline varies within a given package footprint. Each device in the NanoStar package will detail the exact product device size in the relevant data sheet.

DIE-SIZE BALL GRID ARRAY

- Reference Product Data Sheet for die size and orientation.

- Â

- Reference Product Data Sheet for array population. 2 x 2 matrix pattern is shown for illustration only.

F. This package is Tin-Lead (SnPb). Refer to YZB (Drawing #4205055) for Lead Free version.

Figure 5. YEB Package Dimensions

#### 2.3 Thermal Performance

Typical thermal performance of the NanoStar devices can be found in Table 2. Due to the small size, low profile, and location of the power plane, the primary path for heat dissipation in the NanoStar device is through the board. This makes the Theta JB a more significant number than Theta JA when considering the thermal characteristics of a NanoStar package. (Theta JA, or  $\theta_{JA}$ , is junction-to-air; Theta JB, or  $\theta_{JB}$ , is junction-to-board). Thermal performance can be improved for all package sizes by using thermal planes in a multilayer PCB under the NanoStar device. It is not recommended to clamp any heatsink to the top of a NanoStar device. Figure 6 shows a graphical comparison of the thermal resistance change across a range of package designators for a simple JEDEC 1S0P board. Figure 7 shows the possible improvement by using a typical four-layer JEDEC 2S2P board.

Figure 6. JEDEC 1S0P Thermal Performance Data Graph

Figure 7. JEDEC 2S2P Thermal Performance Data Graph

| Chip Size<br>(mm) | Linear Airflow Velocity<br>(m/s) |         |        |        |        |           |

|-------------------|----------------------------------|---------|--------|--------|--------|-----------|

|                   | (°C/W)                           | 0 m/s   | 1 m/s  | 2 m/s  | 3 m/s  | JEDEC PCE |

| YEB               | $R_{	heta}JA$                    | 161.14  | 144.57 | 137.07 | 131.95 | 2S2P      |

| 0.85 x 0.85       | $R_{	heta}JA$                    | 304.51  | 229.93 | 202.24 | 186.62 | 1S0P      |

| 4-Bump            | $R_{\theta JB}$                  | 76.54   |        |        |        | 2S2P      |

|                   | $R_{	heta}JC$                    | 77.05   |        |        |        | 1S0P      |

| YEU               | $R_{	heta JA}$                   | 129.93  | 114.51 | 108.26 | 104.06 | 2S2P      |

| 0.95 x 1.25       | $R_{	heta}JA$                    | 247.84  | 183.41 | 160.92 | 148.31 | 1S0P      |

| 5-Bump            | $R_{	heta JB}$                   | 51.10   |        |        |        | 2S2P      |

|                   | $R_{	heta JC}$                   | 54.29   |        |        |        | 1S0P      |

| YEC               | $R_{	hetaJA}$                    | 126.383 | 110.04 | 103.98 | 99.88  | 2S2P      |

| 0.85 x 1.35       | $R_{	heta}JA$                    | 257.80  | 185.03 | 160.88 | 147.45 | 1S0P      |

| 6-Bump            | $R_{\theta JB}$                  | 53.26   |        |        |        | 2S2P      |

|                   | $R_{	heta JC}$                   | 55.97   |        |        |        | 1S0P      |

| YED               | $R_{	heta}JA$                    | 107.58  | 92.58  | 87.42  | 84.02  | 2S2P      |

| 0.85 x 1.85       | $R_{	heta JA}$                   | 231.09  | 163.62 | 142.04 | 130.14 | 1S0P      |

| 8-Bump            | $R_{\theta JB}$                  | 43.16   |        |        |        | 2S2P      |

|                   | $R_{	heta JC}$                   | 39.27   |        |        |        | 1S0P      |

| YEF               | $R_{	heta}JA$                    | 105.44  | 91.54  | 86.29  | 82.79  | 2S2P      |

| 1.35 x 1.35       | $R_{	hetaJA}$                    | 215.45  | 148.93 | 127.01 | 114.92 | 1S0P      |

| 9-Bump            | $R_{\theta JB}$                  | 35.11   |        |        |        | 2S2P      |

|                   | $R_{	heta JC}$                   | 38.49   |        |        |        | 1S0P      |

| YEG               | $R_{	heta JA}$                   | 88.99   | 75.31  | 70.55  | 67.43  | 2S2P      |

| 1.85 x 1.35       | $R_{	heta JA}$                   | 202.89  | 136.15 | 115.95 | 104.98 | 1S0P      |

| 12-Bump           | $R_{\theta JB}$                  | 31.83   |        |        |        | 2S2P      |

|                   | $R_{	heta}JC$                    | 26.20   |        |        |        | 1S0P      |

| YEH               | $R_{	heta JA}$                   | 75.96   | 66.86  | 62.23  | 59.29  | 2S2P      |

| 1.85 x 1.85       | $R_{	heta JA}$                   | 185.51  | 121.93 | 103.31 | 93.19  | 1S0P      |

| 16-Bump           | $R_{\theta JB}$                  | 26.59   |        |        |        | 2S2P      |

|                   | $R_{\theta JC}$                  | 22.75   |        |        |        | 1S0P      |

| YEJ               | $R_{	heta JA}$                   | 70.89   | 61.79  | 59.05  | 57.36  | 2S2P      |

| 1.85 x 2.35       | $R_{\theta}JA$                   | 173.48  | 112.28 | 94.55  | 85.08  | 1S0P      |

| 20-Bump           | $R_{\theta JB}$                  | 20.47   |        |        |        | 2S2P      |

|                   | $R_{\theta}$ JC                  | 17.55   |        |        |        | 1S0P      |

NOTE 1: Per JESD 51-7 [4], and JESD 51-3 [5], Power = 1W

|             | (°C/W)          | 0 m/s  | 1 m/s  | 2 m/s | 3 m/s | JEDEC PCB |

|-------------|-----------------|--------|--------|-------|-------|-----------|

| YEK         | $R_{	heta JA}$  | 57.87  | 51.59  | 48.14 | 45.85 | 2S2P      |

| 2.35 x 2.35 | $R_{	heta JA}$  | 162.01 | 105.30 | 90.28 | 80.22 | 1S0P      |

| 25-Bump     | $R_{\theta JB}$ | 18.86  |        |       |       | 2S2P      |

|             | $R_{\theta JC}$ | 14.14  |        |       |       | 1S0P      |

| YEL         | $R_{	heta JA}$  | 55.02  | 48.33  | 45.42 | 43.50 | 2S2P      |

| 2.35 x 2.85 | $R_{	heta JA}$  | 147.42 | 97.49  | 82.42 | 74.33 | 1S0P      |

| 30-Bump     | $R_{\theta JB}$ | 17.98  |        |       |       | 2S2P      |

|             | $R_{\theta JC}$ | 12.32  |        |       |       | 1S0P      |

| YEM         | $R_{	heta JA}$  | 47.49  | 45.50  | 43.49 | 42.19 | 2S2P      |

| 2.85 x 2.85 | $R_{	heta JA}$  | 141.41 | 90.60  | 74.02 | 65.47 | 1S0P      |

| 36-Bump     | $R_{\theta JB}$ | 15.26  |        |       |       | 2S2P      |

|             | $R_{\theta JC}$ | 10.34  |        |       |       | 1S0P      |

Table 2. Simulated Thermal Resistance Data<sup>(1)</sup> (continued)

NOTE 1: Per JESD 51-7 [4], and JESD 51-3 [5], Power = 1W

#### 2.4 Board Level Reliability

The Texas Instruments packaging development team has performed extensive board-level reliability (BLR) testing on the NanoStar WCSP. These board-level reliability tests are in addition to standard device performance testing. A summary of the package-level tests and the passing criteria for WCSP are given in Table 3.

Table 3. Board-Level Reliability Test Matrix

| Test              | Condition                                                                          | Criteria                                  | Sample Size |

|-------------------|------------------------------------------------------------------------------------|-------------------------------------------|-------------|

| Temperature Cycle | -40 to +125°C, 1 cycle/hr, 15 min. ramp(1)                                         | 1000 cycles, R < 1.2x from R <sub>0</sub> | 36          |

| Temperature Shock | -40 to +125°C, 2 cycle/hr, 5 min. ramp <sup>(2)</sup>                              | 500 cycle minimum, R < 1.2x from $R_0$    | 36          |

| Drop              | 0.5m, 2000+ $\mu\epsilon^{(3)}$ measured impact                                    | 10 drops, R < 1.2x from $R_0$             | 5           |

| Key Push          | 100 cycle/min., 20N max force,<br>1300με <sup>(3)</sup> , Displacement = 2.7mm max | 20K cycles, R < 1.2x from R <sub>0</sub>  | 5           |

| Three-Point Bend  | Strain Rate 5mm/min. 100mm span                                                    | $R < 1.2x$ from $R_0$ (35mm maximum)      | 5           |

NOTE 1: Per JEDEC JESD22–A104B Condition G [6] NOTE 2: Per IPC-9701

NOTE 3:  $\mu\epsilon$  = microstrain

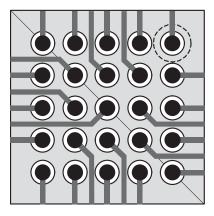

In order to simplify the BLR testing, TI developed several different daisy-chain test devices. Separate devices were created to test both BOP and RDL technologies. The principal test vehicle configuration used was a N25, 5x5 array pattern. Information on the configuration of these devices is shown in Figure 8 and Figure 9.

Figure 9. N12 3x4 Pin Array, 2.14mm x 1.5mm, Daisy-Chain Test Die Diagram

The DC devices were mounted on 160°C glass transition laminate PCBs for testing. Figure 10 shows an example of one of these test boards. These test PCBs were used for all thermal cycle BLR testing. All devices were tested using a thermal cycle with less than a 5-minute ramp, and were continuously monitored during testing. Those test boards placed into the 15-minute ramp temperature cycle were checked at ~65 cycle intervals. Summary thermal cycle testing failure data is provided in Table 4.

Figure 10. 12-Site Thermal Cycle Test BLR Test Board

|                   |              | Vehicle             |               |                     |              |                     |  |

|-------------------|--------------|---------------------|---------------|---------------------|--------------|---------------------|--|

| Test              | N25 Tin-Lead |                     | N25 Lead-Free |                     | N12 Tin-Lead |                     |  |

|                   | 1st Fail     | 63% Weibull<br>Life | 1st Fail      | 63% Weibull<br>Life | 1st Fail     | 63% Weibull<br>Life |  |

| Temperature Cycle | 1660 Cycles  | 2502 Cycles         | 1389 Cycles   | 2301 Cycles         | 1827 Cycles  | +2579(1)            |  |

| Temperature Shock | 1177 Cycles  | 1850 Cycles         | 1515 Cycles   | 2326 Cycles         | 1516 Cycles  | 3885 Cycles         |  |

| Drop              | 123 Drops    | 208 Drops           | 101 Drops     | 160 Drops           | 223 Drops    | 548 Drops           |  |

| Key Push          | 0/8 Fail     | 451301 Cycles       | 0/8 Fail      | 1.24M Cycles        | 0/8 Fail     | 651160 Cycles       |  |

| Three-Point Bend  | N/A          | Maximum             | N/A           | Maximum             | N/A          | Maximum             |  |

| Table 4. Na | anoStar Board | Level Reliability | Summary |

|-------------|---------------|-------------------|---------|

|-------------|---------------|-------------------|---------|

NOTE 1: Test stopped at 2579 cycles due to chamber malfunction.

The NanoStar WCSP BLR testing demonstrated excellent reliability in all testing. The BLR Weibull graph shows the difference achieved by using different thermal cycle profiles. As shown in Figure 11, the Weibull slope increased and the N63 fatigue life decreased as the thermal ramp temperature rate increased. Additionally, the graph shows significant improvement in a fatigue cycle file between brittle polymeric materials and TI's new re-passivation polymer technology. Also, the cycle life increases as the array size on WCSP decreases. This finding is shown by the increased performance exhibited by the N12 device.

Figure 11. N25 TCT Weibull Comparison of Ramp Rates and Materials

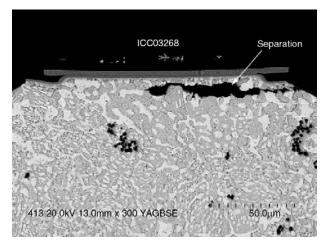

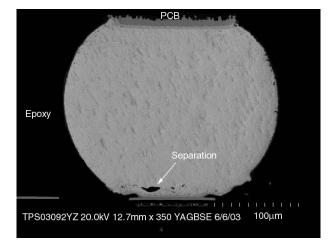

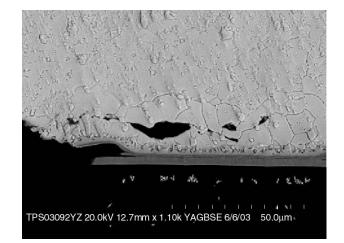

Cross-sectional images of NanoStar BLR failures are shown in Figure 12 through Figure 15. The images display typical solder cracks for BLR failures obtained with both tin-lead and lead-free solder.

Figure 12. Typical Tin-Lead BLR Solder Fatigue Crack

Figure 13. Enlargement of Crack Area in Figure 12

Figure 14. Typical Lead-Free BLR Solder Fatigue Crack

Figure 15. Enlargement of Crack Area in Figure 14

## 3 Printed Circuit Board Assembly

NanoStar can be assembled with normal SMT assembly practices in solder paste print, component placement, and reflow. This section provides detailed recommendations to achieve best overall performance.

### 3.1 PCB Design Guidelines

The size of WCSP requires care in the PCB design process for optimum reliability, processing, and manufacturability. In addition to the land pattern information (see section 3.2), the following rules should be observed:

• Best reliability results are achieved when the PCB laminate glass transition temperature is above the operating range of the intended application.

- For PCBs using a Ni/Au surface finish, the gold thickness should be less 0.5μm to avoid a reduction in solder joint thermal fatigue performance.

- Ni/Au surface finishes are not recommended for use with lead-free solder devices. OSP surface finish will deliver superior reliability results.

- Trace routing away from WCSP device should be balanced in *x* and *y* directions to avoid unintentional component movement as a result of unbalanced solder wetting forces. (An example of this effect can be seen in Figure 16.)

- Solder-mask thickness should be less than 1 mil (.001in) on top of the copper circuit pattern.

- Circuit traces routed away from PCB land pads should be less than 100µm wide (preferably  $\approx 75\mu$ m) in the exposed area inside the solder mask opening. Wider trace widths will reduce device stand-off and impact reliability.

- Recommended solder paste is Type 3.

Figure 16. Example of 5x5 Array Balanced Routing Pattern

#### 3.2 PCB Land Pattern Recommendations

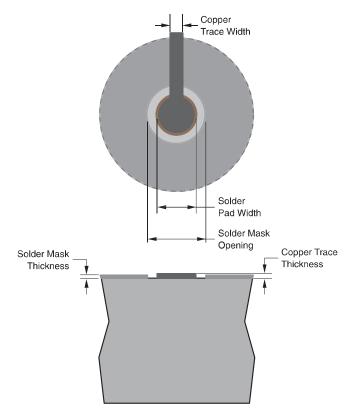

The recommended land pattern for all NanoStar solder pads is a Non-Solder-Mask defined (NMSD) solder pad. The size and shape recommendation for all devices is identical, and is given in Figure 17. Recommended dimensions are provided in Table 5.

| Table 5. | Recommended | <b>PCB Solder</b> | Land Pattern |

|----------|-------------|-------------------|--------------|

|----------|-------------|-------------------|--------------|

| Solder Pad Definition          | Copper Pad          | Solder Mask Opening | Copper Thickness |

|--------------------------------|---------------------|---------------------|------------------|

| Non-Solder-Mask Defined (NMSD) | 275µm (+0.0, –25µm) | 375μm (+0.0, –25μm) | 1oz max (32µm)   |

Figure 17. Recommended Solder Land Pattern Outline

#### 3.3 Solder Paste Stencil Design

Stencil design for NanoStar should follow standard industry recommendations such as IPC-7525 *Stencil Design Guidelines* [7]. Best BLR performance is achieved when maximum device standoff exists, which is obtained with maximum manufacturable solder paste volume. The solder stencil opening is identical for all solder pads in a WCSP array. Recommended stencil information is found in Table 6.

Table 6. Recommended Solder Stencil Pattern

| Stencil Opening <sup>(1)</sup>       | Stencil Thickness <sup>(2)</sup> |

|--------------------------------------|----------------------------------|

| 300µm Round, or 275µm x 275µm Square | 100–125µm thick                  |

NOTE 1: Round stencil opening preferred.

NOTE 2: Best solder stencil performance will be achieved using laser cut stencils with electro-polishing. The use of chemically etched stencils results in inferior solder paste volume control.

### 3.4 Component Placement

Typical surface mount placement equipment capable of placing similar sized SMT devices can assemble the NanoStar WCSP. The package provides robust self-alignment, and will re-center with up to  $150\mu$ m of displacement. There is one recommendation concerning placement force for best successwith component placement processes, however.

• On equipment without component force adjustments, the **Z** placement height should be set to avoid overdriving the board location. Optimally, the **Z** height should be set at one-half the printed solder paste height.

On equipment with component placement force adjustments, the maximum recommended placement force is 35g/bump. Exceeding this force level can reduce reliability due to excessive silicon impact stress and subsequent damage.

#### 3.5 Reflow

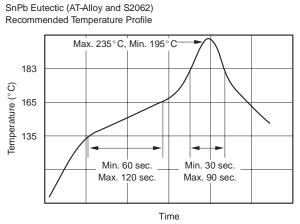

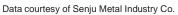

Recommended solder reflow profiles for NanoStar are shown in Figure 18. Critical reflow temperatures are given in Table 7.

Pb-Free Bump NanoFree Recommended Temperature Profile

Figure 18. Recommended Reflow Profiles

| Process Step                        | Tin-Lead Solder          | Lead-Free Solder                       |

|-------------------------------------|--------------------------|----------------------------------------|

| Ramp Rate                           | 3°C/sec Maximum          | 3°C/sec                                |

| Pre-Heat                            | 165°C, 60 to 120 seconds | Max. 150°C to 180°C, 60 to 180 seconds |

| Time above Liquidus                 | 183°C, 30 to 90 seconds  | 220°C, 30 to 90 seconds                |

| Peak Temperature                    | 235°C                    | 255°C ±5°C                             |

| Time within 5°C of Peak Temperature | 10 to 20 seconds         | 10 to 20 seconds                       |

| Ramp Down Rate                      | 6°C/sec Maximum          | 6°C/sec Maximum                        |

| Table 7. | Recommended | <b>Critical Reflov</b> | <i>w</i> Parameters |

|----------|-------------|------------------------|---------------------|

|----------|-------------|------------------------|---------------------|

### 4 Tape and Reel Information

#### 4.1 Material Specifications

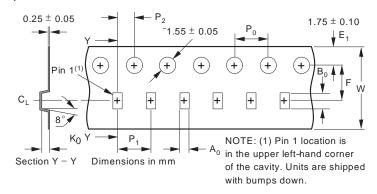

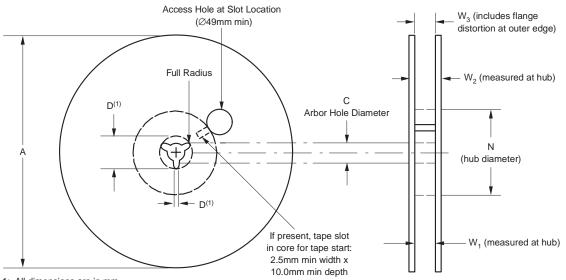

TI offers tape-and-reel packing for NanoStar packages in standard packing quantities (SPQ) of 250 and 3000 units/reel. The units are shipped in embossed carrier tape, sealed with heat-activated or pressure-sensitive cover tape, and wound on plastic reels. All of the tape-and-reel materials comply with EIA–481, and EIA–541 [8, 9]. The EIA specifications are shown in Figure 19 and Figure 20, as well as in Table 8 and Table 9. The carrier tape is made of conductive polystyrene and has a surface resistivity that falls within the static-dissipative range (1×10<sup>5</sup> to  $1×10^{11}\Omega^2$ ). Heat-activated or pressure-sensitive, antistatic, clear polyester film is used for the cover tape. The dimensions of most interest to the end user are tape width (W), cavity pitch (P), and cavity size (A<sub>0</sub>, B<sub>0</sub>, K<sub>0</sub>), as shown in Figure 19. Due to the wide range of die sizes within a given array size, the cavity size dimensions will vary. Please refer to the specific product data sheet for devices of interest for the cavity dimensions (A<sub>0</sub>, B<sub>0</sub>, K<sub>0</sub>).

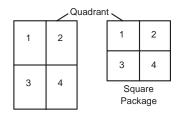

The units are placed in the carrier-tape cavity, with pin 1 located as specified in EIA–481. The longest axis of the package is perpendicular to the tape sprocket holes, and pin 1 is closest to the round sprocket holes. Thus, for rectangular or square packages, pin 1 is located in quadrant 1 (see Figure 21). All dimensions are in millimeters.

Figure 19. Pocket Tape Dimensions

| Designator                                        | YEB       | YEC            | YED          | YEF          | YEG          | YEH          | YEJ            | YEK          | YEL            | YEM            |

|---------------------------------------------------|-----------|----------------|--------------|--------------|--------------|--------------|----------------|--------------|----------------|----------------|

| Pocket Pitch, P <sub>1</sub>                      | 4.00 ±.10 | $4.00\pm.10$   | 4.00 ±.10    | 4.00 ±.10    | 4.00 ±.10    | 4.00±.10     | $8.00\pm.10$   | 8.00 ±.10    | 8.00 ± .10     | 8.00 ± .10     |

| Sprocket Hole-to-Pocket<br>Centerline, F          | 3.50±.05  | $3.50 \pm .05$ | $3.50\pm.05$ | $3.50\pm.05$ | $3.50\pm.05$ | $3.50\pm.05$ | $5.50 \pm .05$ | $5.50\pm.05$ | $5.50 \pm .05$ | $5.50 \pm .05$ |

| Sprocket Hole-to-Pocket<br>Offset, P <sub>2</sub> | 2.00±.05  | $2.00 \pm .05$ | 2.00±.05     | 2.00±.05     | 2.00±.05     | 2.00±.05     | 2.00±.05       | 2.00±.05     | 2.00±.05       | $2.00\pm.05$   |

| Sprocket Hole Pitch, P0                           | 4.00 ±.10 | $4.00\pm.10$   | 4.00 ±.10    | 4.00 ±.10    | 4.00 ±.10    | 4.00±.10     | $4.00\pm.10$   | 4.00 ±.10    | $4.00\pm.10$   | $4.00\pm.10$   |

| Tape Width, W                                     | 8         | 8              | 8            | 8            | 8            | 8            | 12             | 12           | 12             | 12             |

| Reel Diameter, Max.                               | 178       | 178            | 178          | 178          | 178          | 178          | 178 / 330      | 178 / 330    | 178 / 330      | 178 / 330      |

Table 8. Common Tape Dimensions by Designator<sup>(1)</sup>

NOTE 1: All dimensions are in mm.

NOTE 1: All dimensions are in mm.

Figure 20. Pocket Tape Dimensions

| Table 9. | Reel | Specifications <sup>(1)</sup> |

|----------|------|-------------------------------|

|----------|------|-------------------------------|

| Reel<br>Diameter<br>(A) | Reel<br>Width<br>(W1) | Hub<br>Diameter Max<br>(N) | Reel<br>Thickness<br>(W2) | Arbor-Hole<br>Diameter<br>(C) | Quantity/Reel |

|-------------------------|-----------------------|----------------------------|---------------------------|-------------------------------|---------------|

| $178\pm0.60$            | $8.4 \pm 1.65$        | $62\pm0.50$                | $14.4\pm1.65$             | $13.0 \pm 0.5 / - 0.2$        | 250 or 3000   |

| $178\pm0.60$            | $12.4 \pm 1.65$       | $62\pm0.50$                | $18.4 \pm 1.65$           | $13.0 \pm 0.5 / -0.2$         | 250           |

| $330\pm0.60$            | $12.4 \pm 1.65$       | $62\pm0.50$                | $18.4 \pm 1.65$           | 13.0±0.5/-0.2                 | 3000          |

NOTE 1: All dimensions are in mm.

### 5 Symbolization

The top of the package is laser-marked with device name, date code, assembly-site code, assembly-lot trace code, and pin-1 location as space allows. Table 10 shows the device-marking symbolization guidelines for NanoStar packages.

The *Character* and *WCSP Laser Mark Image* column entries in Table 10 have the following meanings:

- **CCCC** Device name (shortened in accordance with product data sheet)

- Y Year

- M Month

- D Day

- S Site code

- LLLL Lot trace code

- A Pin-1 quadrant identifier (data sheet specifies exact pin-1 location)

Tin-lead solder devices use a "1" (one), and lead-free solder devices use a "0" (zero).

For specific marking information on a particular device, please see the device data sheet (available for download from the TI web site).

| Designator                                                       | Text Rows | Characters                              | WCSP Laser Mark Image |

|------------------------------------------------------------------|-----------|-----------------------------------------|-----------------------|

| YEB<br>YZB<br>4YZT                                               | 1         | Lot Code<br>and 2-Character Device Code | A CC                  |

| YEA/YZA<br>YEP/YZT<br>5YZT/6YZT<br>YEC/YZC<br>YEQ/YZQ<br>YEU/YZU | 1         | Lot Code<br>and 2-Character Device Code | A                     |

| YED<br>YZD                                                       | 0         | Full Lot Code<br>No Device Code         | AMLLLLS               |

Table 10. Device-Marking Guidelines

| Designator | Text Rows | Characters                                             | WCSP Laser Mark Image                        |

|------------|-----------|--------------------------------------------------------|----------------------------------------------|

| YEF<br>YZF | 2         | Full Lot Code<br>and 3-Character Device Code           | YMLLLL<br>CCCS<br>A                          |

| YEG<br>YZG | 2         | Full Lot Code<br>and 6-Character Device Code           | YMLLLLS<br>A                                 |

| YEH<br>YZH | 3         | Full Lot Code<br>and 8-Character Device Code           | YMLLLS<br>cccccccc                           |

| YEJ<br>YZJ | 3         | Full Lot Code<br>and up to<br>22-Character Device Code | CCCCCCCCCC<br>CCCCCCCCCCCC<br>YMLLLLS<br>A   |

| YEK<br>YZK | 3         | Full Lot Code<br>and up to<br>22-Character Device Code | CCCCCCCCCC<br>CCCCCCCCCCC<br>YMLLLLS<br>A    |

| YEL<br>YZL | 3         | Full Lot Code<br>and up to<br>22-Character Device Code | CCCCCCCCCCCC<br>CCCCCCCCCCCC<br>YMLLLLS<br>A |

| YEM<br>YZM | 3         | Full Lot Code<br>and up to<br>22-Character Device Code | A CCCCCCCCCCC                                |

| Table 10. | <b>Device-Marking</b> | Guidelines | (continued) |

|-----------|-----------------------|------------|-------------|

|-----------|-----------------------|------------|-------------|

### 6 Features and Benefits

In summary, key features and advantages for devices in the NanoStar package are:

- Smallest possible form factor; die size equals package size.

- Excellent proven board level reliability performance

- Compatible with standard SMT assembly processes.

- Compatible with standard surface mount PCB technology.

## 7 Conclusion

Texas Instruments NanoStar package offerings are bare die packages, with improved performance and reduced package footprint over similar SOT-23, SC-70, and SOIC packages. Additionally, the NanoStar packages meet the industry's lead-free demands, have reliable solderability using either lead or lead-free solder paste, and can be reworked and manufactured using conventional equipment. The packages allow for product miniaturization and comply with dimensional specifications of JEDEC standard MO–211.

### Acknowledgments

The author wishes to thank the entire NanoStar development team. This package would not have been possible without the support of each and every person on the worldwide WCSP team. Unfortunately, the list of contributors is too large for print.

### References

Listed JEDEC references can be found at: <u>http://www.jedec.org/download/default.cfm</u>.

- 1. Package standard MO–211, *Die–size Ball Grid Array, Fine Pitch, Thin/Very, Thin/Extremely, Thin Profile, F–XBGA.* (JEDEC)

- Smetana, J. Wafer Scale CSP Reliability Characterization Project Final Report. High Density Packaging User Group International.Scottsdale, AZ and Alvsjo, Sweden. Available at: http://www.hdpug.org/public/4-papers/2001/ws-csp/wafer\_scale\_final.pdf.

- 3. Package standard MO–211, *Die–size Ball Grid Array, Fine Pitch, Thin/Very, Thin/Extremely, Thin Profile, F–XBGA.* (JEDEC)

- 4. High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages. JESD 51–7. (JEDEC)

- 5. Low Effective Thermal Conductivity Test Board for Leaded Surface Mount Package. JESD 51–3 (JEDEC)

- 6. Test Method Temperature Cycling. JESD22–A104B. (JEDEC)

- Stencil Design Guidelines. IPC–7525. Available at: www.dynamixtechnology.com/docs/IPC–7525s.pdf, or order from IPC (www.ipc.org).

- Taping of Surface Mount Components for Automatic Placement. EIA-481. Electronics Industry Alliance. Available at: http://www.chipro.com/PDF%20Files/EIA-481-B.pdf, or order from EIA (www.eia.org).

- Packing Material Standards for ESD Sensitive Items. EIA–541. Available for purchase at: http://www.tiaonline.org/standards/search\_results2.cfm?document\_no=EIA%2D541, or from EIA (www.eia.org).

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated