# Analog Engineer's Circuit: Data Converters

JAJA614-January 2019

# DAC フォース / センス基準電圧駆動回路

Paul Frost

#### 設計目標

| DAC 出力範囲 | DAC V <sub>REF</sub> H の入力電圧 | DAC V <sub>REF</sub> L の入力電圧 |

|----------|------------------------------|------------------------------|

| -5V∼5V   | 5V                           | -5V                          |

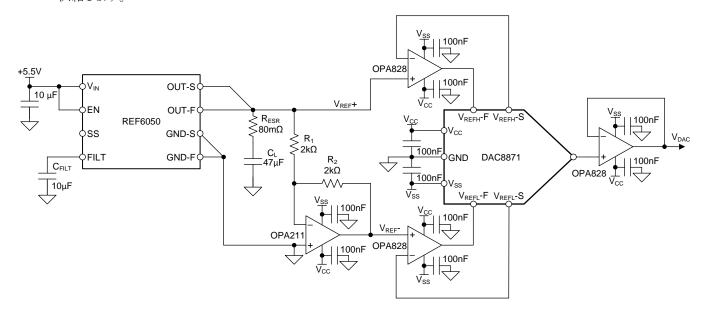

#### 設計の説明

核磁気共鳴画像診断装置 (MRI) や 任意波形ジェネレータ (AWG) などのアプリケーションに使用される高精度デジタル / アナログ・コンバータ (DAC) には一般に、高精度の基準電圧が必要です。これらのシステムにおける一般的な問題点の原因は、DAC の基準入力に不要な直列抵抗が発生することです。この抵抗により、コードに基づいて R-2R ラダーの入力電流が変化するにつれて、DAC の入力コードに応じた電位降下がラダーの両端に発生します。結果として、DAC コードに応じて基準電圧が変化するように見え、弓型の積分非線形誤差曲線の原因となります。

この問題を解決するため、高精度の DAC には多くの場合、各基準入力 (V<sub>REF</sub>H および V<sub>REF</sub>L) に基準電圧のフォース / センス・ピンが備わっています。これらのピンは本質的に、それぞれ独自の直列抵抗を持つ、R-2R ラダーの基準入力ノードに対する 2 つの並列接続に過ぎませんが、外部にユニティ・ゲイン基準電源バッファを追加することで、ノード電圧をこのアンプによって補償できます。オペアンプの反転入力に流れ込む微小バイアス電流によって、センス入力の直列抵抗の両端に微小電圧が発生し、オペアンプ出力は R-2R ラダーが必要とする電流を供給します。

### デザイン・ノート

- 1. 選択した基準電圧には正の 5V 出力しか存在しないため、 $V_{REF}$  値を生成するには反転アンプが必須です。抵抗  $R_1$  と  $R_2$  も、基準電圧出力から -5V 電位への電流経路を作っています。この電流は基準電圧により供給されます。電流を制限するため  $R_1$  と  $R_2$  の値を増やすことができますが、回路のノイズが増加します。アンプの電流ノイズと、抵抗の熱ノイズは、回路の全ノイズを増加させます。

- 2. 基準電圧のノイズは、C<sub>FILT</sub> を追加し、内部基準電圧のバンドギャップにより生成されるノイズにフィルタ処理を行うことで低減できます。また、基準電圧の出力には、等価直列抵抗 (ESR) の最小値が規定されているコンデンサ (C<sub>I</sub>) も必要です。この抵抗を PCB 上の長い配線により作成することも可能で、R<sub>ESR</sub> として示されています。

- 3. DAC のノイズは、主に抵抗ラダーの熱ノイズから生まれます。熱ノイズは次の式で計算されます。ここで  $K_b$  はボルツマン定数、T はケルビン単位の温度、R はラダーの抵抗、F は周波数範囲です。

$$V_{NOISE} = \sqrt{4 \cdot K_b \cdot T \cdot R \cdot \Delta F}$$

DAC8871 の出力インピーダンスは約 6.25kΩ (標準値) であり、室温での動作を想定すると、熱ノイズは次の式で計算できます。

$$V_{NOISE} = \sqrt{4 \cdot 1.38 \cdot 10^{-23} \text{ J/K} \cdot 300 \text{K} \cdot 6.25 \text{k}\Omega \cdot 1 \text{Hz}}$$

$$= 10.17 \text{nV} / \sqrt{\text{Hz}}$$

### 設計手順

- 1. 分解能、精度、ノイズ性能から DAC を選択します。分解能はアプリケーションによって異なりますが、この回路では 16 ビット以上の分解能が普通です。 DAC の出力誤差は、非線形誤差と見なされます。 非線形誤差は、積分非線形誤差 (INL) および差分非線形誤差 (DNL) として表されます。 DAC の入力に理想的な基準電圧が接続されていると仮定すると、システムの INL および DNL 誤差は R-2R ラダーの抵抗の不正確性に起因します。

- 2. 基準電圧は、アプリケーションの精度、温度ドリフト、ノイズの要件に基づいて選択します。出力電圧精度は通常パーセント単位で規定されます。温度ドリフトは ppm/℃ (百万分率) 単位で規定されます。回路のノイズには 2 つの仕様があります。低周波数ノイズは通常、限られた周波数ドメイン (0.1Hz~10Hz) 上の V<sub>PEAK-PEAK</sub> で規定され、合計積分ノイズは V<sub>RMS</sub> で規定されます。

- 3. 基準電圧の反転に使用されるオペアンプは、ノイズ性能に基づいて選択する必要があります。このアンプは、電圧ノイズと電流ノイズの 2 つの経路でシステムのノイズを増加させます。電圧ノイズからの増加分は、電圧ノイズが通常小さいバイポーラ入力アンプを選択することで、最小化できます。バイポーラ入力アンプは CMOS 入力アンプよりも電流ノイズが大きくなりますが、回路の抵抗 R<sub>1</sub> と R<sub>2</sub> により、電流ノイズは電圧ノイズに変換されます。これらの部品の抵抗値を最小化することで、アンプの電流ノイズによる増加分を最小化できます。

- 4. DAC のフォース/センス入力を駆動するアンプは、高速なセトリングと帯域幅を重視して選択する必要があります。 DAC が新しい入力コードで更新されると、R-2R 抵抗ラダーのスイッチにより、基準電圧入力から要求される電流が突然変化します。 その結果、基準電圧入力の過渡が発生し、DAC 出力にも伝搬されます。 基準電圧バッファ・アンプが迅速にセトリングできれば、出力の誤差は最小限に抑えられます。

さらに、これらのアンプの電圧ノイズは、システムの全ノイズを増加させます。この理由から、バイポーラまたは JFET 入力アンプを選択する必要があります。

- 5. 本回路が負荷を駆動する必要がある場合、出力バッファを選択します。DAC8871 はバッファなしのデバイスであり、DAC の出力は抵抗ラダーのノードです。このアンプは、電流出力能力、容量性負荷での安定性、スルー・レート、電圧範囲など、負荷の要件に基づいて選択されています。

- 6. コンデンサ  $C_{FILT}$  と  $C_L$  は低 ESR のセラミック・コンデンサです。コンデンサの電圧定格は、5V 基準電圧出力に 適合している必要があります。

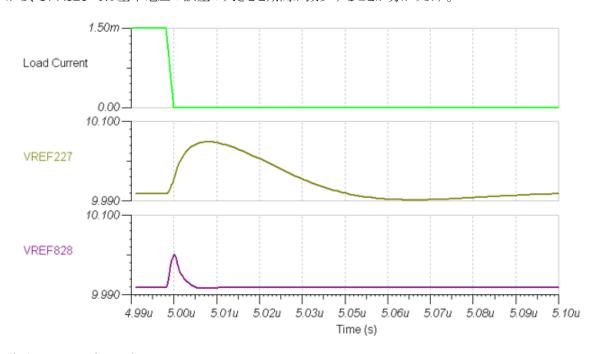

# 基準電圧バッファの負荷過渡

基準電圧バッファは、DAC のコードが変化したとき、R-2R ラダーに必要な過渡電流を迅速に供給できる必要があります。DAC8871 のアーキテクチャから、最大過渡電流は DAC がゼロまたはフルスケール・コードから中間スケールへ移行するとき発生します。この過渡は、V<sub>REF</sub>H 入力と V<sub>REF</sub>L 入力の間に電流源を接続することでシミュレーションできます。次のシミュレーションは、OPA828 と OPA227 での電流過渡時の基準電圧の差を示します。この結果から、OPA828 では基準電圧の誤差の大きさと期間が減少することが分かります。

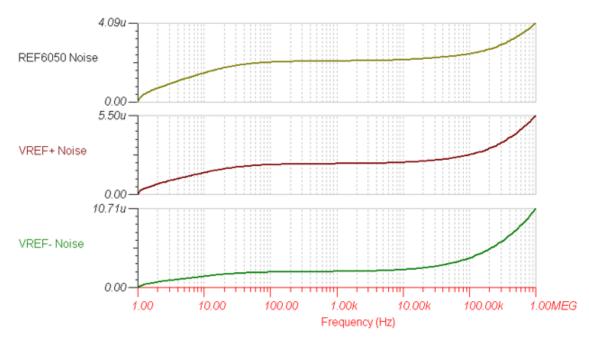

#### 基準バッファの全ノイズ

回路により生成される全ノイズを、次のシミュレーションに示します。基準電源、反転アンプ、基準バッファがそれぞれノイズに寄与します。V<sub>REF</sub>- 入力のノイズが大きいことに注意してください。これは、反転アンプと、その帰還ネットワークのディスクリート抵抗による増加によるものです。

# 設計の参照資料

TIの総合的な回路ライブラリについては、「アナログ・エンジニア向け回路クックブック」を参照してください。 この回路用の付属シミュレーション・ファイルをダウンロードできます。

### 使用デバイス

| デバイス    | 主な特長                                              | リンク                               | 他の使用可能デバイス                 |

|---------|---------------------------------------------------|-----------------------------------|----------------------------|

| DAC8871 | 16 ビット・シングル・チャネル、シリアル・インターフェイス、高耐圧バイポーラ<br>出力 DAC | http://www.ti.com/product/DAC8871 | テキサス・インスツルメンツ製の<br>高精度 DAC |

| OPA828  | 低オフセット、低ドリフト、低ノイズ、45MHz、JFET 入力オペアンプ              | http://www.ti.com/product/OPA828  | 高精度アンプの概要                  |

| OPA221  | 1.1nV/rtHz のノイズ、低消費電力、高精度オペアンプ                    | http://www.ti.com/product/OPA211  | 高精度アンプの概要                  |

| REF6050 | 低ノイズ、高精度、5V 出力基準電圧                                | http://www.ti.com/product/REF6050 | テキサス・インスツルメンツ製の<br>直列基準電圧  |

# その他のリンク

弊社の高精度 DAC ラーニング・センターで、高精度 DAC を使用する設計方法について学習できます。

TI の高精度 DAC ポートフォリオや他の技術資料をご覧ください。

# 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションが適用される各種規格や、その他のあらゆる安全性、セキュリティ、またはその他の要件を満たしていることを確実にする責任を、お客様のみが単独で負うものとします。上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売約款 (https://www.tij.co.jp/ja-jp/legal/terms-of-sale.html)、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

日本語版 日本テキサス・インスツルメンツ合同会社 Copyright © 2021, Texas Instruments Incorporated