# トランス・インピーダンス・アンプ設計の基礎

川田章弘

Field Application & Solutions, Analog Signal Chain

#### アブストラクト

本アプリケーション・レポートは、初めてトランス・イン ピーダンス・アンプを設計する人のために、回路定数を決定 する方法とアンプの雑音レベル、および回路の安定性につい て検討する方法を解説するものです。

第1章では、トランス・インピーダンス・アンプの回路定数を決定する方法について解説します。第2章では、第1章で求めた回路定数からアンプの出力雑音レベルを求める方法、およびそのシミュレーション結果について解説します。そし

て第3章では、設計後のアンプの安定性をシミュレーション により確認する方法について解説します. 回路のシミュレー ションには、Design Soft社のTINAを使用します.

本レポートでの回路解析は、OPアンプ回路の基本動作原理や、雑音解析手法について理解していることを前提にしています。もし、OPアンプ回路の雑音計算に不慣れな場合は、必要に応じて他のアプリケーション・レポート(たとえば、sloa082など)を参照してください。

#### 目次

| 1. | 回路定数の決め方                         |    |

|----|----------------------------------|----|

|    | 1.1 トランス・インピーダンス・ゲインを決める         | 2  |

|    | 1.2 安定性を確保する                     | 2  |

| 2. | 雑音レベルを計算する                       | 4  |

|    | 2.1 ノイズ・ゲインを求める                  | 4  |

|    | 2.2 各ノイズ・ゲイン領域での雑音帯域を求           | 5  |

|    | 2.3 ステップ1: OPアンプに起因する出力教         | 6  |

|    | 2.4 ステップ2: すべての要素を合成して出力雑音電圧を求める | 7  |

|    | 2.5 シミュレーションによる確認                |    |

| 3. | 安定性の確認                           | 10 |

|    | 3.1 シミュレーション方法                   |    |

|    | 3.2 シミュレーション結果                   | 11 |

|    | まとめ                              |    |

| 5. | 参考文献                             | 12 |

この資料は日本テキサス・インスツルメンツ(日本TI)が、お客様がTIおよび日本TI製品を理解するための一助としてお役に立てるよう、作成しております。製品に関する情報は随時更新されますので最新版の情報を取得するようお勧めします。

TIおよび日本TIは、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。また、TI及び日本TIは本ドキュメントに記載された情報により発生した問題や障害等につきましては如何なる責任も負いません。

# 1. 回路定数の決め方

### 1.1 トランス・インピーダンス・ゲインを決める

C1や、R1の値は、フォトダイオードのデータシートから判断 します。

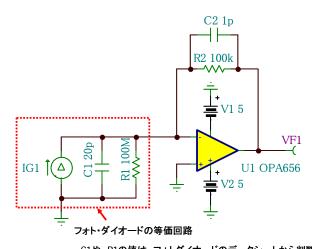

図1 一般的なトランス・インピーダンス・アンプ

図 1 に一般的なトランス・インピーダンス・アンプの例を示しました。この回路は,フォト・ダイオードから発生した微弱な電流をトランス・インピーダンス $R_2$ で電圧に変換して出力する回路です。フォト・ダイオードの等価回路は,図の赤い鎖線に示したように定電流源 $IG_1$ ,および並列接続されたダイオードの寄生容量 $C_1$ ,および内部抵抗 $C_1$ によって構成されます。詳細は後述しますが,ダイオードの寄生容量 $C_1$ は,雑音性能に影響を与えます。この値が小さいほどトランス・インピーダンス・アンプから発生する雑音を小さくすることが可能です。

トランス・インピーダンス・ゲインは、 $R_2$ により決定されますので、入力電流を $I_{in}$ 、そのときの出力電圧を $V_0$ として、以下の式により決定します。

$$R_2 = \frac{V_o}{I_{in}}$$

ここで、入力電流  $40\mu$  A のときの出力電圧を 4V とすると、次のように求まります.

$$R_2 = \frac{4}{40 \times 10^{-6}} = 100k\Omega$$

このように、トランス・インピーダンス・ゲインを決める $R_2$ の値は、簡単な計算によって求めることができます。

#### 1.2 安定性を確保する

トランス・インピーダンス・アンプにおいて、負帰還安定性を確保するために $C_2$ は必須です。この値の決定には、参考文献(1)に示されている解析結果を利用します。それは、以下の式により $C_2$ を計算するというものです。

$$C_2 = \sqrt{\frac{C_1 + C_{in}}{2\pi \times Q^2 \times GBW \times R_2}}$$

ここで、 $C_1$ はフォト・ダイオードによって決まる定数です。また、 $C_{in}$ はOPアンプの入力容量によって決まる定数です。ここで、

$$C_1 >> C_{in}$$

であれば, $C_1+C_{in}\approx C_1$ と見なすことができます.ここでは,この近似によって定数計算を行います.GBW は,使用する OP アンプの利得帯域幅積です.Q は,回路の安定性とセトリング特性を決める定数で,臨界制動条件であれば, $Q=\frac{1}{\sqrt{2}}$ です.スピードと安定性を両立するために,Q はこの値としておきます.また,パルス応答特性にオーバ・シュートなどが生じても良い場合は,Q の値を大き

くしますが、発振を防ぐために1以下の値とします。

ここで、図 1 の回路定数で、かつOPアンプにOPA656 を使用すると仮定して定数計算をしてみます。OPA656 のGBWは 230MHzですので、 $C_2$ の値は、

$$C2 = \sqrt{\frac{20 \times 10^{-12}}{\pi \times 230 \times 10^6 \times 100 \times 10^3}} \approx 0.526 \, pF$$

と求まります.  $C_2$ の値がこれよりも大きければ回路は安定ですので、図 1 では、 $C_2$ =1pFとしています. なお、 $C_2$ =1pFのときのQは、約 0.4 になります.

# 2. 雑音レベルを計算する

安定性を考えるときに、OPアンプの入力容量 $C_{in}$ について考慮したように、実際の回路では、 $C_1$ と並列にOPアンプの入力容量が接続されます。

この結果,トランス・インピーダンス・アンプを低雑音化する鍵は, $C_1$ の小さなフォト・ダイオードを選択することと,入力容量 $C_{in}$ の小さなOPアンプを選択することの 2 つになります.なぜそうなるのか,これから検討していくことにします.

### 2.1 ノイズ・ゲインを求める

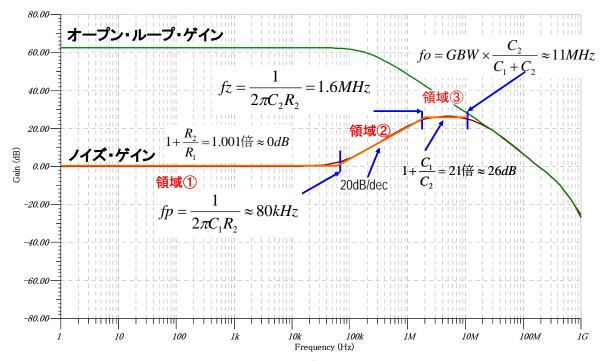

図2 図1の回路のノイズ・ゲインー周波数特性

OP アンプ回路の雑音を計算するときには、ノイズ・ゲインという値を使います.この値は、OP アンプの入力換算雑音電圧に対するゲインを表しています.

図 2 に、図 1 に示したトランス・インピーダンス・アンプのノイズ・ゲインー周波数特性を示しました. 直流から $C_1$ と $R_2$ によって決まる周波数 $f_p[H_Z]$ までのノイズ・ゲインは、

$$NG_{\text{(ijw]}} = 1 + \frac{R_2}{R_1}$$

となります.

ここで、周波数 fp から周波数 fz までの間は、20dB/dec(6dB/oct)でゲインが上昇します。これは、OP アンプの入力換算雑音電圧が 20dB/dec の傾きで増大することを表しています。なお、fp[Hz]とfz[Hz]の周波数は、以下の式によって求めることができます。

$$fp = \frac{1}{2\pi C_1 R_2}$$

$$fz = \frac{1}{2\pi C_2 R_2}$$

トランス・インピーダンス・アンプのしゃ断周波数  $fc=\frac{1}{2\pi C_2R_2}$  付近でのノイズ・ゲインは,領域③となり,このときのノイズ・ゲインは,

$$NG_{\text{(ijw3)}} = 1 + \frac{C_1}{C_2}$$

となります.

この式から、 $C_1$ を小さくするか、 $C_2$ を大きくしない限り、領域③での雑音が大きくなってしまうことがわかります。しかし、 $C_2$ の値を大きくするということは、トランス・インピーダンス・アンプの周波数帯域を制限することに他なりません。したがって、現実的には $C_1$ の小さなフォト・ダイオードを選択することになります。

なお、 $C_1$ の値が大きいということは、周波数fpが低いということになり、領域②の範囲が広くなることをも意味しています。このことからも、トランス・インピーダンス・アンプを低雑音化するには、 $C_1$ を小さくすることが大切であることがわかります。

さらに注意を要するのは、フォト・ダイオードの $C_1$ が十分に小さい場合、今度はOPアンプの入力容量が雑音特性に影響を与え始めるということです。このようなときは、入力容量のより小さなOPアンプを選択する必要があります。

ここで、図1のトランス・インピーダンス・アンプにおいて、負帰還によるメリットがなくなる点(負帰還ループが切れる点)foは、以下の式で求まります。

$$fo = GBW \times \frac{C_2}{C_1 + C_2}$$

これまで説明してきた各周波数、およびノイズ・ゲインについて、図 1 の回路に基づき、実際に計算した結果を図 2 に示しました.

#### 2.2 各ノイズ・ゲイン領域での雑音帯域を求める

前節で、ノイズ・ゲインの周波数特性を示しました。本節では、先の検討結果を元に、トランス・インピーダンス・アンプから出力される積分雑音電圧(実効値雑音電圧)を求める方法について検討していきます。

実効値雑音電圧を求める上で必要になるのは、各ノイズ・ゲイン領域における雑音帯域幅の計算式です. そこで本節では、領域①~③について雑音帯域を求める式を示します.

領域①には、OPアンプから発生する 1/f雑音を含みます。1/f雑音は、周波数に反比例して雑音電力が減少します。ここで、1/f雑音の下限周波数を $f_L$ 、上限周波数を $f_H$ とすると、以下のように求まります。

$$BW_{vn1/f} = \sqrt{\int_{f_L}^{f_H} \frac{1}{f} df} = \sqrt{\ln\left(\frac{f_H}{f_L}\right)}$$

なお、1/f雑音の上限周波数 $f_H$ は、後述する 1/fコーナ周波数によって決まりますが、下限周波数 $f_L$ の値ついては任意です。つまり回路の設計者が要求仕様に基づいて任意に決める値です。

領域②は、周波数の上昇に伴って、ゲインが 20dB/dec の傾きで上昇する領域です。したがって、 雑音電力は周波数の2乗に比例することになります。したがって、次式のように計算することができ ます.

$$BW_{vn2} = \sqrt{\int_{f_L}^{f_H} f^2 df} = \sqrt{\frac{f_H^3}{3} - \frac{f_L^3}{3}}$$

最後に、領域③について考えます. この領域は帯域内でゲインがフラットですので、抵抗から発生 する熱雑音と同様に(白色雑音として)考えることができます。また、高域では、OP アンプのオープ ン・ループ・ゲイン特性に沿ってそのゲインが-20dB/dec で減衰していきます. このことから, 等 価雑音帯域幅係数 $\frac{\pi}{2}$ を考慮すると、この領域の雑音帯域は以下のように計算することができます.

$$BW_{vn3} = \sqrt{\frac{\pi}{2} (f_H - f_L)}$$

以上で、出力雑音電圧を計算する上で必要な式は揃いました、次節では、実際に各領域におけるノ イズ・ゲインと雑音帯域を使って出力雑音電圧を求めてみます.

## 2.3 ステップ1: OPアンプに起因する出力雑音電圧を求める

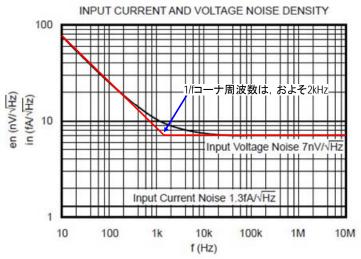

図3 OPA656 の入力換算雑音電圧密度特性

出力雑音の計算は、領域①~③におけるノイズ・ゲインと、図 3 に示す OP アンプの入力換算雑音 電圧密度、および雑音帯域を乗算することで求めることができます。具体的には、以下のような計算 になります.

$$V_n = V_{ni} \times NG \times BW$$

ここで、 $V_{ni}$ はOPアンプの入力換算雑音電圧密度、NGは各領域におけるノイズ・ゲイン、BWは各 領域における雑音帯域です.

次に、図1の回路の出力雑音電圧を実際に計算してみます.

図3の特性から,1/f雑音帯域を0.01Hz~2kHzとします.上限周波数である2kHzは,図3から 1/f コーナ周波数を読み取ったものです. 0.01Hz という下限周波数は、任意に決めた値です. 低周波 雑音をあまり気にしない場合は、0.1Hzや1Hzとします.

1/f 雑音領域が決まったら、図 3 の 10 Hz における入力換算雑音電圧密度の値を読み取ります.そして,この雑音電圧密度の値を 1 Hz での値に換算します.この変換が,今回の雑音計算を行なう上での鍵です.1/f 雑音電圧(電力ではない)は,周波数の平方根に反比例しますので,10 Hz で 80n V  $1/\sqrt{10}$  Hz ということは,1 Hz では,その $1/\sqrt{10}$  行になります.したがって,

$$V_{n1_{-1/f}} = \left(80 \times 10^{-9} \times \sqrt{10}\right) \times 1.001 \times \sqrt{\ln\left(\frac{2 \times 10^{3}}{0.01}\right)} \approx 0.9 \,\mu V_{RMS}$$

となります. ここで、1.001 という値は、図 2 で示した領域①におけるノイズ・ゲインであることに注意してください.

また、領域①は、1/f 雑音以外に、白色雑音も含みます。したがって、1/f コーナ周波数である  $2kHz\sim fp=80kHz$  までの出力雑音電圧を以下のように計算します。

$$V_{n1\ white} = 7 \times 10^{-9} \times 1.001 \times \sqrt{80 \times 10^3 - 2 \times 10^3} \approx 2.0 \mu V_{RMS}$$

引き続き、領域②の出力雑音について考えます。この領域では、fp=80kHz における OP アンプの入力換算雑音電圧密度を 1Hz に換算して考えます。この領域では、周波数に比例して振幅が大きくなっています。つまり、fp=80kHz で  $7nV/\sqrt{Hz}$  である入力雑音電圧密度は、1Hz では 1/80000 倍に小さくなると考えることができます。したがって、

$$V_{n2} = \left(7 \times 10^{-9} \times \frac{1}{80 \times 10^{3}}\right) \times 1.001 \times \sqrt{\frac{\left(1.6 \times 10^{6}\right)^{3}}{3} - \frac{\left(80 \times 10^{3}\right)^{3}}{3}} \approx 102 \mu V_{RMS}$$

と求まります.

最後に、領域③の出力雑音を求めます.

$$V_{n3} = 7 \times 10^{-9} \times 21 \times \sqrt{\frac{\pi}{2} \left(11 \times 10^6 - 1.6 \times 10^6\right)} \approx 545 \mu V_{RMS}$$

以上により求めた $V_{n1}$ ,  $V_{n2}$ ,  $V_{n3}$ を二乗平均すると,OPアンプの入力換算雑音に起因する出力雑音電圧は,以下のように求まります.

$$Vn = \sqrt{V_{n1\_1/f}^2 + V_{n1\_white}^2 + V_{n2}^2 + V_{n3}^2} = \sqrt{0.9^2 + 2.0^2 + 102^2 + 545^2} \times 10^{-6} \approx 554 \,\mu V_{RMS}$$

#### 2.4 ステップ2:すべての雑音電圧を合成して出力雑音電圧を求める

2.3 で求めた出力雑音電圧には、OPアンプの入力換算雑音電流の影響や、帰還抵抗の熱雑音の影響が含まれていません。そこで、本節では、これらの影響も考慮した上で、トランス・インピーダンス・アンプ全体の出力雑音電圧を求めます。

OPA656 のデータシートより,入力換算雑音電流 $I_n$ は, $1.3fA/\sqrt{Hz}$ 程度と考えることができます.図 1 のトランス・インピーダンス・アンプの-3dBしゃ断周波数fcは,1.6MHzですので,この雑音電流に起因する出力雑音電圧は,以下のように計算することができます.

$$V_{n\_current} = I_n \times R_2 \times \sqrt{\frac{\pi}{2} fc} = 1.3 \times 10^{-15} \times 100 \times 10^3 \times \sqrt{\frac{\pi}{2} \times 1.6 \times 10^6} \approx 0.2 \mu V_{RMS}$$

この雑音は、非常に小さいため、ほとんど無視して良いと言えます. 最後に、抵抗から発生する熱雑音を求めます.

$$V_{n_{-}R} = \sqrt{4kTR_2} \times \sqrt{\frac{\pi}{2}fc}$$

ここで、 $k: ボルツマン定数(1.38 \times 10^{-23})$ 、T: 絶対温度(300K) とすると、次のように求まります.

$$V_{n_{-}R} = \sqrt{4 \times 1.38 \times 10^{-23} \times 300 \times 100 \times 10^{3}} \times \sqrt{\frac{\pi}{2} \times 1.6 \times 10^{6}} \approx 65 \mu V_{RMS}$$

入力換算雑音電流に起因する雑音と抵抗による熱雑音,および,2.3での計算結果: $554 \mu V$ を合成すると,

$$V_{n\_total} = \sqrt{\left(554 \times 10^{-6}\right)^2 + \left(0.2 \times 10^{-6}\right)^2 + \left(65 \times 10^{-6}\right)^2} \approx 558 \mu V_{RMS}$$

となります.これが、図1のトランス・インピーダンス・アンプの実効値出力雑音電圧です.

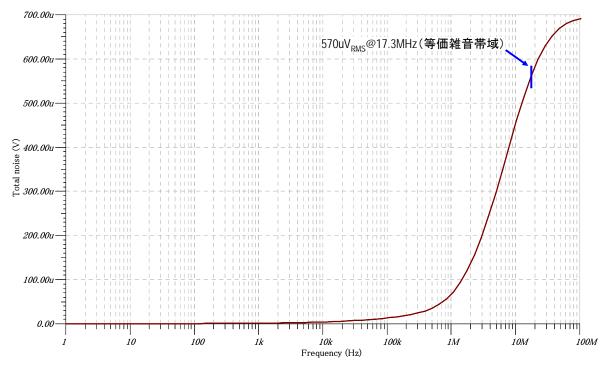

### 2.5 シミュレーションによる確認

トランス・インピーダンス・アンプの出力雑音電圧を手計算により求めることは、どの回路定数が全体の雑音性能に大きく寄与するかを考える上では有効です。しかし、実際の回路設計においては煩雑な計算です。

そこで、現在の設計手法としては、回路シミュレータにより検証を行なうのがもっとも容易であると言えます。図 4 に Design Soft 社の電子回路シミュレータ TINA によりシミュレーションした結果を示します。

図4 図1の回路の実効値出力雑音電圧のシミュレーション結果

図 4 からわかるように、手計算の結果とほぼ一致しています。若干の違いは、OPA656 から発生する分配雑音の影響が考えられます。

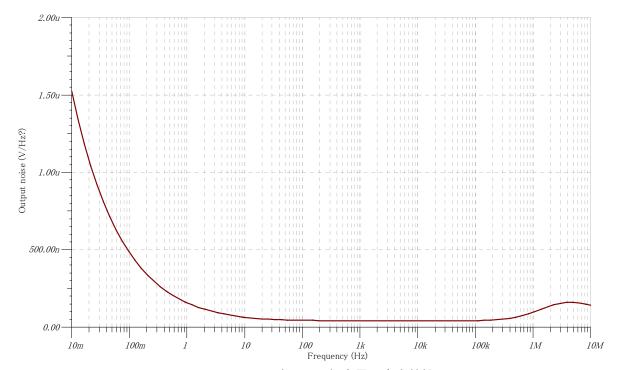

参考までに、図5に、出力雑音電圧密度のグラフを示しました.このようなグラフを容易に得ることができるのも回路シミュレータの利点と言えるでしょう.

図5 図1の回路の出力雑音電圧密度特性

# 3. 安定性の確認

### 3.1 シミュレーション方法

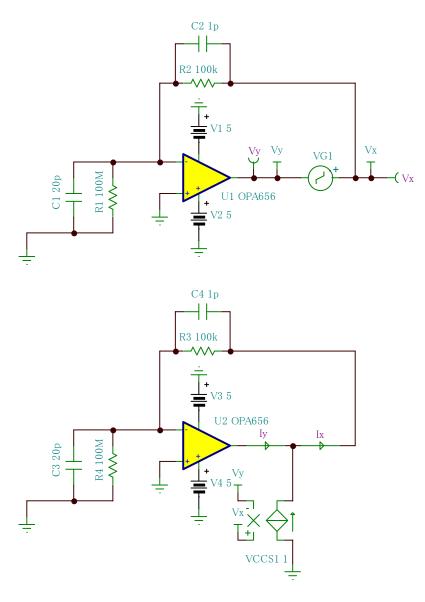

第1章において、位相補償容量 $C_2$ を計算する簡単な式を示しました。ここでは、その式によって 算出された値が、回路の安定性を確保する上で妥当な数値であることを回路シミュレータによって確 認します。シミュレーション回路は、図6のとおりです。ループ・ゲインの周波数特性をシミュレーションするための方法としては、ミドルブルック法を使用しました。

なお、負帰還安定性の基礎やミドルブルック法についての解説は、参考文献(4)を参照してください.

図6 シミュレーション回路

#### 3.2 シミュレーション結果

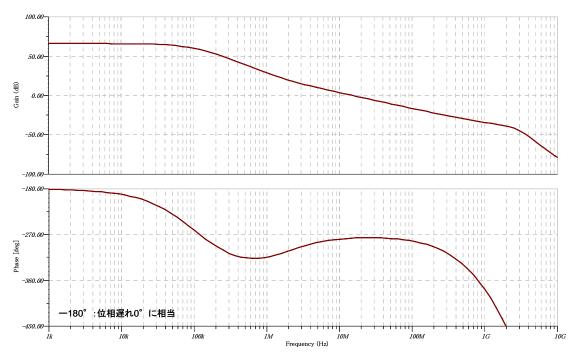

図 6 の回路において、 $C_2(=C_4)$ が位相補償容量となります.この値を 1pFとしたときのループ・ゲイン特性のシミュレーション結果は、図 7 のようになりました.

図7 C<sub>2</sub>=C<sub>4</sub>=1pFのときのシミュレーション結果(位相余裕:83.02°, ゲイン余裕:32.86dB)

位相余裕は、83.02°であり、ゲイン余裕も32dB以上と、安定性確保のために最低限必要な10dB以上となっているため、この回路はきわめて安定であると言えます。つぎに、位相補償容量を計算値そのものである $C_2(=C_4)=0.526$ pFに変更してシミュレーションしてみます。

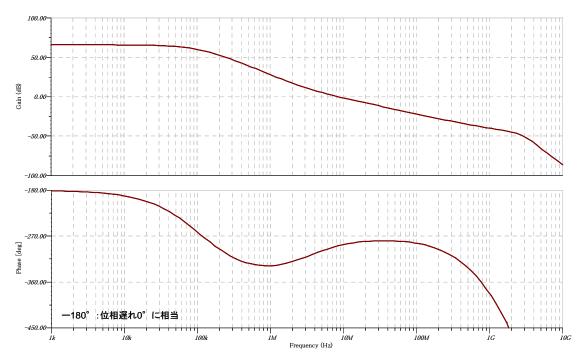

図 8 C<sub>2</sub>(=C<sub>4</sub>)を 0.526pFに変更(位相余裕:71.14°, ゲイン余裕:38.06dB)

シミュレーション結果は図 8 のとおりです. 位相余裕は 71.14° となっています. 周波数特性にピークの生じない臨界制動条件は, 位相余裕が 72° 程度のときであると考えられるため, 第 1 章で紹介した計算式は, 適切な位相補償容量を得るために有用な式であることがわかります.

## 4. まとめ

本アプリケーション・レポートは、初めてトランス・インピーダンス・アンプを設計する人に必要と思われる技術事項について、簡単にまとめたものです。現在では、種々の回路シミュレータが存在しますので、回路動作の基本を理解した後は回路シミュレータによって諸特性を確認するのがもっとも効率的であり、間違いも起こしにくいと言えます。

最後に、位相補償容量を決定する参考文献(1)の計算式についての妥当性を回路シミュレーションによって検討してみました。その際に使用した「ミドルブルック法」について、具体的な実行方法を知りたい方は、別途、参考文献(4)を参照してください。

# 5. 参考文献

- (1) Michael Steffes : Control frequency response and noise in broadband, photodetector, transimpedance amplifiers, EDN, July 4, 1996

- (2) Noise Analysis of FET Transimpedance Amplifiers, Application Bulletin, SBOA060, 1994, Texas Instruments Inc.

- (3) OPA380 Data Sheet, SBOS291F, 2005, Texas Instruments Inc.

- (4)川田章弘:電子回路シミュレータTINAを使用した負帰還安定性の検討,JAJA097,日本テキサス・インスツルメンツ

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して項き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright 2008, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

# 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラツフ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置 類の接地等の静電気帯電防止措置は、常に管理されその機能が確認 されていること。

#### 2. 温·湿度環境

温度:0~40℃、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

- 4. 機械的衝撃

- 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

- 5. 熱衝撃

- はんだ付け時は、最低限260℃以上の高混状態に、10秒以上さら さないこと。(個別推奨条件がある時はそれに従うこと。)

- 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイフのフラックスは除く。)

以上