参考文献

UCC28070A ZHCS779B - MARCH 2012 - REVISED DECEMBER 2023

# UCC28070A 扩展频率范围(10kHz 至 300kHz),交错式连续导通模式 PFC 控 制器

# 1 特性

- 具有固有电流匹配的交错平均电流模式 PWM 控制

- 先进的电流合成器电流检测可实现卓越的效率

- 具有内部量化电压前馈校正的高线性乘法器输出, 用于近单位 PF

- 扩展范围可编程频率 (10kHz 至 300kHz)

- 可编程最大占空比钳位

- 可编程频率抖动速率和幅度,可增强 EMI 降低水平

- 幅度: 3kHz 至 30kHz

- 速率: 高达 30kHz

- 外部时钟同步功能

- 通过电压放大器输出电流的压摆率校正增强了负载 和线路瞬态响应

- 可编程峰值电流限制

- 辅助电源 UVLO、过压保护、开环检测和 PFC 启用

- 外部 PFC 禁用接口

- · VSENSE 和 VINAC 引脚上的开路保护

- 可编程软启动

# 2 应用

- 空调和白色家电

- 具有 IGBT 电源开关的 PFC 应用

- 高效服务器和台式机电源

- 大屏幕电视和显示器

- 通信整流器

- 工业设备

### 3 说明

UCC28070A 器件是 UCC28070 器件的扩展频率范围 衍生产品,能够在大功率应用中基于 IGBT 功率开关的 PFC 转换器所需的低开关频率下工作。

UCC28070A 器件能够在 10kHz 至 300kHz 的频率范 围内运行,相比最小运行频率被限制为 30kHz 的 UCC28070 器件,扩展了运行范围。UCC28070A 器 件也提供了 UCC28070 器件的所有其他特性和优势。 180° 异相交错操作可大幅减少输入和输出端的波纹电 流,这使得器件能够以更低的成本轻松滤除传导电磁干 扰 (EMI)。

与 UCC28070 器件一样, UCC28070A 器件也具有多 项创新功能,包括电流合成和量化电压前馈,以促进 PF、效率、THD 和瞬态响应方面的性能增强。频率抖 动、时钟同步和压摆率增强等功能进一步扩大了性能增 强的潜力。UCC28070A 器件中也提供了 UCC28070 器件中的所有保护功能,例如输出过压检测、可编程峰 值电流限制、欠压锁定和开环保护。

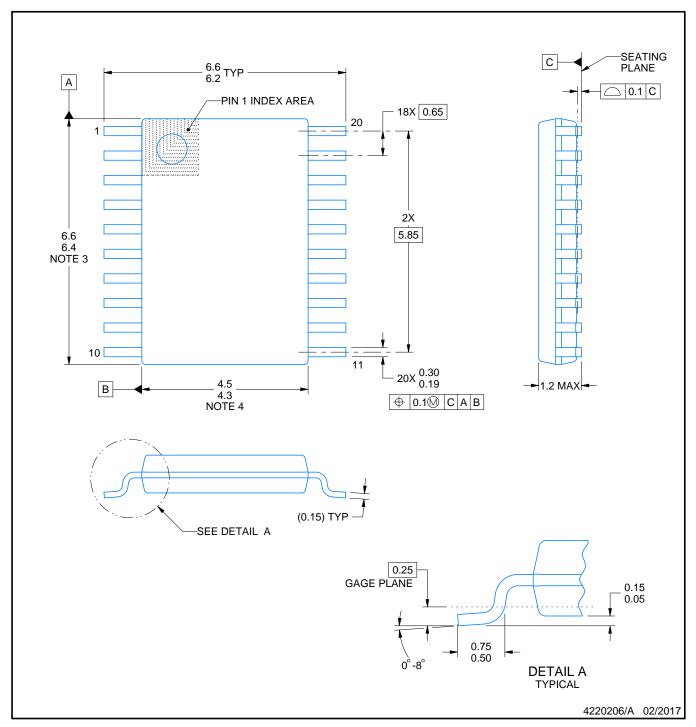

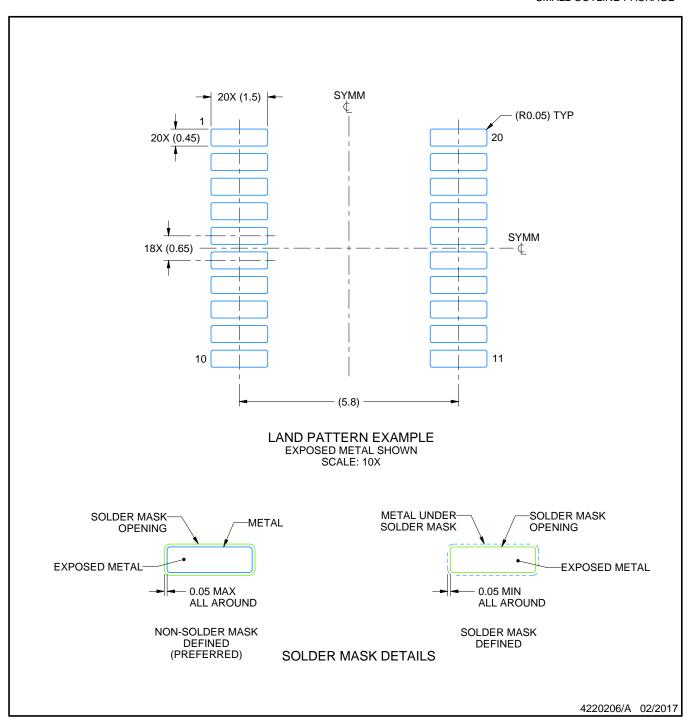

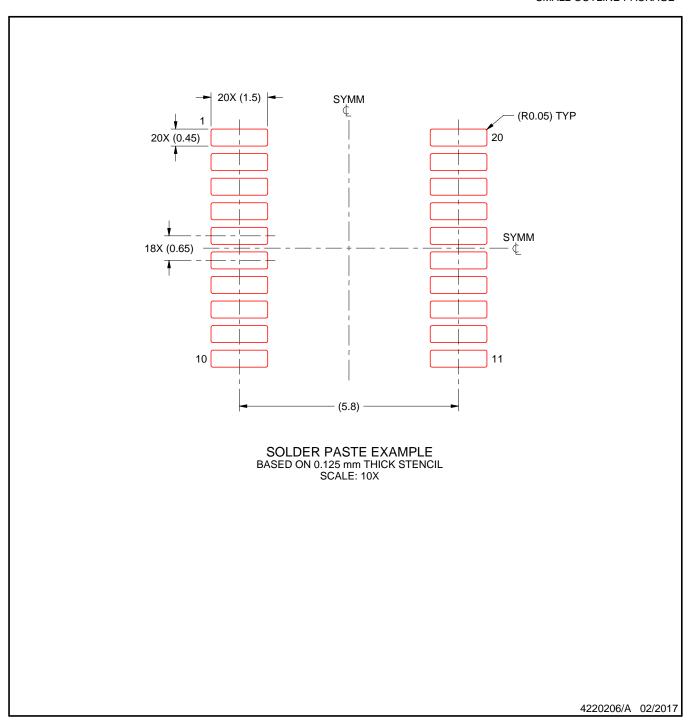

# 器件信息

| 器件型号      | 封装         | 封装尺寸 ( 标称值 )    |

|-----------|------------|-----------------|

| UCC28070A | TSSOP (20) | 6.50mm x 4.40mm |

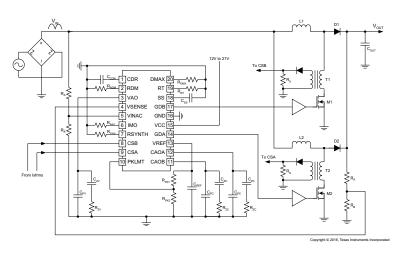

简化版应用示意图

# **Table of Contents**

| 1 特性                                  |

|---------------------------------------|

| 2 应用1                                 |

| 3 说明1                                 |

| 4 Pin Configuration and Functions3    |

| 4.1 Pin Functions4                    |

| 5 Specifications5                     |

| 5.1 Absolute Maximum Ratings5         |

| 5.2 ESD Ratings5                      |

| 5.3 Recommended Operating Conditions6 |

| 5.4 Thermal Information6              |

| 5.5 Electrical Characteristics7       |

| 5.6 Typical Characteristics11         |

| 6 Detailed Description14              |

| 6.1 Overview14                        |

| 6.2 Functional Block Diagram15        |

| 6.3 Feature Description                 | 16 |

|-----------------------------------------|----|

| 6.4 Device Functional Modes             | 32 |

| 7 Application and Implementation        | 33 |

| 7.1 Application Information             | 33 |

| 7.2 Typical Application                 | 33 |

| 7.3 Power Supply Recommendations        | 42 |

| 7.4 Layout                              | 43 |

| 8 Device and Documentation Support      | 44 |

| 8.1 Documentation Support               | 44 |

| 8.2 Community Resources                 | 44 |

| 8.3 Trademarks                          | 44 |

| 9 Revision History                      | 44 |

| 10 Mechanical, Packaging, and Orderable |    |

| Information                             | 45 |

|                                         |    |

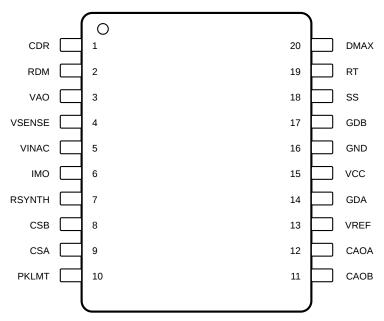

# **4 Pin Configuration and Functions**

图 4-1. PW Packages 20-Pin TSSOP Top View

# **4.1 Pin Functions**

| PIN |               |     | DECORPORTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|-----|---------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NO. | NAME          | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 1   | CDR           | I   | Dither Rate Capacitor. Frequency-dithering timing pin. An external capacitor to GND programs the rate of oscillator dither. Connect the CDR pin to the VREF pin to disable dithering.                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 2   | RDM<br>(SYNC) | I   | Dither Magnitude Resistor. Frequency-dithering magnitude and external synchronization pin. An external resistor to GND programs the magnitude of oscillator frequency dither. When frequency dithering is disabled (CDR > 5 V), the internal master clock synchronizes to positive edges presented on the RDM pin. Connect RDM to GND with a zero-ohm resistance when dithering is disabled and synchronization is not desired.                                                                                  |  |  |  |  |  |

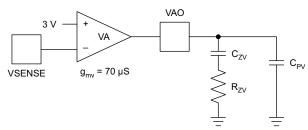

| 3   | VAO           | 0   | Voltage Amplifier Output. Output of transconductance voltage error amplifier. Internally connected to the multiplier input and the zero-power comparator. Connect the voltage regulation loop compensation components between this pin and GND.                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 4   | VSENSE        | I   | put Voltage Sense. Internally connected to the inverting input of the transconductance voltage error oblifier in addition to the positive terminal of the current synthesis difference amplifier. Also connected to P, PFC enable, and slew-rate comparators. Connect to PFC output with a resistor-divider network.                                                                                                                                                                                             |  |  |  |  |  |

| 5   | VINAC         | I   | Scaled AC Line Input Voltage. Internally connected to the multiplier and negative terminal of the current synthesis difference amplifier. Connect a resistor-divider network between V <sub>IN</sub> , VINAC, and GND identical to the PFC output divider network connected at VSENSE.                                                                                                                                                                                                                           |  |  |  |  |  |

| 6   | IMO           | 0   | Multiplier Current Output. Connect a resistor between this pin and GND to set the multiplier gain.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 7   | RSYNTH        | I   | Current Synthesis Down-Slope Programming. Connect a resistor between this pin and GND to set the magnitude of the current synthesizer down-slope. Connecting RSYNTH to VREF disables current synthesis and connect CSA and CSB directly to their respective current amplifiers.                                                                                                                                                                                                                                  |  |  |  |  |  |

| 8   | CSB           | I   | Phase B Current Sense Input. During the ON-time of GDB, CSB is internally connected to the inverting input of phase B current amplifier through the current synthesis stage.                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 9   | CSA           | I   | Phase A Current Sense Input. During the ON-time of GDA, CSA is internally connected to the inverting input of phase A current amplifier through the current synthesis stage.                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 10  | PKLMT         | I   | Peak Current Limit Programming. Connect a resistor-divider network between VREF and this pin to set the voltage threshold of the cycle-by-cycle peak current limiting comparators. Allows adjustment for desired $\Delta I_{LB}$ .                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 11  | CAOB          | 0   | Phase B Current Amplifier Output. Output of phase B transconductance current amplifier. Internally connected to the inverting input of phase B PWM comparator for trailing-edge modulation. Connect the current regulation loop compensation components between this pin and GND.                                                                                                                                                                                                                                |  |  |  |  |  |

| 12  | CAOA          | 0   | Phase A Current Amplifier Output. Output of phase A transconductance current amplifier. Internally connected to the inverting input of phase A PWM comparator for trailing-edge modulation. Connect the current regulation loop compensation components between this pin and GND.                                                                                                                                                                                                                                |  |  |  |  |  |

| 13  | VREF          | 0   | 6-V Reference Voltage and Internal Bias Voltage. Connect a 0.1- μ F ceramic bypass capacitor as close as possible to this pin and GND.                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 14  | GDA           | 0   | Phase A Gate Drive. This limited-current output is intended to connect to a separate gate-drive device suitable for driving the phase A switching component(s). The output voltage is typically clamped to 13.5 V.                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 15  | VCC           | ı   | Bias Voltage Input. Connect a 0.1- μ F ceramic bypass capacitor as close as possible to this pin and GND.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 16  | GND           | I/O | Device Ground Reference. Connect all compensation and programming resistor and capacitor networks to this pin. Connect this pin to the system through a separate trace for high-current noise isolation.                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 17  | GDB           | 0   | Phase B Gate Drive. This limited-current output is intended to connect to a separate gate-drive device suitable for driving the phase B switching component(s). The output voltage is typically clamped to 13.5 V.                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 18  | SS            | I   | Soft-Start and External Fault Interface. Connect a capacitor to GND on this pin to set the soft-start slew rate based on an internally-fixed, 10- $\mu$ A current source. The regulation reference voltage for VSENSE is clamped to V <sub>SS</sub> until V <sub>SS</sub> exceeds 3 V. Upon recovery from certain fault conditions, a 1-mA current source is present at the SS pin until the SS voltage equals the VSENSE voltage. Pulling the SS pin below 0.6 V immediately disables both GDA and GDB outputs. |  |  |  |  |  |

| 19  | RT            | -   | Timing Resistor. Oscillator frequency programming pin. A resistor to GND sets the running frequency of the internal oscillator.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 20  | DMAX          | I   | Maximum Duty-Cycle Resistor. Maximum PWM duty-cycle programming pin. A resistor to GND sets the PWM maximum duty-cycle based on the ratio of $R_{\text{DMX}}$ / $R_{\text{RT}}$ .                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

# **5 Specifications**

# 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1) (2) (3) (4)

|                                       |                                                                                    | MIN   | MAX                   | UNIT   |  |

|---------------------------------------|------------------------------------------------------------------------------------|-------|-----------------------|--------|--|

| Supply voltage                        | VCC                                                                                |       | 22                    | V      |  |

| Supply current, I <sub>VCC</sub>      |                                                                                    |       | 20                    | mA     |  |

| Gate drive current - continuous       | GDA, GDB                                                                           |       | ±0.25                 | Α      |  |

| Gate drive current - pulsed           | GDA, GDB                                                                           |       | ±0.75                 | Α      |  |

|                                       | GDA, GDB                                                                           | - 0.5 | V <sub>CC</sub> + 0.3 |        |  |

| Voltage                               | DMAX, RDM, RT, CDR, VINAC, VSENSE, SS, VAO, IMO, CSA, CSB, CAOA, CAOB, PKLMT, VREF | - 0.5 | 7                     | V      |  |

| Current                               | RT, DMAX, RDM, RSYNTH                                                              |       | - 0.5                 | mA     |  |

| Current                               | VREF, VAO, CAOA, CAOB, IMO                                                         |       | 10                    | l IIIA |  |

| Lead temperature (10 seconds)         |                                                                                    |       | 260                   | °C     |  |

| Operating junction temperature, T     | J                                                                                  | - 40  | 125                   | °C     |  |

| Storage temperature, T <sub>stg</sub> |                                                                                    | - 65  | 150                   | °C     |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under #5.3. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 5.2 ESD Ratings

|                    |                                    |                                                                                | VALUE | UNIT |

|--------------------|------------------------------------|--------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge            | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | 2000  | \/   |

| V <sub>(ESD)</sub> | Charged-device model (CDM), per JE | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | 500   | V    |

<sup>2)</sup> All voltages are with respect to GND.

<sup>(3)</sup> All currents are positive into the terminal, negative out of the terminal.

<sup>(4)</sup> In normal use, terminals GDA and GDB are connected to an external gate driver and are internally limited in output current.

<sup>(1)</sup> JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

# **5.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                  |                                                    | MIN                   | MAX | UNIT |

|------------------|----------------------------------------------------|-----------------------|-----|------|

|                  | Input voltage (from a low-impedance source) to VCC | V <sub>UVLO</sub> + 1 | 21  | V    |

|                  | Load current on VREF                               |                       | 2   | mA   |

|                  | Input voltage to VINAC                             | 0                     | 3   | V    |

|                  | Voltage on IMO                                     | 0                     | 3.3 | V    |

|                  | Voltage on CSA, CSB, PKLMT                         | 0                     | 3.6 | V    |

| R <sub>SYN</sub> | RSYNTH resistance                                  | 15                    | 750 | kΩ   |

| R <sub>RDM</sub> | RDM resistance                                     | 30                    | 330 | kΩ   |

# **5.4 Thermal Information**

|                        | THERMAL METRIC <sup>(1)</sup>                | UCC28070A<br>PW (TSSOP)<br>20 PINS | UNIT |

|------------------------|----------------------------------------------|------------------------------------|------|

| R <sub>0 JA</sub>      | Junction-to-ambient thermal resistance       | 99.9                               | °C/W |

| R <sub>θ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 34.1                               | °C/W |

| R <sub>0</sub> JB      | Junction-to-board thermal resistance         | 50.8                               | °C/W |

| ψJT                    | Junction-to-top characterization parameter   | 1.9                                | °C/W |

| <sup>ф</sup> ЈВ        | Junction-to-board characterization parameter | 50.3                               | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# **5.5 Electrical Characteristics**

$T_{J}=T_{A}=-40^{\circ}C~to~125^{\circ}C,~V_{CC}=12V,~GND=0V,~R_{RT}=75k\Omega,~R_{DMX}=68.1k\Omega,~R_{RDM}=R_{SYN}=100k\Omega,~C_{CDR}=2.2nF,~C_{SS}=C_{VREF}=0.1~\mu~F,~C_{VCC}=1~\mu~F,~I_{VREF}=0mA~(unless~otherwise~noted)$

|                                       | PARAMETER                                    |                   | TEST CONDITIONS                                                                            | MIN  | TYP   | MAX   | UNIT |

|---------------------------------------|----------------------------------------------|-------------------|--------------------------------------------------------------------------------------------|------|-------|-------|------|

| BIAS SUPP                             | LY                                           |                   |                                                                                            |      |       | '     |      |

| V <sub>CC(SHUNT)</sub>                | V <sub>CC</sub> shunt voltage <sup>(1)</sup> |                   | I <sub>VCC</sub> = 10mA                                                                    | 23   | 25    | 27    | V    |

|                                       |                                              | Disabled          | V <sub>VSENSE</sub> = 0V                                                                   |      | 7     |       | mΛ   |

|                                       | 0 1                                          | Enabled           | V <sub>VSENSE</sub> = 3V (switching)                                                       |      | 9     | 12    | mA   |

| I <sub>VCC</sub>                      | Supply current                               |                   | V <sub>CC</sub> = 7V                                                                       |      |       | 200   | μΑ   |

|                                       |                                              | UVLO              | V <sub>CC</sub> = 9V                                                                       |      | 4     | 6     | mA   |

| .,                                    | UVLO turnon thresho                          | old               | Measured at VCC (rising)                                                                   | 9.8  | 10.2  | 10.6  | V    |

| $V_{\text{UVLO}}$                     | UVLO hysteresis                              |                   | Measured at VCC (falling)                                                                  |      | 1     |       | V    |

|                                       | VREF enable thresho                          | old               | Measured at VCC (rising)                                                                   | 7.5  | 8     | 8.5   | V    |

| LINEAR RE                             | GULATOR                                      |                   | , ,,                                                                                       |      |       |       |      |

|                                       |                                              | No load           | I <sub>VREF</sub> = 0mA                                                                    | 5.82 | 6     | 6.18  | V    |

|                                       |                                              |                   | Measured as the change in V <sub>VREF</sub>                                                |      |       |       |      |

| $V_{VREF}$                            | Reference voltage                            | Load rejection    | $(I_{VREF} = 0 \text{mA} \text{ and } -2 \text{mA})$                                       | - 12 |       | 12    | \    |

|                                       |                                              | Line rejection    | Measured as the change in V <sub>VREF</sub>                                                | - 12 |       | 12    | m۱   |

|                                       |                                              | Line rejection    | $(V_{CC}$ = 11V and 20V, $I_{VREF}$ = 0 $\mu$ A)                                           | - 12 |       | 12    |      |

| PFC ENABL                             | LE                                           |                   |                                                                                            |      |       |       |      |

| V                                     | Enable threshold                             |                   | Measured at VSENSE (rising)                                                                | 0.65 | 0.75  | 0.85  | V    |

| V <sub>EN</sub>                       | Enable hysteresis                            |                   |                                                                                            |      | 0.15  |       | v    |

| EXTERNAL                              | PFC DISABLE                                  |                   |                                                                                            |      |       | '     |      |

|                                       | Disable threshold                            |                   | Measured at SS (falling)                                                                   | 0.5  | 0.6   |       | V    |

|                                       | Hysteresis                                   |                   | V <sub>VSENSE</sub> > 0.85V                                                                |      | 0.15  |       | V    |

| OSCILLATO                             | DR .                                         |                   |                                                                                            |      |       |       |      |

|                                       | Output phase shift                           |                   | Measured between GDA and GDB                                                               | 179  | 180   | 181   | 0    |

| V <sub>DMAX</sub> , V <sub>RT</sub> , | Timing regulation volt                       | ages              | Measured at DMAX, RT, and RDM                                                              | 2.91 | 3     | 3.09  | V    |

|                                       |                                              |                   | $R_{RT}$ = 750kΩ, $R_{DMX}$ = 681kΩ, $V_{RDM}$ = 0V, $V_{CDR}$ = 6V                        | 9.75 | 10.25 | 10.75 |      |

| $f_{PWM}$                             | PWM switching frequency                      |                   | $R_{RT}$ = 75kΩ, $R_{DMX}$ = 68.1kΩ,<br>$V_{RDM}$ = 0V, $V_{CDR}$ = 6V                     | 95   | 100   | 105   | kH:  |

|                                       |                                              |                   | $R_{RT}$ = 24.9k $\Omega$ , $R_{DMX}$ = 22.6k $\Omega$ , $V_{RDM}$ = 0V, $V_{CDR}$ = 6V    | 270  | 290   | 330   |      |

| D <sub>MAX</sub>                      | Duty-cycle clamp                             |                   | $R_{RT}$ = 75k $\Omega$ , $R_{DMX}$ = 68.1k $\Omega$ ,<br>$V_{RDM}$ = 0V, $V_{CDR}$ = 6V   | 92%  | 95%   | 98%   |      |

|                                       | Minimum programma                            | ble OFF-time      | $R_{RT}$ = 24.9k $\Omega$ , $R_{DMX}$ = 22.6k $\Omega$ ,<br>$V_{RDM}$ = 0V, $V_{CDR}$ = 6V | 50   | 150   | 250   | ns   |

|                                       | Frequency dithering r                        | magnitude change  | $R_{RDM} = 316k\Omega$ , $R_{RT} = 75k\Omega$                                              | 2    | 3     | 4     |      |

| f <sub>DM</sub>                       | in f <sub>PWM</sub>                          |                   | $R_{RDM}$ = 31.6kΩ, $R_{RT}$ = 24.9kΩ                                                      | 24   | 30    | 36    | kH:  |

|                                       | Frequency dithering                          | rate of change in | $C_{CDR} = 2.2 \text{nF}, R_{RDM} = 100 \text{k}\Omega$                                    |      | 3     |       |      |

|                                       | Frequency dithering rate of change in        |                   | $C_{CDR} = 0.3 \text{nF}, R_{RDM} = 100 \text{k}\Omega$                                    |      | 20    |       | kH   |

| f <sub>DR</sub>                       | t <sub>PWM</sub>                             |                   |                                                                                            |      |       |       |      |

| f <sub>DR</sub>                       | Dither rate current                          |                   | Measured at CDR (sink and source)                                                          |      | ±10   |       | μ/   |

$T_{J} = T_{A} = -40^{\circ}\text{C to } 125^{\circ}\text{C}, \ V_{CC} = 12\text{V}, \ \text{GND} = 0\text{V}, \ R_{RT} = 75\text{k}\Omega, \ R_{DMX} = 68.1\text{k}\Omega, \ R_{RDM} = R_{SYN} = 100\text{k}\Omega, \ C_{CDR} = 2.2\text{nF}, \ C_{SS} = C_{VREF} = 0.1\ \mu \text{ F}, \ C_{VCC} = 1\ \mu \text{ F}, \ I_{VREF} = 0\text{mA} \ \text{(unless otherwise noted)}$

|                  | PARAMETER                                               | TEST CONDITIONS                                                              | MIN  | TYP   | MAX      | UNIT       |

|------------------|---------------------------------------------------------|------------------------------------------------------------------------------|------|-------|----------|------------|

| CLOCK            | SYNCHRONIZATION                                         |                                                                              |      |       |          |            |

| V <sub>CDR</sub> | SYNC enable threshold                                   | Measured at CDR (rising)                                                     |      | 5     | 5.25     | V          |

|                  | SYNC propagation delay                                  | V <sub>CDR</sub> = 6V, measured from RDM (rising) to GDx (rising)            |      | 50    | 100      | ns         |

|                  | SYNC threshold (rising)                                 | V <sub>CDR</sub> = 6V, measured at RDM                                       |      | 1.2   | 1.5      | V          |

|                  | SYNC threshold (falling)                                | V <sub>CDR</sub> = 6V, measured at RDM                                       | 0.4  | 0.7   |          | V          |

|                  | SYNC pulses                                             | Positive pulse width                                                         | 0.2  |       |          | μs         |

|                  | Maximum duty cycle <sup>(2)</sup>                       |                                                                              |      | 50%   |          |            |

| VOLTAG           | E AMPLIFIER                                             |                                                                              |      |       | <u> </u> |            |

|                  | VSENSE voltage                                          | In regulation, T <sub>A</sub> = 25°C                                         | 2.97 | 3     | 3.03     | V          |

|                  | VSENSE voltage                                          | In regulation                                                                | 2.94 | 3     | 3.06     | V          |

|                  | VSENSE input bias current                               | In regulation                                                                |      | 250   | 500      | nA         |

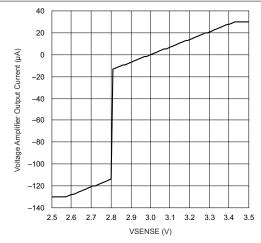

|                  | VAO high voltage                                        | V <sub>VSENSE</sub> = 2.9V                                                   | 4.8  | 5     | 5.2      | V          |

|                  | VAO low voltage                                         | V <sub>VSENSE</sub> = 3.1V                                                   |      | 0.05  | 0.5      | V          |

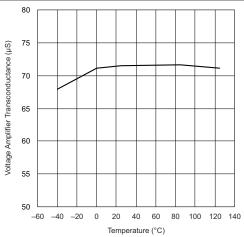

| 9м∨              | VAO transconductance                                    | V <sub>VSENSE</sub> = 2.8V to 3.2V, V <sub>VAO</sub> = 3V                    |      | 70    |          | μS         |

|                  | VAO sink current, overdriven limit                      | V <sub>VSENSE</sub> = 3.5V, V <sub>VAO</sub> = 3V                            |      | 30    |          | μА         |

|                  | VAO source current, overdriven                          | V <sub>VSENSE</sub> = 2.5V, V <sub>VAO</sub> = 3V, SS = 3V                   |      | - 30  |          | μ <b>A</b> |

|                  | VAO source current, overdriven limit + I <sub>SRC</sub> | V <sub>VSENSE</sub> = 2.5V, V <sub>VAO</sub> = 3V                            |      | - 130 |          | μ <b>А</b> |

|                  | Slew-rate correction threshold                          | Measured as V <sub>VSENSE</sub> (falling) / V <sub>VSENSE</sub> (regulation) | 92%  | 93%   | 95%      |            |

|                  | Slew-rate correction hysteresis                         | Measured at VSENSE (rising)                                                  |      | 3     | 9        | mV         |

| I <sub>SRC</sub> | Slew-rate correction current                            | Measured at VAO, in addition to VAO source current                           |      | - 100 |          | μ <b>А</b> |

|                  | Slew-rate correction enable threshold                   | Measured at SS (rising)                                                      |      | 4     |          | V          |

|                  | VAO discharge current                                   | V <sub>VSENSE</sub> = 0.5V, V <sub>VAO</sub> = 1V                            |      | 10    |          | μ <b>А</b> |

| SOFT ST          | ART                                                     |                                                                              |      |       | <u>'</u> |            |

| I <sub>SS</sub>  | SS source current                                       | V <sub>VSENSE</sub> = 0.9V, V <sub>SS</sub> = 1V                             |      | - 10  |          | μА         |

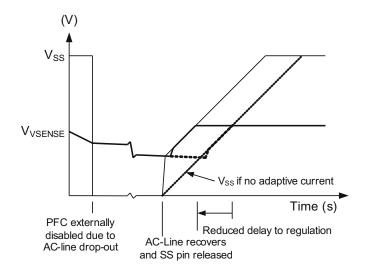

|                  | Adaptive source current                                 | V <sub>VSENSE</sub> = 2V, V <sub>SS</sub> = 1V                               |      | - 1.5 | - 2.5    | mA         |

|                  | Adaptive SS disable                                     | Measured as V <sub>VSENSE</sub> - V <sub>SS</sub>                            | - 30 | 0     | 30       | mV         |

|                  | SS sink current                                         | V <sub>VSENSE</sub> = 0.5V, V <sub>SS</sub> = 0.2V                           | 0.5  | 0.9   |          | mA         |

| OVERVO           | LTAGE                                                   |                                                                              | -    |       |          |            |

| V <sub>OVP</sub> | OVP threshold                                           | Measured as V <sub>VSENSE</sub> (rising) / V <sub>VSENSE</sub> (regulation)  | 104% | 106%  | 108%     |            |

|                  | OVP hysteresis                                          | Measured at VSENSE (falling)                                                 |      | 100   |          | mV         |

|                  | OVP propagation delay                                   | Measured between VSENSE (rising) and GDx (falling)                           |      | 0.2   | 0.3      | μs         |

www.ti.com.cn

$T_{J} = T_{A} = -40^{\circ}\text{C to } 125^{\circ}\text{C}, \ V_{CC} = 12\text{V}, \ \text{GND} = 0\text{V}, \ R_{RT} = 75\text{k}\Omega, \ R_{DMX} = 68.1\text{k}\Omega, \ R_{RDM} = R_{SYN} = 100\text{k}\Omega, \ C_{CDR} = 2.2\text{nF}, \ C_{SS} = C_{VREF} = 0.1\ \mu \text{ F}, \ C_{VCC} = 1\ \mu \text{ F}, \ I_{VREF} = 0\text{mA} \ \text{(unless otherwise noted)}$

|                     | PARAMETER                        | TEST CONDITIONS                                             | MIN   | TYP  | MAX  | UNIT       |

|---------------------|----------------------------------|-------------------------------------------------------------|-------|------|------|------------|

| ZERO-PO             | WER                              |                                                             |       |      |      |            |

| V <sub>ZPWR</sub>   | Zero-power detect threshold      | Measured at VAO (falling)                                   | 0.65  | 0.75 |      | V          |

|                     | Zero-power hysteresis            |                                                             |       | 0.15 |      | V          |

| MULTIPLII           | ER                               |                                                             |       |      | '    |            |

|                     |                                  | V <sub>VAO</sub> ≥ 1.5V, T <sub>A</sub> = 25°C              | 16    | 17   | 18   |            |

| k <b>–</b>          | Cain constant                    | V <sub>VAO</sub> = 1.2V, T <sub>A</sub> = 25°C              | 14.5  | 17   | 19.5 | ^          |

| K <sub>MULT</sub>   | Gain constant                    | V <sub>VAO</sub> ≥ 1.5V                                     | 15    | 17   | 19   | μA         |

|                     |                                  | V <sub>VAO</sub> = 1.2V                                     | 13    | 17   | 21   |            |

|                     |                                  | $V_{VINAC} = 0.9V_{PK}, V_{VAO} = 0.8V$                     | - 0.2 | 0    | 0.2  |            |

| I <sub>IMO</sub>    | Output current: zero             | V <sub>VINAC</sub> = 0V, V <sub>VAO</sub> = 5V              | - 0.2 | 0    | 0.2  | μA         |

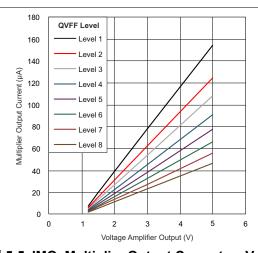

| QUANTIZE            | ED VOLTAGE FEEDFORWARD           |                                                             |       |      |      |            |

| V <sub>LVL1</sub>   | Level 1 threshold <sup>(3)</sup> | Measured at VINAC (rising)                                  | 0.6   | 0.7  | 8.0  | V          |

| V <sub>LVL2</sub>   | Level 2 threshold                | Measured at VINAC (rising)                                  |       | 1.0  |      | V          |

| V <sub>LVL3</sub>   | Level 3 threshold                | Measured at VINAC (rising)                                  |       | 1.2  |      | V          |

| V <sub>LVL4</sub>   | Level 4 threshold                | Measured at VINAC (rising)                                  |       | 1.4  |      | V          |

| V <sub>LVL5</sub>   | Level 5 threshold                | Measured at VINAC (rising)                                  |       | 1.65 |      | V          |

| V <sub>LVL6</sub>   | Level 6 threshold                | Measured at VINAC (rising)                                  |       | 1.95 |      | V          |

| V <sub>LVL7</sub>   | Level 7 threshold                | Measured at VINAC (rising)                                  |       | 2.25 |      | V          |

| V <sub>LVL8</sub>   | Level 8 threshold                | Measured at VINAC (rising)                                  |       | 2.6  |      | V          |

| CURRENT             | AMPLIFIERS                       |                                                             |       |      |      |            |

|                     | CAOx high voltage                |                                                             | 5.75  | 6    |      | V          |

|                     | CAOx low voltage                 |                                                             |       |      | 0.1  | V          |

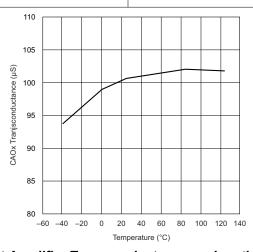

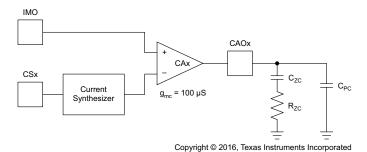

| 9мс                 | CAOx transconductance            |                                                             |       | 100  |      | μS         |

|                     | CAOx sink current, overdriven    |                                                             |       | 50   |      | μА         |

|                     | CAOx source current, overdriven  |                                                             |       | - 50 |      | μА         |

|                     | Input common mode range          |                                                             | 0     |      | 3.6  | V          |

|                     |                                  | V <sub>RSYNTH</sub> = 6V, T <sub>A</sub> = 25°C             | - 4   | - 8  | - 13 | .,         |

|                     | Input offset voltage             | V <sub>RSYNTH</sub> = 6V                                    | 0     | - 8  | - 20 | mV         |

|                     | Input offset voltage             |                                                             | 0     | - 8  | - 20 | mV         |

|                     | Phase mismatch                   | Measured as phase A input offset minus phase B input offset | - 12  | 0    | 12   | mV         |

|                     | CAOx pulldown current            | $V_{VSENSE} = 0.5V$ , $V_{CAOx} = 0.2V$                     | 0.5   | 0.9  |      | mA         |

| CURRENT             | SYNTHESIZER                      |                                                             |       |      |      |            |

| .,                  |                                  | V <sub>VSENSE</sub> = 3V, V <sub>VINAC</sub> = 0V           | 2.91  | 3    | 3.09 |            |

| V <sub>RSYNTH</sub> | Regulation voltage               | $V_{VSENSE} = 3V$ , $V_{VINAC} = 2.85V$                     | 0.1   | 0.15 | 0.2  | V          |

|                     | Synthesizer disable threshold    | Measured at RSYNTH (rising)                                 |       | 5    | 5.25 | V          |

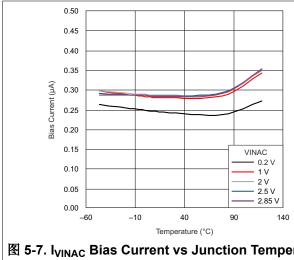

|                     | VINAC input bias current         |                                                             |       | 0.25 | 0.5  | μ <b>A</b> |

|                     | •                                |                                                             |       |      |      |            |

$T_{J}=T_{A}=-40^{\circ}\text{C to }125^{\circ}\text{C},\ V_{CC}=12\text{V},\ \text{GND}=0\text{V},\ R_{RT}=75\text{k}\Omega,\ R_{DMX}=68.1\text{k}\Omega,\ R_{RDM}=R_{SYN}=100\text{k}\Omega,\ C_{CDR}=2.2\text{nF},\ C_{SS}=C_{VRFF}=0.1\ \mu\text{ F},\ C_{VCC}=1\ \mu\text{ F},\ I_{VREF}=0\text{mA}\ \text{(unless otherwise noted)}$

|           | PARAMETER                               | TEST CONDITIONS                                                   | MIN  | TYP  | MAX  | UNIT  |

|-----------|-----------------------------------------|-------------------------------------------------------------------|------|------|------|-------|

| PEAK CU   | JRRENT LIMIT                            |                                                                   |      |      |      |       |

|           | Peak current limit threshold            | V <sub>PKLMT</sub> = 3.3V, measured at CSx (rising)               | 3.27 | 3.3  | 3.33 | V     |

|           | Peak current limit propagation delay    | Measured between CSx (rising) and GDx (falling) edges             |      | 60   | 100  | ns    |

| PWM RA    | MP                                      |                                                                   |      |      |      |       |

| $V_{RMP}$ | PWM ramp amplitude                      |                                                                   | 3.8  | 4    | 4.2  | V     |

|           | PWM ramp offset voltage                 | $T_A = 25^{\circ}C$ , $R_{RT} = 75k\Omega$                        | 0.65 | 0.7  |      | V     |

|           | PWM ramp offset temperature coefficient |                                                                   |      | - 2  |      | mV/°C |

| GATE DF   | RIVE                                    |                                                                   | -    |      |      |       |

|           | GDA, GDB output voltage, high, clamped  | V <sub>CC</sub> = 20V, C <sub>LOAD</sub> = 1nF                    | 11.5 | 13   | 15   | V     |

|           | GDA, GDB output voltage, high           | C <sub>LOAD</sub> = 1nF                                           | 10   | 10.5 |      | V     |

|           | GDA, GDB output voltage, low            | C <sub>LOAD</sub> = 1nF                                           |      | 0.2  | 0.3  | V     |

|           | Rise time GDx                           | 1V to 9V, C <sub>LOAD</sub> = 1nF                                 |      | 18   | 30   | ns    |

|           | Fall time GDx                           | 9V to 1V, C <sub>LOAD</sub> = 1nF                                 |      | 12   | 25   | ns    |

|           | GDA, GDB output voltage, UVLO           | V <sub>CC</sub> = 0V, I <sub>GDA</sub> , I <sub>GDB</sub> = 2.5mA |      | 0.7  | 2    | V     |

| THERMA    | L SHUTDOWN                              |                                                                   | •    |      |      |       |

|           | Thermal shutdown threshold              |                                                                   |      | 160  |      | °C    |

|           | Thermal shutdown recovery               |                                                                   |      | 140  |      | °C    |

<sup>(1)</sup> Excessive VCC input voltage or current damages the device. The VCC clamp does not protect the device from an unregulated bias supply. If an unregulated supply is used, TI recommends a series-connected fixed positive-voltage regulator such as a UA78L15A. See #5.1 for the limits on VCC voltage and current.

Product Folder Links: UCC28070A

<sup>(2)</sup> Due to the influence of the synchronization pulse-width on the programmability of the maximum PWM switching duty-cycle (D<sub>MAX</sub>), TI recommends to minimize the duty-cycle of the synchronization signal.

<sup>(3)</sup> The Level 1 threshold represents the *zero-crossing* detection threshold above which VINAC must rise to initiate a new input half-cycle, and below which VINAC must fall to terminate that half-cycle.

# 5.6 Typical Characteristics

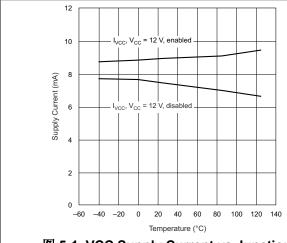

图 5-1. VCC Supply Current vs Junction Temperature

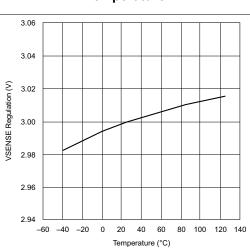

图 5-3. V<sub>VSENSE</sub> Regulation vs Junction Temperature

图 5-5. IMO, Multiplier Output Current vs V<sub>VAO</sub>

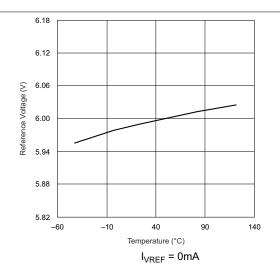

图 5-2. V<sub>VREF</sub> vs Junction Temperature

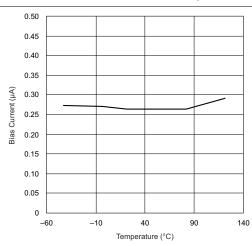

图 5-4. I<sub>VSENSE</sub> Bias Current vs Junction Temperature

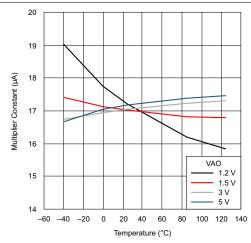

图 5-6. Multiplier Constant vs Junction Temperature

图 5-7. I<sub>VINAC</sub> Bias Current vs Junction Temperature

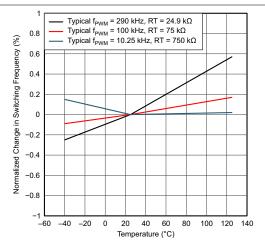

图 5-8. Switching Frequency vs Temperature

图 5-9. VAO, Voltage Amplifier Transconductance vs Junction Temperature

图 5-10. Voltage Amplifier Transfer Function vs **V<sub>VSENSE</sub>**

图 5-11. Current Amplifier Transconductance vs Junction Temperature

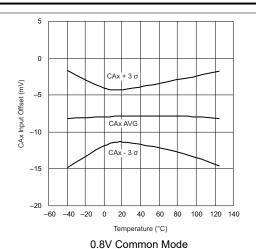

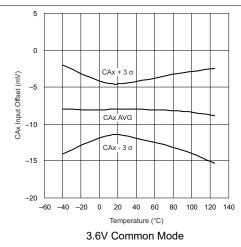

图 5-12. CAx Input Offset Voltage vs Junction Temperature

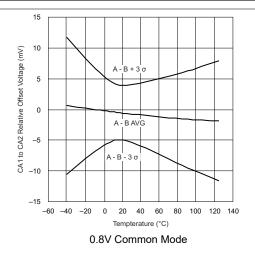

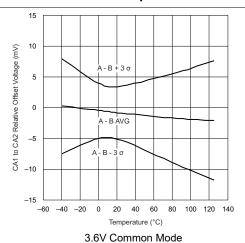

图 5-13. CA1 to CA2 Relative Offset vs Junction Temperature

图 5-14. CAx Input Offset Voltage vs Junction Temperature

图 5-15. CA1 to CA2 Relative Offset vs Junction Temperature

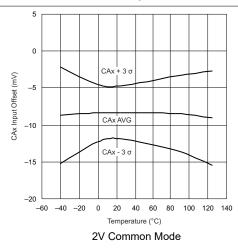

图 5-16. CAx Input Offset Voltage vs Junction Temperature

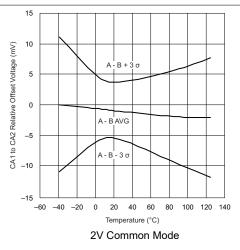

图 5-17. CA1 to CA2 Relative Offset vs Junction Temperature

# **6 Detailed Description**

# 6.1 Overview

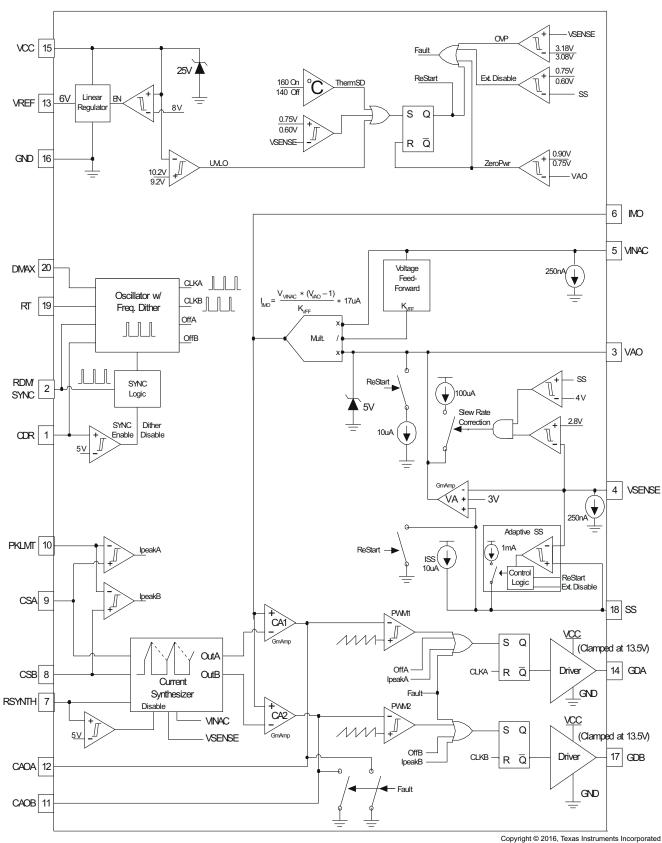

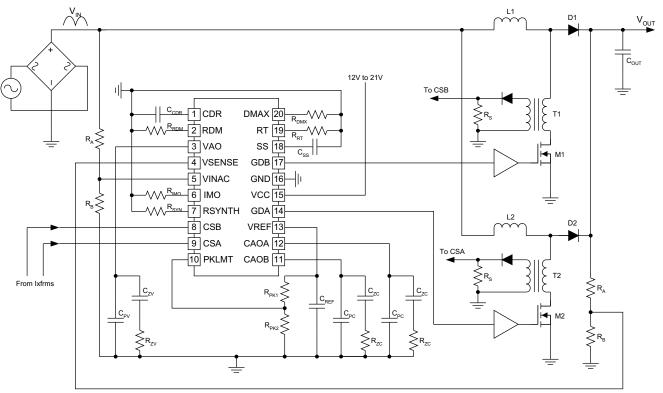

The UCC28070A power factor corrector IC controls two CCM (Continuous Conduction Mode) Boost PFC power stages operating 180° out of phase with each other. This interleaving action reduces the input and output ripple currents so that less EMI filtering is needed and allows operation at higher power levels than a non-interleaved solution.

The UCC28070A can operate over a wide range of frequencies, making it suitable for use with both MOSFET and IGBT power switches. Multiple UCC28070A controllers can be synchronized for use in higher-power applications where more than two interleaved power stages are needed.

This device is especially suited to high-performance, high-power, PFC applications where the use of Average Current Mode PWM control gives low THD.

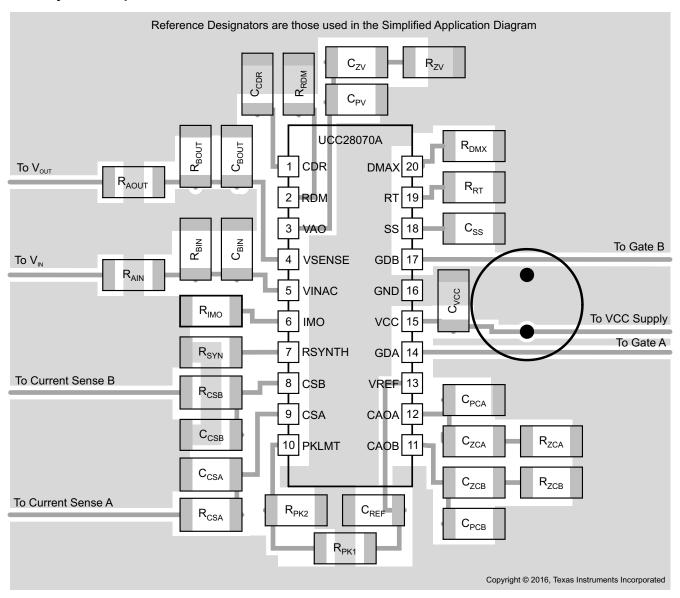

# 6.2 Functional Block Diagram

### **6.3 Feature Description**

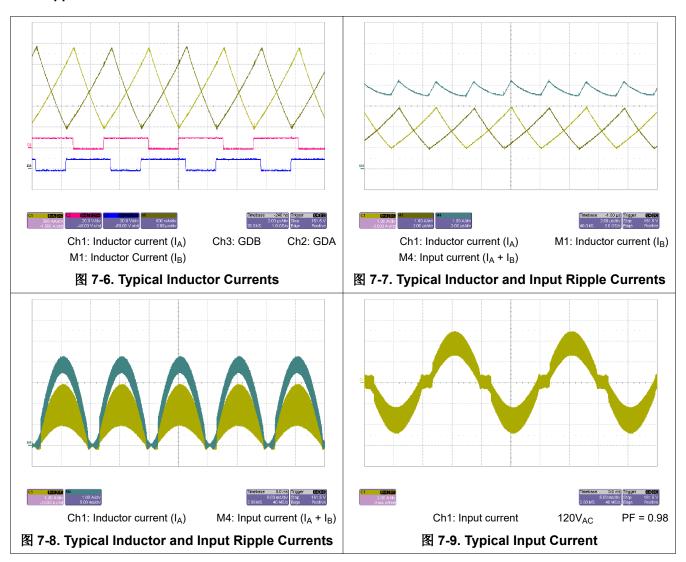

#### 6.3.1 Interleaving

One of the main benefits from the  $180^{\circ}$  interleaving of phases is significant reductions in the high-frequency ripple components of both the input current and the current into the output capacitor of the PFC preregulator. Compared to that of a single-phase PFC stage of equal power, the reduced ripple on the input current eases the burden of filtering conducted-EMI noise and helps reduce the EMI filter and  $C_{IN}$  sizes. Additionally, reduced high-frequency ripple current into the PFC output capacitor,  $C_{OUT}$ , helps to reduce its size and cost. Furthermore, with reduced ripple and average current in each phase, the boost inductor size can be smaller than in a single-phase design [3].

Ripple current reduction due to interleaving is often referred to as ripple cancellation, but strictly speaking, the peak-to-peak ripple is completely cancelled only at 50% duty-cycle in a 2-phase system. At duty-cycles other than 50%, ripple reduction occurs in the form of partial cancellation due to the superposition of the individual phase currents. Nevertheless, compared to the ripple currents of an equivalent single-phase PFC preregulator, those of a 2-phase interleaved design are extraordinarily smaller [3]. Independent of ripple cancellation, the frequency of the interleaved ripple, at both the input and output, is  $2 \times f_{PWM}$ .

At the PFC input, 180° interleaving reduces the peak-to-peak current-ripple amplitude to ½ or less of the ripple amplitude of the equivalent single-phase current.

At the PFC output, 180° interleaving reduces the rms value of the PFC-generated ripple current in the output capacitor by a factor of slightly more than  $\sqrt{2}$ , for PWM duty-cycles > 50%.

This can be seen in the following derivations, adapting the method by Erickson [4].

In a single-phase PFC preregulator, the total rms capacitor current contributed by the PFC stage at all duty-cycles can be shown to be approximated by:

$$i_{\text{CRMS1}_{\phi}} = \left(\frac{I_{\text{O}}}{\eta}\right) \sqrt{\left(\left(\frac{16 \times V_{\text{O}}}{3\pi \times V_{\text{M}}}\right) - \eta^{2}\right)}$$

(1)

#### where

- I<sub>O</sub> is the average PFC output load current

- V<sub>O</sub> is the average PFC output voltage

- V<sub>M</sub> is the peak of the input AC-line voltage

- η is the efficiency of the PFC stage at these conditions

In a dual-phase interleaved PFC preregulator, the total rms capacitor current contributed by the PFC stage for D > 50% can be shown to be approximated by:

$$i_{CRMS2\phi} = \left(\frac{I_O}{\eta}\right) \sqrt{\left(\left(\frac{16 \times V_O}{6\pi \times V_M}\right) - \eta^2\right)}$$

(2)

It can be seen that the quantity under the radical for  $i_{CRMS2\, \varphi}$  is slightly smaller than ½ of that under the radical for  $i_{CRMS1\, \varphi}$ . The rms currents shown contain both the low-frequency and the high-frequency components of the PFC output current. Interleaving reduces the high-frequency component, but not the low-frequency component.

#### 6.3.2 Programming the PWM Frequency and Maximum Duty-Cycle Clamp

The PWM frequency and maximum duty-cycle clamps for both GDx outputs of the UCC28070A are set through the selection of the resistors connected to the RT and DMAX pins, respectively. The selection of the RT resistor (R<sub>RT</sub>) directly sets the PWM frequency (f<sub>PWM</sub>).

$$R_{RT}(k\Omega) = \frac{7500}{f_{PWM}(kHz)}$$

(3)

Once R<sub>RT</sub> has been determined, the D<sub>MAX</sub> resistor (R<sub>DMX</sub>) may be derived.

$$R_{DMX} = R_{RT} \times (2 \times D_{MAX} - 1)$$

(4)

where

D<sub>MAX</sub> is the desired maximum PWM duty-cycle

### 6.3.3 Frequency Dithering (Magnitude and Rate)

Frequency dithering refers to modulating the switching frequency to achieve a reduction in conducted-EMI noise beyond the capability of the line filter alone. The UCC28070A implements a triangular modulation method which results in equal time spent at every point along the switching frequency range. This total range from minimum to maximum frequency is defined as the dither magnitude, and is centered around the nominal switching frequency f<sub>PWM</sub> set with R<sub>RT</sub>. For example, a dither magnitude of 20kHz on a nominal f<sub>PWM</sub> of 100kHz results in a frequency range of 100kHz ±10kHz. Furthermore, the programmed duty-cycle clamp set by R<sub>DMX</sub> remains constant at the programmed value across the entire range of the frequency dithering.

The rate at which f<sub>PWM</sub> traverses from one extreme to the other and back again is defined as the dither rate. For example, a dither rate of 1kHz would linearly modulate the nominal frequency from 110kHz to 90kHz to 110kHz once every millisecond. A good initial design target for dither magnitude is ±10% of f<sub>PWM</sub>. Most boost components can tolerate such a spread in fPWM. The designer can then iterate around there to find the best compromise between EMI reduction, component tolerances, and loop stability.

The desired dither magnitude is set by a resistor from the RDM pin to GND, of value calculated with 方程式 5:

$$R_{RDM}(k\Omega) = \frac{937.5}{f_{DM}(kHz)}$$

(5)

Once the value of R<sub>RDM</sub> is determined, the desired dither rate may be set by a capacitor from the CDR pin to GND, of value calculated with 方程式 6:

$$C_{CDR}(pF) = 66.7 \times \left(\frac{R_{RDM}(k\Omega)}{f_{DR}(kHz)}\right)$$

(6)

Frequency dithering may be fully disabled by forcing the CDR pin > 5V or by connecting it to VREF (6V) and connecting the RDM pin directly to GND. (If populated, the relatively high impedance of the RDM resistor may allow system switching noise to couple in and interfere with the controller timing functions if not bypassed with a low impedance path when dithering is disabled.)

If an external frequency source is used to synchronize f<sub>PWM</sub> and frequency dithering is desired, the external frequency source must provide the dither magnitude and rate functions as the internal dither circuitry is disabled to prevent undesired performance during synchronization. (See External Clock Synchronization for more details.)

Product Folder Links: UCC28070A

Copyright © 2024 Texas Instruments Incorporated

提交文档反馈

#### 6.3.4 External Clock Synchronization

The UCC28070A has also been designed to be easily synchronized to almost any external frequency source. By disabling frequency dithering (pulling CDR > 5V), the SYNC circuitry is enabled permitting the internal oscillator to be synchronized with pulses presented on the RDM pin. To ensure that a precise 180 $^{\circ}$  phase shift is maintained between the GDA and GDB outputs, the frequency ( $f_{SYNC}$ ) of the pulses presented at the RDM pin must be at twice the desired  $f_{PWM}$ . For example, if a 100kHz switching frequency is desired, the  $f_{SYNC}$  must be 200kHz.

$$f_{PWM} = \frac{f_{SYNC}}{2} \tag{7}$$

To ensure the internal oscillator does not interfere with the SYNC function,  $R_{RT}$  must be sized to set the internal oscillator frequency about 10% below the minimum expected  $f_{SYNC}$ .

$$R_{RT}(k\Omega) = \frac{15000}{f_{SYNC}(kHz)} \times 1.1$$

(8)

It must be noted that the PWM modulator gain is reduced by a factor equivalent to the scaled  $R_{RT}$  due to a direct correlation between the PWM ramp current and  $R_{RT}$ . Adjustments to the current-loop gains must be made accordingly, using the  $k_{SYNC}$  factor as indicated in Current Loop Compensation.

It must also be noted that the maximum duty-cycle clamp programmability is affected during external synchronization. The internal timing circuitry responsible for setting the maximum duty cycle is initiated on the falling edge of the synchronization pulse. Therefore, the selection of  $R_{DMX}$  becomes dependent on the synchronization pulse width ( $t_{SYNC}$ ).

$$D_{SYNC} = t_{SYNC} \times f_{SYNC}$$

(For use in  $R_{DMX}$  equation immediately below.) (9)

$$R_{DMX}(k\Omega) = \left(\frac{15000}{f_{SYNC}(kHz)}\right) \times \left(2 \times D_{MAX} - 1 - D_{SYNC}\right)$$

(10)

Consequently to minimize the impact of the t<sub>SYNC</sub> it is clearly advantageous to use the smallest synchronization pulse width feasible.

#### 备注

When external synchronization is used, a propagation delay of approximately 50ns to 100ns exists between internal timing circuits and the falling edge of the SYNC signal, which may result in reduced OFF-time at the highest of switching frequencies. Therefore, at high SYNC frequencies  $R_{DMX}$  value must be adjusted downward slightly by  $(t_{SYNC} - 0.1 \,\mu\,s) / t_{SYNC}$  to compensate. At lower SYNC frequencies, this delay becomes an insignificant fraction of the PWM period, and can be neglected.

#### 备注

The oscillator in the UCC28070A device is not designed to accommodate wide variations in the external SYNC frequency. Do not allow the SYNC frequency variation to exceed  $\pm 10\%$  of the nominal  $f_{SYNC}$  as used in  $\hbar$ 2. Excessive variation of  $f_{SYNC}$  can cause malfunction of the controller to occur.  $R_{RT}$  value must be calculated at the lowest  $f_{SYNC}$ .

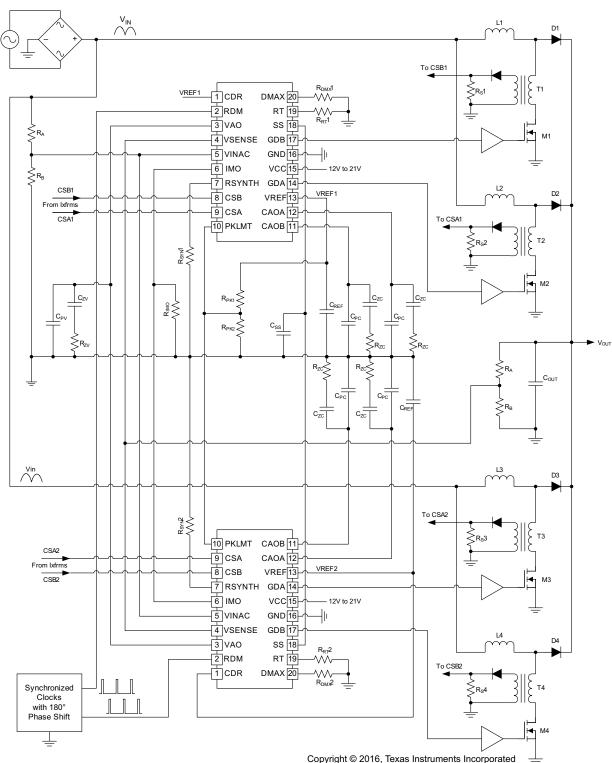

#### 6.3.5 Multi-phase Operation

External synchronization also facilitates using more than 2 phases for interleaving. Multiple UCC28070A devices can easily be paralleled to add an even number of additional phases for higher-power applications. With appropriate phase-shifting of the synchronization signals, even more input and output ripple current cancellation can be obtained. (An odd number of phases can be accommodated if desired, but the ripple cancellation would not be optimal.) For 4-, 6-, or any 2 × n-phases (where n = the number of UCC28070A controllers), each controller must receive a SYNC signal which is 360/n degrees out of phase with each other. For a 4-phase application interleaving with two controllers, SYNC1 must be 180° out of phase with SYNC2 for optimal ripple cancellation. Similarly for a 6-phase system, SYNC1, SYNC2, and SYNC3 must be 120° out of phase with each other for optimal ripple cancellation.

In a multi-phase interleaved system, each current loop is independent and treated separately; however, there is only one common voltage loop. To maintain a single control loop, all VSENSE, VINAC, SS, IMO, and VAO signals are paralleled, respectively between the n controllers. Where current-source outputs are combined (SS, IMO, VAO), the calculated load impedances must be adjusted by 1/n to maintain the same performance as with a single controller.

### 6.3.6 VSENSE and VINAC Resistor Configuration

The primary purpose of the VSENSE input is to provide the voltage feedback from the output to the voltage control loop. Thus, a traditional resistor-divider network must be sized and connected between the output capacitor and the VSENSE pin to set the desired output voltage based on the 3V regulation voltage on VSENSE.

A unique aspect of the UCC28070A is the need to place the same resistor-divider network on the  $V_{IN}$  side of the inductor to the VINAC pin. This provides the scaled input voltage monitoring needed for the linear multiplier and current synthesizer circuitry. It is not required that the actual resistance of the VINAC network be identical to the VSENSE network, but it is necessary that the attenuation ( $k_R$ ) of the two divider networks be equivalent for proper PFC operation.

$$k_{R} = \frac{R_{B}}{\left(R_{A} + R_{B}\right)} \tag{11}$$

In noisy environments, it may be beneficial for small filter capacitors to be applied to the VSENSE and VINAC inputs to avoid the destabilizing effects of excessive noise on these inputs. If applied, the RC time-constant must not exceed 100  $\mu$  s on the VSENSE input to avoid significant delay in the output transient response. The RC time-constant must also not exceed 100  $\mu$  s on the VINAC input to avoid degrading of the wave-shape zero-crossings. Usually, a time constant of 3 / f<sub>PWM</sub> is adequate to filter out typical noise on VSENSE and VINAC. Some design and test iteration may be required to find the optimal amount of filtering required in a particular application.

提交文档反馈

### 6.3.7 VSENSE and VINAC Open-Circuit Protection

Both the VSENSE and VINAC pins have been designed with an internal 250nA current sink to ensure that in the event of an open circuit at either pin, the voltage is not left undefined, and the UCC28070A remains in a safe operating mode.

图 6-1. Simplified Four-Phase Application Diagram Using Two UCC28070A Devices

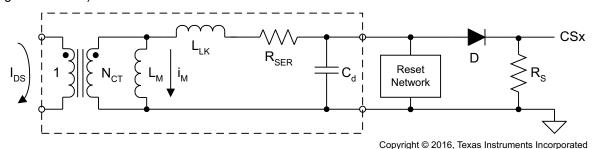

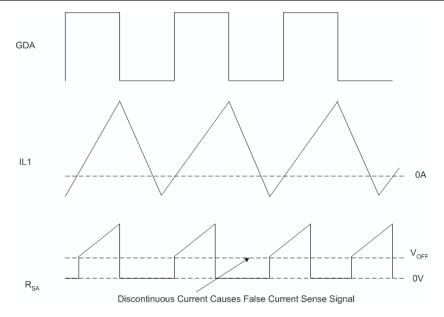

#### 6.3.8 Current Synthesizer

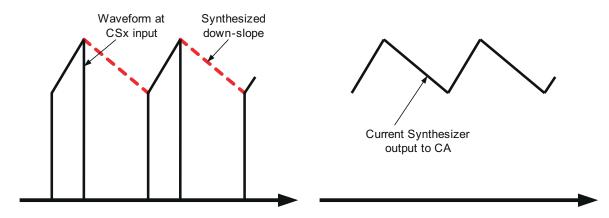

One of the most prominent innovations in the UCC28070A design is the current synthesizer circuitry that synchronously monitors the instantaneous inductor current through a combination of ON-time sampling and OFF-time down-slope emulation.

During the ON-time of the GDA and GDB outputs, the inductor current is recorded at the CSA and CSB pins. respectively, through the current transformer network in each output phase. Meanwhile, the continuous monitoring of the input and output voltages through the VINAC and VSENSE pins permits the UCC28070A to internally recreate the down-slope of the inductor current during the respective OFF-time of each output. Through the selection of the RSYNTH resistor (R<sub>SYN</sub>), based on 方程式 12, the internal response may be adjusted to accommodate the wide range of inductances expected across the wide array of applications.

During inrush surge events at power up and AC drop-out recovery, V<sub>VSENSE</sub> < V<sub>VINAC</sub>, the synthesized downslope becomes zero. In this case, the synthesized inductor current remains above the IMO reference and the current loop drives the duty cycle to zero. This avoids excessive stress on the MOSFETs during the surge event. Once V<sub>VINAC</sub> falls below V<sub>VSENSE</sub>, the duty cycle increases until steady-state operation resumes.

图 6-2. Downslope of the Inductor Current

$$R_{SYN}(k\Omega) = \frac{\left(10 \times N_{CT} \times L_{B}(\mu H) \times k_{R}\right)}{R_{S}(\Omega)}$$

(12)

Product Folder Links: UCC28070A

#### where:

- L<sub>B</sub> = Nominal Zero-Bias Boost Inductance ( μ H)

- $R_S$  = Sense Resistor ( $\Omega$ )

- N<sub>CT</sub> = Current-sense Transformer turns ratio

- $k_R = R_B / (R_A + R_B)$  = the resistor-divider attenuation at the VSENSE and VINAC pins

Copyright © 2024 Texas Instruments Incorporated

提交文档反馈

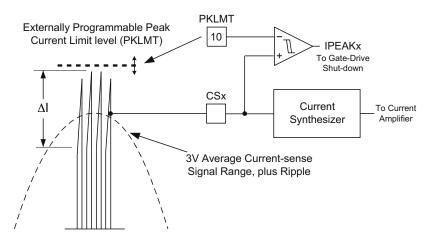

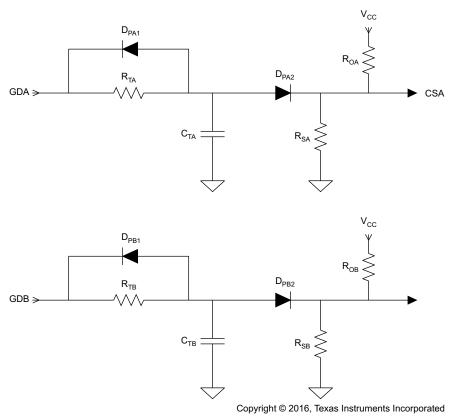

# 6.3.9 Programmable Peak Current Limit

The UCC28070A has been designed with a programmable cycle-by-cycle peak current limit dedicated to disabling either the GDA or GDB output whenever the corresponding current-sense input (CSA or CSB, respectively) rises above the voltage established on the PKLMT pin. Once an output has been disabled through the detection of peak current limit, the output remains disabled until the next clock cycle initiates a new PWM period. The programming range of the PKLMT voltage extends to upwards of 4V to permit the full use of the 3V average current sense signal range; however, note that the linearity of the current amplifiers begins to compress above 3.6V.

A resistor-divider network from VREF to GND can easily program the peak current limit voltage on PKLMT, provided the total current out of VREF is less than 2mA to avoid drooping of the 6V VREF voltage. TI recommends a load of less than 0.5mA, but if the resistance on PKLMT is very high, TI recommends a small filter capacitor on PKLMT to avoid operational problems in high-noise environments.

图 6-3. Externally Programmable Peak Current Limit

Peak Current Limit is a protection feature and has no built-in slope-compensation for duty-cycles greater than 0.5. During occurrences of peak limiting, sub-harmonic oscillation will occur with possible audible noise from such oscillation. If the PKLMT feature is re-purposed to implement a steady-state power-limit function, suitable slope compensation should be added by external means.

#### 6.3.10 Linear Multiplier and Quantized Voltage Feed Forward

The UCC28070A multiplier generates a reference current which represents the desired wave shape and proportional amplitude of the AC input current. This current is converted to a reference voltage signal by the  $R_{IMO}$  resistor which is scaled in value to match the voltage of the current-sense signals. The instantaneous multiplier current is dependent upon the rectified, scaled input voltage  $V_{VINAC}$  and the voltage-error amplifier output  $V_{VAO}$ .  $V_{VINAC}$  conveys three pieces of information to the multiplier:

- · The overall wave-shape of the input voltage (typically sinusoidal)

- The instantaneous input voltage magnitude at any point in the line cycle

- · The rms level of the input voltage.

V<sub>VAO</sub> represents the total output power of the PFC preregulator.

A major innovation in the UCC28070A multiplier architecture is the internal quantized  $V_{RMS}$  feed-forward ( $Q_{VFF}$ ) circuitry, which eliminates the requirement for external filtering of the VINAC signal and the subsequent slow response to transient line variations. A unique circuit algorithm detects the transition of the peak of  $V_{VINAC}$  through seven thresholds and generates an equivalent VFF level centered within the 8- $Q_{VFF}$  ranges. The boundaries of the ranges expand with increasing  $V_{IN}$  to maintain an approximately equal-percentage delta between levels. These 8- $Q_{VFF}$  levels are spaced to accommodate the full universal line range of  $85V_{RMS}$  to  $265V_{RMS}$ .

Copyright © 2024 Texas Instruments Incorporated

A great benefit of the Q<sub>VFF</sub> architecture is that the fixed k<sub>VFF</sub> factors eliminate any contribution to distortion of the multiplier output, unlike an externally-filtered VINAC signal which unavoidably contains 2nd-harmonic distortion components. Furthermore, the Q<sub>VFF</sub> algorithm allows for rapid response to both increasing and decreasing changes in input rms voltage so that disturbances transmitted to the PFC output are minimized. 5% hysteresis in the level thresholds help avoid chattering between  $Q_{VFF}$  levels for  $V_{VINAC}$  voltage peaks near a particular threshold or containing mild ringing or distortion. The  $Q_{VFF}$  architecture requires that the input voltage be largely sinusoidal, and relies on detecting zero-crossings to adjust  $Q_{VFF}$  downward on decreasing input voltage. Zerocrossings are defined as V<sub>VINAC</sub> falling below 0.7V for at least 50 µ s, typically.

表 6-1 shows the relationship between the various  $\mathsf{V}_\mathsf{VINAC}$  peak voltages and the corresponding  $\mathsf{k}_\mathsf{VFF}$  terms for the multiplier equation.

| LEVEL | V <sub>VINAC</sub> PEAK VOLTAGE        | k <sub>VFF</sub> (V <sup>2</sup> ) | V <sub>IN</sub> PEAK VOLTAGE (1) |  |  |

|-------|----------------------------------------|------------------------------------|----------------------------------|--|--|

| 8     | 2.6V ≤ V <sub>VINAC(pk)</sub>          | 3.857                              | >345V                            |  |  |

| 7     | 2.25V ≤ V <sub>VINAC(pk)</sub> < 2.6V  | 2.922                              | 300V to 345V                     |  |  |

| 6     | 1.95V ≤ V <sub>VINAC(pk)</sub> < 2.25V | 2.199                              | 260V to 300V                     |  |  |

| 5     | 1.65V ≤ V <sub>VINAC(pk)</sub> < 1.95V | 1.604                              | 220V to 260V                     |  |  |

| 4     | 1.4V ≤ V <sub>VINAC(pk)</sub> < 1.65V  | 1.156                              | 187V to 220V                     |  |  |

| 3     | 1.2V ≤ V <sub>VINAC(pk)</sub> < 1.4V   | 0.839                              | 160V to 187V                     |  |  |

| 2     | $1V \leq V_{VINAC(pk)} < 1.2V$         | 0.6                                | 133V to 160V                     |  |  |

| 1     | $V_{VINAC(pk)} \leqslant 1V$           | 0.398                              | <133V                            |  |  |

表 6-1. V<sub>VINAC</sub> Peak Voltages

The multiplier output current I<sub>IMO</sub> for any line and load condition can thus be determined using 方程式 13:

$$I_{IMO} = \frac{17 \,\mu\text{A} \times \left(\text{V}_{VINAC}\right) \times \left(\text{V}_{VAO} - 1\right)}{\text{k}_{VFF}} \tag{13}$$

Because the  $k_{VFF}$  value represents the scaled  $(V_{RMS})^2$  at the center of a level,  $V_{VAO}$  adjusts slightly upwards or downwards when V<sub>VINAC(pk)</sub> is either lower or higher than the center of the Q<sub>VFF</sub> voltage range to compensate for the difference. This is automatically accomplished by the voltage loop control when V<sub>IN</sub> varies, both within a level and after a transition between levels.

The output of the voltage-error amplifier (V<sub>VAO</sub>) is clamped at 5V, which represents the maximum PFC output power. This value is used to calculate the maximum reference current at the IMO pin, and sets a limit for the maximum input power allowed (and, as a consequence, limits maximum output power).

Unlike a continuous  $V_{FF}$  situation, where maximum input power is a fixed power at any  $V_{RMS}$  input, the discrete Q<sub>VFF</sub> levels permit a variation in maximum input power within limited boundaries as the input V<sub>RMS</sub> varies within each level.

The lowest maximum power limit occurs at the  $V_{VINAC}$  voltage of 0.76V, while the highest maximum power limit occurs at the increasing threshold from level-1 to level-2. This pattern repeats at every level transition threshold, considering that decreasing thresholds are 95% of the increasing threshold values. Below V<sub>VINAC</sub> = 0.76V, P<sub>IN</sub> is always less than  $P_{\text{IN(max)}}$ , falling linearly to zero with decreasing input voltage.

For example, to design for the lowest maximum power allowable, determine the maximum steady-state (average) output power required of the PFC preregulator and add some additional percentage to account for line drop-out recovery power (to recharge C<sub>OUT</sub> while full load power is drawn) such as 10% or 20% of P<sub>OUT(max)</sub>. Then apply the expected efficiency factor to find the lowest maximum input power allowable:

Product Folder Links: UCC28070A

Copyright © 2024 Texas Instruments Incorporated

The V<sub>IN</sub> peak voltage boundary values listed above are calculated based on a 400V PFC output voltage and the use of a matched resistor-divider network ( $k_R = 3V / 400V = 0.0075$ ) on VINAC and VSENSE (as required for current synthesis). When  $V_{OUT}$  is designed to be higher or lower than 400V,  $k_R = 3V / V_{OUT}$ , and the  $V_{IN}$  peak voltage boundary values for each  $Q_{VFF}$  level adjust to  $V_{VINAC(pk)} / k_R$ .

$$P_{IN(max)} = \frac{1.1 \times P_{OUT(max)}}{\eta}$$

(14)

At the  $P_{IN(max)}$  design threshold,  $V_{VINAC}$  = 0.76V, hence  $Q_{VFF}$  = 0.398 and input  $V_{AC}$  = 73 $V_{RMS}$  (accounting for 2V bridge-rectifier drop) for a nominal 400V output system.

$$I_{IN(rms)} = \frac{P_{IN(max)}}{73 V_{RMS}} \tag{15}$$

$$I_{\text{IN(pk)}} = 1.414 \times I_{\text{IN(rms)}} \tag{16}$$

This  $I_{IN(pk)}$  value represents the combined average current through the boost inductors at the peak of the line voltage. Each inductor current is detected and scaled by a current-sense transformer (CT). Assuming equal currents through each interleaved phase, the signal voltage at each current sense input pin (CSA and CSB) is developed across a sense resistor selected to generate approximately 3V based on  $\frac{1}{2}I_{IN(pk)} \times R_S / N_{CT}$ , where  $R_S$  is the current sense resistor and  $N_{CT}$  is the CT turns-ratio.

I<sub>IMO</sub> is then calculated at that same lowest maximum-power point, as:

$$I_{\text{IMO(max)}} = 17 \ \mu\text{A} \times \frac{(0.76 \ \text{V})(5 \ \text{V} - 1 \ \text{V})}{0.398} = 130 \ \mu\text{A} \tag{17}$$

R<sub>IMO</sub> is selected such that:

$$R_{\text{IMO}} \times I_{\text{IMO(max)}} = \frac{1}{2} \times I_{\text{IN(pk)}} \times \frac{R_{\text{S}}}{N_{\text{CT}}}$$

(18)

Therefore:

$$R_{IMO} = \frac{\left(\frac{1}{2} \times I_{IN(pk)} \times R_{S}\right)}{\left(N_{CT} \times I_{IMO(max)}\right)}$$

(19)

At the increasing side of the level-1 to level-2 threshold, note that the IMO current would allow higher input currents at low-line:

$$I_{\text{IMO(L1-L2)}} = 17 \ \mu\text{A} \times \frac{(1 \ \text{V})(5 \ \text{V} - 1 \ \text{V})}{0.398} = 171 \ \mu\text{A} \tag{20}$$

However, this current may easily be limited by the programmable peak current limiting (PKLMT) feature of the UCC28070A if required by the power stage design.

The same procedure can be used to find the lowest and highest input power limits at each of the  $Q_{VFF}$  level transition thresholds. At higher line voltages, where the average current with inductor ripple is traditionally below the PKLMT threshold, the full variation of maximum input power is seen, but the input currents are inherently below the maximum acceptable current levels of the power stage.

The performance of the multiplier in the UCC28070A has been significantly enhanced when compared to previous generation PFC controllers, with high linearity and accuracy over most of the input ranges. The accuracy is at its worst as  $V_{VAO}$  approaches 1V because the error of the ( $V_{VAO}$  - 1) subtraction increases and begins to distort the IMO reference current to a greater degree.

### 6.3.11 Enhanced Transient Response (VA Slew-Rate Correction)

Due to the low-voltage loop bandwidth required to maintain proper PFC and ignore the slight ripple at twice line frequency on the output, the response of ordinary controllers to input voltage and load transients are also slow. However, the  $Q_{VFF}$  function effectively handles the line transient response with the exception of any minor adjustments needed within a  $Q_{VFF}$  level. Load transients on the other hand can only be handled by the voltage loop; therefore, the UCC28070A has been designed to improve its transient response by pulling up on the output of the voltage amplifier ( $V_{VAO}$ ) with an additional 100  $\mu$  A of current in the event the voltage on VSENSE drops below 93% of regulation (2.79V). During a soft-start cycle, when  $V_{VSENSE}$  is ramping up from the 0.75V PFC Enable threshold, the 100  $\mu$  A correction current source is disabled to ensure the gradual and controlled ramping of output voltage and current during a soft start.

# 6.3.12 Voltage Biasing (V<sub>CC</sub> and V<sub>VREF</sub>)

The UCC28070A operates within a  $V_{CC}$  bias supply range of 10V to 21V. An undervoltage lockout (UVLO) threshold prevents the PFC from activating until  $V_{CC} > 10.2$ V, and 1V of hysteresis assures reliable start-up from a possibly low-compliance bias source. An internal 25V Zener-like clamp on the VCC pin is intended only to protect the device from brief energy-limited surges from the bias supply, and must not be used as a regulator with a current-limited source.

At minimum, a  $0.1~\mu$  F ceramic bypass capacitor must be applied from VCC to GND close to the device pins to provide local filtering of the bias supply. Larger values may be required depending on  $I_{CC}$  peak current magnitudes and durations to minimize ripple voltage on VCC.

To provide a smooth transition out of UVLO and to make the 6V voltage reference available as early as possible, the output from VREF is enabled when  $V_{CC}$  exceeds 8V typically.

The VREF circuitry is designed to provide the biasing of all internal control circuits and for limited use externally. At minimum, a 22nF ceramic bypass capacitor must be applied from VREF to GND close to the device pins to ensure stability of the circuit. External load current on the VREF pin must be limited to less than 2mA, or degraded regulation may result.

#### 6.3.13 PFC Enable and Disable