# AFE74xx Power Dissipation Comparison Across Modes

Russell Hoppenstein

#### ABSTRACT

The AFE7422 and AFE7444 (AFE74xx) are a family of 4T4R RF sampling transceivers. There are a variety of ways to configure these devices related to sampling frequency, data rate, number of SerDes lanes, number of channels, and FDD or TDD duplex options. Each option impacts the power consumption of the device. This document illustrates the power consumption trade-offs between modes so that the designer can implement the best options for the system at the optimum power dissipation. This document also provides insights into the power consumption relative to device parameters with the intent to showcase which parameters have the most significant impact on current consumption.

| 1 | Introduction   | 2 |

|---|----------------|---|

| 2 | Power Analysis | 3 |

| 3 | Conclusion     | 6 |

|   |                |   |

#### List of Figures

| 1 | Four-Channel Power Dissipation Across Data Rate, Sample Clock, and SerDes Lanes | 3 |

|---|---------------------------------------------------------------------------------|---|

| 2 | Two-Channel Power Dissipation Across Data Rate, Sample Clock, and SerDes Lanes  | 4 |

| 3 | Power Dissipation vs External Sample Clock                                      | 4 |

| 4 | Power Dissipation in TDD Mode                                                   | 5 |

|   |                                                                                 |   |

#### List of Tables

| 1 | Power Dissipation Analysis Parameters   | 6 |

|---|-----------------------------------------|---|

|   | T Ower Dissipation Analysis I alameters | J |

### Trademarks

All trademarks are the property of their respective owners.

#### Introduction

## 1 Introduction

The AFE7422 and AFE7444 (AFE74xx) are a family of 4T4R RF sampling transceivers. There are a variety of ways to configure the device in order to achieve required system performance and allocation and to minimize power consumption. The parameters varied are:

- Clock frequency

- Internal: 5898.24 MHz or 8847.36 MHz

- External: 5898.24 MHz to 3500 MHz

- Interpolation rate and decimation rate

- Number of lanes

- Channel count: 2 or 4

- Duplex options: FDD or TDD

These parameters are not all independent. Interpolation and decimation rate, sample frequency, number of lanes, and channel count determine appropriate LMFS JESD204B parameters and SerDes speed. For this analysis, the SerDes speed is limited to 10 Gbps or less, and the TX/RX SerDes speeds is kept the same.

The relationship to these parameters is:

- Fdata = Fs (Sampling Frequency) / INT

- Total Bit Rate = Fdata \* 16-bits \* 10/8 (encoding) \* I/Q Channels \* # of Channels

- Bit Rate per Lane = Total Bit Rate / Number of Lanes.

Here is an example calculation with the following parameters:

- Fs = 8847.36 MSPS

- INT = 18x

- 4 I/Q Channels

- 8 Lanes

The calculations yield:

- Fdata = 8847.36 MSPS / 18 = 491.52 MSPS

- Total Bit Rate = 491.52 MSPS \* 16 \* 10/8 \* 2 (I/Q) \* 4 (Channels) = 78.6432 Gbps

- Bit Rate per lane = 78.6432 / 8 = 9.8304 Gbps per lane

In this example, the SerDes speed is just at the (artificial) limit. Reducing the speed requires increasing the number of lanes (except the value is already at the limit), or reducing the sampling clock and/or increasing the interpolation/decimation (that is, reducing data rate) or decreasing the channel count. Reducing the data rate decreases bandwidth capability. Reducing sampling clock generally reduces higher-frequency operation. Although these modifications limit the performance capability of the device, the modifications reduce power consumption. The designer has the flexibility to weigh the trade-offs in order to meet system requirements.

Official power consumption specifications are outlined in the data sheet. The power consumption parameters used in this analysis were taken on a single device on the AFE7422EVM and AFE7444EVM evaluation modules and may have slight differences due to power management configurations. The primary intent is to provide relative consumption performance across different parameters.

#### www.ti.com

## 2 Power Analysis

# 2.1 4-Channel FDD Power Dissipation

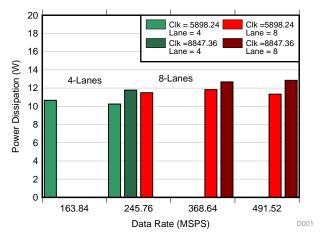

Figure 1 shows the power dissipation for four channels operating in FDD for a variety of data rates over two sample clock frequencies and across either four or eight lanes.

### Figure 1. Four-Channel Power Dissipation Across Data Rate, Sample Clock, and SerDes Lanes

The far-right power dissipation is at the highest sample clock and highest number of lanes operating at the highest (within this analysis) data rate. This mode corresponds to the E1 mode within the data sheet and represents the highest power consumption reference point. The key observations from the data show:

- Reducing clock from ~9 GSPS to ~6 GSPS saves 1 W to 1.5 W of dissipation

- Reducing only the data rate has minimal impact on power dissipation; may see some increase due to different digital decimation and interpolation configuration.

- Reducing lane count in half provides about 1 W to 1.25 W power savings.

www.ti.com

Power Analysis

# 2.2 2-Channel FDD Power Dissipation

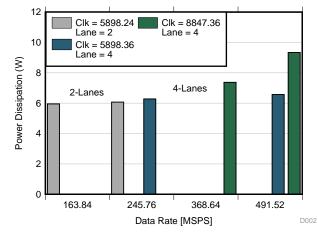

Figure 2 shows the power dissipation for two channels operating in FDD for a variety of data rates over two sample clock frequencies and across either two, four, or eight lanes.

Figure 2. Two-Channel Power Dissipation Across Data Rate, Sample Clock, and SerDes Lanes

The following key observations for this data are:

- Reducing from four channels to two channels saves approximately 3.5 W to 5 W

- Reducing from ~9-GSPS clock to ~6-GHz clock yield savings of ~2 W

- · Reducing only the data rate has minimal impact on power dissipation

- Reducing lane count in half provides about 200 mW power savings.

Operating with ~6-GHz clock in two lanes at the lower data rate results in total power consumption just under 6 W, which is a good threshold for narrow-band systems.

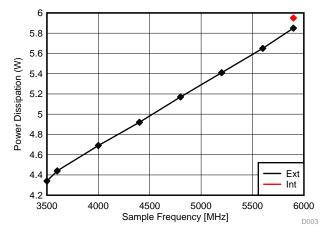

# 2.3 Power Dissipation over Sampling Frequency

Reducing the sample clock rate further reduces the power consumption. The internal PLL/VCO minimum limit is approximately 6-GHz, but an external clock provides any arbitrary value. The power consumption as a function of clock frequency is shown in Figure 3.

Figure 3. Power Dissipation vs External Sample Clock

#### www.ti.com

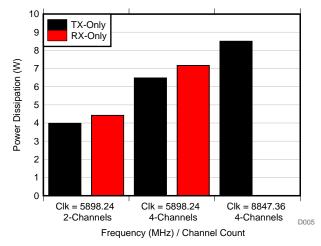

# 2.4 TDD Power Dissipation

The previous analysis assumed FDD operation, implying the transmitter and receiver operated simultaneously. In TDD applications, the transmitter and receiver alternate. As expected, the average current is drastically reduced when only one side is on at a time. Figure 4 shows the power dissipation with ~6-GHz clock in TDD mode across four and two channels. For reference, the ~9-GHz, TX-only, quad-channel data point is shown, which corresponds to mode E2 in the data sheet.

Figure 4. Power Dissipation in TDD Mode

The power dissipation in TDD mode in the two-channel configuration operating with a ~6-GHz clock is less than 4.5 W.

# 3 Conclusion

The configuration of the AFE74xx device directly impacts power dissipation. In critical power-consumption systems or thermally constrained mechanics, the variables outlined within this report provide a means to adjust the parameters in order to estimate power consumption for a given system constraint, such as bandwidth requirements or SerDes speed limitation. Table 1 shows the details of the configurations used in the graphs and analysis.

| Clk Input | Clk     | Int | Dec | DataRate | Channels | Lanes | SerDes/Lane | Duplex | Pdiss |

|-----------|---------|-----|-----|----------|----------|-------|-------------|--------|-------|

| Int       | 8847.36 | 18  | 6   | 491.52   | 4        | 8     | 9830.4      | FDD    | 12.85 |

| Int       | 8847.36 | 24  | 8   | 368.64   | 4        | 8     | 7372.8      | FDD    | 12.68 |

| Int       | 5898.24 | 12  | 6   | 491.52   | 4        | 8     | 9830.4      | FDD    | 11.33 |

| Int       | 5898.24 | 16  | 8   | 368.64   | 4        | 8     | 7372.8      | FDD    | 11.83 |

| Int       | 5898.24 | 24  | 12  | 245.76   | 4        | 8     | 4915.2      | FDD    | 11.49 |

| Int       | 8847.36 | 36  | 12  | 245.76   | 4        | 4     | 9830.4      | FDD    | 11.78 |

| Int       | 5898.24 | 24  | 12  | 245.76   | 4        | 4     | 9830.4      | FDD    | 10.25 |

| Int       | 5898.24 | 36  | 18  | 163.84   | 4        | 4     | 6553.6      | FDD    | 10.66 |

| Int       | 8847.36 | 18  | 6   | 491.52   | 2        | 4     | 9830.4      | FDD    | 9.34  |

| Int       | 8847.36 | 24  | 8   | 368.64   | 2        | 4     | 7372.8      | FDD    | 7.37  |

| Int       | 5898.24 | 12  | 6   | 491.52   | 2        | 4     | 9830.4      | FDD    | 6.57  |

| Int       | 5898.24 | 24  | 12  | 245.76   | 2        | 4     | 4915.2      | FDD    | 6.28  |

| Int       | 5898.24 | 24  | 12  | 245.76   | 2        | 2     | 9830.4      | FDD    | 6.07  |

| Int       | 5898.24 | 36  | 18  | 163.84   | 2        | 2     | 6553.6      | FDD    | 5.95  |

| Ext       | 5898.24 | 36  | 18  | 163.84   | 2        | 2     | 6553.6      | FDD    | 5.85  |

| Ext       | 5600    | 36  | 18  | 155.56   | 2        | 2     | 6222.2      | FDD    | 5.65  |

| Ext       | 5200    | 36  | 18  | 144.44   | 2        | 2     | 5777.8      | FDD    | 5.41  |

| Ext       | 4800    | 36  | 18  | 133.33   | 2        | 2     | 5333.3      | FDD    | 5.17  |

| Ext       | 4400    | 36  | 18  | 122.22   | 2        | 2     | 4888.9      | FDD    | 4.92  |

| Ext       | 4000    | 36  | 18  | 111.11   | 2        | 2     | 4444.4      | FDD    | 4.69  |

| Ext       | 3600    | 36  | 18  | 100.00   | 2        | 2     | 4000.0      | FDD    | 4.44  |

| Ext       | 3500    | 36  | 18  | 97.22    | 2        | 2     | 3888.9      | FDD    | 4.34  |

| Int       | 5898.24 | 24  | 12  | 245.76   | 2        | 4     | 4915.2      | TDD-TX | 3.98  |

| Int       | 5898.24 | 24  | 12  | 245.76   | 2        | 4     | 4915.2      | TDD-RX | 4.42  |

| Int       | 5898.24 | 24  | 12  | 245.76   | 4        | 8     | 4915.2      | TDD-TX | 6.48  |

| Int       | 5898.24 | 24  | 12  | 245.76   | 4        | 8     | 4915.2      | TDD-RX | 7.17  |

| Int       | 8847.36 | 18  | 6   | 491.52   | 4        | 8     | 9830.4      | TDD-TX | 8.5   |

# **Table 1. Power Dissipation Analysis Parameters**

AFE74xx Power Dissipation Comparison Across Modes

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated